### NASA Technical Memorandum 4259

# Efficient Multitasking of Choleski Matrix Factorization on CRAY Supercomputers

Andrea L. Overman and Eugene L. Poole

- Estato anal (Apparenta

(NASA-TM-4259) EFFICIENT MULTITASKING OF CHOLESKI MATRIX FACTURIZATION ON CRAY SUPERCOMPUTERS (NASA) 63 p CSCL 09B

N92-10302

Unclas H1/61 0000169

# Efficient Multitasking of Choleski Matrix Factorization on CRAY Supercomputers

Andrea L. Overman Langley Research Center Hampton, Virginia

Eugene L. Poole Analytical Services & Materials, Inc. Hampton, Virginia

## NASA

National Aeronautics and Space Administration Office of Management Scientific and Technical Information Program The use of trademarks or names of manufacturers in this report is for accurate reporting and does not constitute an official endorsement, either expressed or implied, of such products or manufacturers by the National Aeronautics and Space Administration.

| NASA TM-4259                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | National Aeronautics and                                                                                                                                                                                                                                                                                                                                                                                                                             | Report Doc                                                                                                                                                                                                                                                                                                                                                                               | cumentation Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Efficient Multitasking of Choleski Matrix Factorization on CRAY Supercomputers  7. Author(s) Andrea L. Overman and Eugene L. Poole  8. Performing Organization Name and Address NASA Langley Research Center Hampton, VA 23665-5225  12. Sponsoring Agency Name and Address National Aeronautics and Space Administration Washington, DC 20546-0001  13. Supplementary Notes Andrea L. Overman: Langley Research Center, Hampton, Virginia. Eugene L. Poole: Analytical Services & Materials, Inc., Hampton, Virginia. Eugene L. Poole: Analytical Services & Materials, Inc., Hampton, Virginia. Eugene L. Poole: Analytical Services & Materials, Inc., Hampton, Virginia. Eugene L. Poole: Analytical Services & Materials, Inc., Hampton, Virginia. 16. Abstract This paper describes a Choleski method used to solve linear systems of equations that arise in large-scale structural analyses. The method uses a novel variable-band storage scheme and is structured to exploit fast local memory caches while minimizing data access delays between main memory and vector registers. Several parallel implementations of this method are described for the CRAY-2 and CRAY Y-MP computers demonstrating the use of microtasking and autotasking directives. A portable parallel language, FORCE, is used for comparison with the microtasked and autotasked implementations. Results are presented comparing the matrix factorization times for three representative structural analysis problems from runs made in both dedicated and multiuser modes on both the CRAY-2 and CRAY Y-MP computers. Both CPU (central processing unit) times and wall clock times are given for the parallel implementations and are compared with single-processor times of the same algorithm. Computation rates over 1 GIGAFLOPS on an eight-processor CRAY Y-MP are demonstrated as measured by wall clock time in a dedicated environment. Reduced wall clock times for the parallel implementations relative to the single-processor implementation of the same Choleski algorithm are also demonstrated for runs made in a mult | 1. Report No.                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2. Government Accession N                                                                                                                                                                                                                                                                                                                                                                | Jo. 3. Recipient's Catalog No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Efficient Multitasking of Choleski Matrix Factorization on CRAY Supercomputers  7. Author(s) Andrea L. Overman and Eugene L. Poole  8. Performing Organization Report No. L-16901  10. Work Unit No. 505-90-52-02  11. Contract or Grant No.  12. Sponsoring Agency Name and Address NASA Langley Research Center Hampton, VA 23665-5225  13. Type of Report and Period Covere Washington, DC 20546-0001  14. Sponsoring Agency Name and Address National Aeronautics and Space Administration Washington, DC 20546-0001  15. Supplementary Notes Andrea L. Overman: Langley Research Center, Hampton, Virginia. Eugene L. Poole: Analytical Services & Materials, Inc., Hampton, Virginia. 16. Abstract This paper describes a Choleski method used to solve linear systems of equations that arise in large-scale structural analyses. The method used to solve linear systems of equations that arise in large-scale structural analyses. The method uses a novel variable-band storage scheme and is structured to exploit fast local memory caches while minimizing data access delays between main memory and vector registers. Several parallel implementations of this method are described for the CRAY-2 and CRAY V-MP computers demonstrating the use of microtasking and autotasking directives. A portable parallel language, FORCE, is used for comparison with the microtasked and autotasked implementations. Results are given for the parallel implementations and are compared with single-processor by the caches are given for the parallel implementations and are compared with single-processor of the same algorithm. Computation rates over 1 GIGAFLOP (1 billion floating point operations per second) on a four-processor CRAY-2 and over 2 GIGAFLOPS on an eight-processor of the same algorithm. Computation rates over 1 GIGAFLOP (1 billion floating point operations per second) on a four-processor CRAY-2 and over 2 GIGAFLOPS on an eight-processor implementation of the same Choleski algorithm are also demonstrated for runs made in a multiuser environment.  17. Key Words (Suggeste |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                          | 5. Report Date                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Supercomputers  6. Performing Organization Code Andrea L. Overman and Eugene L. Poole  1. Performing Organization Name and Address NASA Langley Research Center Hampton, VA 23665-5225  1. Contract or Grant No.  2. Sponsoring Agency Name and Address National Aeronautics and Space Administration Washington, DC 20546-0001  15. Supplementary Notes Andrea L. Overman: Langley Research Center, Hampton, Virginia. Eugene L. Poole: Analytical Services & Materials, Inc., Hampton, Virginia. Eugene L. Poole: Analytical Services & Materials, Inc., Hampton, Virginia. 16. Abstract This paper describes a Choleski method used to solve linear systems of equations that arise in large-scale structural analyses. The method uses a novel variable-band storage scheme and is structured to exploit fast local memory caches while minimizing data access delays between main memory and vector registers. Several parallel implementations of this method are described for the CRAY-2 and CRAY Y-MP computers demonstrating the use of microtasking and autotasking directives. A portable parallel language, FORCE, is used for comparison with the microtasked and autotasked implementations. Results are presented comparing the matrix factorization times for three representative structural analysis problems from runs made in both dedicated and multiuser modes on both the CRAY-2 and CRAY Y-MP computers. Both CPU (central processing unit) times and wall clock times are given for the parallel implementations and are compared with single-processor times of the same algorithm. Computation rates over 1 GIGAFLOPS on an eight-processor GRAY-2 and over 2 GIGAFLOPS on an eight-processor implementation of the same Choleski algorithm are also demonstrated for runs made in a multiuser environment.  11. Key Words (Suggested by Author(s)) Choleski factorization CRAY-2/CRAY Y-MP Parallel processing/vectorization Macrotasking, microtasking, and autotasking FORCE preprocessor                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      | on on CRAY   September 1991                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Andrea L. Overman and Eugene L. Poole  D. Performing Organization Name and Address NASA Langley Research Center Hampton, VA 23665-5225  11. Contract or Grant No.  12. Sporssoring Agency Name and Address National Aeronautics and Space Administration Washington, DC 20546-0001  13. Type of Report and Period Covere Technical Memorandum Washington, DC 20546-0001  14. Sponsoring Agency Code  15. Supplementary Notes Andrea L. Overman: Langley Research Center, Hampton, Virginia. Eugene L. Poole: Analytical Services & Materials, Inc., Hampton, Virginia. 16. Abstract This paper describes a Choleski method used to solve linear systems of equations that arise in large-scale structural analyses. The method uses a novel variable-band storage scheme and is structured to exploit fast local memory caches while minimizing data access delays between main memory and vector registers. Several parallel implementations of this method are described for the CRAY-2 and CRAY Y-MP computers demonstrating the use of microtasking and autotasking directives. A portable parallel language, FORCE, is used for comparison with the microtasked and autotasked implementations. Results are presented comparing the matrix factorization times for three representative structural analysis problems from runs made in both dedicated and multiuser modes on both the CRAY-2 and CRAY Y-MP computers. Both CPU (central processing unit) times and wall clock times are given for the parallel implementations and are compared with single-processor times of the same algorithm. Computation rates over 1 GIGAFLOP (1 billion floating point operations per second) on a four-processor CRAY-2 and over 2 GIGAFLOPs on an eight-processor CRAY Y-MP are demonstrated as measured by wall clock time in a dedicated environment. Reduced wall clock times for the parallel implementations relative to the single-processor implementation of the same Choleski algorithm are also demonstrated for runs made in a multiuser environment.  17. Key Words (Suggested by Author(s)) Choleski factorization |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 9. Performing Organization Name and Address NASA Langley Research Center Hampton, VA 23665-5225  12. Sponsoring Agency Name and Address National Aeronautics and Space Administration Washington, DC 20546-0001  13. Supplementary Notes Andrea L. Overman: Langley Research Center, Hampton, Virginia. Eugene L. Poole: Analytical Services & Materials, Inc., Hampton, Virginia. 16. Abstract This paper describes a Choleski method used to solve linear systems of equations that arise in large-scale structural analyses. The method used to solve linear systems of equations that arise in large-scale structural tast local memory caches while minimizing data access delays between main memory and vector registers. Several parallel implementations of this method are described for the CRAY-2 and CRAY Y-MP computers demonstrating the use of microtasking and autotasked implementations. Results are presented comparing the matrix factorization times for three representative structural analysis problems from runs made in both dedicated and multiuser modes on both the CRAY-2 and CRAY Y-MP computers. Both CPU (central processing unit) times and wall clock times are given for the parallel implementations and are compared with single-processor times of the same algorithm. Computation rates over 1 GIGAFLOP (1 billion floating point operations per second) on a four-processor CRAY-2 and over 2 GIGAFLOPS on an eight-processor cRAY Y-MP are demonstrated as measured by wall clock time in a dedicated environment. Reduced wall clock times for the parallel implementations relative to the single-processor implementation of the same Choleski algorithm are also demonstrated for runs made in a multiuser environment.  17. Key Words (Suggested by Author(e)) Choleski factorization CRAY-2/CRAY Y-MP Parallel processing/vectorization Macrotasking, microtasking, and autotasking FORCE preprocessor                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                          | 8. Performing Organization Report No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| NASA Langley Research Center Hampton, VA 23665-5225  13. Type of Report and Period Covere Washington, DC 20546-0001  15. Supplementary Notes Andrea L. Overman: Langley Research Center, Hampton, Virginia. Eugene L. Poole: Analytical Services & Materials, Inc., Hampton, Virginia. 16. Abstract This paper describes a Choleski method used to solve linear systems of equations that arise in large-scale structural analyses. The method used so a novel variable-band storage scheme and is structured to exploit fast local memory caches while minimizing data access delays teween main memory and vector registers. Several parallel implementations of this method are described for the CRAY-2 and CRAY Y-MP computers demonstrating the use of microtasking and autotasking directives. A portable parallel language, FORCE, is used for comparison with the microtasked and autotasked implementations. Results are presented comparing the matrix factorization times for three representative structural analysis problems from runs made in both dedicated and multiuser modes on both the CRAY-2 and CRAY Y-MP computers. Both CPU (central processing unit) times and wall clock times are given for the parallel implementations and are compared with single-processor times of the same algorithm. Computation rates over 1 GIGAFLOPs on an eight-processor CRAY V-MP are demonstrated as measured by wall clock time in a dedicated environment. Reduced wall clock times for the parallel implementations relative to the single-processor implementation of the same Choleski algorithm are also demonstrated for runs made in a multiuser environment.  17. Key Words (Suggested by Author(e)) Choleski factorization CRAY-2/CRAY Y-MP Parallel processing/vectorization Macrotasking, microtasking, and autotasking FORCE preprocessor                                                                                                                                                                                                                                                             | Andrea L. Overman and                                                                                                                                                                                                                                                                                                                                                                                                                                | Eugene L. Poole                                                                                                                                                                                                                                                                                                                                                                          | L-16901                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| NASA Langley Research Center Hampton, VA 23665-5225  2. Sponsoring Agency Name and Address National Aeronautics and Space Administration Washington, DC 20546-0001  15. Supplementary Notes Andrea L. Overman: Langley Research Center, Hampton, Virginia. Eugene L. Poole: Analytical Services & Materials, Inc., Hampton, Virginia. Eugene L. Poole: Analytical Services & Materials, Inc., Hampton, Virginia.  16. Abstract This paper describes a Choleski method used to solve linear systems of equations that arise in large-scale structural analyses. The method uses a novel variable-band storage scheme and is structured to exploit fast local memory caches while minimizing data access delays between main memory and vector registers. Several parallel implementations of this method are described for the CRAY-2 and CRAY Y-MP computers demonstrating the use of microtasking and autotasking directives. A portable parallel language, FORCE, is used for comparison with the microtasked and autotasked implementations. Results are presented comparing the matrix factorization times for three representative structural analysis problems from runs made in both declicated and multiuser modes on both the CRAY-2 and CRAY Y-MP computers. Both CPU (central processing unit) times and wall clock times are given for the parallel implementations and are compared with single-processor times of the same algorithm. Computation rates over 1 GIGAFLOP (1 billion floating point operations per second) on a four-processor CRAY-2 and over 2 GIGAFLOPS on an eight-processor CRAY Y-MP are demonstrated as measured by wall clock time in a dedicated environment. Reduced wall clock times for the parallel implementations relative to the single-processor implementation of the same Choleski algorithm are also demonstrated for runs made in a multiuser environment.  17. Key Words (Suggested by Author(s)) Choleski factorization CRAY-2/CRAY Y-MP Parallel processing/vectorization Macrotasking, microtasking, and autotasking FORCE preprocessor                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                          | 10. Work Unit No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 11. Contract or Grant No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                          | 505-90-52-02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2. Sponsoring Agency Name and Address National Aeronautics and Space Administration Washington, DC 20546-0001  15. Supplementary Notes Andrea L. Overman: Langley Research Center, Hampton, Virginia. Eugene L. Poole: Analytical Services & Materials, Inc., Hampton, Virginia.  16. Abstract This paper describes a Choleski method used to solve linear systems of equations that arise in large-scale structural analyses. The method uses a novel variable-band storage scheme and is structured to exploit fast local memory caches while minimizing data access delays between main memory and vector registers. Several parallel implementations of this method are described for the CRAY-2 and CRAY Y-MP computers demonstrating the use of microtasking and autotasking directives. A portable parallel language, FORCE, is used for comparison with the microtasked and autotasked implementations. Results are presented comparing the matrix factorization times for three representative structural analysis problems from runs made in both dedicated and multiuser modes on both the CRAY-2 and CRAY Y-MP computers. Both CPU (central processing unit) times and wall clock times are given for the parallel implementations and are compared with single-processor times of the same algorithm. Computation rates over 1 GIGAFLOP (1 billion floating point operations per second) on a four-processor CRAY-2 and over 2 GIGAFLOPS on an eight-processor CRAY Y-MP are demonstrated as measured by wall clock time in a dedicated environment. Reduced wall clock times for the parallel implementations relative to the single-processor implementation of the same Choleski algorithm are also demonstrated for runs made in a multiuser environment.  17. Key Words (Suggested by Author(s)) Choleski factorization CRAY-2/CRAY Y-MP Parallel processing/vectorization Macrotasking, microtasking, and autotasking FORCE preprocessor                                                                                                                                                                    | Ç î                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2. Sponsoring Agency Name and Address National Aeronautics and Space Administration Washington, DC 20546-0001  3. Supplementary Notes Andrea L. Overman: Langley Research Center, Hampton, Virginia. Eugene L. Poole: Analytical Services & Materials, Inc., Hampton, Virginia. 6. Abstract This paper describes a Choleski method used to solve linear systems of equations that arise in large-scale structural analyses. The method uses a novel variable-band storage scheme and is structured to exploit fast local memory caches while minimizing data access delays between main memory and vector registers. Several parallel implementations of this method are described for the CRAY-2 and CRAY Y-MP computers demonstrating the use of microtasking and autotasking directives. A portable parallel language, FORCE, is used for comparison with the microtasked and autotasked implementations. Results are presented comparing the matrix factorization times for three representative structural analysis problems from runs made in both dedicated and multiuser modes on both the CRAY-2 and CRAY Y-MP computers. Both CPU (central processing unit) times and wall clock times are given for the parallel implementations and are compared with single-processor times of the same algorithm. Computation rates over 1 GIGAFLOP (1 billion floating point operations per second) on a four-processor CRAY-2 and over 2 GIGAFLOPS on an eight-processor CRAY Y-MP are demonstrated as measured by wall clock time in a dedicated environment. Reduced wall clock times for the parallel implementations relative to the single-processor implementation of the same Choleski algorithm are also demonstrated for runs made in a multiuser environment.  17. Key Words (Suggested by Author(s)) Choleski factorization CRAY-2/CRAY Y-MP Parallel processing/vectorization Macrotasking, microtasking, and autotasking FORCE preprocessor                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                          | 10 There of Depart and Desired Covered                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| National Aeronautics and Space Administration Washington, DC 20546-0001  5. Supplementary Notes Andrea L. Overman: Langley Research Center, Hampton, Virginia. Eugene L. Poole: Analytical Services & Materials, Inc., Hampton, Virginia. 6. Abstract This paper describes a Choleski method used to solve linear systems of equations that arise in large-scale structural analyses. The method uses a novel variable-band storage scheme and is structured to exploit fast local memory caches while minimizing data access delays between main memory and vector registers. Several parallel implementations of this method are described for the CRAY-2 and CRAY Y-MP computers demonstrating the use of microtasking and autotasking directives. A portable parallel language, FORCE, is used for comparison with the microtasked and autotasked implementations. Results are presented comparing the matrix factorization times for three representative structural analysis problems from runs made in both dedicated and multiuser modes on both the CRAY-2 and CRAY Y-MP computers. Both CPU (central processing unit) times and wall clock times are given for the parallel implementations and arc compared with single-processor times of the same algorithm. Computation rates over 1 GIGAFLOP (1 billion floating point operations per second) on a four-processor CRAY-2 and over 2 GIGAFLOPS on an eight-processor CRAY Y-MP are demonstrated as measured by wall clock time in a dedicated environment. Reduced wall clock times for the parallel implementations relative to the single-processor implementation of the same Choleski algorithm are also demonstrated for runs made in a multiuser environment.  17. Key Words (Suggested by Author(s)) Choleski factorization CRAY-2/CRAY Y-MP Parallel processing/vectorization Macrotasking, microtasking, and autotasking FORCE preprocessor  Subject Category 60                                                                                                                                                                                        | 2. Sponsoring Agency Name and A                                                                                                                                                                                                                                                                                                                                                                                                                      | ddress                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Washington, DC 20546-0001  14. Sponsoring Agency Code  15. Supplementary Notes Andrea L. Overman: Langley Research Center, Hampton, Virginia. Eugene L. Poole: Analytical Services & Materials, Inc., Hampton, Virginia.  16. Abstract This paper describes a Choleski method used to solve linear systems of equations that arise in large-scale structural analyses. The method uses a novel variable-band storage scheme and is structured to exploit fast local memory caches while minimizing data access delays between main memory and vector registers. Several parallel implementations of this method are described for the CRAY-2 and CRAY Y-MP computers demonstrating the use of microtasking and autotasking directives. A portable parallel language, FORCE, is used for comparison with the microtasked and autotasked implementations. Results are presented comparing the matrix factorization times for three representative structural analysis problems from runs made in both dedicated and multiuser modes on both the CRAY-2 and CRAY Y-MP computers. Both CPU (central processing unit) times and wall clock times are given for the parallel implementations and are compared with single-processor times of the same algorithm. Computation rates over 1 GIGAFLOP (1 billion floating point operations per second) on a four-processor CRAY-2 and over 2 GIGAFLOPS on an eight-processor CRAY Y-MP are demonstrated as measured by wall clock time in a dedicated environment. Reduced wall clock times for the parallel implementations relative to the single-processor implementation of the same Choleski algorithm are also demonstrated for runs made in a multiuser environment.  17. Key Words (Suggested by Author(s)) Choleski factorization CRAY-2/CRAY Y-MP Parallel processor; and autotasking, and autotasking FORCE preprocessor                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Andrea L. Overman: Langley Research Center, Hampton, Virginia.  Eugene L. Poole: Analytical Services & Materials, Inc., Hampton, Virginia.  16. Abstract This paper describes a Choleski method used to solve linear systems of equations that arise in large-scale structural analyses. The method uses a novel variable-band storage scheme and is structured to exploit fast local memory caches while minimizing data access delays between main memory and vector registers. Several parallel implementations of this method are described for the CRAY-2 and CRAY Y-MP computers demonstrating the use of microtasking and autotasking directives. A portable parallel language, FORCE, is used for comparison with the microtasked and autotasked implementations. Results are presented comparing the matrix factorization times for three representative structural analysis problems from runs made in both dedicated and multiuser modes on both the CRAY-2 and CRAY Y-MP computers. Both CPU (central processing unit) times and wall clock times are given for the parallel implementations and are compared with single-processor times of the same algorithm. Computation rates over 1 GIGAFLOPS on an eight-processor CRAY Y-MP are demonstrated as measured by wall clock time in a dedicated environment. Reduced wall clock times for the parallel implementations relative to the single-processor implementation of the same Choleski algorithm are also demonstrated for runs made in a multiuser environment.  17. Key Words (Suggested by Author(s)) Choleski factorization CRAY-2/CRAY Y-MP Parallel processing/vectorization Macrotasking, microtasking, and autotasking FORCE preprocessor  Subject Category 60                                                                                                                                                                                                                                                                                                                                                                                     | Washington, DC 20546-0                                                                                                                                                                                                                                                                                                                                                                                                                               | 001                                                                                                                                                                                                                                                                                                                                                                                      | 14. Sponsoring Agency Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Choleski factorization CRAY-2/CRAY Y-MP Parallel processing/vectorization Macrotasking, microtasking, and autotasking FORCE preprocessor Subject Category 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Eugene L. Poole: Analytem 16. Abstract This paper describes a Clarge-scale structural anstructured to exploit fast memory and vector regist the CRAY-2 and CRAY directives. A portable parautotasked implementati three representative structure modes on both the CRA times and wall clock times and wall clock times ingle-processor times of floating point operations an eight-processor CRAY environment. Reduced to processor implementations. | Choleski method used to solvalyses. The method uses a local memory caches while reters. Several parallel implem Y-MP computers demonstrate rallel language, FORCE, is used on the same algorithm. Computers are given for the parallel the same algorithm. Computer second) on a four-procest Y-MP are demonstrated as wall clock times for the parallel of the same Choleski algorithm. | ve linear systems of equations that arise in novel variable-band storage scheme and is minimizing data access delays between main mentations of this method are described for ting the use of microtasking and autotasking sed for comparison with the microtasked and omparing the matrix factorization times for a runs made in both dedicated and multiuser outers. Both CPU (central processing unit) the limplementations and are compared with outation rates over 1 GIGAFLOP (1 billion tessor CRAY-2 and over 2 GIGAFLOPS on a measured by wall clock time in a dedicated allel implementations relative to the single- |

| 10 Security Classif (of this report) 20 Security Classif (of this page) 21. No. of Pages 22. Price                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Choleski factorization<br>CRAY-2/CRAY Y-MP<br>Parallel processing/vector<br>Macrotasking, microtask                                                                                                                                                                                                                                                                                                                                                  | prization                                                                                                                                                                                                                                                                                                                                                                                | ${\bf Unclassified-Unlimited}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 17. Decurred Compart, (or one report)   20. Decurred Compart (or one penal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 19. Security Classif. (of this report)                                                                                                                                                                                                                                                                                                                                                                                                               | 20. Security Classif. (of thi                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

-

#### **Abstract**

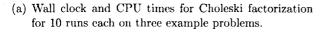

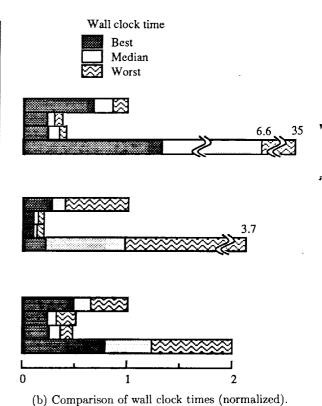

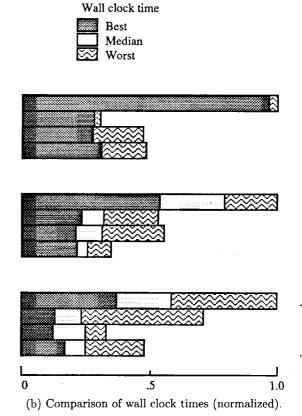

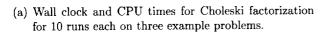

This paper describes a Choleski method used to solve linear system. of equations that arise in large-scale structural analyses. The method uses a novel variable-band storage scheme and is structured to exploit fast local memory caches while minimizing data access delays between main memory and vector registers. Several parallel implementations of this method are described for the CRAY-2 and CRAY Y-MP computers demonstrating the use of microtasking and autotasking directives. A portable parallel language, FORCE, is used for comparison with the microtasked and autotasked implementations. Results are presented comparing the matrix factorization times for three representative structural analysis problems from runs made in both dedicated and multiuser modes on both the CRAY-2 and CRAY Y-MP computers. Both CPU (central processing unit) times and wall clock times are given for the parallel implementations and are compared with single-processor times of the same algorithm. Computation rates over 1 GIGAFLOP (1 billion floating point operations per second) on a four-processor CRAY-2 and over 2 GIGAFLOPS on an eight-processor CRAY Y-MP are demonstrated as measured by wall clock time in a dedicated environment. Reduced wall clock times for the parallel implementations relative to the single-processor implementation of the same Choleski algorithm are also demonstrated for runs made in a multiuser environment.

#### 1. Introduction

The computational cost of computerized structural analysis is often dominated by the cost of solving a very large system of algebraic equations associated with a finite element model. This linear system of equations has the form

$$\mathbf{K}\mathbf{u} = \mathbf{f} \tag{1}$$

where **K** is the symmetric positive-definite stiffness matrix, **f** is the load vector, and **u** is the vector of generalized displacements. The linear systems can be as large as several hundred thousand degrees of freedom and often require significant computing resources, in terms of both memory and execution time. The development of algorithms to solve these linear systems on existing and future high-performance supercomputers that have multiple parallel high-speed vector CPU's (central processing units) can significantly reduce the computer time required for structural analysis. Efficient algorithms that exploit both vectorization and parallelization gain the maximum benefit on such supercomputers.

One widely used method for solving equation (1) is the Choleski method (ref. 1). In the Choleski method the stiffness matrix  $\mathbf{K}$  is factored into the product of the triangular matrices  $\mathbf{LL}^T$ , followed by

a forward-and-backward solution using the triangular systems

$$\mathbf{L}\mathbf{z} = \mathbf{f}$$

(forward) (2a)

$$\mathbf{L}^T \mathbf{u} = \mathbf{z} \qquad \text{(backward)} \tag{2b}$$

The factorization of **K**, which is by far the most computationally expensive part of the Choleski method, can be carried out in many ways. The particular implementation of the Choleski method that is the most effective for a class of problems depends on both the structure of the linear systems and the architectural features of the computer used for the analysis. Though the structure of K for many structural analysis applications is initially very sparse, usually 20 to 50 nonzero coefficients in a given row of the matrix, the factored matrix L contains many more coefficients produced during the factorization step. For many structural analysis problems, a reordering of the nodes in the finite element model can be carried out that minimizes the bandwidth of the factored matrix, thereby significantly reducing matrix storage requirements and the number of computations required. A novel variable-band matrix storage scheme is used with the Choleski implementations described in this paper to reduce the computational cost of the factorization. The reverse Cuthill-McKee

reordering algorithm (ref. 2) is used to minimize the bandwidth of the linear systems.

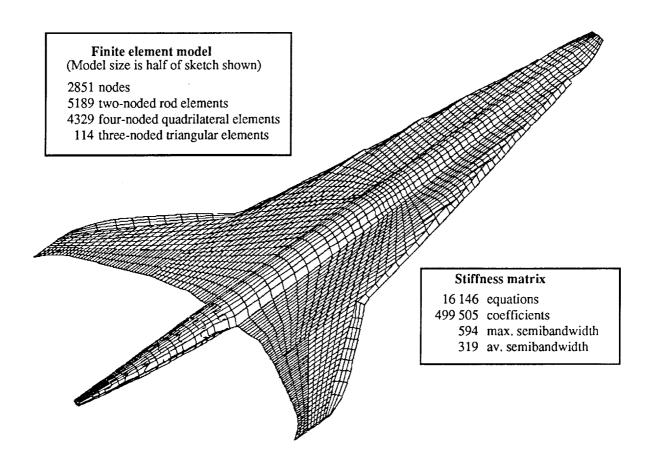

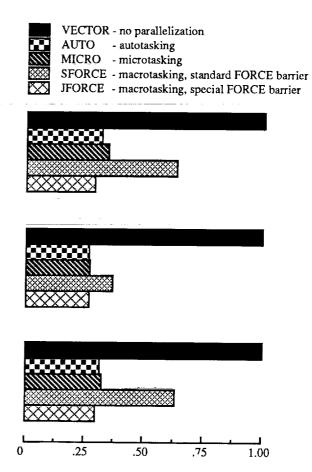

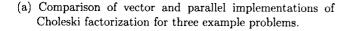

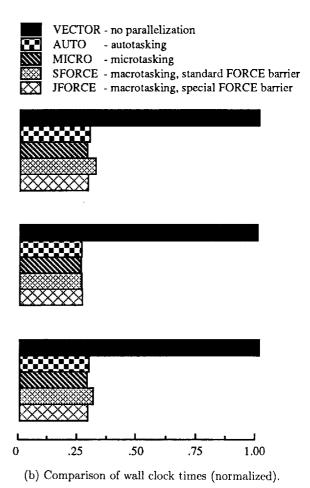

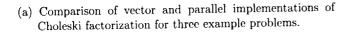

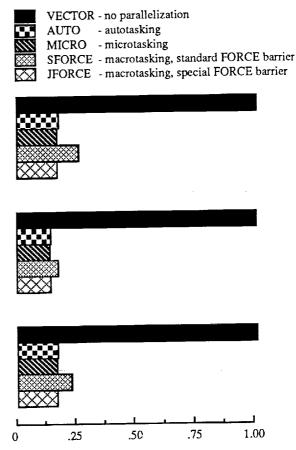

In this paper a vectorized variable-band Choleski method, denoted as VBAND, is described for singleprocessor implementation. A parallel Choleski equation solver, based on the VBAND method and denoted as PVBAND, is also presented. Several implementations of the PVBAND method are described demonstrating three different approaches for implementing parallel algorithms on CRAY multiprocessor supercomputers (manufactured by Cray Research, Inc.). The performance of the parallel implementations is demonstrated by comparing factorization times for several large representative structural analysis problems. In a dedicated computing environment, maximum computation rates over 1 GIGAFLOP (1 billion floating point operations per second) on a four-processor CRAY-2 and over 2 GIGAFLOPS on an eight-processor CRAY Y-MP are achieved for the matrix factorization portion of the computerized structural analyses. In a multiuser environment, reduced wall clock times are demonstrated for the parallel methods as compared with the wall clock times for the single-processor VBAND Choleski algorithm.

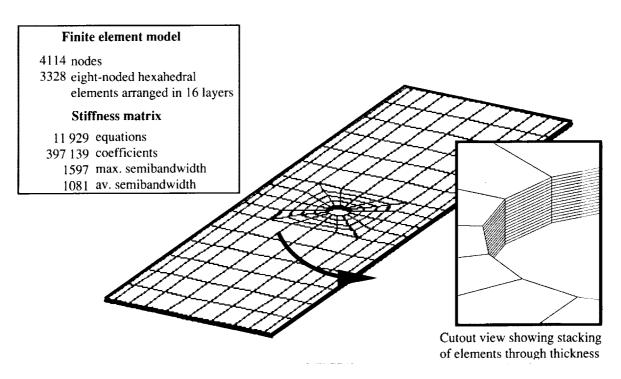

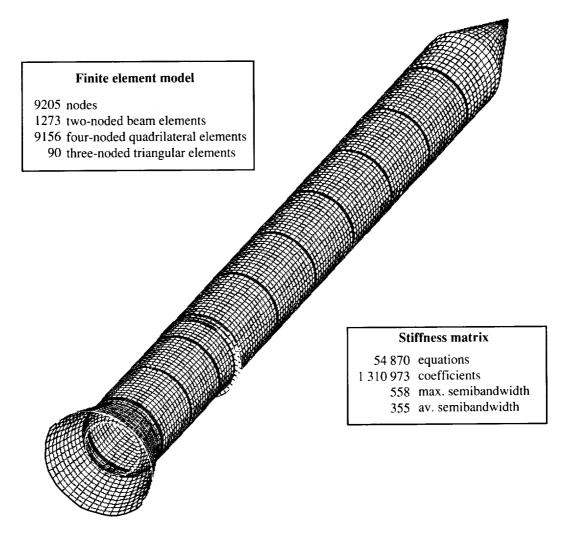

The outline of this paper is as follows: In section 2, architectural features of the CRAY multiprocessor supercomputers are described. Key hardware features of the CRAY-2 and CRAY Y-MP computers are compared and contrasted, and implementation issues related to exploiting vectorization as well as parallel processing on CRAY supercomputers are discussed. CRAY multitasking alternatives (macrotasking, microtasking, and autotasking) are introduced. In section 3, both single-processor and parallel implementations of the variable-band Choleski method are described. Detailed discussions of the differences between the parallel implementations on the CRAY computers are included. The implementation details provide an aid for understanding the differences in performance across the parallel implementations. In section 4, the role of equation solvers in computerized structural analysis is briefly discussed. Three representative structural analysis problems that are used to compare the parallel implementations of the variable-band Choleski method are described. In section 5, numerical results are presented from multiple runs in both dedicated and multiuser environments, and in section 6, concluding remarks are given. Finally, an appendix is given containing FORTRAN listings for several of the subroutines described in this paper.

## 2. Parallel-Vector Computer Architectures

The experiments described in this report were performed on a CRAY-2 at the NASA Langley Research Center (LaRC) and a CRAY Y-MP at the NASA Ames Research Center (ARC). This section briefly describes the key architectural features of these computers including a discussion of the major hardware differences of the CRAY-2 and CRAY Y-MP machines that affect algorithm design. In addition, optimization issues related to exploiting both the vector and parallel processing capabilities of CRAY supercomputers are briefly introduced. Differences between macrotasking, microtasking, and autotasking that affect algorithm performance are discussed at the end of the parallel processing subsection.

#### **CRAY** Hardware

The CRAY-2 and the CRAY Y-MP are sharedmemory multiprocessor computers that have a maximum of four and eight central processing units (CPU's), respectively. Each CPU has multiple vector arithmetic and logic functional units that access very large main memories through eight high-speed vector The maximum computation rate, comregisters. monly measured in units known as MFLOPS (millions of floating point operations per second), is attained when both addition and multiplication vector functional units are operating simultaneously, thus producing two results every machine clock period. The CRAY-2 has a clock period of 4.1 nanoseconds (nsec) that results in a maximum theoretical rate of 488 MFLOPS per processor. The CRAY Y-MP used for the experiments in this paper has a clock period of 6.0 nsec that results in a maximum theoretical rate of 333 MFLOPS per processor. These theoretical peak rates are seldom achieved because of several factors, two of which are discussed next.

Memory access delays. One factor that reduces the computation rate is memory access delay. Some delay is always incurred if the operands for a vector addition or multiplication must be transferred from main memory to the vector registers. As soon as the elements are in the vector registers they can be accessed at the maximum computation rate. Both the CRAY Y-MP and the CRAY-2 have 128 million words of main memory arranged in banks. Since memory locations in the same bank cannot be accessed in successive clock periods, contiguous array elements are stored in an interleaved pattern across the banks. This storage pattern allows contiguous array elements to be accessed at successive clock periods after an initial access delay. In general, the

does not have chaining, the memory references for a given set of operands must be completed before computations can begin. This problem is greatly reduced for FORTRAN DO loops containing many addition and multiplication instructions and several different operands since memory references on one set of operands can be carried out while multiplications or additions are taking place on another set of operands. One technique used to increase the ratio of computations to memory references is referred to as loop unrolling. In this technique, nested loops containing single-vector instructions, such as SAXPY's or inner products, are combined within a single loop containing several vector computations. This technique allows vectors to remain in the vector registers longer before results are stored back to main memory, thus resulting in a more efficient use of the multiple functional units.

#### **Parallel Processing**

In addition to the hardware features of the CRAY-2 and CRAY Y-MP that improve performance on a single CPU, parallel processing is available. The individual CPU's share a large main memory, and synchronization is accomplished using both the shared-memory and special hardware semaphore registers. Because current CRAY computers have small numbers of very powerful processors, the best overall speedups are obtained by parallelizing highly vectorized codes. The speedup from parallel processing is always less than p, where p is the number of processors, whereas the speedup due to vectorization often exceeds 20 or more on a single processor for many codes. Three types of multitasking are available on the CRAY computers and are described below. The PVBAND method was implemented using all three types of multitasking to determine the best approach for both multiuser and dedicated modes. Details of the parallel implementations are given in section 3.

Macrotasking. The earliest form of parallel processing developed for CRAY computers was macrotasking. Macrotasking is intended to be used with large codes running in a dedicated environment. Macrotasked codes perform best when separate parallel tasks, requiring little synchronization, are defined at the subroutine level. Macrotasking is the most difficult form of multitasking used on CRAY machines. Since parallelism must be defined at a higher level, macrotasking typically requires more code changes and data analysis than microtasking and autotasking. Parallelism is defined through the insertion of library subroutines, making the code un-

portable to other machines. (See refs. 3 and 4 for detailed discussions on macrotasking.)

Macrotasking requires extensive task management that is handled by the library scheduler, a collection of library subroutines. Parallel tasks, independent portions of work, are initiated through calls to the TSKSTART and are synchronized by events, locks, or the TSKWAIT subroutine. TSKSTART creates the logical CPU's, or processes, if they have not been created previously. When a task changes state, the library scheduler places the task in the appropriate library queue. For example, the scheduler periodically checks the *Ready* queue for tasks that can be attached to logical CPU's. Attachment to a logical CPU designates a task as schedulable for execution on a physical CPU. On the other hand, if a task must wait for another task to be completed, the library scheduler disconnects the waiting task from the logical CPU and places it in the Suspended queue. In addition, if no new tasks are ready, the logical CPU is "put to sleep," marking that process as unschedulable. That logical CPU must be reactivated later.

A portable parallel language, FORCE, developed for shared-memory parallel computers (refs. 5 and 6) has been implemented on the CRAY computers using macrotasking. FORCE is a machineindependent parallel language that allows programmers to implement parallel algorithms using a fixed syntax. Both parallel constructs (such as barriers and critical regions) and data types (i.e., private and shared variables) can be programmed without detailed knowledge of the implementation of the parallel constructs and data-type definitions on each computer. FORCE uses the UNIX sed editor and a set of script files to substitute machine specific code for each of the FORCE statements. In addition to replacing FORCE statements in the user's program, the FORCE preprocessing phase converts the user's main program to a subroutine that is called by a standard driver routine at run time. The driver routine is not seen by the user and serves to create, through calls to TSKSTART, the fixed number of tasks specified by the user at run time. The entire user's program is called from the main driver program by each task. Sequential portions of the code must be placed within FORCE barrier statements or other explicit code statements. At the end of the program, the FORCE driver routine terminates the tasks with the TSKWAIT subroutine.

Microtasking. Microtasking was designed to lower the overhead for CPU synchronization and to allow for more efficient multitasking in a multiuser environment. In a multiuser environment,

maximum transfer rate between main memory and the vector registers occurs when contiguous array elements are accessed from main memory.

There are two key differences in the architectures of the CRAY-2 and CRAY Y-MP that affect memory access delays. The first is the number of paths to memory. On the CRAY-2, there is only a single path between main memory and the vector registers. On the CRAY Y-MP, there are four paths to main memory; two can be used to read from memory, one to write from the registers to main memory, and one for input/output (I/O) operations. The second key difference is the use of local memory caches on the CRAY-2. Each processor on the CRAY-2 has a 16384-word local memory cache. Local memory is accessible only through the vector registers, and only contiguous access of array elements is possible. However, the time delay incurred when accessing array elements stored in local memory is significantly less than that when accessing array elements stored in main memory. As a result, vectors that are used repeatedly in computations may be stored in local memory in order to significantly reduce memory access delays.

Floating point operations and chaining. Another key factor that affects the computation rate is the type of operations performed to carry out an algorithm. For example, vector SAXPY operations (single precision  $a \times X + Y$ ) are efficient on CRAY computers since they contain both addition and multiplication instructions that can be carried out nearly simultaneously. However, inner-product instructions  $(Sum = \sum_{i=1}^{n} x_i y_i)$  are somewhat less efficient since they require a summation of many vector elements into a single scalar value.