# Dynamics Technology, Inc.

DTW-8944-91003

## **METRIWAVE FINAL REPORT** NAS7-1071

By:

**Wyman Williams**

P. 223

OCTOBER 1991

Dynamics Technology, Inc. 21311 Hawthorne Boulevard Suite 300 Torrance, CA 90503 (310) 543-5433

(MACA-CO-1 PARTA) HETCHNAY, AT INC. COPT CT. COMPACT, PROCEEDINGS, 200

192-17045

508964

53/32 JOUSTES

#### TABLE OF CONTENTS

|     |                                                       |                                                                                                                                                                        | Page                 |  |  |  |  |

|-----|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|--|

| 1.0 | INTE                                                  | ODUCTION                                                                                                                                                               | 1-1                  |  |  |  |  |

| 2.0 | SAMPLED-LINE MODULE DESIGN                            |                                                                                                                                                                        |                      |  |  |  |  |

|     | 2.1 Four-Port Network Analyzer Theory                 |                                                                                                                                                                        |                      |  |  |  |  |

|     |                                                       | <ul> <li>2.1.1 <u>Reflection Measurements with the Four-Port Network Analyzer</u></li> <li>2.1.2 <u>S-Parameter Measurements with the Four-Port Network</u></li> </ul> | 2-2                  |  |  |  |  |

|     |                                                       | Analyzer                                                                                                                                                               | 2-8                  |  |  |  |  |

|     | 2.2 Six-Port Network Analyzer Theory                  |                                                                                                                                                                        |                      |  |  |  |  |

|     |                                                       | <ul> <li>2.2.2 <u>Dual Reflectometer Calibration - The TRL Scheme</u></li> <li>2.2.3 <u>S-Parameter Measurements with the Six-Port Network Analyzer</u></li> </ul>     | 2-29<br>2-37         |  |  |  |  |

|     | 2.3 Sampled-Line Network Analyzer Theory              |                                                                                                                                                                        |                      |  |  |  |  |

|     |                                                       | 2.3.1 Placement of the Measurement Centers 2.3.2 Calibration and Measurement Options with the Sampled-Line 2.3.3 Comparison of the Sampled-Line and NBS Six-Ports      | 2-43<br>2-52<br>2-52 |  |  |  |  |

|     | 2.4                                                   | Construction of the Sampled-Line Module                                                                                                                                | 2-55                 |  |  |  |  |

|     | 2.5                                                   | Calibration and Measurement Tests with the Sampled-Line Module                                                                                                         | 2-62                 |  |  |  |  |

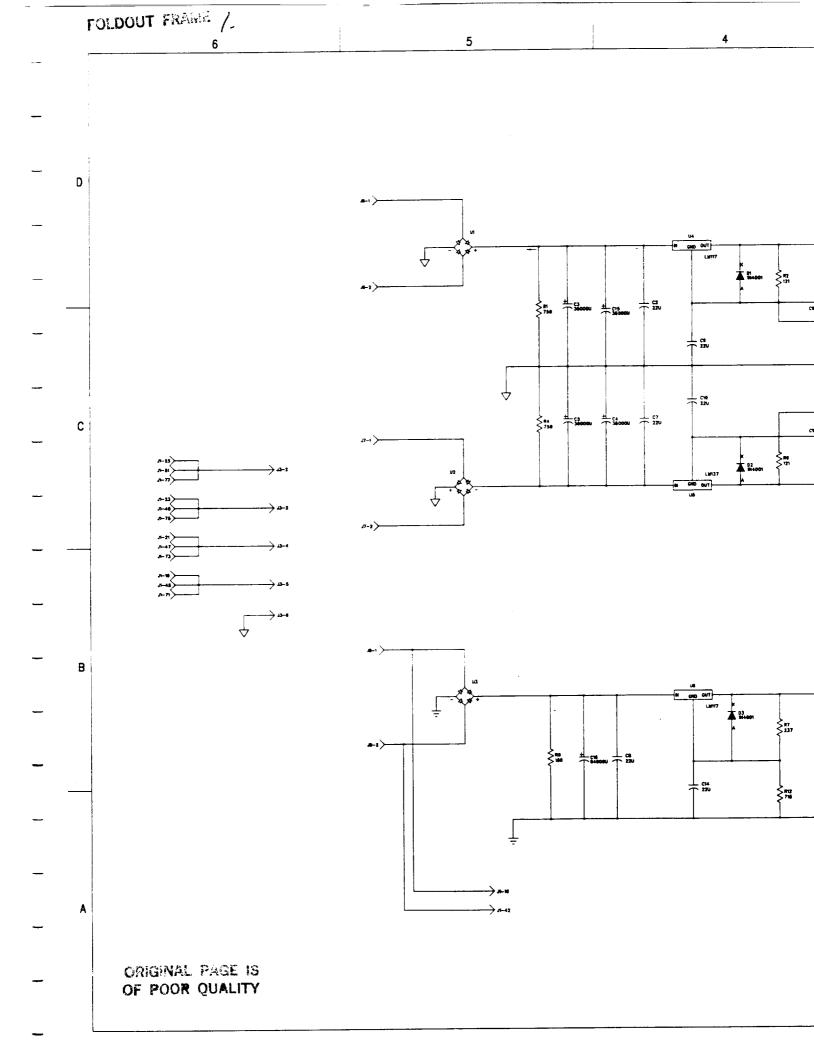

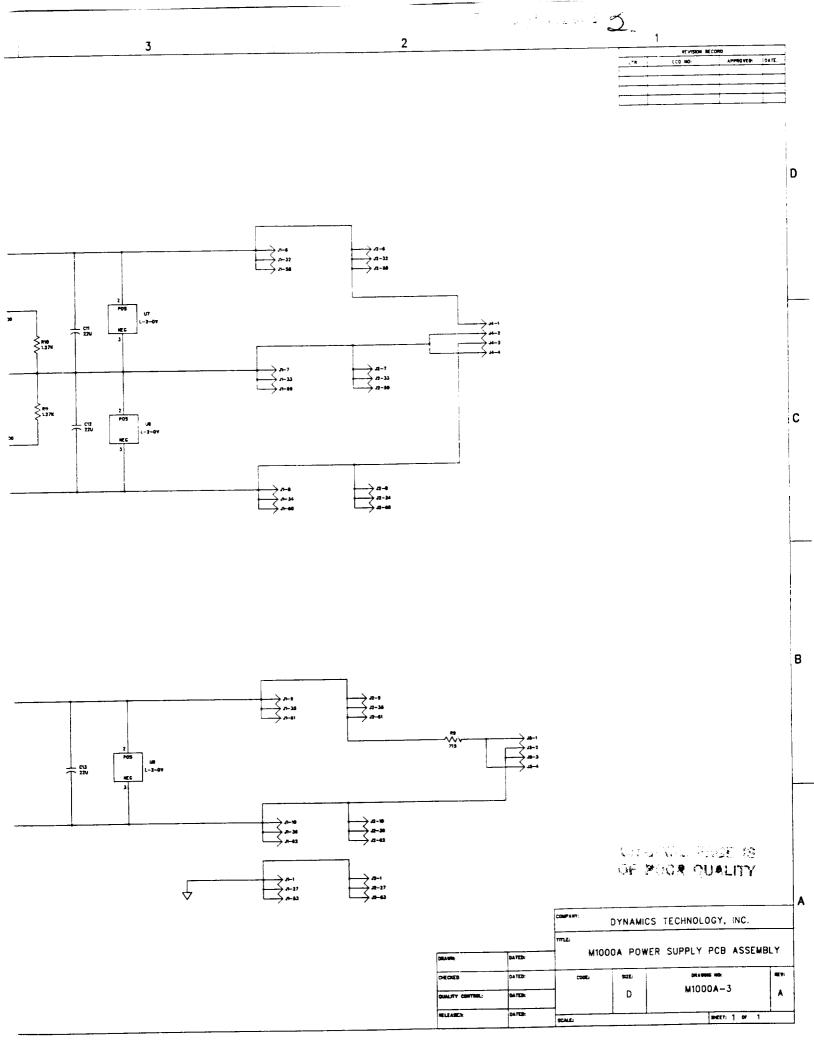

| 3.0 | .0 POST-DETECTION ELECTRONICS DESIGN AND CONSTRUCTION |                                                                                                                                                                        |                      |  |  |  |  |

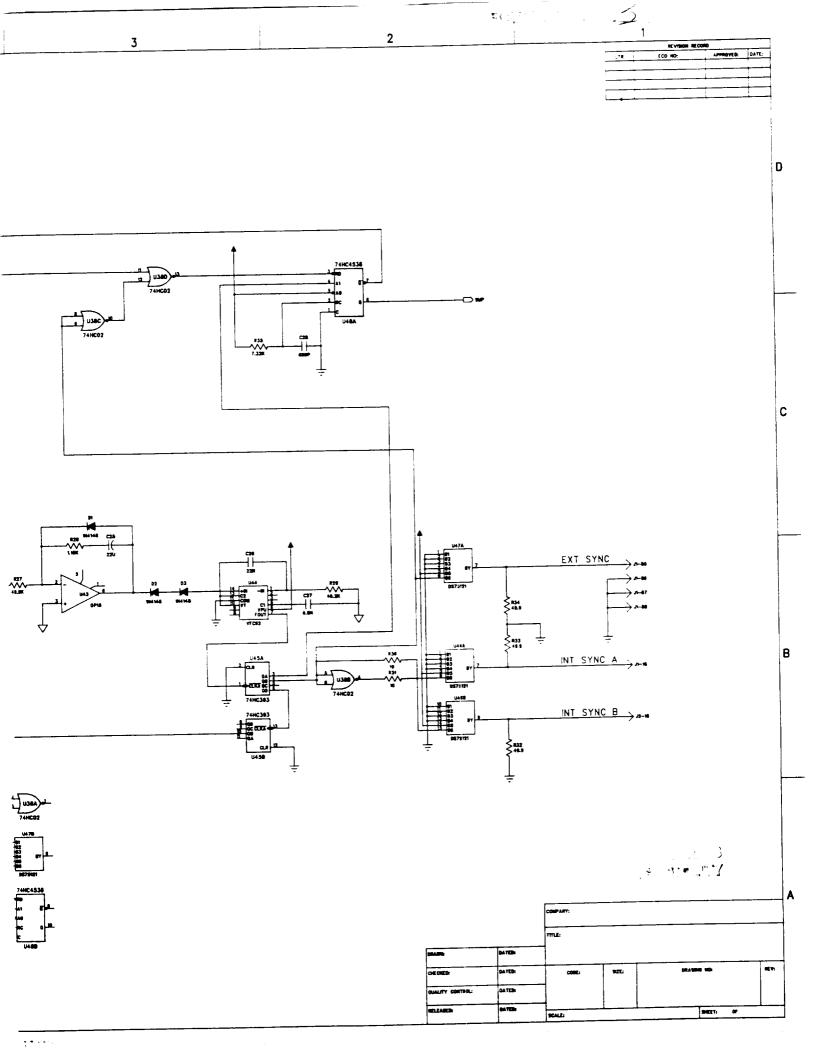

| 4.0 | 4.0 SYNCHRONIZATION CIRCUITRY                         |                                                                                                                                                                        |                      |  |  |  |  |

| 5.0 | 5.0 SYSTEM SIGNAL GENERATOR                           |                                                                                                                                                                        |                      |  |  |  |  |

| 6.0 | 6.0 SYSTEM PHASE SHIFTER                              |                                                                                                                                                                        |                      |  |  |  |  |

| 7.0 | CON                                                   | CLUSION                                                                                                                                                                | 7-1                  |  |  |  |  |

| RF  | REFERENCES F                                          |                                                                                                                                                                        |                      |  |  |  |  |

#### LIST OF FIGURES

|          |             | F                                                                                                                                                                                                                                                              | Page |

|----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

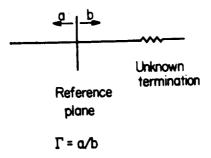

| -        | Figure 2.1  | The normalized scattering waves a and b are related to the forward-going and reverse-going voltage waves $V^+$ and $V^-$ on the transmission line by $a = V^+/12Z_0$ and $b = V^-/12Z_0$ where $Z_0$ is the characteristic impedance of the transmission line. | 2-1  |

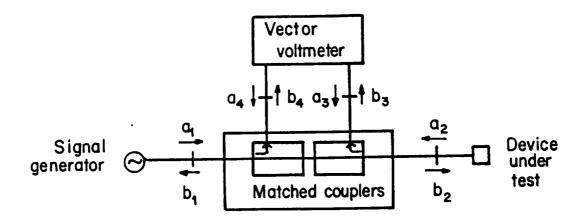

| -        | Figure 2.2  | The four-port network analyzer uses a vector voltmeter and a pair of matched directional couplers to measure the reflection coefficient                                                                                                                        | 2-3  |

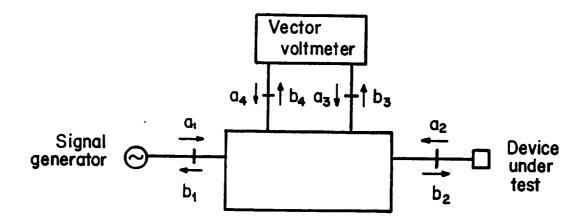

| -        | Figure 2.3  | This four-port network analyzer uses a vector voltmeter and an arbitrary linear four-port network to measure the reflection coefficient. If $b_3/b_4$ exists, it is just a bilinear transform of $\Gamma$ .                                                    | 2-4  |

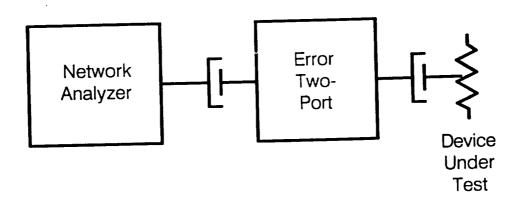

| _        | Figure 2.4  | Errors in the reflection measurement can be modeled by an error two-<br>port between the reflectometer and the device under test                                                                                                                               | 2-6  |

| <b>-</b> | Figure 2.5  | Signal flow graph for errors in the reflection measurement.                                                                                                                                                                                                    | 2-7  |

|          | Figure 2.6  | A reflection-transmission test set for full S-parameter measurements using a four-port network analyzer.                                                                                                                                                       | 2-9  |

| _        | Figure 2.7  | This flow graph shows the error model for the reflection-transmission test set.                                                                                                                                                                                | 2-13 |

|          | Figure 2.8  | A full S-parameter test set using the four-port network analyzer                                                                                                                                                                                               | 2-15 |

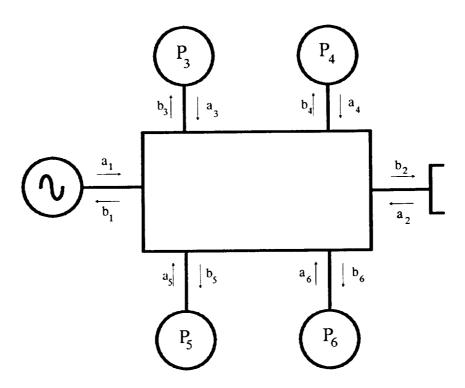

| _        | Figure 2.9  | The six-port network analyzer uses only power detectors to determine the complex ratio $a_2/b_2$ at its test port                                                                                                                                              | 2-16 |

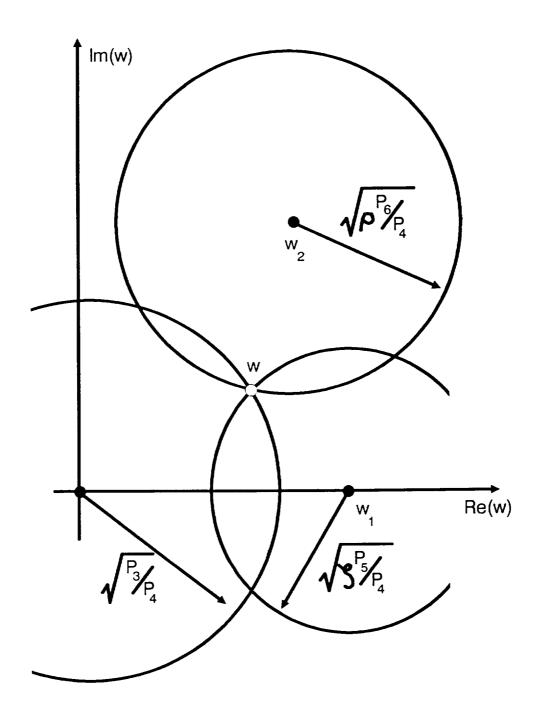

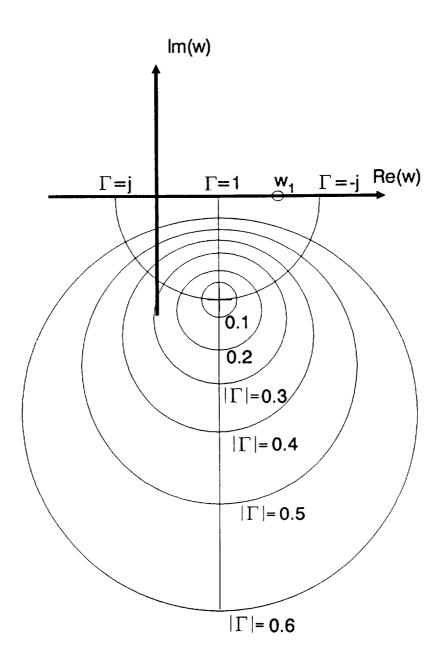

| -        | Figure 2.10 | Outputs of the six-port's power detectors give a family of circles that can be solved for the complex ratio of the signals at two of the detectors.                                                                                                            | 2-19 |

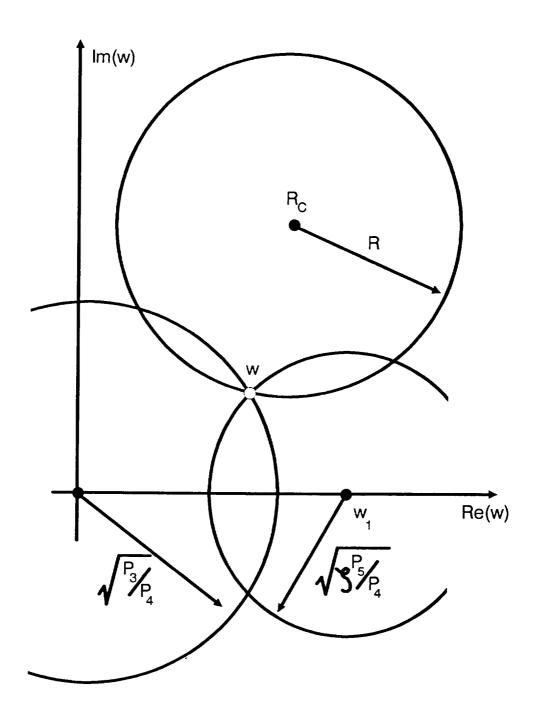

| -        | Figure 2.11 | The sliding short circuit, used in the first stage of the the six-port calibration, traces out a circle in the complex w-plane.                                                                                                                                | 2-23 |

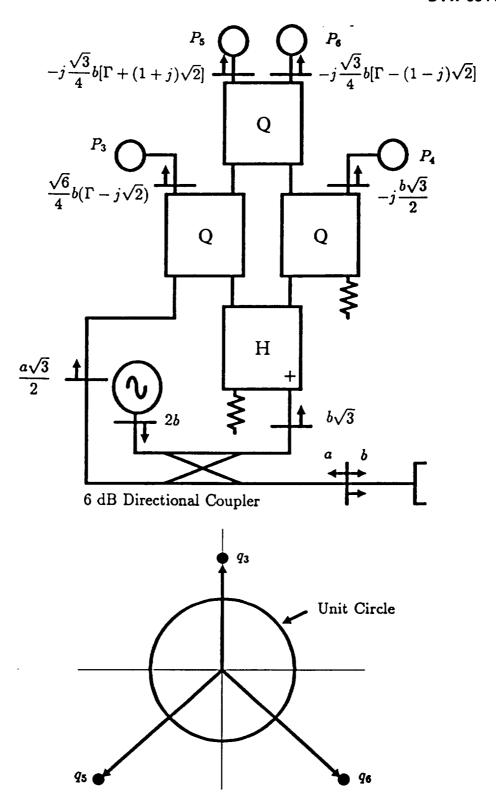

|          | Figure 2.12 | The six-port network analyzer as implemented at NBS                                                                                                                                                                                                            | 2-28 |

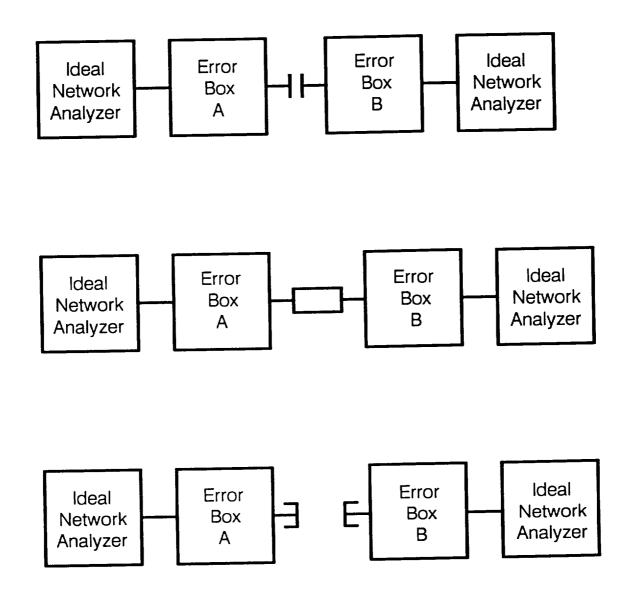

| _        | Figure 2.13 | In the TRL calibration procedure, the coefficients of the error boxes A and B of two reflectometers are determined by making the three measurements shown here.                                                                                                | 2-31 |

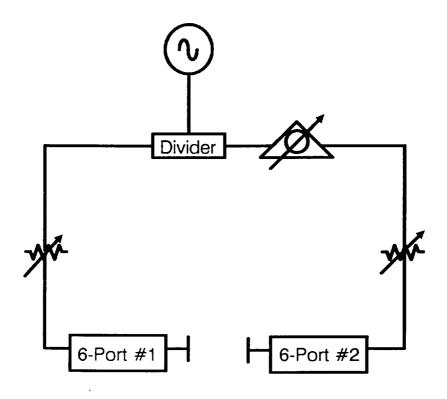

| _        | Figure 2.14 | A full S-parameter measurement system using six-port network analyzers.                                                                                                                                                                                        | 2-38 |

|             |                                                                                                                                                                                           | Page |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

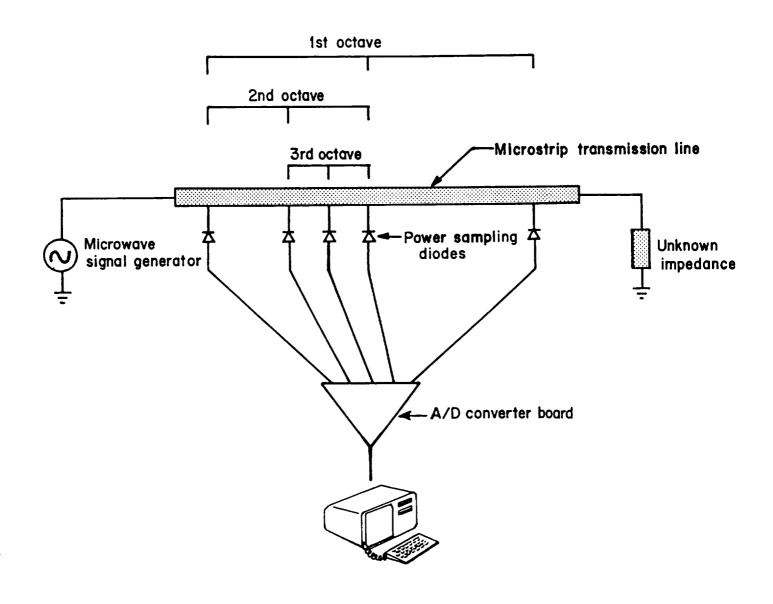

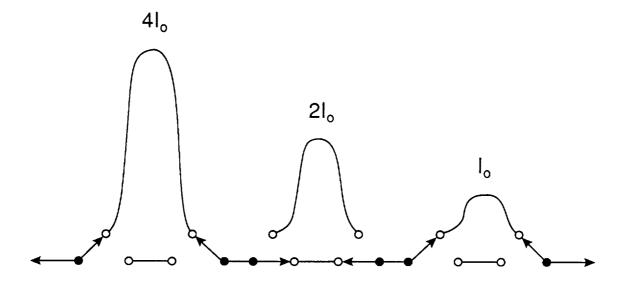

| Figure 2.15 | The sampled-line analyzer consists of a number of power detectors distributed along a transmission line.                                                                                  | 2-42 |

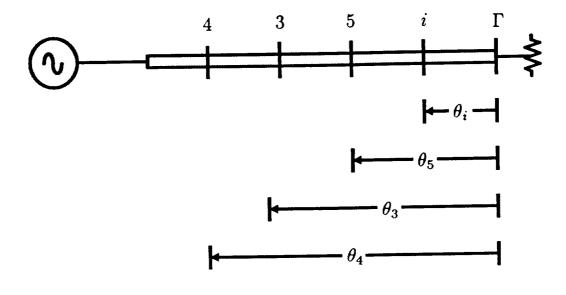

| Figure 2.16 | Model of the ideal sampled-line at a single frequency                                                                                                                                     | 2-45 |

| Figure 2.17 | The sampled-line analyzer maps the Γ-plane to the w-plane                                                                                                                                 | 2-48 |

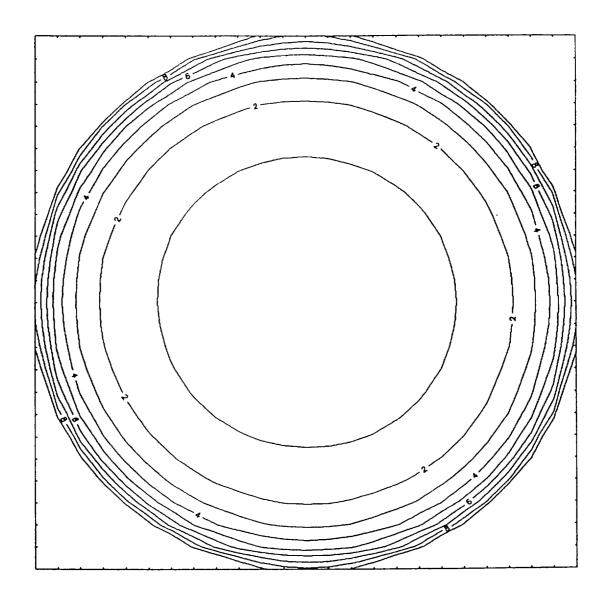

| Figure 2.18 | Sensitivity of the calculated $\Gamma$ to noise in the power detectors over the $ \Gamma  \le 1$ region with a 0.5 dB attenuator between the sampled-line and the device under test.      | 2-50 |

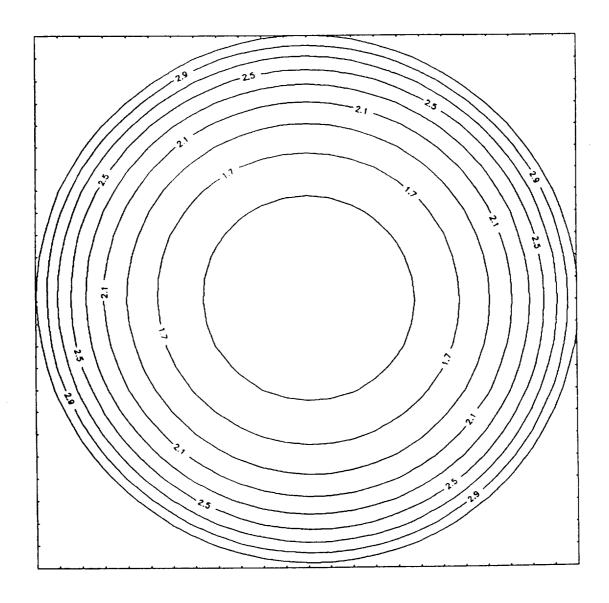

| Figure 2.19 | Sensitivity of the calculated $\Gamma$ to noise in the power detectors over the $ \Gamma  \le  \Gamma $ region with a 3 dB attenuator between the sampled-line and the device under test. | 2-51 |

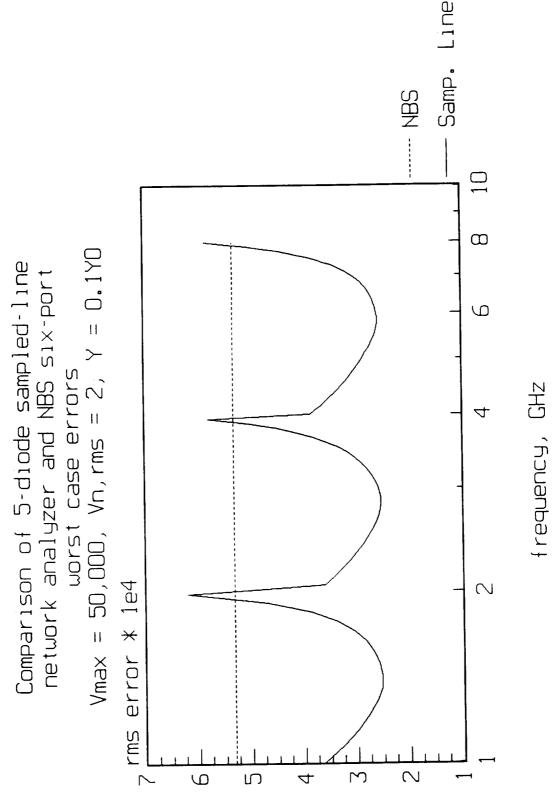

| Figure 2.20 | Comparison of the sampled-line network analyzer with an NBS-type six-port network analyzer. Ideal models are used for couplers in NBS circuit.                                            | 2-53 |

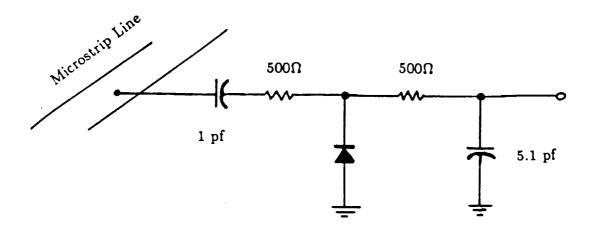

| Figure 2.21 | Sampling circuit used in the sampled-line network analyzer                                                                                                                                | 2-55 |

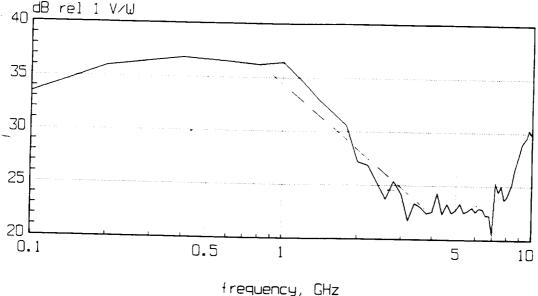

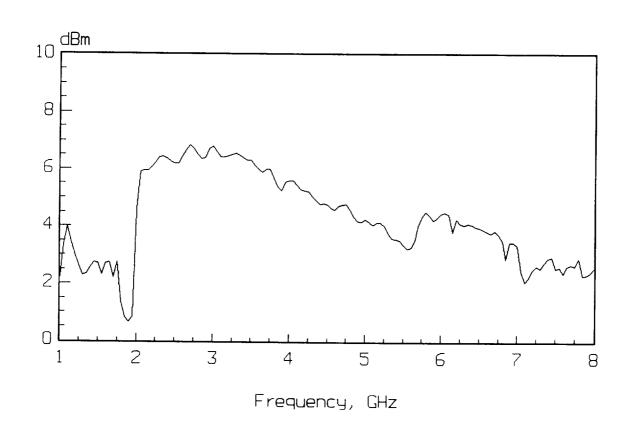

| Figure 2.22 | Measured responsivities for two sampler circuits.                                                                                                                                         | 2-57 |

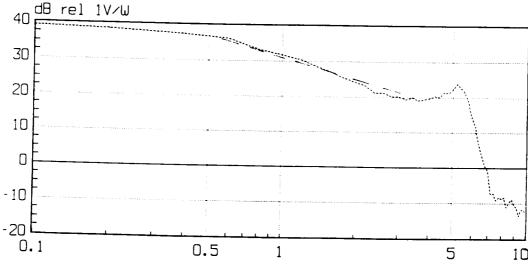

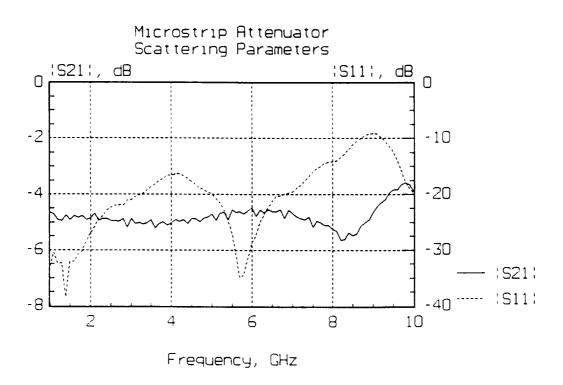

| Figure 2.23 | The microstrip attenuator integrated into the sampled-line module exhibits attenuation flatness of ±0.5 dB over the 1-8 GHz band                                                          | 2-59 |

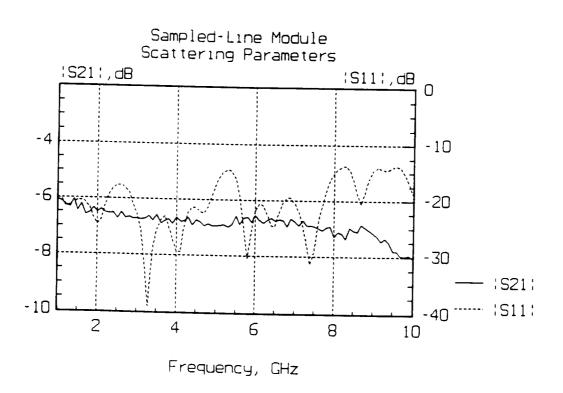

| Figure 2.24 | S-parameters of the sampled-line network analyzer module                                                                                                                                  | 2-60 |

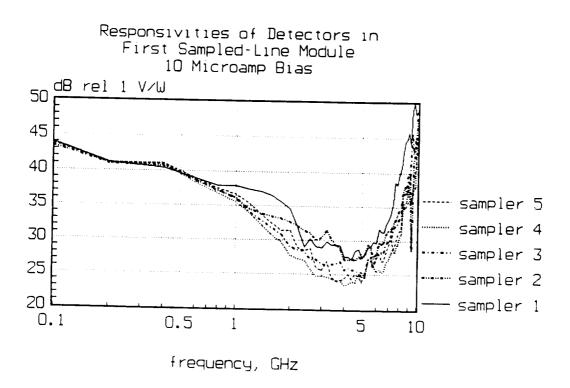

| Figure 2.25 | Detector responsivities of the sampled-line module                                                                                                                                        | 2-61 |

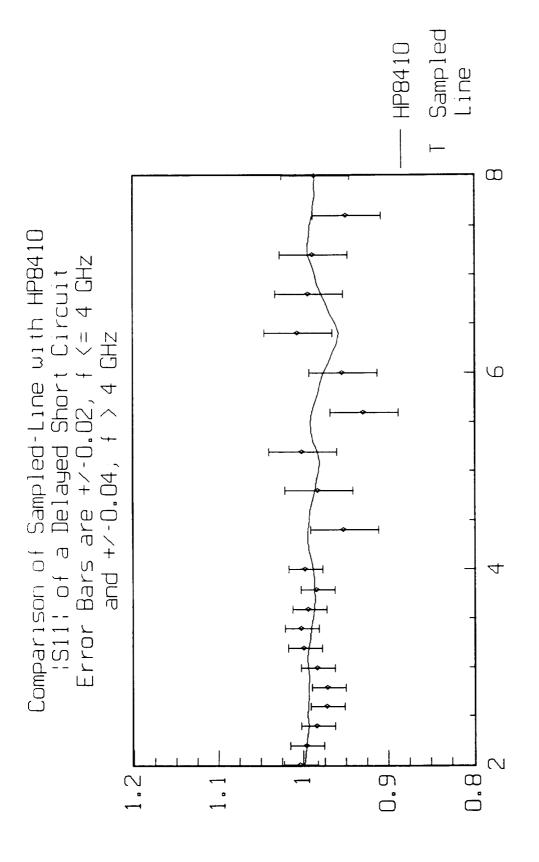

| Figure 2.26 | Results of a typical room temperature test                                                                                                                                                | 2-63 |

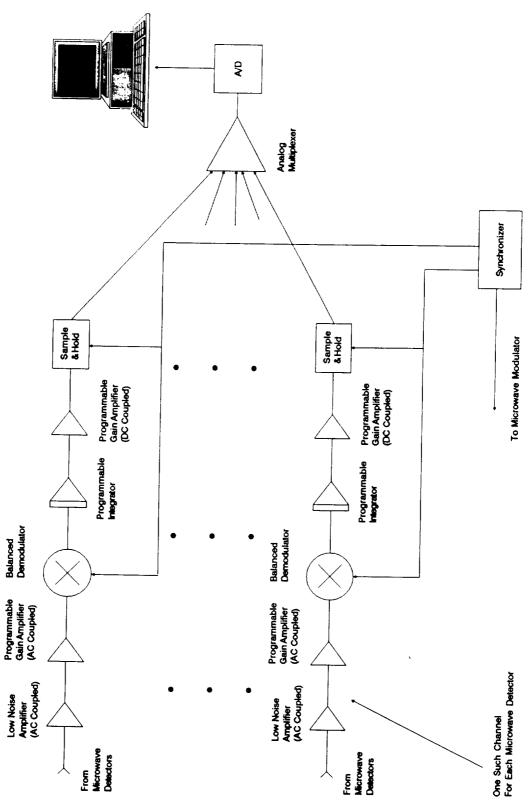

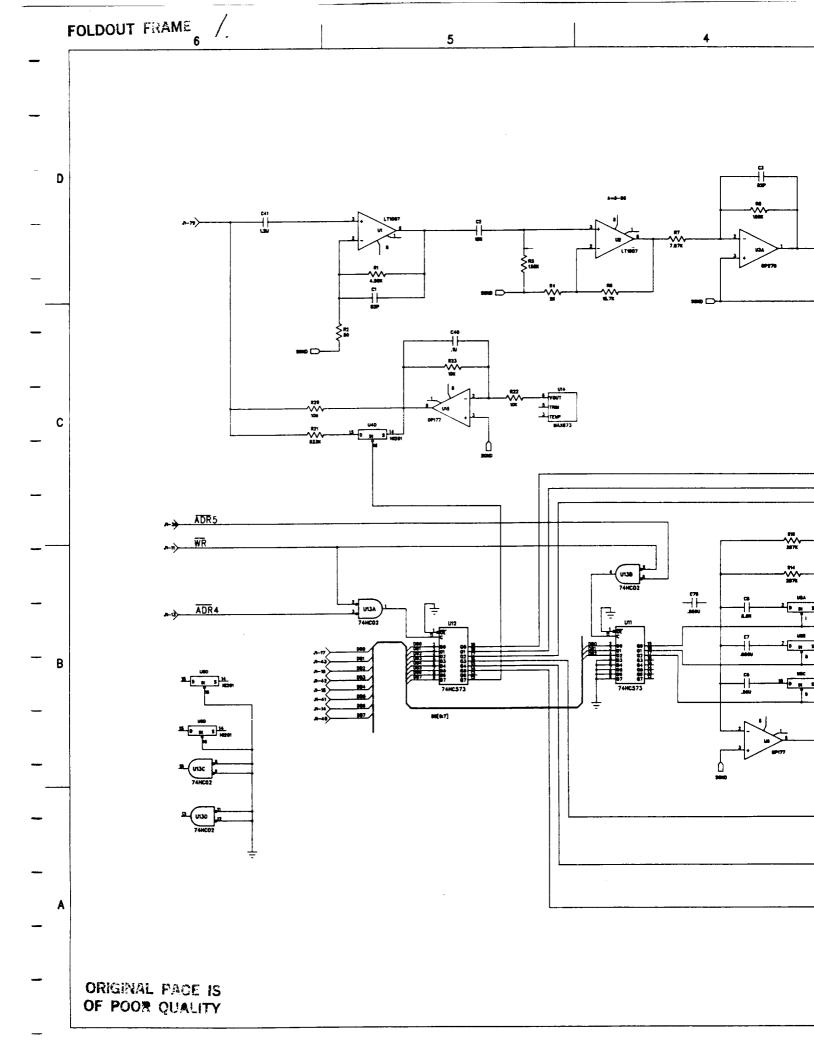

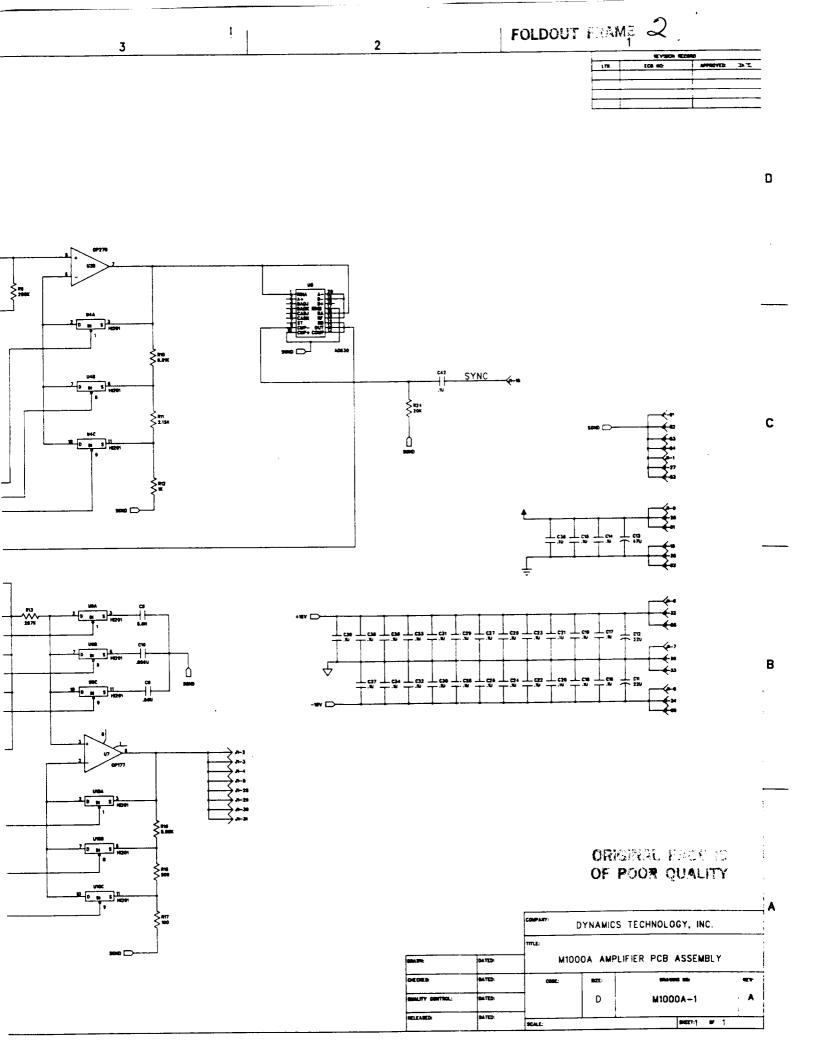

| Figure 3.1  | Instrumentation electronics for the sampled-line network analyzer consist of a multi-channel PC-based lock-in amplifier.                                                                  | 3-3  |

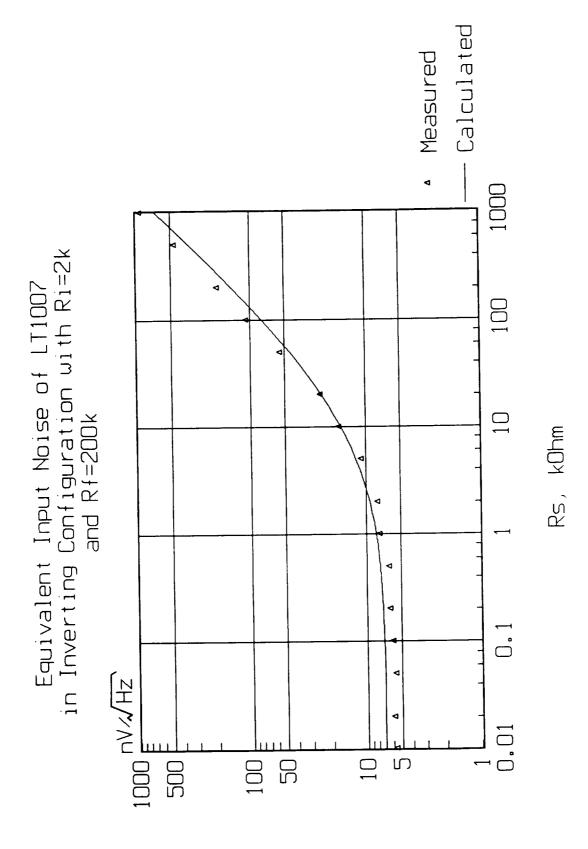

| Figure 3.2  | Noise performance of a typical channel of the post-detection electronics.                                                                                                                 | 3-4  |

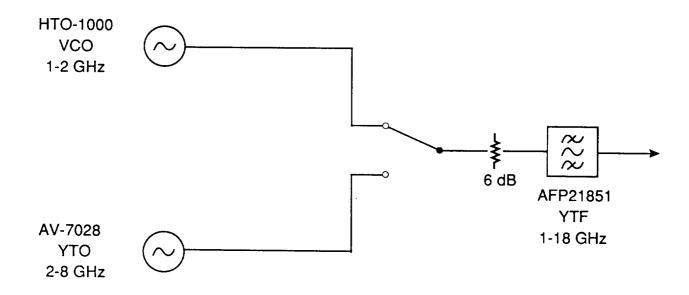

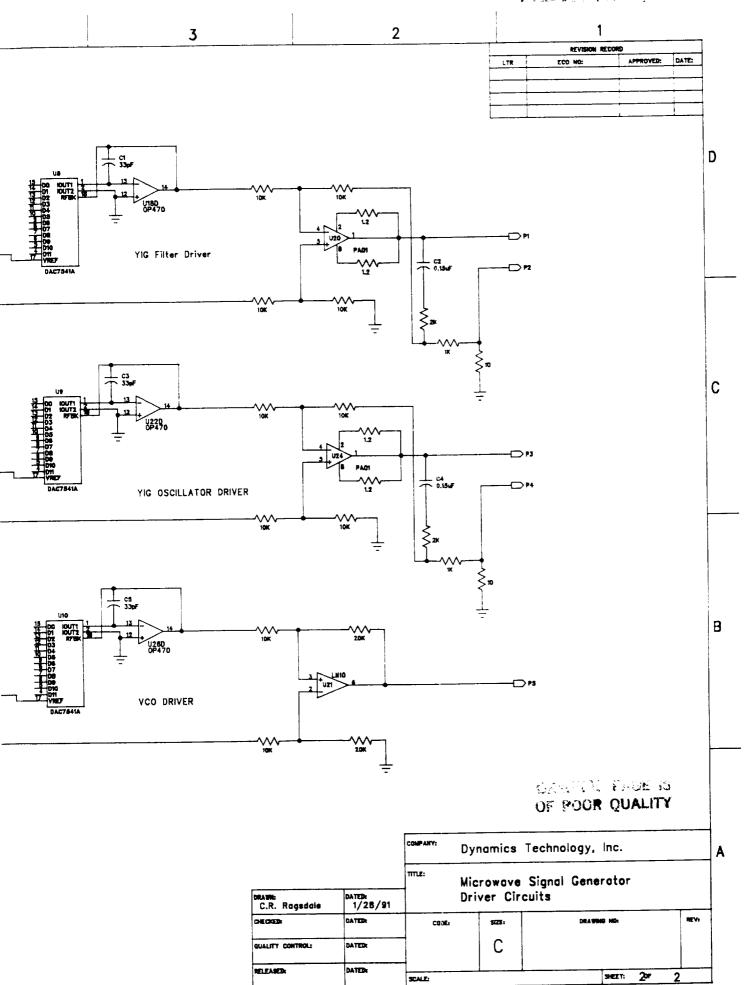

| Figure 5.1  | Block diagram of the high-purity 2-8 GHz signal generator                                                                                                                                 | 5-2  |

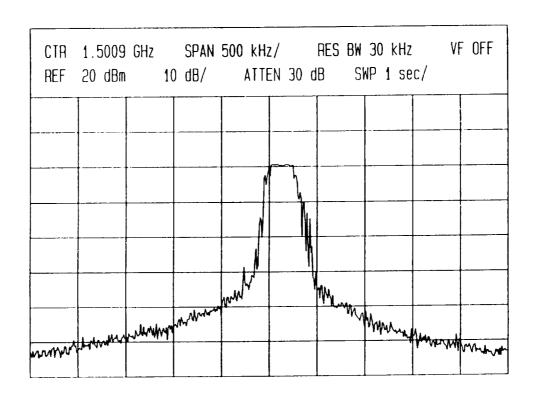

| Figure 5.2  | The signal generator output at 1.5 GHz shows typical performance of the hyperabrupt varactor-tuned oscillator.                                                                            | 5-4  |

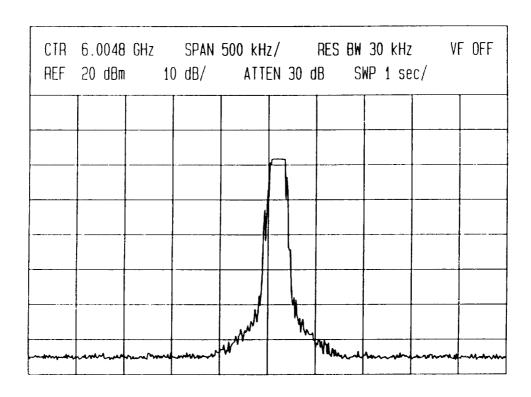

| Figure 5.3  | The signal generator output at 6 GHz shows typical performance of the YIG- tuned oscillator.                                                                                              | 5-5  |

| Figure 5.4  | Power output of the signal generator was measured using an HP 432A power meter with a HP 478A thermistor mount.                                                                           |      |

| Figure 6.1  | A digital phase shifter.                                                                                                                                                                  | 6-2  |

#### 1.0 INTRODUCTION

The superconductor-insulator-superconductor (SIS) mixer is a device which is being used in the construction of very sensitive receivers in the millimeter and submillimeter wavelength regions. With its potential for conversion gain and quantum-limited performance, it is becoming a device of prime importance in radio astronomy as well as earth and planetary atmospheric research.

Many of the parameters of the SIS mixer cannot be readily measured in the laboratory, however, since most commercially available test instruments use test signal powers large enough to saturate or destroy SIS junctions. This report details the construction of a microwave network analyzer with extremely low test signal powers. It documents the results of a development performed by Dynamics Technology, Inc., under a Phase II SBIR contract from NASA (NAS7-1025).

The work resulted in a network analyzer to be delivered to workers at the Jet Propulsion Laboratory, which should be capable of SIS mixer characterization in support of their ongoing work in this area.

This report is organized in sections which correspond to the technical objectives identified in the Phase II proposal. Appendices provide detailed schematics and parts lists of all circuitry designed in this work. Circuit descriptions in the main text of the report support the schematics. In addition, another appendix contains an operator's manual for the delivered network analyzer. These Phase II technical objectives were:

- 1. Develop parametric variations of the existing design of the sampled-line reflectometer modules. Evaluate the performance of the variations. Build and test modules with desirable performance parameters.

- 2. Design instrumentation preamplifiers and A/D converters for use with the network analyzer. Build and test the preamplifiers.

- 3. Design and build synchronization circuitry for use with the network analyzer.

- Refine the existing phase shifter design.

- 5. Design and build a microwave signal generator for use with the network analyzer.

- 6. Deliver a working prototype network analyzer to NASA.

The sections following this introduction present theoretical and experimental results from work on each of the above objectives.

## 2.0 SAMPLED-LINE MODULE DESIGN

For the sake of completeness, the theoretical background for the sampled-line network analyzer is presented here. Some new theoretical results derived as part of the Phase ii effort are presented. This is followed by a description of the design and testing of the new sampled-line modules.

## 2.1 Four-Port Network Analyzer Theory

The job a network analyzer must perform can be stated quite simply. The parameters are shown in Figure 2.1. Two travelling voltage waves, a and b, propagate in opposite directions on a transmission line. At a particular point on the line, known as the reference plane, the network analyzer measures the amplitude ratio and phase difference between these two (sinusoidal) waves.

The ability to measure this complex ratio, for a set of transmission lines connected to the ports of an unknown microwave network, allows the network analyzer to determine the complete S-parameters of that network. The machinations required to derive all the S-parameters from a given set of measurements, however, become more elaborate as the number of ports on the unknown network increases.

Machines that measure the complex ratio of travelling waves fall into two categories. The first type is built by combining a linear four-port network with a vector voltmeter, and the second uses a six-port network and several power detectors.

Figure 2.1 The normalized scattering waves a and b are related to the forward-going and reverse-going voltage waves V<sup>+</sup> and V<sup>-</sup> on the transmission line by  $a = V^+/\sqrt{2Z_0}$  and  $b = V^-/\sqrt{2Z_0}$  where  $Z_0$  is the characteristic impedance of the transmission line. Thus,  $\Gamma$  is the voltage reflection coefficient,  $\Gamma = V^+/V^-$ .

The four-port network analyzer was the first developed, and forms the basis of most of the currently available commercial network analyzers. In this chapter, the theory of operation of the four-port network analyzer will be presented. The theories of operation of the six-port and sampled-line network analyzers build upon this theory, and assumptions made in developing the four-port theory are germane to comparisons of performance of the various network analyzer approaches.

### 2.1.1 Reflection Measurements with the Four-Port Network Analyzer

The reflection measurement is the simplest network analyzer measurement. As shown in Figure 2.1, only an unknown impedance and two travelling wave quantities are involved. The unknown impedance is connected to the end of a transmission line. The voltage wave a, travelling on the line impinges on the unknown device. The travelling wave b, resulting from the impedance mismatch between the unknown device and the transmission line, is reflected back along the line. By measuring the amplitude ratio and phase difference between the incident and reflected waves at a fixed reference plane, the complex reflection coefficient,  $\Gamma$  of the unknown device is determined. This, along with knowledge of the characteristic impedance of the transmission line, is sufficient to determine the unknown impedance.

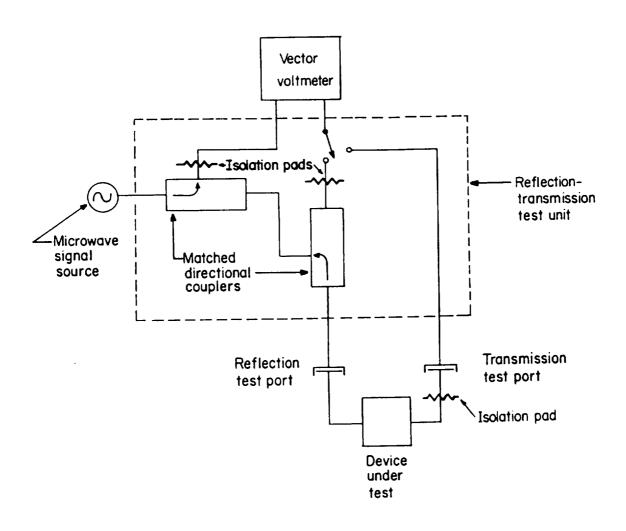

Figure 2.2 shows schematically how a vector voltmeter and a pair of matched directional couplers can be combined to yield a four-port reflectometer (the box containing the two couplers forms the "four-port" for which the analyzer is named). The vector voltmeter is a frequency-tracking heterodyne receiver that indicates the complex ratio of the two microwave signals presented at its inputs.

One directional coupler samples the forward-going wave, and the other the reflected wave. If the directional couplers are matched and have perfect directivity, and if port 2 presents a source impedance of exactly  $Z_0$  to the device under test, then  $b_3/b_4 = a_2/b_2 = \Gamma$  and the value indicated by the vector voltmeter will be the true reflection coefficient.

These conditions are stringent, however, and even with the best designs imperfections in the components give rise to large errors. With the Hewlett-Packard 8743B reflection-transmission test unit, for example, in the 2-8 GHz frequency range, magnitude errors of 0.15 are possible when measuring reflection coefficients of unity magnitude.

Figure 2.2 The four-port network analyzer uses a vector voltmeter and a pair of matched directional couplers to measure the reflection coefficient.

These large errors, however, are systematic and can be calibrated out by measuring known calibration standards. The calibration procedure and the number of standards required are determined by the relationship between the true and indicated values of  $\Gamma$ . This relationship can be found in a straightforward way by adapting Middlebrook's extra element theorem<sup>[1]</sup> to travelling wave network parameters.

Consider the four-port network analyzer of Figure 2.3. Here the dual directional couplers of Figure 2.2 have been replaced by an arbitrary linear four-port. Also, offset and gain terms have been added to the response of the vector voltmeter.

By superposition,

$$b_4 = K_1 a_1 + K_2 a_2 \tag{2.1}$$

$$b_3 = L_1 a_1 + L_2 a_2 \tag{2.2}$$

$$b_2 = M_1 a_1 + M_2 a_2 \tag{2.3}$$

Figure 2.3 This four-port network analyzer uses a vector voltmeter and an arbitrary linear four-port network to measure the reflection coefficient. If  $b_3/b_4$  exists, it is just a bilinear transform of  $\Gamma$ .

By definition,  $a_2 = \Gamma b_2$ . Inserting this in (2.1 - 2.3) and solving (2.3) for  $b_2$  gives

$$b_4 = K_1 a_1 + K_2 \Gamma b_2$$

(2.4)

$$b_3 = L_1 a_1 + L_2 \Gamma b_2 \tag{2.5}$$

$$b_2 = \frac{M_1}{1 - M_2 \Gamma} a_1 \tag{2.6}$$

Substituting (2.6) into (2.4) and (2.5) gives

$$b_4 = \frac{K_1 + (M_1 K_2 - M_2 K_1) \Gamma}{1 - M_2 \Gamma} a_1$$

(2.7)

$$b_3 = \frac{L_1 + (M_1 L_2 - M_2 L_1) \Gamma}{1 - M_2 \Gamma} a_1$$

(2.8)

Dividing (2.8) by (2.7) gives

$$\frac{b_3}{b_4} = \frac{L_1 + (M_1 L_2 - M_2 L_1) \Gamma}{K_1 + (M_1 K_2 - M_2 K_1) \Gamma}$$

(2.9)

Finally, including the response of the vector voltmeter,  $\Gamma' = C_0 + C_1 b_3/b_4$  and dividing the numerator and denominator through by the coefficient of  $\Gamma$  in the numerator gives

$$\Gamma' = \frac{\Gamma + A}{B\Gamma + C} \tag{2.10}$$

So the final result is that the value  $\Gamma'$  indicated on the vector voltmeter is a bilinear transform of the actual value of  $\Gamma$ . The bilinear transform has three complex constants, so three known standards must be measured in order to determine the calibration coefficients, and thereafter correct the measured data.

The calibration procedure is straightforward. Multiplying (2.10) through by the denominator of the right side gives

$$-A + \Gamma\Gamma' B + \Gamma' C = \Gamma$$

(2.11)

which is a linear equation in A, B, and C. By observing  $\Gamma'$  for three different known values of  $\Gamma$ , the coefficients of three such equations are determined, and the values of A, B, and C can be determined. The true value of  $\Gamma$  is then found by inverting the transform:

$$\Gamma = \frac{C\Gamma' - A}{1 - B\Gamma'} \tag{2.12}$$

The above result is interesting in several respects. The first is its generality. Any four-port network that is linear, and for which the ratio of (2.10) exists, can be used as a network analyzer and calibrated by measuring three known standards. Also, the fact that  $\Gamma'$  is a ratio measurement makes the result independent of the level of the test signal injected at port 1 and thus the source impedance of the generator.

The fact that  $\Gamma'$  is a bilinear transform of  $\Gamma$  allows the systematic errors of the system to be modeled in a simple way. Figure 2.4 shows the error model. It consists of an ideal network analyzer with an "error two-port" between the ideal analyzer's reference plane and the device under test. The fact that this gives rise to the same relationship between observed and actual values as that derived above can be seen by considering the T-parameters of the error two-port.

Figure 2.4 Errors in the reflection measurement can be modeled by an error 2-port between the reflectometer and the device under test.

$$b_1 = T_{11}a_2 + T_{12}b_2 \tag{2.13}$$

$$a_1 = T_{21}a_2 + T_{22}b_2 \tag{2.14}$$

$$\Gamma' = \frac{b_1}{a_1} = \frac{T_{11}a_2 + T_{12}b_2}{T_{21}a_2 + T_{22}b_2}$$

(2.15)

$$= \frac{T_{11}\Gamma + T_{12}}{T_{21}\Gamma + T_{22}}$$

(2.16)

For a practical system  $T_{11} \neq 0$  and dividing the numerator and denominator of (2.16) through by  $T_{11}$  gives (2.10).

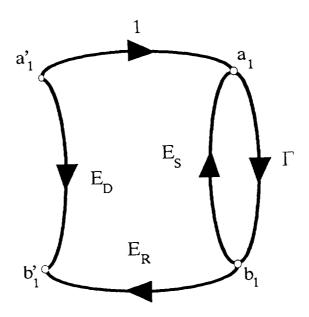

This error model can be represented by the signal flow graph of Figure 2.5. The graph is labeled with three error terms that are often quoted for reflectometers. They are related to the physical sources of error in the dual-coupler type reflection test set.  $E_D$  is the directivity error, related to the imperfect directivity of the couplers in the test set.  $E_S$  is the source match error, related to the impedance mismatch at the measurement port of the test set. Lastly,  $E_R$  is the frequency response error, related to differences in the frequency responses of the two directional couplers.

Figure 2.5 Signal flow graph for errors in the reflection measurement.

In terms of these quantities, the relation between  $\Gamma$  and  $\Gamma'$  can be found through Mason's gain rule as

$$\Gamma' = E_D + \frac{E_R \Gamma}{1 - E_S \Gamma}$$

(2.17)

$$= \frac{E_D + (E_R - E_S E_D)\Gamma}{1 - E_S\Gamma}$$

(2.18)

In practical systems, the greatest errors typically arise from the source mismatch error, when  $\Gamma$  is near unity in magnitude.

In modern network analyzers, built-in computers store the calibration constants and perform the bilinear transform to display the corrected reflection coefficient. Specifications are still often quoted, however, in terms of effective directivity, source match, etc. This method of specification makes sense due to a property of the bilinear transform: if  $\Gamma'$  is a bilinear transform of  $\Gamma$ , and  $\Gamma'$  is a bilinear transform of  $\Gamma'$ , then  $\Gamma'$  is a bilinear transform of  $\Gamma$ . Thus, if there are errors in determination of the calibration coefficients above, and the transform is applied to the measured data, one may still be assured that the result is a bilinear transform of the true  $\Gamma$ , and this bilinear transform can be classified in terms of the quantities on a signal flow graph like that of Figure 2.5.

If it is assumed that perfect calibration standards are used, and the terms of the bilinear transform are found without error, then the only sources of error remaining in the system are those due to noise and nonlinearities in the vector voltmeter.

In the vector voltmeter, the test and reference microwave signals are down-converted to intermediate frequencies of a few MHz or hundreds of kHz by a sampling mixer. At the i-f, the test signal is split into two components, one in phase with the reference signal and one in quadrature with it. From these two components, the real and imaginary parts of the complex ratio are derived. If the gains of the two channels for the test signal are not precisely matched, or if the quadrature signal is not truly orthogonal to the in-phase signal, then errors will result which cannot be calibrated out by the linear procedures described above.

Since the i-f circuitry needs only to be adjusted for operation at a single frequency, however, sufficient precision can be achieved. In modern computer-corrected network analyzers, the errors due to these nonlinearities are less than the errors resulting from lack of repeatability of the microwave connectors used to connect the device under test to the network analyzer. This lack of repeatability - the inability to exactly match all the connectors on all the calibration standards - is the factor limiting accuracy of reflection measurements with these analyzers.

## 2.1.2 S-Parameter Measurements with the Four-Port Network Analyzer

The situation is a bit more complicated when the S-parameters of an unknown two-port are to be measured. Transmission as well as reflection must be measured. A setup for making this measurement is shown in Figure 2.6.

The test set contains a reflectometer like that described above. Port 1 of the device under test is connected to this reflectometer test port. Another port, the "transmission return" receives the signal emerging from port 2. A coaxial relay selects which signal is presented to the vector voltmeter for the complex ratio measurement. To perform a full S-parameter measurement, the unknown two-port must be flipped end-for-end once during the measurement, and the coaxial relay switched each time to observe the reflection at both the network's ports, and the transmission through it in both directions.

This gives a total of four measurements. Expressions will be derived here for the values indicated by the vector voltmeter for each of these measurements in terms of the S-parameters of the device under test. These will then be inverted to yield expressions for these S-parameters in terms of the measured quantities.

Figure 2.6 A reflection-transmission test set for full S-parameter measurements using a 4-port network analyzer.

The reflection measurement is the same as that described in the previous section, except that here the measurement is of the reflection coefficient of port 1 of the two-port with its port 2 terminated in  $\Gamma_L$ , the impedance of the transmission return. This reflection coefficient,  $\Gamma_1$  is given by

$$\Gamma_{1} = S_{11} + \frac{S_{12}S_{21}\Gamma_{L}}{1 - S_{22}\Gamma_{L}}$$

(2.19)

where the S-parameters are those of the 2-port that is being measured. Substituting this into equation (2.10) yields

$$S'_{11} = \frac{\left(S_{11} + \frac{S_{12}S_{21}\Gamma_{L}}{1 - S_{22}\Gamma_{L}}\right) + A}{B\left(S_{11} + \frac{S_{12}S_{21}\Gamma_{L}}{1 - S_{22}\Gamma_{L}}\right) + C}$$

(2.20)

$$= \frac{\left(S_{11} - \Gamma_{L}\Delta\right) + A\left(1 - S_{22}\Gamma_{L}\right)}{B\left(S_{11} - \Gamma_{L}\Delta\right) + C\left(1 - S_{22}\Gamma_{L}\right)}$$

(2.21)

where  $S_{11}'$  is the value indicated by the vector voltmeter and  $\Delta \equiv S_{11} S_{22} - S_{12} S_{21}$  is the system determinant of the two-port being measured.

When performing the transmission measurement, port 2 of the device under test is connected directly to the vector voltmeter, so the meter measures  $b_5/b_4$ . To derive an expression for  $b_5/b_4$ , equation (2.6) is first rearranged to give

$$a_1 = \frac{1 - M_{2T} \Gamma}{M_{1T}} b_2$$

(2.22)

The subscript "T" is added to the coefficients of this expression because, in general, when the coaxial switch is moved from the reflection to the transmission position, the values of the K's, L's and M's in equations (2.1 - 2.8) will change, due to a change in the reflection coefficient seen looking out port 3 of the four-port network. The value of  $\Gamma_L$ , the reflection coefficient of the transmission return, will also change in general when this switch is moved, to a value of  $\Gamma_{LT}$ .

This noted, the derivation of  $b_5/b_4$  continues by substituting (2.22) into (2.4) to give

$$b_4 = \frac{1}{M_{1T}} [K_{1T} + (M_{1T} K_{2T} - M_{2T} K_{1T}) \Gamma] b_2$$

(2.23)

$$= P(B_T \Gamma + C_T) b_2$$

(2.24)

where  $B_T$  and  $C_T$  have the same functional form as B and C in equation (2.10), but with T subscripts on the L's and M's.

The value of  $\Gamma$  in (2.22 - 2.24) above is the reflection coefficient looking into port 1 of the two-port being measured when its second port sees  $\Gamma_{LT}$ . Using (2.19), the expression for  $b_4$  can be expanded to give

$$b_4 = P \left[ B_T \left( S_{11} + \frac{S_{12} S_{21} \Gamma_{LT}}{1 - S_{22} \Gamma_{LT}} \right) + C_T \right] b_2$$

(2.25)

An expression for b<sub>5</sub> can be written in terms of b<sub>2</sub>, as well:

$$b_5 = \frac{NS_{21}}{1 - S_{22}\Gamma_{LT}} b_2 \tag{2.26}$$

where N is the gain of the path from the transmission return port to the vector voltmeter's port.

Dividing (2.26) by (2.25) gives

$$\frac{b_{5}}{b_{4}} = \frac{1}{P} \frac{\frac{NS_{21}}{1 - S_{22}\Gamma_{LT}}}{B_{T} \left(S_{11} + \frac{S_{12}S_{21}\Gamma_{LT}}{1 - S_{22}\Gamma_{LT}}\right) + C_{T}}$$

(2.27)

$$= \frac{1}{P} \frac{NS_{21}}{B_{T}(S_{11} - \Gamma_{LT}\Delta) + C_{T}(1 - S_{22}\Gamma_{LT})}$$

(2.28)

Applying the offset and gain terms of the vector voltmeter (S'  $_{21}$  =  $C_0$  +  $C_1$   $b_5/b_4$ ) gives

$$S'_{21} = D + \frac{ES_{21}}{B_{T}(S_{11} - \Gamma_{LT}\Delta) + C_{T}(1 - S_{22}\Gamma_{LT})}$$

(2.29)

where  $S_{21}'$  is the value indicated by the vector voltmeter when the coaxial switch is in the transmission measurement position. Equations (2.21) and (2.29) are two equations in the unknown S-parameters resulting from the measurements. Flipping the two-port under test end for end and measuring it in the reverse direction yields two more equations.

$$S'_{22} = \frac{\left(S_{22} - \Gamma_{L}\Delta\right) + A\left(1 - S_{11}\Gamma_{L}\right)}{B\left(S_{22} - \Gamma_{L}\Delta\right) + C\left(1 - S_{11}\Gamma_{L}\right)}$$

(2.30)

$$S'_{12} = D + \frac{ES_{12}}{B_T(S_{22} - \Gamma_{LT}\Delta) + C_T(1 - S_{11}\Gamma_{LT})}$$

(2.31)

Equations (2.21) and (2.29 - 2.31) give four equations in the four unknown S-parameters. Unfortunately, these equations are nonlinear, and cannot be inverted in closed form to give the S-parameters<sup>[2]</sup>. This difficulty is removed, however, if  $\Gamma_L$ , B and C do not change when the vector voltmeter is switched from reflection to transmission measurement. Taking  $\Gamma_L = \Gamma_{LT}$ , B<sub>T</sub> = B and C<sub>T</sub> = C the above equations can be solved. This inversion yields expressions for the true S-parameters in terms of the measured values:

$$S_{11} = \frac{E^{2}(A - CS'_{11})(BS'_{22} - 1) - \Gamma_{L}(AB - C)^{2}(S'_{12} - D)(S'_{21} - D)}{E^{2}(BS'_{11} - 1)(BS'_{22} - 1) - \Gamma_{L}^{2}(AB - C)^{2}(S'_{12} - D)(S'_{21} - D)}$$

(2.32)

$$S_{12} = \frac{E(AB - C)(S'_{12} - D)[(BS'_{11} - 1) - \Gamma_L(A - CS'_{11})]}{E^2(BS'_{11} - 1)(BS'_{22} - 1) - \Gamma_L(AB - C)^2(S'_{12} - D)(S'_{21} - D)}$$

(2.33)

$$S_{21} = \frac{E(AB - C)(S'_{21} - D)[(BS'_{22} - 1) - \Gamma_{L}(A - CS'_{22})]}{E^{2}(BS'_{11} - 1)(BS'_{22} - 1) - \Gamma_{L}(AB - C)^{2}(S'_{12} - D)(S'_{21} - D)}$$

(2.34)

$$S_{22} = \frac{E^{2}(A - CS'_{22})(BS'_{11} - 1) - \Gamma_{L}(AB - C)^{2}(S'_{12} - D)(S'_{21} - D)}{E^{2}(BS'_{11} - 1)(BS'_{22} - 1) - \Gamma_{L}^{2}(AB - C)^{2}(S'_{12} - D)(S'_{21} - D)}$$

(2.35)

In order to use these closed-form solutions and avoid an iterative calculation at each frequency point of the measurement, the hardware of the system is engineered to isolate the detector switch from the RF measurement ports of the analyzer. Attenuators are placed between the four-port network and the vector voltmeter, and between port 2 of the device under test and the transmission return port, as indicated in Figure 2.6. Also, the input port of the vector voltmeter is matched to the line as well as possible, and switches that terminate unselected lines in 50  $\Omega$  are used.

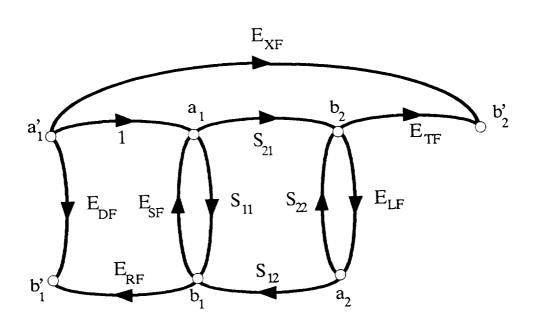

With the assumption of switch-independence, then, only six complex constants, A, B, C, D, E, and  $\Gamma_L$  are required to model the linear systematic errors of the reflection-transmission test set. The error model for the test set can again be drawn as a signal flow graph, as shown in Figure 2.7. The three error terms noted above have not changed, but three new ones have been added.  $E_L$  is the load mismatch term, related to the mismatch of the transmission return port of the analyzer.  $E_T$  is the gain of the transmission return path.  $E_X$  is related to the vector voltmeter's offset term. The results above can be rewritten in terms of this error model to give

Figure 2.7 This flow graph shows the error model for the reflection-transmission test set.

$$S_{11} = \frac{\left\{ \left[ \frac{S'_{11} - E_{D}}{E_{R}} \right] \left[ 1 + \left[ \frac{S'_{22} - E_{D}}{E_{R}} \right] E_{S} \right] - \left[ \left[ \frac{S'_{21} - E_{X}}{E_{T}} \right] \left[ \frac{S'_{12} - E_{X}}{E_{T}} \right] E_{L} \right]}{\left[ 1 + \left[ \frac{S'_{11} - E_{D}}{E_{R}} \right] E_{S} \right] \left[ 1 + \left[ \frac{S'_{22} - E_{D}}{E_{R}} \right] E_{S} \right] - \left[ \left[ \frac{S'_{21} - E_{X}}{E_{T}} \right] \left[ \frac{S'_{12} - E_{X}}{E_{T}} \right] E_{L} \right]} (2.36)$$

$$S_{21} = \frac{\left[1 + \left[\frac{S_{22}' - E_{D}}{E_{R}}\right] (E_{S} - E_{L})\right] \left[\frac{S_{21}' - E_{X}}{E_{T}}\right]}{\left[1 + \left[\frac{S_{11}' - E_{D}}{E_{R}}\right] E_{S}\right] \left[1 + \left[\frac{S_{22}' - E_{D}}{E_{R}}\right] E_{S}\right] - \left[\left[\frac{S_{21}' - E_{X}}{E_{T}}\right] \left[\frac{S_{12}' - E_{X}}{E_{T}}\right] E_{L}^{2}} (2.37)}$$

with similar results for  $S_{12}$  and  $S_{22}$ .

So six complex constants (at each frequency of interest) are sufficient to completely characterize the errors of this type of network analyzer. These constants are found by measuring six known standards.

In addition to the assumption of switch-independence, another assumption has been made to arrive at the result above. It is assumed that the only coupling between the reflection and transmission test ports is through the network under test: there are no RF leakage paths (the "leakage path" that gives rise to the D term in (2.29) is in fact just a result of the offset term in the vector voltmeter's response). The assumption of no RF leakage is good in most systems, since coaxial relays, which have very high isolation, are typically used to switch the signal paths. If significant leakage paths do exist, the expressions above are invalid and the closed-form solution impossible.

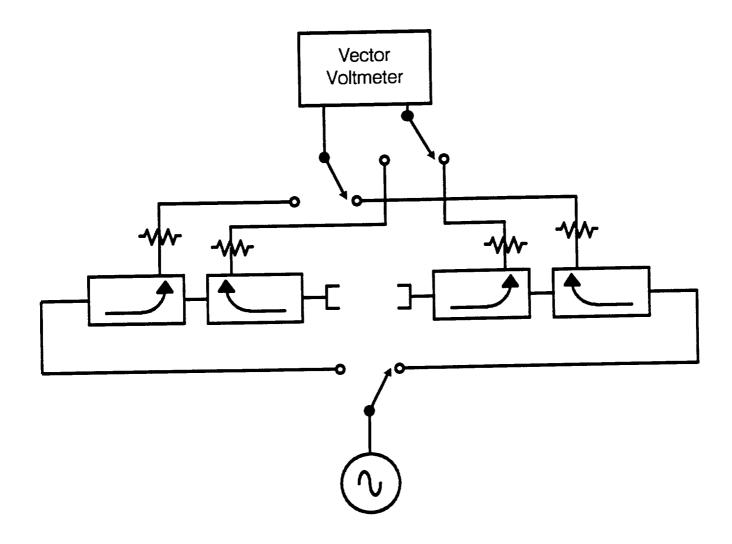

Finally, for the sake of thoroughness, Figure 2.8 shows the architecture of a full S-parameter test set. This is the configuration used in such state-of-the-art network analyzers as the Hewlett-Packard 8510. It consists essentially of two transmission-reflection test sets of the type just discussed placed back to back. Another coaxial switch selects which end of the setup receives the test signal. Thus, there is no need to flip the device under test end for end. This improves measurement speed and accuracy. As long as the detector switch is isolated from the network as described above, an analysis similar to that above can be performed to yield closed-form expressions for the S-parameters. The analysis is essentially performed twice, once for each position of the source switch. The result is two signal flow graphs like that of Figure 2.7, and an error model which contains twelve complex constants. This is the "full twelve term error model" which is often mentioned in connection with these analyzers.

Figure 2.8 A full S-parameter test set using the 4-port network analyzer.

So in summary, four-port type network analyzers measure the S-parameters of two-ports by using a single vector voltmeter with an arrangement of switches and directional couplers to route the appropriate signals to the voltmeter. As long as the networks used satisfy requirements of switch independence and isolation, the S-parameters of the unknown device can be found from the measured data.

As will be seen in the next section, things are simplified somewhat if two vector voltmeters are included in the system, and the number of switches reduced. This is the approach taken when six-port network analyzers are used to measure S-parameters.

#### 2.2 Six-Port Network Analyzer Theory

It was shown in the previous section that if the complex ratio,  $b_3/b_4$ , of two voltage waves emerging from a four-port network can be determined, then the reflection coefficient  $\Gamma$  of the unknown load connected to the four-port's test port can be calculated. The six-port network analyzer allows  $b_3/b_4$  to be determined without the use of a vector voltmeter. This reduces the cost and complexity of the system.

Figure 2.9 shows the general six-port network analyzer configuration<sup>[3]</sup>. Only microwave power detectors are used in this instrument. These are square law detectors; that is  $P_i = |b_i|^2$ , i = 3..6. By measuring the magnitudes of the voltage waves emerging from port 3, 4, 5 and 6, and doing some trigonometry, the complex ratio of the wave emerging from port 3 to that at port 4 can be calculated. This reduces the six-port to an equivalent four-port network analyzer, which may be calibrated as described in Chapter 2.

The equivalence of the six-port and the four-port analyzers can be seen by noting that the addition of ports 5 and 6 does not change any of the arguments presented in the previous section. One can think of ports 5 and 6, and their terminating impedances being absorbed into the network, leaving a four-port network.

Figure 2.9 The six-port network analyzer uses only power detectors to determine the complex ratio  $a_2/b_2$  at its test port.

The six-port network, with power detectors installed, then, is like a four-port network with a built-in vector voltmeter. Since power detectors are relatively inexpensive, it is usually unnecessary to switch-multiplex them between two six-port networks as was done with the vector voltmeter in the four-port measurement systems described above. The self-contained reflectometer module becomes the basic building block of measurement systems using the six-port network analyzer. As will be seen below, this facilitates measurement architectures and procedures different from those used with the four-port system.

As in Section 2.1, the theory of the reflectometer will be described first, followed by that of the S-parameter measurement system.

#### 2.2.1 Reflection Measurements with the 6-Port Network Analyzer

With the reflectometer of Figure 2.9, the goal is to find the ratio of  $b_3/b_4$ . This quantity is defined as w. Once the complex ratio w is found, the same calibration and measurement procedures as were used for the four-port network analyzer can be applied. For this reason, finding w from the six-port's power detector outputs is termed a six-port to four-port conversion. Although w is a bilinear transform of the desired quantity  $\Gamma$ , the complex w-plane is the most convenient in which to work for many of the calculations related to calibration and measurement with the six-port.

The key observation for making the six-port to four-port conversion is that the voltage waves emerging from ports 5 and 6 of the six-port are related to those from ports 3 and 4 in a simple way [4]:

$$b_5 = Kb_3 + Lb_4$$

(2.38)

$$b_6 = Mb_3 + Nb_4$$

(2.39)

Rearranging and taking magnitudes gives

$$\frac{1}{|K|} \left| \frac{b_5}{b_4} \right| = \left| \frac{b_3}{b_4} + \frac{L}{K} \right| \tag{2.40}$$

$$\frac{1}{\text{IMI}} \begin{vmatrix} b_6 \\ b_4 \end{vmatrix} = \begin{vmatrix} b_3 \\ b_4 \end{vmatrix} + \frac{N}{M}$$

(2.41)

Taking  $w \equiv b_3/b_4$ , these expressions can be written as

$$|w| = \left| \frac{b_3}{b_4} \right| \tag{2.42}$$

$$\left| w - w_1 \right| = \frac{1}{|K|} \left| \frac{b_5}{b_4} \right| \tag{2.43}$$

$$|w - w_2| = \frac{1}{|M|} \left| \frac{b_6}{b_4} \right|$$

(2.44)

where  $w_1 = -L/K$  and  $w_2 = -N/M$ . In terms of the powers measured at the various ports, this gives

$$|w|^2 = {}^{P}3/P_4$$

(2.45)

$$|w - w_1|^2 = \zeta^{P_5/P_4}$$

(2.46)

$$|w - w_2|^2 = \rho^{P} 6/P_4 \tag{2.47}$$

In the complex w plane these are just equations of circles, as shown in Figure 2.10. So with the powers at ports 3, 4, 5 and 6 known, the problem of finding the complex quantity  $b_3/b_4$  and reducing the six-port to an equivalent four-port is just one of finding the intersection of three circles.

The more difficult problem is that of finding the calibration constants,  $w_1$ ,  $w_2$ ,  $\varsigma$  and  $\rho$ . This requires an additional level of calibration for the six-port. First, a six-port-to-four-port calibration determines these constants, and then a four-port calibration procedure which may be similar to that described in section 2.1 completes the system calibration.

Interestingly enough, no precision calibration standards are required for the six-port-to-four-port calibration. A constraining relationship can be found between the calibration constants based solely on the linearity of the six-port network. This relationship allows the calibration constants to be determined by observing measurements of a few roughly-known reflection coefficients. The values of the calibration constants determined are independent of the particular reflection coefficient values used for the calibration.

Figure 2.10 Outputs of the six-port's power detectors give a family of circles that can be solved for the complex ratio of the signals at two of the detectors.

The procedure for deriving the constraining relationship, as outlined by Engen<sup>[5]</sup>, is to solve (2.46) and (2.47) to give the real and imaginary parts of w in terms of the measured powers and the calibration constants. Then, using (2.45), (Re w)<sup>2</sup> + (Im w)<sup>2</sup> =  $P_3/P_4$  eliminates the dependence on w altogether, leaving the desired result.

Expanding (2.46) gives

$$(w - w_1) (w^* - w_1^*) = 5 \frac{P_5}{P_4}$$

(2.48)

$$|w|^2 - ww_1^* - w_1w^* + |w_1|^2 = \zeta \frac{P_5}{P_4}$$

(2.49)

$$|w|^2 - 2R_e (ww_1^*) + |w_1|^2 = 5 \frac{P_5}{P_4}$$

(2.50)

Substituting (2.35) into (2.50) and expanding R<sub>e</sub>(ww<sub>1</sub>\*) gives

$$\frac{P_3}{P_4} - 2 \left[ (\text{Re w}) (\text{Re w}_1) + (\text{Im w}) (\text{Im w}_1) \right] + |w_1|^2 = 5 \frac{P_5}{P_4}$$

(2.51)

which is a linear equation in Re w and Im w. Performing the same operations on (2.47) gives

$$\frac{P_3}{P_4} - 2 \left[ (\text{Re w}) (\text{Re w}_2) + (\text{Im w}) (\text{Im w}_2) \right] + |w_2|^2 = \rho \frac{P_6}{P_4}$$

(2.52)

These two equations can be solved for Re w and Im w to give

$$Re \ w = \frac{1}{2} \frac{(Im \ w) (Iw_2 I^2 + P_3/P_4 - \rho P_6/P_4) + (Im \ w_2) (\$ P_5/P_4 - P_3/P_4 - Iw_1 I^2)}{(Re \ w_2) (Im \ w_1) - (Re \ w_1) (Im \ w_2)}$$

(2.53)

$$\operatorname{Im} w = -\frac{1}{2} \frac{(\operatorname{Re} w_{1})(|w_{2}|^{2} + P_{3}/P_{4} - \rho P_{6}/P_{4}) + (\operatorname{Re} w_{2})(\xi P_{5}/P_{4}-P_{3}/P_{4}-|w_{1}|^{2})}{(\operatorname{Re} w_{2})(\operatorname{Im} w_{1}) - (\operatorname{Re} w_{1})(\operatorname{Im} w_{2})}$$

(2.54)

Squaring these and adding them gives, after some lengthy algebra,

$$a\left(\frac{P_{3}}{P_{4}}\right)^{2} + b \, \xi^{2} \left(\frac{P_{5}}{P_{4}}\right)^{2} + c \, \rho^{2} \left(\frac{P_{6}}{P_{4}}\right)^{2} + (c-a-b) \, \, \xi \left(\frac{P_{3}P_{5}}{P_{4}}\right)$$

$$+ (b-a-c) \, \rho \left(\frac{P_{3}P_{6}}{P_{4}}\right) + (a-b-c) \, \, \xi \, \rho \left(\frac{P_{5}P_{6}}{P_{4}}\right)$$

$$+ a(a-b-c) \, \frac{P_{3}P_{6}}{P_{4}} + b(b-a-c) \, \, \xi \, \frac{P_{5}P_{6}}{P_{4}} + c(c-a-b) \, \rho \, \frac{P_{6}}{P_{4}} + abc = 0$$

$$(2.55)$$

where

$$a = |w_1 - w_2|^2 (2.56)$$

$$b = |w_2|^2$$

(2.57)

$$c = |w_1|^2 \tag{2.58}$$

Equation (2.55) gives the relationship between  $w_1$ ,  $w_2$ ,  $\zeta$  and  $\rho$  and the power readings observed for any measured reflection coefficient. From here, the calibration can proceed in one of two ways. Observing nine different values of reflection coefficient, and inserting the observed values of power into (2.55) generates a 9X9 matrix, which can be solved to give the values of a/(abc), b $\zeta^2$ /(abc),...,c(c-a-b)  $\rho$ /(abc). In order to find a,...,  $\rho$ , however, this third-order set of equations must be solved simultaneously, an iterative process which does not always converge to the proper values.

There is an alternative approach, pointed out by Engen [5], which yields the values of a,...,  $\rho$  in closed form with as few as five observations of reflection coefficients. The assumption that results in this simplification is that all of the values used in the calibration lie along a single circle in the w-plane. This can be achieved experimentally to a good precision through the use of a sliding short circuit. Sliding short circuits are readily available in coaxial transmission lines and rectangular waveguides. As the short circuit moves from point to point in the transmission line, it traces out a circle in the reflection coefficient plane ( $|\Gamma| = 1$ ). A bilinear transform always carries a circle into a circle, so in the w-plane, another circle is traced out,  $|w-R_C|^2 = R^2$ .

The situation is shown in Figure 2.11. Only one measurement center,  $w_1$ , is considered in the first stage of the calibration. It can be assumed that this first center lies on the w-plane's real axis. This simply amounts to an arbitrary choice of the phase of  $b_3$ . Since the phase quantity to be found is the phase difference between  $b_3$  and  $b_4$ , this does not affect the problem. Choosing the phase of  $w_1$  sets the value of the phase of  $w_2$ , which must be found later in the procedure.

A relationship similar to (2.55) between the observed powers and the calibration constants must be found. This can be done most easily by observing that the equations that define the present case,  $|w|^2 = P_3/P_4$ ,  $|w-w_1|^2 = \zeta P_5/P_4$  and  $|w-R_c|^2 = R^2$  differ from (2.45-2.47) only in the last equation. Thus, the result of eliminating w from these equations can be found by substituting  $R_c$  for  $w_2$  and  $R^2$  for  $\rho$   $P_6/P_4$  in equation (2.55). This gives

$$A\left(\frac{P_3}{P_4}\right)^2 + 2B\left(\frac{P_3 P_5}{P_4^2}\right) + C\left(\frac{P_5}{P_4}\right)^2 + 2D\left(\frac{P_3}{P_4}\right) + 2E\left(\frac{P_5}{P_4}\right) + F = 0$$

(2.59)

where

$$A = a' \tag{2.60}$$

$$B = \zeta (c-a'-b')/2$$

(2.61)

$$C = \xi^2 b' \qquad (2.62)$$

$$D = [R^{2}(b'-a'-c) + a'(a'-b'-c)]/2$$

(2.63)

$$E = \S[R^{2}(a'-b'-c) + b'(b'-a'-c)]/2$$

(2.64)

$$F = [R^4 + R^2(c-a'-b') + a'b']c$$

(2.65)

and where

$$a' = |w_1 - R_C|^2$$

(2.66)

$$b' = |R_c|^2 \tag{2.67}$$

$$c = |w_1|^2$$

(2.68)

$$\zeta = \frac{1}{|K|^2} \tag{2.69}$$

Figure 2.11 The sliding short circuit, used in the first stage of the the six-port calibration, traces out a circle in the complex w-plane.

Surprisingly, as will be seen below, (2.60-2.65) can be solved in closed form to give a', b', c,  $\zeta$  and  $R^2$ . First, however, values of A,...,F must be determined experimentally.

Application of a standard test [6] to (2.59) shows that it is the equation of an ellipse in the  $P_3/P_4$ ,  $P_5/P_4$  plane. This ellipse is constrained to the first quadrant of the plane. Thus, A,...,F can be determined by least-squares fitting a conic section to the observed pairs  $(P_3/P_4, P_5/P_4)$ , and then testing to assure that the resulting coefficients give an ellipse in the first quadrant. A six-port network with the center  $w_1$  badly placed (e.g.,  $w_1$  very close to zero relative to the radius R) can fail these tests. In this case, the observed pairs will lie along an ellipse that is so eccentric that small measurement errors in the values of  $(P_3/P_4, P_5/P_4)$  can cause the best-fit conic section to be a hyperbola, or an ellipse crossing out of the first quadrant. A failure of this type indicates that measurement accuracy of the six-port at the frequency of the failure would be intolerably bad.

The best fit conic section can be found in a straightforward way. Substituting  $x = P_3/P_4$  and  $y = P_5/P_4$  into (2.59) and dividing through by F gives

$$\frac{A}{F} x^2 + 2 \frac{B}{F} xy + \frac{C}{F} y^2 + 2 \frac{D}{F} x + 2 \frac{E}{F} y + 1 = 0$$

(2.70)

The error to be minimized can then be written as

$$\xi = \sum_{i} \left( \frac{A}{F} \times_{i}^{2} + 2 \frac{B}{F} \times_{i} Y_{i} + \frac{C}{F} Y_{i}^{2} + 2 \frac{D}{F} \times_{i}^{+} + 2 \frac{E}{F} Y_{i}^{+} + 1 \right)^{2}$$

(2.71)

To minimize this error, the partial derivatives  $\partial \xi/\partial (A/F),..., \partial \xi/\partial (E/F)$  are taken and set equal to zero. This yields five linear equations in the five unknowns A/F,...,E/F. Observing at least five different values of reflection coefficient, and solving a 5X5 matrix, then, yields values of A/F,...,E/F. Given these values, the task remaining is to solve (2.60 - 2.65) for a'...\(\xi\).

This is achieved by first making the following definitions:

$$\alpha = (R^2 + a')/\zeta \tag{2.72}$$

$$\beta = [(R^2 - a')(R^2 - b') + 2R^2C]/\xi$$

(2.73)

$$\gamma = R^2 + b' \tag{2.74}$$

$$\delta = (R^2 - a')/\zeta \tag{2.75}$$

$$E = R^2 - b'$$

(2.76)

Substitution shows that the quantities  $\alpha,...,\epsilon$  can be expressed directly in terms of A,...,F:

$$\frac{BD - AE}{AC - B^2} = \alpha \tag{2.77}$$

$$\frac{DE - BF}{AC - B^2} = \beta \tag{2.78}$$

$$\frac{BE - DC}{AC - B^2} = \gamma \tag{2.79}$$

$$\frac{AF - D^2}{AC - B^2} = \delta^2$$

(2.80)

$$\frac{\text{CF} - \text{E}^2}{\text{AC} - \text{B}^2} = \epsilon^2 \tag{2.81}$$

It is observed that the numerators and denominators of the left sides of (2.77 - 2.81) can be divided through by  $F^2$  to yield expressions only in terms of A/F,...,E/F. Thus the values of  $\alpha$ ,..., $E^2$  can be found directly from the sliding short calibration data. The expressions for  $\alpha$ ,..., $E^2$ , (2.72 - 2.76) can in turn be solved for a',..., $E^2$ :

$$a' = |w_1 - R_C|^2 = \frac{(\alpha - \delta)(\gamma + \epsilon)}{2(\alpha + \delta)}$$

(2.82)

$$b' = |R_C|^2 = \frac{\gamma - \epsilon}{2} \tag{2.83}$$

$$c = |w_1|^2 = \frac{\beta - \delta \epsilon}{\alpha + \delta}$$

(2.84)

$$\zeta = \frac{\gamma + \epsilon}{\alpha + \delta} \tag{2.85}$$

$$R^2 = \frac{\gamma + \epsilon}{2} \tag{2.86}$$

So the total six-port-to-four-port reduction is a three-step process. First, the sliding short calibration data are summed into the 5X5 matrix derived from (2.71). Solving this gives A/F,...,E/F. Next, these values are used in (2.77 - 2.81) to give values of  $\alpha$ ,..., $\epsilon$ <sup>2</sup>. Finally, these quantities are used in (2.82 - 2.86) to give values of a',...,R<sup>2</sup>, which contain the calibration constants wanted.

There are still problems, however. Since (2.80) and (2.81) only give expressions for  $\delta^2$  and  $\epsilon^2$ , there is a sign ambiguity in the determinations of  $\delta$  and  $\epsilon$ . Sign ambiguity problems are inherent in the six-port network analyzer, since only magnitudes squared are measured by the instrument. Such ambiguities are encountered at several steps of calibration and measurement, and must be carefully resolved at each step to assure the validity of subsequent results.

In the present case, it is seen from the definition (2.76) that  $\epsilon$  is negative if  $|R_C|^2 > R^2$ , that is, if the circle drawn in the w-plane does not enclose the origin. Similarly from (2.75),  $\delta$  is negative if the measurement center  $w_1$  is outside the circle drawn by the sliding short. This provides one method of resolving this sign ambiguity using knowledge of the network used. Assume first that the interior of the  $|\Gamma|=1$  circle maps to the interior of the corresponding circle in the w-plane. This is the case for most practical six-ports and can be verified by checking the values of  $P_3/P_4$  and  $P_5/P_4$  for some  $\Gamma$ ,  $|\Gamma|<1$  and verifying that the resulting point falls inside the sliding short's ellipse. Given this, if it is known that  $|b_3|\rightarrow 0$  for some value of  $\Gamma$  with  $|\Gamma|\leq 1$ , then the  $|\Gamma|=1$  circle encloses the origin of the w-plane and  $\epsilon>0$ . A similar argument using  $b_5$  can be used for  $\delta$ .

This is the approach taken with the sampled-line network analyzer. The system is engineered so that none of the  $|b_i|$ 's can go to zero for any  $\Gamma$ ,  $|\Gamma| \le 1$ , ensuring that  $\epsilon < 0$  and  $\delta < 0$ .

If the properties of the six-port network are not known, this sign ambiguity can still be resolved, through a clever technique outlined by Engen. One takes all four possible choices of sign for  $\epsilon$  and  $\delta$ . Using the resulting values of the calibration constants and the calibration data from the sliding short and a matched termination, four parallel calculations of the value of  $w_2$  can be performed. All the calculations with incorrect sign assumptions yield self-contradictory results. The one with the correct  $\delta$  and  $\epsilon$  will yield the correct value of  $w_2$ .

Given that  $\epsilon$  and  $\delta$  are found correctly, there is still a sign ambiguity that can not be resolved through the equations above. This ambiguity is in the sign of Im R<sub>C</sub>. If it is chosen incorrectly, the value found by the six-port will be w\* instead of w.

Knowledge of the properties of the six-port used provides the best way to find the sign of  $\rm Im\ R_{\rm C}$ . This is the approach used with sampled-line network analyzer. Otherwise, some completely independent scheme must be devised, perhaps using the reflection coefficient of an additional known standard.

With these sign ambiguities in the determination of a,..., $R^2$  and Im  $R_c$  resolved, there is still the problem of finding  $w_2$  and  $\rho$ . Engen's method described above is an option here. Another option is to substitute  $w_2$  for  $w_1$  and  $\rho$  for  $\zeta$ , in the above and redo the procedure used to find  $w_1$ .

This yields  $w_2$  on the real axis, but the value of  $R_c$  found has a different angle from that found in the determination of  $w_1$ . Rotating the second result for  $R_c$  so that it matches the first rotates  $w_2$  to its proper angle in the plane of the first solution as well. This is the approach used in the sampled-line network analyzer. It is fairly simple and allows the results from the various detector outputs to be compared with uniform criteria in the calibration procedure.

It is interesting to note at this point that, without any knowledge of  $w_2$  or  $\rho$ , it is possible to determine w to within a sign. As can be seen by returning to Figure 2.10, the value of w must be at one of the two intersections of the  $b_3/b_4$  circle and the  $b_5/b_4$  circle. The  $b_6/b_4$  circle simply resolves this ambiguity. If, however, there is another constraint imposed by the network used, which rules out one of these intersections, then the third circle is unnecessary. Then only three detector outputs are required to determine w, and the resulting instrument is known as a five-port network analyzer. The sampled-line network analyzer has this property and is in many ways an extension of the five-port network analyzer concept.

If additional accuracy is sought in determination of the calibration constants, the values found through the closed-form approach outlined above can be used as first estimates of the coefficients of (2.45). An optimizer can then be used to minimize the sum of the squares of the values found in evaluating the left side of (2.45) for all the reflection coefficients observed in the calibration procedure.

An important determinant of system accuracy is the geometric placement of the measurement centers around the  $|\Gamma|=1$  circle in the w-plane. This placement is set by the particular six-port network used in the implementation of the network analyzer. Clearly, if all the measurement centers are close together compared to the unit circle, then triangulating from them to find  $\Gamma$  will yield poor accuracy. Figure 2.12 shows an implementation used at NBS [7], and the resulting placement of the measurement centers.

This implementation has the advantage that  $b_4$  depends only on  $b_2$ , to the limit of the directivity of the hybrids used. This makes  $b_3/b_4$  approximately a linear transform of  $\Gamma$  instead of a bilinear transform, which can simplify some of the preliminary calculations. The regular spacing of the measurement centers around the unit circle results in good accuracy for this instrument.

Figure 2.12 The six-port network analyzer as implemented at NBS. The boxes marked 'H' are 180° hybrid networks and those marked with 'Q' are quadrature hybrids.

As has been seen, the six-port network can be calibrated to measure the complex ratio of  $b_3/b_4$ . This ratio must then be calibrated to yield the value of  $\Gamma = a_2/b_2$ . As noted above, this requires determination of the three complex constants of the bilinear transform relating  $\Gamma$  and  $b_3/b_4$ .

If a single six-port reflectometer is used, then the same calibration options are available as with the four-port reflectometer. Three known standards are measured, and the results can be inverted to give the complex constants of the bilinear transform. If two six-ports are used, as in an S-parameter measurement system, however, other options are available, as will be seen below.

#### 2.2.2 Dual Reflectometer Calibration - The TRL Scheme

With a single reflectometer, the final accuracy of a calibration depends on how accurately the reflection coefficients of a set of precision terminations are known. To set the reference plane, the reflection coefficient of at least one of the standards must be known to a precision greater than that of the network analyzer over the entire frequency range of operation. Even with the simplest of calibration standards, the short circuit, this is often impractical. A set of two reflectometers, however, can "calibrate each other" through a procedure developed at the National Bureau of Standards [8] known as the "thru-reflect-line" or TRL calibration procedure. In this procedure, the precise properties of the calibration standards need not be known, and are in fact derived as a by-product of the calibration. Two standards are used for this procedure. One is a precision coaxial line of approximately known length and the other is a termination with a reflection coefficient different from zero, the exact value of which is only approximately known.

As it turns out, the requirement of having two reflectometers for the TRL procedure is not a drawback. It will be seen below that two reflectometers are used to construct an S-parameter measurement system using six-ports. With two six-ports present in the system in any case, the fact that they can calibrate each other is a bonus.

The TRL calibration procedure is implemented on the sampled-line network analyzer, and will be described briefly here.

The TRL calibration procedure is only a reflectometer calibration procedure. Given two reflectometers that can measure  $b_3/b_4$ , TRL provides the coefficients of the bilinear transforms to give the  $\Gamma$ 's connected to each reflectometer. Additional calibration is required to allow the two reflectometers to measure the S-parameters of a general two-port network.

The three measurements used for TRL are shown in Figure 2.13. As described in Section 2.1, an uncalibrated reflectometer can be represented as an ideal reflectometer with an error two-port between its port and the measurement port. This representation is used in Figure 2.13. The six-port to four-port conversion described above allows the two reflectometers to measure their respective  $b_3/b_4$ 's. The goal of the TRL calibration procedure is to determine the parameters of the error boxes A and B.

In the first measurement, the two reflectometers are connected port to port. This measurement yields the cascade of the two error two-ports. In the second measurement, the two reflectometers look at each other through a length of precision transmission line, which by hypothesis contains no internal reflections or reflections from its ports. The length of this line does not need to be known exactly, but for numerical stability, a value near a quarter wavelength at the measurement frequency is desirable. In the final measurement, a nominal short circuit is connected to the two reflectometer ports.

When the two reflectometers look at each other through a given two-port, their responses in terms of that network's S-parameters can be written as follows:

$$b_1 = S_{11}^{a_1} + S_{12}^{a_2} (2.87)$$

$$b_2 = S_{21}a_1 + S_{22}a_2 \tag{2.88}$$

where, for the present case  $(a_1 \ a_2)^T = (b_4 \ b_4')^T$  and  $(b_1 \ b_2)^T = (b_3 \ b_3')^T$ . Dividing (2.87) by  $a_1$  and (2.88) by  $a_2$  and eliminating  $a_2/a_1$  gives

$$w_2 S_{11} + w_1 S_{22} - \Delta = w_1 w_2$$

(2.89)

where

$$\Delta = S_{11} S_{22} - S_{12} S_{21}$$

(2.90)

and

$$w_1 = b_1/a_1 = b_3/b_4 (2.91)$$

$$w_2 = b_2/a_2 = b_3'/b_4'$$

(2.92)

Figure 2.13 In the TRL calibration procedure, the coefficients of the error boxes A and B of two reflectometers are determined by making the three measurements shown here. A straight through, a length of line and a high-reflection load of approximately known value are used.

By observing values of  $w_1$  and  $w_2$  for three values of  $a_2/a_1$ , a set of three linear equations in three unknowns can be generated, and solving these gives the values of  $S_{11}$ ,  $S_{22}$  and  $\Delta$ . In the laboratory, the value of  $a_2/a_1$  is changed by placing a variable phase shifter or variable attenuator between one of the reflectometer heads and the signal generator. In practice, more than three values of  $a_2/a_1$  are used and a least-squares solution is found.

Since the TRL procedure involves cascaded two-port networks, it is convenient to work in terms of the wave cascading parameters or T-parameters. The T-parameters are defined by

$$= \frac{1}{T} \begin{pmatrix} a_2 \\ b_2 \end{pmatrix} \qquad (2.94)$$

The T-matrix for the cascade of two networks is just the product of the T-matrices of the two networks.

The T-matrix can be written in terms of the S-matrix as

This result is interesting in that it shows that by solving a set of equations like (2.89) all the T-parameters of an unknown network can be found to within a multiplicative factor,  $1/S_{21}$ . As will be seen below, the TRL method deals only with ratios of T-parameters, so all the required information can be found in this way. With this recognized, the description of the TRL procedure may continue.

If  $\overrightarrow{A}$  and  $\overrightarrow{B}$  represent the T-matrices of the two error boxes, A and B, respectively, then for the "thru" connection, the fictional two-port  $\overrightarrow{U}$  that is observed is given by

$$\overline{U} = \overline{A} \overline{B}$$

(2.96)

For the "line" connection, the observed two-port D is

where L represents the T-parameters of the line inserted between the two reflectometers.

Equation (2.96) can be solved for B to give

$$\overline{\overline{B}} = \overline{\overline{A}}^{-1} \overline{\overline{U}}$$

(2.98)

inverting both sides of (2.98) and post-multiplying (2.97) by the result gives

$$\stackrel{=}{\overset{=}{D}} \stackrel{=}{\overset{=}{U}} \stackrel{=}{\overset{=}{A}} \stackrel{=}{\overset{=}{A}} \stackrel{=}{\overset{=}{B}} \stackrel{=}{\overset{=}{B}}$$

(2.99)

$$\overline{\overline{X}} \overline{A} = \overline{\overline{A}} \overline{L}$$

(2.100)

where

$$\overline{\overline{X}} = \overline{\overline{D}} \overline{\overline{U}}^{-1} \tag{2.101}$$

An assumption must be made about the value of L, the T-parameters of the length of line used as a calibration standard. It is taken to be

$$\stackrel{=}{L} \begin{bmatrix} e^{-\gamma 1} & 0 \\ 0 & e^{\gamma 1} \end{bmatrix}$$

(2.102)

This assumes that the line is uniform, not necessarily lossless, and that there are no reflections from it  $(S_{11} = S_{22} = 0)$ .

Given this assumption, equation (2.100) can be expanded to give

$$X_{11} A_{11} + X_{12} A_{21} = A_{11} e^{-\gamma 1}$$

(2.103)

$$X_{21} A_{11} + X_{22} A_{21} = A_{21} e^{-\gamma 1}$$

(2.104)

$$X_{11} A_{12} + X_{12} A_{22} = A_{21} e^{\gamma 1}$$

(2.105)

$$X_{21} A_{12} + X_{22} A_{22} = A_{22} e^{\gamma 1}$$

(2.106)

Dividing (2.103) by (2.104) and (2.105) by (2.106) gives

$$\frac{X_{21}}{X_{12}} \left( \frac{A_{11}}{A_{21}} \right)^2 + \frac{X_{22} - X_{11}}{X_{12}} \left( \frac{A_{11}}{A_{21}} \right) - 1 = 0$$

(2.107)

$$\frac{X_{21}}{X_{12}} \left( \frac{A_{12}}{A_{22}} \right)^2 + \frac{X_{22} - X_{11}}{X_{12}} \left( \frac{A_{12}}{A_{22}} \right) - 1 = 0$$

(2.108)

So it is seen that the values  $A_{11}/A_{21}$  and  $A_{12}/A_{22}$  are solutions of the same quadratic equation. The coefficients of this equation can be determined from the measured  $b_3/b_4$ 's for the thru and line measurements via (2.89) and (2.101).

It is easy to see that  $(A_{11}/A_{21}) \neq (A_{12}/A_{22})$ . From (2.95) this would require that the error box A have  $S_{12}S_{22} = 0$  so there would be no transmission through the box.

Thus  $(A_{11}/A_{21})$  and  $(A_{12}/A_{22})$  are the two distinct roots of the quadratic equation. The question of root choice then arises again: which root represents which ratio? Approximate knowledge of the properties of the line calibration standard can be used to answer this question.

Dividing (2.106) by (2.104) gives

$$e^{2\gamma 1} \frac{X_{21} (A_{12}/A_{22}) + X_{22}}{X_{12} (A_{21}/A_{11}) + X_{11}}$$

(2.109)

so if the length of the transmission line used as the line standard is known fairly accurately, the value of  $e^{2\gamma l}$  can be calculated, and this can be used to resolve the root ambiguity. This method has the advantage that it depends only on quantities found in the course of the TRL calibration procedure, but unfortunately it is not foolproof. As stated above, the transmission line standard is chosen to have a phase delay near  $\pm 90^{\circ}$ . It is a low-loss line, so  $|e^{2\gamma l}| \approx 1$ . This places  $e^{2\gamma l}$  near  $\pm 1$ . The two possible root choices, when inserted in the right side of (2.109), yield values that are reciprocals of each other. If the phase delay of the line is too near  $\pm 90^{\circ}$ , then  $e^{2\gamma l}$  and its reciprocal cannot be easily distinguished, and measurement errors may lead to an improper root choice.

An alternative approach uses the result found in Section 2.1, that for the reflectometer with error box A,

$$w_1 = \frac{a\Gamma + b}{c\Gamma + 1} \tag{2.110}$$

where  $\Gamma$  is the reflection coefficient measured by the reflectometer and

$$a = A_{11}/A_{22}$$

(2.111)

$$b = A_{12}/A_{22} (2.112)$$

$$c = A_{21}/A_{22}$$

(2.113)

A rough calibration using three impedance standards, such as a short circuit, an open circuit and a matched load, can be performed to find approximate values of a, b, and c. Only one of the roots of (2.107) and (2.108) will be close to b, and this serves to resolve the root ambiguity. This method does not suffer the problems of the previous one, but does require additional known, independent calibration standards, which are not easy to come by in all types of transmission line.

Inspecting (2.110 - 2.113), it is seen that b and a/c have been determined from the roots of the quadratic equation (2.103). All that remains to characterize error box A is to determine the value of a. Rearranging (2.106) gives

$$a = \frac{w_1 - b}{\Gamma(1 - w_1 c/a)}$$

(2.114)

So, if one uses one precision standard, say a short circuit, then (2.114) can be solved for a and the calibration of error box A is complete. This approach is known as the "thru-short-delay," or TSD calibration procedure. Error box B can then be determined from (2.96).

For the TRL procedure it is assumed that  $\Gamma$  is not known precisely. More manipulation shows that this knowledge is not required for the determination of a. Equation (2.96) can be rewritten as

$$A_{22} B_{22} \begin{pmatrix} a & b \\ c & 1 \end{pmatrix} \begin{pmatrix} \alpha & \beta \\ \gamma & 1 \end{pmatrix} = U_{22} \begin{pmatrix} d & e \\ f & 1 \end{pmatrix}$$

(2.115)

where

$$a = A_{11}/A_{22} (2.116)$$

$$b = A_{12}/A_{22} (2.117)$$

$$c = A_{21}/A_{22} \tag{2.118}$$

$$\alpha = B_{11}/B_{22} \tag{2.119}$$

$$\beta = B_{12}/B_{22} \tag{2.120}$$

$$\gamma = B_{21}/B_{22} \tag{2.121}$$

$$d = U_{11}/U_{22} (2.122)$$

$$e = U_{12}/U_{22}$$

(2.123)

$$f = U_{21}/U_{22} \tag{2.124}$$

By premultiplying both sides of (2.115) by  $A^{-1}$  and expanding, it can be shown that

$$\gamma = \frac{f - dc/a}{1 - ec/a} \tag{2.125}$$

$$\beta/\alpha = \frac{e - b}{d - bf} \tag{2.126}$$

$$a\alpha = \frac{d - bf}{1 - ec/a} \tag{2.127}$$

All the quantities on the right side of (2.125 - 2.127) are known, so  $\gamma$ ,  $\beta/\alpha$  and  $\alpha$  can be determined. A relationship like (2.114) holds for error box B. It is

$$\alpha = \frac{w_2 + \gamma}{\Gamma(1 + w_2 \beta/\alpha)}$$

(2.128)

Assuming that the same  $\Gamma$  is connected to both reflectometers during the calibration procedure,  $\Gamma$  can be eliminated from (2.114) and (2.128) to give

$$a/\alpha = \frac{(w_1 - b) (1 + w_2 \beta/\alpha)}{(w_2 + \gamma) (1 - w_1 c/a)}$$

(2.129)

and finally, (2.129) can be combined with (2.127):

$$a = \pm \sqrt{\frac{(w_1 - b) (1 + w_2 \beta/\alpha) (d - bf)}{(w_2 + \gamma) (1 - w_1 c/a) (1 - ec/a)}}$$

(2.130)

and

$$\alpha = \frac{d - bf}{a(1 - ec/a)} \tag{2.131}$$

The sign ambiguity in (2.129) can be resolved by approximate knowledge of  $\Gamma$ . Use of a short circuit for  $\Gamma$  is convenient here. Good short circuit standards are readily available in coaxial lines and waveguides, and can be constructed without great difficulty in many of the transmission lines used in microwave ICs.

So the final result of the above is that two reflectometers can calibrate each other without the use of high-precision calibration standards. The one big assumption made in the preceding development is that the transmission line standard used is reflectionless. The effects of reflections in this standard have not been fully evaluated, but experimental results at the National Bureau of Standards indicate that the TRL procedure yields a very accurate calibration. Typical errors estimated at  $\pm 0.001$  dB in measuring a 20 dB attenuator have been reported [9].

## 2.2.3 S-Parameter Measurements with the Six-Port Network Analyzer

Figure 2.14 shows how two six-port network analyzers are used to construct an S-parameter measurement system. It is assumed here that both six-ports have been calibrated to read the true ratios,  $\Gamma_1$  (=b<sub>1</sub>/a<sub>1</sub>) and  $\Gamma_2$  (=b<sub>2</sub>/a<sub>2</sub>) at the reference planes 1 and 2. This calibration may proceed through any of the methods outlined in the previous sections.

Through a procedure identical to that given in equations (3.50 - 3.55) above, then, the values of  $S_{11}$ ,  $S_{22}$  and  $\Delta$  for the unknown two-port can be determined by observing the values of  $\Gamma_1$  and  $\Gamma_2$  for at least three different excitations (positions of the phase shifter or attenuators).

Figure 2.14 A full S-parameter measurement system using six-port network analyzers.

In order to find the complete S-parameters, some way of separating  $\Delta$  to give S<sub>12</sub> and S<sub>21</sub> must be found. Rewriting (2.87 - 2.88) gives

$$S_{12} = (\mathbf{r}_1 - S_{11}) \frac{a_1}{a_2}$$

(2.132)

$$S_{21} = (\mathbf{r}_2 - S_{22}) \frac{a_2}{a_1}$$

(2.133)

so if the value of  $a_2/a_1$  can be found for each measurement, then  $S_{12}$  and  $S_{21}$  can be found. Some additional calibration is necessary for this determination.

Consider the measurement system of Figure 2.14 as a three-port network with its port 3 near the generator and ports 1 and 2 being the measurement reference planes as numbered. Then it can be shown [7] that

$$\frac{a_2}{a_1} = \left[ s_{21} - s_{11} \frac{s_{23}}{s_{13}} \right] \Gamma_1 - \left[ s_{12} \frac{s_{23}}{s_{13}} - s_{22} \right] \Gamma_2 \frac{a_2}{a_1} + \frac{s_{23}}{s_{13}}$$

(2.134)

where the  $s_{ij}$ 's are the S-parameters of the measurement system three-port. This can be rewritten as

$$\frac{a_2}{a_1} = c_1 \Gamma_1 - c_2 \Gamma_2 \frac{a_2}{a_1} + c_3$$

(2.135)

which can be rearranged to give

$$\frac{a_2}{a_1} = \frac{C_3 + C_1 \Gamma_1}{1 + C_2 \Gamma_2} \tag{2.136}$$

With equation (2.136), then,  $a_2/a_1$  can be determined from the observed  $\Gamma$ 's for any measurement. The remaining difficulty is to find the values of the C's. This can be done by noting that equation (2.135) is linear in the C's. Using at least three known values of  $\Gamma_1$ ,  $\Gamma_2$  and  $a_2/a_1$ , a system of linear equations is formed which can be solved for the C's.