P-119

# Content Addressable Memory Project NASA NAG-2 668 Semiannual Progress Report (Sep91-Feb92) Rutgers University New Brunswick, NJ 08903

J. Hall (PI) S. Levy (PI) D. Smith K. Miyake Laboratory for Computer Science Research Department of Computer Science

March 1,1992

(Jasa-, -) 70707) CONTANT ADDRESSALL MEMORY PROJECT Cadenna / Progress Report, Sep. 1901 - F.A. 1902 (Putjers - The State Cool OPE

422-22.13

Unclas 00/60 0003770

#### 1 abstract

A parameterized version of the tree processor has been designed and tested (by simulation). The leaf processor design is 90% complete. We expect to complete and test a combination of tree and leaf cell design in the next period. Work has been proceeding on algorithms for the CAM, and once the design is complete we will begin simulating algorithms for large problems.

In the last 6 months we have produced four publications that describe various components of our research. They are summarized below.

- J. Storrs Hall, Donald E. Smith, and Saul Levy, The Practical Implementation of Content Addressable Memory, LCSR-TR-179, Laboratory for Computer Science Research, Rutgers University, March 92. This was also submitted to the 1992 Frontiers of Massively Parallel Computation Conference.

- LCSR-TR-179 presents a functional description of our CAM architecture and discusses attributes(e.g., density, scalability, data-path width, and coupling) that determine the effectiveness of such architectures. In addition, two examples are presented that demonstrate the use of CAM-based algorithms.

- Donald E. Smith, Keith M. Miyake, and J. Storrs Hall, Design of a LEAF cell for the Rutgers CAM Architecture, LCSR-TR-180, Laboratory for Computer Science Research, Rutgers University, March 92.

- LCSR-TR-180 presents a specification of the LEAF cell and its interfaces to other modules in the CAM architecture. It describes the four communicating processors which compose each LEAF cell (i.e., k-bit, 1-bit, IO, and memory) and their respective interfaces.

- Keith M. Miyake, Donald E. Smith, Circuit Design Tool User's Manual, LCSR-TR-181, Laboratory for Computer Science Research, Rutgers University, March 92.

- LCSR-TR-181 describes the design tool we have implemented in support of CAM research. The design tool is written for a UNIX software environment and supports the definition of digital electronic modules, the composition of modules into higher level circuits, and event-driven simulation of the resulting circuits. Our tool provides an interface whose goals include straightforward but flexible primitive module definition and circuit composition, efficient simulation, and a debugging environment that facilitates design verification and alteration.

The unique architectural aspects of the Rutgers CAM uses many of the features typical to most design tools; however, it also requires some features that are not widely supported. Our design makes use of many similar, but not identical, modules which puts a premium on design tools that support parameterized modules (e.g., generic entities in VHDL) and strong typing of a module's ports. In addition, since our design is continually evolving, the quality of and control over error handling, in both the design as well as the simulation phase, is very important. In looking for a design tool to support

our research we found that either some critical features were inadequately supported or the tool was much more than we required. In response to this environment we implemented a prototype design tool that supports exactly the features required by the design of the CAM.

• S. Wei and S. Levy, Design and Analysis off Efficient Hierarchical Interconnection Networks, LCSR-TR-167, Laboratory for Computer Science Research, Rutgers University, September 91. A shorter version of this paper was published as: S. Wei and S. Levy, Design and Analysis off Efficient Hierarchical Interconnection Networks, Proceeding of 1991 Supercomputing Conference, Nov. 91, pgs 390-399.

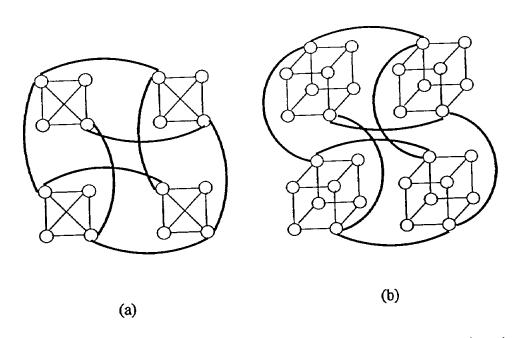

LCSR-TR-167 presents a new approach to message-passing architectures based on the general idea of hierarchical interconnects. The approach chooses the appropriate number of interface nodes and clusters based on performance and cost-effectiveness. The report includes both static and queueing analyses of such networks.

# THE PRACTICAL IMPLEMENTATION OF CONTENT ADDRESSABLE MEMORY\*

J. Storrs Hall, Donald E. Smith, and Saul Levy

LCSR-TR-179

Laboratory for Computer Science Research Hill Center for the Mathematical Science Busch Campus, Rutgers University New Brunswick, New Jersey 08903

# The Practical Implementation of Content Addressable Memory

J. Storrs Hall

Don Smith

Saul Levy

The Rutgers CAM Project<sup>1</sup>

Laboratory for Computer Science Research

Rutgers University

Keywords

content addressable memory, associative processors, SIMD, processor arrays

#### Abstract

The notion of using content addressable memory (CAM) to achieve massively parallel processing has resurfaced regularly since it first appeared in the 1960's, but has consistently failed to produce cost-effective general-purpose systems. An analysis of this situation reveals a number of specific design pitfalls regarding memory density, scalability, datapath width, and processor coupling. Once these are avoided, specific functionalities must be included in the design. This paper details the pitfalls and presents an architecture which avoids them. Further, guidelines are developed for estimating CAM's effectiveness as a parallel processor.

<sup>&</sup>lt;sup>1</sup> Supported by DARPA and NASA under NASA-Ames grant NAG 2-668

#### Introduction

"Pure" content addressable memory (CAM), such as is used in cache lookup, is a method of addressing where each word of memory has a variable address, explicitly stored with the word. With every memory access, the desired address is compared with the stored address in every word. We are concerned here with an extension of this concept which forms the basis for a method of massively parallel processing. It dates back at least to Falkoff[62] and has been called many things, including content addressable parallel processing (Foster[76]) and associative computing (Potter[88]). We shall use CAM as a generic term, to include parallel processing, and will refer to "pure CAM" if it is necessary to distinguish the simple form.

This paradigm is well explained in Foster[76]. The broadcast value, instead of being compared strictly with the address portion of the word, is compared with the entire word (with a mask to provide "don't care" bit positions). The result of the comparison, rather than immediately causing a read or write of a matching word, is stored in an explicit "response bit". The bit is then used to control subsequent read/write operations; in particular, more than one word can be written into simultaneously. Boolean functions are then synthesized from sequences of tests, and bit-serial aithmetic can be performed on all words in parallel.

At a higher level, the model allows for logic, comparisons, and arithmetic between some global value and a local value stored in each word, or between local values in each word. Individual words may refrain from the operations based on locally determined conditions. This results in an architecture which is equivalent to a SIMD star network, with the CPU as the hub and each word as a leaf processor. Since the hardware in the memory is only a few gates in addition to a flip-flop at each bit, CAM should, or so the theory goes, form the basis for massively parallel processors at densities near those of static RAMs.

We examine two questions: (a) can CAM (or some mechanism that implements the CAM computational model) really be built within a small constant factor in cost of RAM, and (b) if so, how efficiently can it be used?

# Typical implementations of CAM

This section explains how, starting from the basic idea of CAM, a designer might ultimately end up with any of a number of existing processor array architectures. This is not to be taken to imply that any of those systems were designed that way, nor indeed had the CAM model in mind at all. It does, however, fairly reflect the authors' own attempts to find a cost-effective realization of the paradigm.

The first problem the CAM designer meets is that CAMs useful for parallel processing require very wide words-256 bits is not unreasonable. Furthermore, each bit position requires a data line and a mask line in the bus, doubling its width. Requiring a 512-bit wide bus is not impossible, but the CAM also requires a connection between each bit in any given word, which ordinary memory does not. Thus it is problematical to split CAM memories onto separate chips, requiring the pinouts of each chip to handle the entire bus width.

What is worse, in the process of most CAM operations, a large portion of the bus is

wasted. Most comparisons are of smaller fields within a word (selected by the mask lines), and in the case of the bit-serial, word-parallel arithmetic, only one or two bits are being tested or set at a time! Clearly, an optimization can be performed: all the comparators at each bit can be removed, and in their place a one-bit ALU can be added to the word. The "match" daisy chain and the read/write control lines can be replaced with a one-bit local bus running across the word. Now the (global) bus is much smaller: an opcode for the ALU, a bit address which can be decoded on-chip, a one-bit data bus. What is more, arithmetic is faster; single-bit arithmetic operations are built into the ALU rather than being synthesized out of logic operations which are in turn synthesized out of masking and testing.

At this point there is a strong temptation for the designer to split the architecture across chips, having processor chips which connect to standard memory chips. This has the advantage of making memory much less expensive, but the disadvantage of tying the number of words to the pinout of the processor chip. The relationship to the original CAM paradigm begins to become somewhat strained also; this implementation puts a strong downward pressure on the number of words/processing elements, and a strong upward pressure on PE complexity, inter-PE connectivity, etc. In practice, this has been the best tradeoff point for CAM-like implementations; it characterizes the evolutionary niche occupied by the CM-1, the DAP, the MPP, and even the Illiac. Of course these machines were not (necessarily) designed as an implementation of CAM: they are mentioned to illustrate the point in the design space toward which CAM tends to gravitate.

We should mention, as a counterpoint, the STARAN (Batcher[74]), which was designed to implement CAM ideas. STARAN consisted of a number of 256-word arrays of 256-bit words. Today a STARAN array could be put on a single chip, but there would still be the bus to contend with. Perhaps predictably, the major thrust in CAM-like architectures in the interim has been along the processor-array lines.

#### Criteria

Given these facts, it behooves the architect of a CAM-based system to develop a very strong theory of why the CAM paradigm has failed to produce a cost-effective general-purpose architecture. Here is the theory:

- o Density: The basic CAM algorithms are based on the assumption that all of the memory in the system is CAM. No implementation to date has come near this. CAM has been a scarce commodity, backed up by RAM, and data is swapped in and out of CAM to be processed. This is deadly, since CAM at best transforms a linear search or other simple loop to a constant-time operation; swapping the data in or out re-introduces the linear time.

- o Scalability: For physical practicality, CAM chips must have constant pinout, independent of the number of words per chip. The size of ordinary RAM is an extraordinarily scalable feature of the von Neumann architecture, varying by more than six orders of magnitude over the range of different systems. If CAM is not also scalable in this very strict sense, it will fail to substitute for RAM.

- o Datapath width: In choosing a one-bit processor, a CAM implementation gains faster

arithmetic but loses content addressability. If comparisons are bit serial, CAM is slower than conventional indexing structures such as binary trees and hash tables. To be usable as CAM, a memory must be able to compare, add, and subtract in a time comparable to a normal memory access.

o Coupling: The overwhelming tendency in designing a SIMD processor array is to place it as an attached processor to some conventional machine which manages the data not being used in the current parallel computation. This is unworkable; the bottleneck means that unless there are large speedups to be gained from operations on relatively long-lived data, the serial host processor can perform most simple associative operations faster than the CAM, when the time to transfer the data to and from the attached processor is taken into account.

## Density

Perhaps the most important criterion is density. The CAM must be usable as memory. If this is met, the basic CAM algorithms can be brought into play. Associative retrieval allows arrays of simple, explicitly-indexed records to be used instead of trees, linked lists, hash tables, priority queues, and inverted indices; what is more, it saves the software designer from having to make choices, with their associated tradeoffs, between these structures. (See Hall[81], Potter[88].)

It would be extremely inefficient to use a "true" parallel processor for search operations. The algorithmic speedup is at best  $\log N$ , so its efficiency is  $\frac{\log N}{N}$ , e.g. 0.002% in the case of a million-word CAM. Luckily, as distinct from "pure" CAM, the parallel processing CAM model produces significantly better speedups for other operations. If a million-word CAM has the same hardware cost as a fully-connected parallel processor with a thousand nodes, the CAM need only achieve an average 0.1% speedup to equal, in operations per cycle, the true parallel processor with perfect 100% linear speedup. (Caveat: A whole-chip processor will almost certainly have faster cycles than a CAM.)

Even so, we would like to keep the CAM to within some small constant factor of RAM cost. While a somewhat speculative analysis indicates that CAM might be rated as having a processing power proportional to the square root of the number of words, it remains the case that in order to do so it must act as the system's primary memory. Thus, its cost must remain low independent of the processing power it provides. This can be accomplished by starting with a high-density DRAM design and only allowing some constant fraction of the chip to be used for the active elements that implement the CAM model.

# Scalability

The only interconnection schemes that meet the strict scalability criterion are a bus, a linear array (daisy chain), and a tree. We find that a bus is desireable to distribute instructions to the words; a tree is essential for implementing the collective functions the CAM computational model requires; and a long shift register is probably the best way to implement an asynchronous I/O capability that does not seriously interfere with other operations.

#### Width

Consider the following design task: you have 1024 full adders and desire to build a machine to compute 1024 evenly spaced points of a linear function y = mx + b in 32-bit fields. You can add whatever control, memory, and communications you like. There are three strategies:

o First, you could make a serial processor using all the hardware to form a circuit that could multiply in one cycle. Then loop computing mx + b at each iteration, taking 2048 cycles. This can be improved by a strength reduction optimization, starting with b and adding m at each iteration, for a total of only 1024 cycles.

o Second, use 1024 1-bit ALUs to compute the result directly, multiplying in each processor mi (where i is the processor number stored as a constant) and adding b, taking 1024+32=1056 cycles. This is better than the naive serial algorithm but comparable to the optimized one.

o Third, one can form 32 32-bit ALUs and take advantage of parallelism and strength reduction: in a 32-cycle multiply (and a 1-cycle add), form the number 32im + b at each processor (where 32i has been stored as a constant) and use that as a starting point for adding m for the next 31 points. This gives you a total of 64 cycles.

This example is illustrative of a class of algorithms, which we call semi-serial algorithms, for which ALUs of a width commensurate with the data of interest and capable of simple arithmetic and comparison, but not more, form a local optimum in hardware efficiency. Note that for large problems using a fixed algorithm, the three designs above are equivalent: each can do 1024 multiplies in 1024 cycles.

# Coupling

Having attained memory-like density in the CAM, we can use it to advantage by the simple expedient of replacing all the system's RAM with CAM. (An alternative approach would be to use a Harvard-like architecture with RAM for instruction memory and CAM for data memory.) It is a long-established trend for processors to be faster than memory and to run asynchronously. In practice, this may mean that special processors are not necessary for CAM-based systems (although it is certainly possible to design them).

In a RAM, where only one word is being accessed at a time, clock skew across the memory is not a serious problem. In a CAM, it might be. If the connectivity is a tree, outgoing information, i.e. from the CPU to the CAM may arrive at the memory in a skewed fashion harmlessly, since no leaf depends on information from any other leaf. However, ingoing information may need to be synchronized. If the ingoing datapaths are combinational, synchronization consists only of waiting the longest number of gate delays from CAM to CPU. If the delay is consistent, this is not only simpler but faster than any other method.

#### Other Features

To be effective as CAM, a system must not only avoid these pitfalls but be designed with a cognizance of typical CAM algorithms in order to make most efficient use of its

hardware. The following is a list of features we have found to confer substantial algorithmic advantages, while remaining implementable within the constraints above:

- o Collective functions: The CAM model is virtually useless without a fairly powerful feedback mechanism from the memory to the processor. After an associative search, the processor may need to know how many (if any) matches were found. In the classical CAM model, operations such as summing all active words, finding the maximum or minimum of a set of values, and the like can be done as word-parallel bit-serial algorithms. These operations are crucial parts of the basic CAM computational model.

- o Segmentation: The CAM model has the capability of doing in parallel essentially a simple loop, dealing only with local and global values at each point. The ability to segment the CAM, still doing the same operation everywhere but having a different "global" value in each segment, corresponds to doing nested loops, and extends the range of parallel operations significantly:

- o Local addressing: The fields of the CAM words which are going to be operated on by an instruction are, in the basic model, the same for each word. The ability to vary the field choice on the basis of local data allows the CAM to do things like regular expression matching or unification in parallel, a prerequisite to the extension of the ideas of content addressability into higher-level models of computation.

## The Rutgers CAM

At this point we shift terminological gears; the specifics of the model are enough more complex that the concept of a "word" splits into two separate terms: a "cell" is the locus of one active element and the unit of activity control; the term "word" hereinafter will mean an addressable unit of simple memory whose width is that of the bus and other datapaths. There are many words per cell.

The design criteria elucidated in the preceding sections interact strongly with particular states of technology to determine the viability of a CAM implementation. As a point of departure, let us assign values to the constants as follows: Word width, 32 bits; density, 1K words per ALU. With these parameters we can devote at least half the silicon to DRAM; the density of the CAM as memory will be at least half that of conventional memory in the same technology.

A decade ago, the dominant memory technology was 64 K-bit DRAMs. The above constraints would specify a 32 K-bit chip, with one ALU occupying half the space and 1K 32-bit words on the other half, for a total of one cam cell per chip. A one-megabyte memory (typical for mainframes of the day) would have consisted of 256 chips (and therefore 256 cam cells). Assuming the CAM could be driven at 5MHz and do one operation every 5 cycles, the CAM would have represented a 256 mega-ops peak processing rate.

For the mid-90's we can use a 64-Meg DRAM as a basis and obtain 1K cam cells per chip. (Each cell is still an ALU and 1K 32-bit words; the memory still occupies half the chip.) 16 chips would provide 64 megabytes of memory and, assuming a 10-MHz operations rate (from a 50-MHz system clock), a peak 160 giga-ops. This is a single-board computer.

We have developed a "CAM virtual machine" as a common focus for architectural and algorithmic efforts. This model of the CAM reflects the capabilities of active elements

which fit the tradeoffs above, i.e. all the circuitry associated with one CAM cell must be roughly the size of 1K words of DRAM.

The CAM model is related to Blelloch's [87] "scan model of computation", but differs in the fundamental regard that the CAM model does not have a general permutation operator and thus is *not* a complete model for parallel computation. It does include:

- o Activity control: all the following can be controlled on a per-cell per-instruction basis. This forms the major difference between CAM and simple vector styles of computation.

- o Parallel vector operations to include addition, subtraction, comparison, bitwise boolean functions, and some shifting and byte extraction. These operations can only be done between words of the same cell, but they need not be the same words in each cell. It does not include multiplication, division, or floating point, although these can be done in software.

- o Broadcast: one of the operands in the above operations can be a "global" constant value (the same in each cell).

- o Collective functions: scalar-valued collective functions include the sum, max, and min of all the elements of a vector; vector-valued collective functions are parallel prefix (and suffix) forms of the scalar ones; and skip-shifting. This last moves a value from each active cell to the next active cell, no matter how far away, as a unit-time primitive.

- Segmentation: All of the collective functions and broadcasting can be done in segments, which, like the activity, are defineable on the fly. Each segment can have a different "global" value which comes from some cell in the segment.

- o Simple one-cell-at-a-time shifting which ignores activity and segment definitions can be done concurrently with other CAM operations; such shifting requires time proportional to distance shifted.

The physical implementation of the CAM model is, as indicated, by way of a set of active elements along with DRAM. Each chip, regardless of the amount of CAM onboard, has 4 busses (making it more like a processor chip in its packaging). These are one bidirectional data bus, one input-only instruction bus, and two I/O busses, one in and one out. 64 pins dedicated to I/O sound extravagant, but in the system as a whole, they are the most heavily used part. Furthermore, this interface is constant; CAM is a scalable architecture in the strongest sense of the word.

- o Each CAM cell consists of an ALU with 16 registers, and 1K (or more) DRAM. The ALU, register, memory, and all datapaths are 32 bits wide. The first 4 registers are mapped into the tree, the memory, the shifter, and the collection of one-bit registers that are the status, activity, segment, and so forth; the rest of the registers are general purpose. Each cell is like a very simple RISC with register-to-register operations and asynchronous load/store.

- The cells form the leaves of a tree of simpler ALU's, each of which has one register. The tree is combinational: that is, each CAM cell presents it with a 32-bit value and two control bits, activity and segment. The tree forms a direct-wired circuit that produces the appropriate value at the root and into each tree node's latch. This allows for virtually any possible clock skew between CAM cells-of course, we pay for this by having tree operations take 5 to 10 times as long as local CAM operations.

In a scan or shift operation, the tree actually does two operations, one up and one

down. Each phase is combinational internally.

- o A (unidirectional) instruction bus, emanating from the CPU, which controls the cells and the tree nodes. Depending on chip size and process parameters, the bus may be pipelined: the bus is optimized for throughput, in contrast to the tree, which is optimized for latency.

- o A shift register for overlapped I/O and data motion between CAM cells. Like the tree and the DRAM, the shift register operates asynchronously from the CAM cell. CAM efficiency is very dependent on its ability to move data. If a loader (see below) can relocate a program in, say, 1000 cycles but then requires a million cycles to move it from CAM to instruction RAM, the CAM is worthless. This is one of the reasons that our architecture has 1K or more words in each cell loading and unloading of one problem's data while another problem is being worked on is crucial to CAM's efficiency. Indeed our design calls for a separate datapath for this function. This can be something as simple as a (32-bit wide) shift register with one position for each cam cell. It doesn't even have to be true DMA: in our mid-90's model, for example, the I/O shift register would clock data for 1024 cycles before needing one memory cycle to store it.

#### CAM Algorithms

We present the following algorithms, in a very high-level form, to give a feeling for both the abilities and the limitations of the CAM.

Consider a very commonly used program, the relocating linking loader. Its initial task, finding the appropriate place in memory to put each of a given set of modules, can be as simple as a single parallel prefix sum. Updating the relative addresses at each point of the code to absolute addresses for execution is a local operation in each cell. Resolving global references, however, depends on the number of distinct symbols referenced (not the total number of occurences). This dominates the rest of the process, which is constant time.

For the next algorithm, we will assume that we have a "small" CAM, on the order of 1000 cells; it is intended to be representative of a simulation and visualization task on a machine at the scale of a workstation. We wish to simulate a number of bouncing particles in some three-dimensional space (at the appropriate scale, molecules in a gas) and display the results on a screen in real time. We will assume that there are enough CAM cells to allocate one per particle, and (separately, not in addition) one per pixel for one scan line.

- 1. [Advance the particles]  $X_{new} = X_{old} + V\Delta T$  for each particle. A purely parallel, local operation.

- 2. [Find collisions] Naively, this is an  $O(N^2)$  sequential time operation, but if the number of particles is large enough, a sophisticated implementation would use spatially-oriented indexing schemes to reduce the complexity to  $N \log N$  (e.g. octrees). CAM gives us linear time with the naive algorithm, and for the parameters given, that is sufficient. (For larger problems, similar indexing schemes could allow enough extra use of parallelism to reduce the CAM time to  $N^{\frac{2}{3}}$ ).

- 3. [Simulate collisions] Once the data for each collision has been brought together, the

new velocities for each particle can be computed in a single parallel step.

4. [Display] For each scan line, perform the following steps:

5. [Select objects] Associatively search for each object whose image intersects the current scan line. For each object from farthest to nearest, do step 6:

6. [Draw] Set the value of each pixel the current object intersects on the current scan line. This step could be split into a sequential and a parallel part like steps 2 and 3 if the rendering algorithm is complex enough to warrant it.

This algorithm exemplifies the cases where conventional worst-case asymptotic complexity analysis is inadequate. Constant factors deriving from the necessity of using sophisticated indexing data structures prevent a real-time implementation on a sequential machine at the same range of clock speeds as a CAM.

CAM also has operations with high constant factors, notably numerical calculations. In many cases, fairly simple algorithmic techniques can move these operations out of loops

and do them in parallel.

The final algorithm is intended to demonstrate what could be done with a "large" CAM, on the order of a million cells. (This would represent 4 gigabytes of RAM.) This time the task is a low-level part of an image-understanding process, namely to divide a picture up into regions. (E.g., suppose we had a black and white picture of a collection of polka-dots. We would want to associate with each white pixel a region number of 0, meaning that all the background was a single connected region, and with each black pixel a region number indicating which polka-dot it was in.)

1. [Process scan lines] Assuming the picture is in row-major form, use segmentation to do each scan line in parallel. Do short-distance shifts to localize horizontal neighbor information, and create a vector with a 1 for each edge, 0 elsewhere. Do a plus-scan of this vector; the result is a unique region number within each scan line, with each

pixel in the region having a copy of the number.

2. [Process one vertical line] For some vertical line, select (with activity control) only those pixels in that line. Perform step 1. for that line (using skip-shifting, etc.). Returning to line-by-line segmentation, combine vertical and horizontal region numbers into a global region number. This finds all pixels co-regional in horizontally contiguous segments touching the chosen vertical line.

3. [Other vertical lines] Which and how many vertical lines need to be processed is a matter of heuristic. This is considerably assisted by associative search, which can be used to skip vertical lines all of whose horizontal segments have been processed by the action of other vertical lines. A bisection method works well. In the best case the number of vertical lines needed will be on the order of the square root of the number of regions. In the worst case it may be the width of the picture, i.e. having to do every vertical line.

If the CAM were, e.g., a mesh-of-trees instead of simply a tree, we could run step 1 vertically as well as horizontally and be done in two steps. Pecial-purpose architectures

<sup>&</sup>lt;sup>1</sup> Actually, a rigorous definition of the algorithmic task can make it arbitrarily complex for either architecture, involving long chains of region coalescence fixups. However, as a basis for a low-level input-processing step for vision, identification of relatively simple regions seems adequate.

for vision invariably have such 2-dimensional connectivity. We consider this algorithm to show that the CAM handles this problem as well as a general-purpose machine might be expected to. Even when heuristics fail, its performance degrades only to  $\sqrt{N}$ .

# Evaluating the Processing Power of CAM

We must stress that it is virtually meaningless to compare the peak ops rate in CAM to serial MIPS. The relationship is extremely problem-dependent, and within a given algorithm, data-dependent, as is clearly shown in the preceding algorithms.

Even more important, perhaps, is that CAM cannot be validly compared with typical parallel processors, with their general interprocessor communications ability. The mid-90's technology estimates above provide a 1K-cell CAM on a chip with roughly 128 data pins. These pins would only provide 1-bit-wide datapaths if a mesh architecture were used (i.e. the perimeter of a 32x32 square); a hypercube architecture would be completely impractical.

A more valid basis for comparing CAM to other architectures is perhaps by pin count. In this scheme one CAM chip might be considered equivalent to a processor chip or 8 DRAM chips. Thus it could be appropriate to compare the processing power of a million-cell CAM to a thousand-processor conventional machine, since they would represent about the same amount of hardware.

But ultimately CAM shouldn't be compared to conventional parallel machines built as networks of microprocessors, because the architectures are orthogonal. Each processor of such a conventional parallel machine could be provided with CAM instead of RAM. Such an arrangement combines the best advantages of each part, synergistically. However, it is beyond the scope of this paper.

# Summary and Conclusion

Content Addressable Memory is memory. Our criteria of density, scalability, width, and coupling mark the boundary between a powerful memory and an anemic parallel processor. Within these limits, CAM can be a very cost-effective system component if average effective utilization is near even one percent.

CAM algorithms can be both simpler and faster than conventional ones; with more ingenuity, substantially better utilization can be achieved. The Rutgers CAM design provides collective functions and segmentation, allowing fairly sophisticated parallel algorithms in an architecture which still retains half the density of DRAM in a given technology.

# · Acknowlegements

The authors wish gratefully to acknowlege the substantial contributions of the Rutgers CAM Project staff, Keith Miyake and Sizheng Wei.

#### References

- [AMD88] Advanced Micro Devices, Inc: AM99C10 Content Addressable Memory data sheets, AMD, Sunnyvale, CA, 1988

- [Bat74] Batcher, K. E., STARAN Parallel Processor System Hardware, Nat. Comp. Conf 1974, pp 405-410.

- [Bla87] Blair, Gerard M.: "A Content Addressable Memory with a Fault-Tolerance Mechanism", IEEE JSSC, vol SC-22, no. 4, pp 614-616, Aug 1987

- [Ble87] Blelloch, Guy: "Scans as Primitive Parallel Operations", pp 355-362, Proceedings of the 15th International Conference on Parallel Processing, Pennsylvania State University Press, University Park, 1987

- [Fal62] Falkoff, A. D.: Algorithms for Parallel-Search Memories JACM 9 #10, Oct 1962, pp 488-511.

- [Fos76] Foster, Caxton C.: Content Addressable Parallel Processors, Van Nostrand Reinhold, New York, 1976

- [Fou87] Fountain, Terry: Processor Arrays: Architecture and Applications, Academic Press, London, 1987

- [Hal81] Hall, J. S.: A general-Purpose CAM-based System, in VLSI Systems and Computations, Kung, Sproull, and Steele, ed. pp 379-388, Computer Science Press, Rockville, MD, 1981

- [Hal89] Hall, J.S., S. Levy: von Neumannizing the Multi-Search Content Addressable Memory in Proceedings of the Symposium on Massively Parallel Processing, pp 27-42, University of South Carolina, Columbia SC 1989

- [Hil85] Hillis, W. Daniel: The Connection Machine, MIT Press, Cambridge, 1985

- [Sch87] Ilgen, Sener and Isaac D. Scherson: "Parallel Processing on VLSI Associative Memory", pp 50-53, Proceedings of the 15th International Conference on Parallel Processing, Pennsylvania State University Press, University Park, 1987

- [Koo70] Koo, J. T.: "Integrated Circuit CAM", pp 208-215, IEEE J. Solid State Circuits, SC5, 1970

- [Koh80] Kohonen, Teuvo: Content-Addressable Memories, Springer-Verlag, Berlin, 1980

- [Lan76] Lange, R G: "High Level Language for Associative and Parallel Computation with Staran", Proceedings of the 1976 International Conference on Parallel Processing

- [Pot85] Potter, J. L. ed: The Massively Parallel Processor, MIT Press, Cambridge, 1985

- [Pot88] Potter, Jerry L.: Data Structures for Associative Supercomputers, pp 77-84, Proceedings of the Frontiers of Massively Parallel Computation, 1988, IEEE Computer Society Press, order number 892

- [Sch88] Scherson, Isaac and Smil Ruhman: "Multi-operand Arithmetic in a Partitioned Associative Architecture", Journal of Parallel and Distributed Computing 5, (1988) pp 655-668.

- [Sto86] Stolfo, Salvatore J. and Daniel P. Miranker: "DADO: A Tree-Structured Architecture for Artificial Intelligence Computation", pp 1-18, Annual Review of Computer Science, Annual Reviews, Palo Alto, 1986

# DESIGN OF A LEAF CELL FOR THE RUTGER'S CAM ARCHITECTURE\*

Donald E. Smith, Keith M. Miyake, and J. Storrs Hall

LCSR-TR-180

Laboratory for Computer Science Research Hill Center for the Mathematical Science Busch Campus, Rutgers University New Brunswick, New Jersey 08903

# 1 Hardware Design

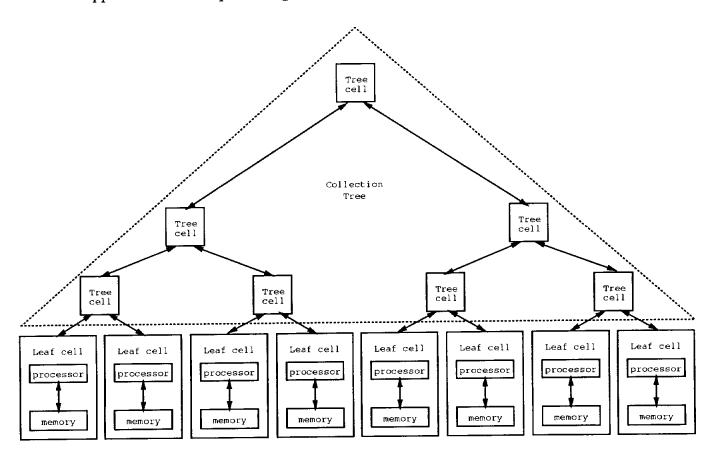

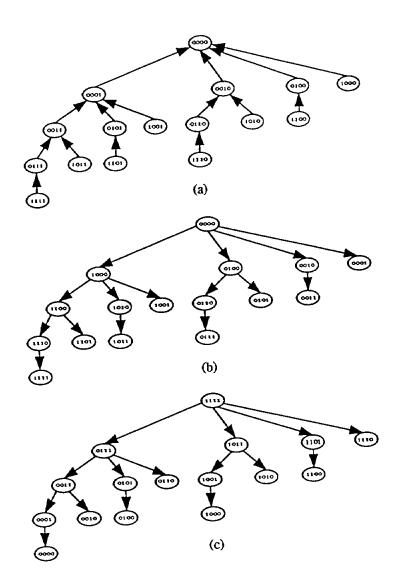

Our Mar91-Aug91 progress report described the Rutger's CAM architecture as a collection tree sitting over a set of LEAF cells each with its own memory. Figure 1 shows this architecture and identifies the two cell types used in its implementation: LEAF cells that are composed of a processor and associated memory, and TREE cells that constitute the Collection Tree. These two cell types serve complementary functions within the architecture: TREE cells provide global processing for data collection, data movement, and parallel pre-fix(scan) operations over the LEAF cells while LEAF cells implement CAM-like operations and support local SIMD processing.

Figure 1: Collection Tree sitting over a set of LEAF Cells

A Register Transfer Level (RTL) description of the tree cell has been completed and tested. It supports both right-to-left and left-to-right integer scan operations, activity controlled and segmented operations, extended integer precision, as well as all tree operations described in our Mar91-Aug91 progress report.

The LEAF cell specification is nearly complete and the first draft of an RTL design is nearing completion. In the next six months, we expect to complete the LEAF cell design, interface it with our TREE cell design, and test these using the shortest path algorithm described in our Sep90-Feb91 progress report.

# 1.1 LEAF Cell Specification

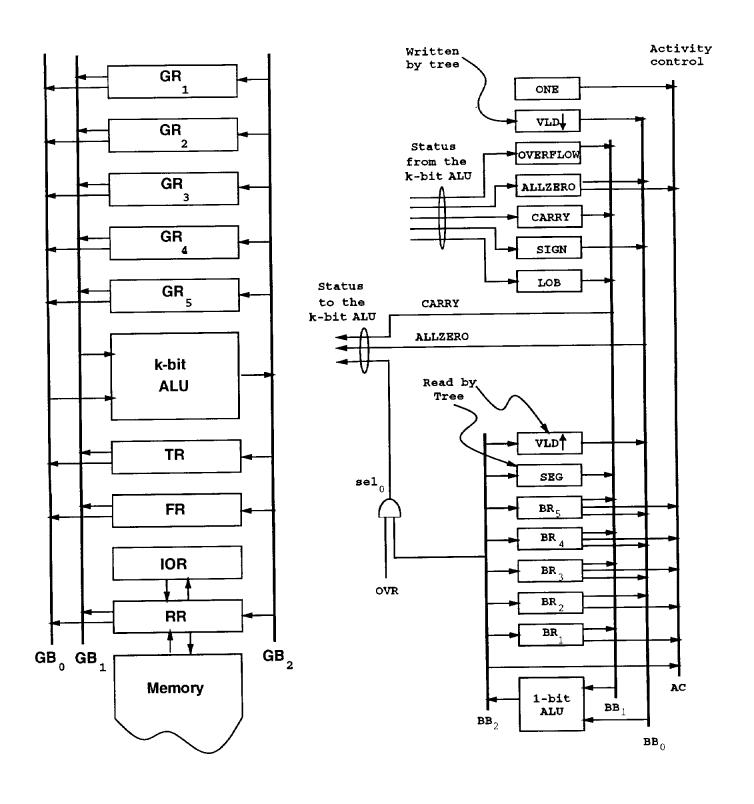

Each LEAF cell is responsible for performing CAM-like operations and is composed of a main processor connected to three support processors via multi-ported interface registers. These support processors are the tree processor, memory processor, and IO processor (not shown in Figure 1). The LEAF cell's main processor is composed of two communicating components; a k-bit processor for standard operations and a 1-bit processor used to control activity within a LEAF cell. Figure 2 shows the interconnection of these components.

# 1.2 Component Descriptions

The k-bit processor is a three bus (i.e., GB<sub>0</sub>, GB<sub>1</sub>, GB<sub>2</sub>) architecture composed of:

- a k-bit ALU

- five general purpose k-bit registers GR<sub>1</sub>, GR<sub>2</sub>, GR<sub>3</sub>, GR<sub>4</sub>, and GR<sub>5</sub>

- a dual ported k-bit flag register(FR) directly coupled to the fourteen 1-bit registers

- a dual ported (k+1)-bit tree register(TR) that provides the interface between leaf and tree processor

- a tri-ported k-bit refresh register register (RR) that provides the interface between the leaf, memory, and IO processors.

- a dual ported IO register(IOR) that provides the interface between the IO processor and the refresh register (RR).

The 1-bit processor is a four bus (i.e., BB<sub>0</sub>, BB<sub>1</sub>, BB<sub>2</sub>, AC) architecture composed of:

- a 1-bit ALU

- five general purpose 1-bit registers BR<sub>1</sub>, BR<sub>2</sub>, BR<sub>3</sub>, BR<sub>4</sub>, and BR<sub>5</sub>

- a dual ported 1-bit segment register(SEG), read by the tree processor, that indicates if a leaf processor is (SEG=1) or is not (SEG=0) the first element in a new segment.

- a dual ported 1-bit status register(VLD $\uparrow$ ), read by the tree processor, that indicates if the tree processor should use (VLD $\uparrow$ =1) or ignore (VLD $\uparrow$ =0) the data in the tree register.

- five 1-bit status registers (OVERFLOW, ALLZERO, CARRY, SIGN, LOB) that contain the status of the k-bit ALU

<sup>&</sup>lt;sup>1</sup>We expect the k-bit processor and its associated registers to be 32-bits wide; however, our design is not restricted to 32-bit widths but parameterized as a function of word width.

Figure 2: LEAF cell architecture

- a dual ported 1-bit status register(VLD $\downarrow$ ), written by the tree processor, that indicates if the leaf processor should use (VLD $\downarrow$ =1) or ignore (VLD $\downarrow$ =0) the data in the tree register

- a 1-bit constant (ONE) used to activate LEAF cells

# 1.3 Interfaces between the 1-bit and k-bit components

The 1-bit and k-bit components communicate through the processor status registers (i.e., the five 1-bit registers that maintain the status of the k-bit processor), through activity control, and through dedicated connections joining the fourteen 1-bit registers and the low-order 14 bits of k-bit register FR.

Activity control is determined by the value carried on AC in the 1-bit processor and is used to enable or disable the writing of both 1-bit and k-bit registers from their respective output buses (i.e., GB<sub>2</sub> and BB<sub>2</sub>). The value placed on AC can be obtained from the output of the 1-bit ALU (BB<sub>2</sub>) or from one of the 1-bit registers BR<sub>1</sub>, BR<sub>2</sub>, BR<sub>3</sub>, BR<sub>4</sub>, BR<sub>5</sub>, ALLZERO, or ONE.

The dedicated connections between the 1-bit registers and the low-order 14 bits of FR provides an additional interface that increases the bandwidth between the 1-bit and k-bit components. These connections are used by the following operations.

- copy all 1-bit registers into FR<sub>0</sub> through FR<sub>13</sub>

- copy FR[0:4] into BR<sub>1</sub> through BR<sub>5</sub>

- copy FR<sub>5</sub> and FR<sub>6</sub> into SEG and VLD↑, respectively

## 1.4 Instruction Fields

Operation of the LEAF cells is specified by the fields summarized in Figure 3. The estimated width of each field is shown in parentheses. These specifications are tentative; refinements to field size and instructions will be made as algorithms are implemented on this architecture.

#### GOP

GOP encodes the operation to be performed by the k-bit ALU. The exact set of operations has not been determined but includes AND, OR, XOR, addition, and subtraction as well as sel-arg<sub>1</sub>, sel-arg<sub>2</sub>. These last two instructions select the indicated input argument and route it to the output.

#### $R_{GB_0}$ and $R_{GB_1}$

R<sub>GB<sub>0</sub></sub> and R<sub>GB<sub>1</sub></sub> encode the refresh register, one of the k-bit general registers, the tree register, or the flag register. Our initial design using 5 general registers is encoded as follows:

GOP(4): encoded operation to be performed by the k-bit ALU

R<sub>GB<sub>0</sub></sub>(3): encoded designation of the source register driving bus GB<sub>0</sub>

R<sub>GB1</sub>(3): encoded designation of the source register driving bus GB<sub>1</sub>

R<sub>GB2</sub>(3): encoded designation of the destination register reading bus GB<sub>2</sub>

RRC(2): refresh register control

ADDR(lg(n)): memory address

WR(1): memory processor write control

IOC(1): IO register control

OVR(1): Enable/disable control of k-bit ALU's override capability

BOP(4): encoded operation to be performed by the 1-bit ALU

R<sub>BB<sub>0</sub></sub>(3): encoded designation of the source register driving bus BB<sub>0</sub>

R<sub>BB1</sub>(3): encoded designation of the source register driving bus BB<sub>1</sub>

R<sub>BB2</sub>(3): encoded designation of the destination register reading bus BB<sub>2</sub>

R<sub>AC</sub>(3): encoded designation of the source driving the activity control line AC

Figure 3: Instruction Fields

$000: RR \quad 001: GR_1 \quad 010: GR_2 \quad 011: GR_3 \quad 100: GR_4 \quad 101: GR_5 \quad 110: TR \quad 111: FR$

$\mathbf{R}_{\mathbf{GB_2}}$

$R_{GB_2}$  encodes a null destination( $\lambda$ ), one of the k-bit general registers, the tree register, or the flag register. The encoded designation determines the register that will record the value on  $GB_2$ . The value is recorded if and only if the LEAF processor's activity control, as determined by AC, is set. This field cannot specify the refresh register. Our 5 register design is encoded as:

$000:\lambda = 001:GR_1 = 010:GR_2 = 011:GR_3 = 100:GR_4 = 101:GR_5 = 110:TR = 111:FR$

#### **RRC**

RRC is a 2 bit field that specifies what data, if any, is written to the refresh register. The field encodes one of four possibilities: a  $noop(\lambda)$ , write from  $GB_2$ , write from memory, or write from IOR. Specifying this field independent of the  $R_{GB_2}$  field allows the refresh register to be written in parallel with any of the destinations specified by  $R_{GB_2}$ . It also isolates the leaf processor from the memory and IO processors allowing each to run at its own optimal speed. Activity control is used when RR is being written from  $GB_2$  - it is ignored for all other cases. Our current design encodes RRC as follows:

00:  $\lambda$  01: RR  $\leftarrow$  GB<sub>2</sub> 10: RR  $\leftarrow$  M[ADDR] 11: RR  $\leftarrow$  IOR

#### ADDR

ADDR is a lg(n) bit field, where n is the number of words of memory, that specifies the memory location to be read from or written to. This field is required only when a read or write is being performed.

#### WR

WR is a 1-bit field that indicates when data is to be written from the refresh register to the memory  $(M[ADDR] \leftarrow RR)$ . This operation can be performed in parallel with other operations that access the refresh register.

#### IOC

IOC is a 1-bit field that specifies when data is written from the refresh register to the IO register (IOR  $\leftarrow$  RR).

#### OVR

OVR is a 1-bit field that enable or disables the override capability of the k-bit ALU. When enabled the k-bit ALU will perform either the operation specified by field GOP or override that specification and transfer data from input bus GB<sub>0</sub> to output bus GB<sub>2</sub>. The override capability is used for computing inclusive scans from exclusive scans as well as providing MUX-like capabilities to the k-bit ALU (see section 1.6).

#### BOP

BOP encodes the operation to be performed by the 1-bit ALU. The bits are the entries in the truth table of the boolean function being computed.

$R_{BB_0}$ ,  $R_{BB_1}$ , and  $R_{AC}$

$R_{BB_0}$ ,  $R_{BB_1}$ , and  $R_{AC}$  each encode 8 registers (not the same registers). These encodings are based on the interrelations between the 1-bit registers and a typical instruction mix. The specific registers connected to each bus and their encodings will be altered as experience is gained with algorithms on this architecture. The following are design goals which influence these choices as well as an initial assignment of registers to busses.

- Extended precision requires that the CARRY and ALLZERO status outputs from the k-bit processor be fed back into the processor's CARRY and ALLZERO inputs. Consequently, data paths that allow parallel routing of the CARRY and ALLZERO registers to the k-bit processor must be supported.

- Inclusive scans are completed in the LEAF processors using the results of the exclusive scan produced by the tree and two additional steps<sup>2</sup> performed by the LEAF processor. These steps makes use of the 1-bit ALU as well as the override feature of the k-bit ALU and require that 1-bit registers VLD\$\dig \text{ and SEG}\$ be presented in parallel to the 1-bit ALU. Details of these operations are described in section 1.6.

- $R_{BB_0}$  encodes one of  $BR_2$ ,  $BR_3$ ,  $BR_4$ ,  $BR_5$ ,  $VLD\uparrow$ , SIGN, ALLZERO, and  $VLD\downarrow$

- $\bullet \ \ field \ R_{BB_1} \ encodes \ one \ of \ BR_1, \ BR_3, \ BR_4, \ BR_5, \ SEG, \ LOB, \ CARRY, \ and \ OVERFLOW$

- The field R<sub>AC</sub> encodes one of BB<sub>2</sub>(i.e., the output bus of the 1-bit ALU) BR<sub>1</sub>, BR<sub>2</sub>, BR<sub>3</sub>, BR<sub>4</sub>, BR<sub>5</sub>, ALLZERO, and ONE

$R_{BB}$

R<sub>BB2</sub> encodes one of null(λ), BR<sub>1</sub>, BR<sub>2</sub>, BR<sub>3</sub>, BR<sub>4</sub>, BR<sub>5</sub>, SEG, VLD↑. This field determines the register that will record the value on BB<sub>2</sub>. This value is recorded if and only if the processor's activity control, as determined by AC, is set. Our initial design is encoded as:

$000:\lambda \quad 001:BR_1 \quad 010:BR_2 \quad 011:BR_3 \quad 100:BR_4 \quad 101:BR_5 \quad 110:SEG \quad 111:VLD\uparrow 110:BR_5$

# 1.5 Interaction between the LEAF and memory processors

The read and write commands form the conceptual interface between the LEAF processor and the memory processor. They are executed by the memory processor and cause data to be transferred between RR and the memory. These commands are encoded in two fields, RRC and WR. The read command is encoded in the RRC field as a command to move data from memory to the refresh register. This command causes the memory processor to

<sup>&</sup>lt;sup>2</sup>Plus scans only require one additional step.

transfer the data at the location specified by ADDR to the refresh register. If the read is destructive, as is the case with a DRAM implementation, the main control unit will issue a write command to rewrite the contents of RR back to memory.

The write command specified by WR indicates that data is to be written from RR to memory and must not conflict with RRC - the WR bit CANNOT specify write-to-memory when RRC specifies read-from-memory. These commands are not affected by the processor's activity control.

Once initiated by either a read or write the memory processor performs the data transfer asynchronously. The LEAF processor should not change RR while the memory processor is busy and is thus limited to using RR only when the memory processor is idle.

# 1.6 Interaction between TREE and LEAF processors

Most of the interactions between the TREE and LEAF processor are of the *standard* variety; however, there are two types of interactions that require special attention. One is the handling of overflow between these two processors. The other is the communication of scan results between the two processors.

These interactions are handled through the interface provided by TR, VLD\, SEG, and VLD\. TR acts as a bidirectional data port connecting the two processors. When the tree accepts data from the leaves it reads VLD\ and SEG. VLD\ indicates if the data in TR should, or should not, participate in the tree operation while SEG indicates if the leaf is, or is not, the first in a segment. These two 1-bit registers can be read and written by the 1-bit ALU; however, they may only be read by the tree.

When the tree provides data to the leaves it use VLD\$\psi\$ to indicates if the data in TR should, or should not, be used by the leaf. VLD\$\psi\$ can only be read by the LEAF processor and can only be written by the TREE processor. There is dedicated hardware in the tree that computes VLD\$\psi\$ as a function of the SEG, VLD\$\psi\$, and the direction of the scan (left-to-right or right-to-left). Changing any of these three fields will cause VLD\$\psi\$ to change.

#### 1.6.1 Overflow Interactions

Since the TREE and LEAF processors jointly participate in numerical computations, the LEAF processor must be responsive to overflow information generated by the TREE processor. This information is stored in a single bit in TR and must be used by the LEAF processor's k-bit ALU to determine its overflow condition. The overflow condition of a LEAF cell operation (even data movement such as  $GR_i \leftarrow TR$ ) that involves the tree register as a source must be dependent on the overflow condition generated in the tree. If TR indicates an overflow from the tree, the LEAF processor must complete the specified operation and set the overflow status to true. The overflow status must also be set if the LEAF processor performs an arithmetic operation that itself generates an overflow.

In the case when the tree is not supplying data to the leaf (i.e., VLD \( \) is 0), the overflow

field in TR is ignored.

#### 1.6.2 Inclusive and Exclusive Scans

When an inclusive scan is desired, the LEAF processor must compute it from the TREE cells exclusive scan and its own internal data.

These operation are performed using the override capability of the k-bit ALU which permits the ALU to either execute the operation specified or to ignore the operation and replace it with a data transfer. The data transfer routes the data on input bus GB<sub>0</sub> directly to output bus GB<sub>2</sub>. When an override is in effect the operation specified by GOP and the data on input bus GB<sub>1</sub> are ignored by the k-bit ALU.

Figure 4 shows a operation and its overridden counterpart. Notice that the data transfer that replaces the specified operations ignores the fields  $R_{GB_1}$  and GOP but uses the fields  $R_{GB_2}$  without alteration.

|                                     | Operation Mnemonic                                               | Operation field specification                                                                                                                  |

|-------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation<br>Overridden Counterpart | $GR_i \leftarrow (GR_j \text{ op } GR_k)$ $GR_i \leftarrow GR_j$ | $\begin{array}{c} {\rm R_{GB_0}\!=\!j,\ R_{GB_1}\!=\!GR_k,\ R_{GB_2}\!=\!i,\ GOP\!=\!op} \\ {\rm R_{GB_0}\!=\!j,\ R_{GB_2}\!=\!i} \end{array}$ |

Figure 4: Comparison of normal operation and it overridden counterpart

In order to produce inclusive scans from exclusive scans two cases must be considered. One, when the tree processor provides data on which the inclusive scan depends ( $VLD\downarrow=1 \land SEG=0$ ) and two, when it does not ( $VLD\downarrow=0 \lor SEG=1$ ). Notice that these conditions are functions not only of the results produced in the tree but also of the segmentation bit in the leaf processor. This latter dependence is due to the fact that the first leaf processor in a segment (SEG=1) must ignore the data it receives from the tree since this data is from a different segment. The LEAF processor must be able to distinguish between these cases and complete the inclusive scan appropriately. Figure 5 shows the operations required of the the LEAF processor for these two cases.

Tree data should be used  $GR_i \leftarrow (GR_j \text{ op } TR)$ Tree data should be ignored  $GR_i \leftarrow GR_j$

Figure 5: Leaf operations for forming inclusive scans from exclusive scans

Since the second of these operations is an overridden version of the first, the choice between the two operations can be performed by the override capability of the k-bit ALU by using the single instruction show in Figure 6.

Figure 6: Using OVR to form inclusive scans from exclusive scans

#### 1.6.3 Using the k-bit ALU as a Multiplexor for MIN and MAX scans

The OVR field can also be used to cause the k-bit ALU to function as a MUX routing one of its inputs, GB<sub>0</sub> or GB<sub>1</sub>, to GB<sub>2</sub>. This is accomplished by using OVR and the 1-bit ALU in conjunction with the k-bit operation sel-arg<sub>2</sub> as shown below. Notice that the sel-arg<sub>2</sub> routes the second argument to the output and that its overridden counterpart routes the first argument.

$$GR_i \leftarrow sel-arg_2(GR_j, GR_k)$$

where:  $sel-arg_2$  performs  $GR_i \leftarrow GR_k$

The ability to use the k-bit ALU as a MUX also provides support for forming inclusive scans from their exclusive counterparts. It is especially useful for MIN and MAX scans because these operations are performed differently in the TREE and LEAF cells<sup>3</sup>. In a TREE cell MIN and MAX are functions that output either the MIN or MAX of their inputs but in a LEAF cell, MIN and MAX are simulated by comparing two data and selecting one based on the result of the comparison. This difference requires that inclusive MIN and MAX scans use the two steps show in Figure 7 to convert an exclusive scan to an inclusive scan.

| $\overline{\mathrm{GR}_i \leftarrow \mathrm{MIN}(\mathrm{GR}_j, \mathrm{TR})}$ |                                                                          |                                                                                                                                                              |  |  |

|--------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| OVR                                                                            | k-bit operation                                                          | 1-bit operation                                                                                                                                              |  |  |

| off<br>on                                                                      | $\lambda \leftarrow (GR_j - TR)$ $GR_i \leftarrow (sel-arg_2(GR_j, TR))$ | $\begin{array}{c} \mathrm{BR_1} \leftarrow (\overline{\mathrm{VLD}} \vee \mathrm{SEG}) \\ \lambda \leftarrow (\mathrm{BR_1} \vee \mathrm{SIGN}) \end{array}$ |  |  |

Figure 7: LEAF cell steps to complete MIN/MAX inclusive scans

While the comparison  $(GR_j - TR)$  is taking place in the k-bit processor, the 1-bit processor decides if TR should be used to complete the scan - this result is stored in  $BR_1$ . In the second step the k-bit processor is used as a multiplexor selecting either  $GR_j$  or TR and routing it to  $GR_i$ . Since OVR is on, the specific selection is determined by the 1-bit ALU computation.  $GR_j$  is selected when either the tree data is not to be used or the contents of  $GR_i$  is less than TR.

<sup>&</sup>lt;sup>3</sup>Addition is performed identically in the LEAF and TREE cells.

#### 1.6.4 Inserting identity elements

TREE cells perform exclusive scans (i.e. the initial element in a segment is the identity element for the operation) but do not insert the identity element into the result. In order for the result to contain the identity element the LEAF processor must insert it.

This is accomplished using the MUX-like capabilities of the LEAF processor to choose between the data provided by the tree and the identity element for the operation. Figure 8 shows the constants that are expected to be of special interest. These five constants can be constructed from a 3-bit field in which one bit specifies the high order bit, one the low order bit, and one the internal bits.

|   | Constant |   | Use                                                   |

|---|----------|---|-------------------------------------------------------|

| 0 | 0000     | 0 | identity for +, OR, MAX on positive integers          |

| 1 | 1111     | 1 | identity for AND, MIN on positive integers; decrement |

| 1 | 0000     | 0 | identity for MAX on 2's complement                    |

| 0 | 1111     | 1 | identity for MIN on 2's complement                    |

| 0 | 0000     | 1 | increment                                             |

Figure 8: Important Constants

# 1.7 Activity control

Activity control is used on all k-bit and 1-bit registers. These registers latch their input values at the end of each execute cycle if and only if they are selected by  $R_{GB_2}$  or  $R_{BB_2}$  and AC is set. There is no activity controlled write-to-memory; however, the effect of this operation can be obtained by using the standard memory operations in conjunction with an activity controlled operation on RR. Figure 9 shows how this is accomplished.

| $M[ADDR] \leftarrow GR_i \text{ in al}$                              | ll active leaf nodes |

|----------------------------------------------------------------------|----------------------|

| $RR \leftarrow M[ADDR]$ $RR \leftarrow GR_i$ $M[ADDR] \leftarrow RR$ | mediated by AC       |

Figure 9: Activity Controlled write to memory

# CIRCUIT DESIGN TOOL USER'S MANUAL\*

# Keith M. Miyake and Donald E. Smith LCSR-TR-181

Laboratory for Computer Science Research Hill Center for the Mathematical Science Busch Campus, Rutgers University New Brunswick, New Jersey 08903

# Contents

| 1 | Intr | oduction                 | 1          |

|---|------|--------------------------|------------|

|   | 1.1  | Circuit Definition       | 2          |

|   | 1.2  | Model Creation           | 2          |

| 2 | The  | Definition Language      | 4          |

|   | 2.1  | Syntax Conventions       | 4          |

|   | 2.2  | Variables and Assignment | 5          |

|   | 2.3  | Expressions              | 6          |

|   | 2.4  | Naming Conventions       | 7          |

|   | 2.5  | Cable Definitions        | 9          |

|   | 2.6  | Module Definitions       | 11         |

| 3 | Cor  | nmand Syntax             | 19         |

|   | 3.1  | Filenames                | 19         |

|   | 3.2  | Current Generated Module | 19         |

|   | 3.3  | Current Submodule        | <b>2</b> 0 |

|   | 3.4  | Parent Constructor       | 20         |

|   | 3.5  | Command Naming           | 20         |

|   | 3.6  | Design Tool Commands     | 22         |

| 4 | Imp  | plementation Details     | 28         |

|   | 4.1  | Primitive Modules        | 28         |

|   | 4.2  | Simulation Construction  | 28         |

|   | 4 3  |                          | 29         |

|              | 4.4 Simulation Events      | 29 |

|--------------|----------------------------|----|

|              | 4.5 Simulation Runs        | 29 |

| 5            | Startup Options            | 31 |

|              | 5.1 Command-line Arguments | 31 |

|              | 5.2 simrc File             | 32 |

| A            | The Lexer                  | 34 |

| В            | Primitive Modules          | 37 |

| $\mathbf{C}$ | Module Examples            | 42 |

| D            | Error Messages             | 46 |

# Chapter 1

# Introduction

The design of the CAM chip has been done in a UNIX software environment using a design tool that supports the definition of digital electronic modules, the composition of these modules into higher level circuits, and event-driven simulation of these circuits. Our tool provides an interface whose goals include straightforward but flexible primitive module definition and circuit composition, efficient simulation, and a debugging environment that facilitates design verification and alteration.

The tool provides a set of primitive modules which can be composed into higher level circuits. Each module is a C-language subroutine that uses a set of interface protocols understood by the design tool. Primitives can be altered simply by recoding their C-code image; in addition new primitives can be added allowing higher level circuits to be described in C-code rather than as a composition of primitive modules - this feature can greatly enhance the speed of simulation<sup>1</sup>.

Effective composition of primitive modules into higher level circuits is essential to our design task. Not only are the standard features of a description language required but in addition, features such as recursive descriptions of circuit composition, parameterized module descriptions, and strongly-typed port types are essential to efficient circuit design. These features are supported by our design tool's composition language which allows the user to specify a hardware description in a C-like syntax. Parameterized modules, recursive and iterative descriptions, macro-like capability to describe collections of wires (i.e., cables), and decision making support that allows context sensitive module expansion are provided by our tool. In addition, our tool can determine the cost of a circuit based on the costs of its primitive modules. This feature is not exact but does provide a good approximation of the complexity of the designed circuit.

Simulation is performed by an event-driven simulator that handles gates as well as tristate bi-directional busses and provides the user not only with a view of what a circuit is computing but also control over the circuit so that design flaws can be effectively isolated

<sup>&</sup>lt;sup>1</sup>Converting a higher-level circuit into a primitive module is straightforward when the timing of the primitive module need not be identical to the higher level circuit. Higher level circuits can be converted to primitive modules with identical time performance; however, the conversion process is much more complex.

and corrected. The simulator is controlled with a command language which allows the user to see a wire or set of wires, as well as change the values on wires. Operations can be done immediately (i.e., at the time the user enters them) or scheduled to take place at a specified time. Simulations can be run for a specific period of time or until a certain condition is detected in the hardware. They can be controlled from the keyboard or indirectly from a file.

The design tool consists of two main parts: the command and definition languages. The definition language is used to read circuit definitions. The command language controls the actions of the simulator. These topics are detailed in sections 2.5 and 2.6.

Following is a brief introduction on the definition and creation of circuit models. It defines many terms used later.

# 1.1 Circuit Definition

The circuit definition language describes connections between primitive objects. These objects, called *primitive modules*, have functionality predefined in the design tool. Primitive modules have a special set of entry points which are connected when forming the circuit model. These entry points are called *ports* and the connections between them are referred to as *signals* or *wires*. There is a causality between connected modules. Execution of a module may affect modules connected to it.

The design tool reads descriptions using a definition language. The language consists of two types of object definitions: module and cable. Cable definitions group related signals together. Module definitions specify primitive modules and their connections. A module may define other modules as children of itself, and specify connections between its child modules. In this case the module is referred to as a composite module.

The circuit is built from a set of hierarchical module and cable definitions. Flattening the hierarchy produces the basic model of a set of primitive modules connected by wires.

In order to name objects in the hierarchical design, hierarchical names are used by the design tool. These names specify objects which cannot be directly referenced within the current context. This is done by supplying a list of names specifying a path to the object. Each field in the composite name is separated by the dot character '.'.

# 1.2 Model Creation

The creation of a circuit model is performed in phases.

When a cable or module definition is read, its syntax is checked and the definition is stored as a master definition. These definitions may have input arguments which need assignment.

When a module is created, input arguments to master definitions are assigned resulting in

a new definition type. These definitions, which have specific input arguments, are referred to as definition instances. Each definition instance is fully examined, checking the consistency of the connections made and the referenced modules.

The circuit model is made from these definition instances. The model is designed for speed in simulating the functionality of the circuit and contains all structures necessary for simulation. Such a model is called a generated module or simulation instance.

# Chapter 2

# The Definition Language

The definition language is used to describe digital electronic circuits by building hierarchical structures connecting primitive modules. A definition file consists of a sequence of module and cable definitions. Modules come in two types: primitive and composite.

Primitive modules are the basic building blocks of the definition language. These objects perform operations defined by C functions which have been precompiled into the design tool. A list of primitive modules is given in appendix B.

A composite module definition defines submodules of itself and connections to be made among their ports, as well as its own ports. Attaching submodule ports causes interactions between the operations of the respective modules.

Cable definitions allow signals to be identified in groups, which simplifies connection of ports.

Module and cable definitions are similar in structure and are analogous to functions in a conventional programming language. They may have formal input arguments and may use other definitions (as well as their own) recursively. Termination of such recursion is not assured.

# 2.1 Syntax Conventions

The language syntax descriptions used in this manual is a variant of the Backus-Naur form. Following is a list of syntax rules:

- 1. Boldface type denotes reserved words.

- 2. Lowercase words, which may have embedded underscores, denote syntactic constructs.

- 3. Character tokens are shown using typewriter type. Most punctuation characters are used as character tokens, with exceptions stated below. Note that the exceptions are printed in Roman type.

- 4. The vertical bar '|' separates alternate syntax items when it is used at the beginning of a line.

- 5. Square brackets ('[', ']') enclose optional items.

- 6. The dollar sign '\$' in a syntax rule denotes the remainder of the line as a comment. '\$' is not used in the syntax.

# 2.2 Variables and Assignment

A variable is a name associated with an integer value in a module or cable definition. Variables have no meaning outside the current definition. A variable name may be any valid string token (quoted or unquoted; see appendix A). There are no arrays of variables. A variable may have the same name as signals, modules, or cables since its context is distinct. There are three variable types: input, loop, and assignment. Within a specific definition, a variable may be used as only one type.

# Input Variables

Input variables are arguments to a module or cable definition. They are determined at invocation and may not be reassigned within the current object. These variables are valid throughout the current object. Each input variable of a definition must be given a value upon use.

# Loop Variables

Loop variables are used in for loops in the component section of modules. Each for loop controls the assignment of a single loop variable. Loop variables are only valid within the controlling loop, and may not be reassigned within the loop.

# Assignment Variables

Assignment variables are used in the component section of modules. They are set using the assign statement (string\_token <- arith\_expr;). This assigns the current value of the expression to the variable. Once a variable has been assigned to, it is valid until the end of the module. Each subsequent use of the variable gets the assignment value unless the variable has been reassigned. Assignment variables may not be reused as loop variables.

Control flow variations resulting from if statements or loops may allow an assignment variable to be referenced prior to assignment.

Cables only have input variables since they have no component section.

# 2.3 Expressions

Expressions are used in various ways to control the assembly of modules. There are two types of expressions: arithmetic and logical. Arithmetic expressions result in integer values. Logical expressions return one of the values TRUE or FALSE. Arithmetic and logical expressions are not interchangeable.

# **Arithmetic Expressions**

Arithmetic expressions compute integer values. They may be string tokens (variables), numeric tokens (constants), or may be created by application of an arithmetic operator to one or more arithmetic expressions.

```

arith_expr :=

$ variable value

string_token

$ constant value

| numeric_token

$ arithmetic negation

- arith_expr

$ arithmetic grouping

(arith_expr)

$ multiplication

arith_expr * arith_expr

$ division

arith_expr / arith_expr

$ modulus

arith_expr % arith_expr

$ addition

arith_expr + arith_expr

$ subtraction

arith_expr - arith_expr

```

Division operations return a truncated result (using C convention), since integer division is not exact.

There are three levels of arithmetic operator precedence. Unary operators (negation and grouping) share the highest precedence. Multiplication, division, and modulus (\*, /, %) have equal precedence, below that of the unary operators. Addition and subtraction (+, -) share the lowest precedence.

All binary arithmetic operators associate left-to-right.

# Logical Expressions

Logical expressions compute the value TRUE or FALSE. They are constructed by the use of relational or logical operators. Relational operators produce a logical expression based on the validity of a relational query between two arithmetic expressions. Logical operators use one or two logical expressions to produce a single logical expression. There are no logical variables or constants.

```

log\_expr :=

$ greater than

arith_expr > arith_expr

$ greater than or equal to

| arith_expr >= arith_expr

$ less than

arith_expr < arith_expr

$ less than or equal to

arith_expr <= arith_expr

arith_expr = arith_expr

$ equal to

arith_expr ! arith_expr

$ not equal to

$ logical negation

~ log_expr

{ log_expr }

$ logical grouping

$ logical AND

log_expr & log_expr

$ logical OR

| log_expr | log_expr

```

Note that the vertical bar in the logical OR represents the character '|'.

The use of arithmetic expressions as operands eliminates precedence or associativity with regard to relational operators.

There are three levels of logical operator precedence. Unary logical operators (negation and grouping) have the highest precedence, followed by logical AND. Logical OR has the lowest precedence of logical operators.

Logical grouping syntax is distinct from that of arithmetic grouping. This reinforces the idea of noncompatibility between expression types.

## 2.4 Naming Conventions

Each child object (signal, cable, or submodule) in a definition must be given a unique name. This allows unambiguous signal naming within simulation instances (for design verification). Names of child objects must be string tokens (quoted or unquoted).

An object name may have a single associated array index. This index is specified by an arithmetic expression enclosed in square brackets following the name. The string token, excluding the array index, is called the *root name* of the object.

```

object_name :=

string_token

| string_token [ arith_expr ]

```

Note that the square brackets do not represent optional arguments.

## Example:

The root name of an object "a[5]" is simply "a".

It is often useful to name lists of objects. In this case, a modified array notation, called an object list, may be used to specify a range of array indices. This is done by supplying a start and end index for the array, separated by a colon ':'. The notation is equivalent to supplying each object name in order, beginning with the start index, and iterating until the

end index is reached. If the start index is less than the end index iteration increments by one, otherwise it decrements by one.

```

object_list := string_token [ arith_expr : arith_expr ]

```

Note that the square brackets do not represent optional arguments.

## Example:

```

"a[1:2]" expands to "a[1]" "a[2]".

"a[2:1]" expands to "a[2]" "a[1]".

```

A list of objects may contain single object names and object lists.

```

object_name_list :=

object_name

| object_list

| object_name_list

| object_list object_name_list

```

In a module definition, each internal subcomponent or signal must have a distinct name (root name and index). Also, objects with the same root name must have similar types. This means that signals, components and cables may not share root names. Furthermore, components or cables which share a root name must share the same master definition. These checks are performed during the creation of module definition instances.

It is often necessary to name an object which cannot be directly referenced from the current level. In this case a composite name is used, using the dot character '.' to separate levels. This is referred to as a hierarchical name.

```

hierarchical_name :=

object_name

| object_name . hierarchical_name

```

### Example:

The hierarchical name "a.b" refers to an object "b" which is a child of object "a", where "a" is a child of the current module.

Hierarchical naming may be used with array expansion, in which case rightmost indices are expanded first.

```