NASA Contractor Report 189621

/W-0/ 101340

P.187

# Integration of Tools for the Design and Assessment of High-Performance, Highly Reliable Computing Systems (DAHPHRS) Phase 1

C. Scheper

R. Baker

G. Frank

Research Triangle Institute

Research Triangle Park, NC 27709

S. Yalamanchili Honeywell, Inc. Systems and Research Center Minneapolis, MN 55418

G. Gray Virginia Polytechnic Institute and State University Bradley Department of Electrical Engineering Blacksburg, VA 24061

**Contract NAS1-17964 May 1992**

Space Administration

Langley Research Center Hampton, Virginia 23665 SATCRTINGST) INTEGRATION OF TOOLS FUR SCRISM AND ASSESSMENT OF MERETRANCE, HIGHLY RELIABLE COMPUTING TERS (PARPHRS), PHANE 1 (POLIBER)

#### Contents

| Li | st of | Figur  | es                                                                      | iv |

|----|-------|--------|-------------------------------------------------------------------------|----|

| Ac | cknov | wledge | ments                                                                   | x  |

| 1. | Intr  | oducti | on                                                                      | 1  |

| 2. | Too   | ls/Me  | thodology                                                               | 3  |

|    | 2.1.  | Perfor | mance Models and Tools                                                  | 6  |

|    | 2.2.  | Reliab | oility Models and Tools                                                 | 10 |

|    | 2.3.  | Integr | ated Performance and Reliability Tools                                  | 14 |

| 3. | Par   | adigm  |                                                                         | 22 |

|    | 3.1.  | Algori | thms                                                                    | 24 |

|    |       | 3.1.1. | Algorithm 1: Weapon to Target Assignment and Target Sequencing (WTA/TS) | 24 |

|    |       | 3.1.2. | WAUCTION_ASSIGNMENT                                                     | 28 |

|    | 3.2.  | Archit | ectures                                                                 | 29 |

|    |       | 3.2.1. | JPI, Mark III Hypercube                                                 | 32 |

|    |       | 3.2.2. | Encore Multimax                                                         | 33 |

|    |       | 3.2.3. | FTPP                                                                    | 36 |

|    | 3.3.  | Parad  | igm Framework for Analyses                                              | 42 |

| 1  | Por   | former | nce Analyses                                                            | 45 |

|    | 4.1.  | Devel   | opment of Algorithm Descriptions                | 47  |

|----|-------|---------|-------------------------------------------------|-----|

|    | 4.2.  | WTA     | /TS High-Level Workload Analysis                | 50  |

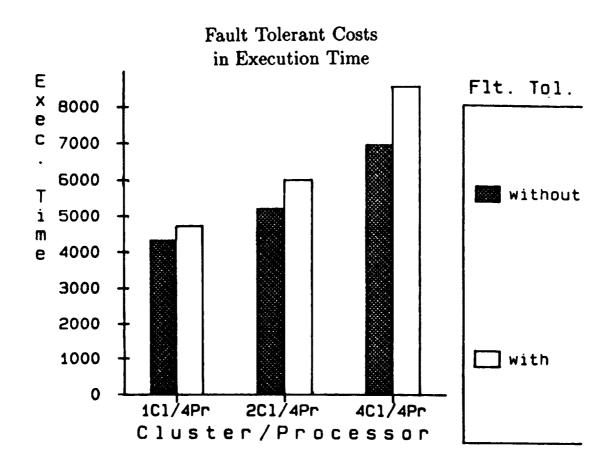

|    | 4.3.  | High-   | Level Decomposition of an Algorithm for FTPP    | 62  |

|    | 4.4.  | High-   | Level Generic Parallel Performance Models       | 69  |

|    | 4.5.  | WAU     | CTION_ASSIGNMENT High-Level Workload Assessment | 77  |

|    | 4.6.  | WTA,    | /TS Using the Hypercube and the Multimax        | 96  |

|    |       | 4.6.1.  | JPL Mark III Hypercube                          | 99  |

|    |       |         | 4.6.1.1. Mapping                                | 99  |

|    |       |         | 4.6.1.2. Scheduling of Intertask Communication  | 100 |

|    |       |         | 4.6.1.3. Simulation Results                     | 105 |

|    |       | 4.6.2.  | Encore Multimax                                 | 112 |

|    |       |         | 4.6.2.1. Mapping                                | 114 |

|    |       |         | 4.6.2.2. Scheduling of Intertask Communication  | 115 |

|    |       |         | 4.6.2.3. Simulation Results                     | 115 |

|    | 4.7.  | Perform | mance Modeling of Reconfiguration Algorithms    | 128 |

|    |       | 4.7.1.  | Description of Architecture                     | 128 |

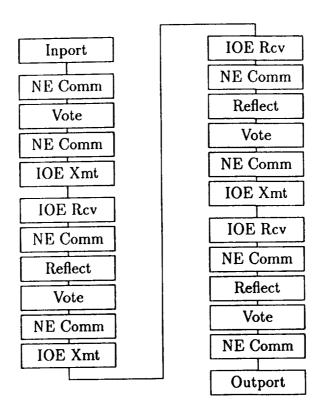

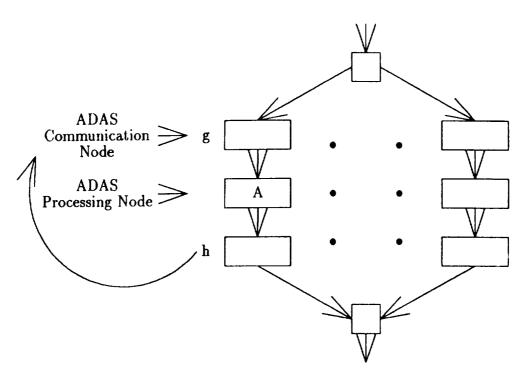

|    |       | 4.7.2.  | Description of ADAS Model                       | 129 |

|    |       | 4.7.3.  | Yanney-Hayes Algorithm                          | 136 |

|    |       | 4.7.4.  | White-Gray Algorithm                            | 138 |

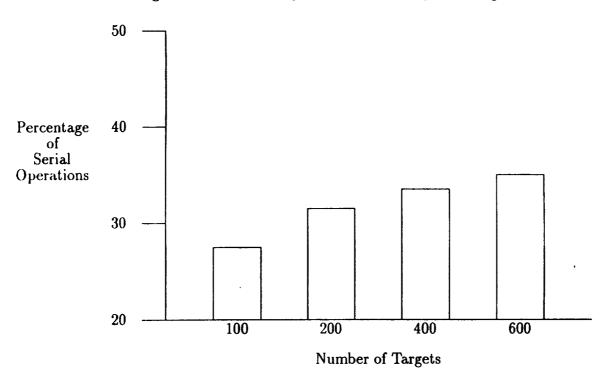

|    |       | 4.7.5.  | Experimental Results                            | 140 |

| 5. | Relia | ability | Analysis 1                                      | .49 |

|    | 5.1.  | High-Level Analyses    | 151 |

|----|-------|------------------------|-----|

|    | 5.2.  | FTPP Cluster Analysis  | 156 |

|    | 5.3.  | Network Analysis       | 160 |

| 6. | Sum   | nmary                  | 166 |

|    | 6.1.  | Goals                  | 166 |

|    | 6.2.  | Simulation Paradigms   | 167 |

|    | 6.3.  | Operational Tools      | 168 |

|    | 6.4.  | Mapping and Scheduling | 169 |

|    | 6.5.  | Validation             | 170 |

|    | 6.6.  | Miscellaneous          | 170 |

|    | 6.7.  | Conclusions            | 171 |

|    | 6.8.  | Further Work           | 173 |

| R  | efere | nces                   | 175 |

### List of Figures

| 2.1.         | Performance Modeling Process                                                    | •  |

|--------------|---------------------------------------------------------------------------------|----|

| 2.2.         | Reliability Modeling Process                                                    | 11 |

| 2.3.         | Process to FTPP Cluster Mapping                                                 | 18 |

| 2.4.         | ASSIST Code                                                                     | 16 |

| 2.5.         | Data Flow Among Performance and Reliability Models                              | 18 |

| 2.6.         | Integrated Performance and Reliability Analysis Tools                           | 20 |

| 3.1.         | Paradigm for Performance/Reliability Modeling in Support of System  Development | 23 |

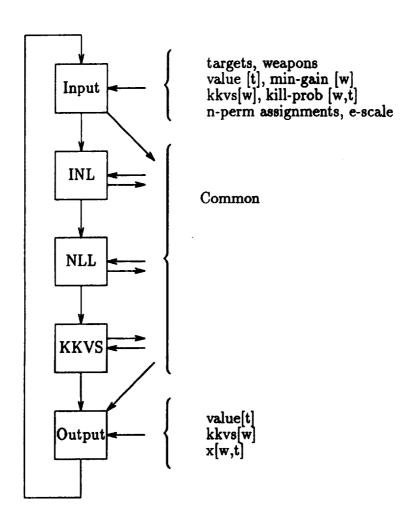

| 3.2.         | WTA/TS Data Flow Diagram                                                        | 25 |

| 3.3.         | General Integer Programming Solution                                            | 27 |

| 3.4.         | WAUCTION_ASSIGNMENT Data Flow Diagram                                           | 30 |

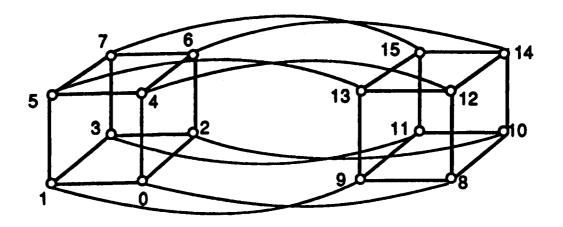

| 3.5.         | 16 Node Binary Hypercube                                                        | 33 |

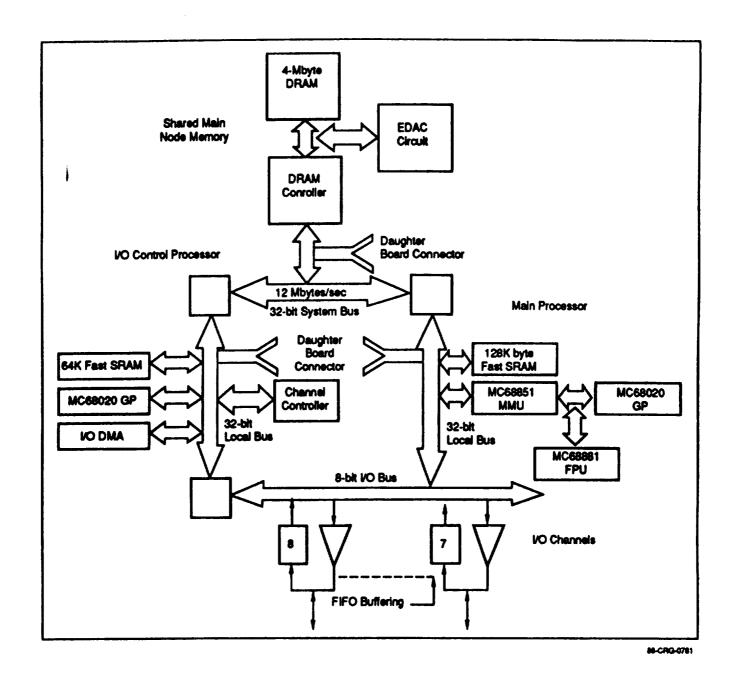

| <b>3.6</b> . | Mark III Node Architecture                                                      | 34 |

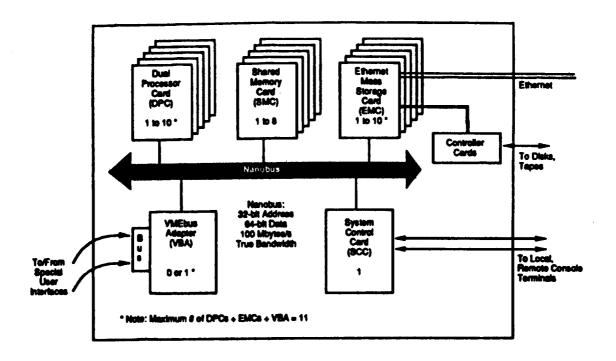

| 3.7.         | Encore Multimax                                                                 | 35 |

| 3.8.         | FTPP Input/Output Element                                                       | 37 |

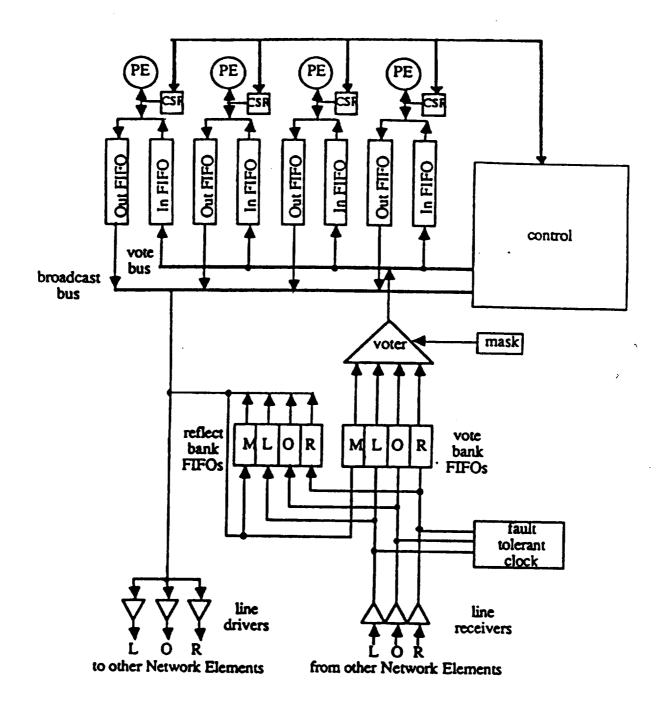

| 3.9.         | FTPP Processing Element                                                         | 37 |

| 3.10.        | FTPP Network Element                                                            | 38 |

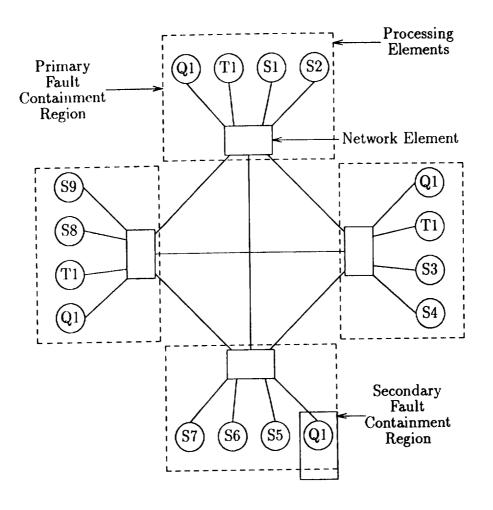

| 3.11.        | Possible 16-Processor Cluster Configuration                                     | 39 |

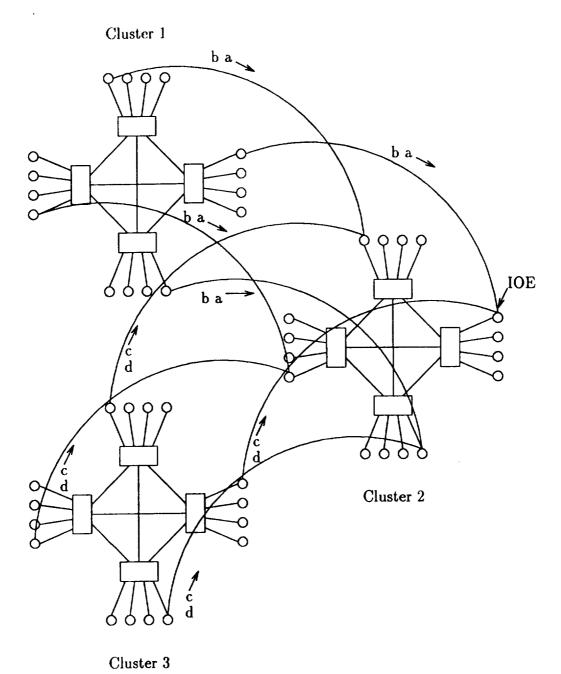

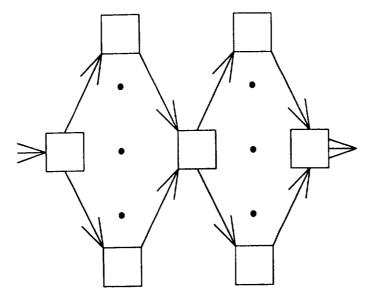

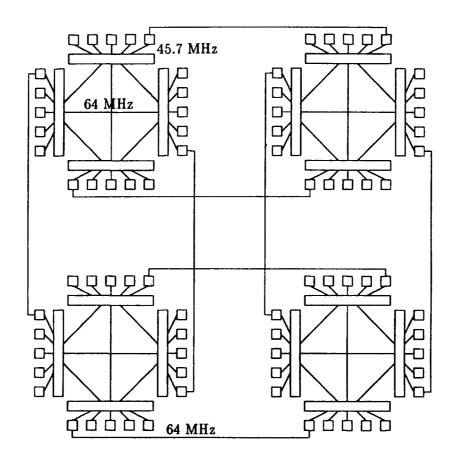

| 3.12.        | Possible Multicluster Topology                                                  | 41 |

| 3.13.        | High-Level Process Graph                                                        | 43 |

| 3.14. Refined Process Graph                                                                     | 44 |

|-------------------------------------------------------------------------------------------------|----|

| 4.1. Summary of Performance Studies                                                             | 46 |

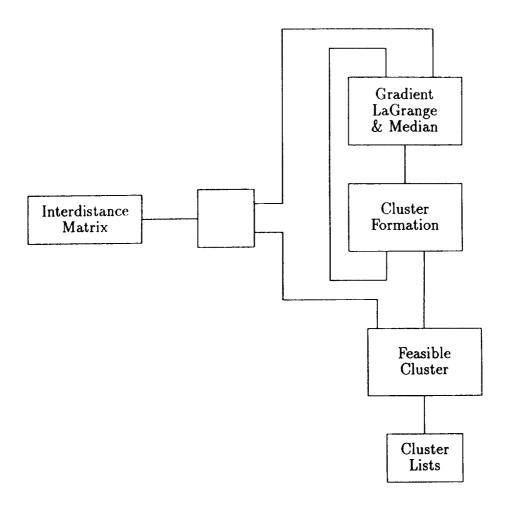

| 4.2. Top-Level WTA/TS ADAS Graph                                                                | 51 |

| 4.3. WTA/TS Target Cluster Definition ADAS Graph — Level 2                                      | 52 |

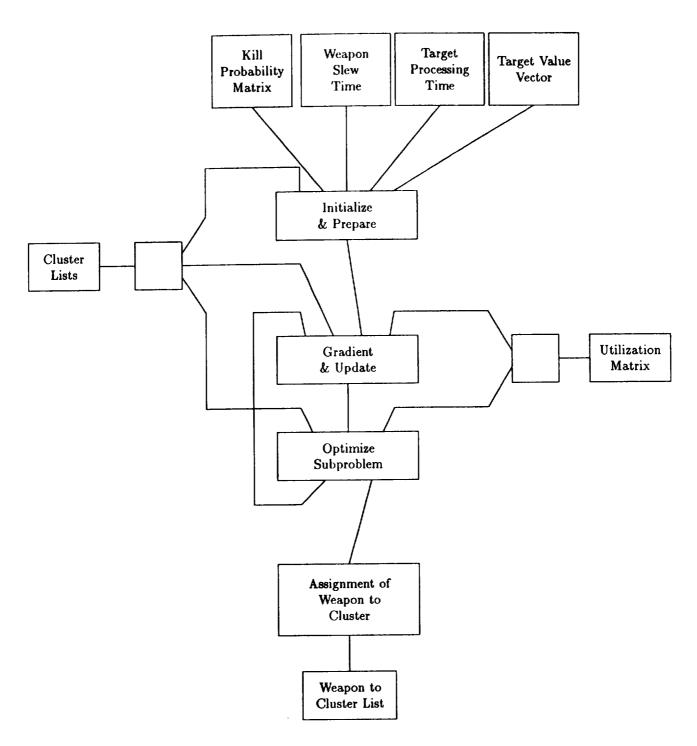

| 4.4. WTA/TS Weapon to Cluster Assignment ADAS Graph — Level 2                                   | 53 |

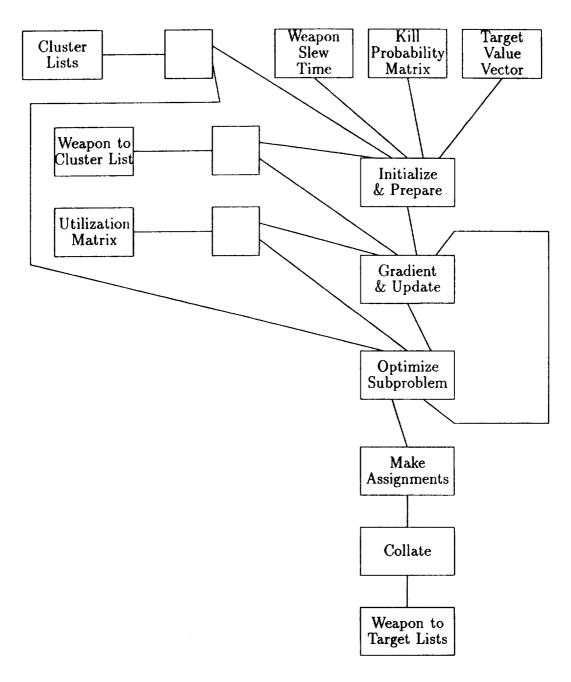

| 4.5. WTA/TS Weapon Assignment ADAS Graph — Level 2                                              | 54 |

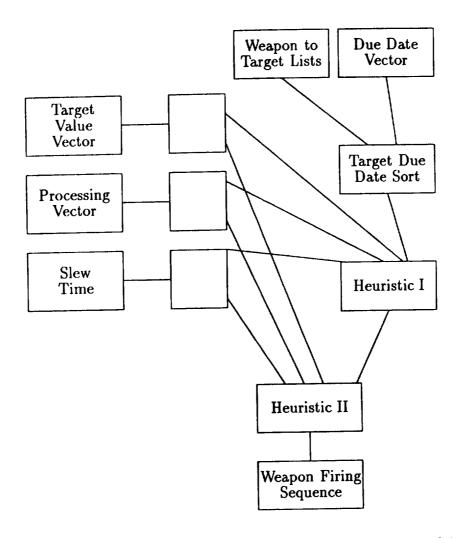

| 4.6. WTA/TS Target Sequencing ADAS Graph — Level 2                                              | 55 |

| 4.7. Example ADL File for WTA/TS ADAS Graph                                                     | 56 |

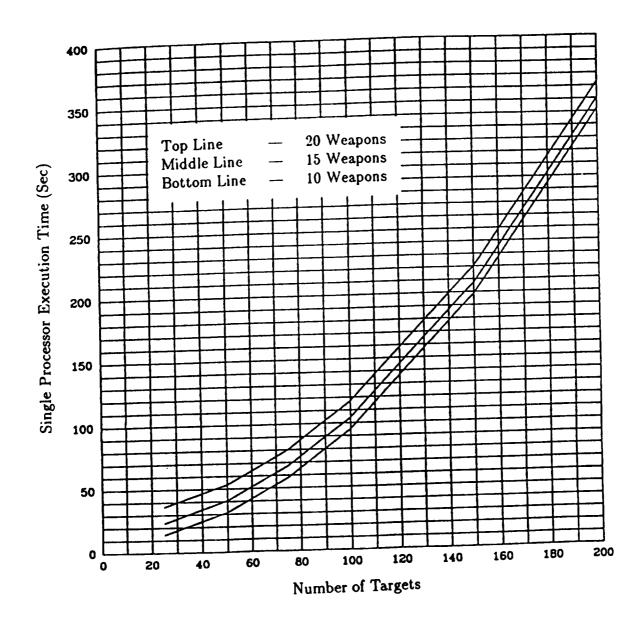

| 4.8. Single Processor Execution Times for WTA/TS                                                | 57 |

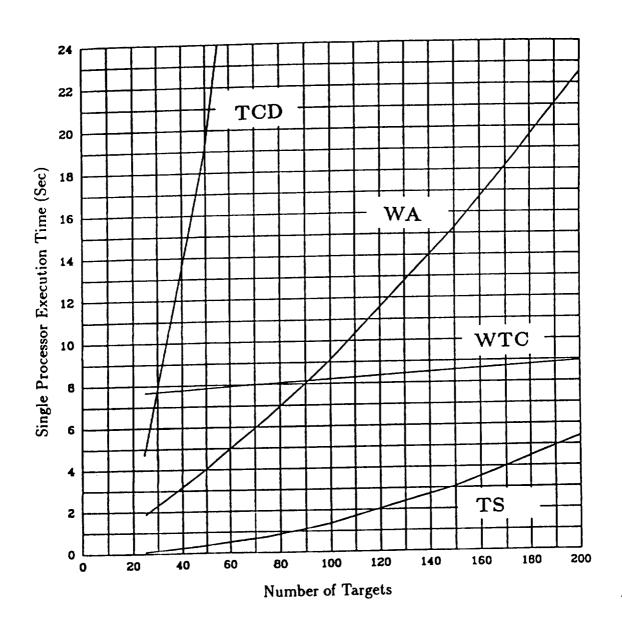

| 4.9. Execution Time Requirements of WTA/TS Functions                                            | 59 |

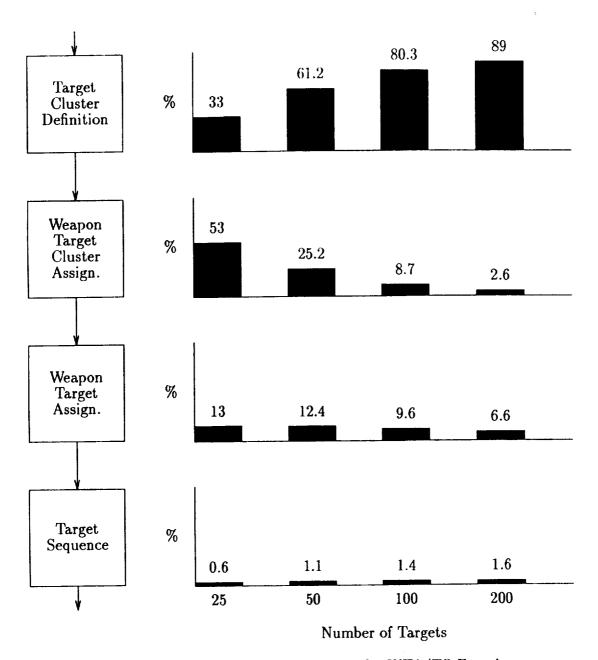

| 4.10. Execution Time Percentages by WTA/TS Function                                             | 60 |

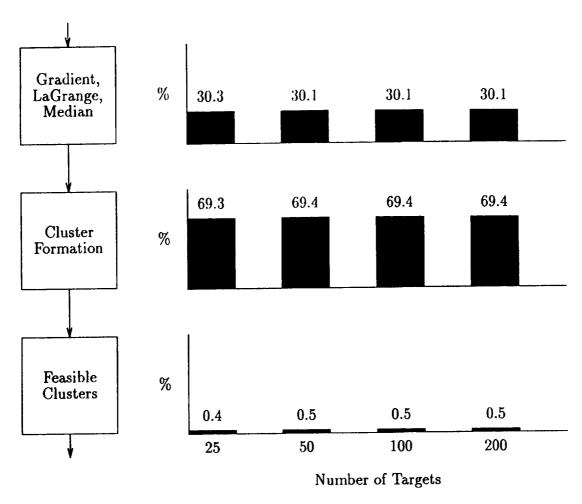

| 4.11. Percentage Workload Distributions for TCD Subfunctions                                    | 61 |

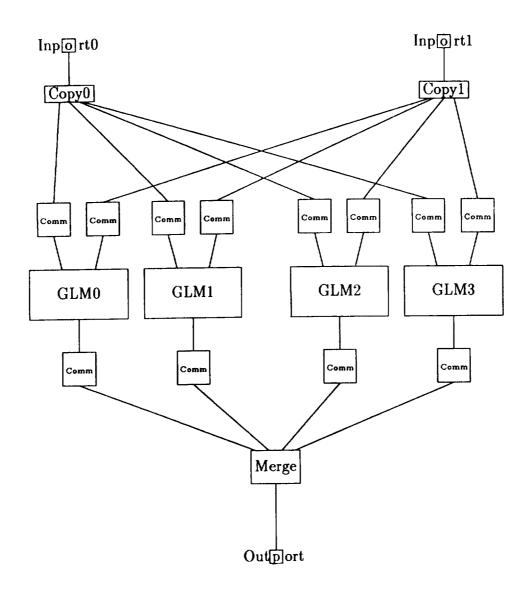

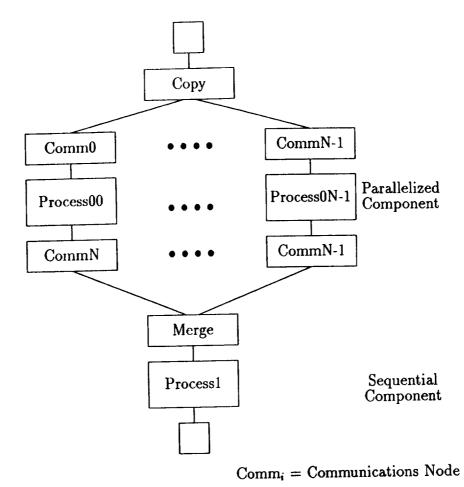

| 4.12. ADAS Model of Parallel Gradient Lagrange Median Portion of WTA/TS                         | 63 |

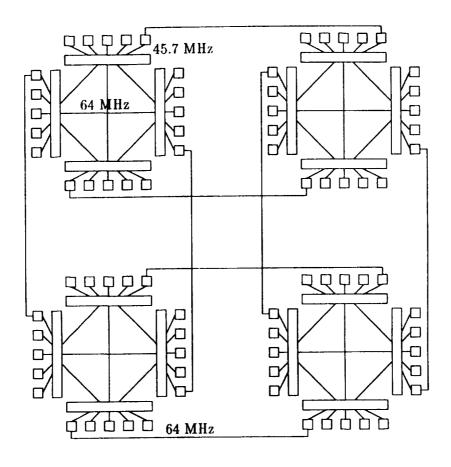

| 4.13. Diagram of a Linearly Connected FTPP Configuration                                        | 64 |

| 4.14. FTPP Data Transfer Steps for Four Cluster Distant Processor Pairs .                       | 65 |

| 4.15. Parallel Gradient Lagrange Median Execution Times                                         | 66 |

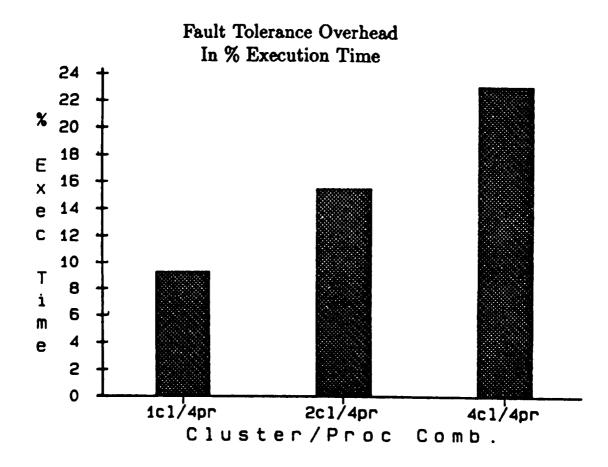

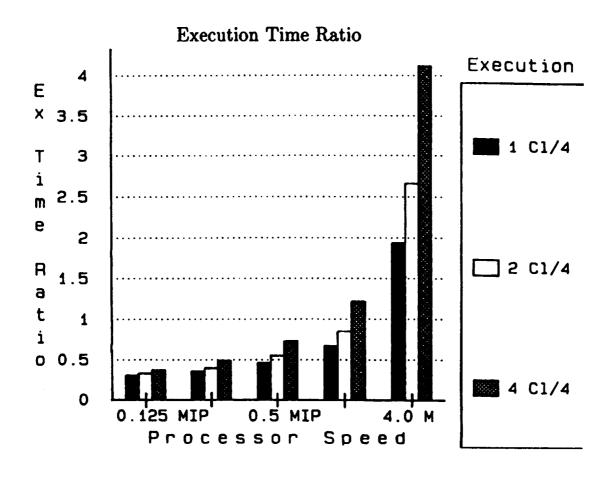

| 4.16. Fault-Tolerant Communications Time Percentage of Processing Time                          | 67 |

| 4.17. Execution Time Ratios for Parallel versus Single Processor as Function of Processor Speed | 68 |

| 4.18. Generic Process Structure                                                                 | 69 |

| 4.19. Architecture for Generic Parallel Performance Model                                       | 70 |

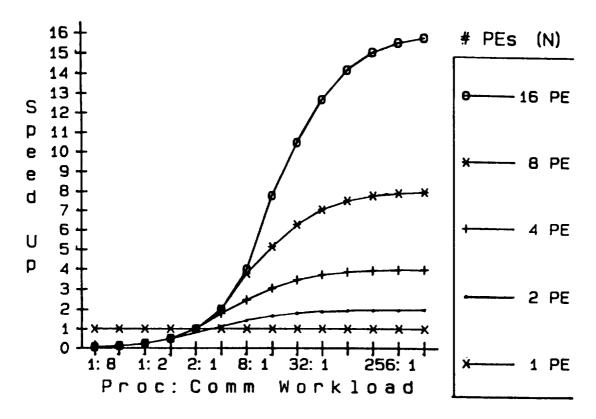

| 4.20. Speedup as Function of Processing to Communication Workload Ratios                        | 71 |

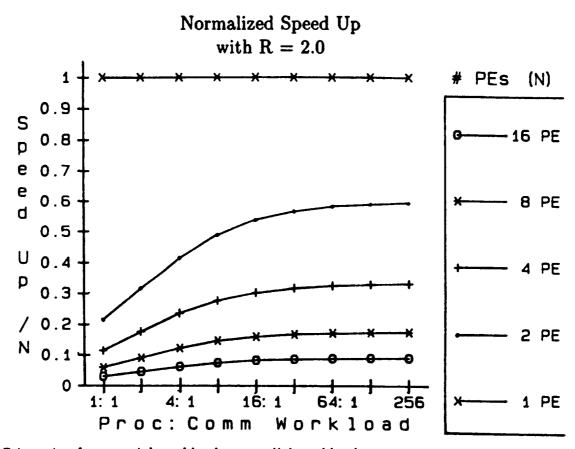

| 4.21          | Normalized Speedup                                                                                                | 72 |

|---------------|-------------------------------------------------------------------------------------------------------------------|----|

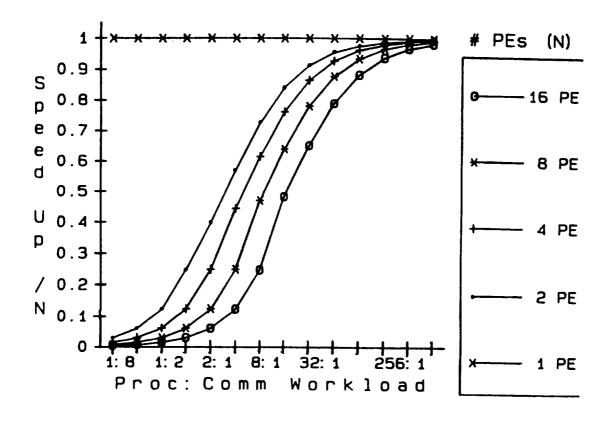

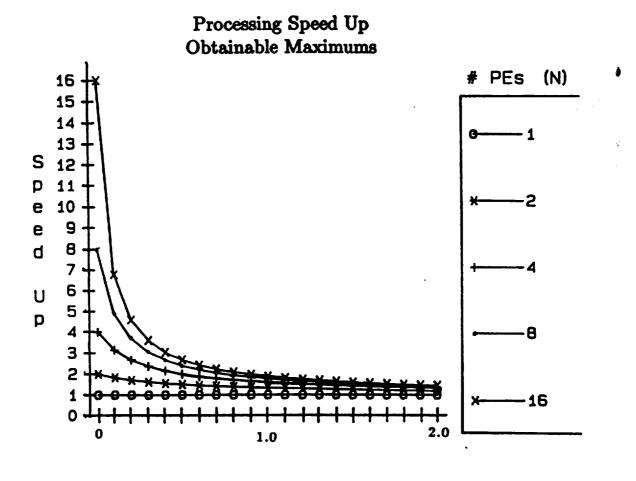

| 4.22          | . Maximum Speedup as Function of Sequential-to-Parallel Workload Ratio                                            | 74 |

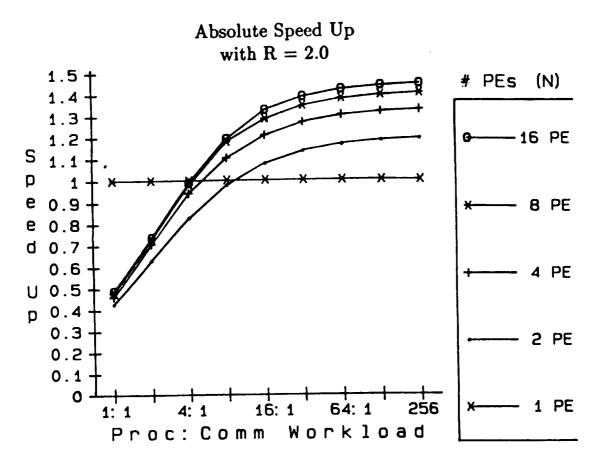

| 4.23          | Speedup as a Function of Processing-to-Communication Workload Ratio for Sequential-to-Parallel Workload Ratio = 2 | 75 |

| 4.24          | Normalized Speedup as Workload Varies                                                                             | 76 |

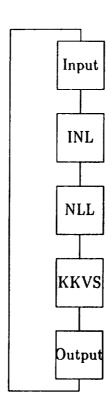

| <b>4.2</b> 5. | Top Level WAUCTION_ASSIGNMENT ADAS Graph                                                                          | 78 |

| 4.26.         | WAUCTION_ASSIGNMENT Non-Linear Loop ADAS Graph — Level 2                                                          | 79 |

| 4.27.         | WAUCTION_ASSIGNMENT Linear Loop ADAS Graph — Level 2 .                                                            | 80 |

| 4.28.         | Predicted Workload for WAUCTION_ASSIGNMENT as Function of Targets and Weapons                                     | 81 |

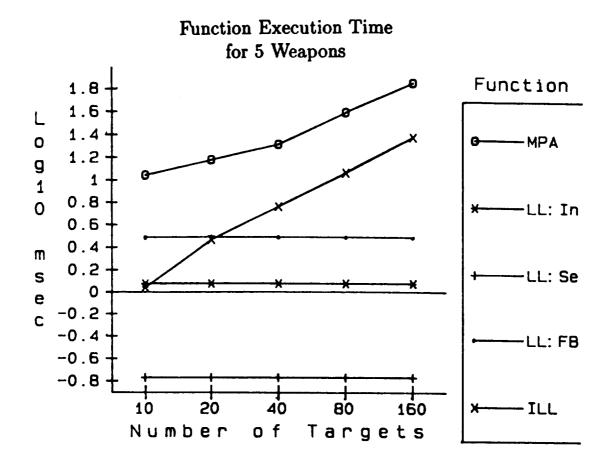

| 4.29.         | WAUCTION_ASSIGNMENT Workload Distribution by Function for Weapons = 5                                             | 83 |

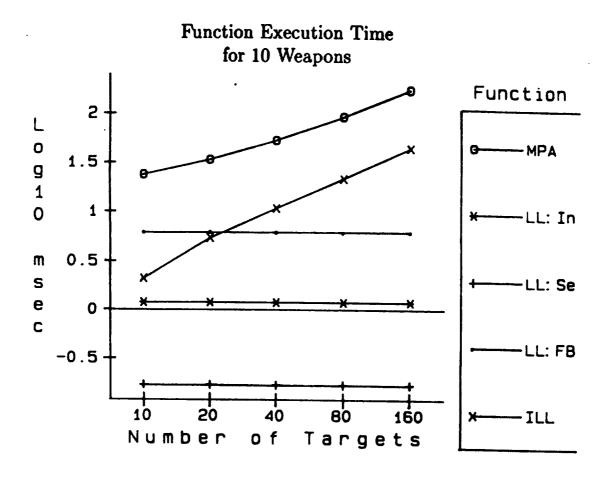

| 4.30.         | WAUCTION_ASSIGNMENT Workload Distribution by Function for Weapons = 10                                            | 84 |

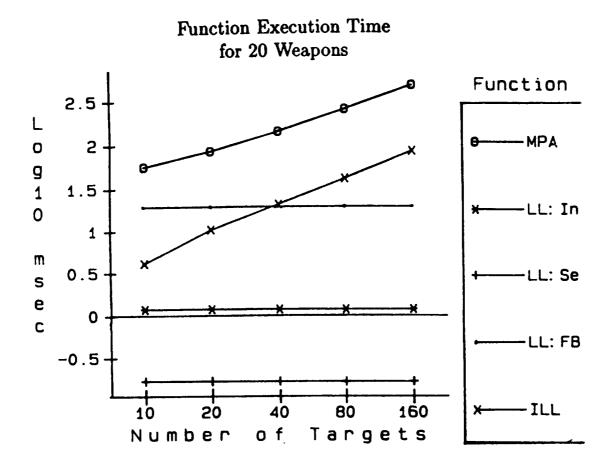

| 4.31.         | WAUCTION_ASSIGNMENT Workload Distribution by Function for Weapons = 20                                            | 85 |

| 4.32.         | WAUCTION_ASSIGNMENT Workload Distribution by Function for Weapons = 40                                            | 86 |

| 4.33.         | WAUCTION_ASSIGNMENT Workload Distribution by Function for Weapons = 80                                            | 87 |

| 4.34.         | WAUCTION_ASSIGNMENT Workload Distribution by Function for Weapons = 160                                           | 88 |

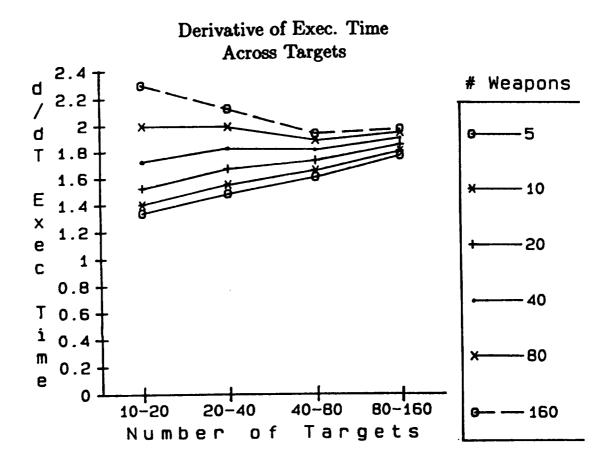

| <b>4.3</b> 5. | First Difference of WAUCTION_ASSIGNMENT Workload with Respect to Number of Targets                                | 89 |

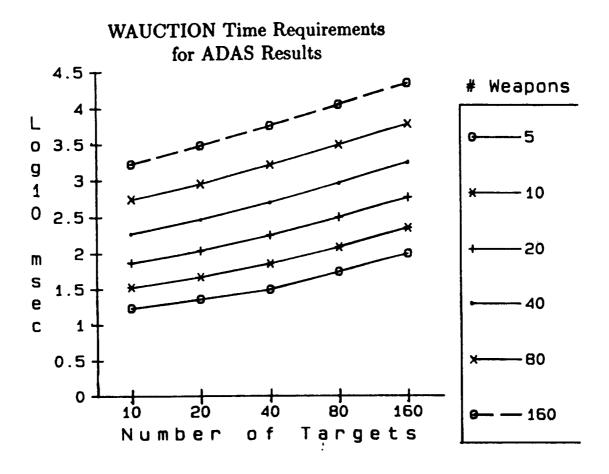

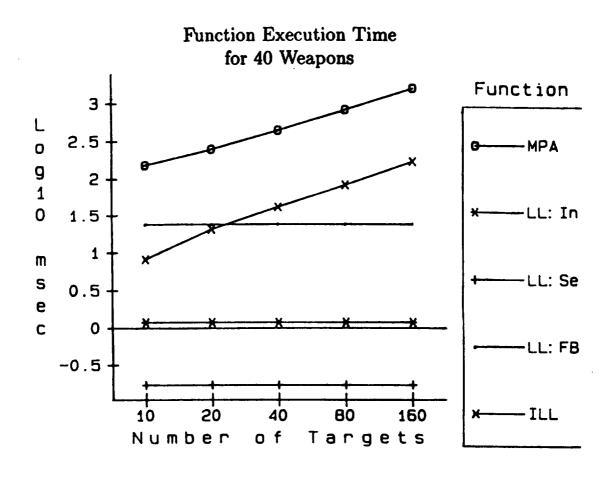

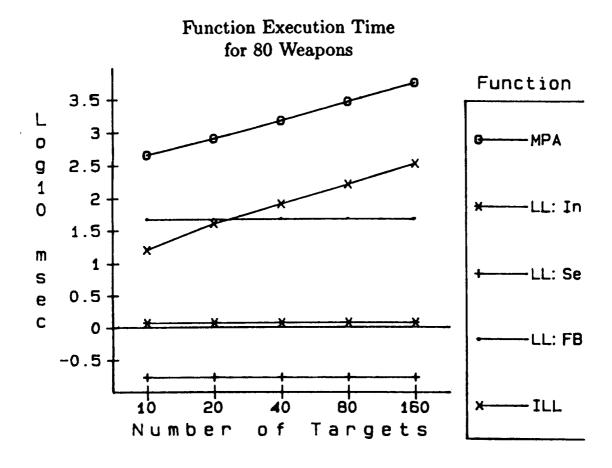

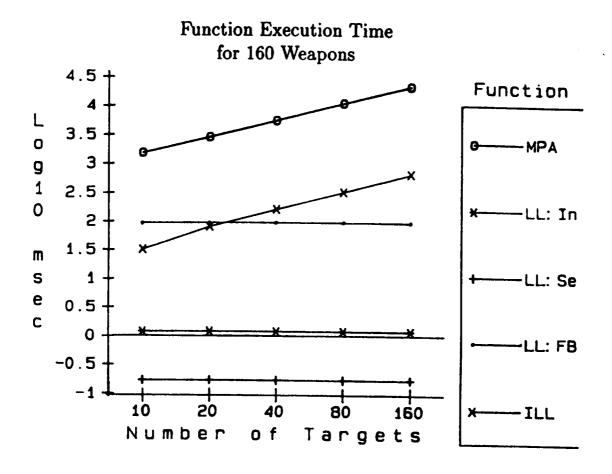

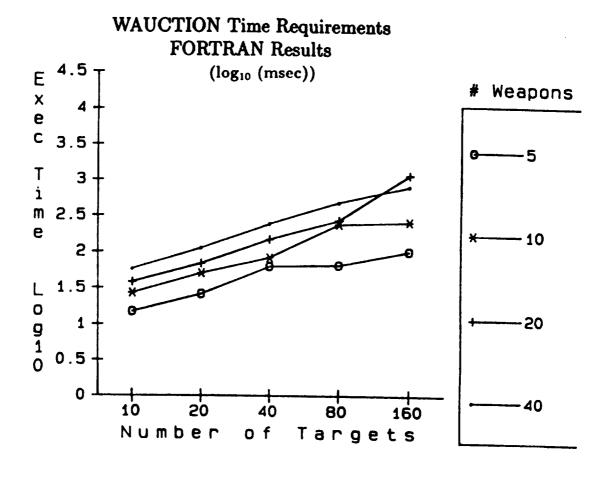

| 4.36.         | Measured CPU Time for WAUCTION_ASSIGNMENT                                                                         | 90 |

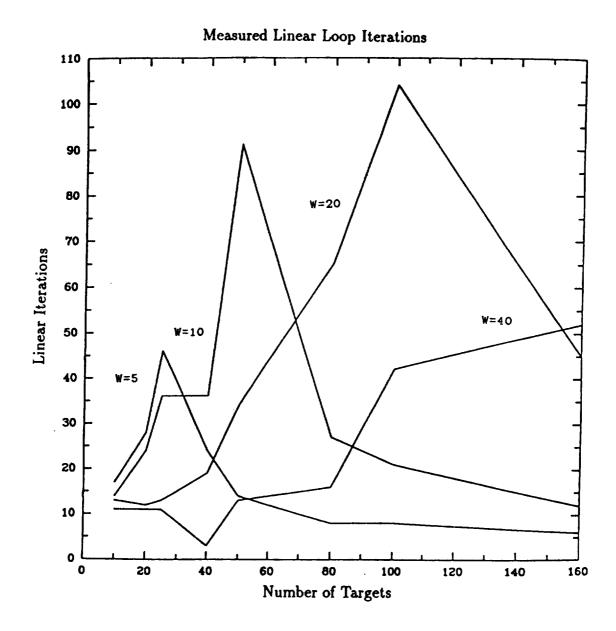

| 4.37.         | Loop Iteration Counts for WAUCTION_ASSIGNMENT Linear Loop                                                         | 91 |

| Loop                                                                           | 92  |

|--------------------------------------------------------------------------------|-----|

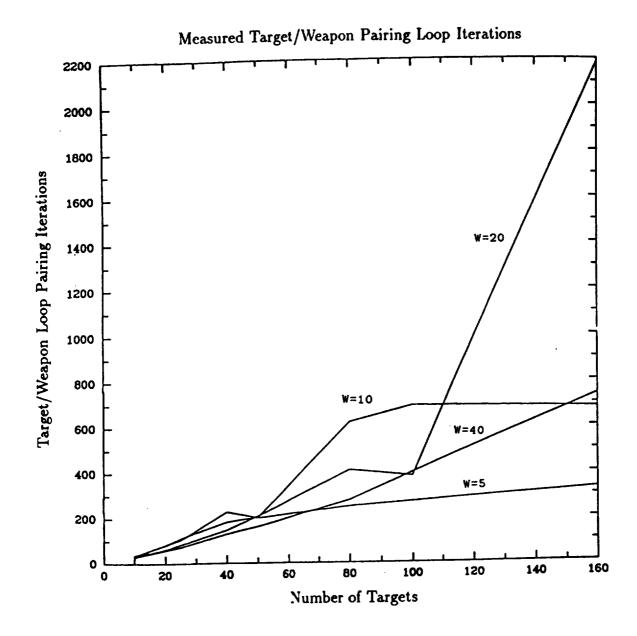

| 4.39. Loop Iteration Counts for WAUCTION_ASSIGNMENT Target Weapon Pairing Loop | 93  |

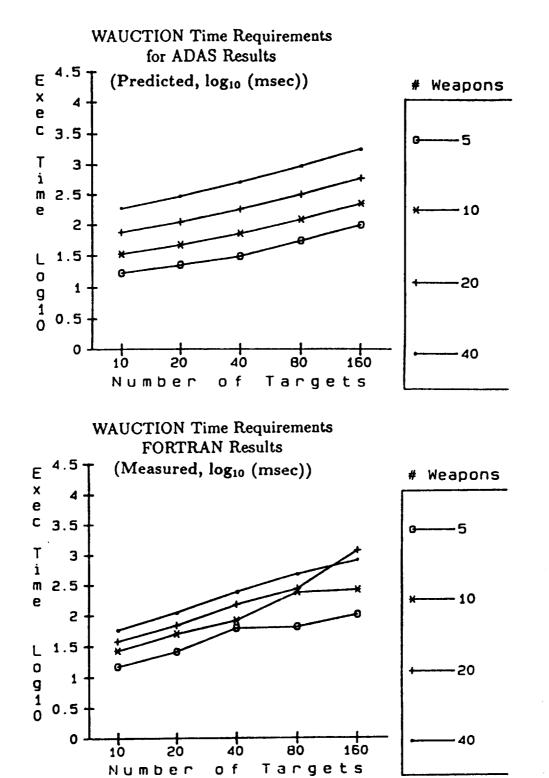

| 4.40. Measured versus Predicted for WAUCTION_ASSIGNMENT                        | 94  |

| 4.41. Algorithm Structure                                                      | 97  |

| 4.42. ADAS Representation of a Pipeline Stage                                  | 98  |

| 4.43. Algorithm Characteristics                                                | 98  |

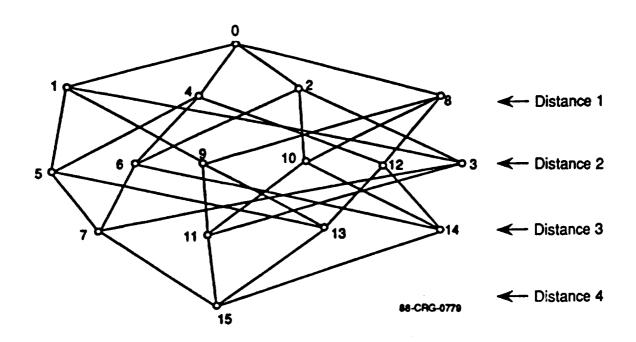

| 4.44. Interprocessor Distances in a 16 Node Binary Hypercube                   | 101 |

| 4.45. Interprocessor Communication in the Mark III                             | 101 |

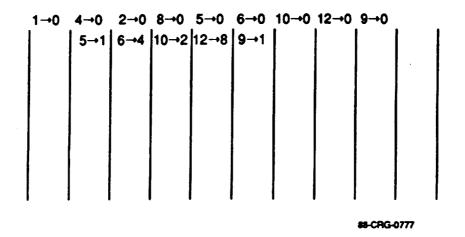

| 4.46. A Communication Schedule for 16 PEs                                      | 104 |

| 4.47. A Communication Schedule for 10 PEs                                      | 104 |

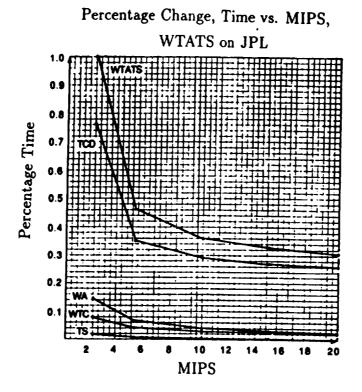

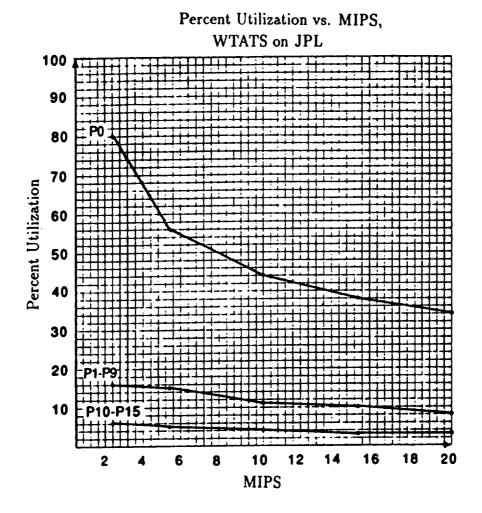

| 4.48. Latency vs. Processor Speed                                              | 106 |

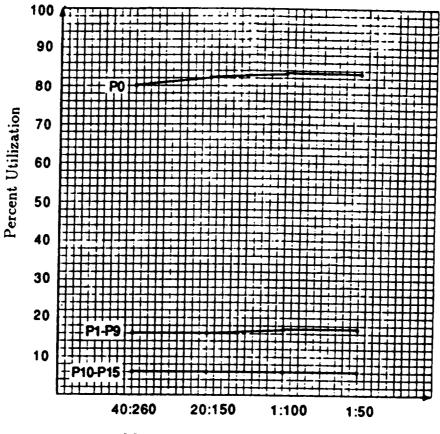

| 4.49. Latency vs. Routing Delay and Memory Access Time                         | 107 |

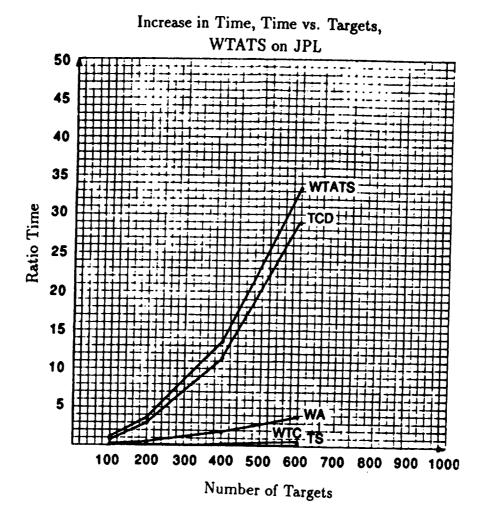

| 4.50. Latency vs. Number of Targets                                            | 108 |

| 4.51. Utilization vs. Processor Speed                                          | 109 |

| 4.52. Utilization vs. Routing Delay and Memory Access Time                     | 110 |

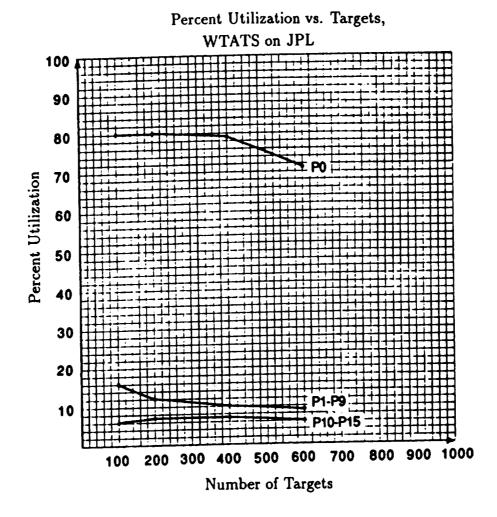

| 4.53. Utilization vs. Number of Targets                                        | 111 |

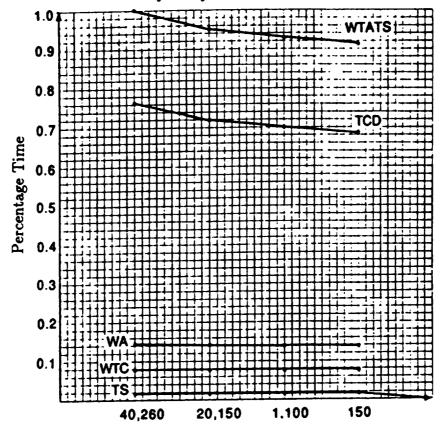

| 4.54. Performance of the Mark III Hypercube                                    | 113 |

| 4.55. Operation Counts for Processor Executing Parallel Tasks                  | 116 |

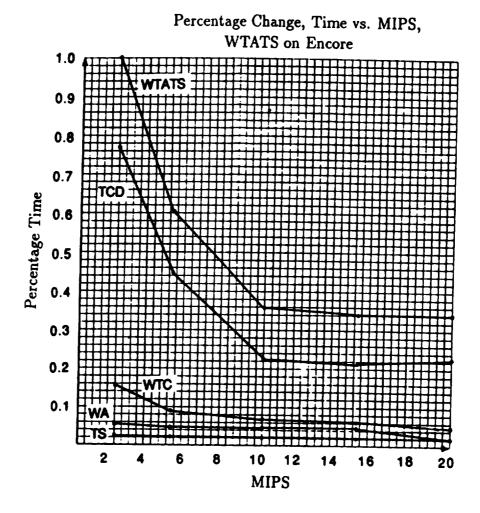

| 4.56. Latency vs. Processor Speed                                              | 118 |

| 4.57. Latency vs. Memory Access Time                                           | 119 |

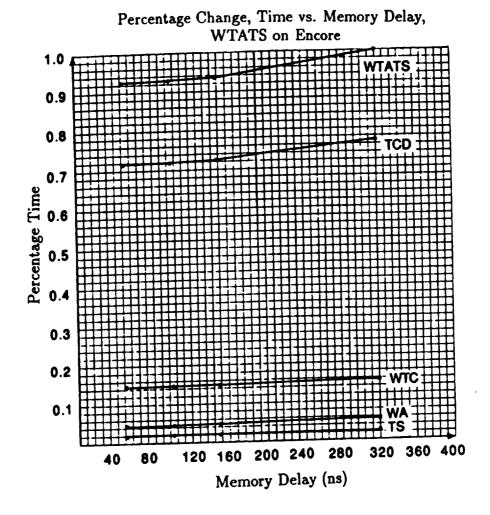

| 4.59 Intency vs. Bus Speed                                                     | 120 |

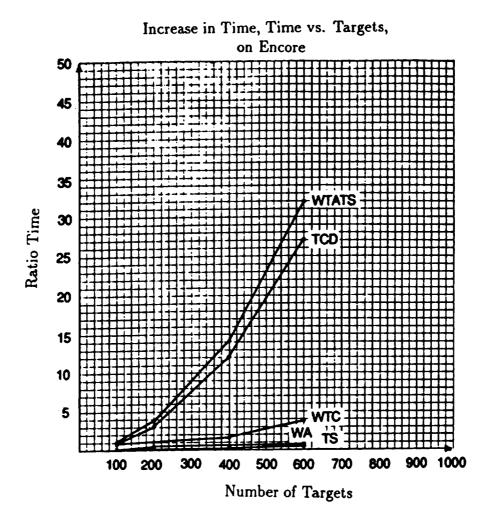

| 4.59. Latency vs. Number of Targets                                    | . 12  |

|------------------------------------------------------------------------|-------|

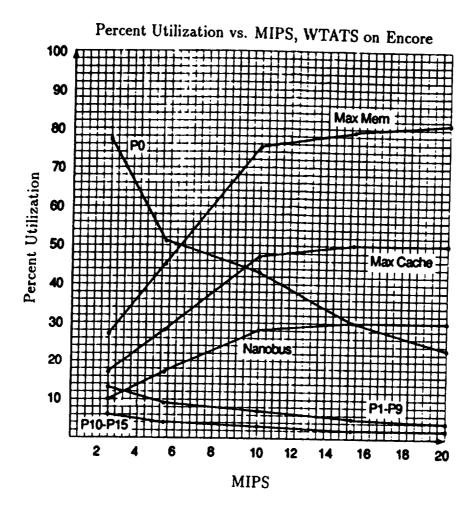

| 4.60. Utilization vs. Processor Speed                                  | . 12  |

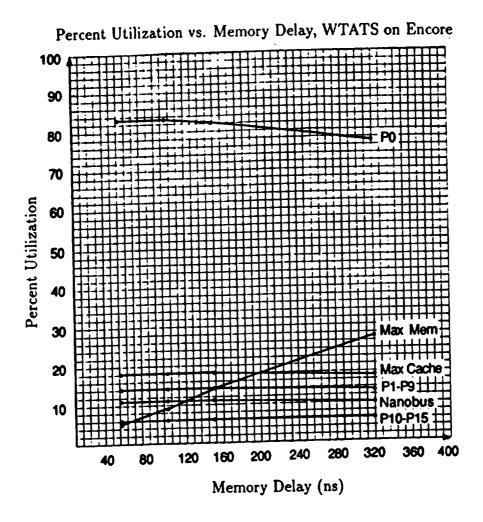

| 4.61. Utilization vs. Memory Access Time                               | . 123 |

| 4.62. Utilization vs. Bus Speed for Processors P0 through P15          | . 124 |

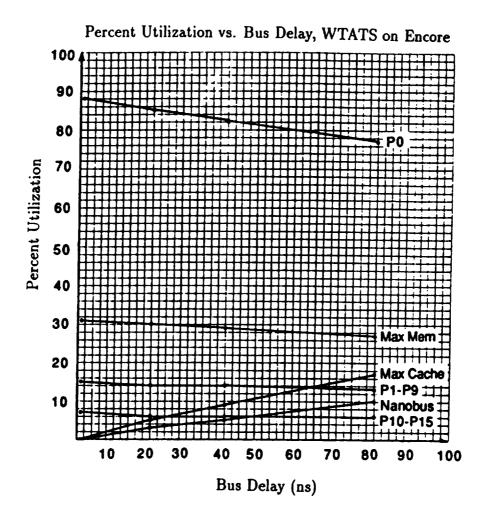

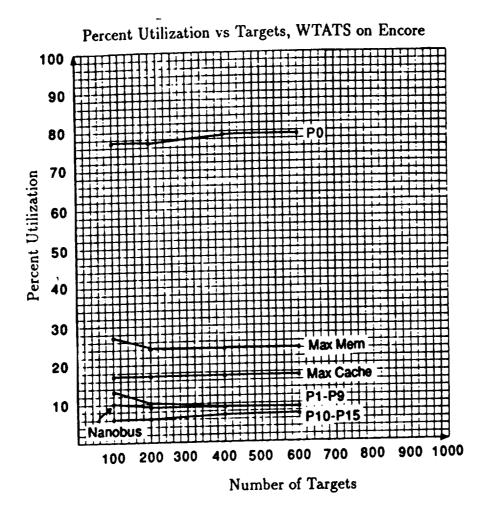

| 4.63. Utilization vs. Number of Targets                                | . 12  |

| 4.64. Performance of the Encore Multimax                               | . 127 |

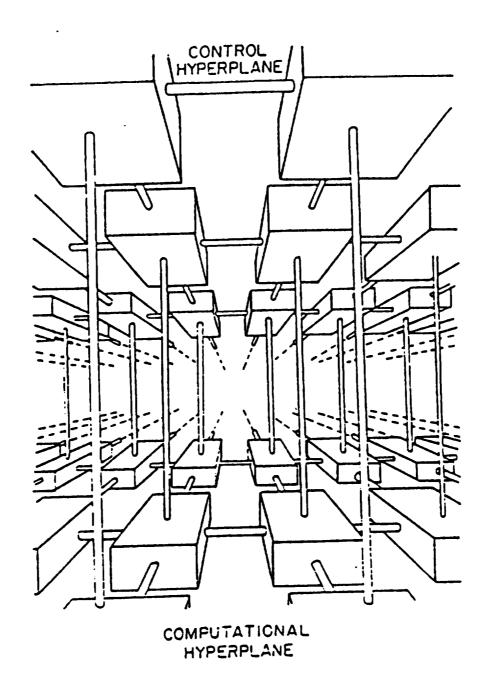

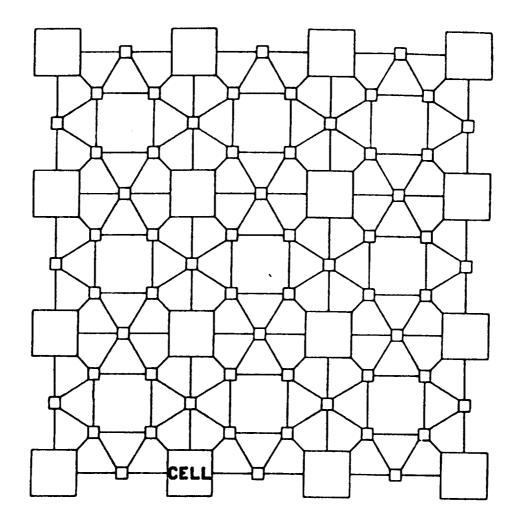

| 4.65. Fault-Tolerant Cellular Array [17]                               | . 131 |

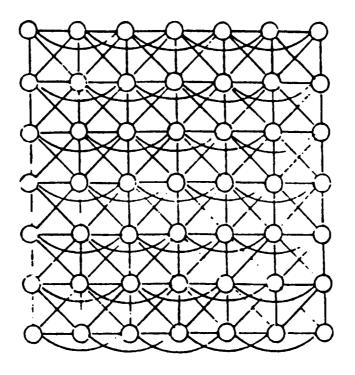

| 4.66. Computational Plane [17]                                         | . 132 |

| 4.67. Control Plane                                                    | . 133 |

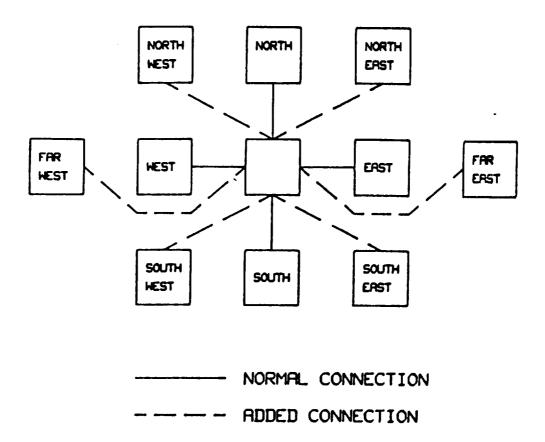

| 4.68. Connections to a Cell in the Control Plane [17]                  | . 134 |

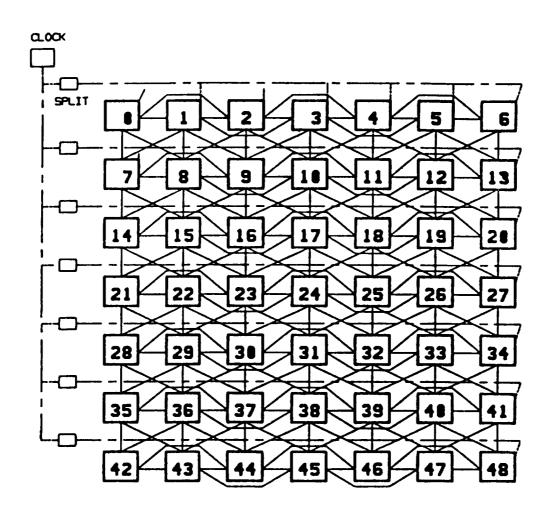

| 4.69. ADAS Simulation Model [17]                                       | . 135 |

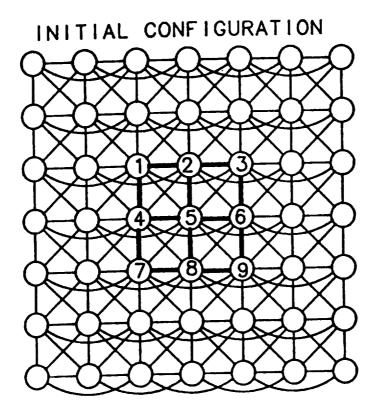

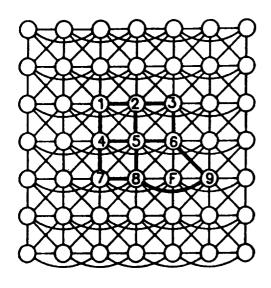

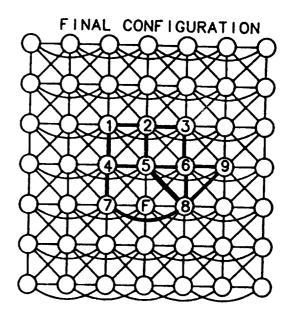

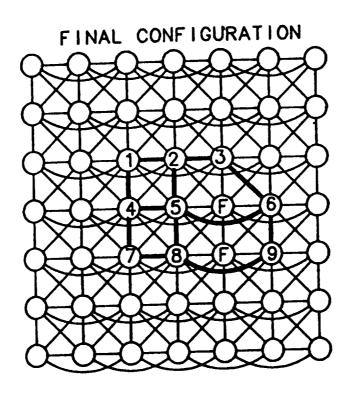

| 4.70. Base Graph Embedded in Global Architecture                       | . 141 |

| 4.71. Error Detection Assignment for Yanney-Hayes Algorithm            | . 143 |

| 4.72. Reconfiguration for a Single Fault in Cell 8                     | . 144 |

| 4.73. Reconfiguration for a Sequential Double Fault in Cells 9 and 6   | . 145 |

| 4.74. Summary of Coverage from ADAS Simulations                        | . 146 |

| 4.75. Time Analysis of Single Faults from ADAS Simulations             | . 146 |

| 4.76. Time Analysis of Double Faults from ADAS Simulations             | . 147 |

| 4.76. Time Analysis of Double Faults from ADAS Simulations (continued) | 148   |

| 5.1. Spare Analysis State Model                                        | . 152 |

| 5.2. Spare Analysis ASSIST File                                        | . 153 |

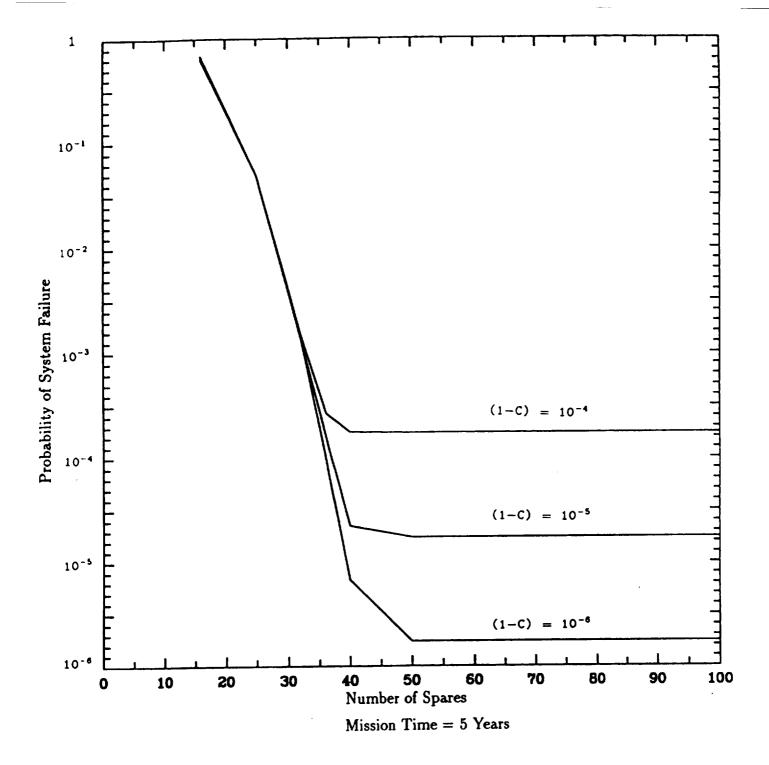

| 5.3 Spare Analysis Results                                             | 154   |

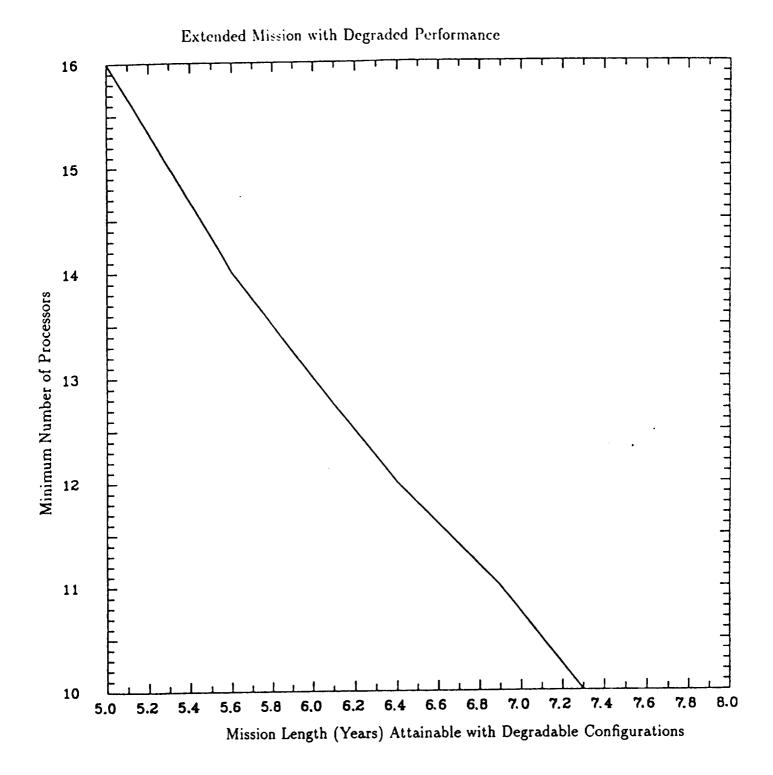

| 5.4.  | Extended Mission Analysis Results                           | • | • | • | 155 |

|-------|-------------------------------------------------------------|---|---|---|-----|

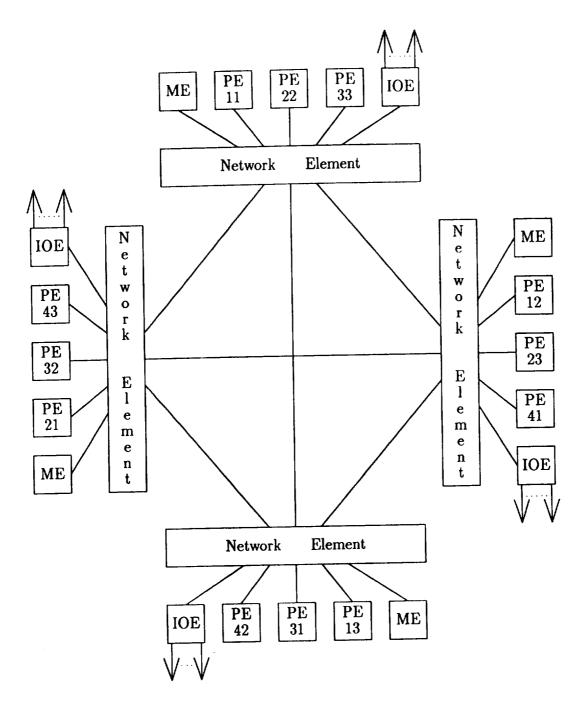

| 5.5.  | Cluster Analysis System Configuration                       | • | • | • | 157 |

| 5.6.  | Cluster Network Topology                                    | • |   | • | 158 |

| 5.7.  | Full Model of Independent Triads                            | • | • | • | 161 |

| 5.8.  | Reduced Model of Independent Triads                         | • |   | • | 162 |

| 5.9.  | Reduced Model of Interdependent Triads and Network Elements | • | • |   | 163 |

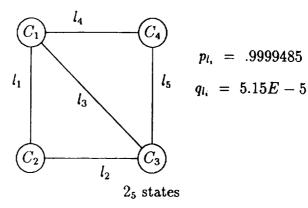

| 5.10. | Example Network Model                                       |   |   |   | 164 |

#### **ACKNOWLEDGEMENTS**

This report was prepared for the Rome Air Development Center (RADC) and the National Aeronautics and Space Administration's Langley Research Center (NASA-LaRC) under Contract NASI-17964. The work was performed in the Center for Digital Systems Research (CDSR) of Research Triangle Institute (RTI) by C. Scheper (Project Leader), R. Baker, G. Frank, and H. Waters; in the Systems and Research Center of Honeywell, Inc. by S. Yalamanchili and T. Carpenter; and in the Bradley Department of Electrical Engineering of Virginia Polytechnic Institute (VPI) by G. Gray, L. DeBrunner, and T. White.

We wish to express our appreciation for the guidance and support provided by the project technical monitors, Capt. G. Paeper of RADC; and W. Bryant, C. Elks, and S. Johnson of NASA-LaRC.

Technical support in preparing the DAHPHRS documentation and this report was provided by G. Crim, J. Muller, P. Noell, J. Sapp, K. Simmons, B. Shay, and B. Taylor.

#### 1. Introduction

The Strategic Defense Initiative (SDI) concepts require the development of systems for complex space applications subject to demanding real time computational resource requirements and very high reliability requirements. Complex space applications are characterized by large amounts of numerical processing, large data bases, and iterative approximations to optimal solutions. The algorithms used in the signal and image processing that are necessary for target detection, classification, tracking, and trajectory estimation are computationally intensive and must meet real-time deadlines to match the incoming data rates of wideband sensors. However, these algorithms can usually be decomposed into highly regular computational structures. On the other hand, mission planning functions employ programming techniques in which the computational requirements vary with dynamic changes in the incoming data. The missions that these applications address require extremely long system operating life. They are also divided into phases composed of long periods of moderate activity followed by very short periods of high activity and characterized by vastly different reliability and performance requirements. In addition, the system operates under demanding system weight and power requirements in an environment subject to radiation and thermal and mechanical stress.

These system characteristics lead to complex non-uniform architectures comprising a large number of processors with mechanisms to extend operational life and to support changes in mission phase or the attrition of system resources. Specifically, the applications require architectures that combine elements of massive parallel computing techniques and of fault-tolerant system design. Parallel computing is a rapidly emerging field of research and many of the complex practical problems related to realizing effective architectures have not been solved. This, coupled with the extra complexity brought on by the fault tolerance requirements, presents the system engineer evaluating the performance and reliability for such systems with the extremely difficult problem of conducting performance and reliability trade-offs over large design spaces and verifying performance and reliability over a wide range of operating conditions.

The methods and tools to fully and effectively deal with these problems do not exist. This is due in part to the sheer size of the systems involved. However, the very nature of these systems dictate evaluation criteria that differ in many respects from those used to evaluate more traditional computing systems. Consequently, tools which can meet the challenge presented by the high level of complexity and the expanded evaluation criteria for such systems are required. Further, the combining of parallel computing with fault tolerance requirements dictates the need for integrating

the performance and reliability evaluation tools in order to facilitate trade-offs between performance and reliability. Even if tools which meet the demands of present applications did exist, the advances in this rapidly emerging area could soon render them inadequate. Thus, the goal of this program is to develop an integrated set of performance and reliability tools capable of managing the complexity of such designs and robust enough to adapt to the inevitable technological advances.

In order to determine what tools are needed and how those tools should interact, this first phase of the toolset development was focused on relating tools to a methodology framework through the development and analysis of a paradigm of the design process for an SDI-like system. The paradigm was used to determine what system models are needed, how the models interact, and what experiments and analyses are needed in an effective methodology for system design for performance and reliability. It was also used to illustrate how tools support such a methodology and what the tool features and capabilities should be. Based on the identified interactions between the reliability and performance analyses, the paradigm will be expanded in a subsequent phase to allow the examination of fault tolerance mechanisms and the study of performance/reliability trade-offs. Also, existing tools will be identified and additional tools and interfaces specified and built in a subsequent phase.

This report documents the activity and findings during the first phase of this contract. Section 2 discusses the issues related to tools and methodology. Section 3 discusses the development of the paradigm and the algorithms and architectures selected for inclusion therein. Sections 4 and 5 discuss the performance and reliability analyses performed for the paradigm.

#### 2. Tools/Methodology

The dual requirements of high reliability and high performance for systems that will operate nearly autonomously in mission- and life-critical applications dictate that those systems be validated to a high level of confidence. Accordingly, it is expected that a rigid development process be utilized to assure that design errors are eliminated before the system is delivered and to assure that the system will meet reliability and performance objectives. A design for reliability methodology framework has been set forth in the working document of the SDIO BM/C<sup>3</sup> Processor and Algorithm Working Group [13]. This methodology specifies eight steps for system design:

- 1. Identify classes of expected faults over the lifetime of the system.

- 2. Specify goals for the dependability of system performance.

- 3. Partition the system into subsystems for implementation, taking into account both performance and fault tolerance.

- 4. Select error detection and fault diagnosis algorithms for every subsystem.

- 5. Devise state recovery and fault removal techniques for every subsystem.

- 6. Integrate subsystem fault tolerance on system scale.

- 7. Evaluate the effectiveness of fault tolerance and its relationship with performance

- 8. Refine the design by iteration on steps three through seven.

The methodology also specifies five phases of design and establishes milestones for each phase and deliverables for the design reviews that occur at the end of each phase. The specified design reviews are as follows:

- 1. System requirements review to specify a computational model, requirements for performance and fault tolerance, applicable architectural approaches, and a development plan.

- 2. System design review to evaluate architectural trade-offs and to select an architectural approach and fault tolerance strategy.

- 3. Preliminary design review to specify preliminary hardware and software design and to provide performance and fault tolerance evaluation.

- 4. Critical design review to provide a completed hardware and software design, refined analysis of performance and fault tolerance attributes, and a plan for a feasibility demonstration.

- 5. Demonstration, evaluation, and test review to include a demonstration of brassboard components and operational software, and an experimental evaluation of performance and fault tolerance features.

The working document also specifies the use of tools in each phase and describes the characteristics of those tools, as summarized below.

During the system requirements phase, tools are needed to evaluate very high-level designs without detailed hardware and architectural information. These tools must interface with the tools that analyze more detailed designs in later phases. The outputs of these tools should be usable as inputs to more detailed tools and/or compared with more detailed evaluation results to verify that the high-level requirements are met by the actual design. It should be possible to share data files by tools at all levels in the design process. The need for integration is paramount. Current practice in this area results in ad hoc methods being reinvented by each contractor and results in tools that do not readily interface with tools at other levels of design. A generally accepted standard is sorely needed.

At the system design review, architecture alternatives are evaluated. Tools are needed that will allow meaningful comparisons of the performance and fault tolerance attributes of each alternative system. The tools must model high-level architecture features and must incorporate a high-level fault model. In the expert report, it is also recommended that error propagation effects and the effects of corruption of system state due to faults be modeled at this level. An accurate testability analysis is also required. Some tools are available that do part of this job (PMS and ISP simulators, for example). Unfortunately, these simulators do not consider the effects of faults. An integrated tool that evaluates both performance and fault tolerance attributes using a common data base and model is needed.

At the preliminary design review, more details of the selected design are available. It should be possible to refine the models created for the system design review to reflect the newly available detail. More accurate estimations of performance and fault tolerance parameters should then be possible. The tools should now be able to provide accurate estimates of coverage of the error detection mechanism and to

evaluate the quality of the error containment and error recovery procedures. The tools must have a clean interface to the more detailed tools that will come later and to the more general tools used earlier. Accurate reliability modeling tools are also a necessity at this stage.

At the critical design review, details of both hardware and software designs are completed. The evaluation tools should allow further refinement of the models to reflect the additional detail. Detailed hardware and software simulations should now be performed. Since existing tools cannot handle the complexities of modern designs at this stage, some form of hierarchical simulation will most likely be needed. A small part of the system will be modeled in great detail and interfaced with higher-level simulations of the remainder of the system. This will require a clean interface between the higher-level and the lower-level simulation tools. Reliability models will also need to be refined to reflect the more detailed information. Simulation results such as coverage factors, recovery times, etc., need to be easily transferred from the simulation program to the reliability analysis program. Again, integration is needed.

At the test, implementation, and validation review, the results of experiments performed on the prototype should be presented. The reliability modeling tool should have predicted a behavior of the system that can be verified by actual injection experiments. The modeling and simulation tools should be interfaced with the testbed so that the required inputs to the testbed can be generated automatically and the outputs compared with those predicted by the simulations.

Given this methodology framework and its reliance on tools to support design and produce deliverables for the design reviews, a tools/methodology task was included in the DAHPHRS program. The objectives of this task were to show how the use of performance and reliability tools within such a methodology framework can support the design process and to identify the interactions between the performance and reliability analyses. The tools/methodology task benefited from actual evaluations of architectures and algorithms using currently available performance and reliability tools. These evaluations produced a number of observations concerning the capabilities of tools for the performance and reliability analysis of multiprocessor architectures. In particular, by addressing the question of what information (level/resolution) is required to ensure that the fidelity of the analysis is adequate and that desirable system configurations are not precluded from consideration, it has become evident that distinct computing paradigms require distinct simulation paradigms. For example, tightly coupled architectures require different modeling techniques from those that are suitable for loosely coupled multiprocessor architectures. It also became clear in the course of this effort that a number of tools are necessary for managing the complexity of the simulation of the designs. The need to establish the accuracy of the simulation results also arose along with a recommended approach for doing so. Validation of results is especially important in critical applications.

#### 2.1. Performance Models and Tools

The role of performance models and tools in support of the methodology was investigated through performance analyses of the paradigm algorithms and architectures. These analyses illustrate the roles of measurement, functional simulation, and stochastic methods in support of modeling. Two fundamental issues are the validation of models and the selection of an appropriate level (fidelity) of modeling. The appropriate level depends both on the information required to build the model versus the information available and on the amount of data that can be derived from the model versus its reliability and usefulness. The analyses also identified additional tool needs.

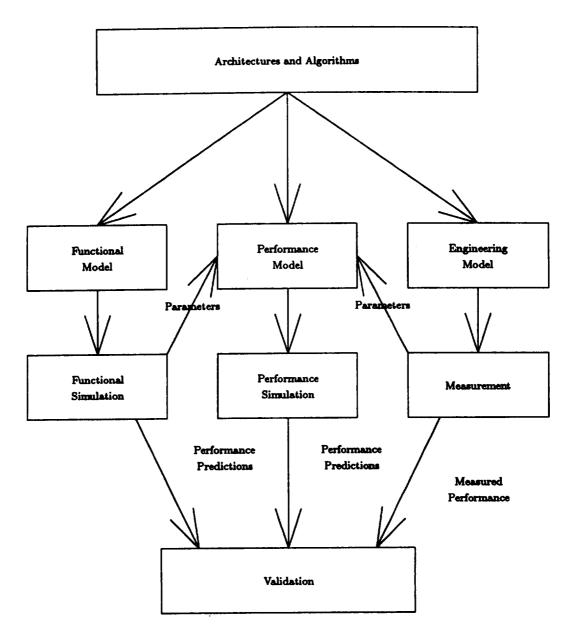

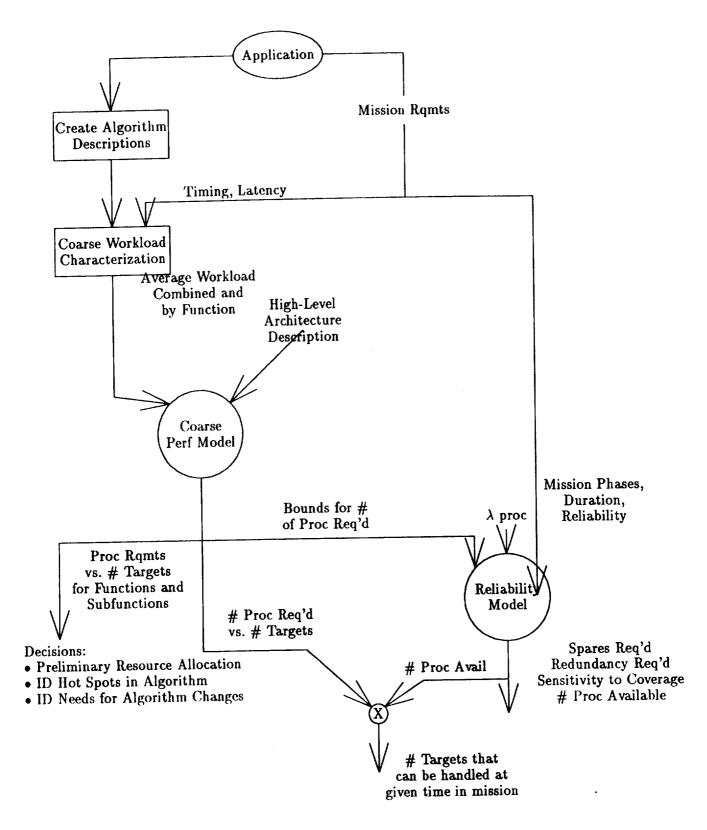

System performance should be modeled by multiple models of increasing detail and complexity consistent with the amount of information available at particular design stages. Also, as the performance analyses conducted by Honeywell for the Encore Multimax and the JPL Hypercube demonstrate, the resolution required in a performance model also depends on the architecture. Consequently, the methodology requires a decision as to what level of model is needed to support the required granularity of simulation for a given architecture at a given design phase. At the highest level, the system is modeled by an analytical model using primitive information such as processing and communication workloads for the algorithms and processors and IO and memory bandwidths for the architecture. As the hardware and software of the system are defined in more detail, performance modeling by simulation and engineering models can be initiated. The performance modeling process, as illustrated in Figure 2.1, starts with a description of the architectures and algorithms that make up the system. From this description, the functional, performance, and engineering models can be developed.

The performance model is the essential system model, consisting of a data/control flow model of the algorithmic processes which has been mapped, or constrained, to a structural model of the architecture. A functional model can be built which describes the behavior of either the components of the architecture or the algorithms that will be executed by the system. Finally, the engineering model consists of system prototypes for the algorithms and/or architectures. All three models produce performance predictions, the functional and performance models through simulation and the engi-

Figure 2.1. Performance Modeling Process

neering model through measurement. The three models interact through parameter values computed by the functional and engineering models for use by the performance model. Each of the models can be built to whatever degree of detail is reasonable for the stage of design under consideration, and the cross-validation that occurs among the models as they produce consistent performance assessments allows the models to be used and built upon with confidence at subsequent levels. Thus, performance models that have been built from and validated by measurements from engineering models can be used in later analyses or subsequent system designs without the need for implementing a full engineering model.

The performance and functional models of the paradigm architectures and algorithms were created using the Architecture Design and Assessment System (ADAS). ADAS is a tool developed by RTI for the hierarchical description and assessment of system designs. In ADAS, the system performance model is created from a structural model of the architecture and a data/control flow model of the processes. The structural model, or ADAS hardware graph, is a directed graph comprising nodes to describe the architectural components and arcs to describe the connectivity among components. Attached to each node and arc of the graph are attributes which become constraints in the performance model based on the construction of a mapping from the structural model to the algorithm model. The algorithm model, or ADAS software graph, is a directed graph describing the data/control flows (arcs) of the software processes (nodes) in the system. Its attributes define the required computing and communication resources and control the assignment of software components to hardware components. The constrained software graph created by the construction of a mapping and containing processing times defined by the attributes of both graphs becomes the ADAS performance model. This performance model can be simulated by the ADAS tool GIPSIM to predict the performance of the software processes on the architecture for that mapping and thereby predict whether the system will attain its throughput requirements. In ADAS, a CSIM functional simulation model can also be constructed to simulate the function of software processes (such as the application algorithms and, as was done by VPI, reconfiguration algorithms) or the detailed operations and interactions of the system components (as was done by Honeywell for the Multimax model).

Recent modifications to ADAS will make it easier to explore the large experiment space inherent in the design of parallel and fault-tolerant systems. An Attribute Definition Language (ADL) and ADL Evaluator (ADLEVAL) have been developed for the creation of parameterized performance models. ADL expressions describe the performance model attributes in terms of system parameters. These expressions are associated with ADAS nodes, arcs, and graphs, and are translated into ADAS

attributes by ADLEVAL. Also, the ADL expressions can be inherited and synthesized throughout the hierarchy of graphs that describe the system so, for example, processor instruction processing speeds, memory and interconnect bandwidths, and mission parameters can be included in an ADL file at the root graph and be accessed at all subsequent graph levels. A prototype ADL and ADLEVAL were used in this study and, as a result, modifications to the ADL specifications and their implementation were identified that provide more flexible parameterization and facilitate modeling more complex systems.

The Graph Transformation System (GTS) is a rule-driven tool that aids the user in customizing software to fit system constraints, including the capabilities of available hardware resources and the processing requirements of other algorithms that are part of the system model. The transformation rule base is a set of ADAS graphs, each of which describes the patterns and transforms of a coexistent set of rules designed to transform an algorithm to improve its fit with the system constraints, without changing its function. Transformations can be used to increase or decrease parallelism, to insert fault-tolerant features into an algorithm, to represent the cost of communications delays, or to eliminate unnecessarily redundant operations from an algorithm's description.

In addition to the ADAS performance and functional models, an engineering model of the WAUCTION\_ASSIGNMENT algorithm was constructed from available engineering code. This engineering model was used to measure expected system performance as well as to provide parameters for the performance model. It is especially important that measurements and statistical data be produced to derive the parameters of simulation models of mission planning algorithms, since the control flow and iterative structure of such algorithms is highly data and mission parameter dependent. It is also necessary for these algorithms that stochastic model attributes can be specified and utilized in performance simulation.

The complexity and size of the systems under consideration are certainly at the stress limits for the existing tools for both model creation and simulation. A considerable amount of effort was required to create the algorithm models. This effort highlights the need for automatic generation of models from system and requirements descriptions, such as those developed by CASE tools. It also highlights the need for a library of models of functions common to a wide class of algorithms, such as sorting and linear programming constructs. Since parameterized function models can be built to a high level of detail independent of any architecture, they can contain a higher degree of information than those that were built for this study. Thus, when a library of function models exists, the individual models can be used to build an application-specific

model of greater resolution than would be feasible by constructing the model from scratch.

#### 2.2. Reliability Models and Tools

The role of reliability models and tools in support of the methodology was investigated through reliability analyses of the paradigm architectures. Since the major emphasis on fault tolerance will occur in Phase II, a selection of preliminary reliability analyses were undertaken in this phase. These preliminary analyses highlighted the reductions of large models, particularly the creation of approximate models to bound the exact model of a complex system; the use of tools to document and provide verification of the models; and additional tool needs.

The high system reliability requirements that exist for an application critical to a long space mission can only be met by a system designed to be fault-tolerant. Such a system has to be carefully evaluated to determine whether or not the reliability requirements are met. However, the existence of fault tolerance mechanisms makes that evaluation more difficult by increasing the number and complexity of significant factors affecting system reliability. Thus, the ideal reliability modeling tools will have to handle very large, complex systems; analyze complex processor intercommunication networks; handle permanent, transient, and intermittent faults; accommodate time-variable failure rates; allow system starting states other than zero failures with unity probability; model complex fault recovery processes; allow for cool spares with reduced failure rates until activated; handle time sequence dependencies between certain faults; and allow for multiple near-coincident faults.

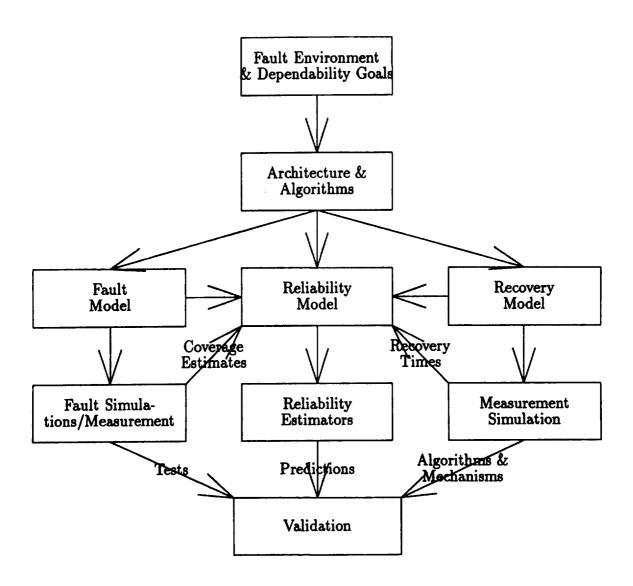

As with system performance, system reliability should be assessed by multiple models of increasing detail and complexity within an overall framework. The reliability modeling process, as illustrated in Figure 2.2, starts with a specification of the fault environment within which the system will operate and of the goals for the dependable performance of the system. System models are then created from a description of the architectures and algorithms that comprise the system. The reliability model describes the behavior of the system in response to the occurrence of faults and is used to predict the probability that the system will be operating correctly at a given time. The fault and recovery models describe the mechanisms by which the system detects faults and isolates and recovers from them. These models are used to predict the effectiveness of these mechanisms and to derive measures of parameters used in the reliability model. Each of the system models can be built to whatever degree of detail

Figure 2.2. Reliability Modeling Process

is reasonable for the stage of design under consideration. However, as the fault and recovery models become more detailed, the parameters of the reliability model can be specified more accurately. When engineering prototypes of the system have been developed, measurements of the fault detection, isolation, and recovery parameters can be made and used to validate the models of the mechanisms for future use.

Two common techniques for reliability analysis are fault tree analysis and Markov modeling. Although the creation of fault tree models is straightforward and tools to solve them exist, such as the NASA-LaRC Fault Tree Compiler [11], they can only be used to describe fault-occurrence behavior. However, for a system to be able to attain the ultrareliability required for mission-and life-critical applications, it must have some fault handling capability and would probably incorporate dynamic reconfiguration. In fact, the fault handling mechanisms can become the most important factor in system reliability for short missions or for particular mission phases. Therefore, tools such as ARIES [12] have been developed based on finite-state, continuous-parameter Markov processes. Since in a Markov model system behavior is described by transitions among operational and failure states, reconfiguration is easily modeled.

The fault-handling recovery mechanisms that are usually represented by a transition rate parameter in Markov models can be explicitly modeled with the semi-Markov extensions of tools such as CARE III [4]. These extensions allow the inclusion of multiple recovery transitions even though they may occur at rates much faster than the fault occurrence transitions.

The solution of Markov and semi-Markov models is computationally difficult and leads to tools being built around fixed, parameterized fault-handling models with simplifying assumptions that permit a stable and efficient solution [1]. Since a rigid model precludes a tool's use on systems not satisfying all of its assumptions and requires that the user develop an in-depth understanding of the model and its assumptions, attempts to generalize or include multiple models have resulted in tools such as HARP [3].

In addition to handling built-in models, most Markov tools assume fixed, usually exponential, distributions for the transitions. However, the Semi-Markov Unreliability Range Estimator (SURE) program from NASA-LaRC [5], can solve models with slow, exponential fault arrival transitions and arbitrary recovery transitions, as long as the fast transitions are several orders of magnitude faster than the slow ones. SURE is fast and accurate for these models because it computes upper and lower bounds on system death state probabilities based on algebraic properties of the means and variances of recovery times, rather than directly solving the differential/integral equations of the

model.

Markov (including semi-Markov) modeling provides a flexible way of describing fault-tolerant systems, and tools exist to compute solutions of the models. However, since the Markov state descriptions increase rapidly with system size and complexity and the solutions are computationally difficult, tools that are based on Markov models have inherent limitations. In general, since highly-reliable, high performance systems result in large, sequence-dependent models, no current reliability analysis tool can address all of the complex interactions of such systems. Even if the underlying model is flexible enough to describe the system, the complete model would be too large to be solved. Furthermore, no tools exist to assess the reliability of the complex multiprocessor networks found in these systems.

Independent of any tool's ability to compute a solution for a particular model, the creation and validation of a correct reliability model is difficult. Thus it is important to have a tool such as the Abstract Semi-Markov Specification Interface to the SURE Tool (ASSIST) [8] that can create a parameterized model from a program language description of the system's fault occurrence and handling behavior. Such a tool not only facilitates the creation and subsequent modification of large models, but also provides documentation for the model and a means of communicating a system's fault tolerance description among different staff and phases of the development process.

Any methodology for reliability analysis has to include facilities for tracking the system requirements through some conceptual reliability model to actual and analyzable approximate models. This suggests exploring methods for the systematic creation of a complete reliability model from the system description to which reduction techniques can be applied to produce analyzable models. A technique for generating a model based on the system description could start with the definition of system failure in terms of software module failure. Module failure would in turn be defined in terms of processor failure, based on the software to hardware mapping. Ultimately, processor failure is defined in terms of hardware component failure, such as the CPU, memory, and interconnections.

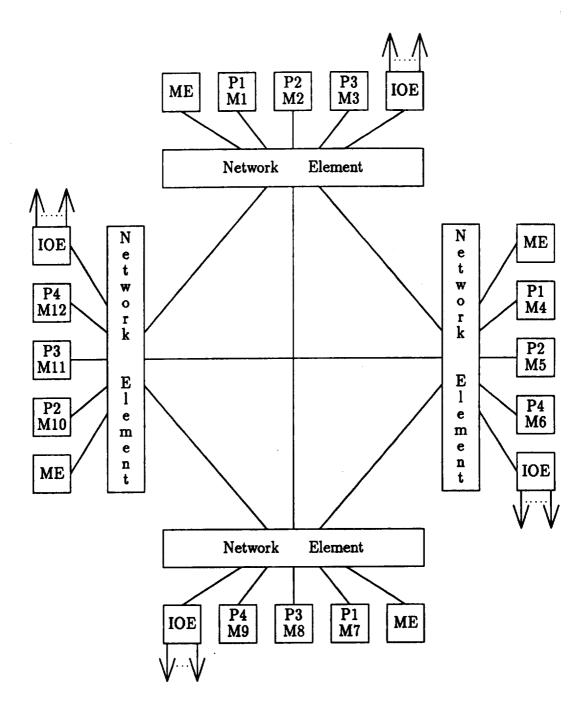

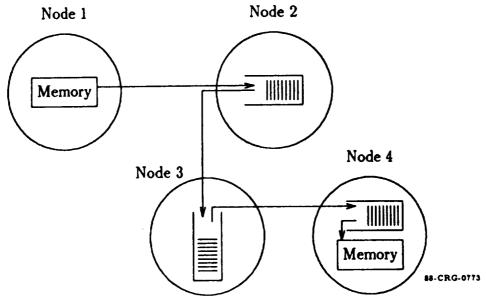

As an example of the construction of such a model, consider a system where system failure is defined as the failure of 4 processes. Each process consists of 3 redundant modules and is considered to have failed if any 2 of its 3 modules fail. A module fails if the Processing Element (PE) that it is mapped to fails. A PE fails if either its CPU or its Network Element (NE) connection fails. If an NE fails, then all PEs connected to it fail. An NE fails if either its CPU or any of its cluster connections fail. Figure 2.3 shows the mapping of such a system to the FTPP cluster. In this

figure, the processors that comprise each of the four TMR's are labeled as P1, P2, P3, or P4. Each of the four processes are mapped to a distinct TMR. For example, process module M1 and its redundant modules M4 and M7 are mapped to TMR P1. The ASSIST code to describe the system and generate the Markov description of the system is listed in Figure 2.4.

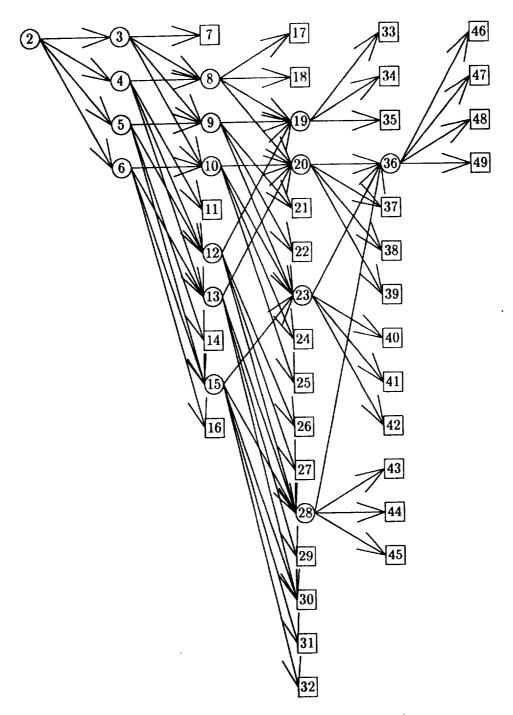

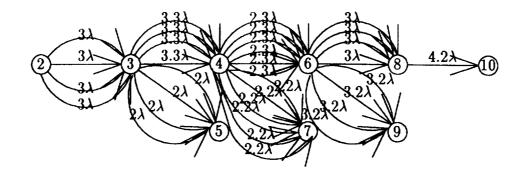

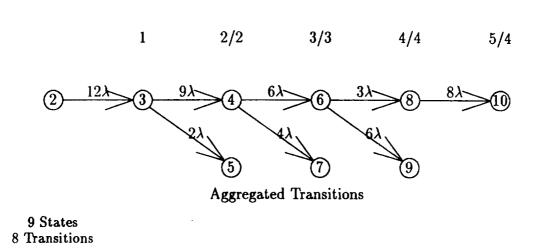

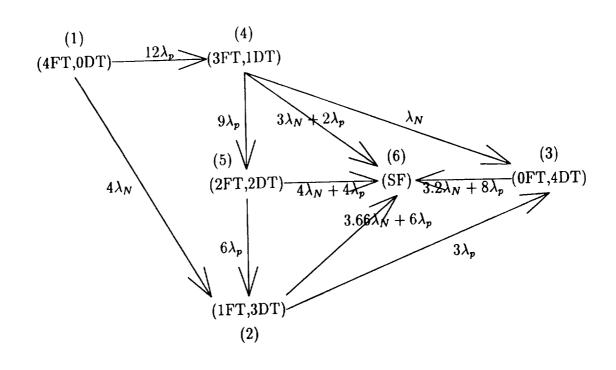

Since the systematic creation of reliability models of complex systems will result in large models, reduction techniques that can be applied to produce analyzable models are needed. One technique is to bound the reliability of the complete system by that of an approximate system. An optimistic bounding model can be built by relaxing constraints on reconfiguration and eliminating some of the degrading transitions. A pessimistic, or conservative, model can be built by limiting reconfiguration possibilities and by creating some degrading transitions. For example, a mapping of the complete model of the above example to a reduced, conservative model can be constructed by aggregating all states where the number of failed modules per process is the same and combining redundant transitions. A Markov description of the complete model contains 260 states, 3312 transitions and 2434 death states (aggregated into 4 death states); the reduced model, 17 states, 128 transitions, and 98 death states (aggregated into 1 death state). While the complete model of this example is not necessarily too large to solve, it illustrates how model size can be significantly reduced.

#### 2.3. Integrated Performance and Reliability Tools

The performance and reliability of a system that must be both fault tolerant and capable of high throughput cannot be accurately gauged independently. A system's fault tolerance mechanisms must be included in the system performance analysis as well as in the reliability analysis since they not only require significant processing resources, but have to be executed within strict timing constraints. Furthermore, the definition of what constitutes an operational versus a failed system state for reliability has to be derived from an assessment of the ability of the system in that state to achieve the required performance levels. Another level of interaction is required when embedding applications into a parallel system since the fault tolerance mechanisms affect the partitioning of tasks. For example, the task granularity that gives the best computational performance may not be optimum for systems where rollback is used for error recovery.

The goal of integrated performance and reliability analysis tools is to provide consis-

Figure 2.3. Process to FTPP Cluster Mapping

```

n_nes = 4; (* Number of Network Elements (NEs) *)

n_processes = 4;(* total number of processes in the system *)

redundancy = 3;

(* number of redundant modules per process *)

n_modules = n_processes + redundancy;

1_con = 1e-7; (* failure rate of interconnections *)

l_vote = ie-6; (* failure rate of voters *)

l_cpu = 1e-5; (* failure rate of processors *)

1_pe = 1_cpu + 1_con;

l_ne = l_vote + (n_nes-1)*l_con;

space = (m: array[i..n_modules] of 0..1);

start = (n_modules of 1);

(* transitions due to processor failure *)

(* each processor services exactly one module *)

for j=1,n_modules

if m[j] > 0 tranto m[j] = 0 by l_pe;

endfor:

(* transitions due to fault containment region failures *)

if m[1] + m[2] + m[3] > 0

tranto m[1] = 0, m[2] = 0, m[3] = 0 by l_ne;

if m[4] + m[5] + m[6] > 0

tranto m[4] = 0, m[5] = 0, m[6] = 0 by l_ne;

if m[7] + m[8] + m[9] > 0

tranto m[7] = 0, m[8] = 0, m[9] = 0 by l_ne;

if m[10] + m[11] + m[12] > 0

tranto m[10] = 0, m[11] = 0, m[12] = 0 by l_ne;

(* death states are defined *)

(* by the mapping of algorithm modules to processors *)

(* and by the grouping of modules into processes *)

deathif m[1] + m[4] + m[7] < 2

(* process 1 failure *)

deathif m[10] + m[2] + m[5] < 2

(* process 2 failure *)

deathif m[8] + m[11] + m[3] < 2

(* process 3 failure *)

deathif m[6] + m[9] + m[12] < 2

(* process 4 failure *)

```

Figure 2.4. ASSIST Code

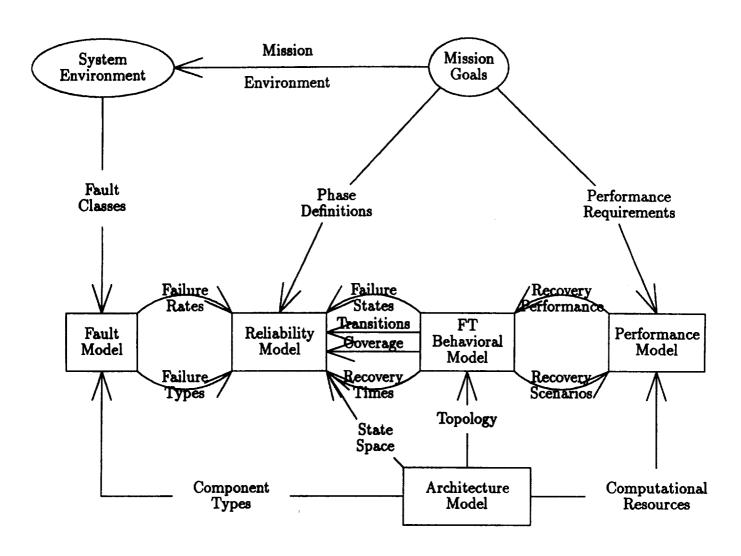

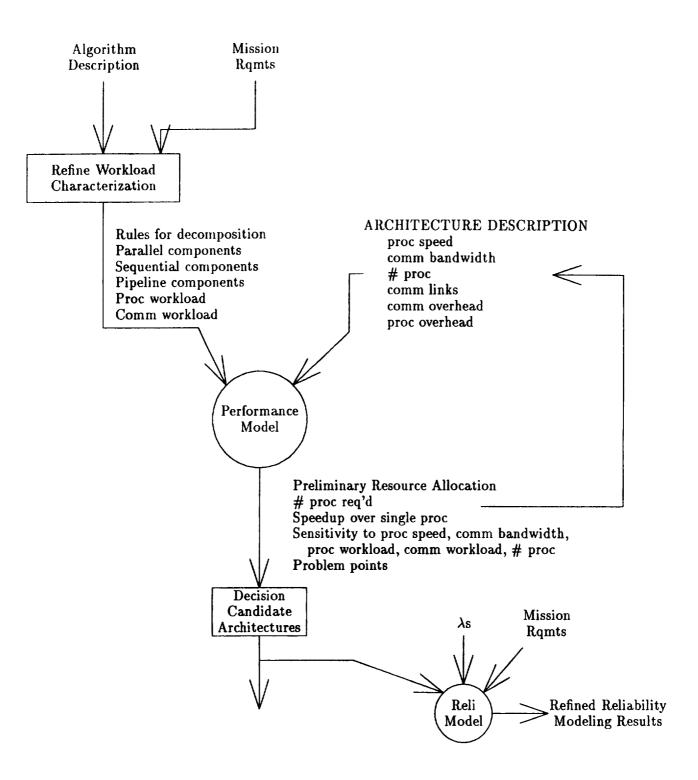

tent performance and reliability models and to facilitate the transfer of data from one model to the other so that through an iterative design process a reasonable trade-off between performance and reliability can be attained. The flow of data among the models is illustrated in Figure 2.5. This data includes the architectural and performance measures that affect reliability model parameters (such as the number and failure rates of components and the system configuration), the network topology, and models of the fault tolerance mechanisms that can be used to assess their impact on performance.

The high-level interactions between the performance and reliability models that need to be studied are those that determine both the minimum number of components, active and spare, and the system configuration required to achieve both the performance and reliability requirements for the system. At a more detailed level, the fault detection, isolation, and reconfiguration (FDIR) parameters such as time and resources required to attain adequate reliability can be measured, and the software-implemented fault tolerance mechanisms such as system reconfiguration algorithms can be evaluated. For example, the reliability analysis may include a coverage model parameter based on the time for execution of an FDIR algorithm. If a performance model of the algorithm exists, its execution time could be obtained from a performance analysis of that model mapped to the target architecture. On the other hand, if a system performance requirement is specified on the basis of an application parameter, such as the number of targets a system should be able to prosecute at a given time during a mission, the reliability analysis could be used to determine the expected number of processors available at that time and a performance analysis could then determine if the required target capacity could be met. Finally, performance/reliability trade-offs can be performed to assess the efficacy of fault-tolerant mechanisms and their effect on system performance, such as a comparison of triplex redundancy versus duplex redundancy with checkpoint/restart with respect to system reliability and performance cost.

Techniques for closer interaction between reliability analysis tools and performance analysis tools will depend upon further work on reliability analysis. In the second phase of this effort, when the fault tolerance mechanisms and algorithms for the paradigm systems will be modeled, the appropriate performance/reliability trade-offs will be conducted. However, in this first phase some examples of preliminary types of analyses were conducted, such as the high-level assessments of the communication costs associated with the FTPP's strategy to achieve Byzantine Resilience (Section 4.3) and a group of analyses to evaluate the performance of alternative reconfiguration procedures (Section 4.7).

Figure 2.5. Data Flow Among Performance and Reliability Models

In addition to enhanced capabilities for performance and reliability analysis, integrated tools would support a design-for-reliability methodology in the areas of experiment planning and documentation for validation. Experiment planning is essential due to the large size of the design space, the use of tools at the limits of their capacity, and the need for regression testing of models. Additional research in experiment planning is needed in the areas of consistency checking and configuration management. Consistency checking has to address ways of assessing that the level of resolution is consistent across all system models and especially that there is consistency of resolution between different input parameters, between simulation time and input parameters, and between input and output. Configuration management policies have to address what consistency checks need to be applied and when they are required, as well as how to support regression testing. Tools for running experiments should allow the user to define the search space, to define the search strategies, and manage the files generated by and for the experiments. They should also support the validation of the models and aid the comparison of results from different runs.

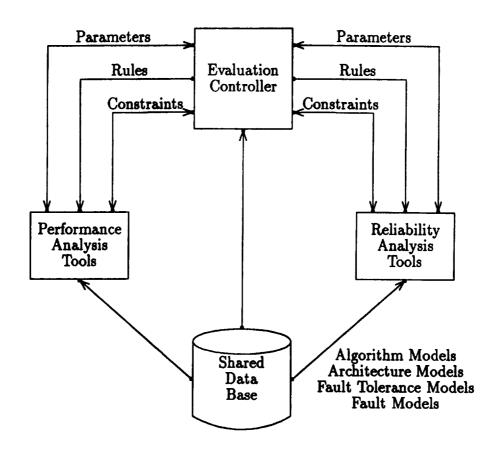

A proposed structure for integrating performance and reliability analysis tools is illustrated in Figure 2.6. This structure would provide a shared data base to facilitate interaction between the models and an evaluation controller to implement the experiment planning and execution functions. In addition to the data required to build the performance and reliability model, the data base would include a library of models of primitive functions that could be used to build algorithm models; rules for the transformation of architecture models to meet requirements of specific applications, to reflect alternate configurations, or to achieve parallelization goals; and rules for mapping algorithms to architectures.

The evaluation controller would control the design and analysis space, maintain consistency among the models, and support model regression testing. To be able to control the design and analysis space, it should support application of appropriate tools at each design and analysis phase, searches of the design space, and pruning of unnecessary analyses. It should provide consistency maintenance through built-in configuration management and consistency verification. Also, since each design change requires some validation that previous constraints have not been violated, the evaluation controller should provide support for regression testing through back annotation and generation of consistent model configurations.

A configuration can be defined as the collection of files which describe and support the analysis of a particular model or of all the models of a system. Many versions of models and the files associated with them result from an iterative and hierarchical approach to design. Thus, it is important that configuration management provide

Figure 2.6. Integrated Performance and Reliability Analysis Tools

access to consistent files for use by the tools. Preliminary requirements for tools to support configuration management are that each file must contain a file version number, each tool must be able to verify that it is processing files for a consistent configuration, and each tool must include configuration information in its outputs. A tool can verify that it is using files from a consistent configuration by building its own configuration, by using a configuration built by the evaluation controller, or by accessing the configuration information in the data base. The configuration data base can be updated by either the evaluation controller or the tool, but consistency checking must be done whenever configurations are defined or modified.

The main issue in the design of the shared data base is the management of the heterogeneous collection of files that results from the many models required to describe and analyze the performance and reliability attributes of a system. Other issues are how to provide common storage for shared data to support both the generation of tool-specific input files and the extraction of parameters from output files and how to incorporate the configuration management facilities of the evaluation controller.

#### 3. Paradigm

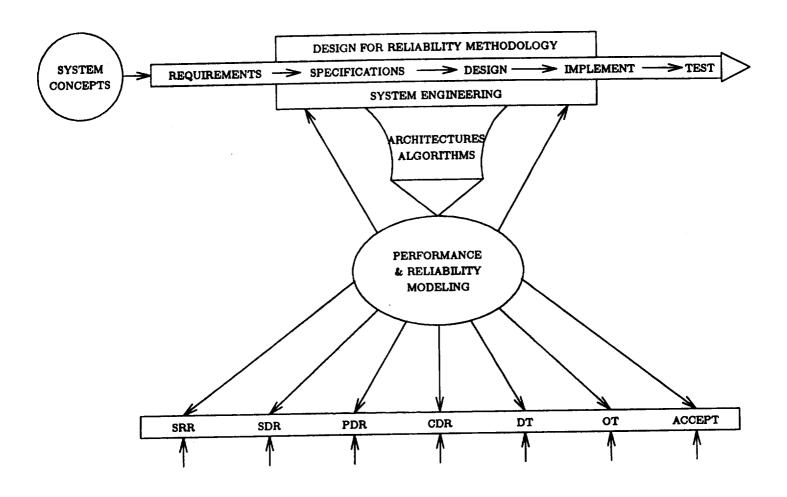

Based on the framework provided by the design for reliability methodology of [13], a paradigm for performance/reliability modeling in support of system development was created, as illustrated in Figure 3.1. In this paradigm, the system development phases from system concept to implementation and test are carried out in the appropriate system engineering domains under the guidelines of the methodology. As architectures and algorithms are developed in this process, performance and reliability tools assist the individual designers in evaluating and changing the designs and in maintaining the consistency of the designs with the overall system requirements and specifications. Selected results from the modeling effort are used to satisfy portions of the requirements for the various development milestones such as design reviews.

Ideally, it would be desirable to exercise the paradigm through the analysis of a complete "SDI-like" system to determine what system models are needed, how the models interact, what experiments and analyses are needed, how tools support the methodology, and what the tool features and capabilities should be. Lacking both the specification of such a system and the funding, it was not possible to exercise and assess all aspects of performance and reliability modeling support for the system development process. Consequently, effort was focused on those facets of the paradigm likely to reveal weaknesses in the existing methods and tools or likely to yield payoffs in the form of refinements to large portions of the methodology. To this end, areas where the characteristics of the complex space mission are distinguished from more ordinary applications were considered of special interest, and two algorithms and three architectures were selected for analysis.

A typical SDI application could have requirements to detect and track potential targets and to allocate weapons necessary to destroy targets. The signal/image processing algorithms that would be employed to provide target detection, classification, tracking, and trajectory estimation are computationally intensive. However, most often they can be decomposed into highly regular computational structures that can be effectively handled by vector and pipeline processing techniques. The optimal allocation of weapon resources to targets requires the use of algorithms that differ significantly from signal/image processing algorithms. These mission planning functions employ linear, integer, nonlinear, or dynamic programming techniques which have computational requirements that are dependent upon the incoming target data and that vary with the number of targets. These algorithms are more difficult to decompose and embed in a parallel computing architecture, and were therefore judged to be of particular interest for this effort. Two mission planning algorithms were

**DEVELOPMENT MILESTONES**

Figure 3.1. Paradigm for Performance/Reliability Modeling in Support of System Development

selected and used in this study. These algorithms are discussed in Section 3.1.

Meeting the demanding throughput requirements of such applications will require advanced architectures consisting of a large number of interconnected processors or computers. Of the various parallel computing architectures that have been proposed, three were selected for use in this study. The JPL Hypercube, an MIMD distributed memory architecture, was selected primarily because the hypercube is one of the most extensively investigated parallel computing architectures. The Encore Multimax, an MIMD shared memory architecture, was selected to provide contrast to the hypercube particularly in the area of interprocessor communications. Finally, the Charles Stark Draper Labs Fault-Tolerant Parallel Processor (FTPP) was selected because it is the only parallel processing architecture which has the advanced fault-tolerant features necessary to attain very high reliability. As such, modeling for the FTPP is distinguished from ordinary parallel processor modeling and should be expected to provide insight into weaknesses in the methods and tools as they pertain to high reliability applications. These architectures are discussed in Section 3.2.

An important aspect of the paradigm is the information required to carry out the modeling for various stages of the design process. As part of this study, an audit of the information used to construct the various models was conducted. This information is discussed in Section 3.1, Algorithms, and Section 3.2, Architectures.

#### 3.1. Algorithms

The algorithms selected for the paradigm are two mission planning algorithms developed by Alphatech, Inc. The first algorithm solves the weapon-target assignment and target sequencing decision problem by breaking it into a four-level optimization problem [16]; the second, by conducting an auction among the targets for the available weapons [16].

## 3.1.1. Algorithm 1: Weapon to Target Assignment and Target Sequencing (WTA/TS)

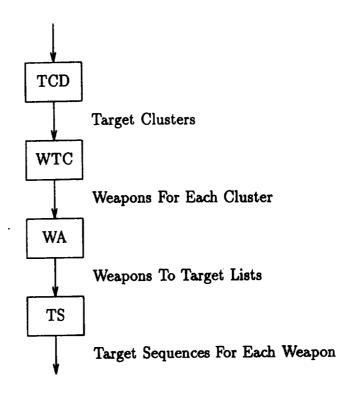

This algorithm is directed toward the optimal assignment of space-based Directed Energy Weapons to multiple hostile boosters [16]. It solves this optimization problem by partitioning into four subproblems that can be solved iteratively. WTA/TS

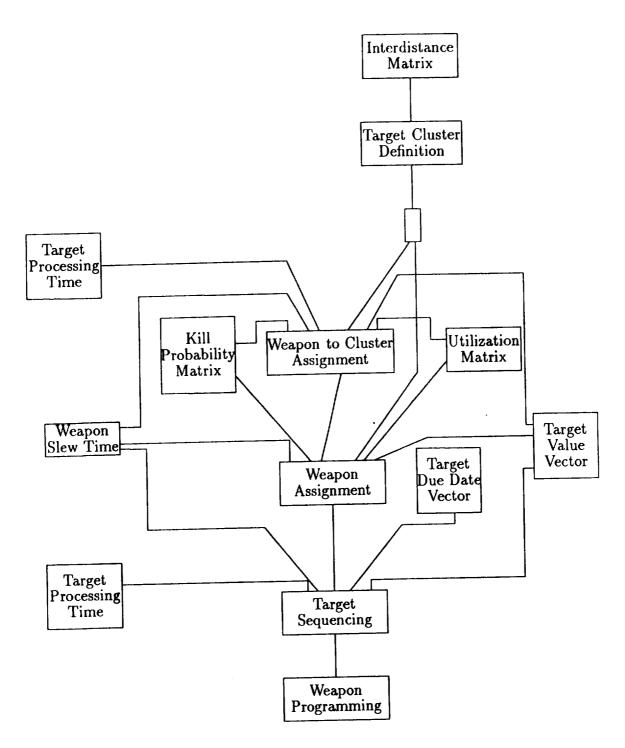

Figure 3.2. WTA/TS Data Flow Diagram

consists of four component functions corresponding to the four subproblems: target cluster definition (TCD), weapon-target cluster allocation (WTC), weapon to target assignment (WA), and target sequencing (TS). Figure 3.2 shows the major data flows among the WTA/TS functions.

The input parameters that control the size of the problem are the number N of targets, the number W of weapons, the number C of clusters to be formed, and the degree R of redundancy for weapon assignment. Other external inputs include the  $N \times N$  target interdistance matrix, the  $N \times W$  kill probability matrix, the  $N \times W$  weapon slew time matrix, the  $N \times W$  utilization matrix, the  $N \times W$  target processing time matrix, the vector of N target due dates, the vector of N target values, the vector of N target processing times, the time start for the planning frame, and the time start for a new launch. Each of the WTA/TS functions is summarized below.

TCD: The target cluster definition function assigns targets to clusters based on intertarget distance. It seeks to optimize Q = F [intertarget distance], where each target is in one and only one cluster. The optimization problem is an integer (0/1) programming problem solved using LaGrange multipliers and a subgradient iterative

algorithm.

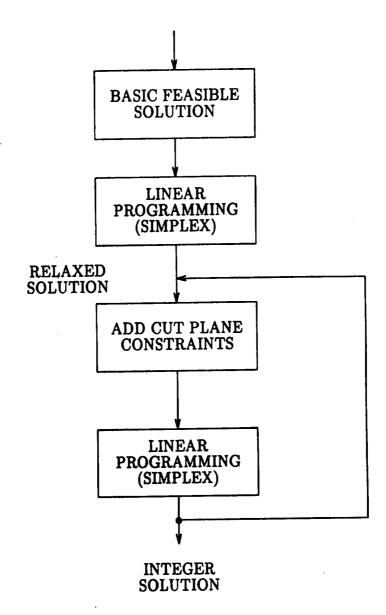

WTC: The weapon-target cluster allocation function balances the cluster allocation load across weapons, assigning multiple weapons to each cluster of targets. It seeks to optimize

$$Q = F[kill\ prob, target\ value, weapon\ use, reassign\ cost]$$

where a cluster is assigned to at least  $R_k$  weapons. The optimization problem is solved by breaking it into subproblems. The first subproblem is defined to be

$$Q_1 = \sum_{cluster} MIN F[killprob, targetvalue, reassigncost, use, LaGrange]$$

and solved as multiple integer programming problems. The general integer programming solution is illustrated in Figure 3.3.

The second subproblem is defined to be

$$Q_2 = F[Use, LaGrange]$$

and solved as simple scalar.

The two subproblems combine as  $Q_1 + Q_2$  with

$$Max [Q_1[M] + Q_2[M]]$$

being solved via a subgradient method.

WA: The weapon-to-target assignment function assigns weapons to targets within a cluster based on kill probability, time required to switch from target to target, and the value of the target. It seeks to optimize

$$Q = F[killprob, switchtime, targetvalue, weapon]$$

for each cluster, where at least one weapon is assigned to each target. This problem is solved similar to the weapon to target cluster allocation problem.

TS: The target sequencing function establishes an optimum firing sequence for the list of targets assigned to each weapon. It seeks to optimize

$$Q = F\left[targetvalue, duedate, proctime, switchtime\right]$$

Seven suboptimal algorithms are under consideration for this function; these algorithms use dynamic programming concepts and two use heuristics.

Figure 3.3. General Integer Programming Solution

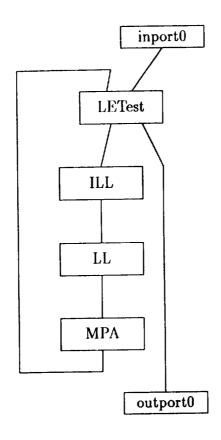

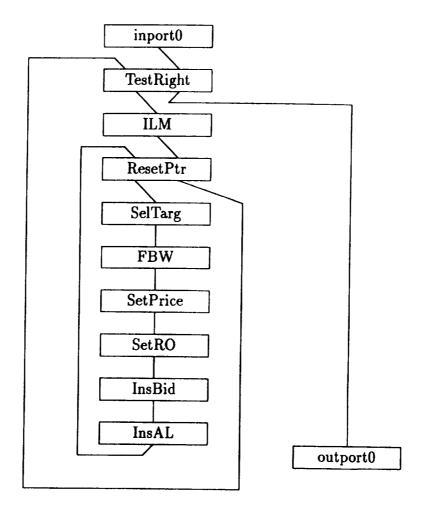

#### 3.1.2. WAUCTION\_ASSIGNMENT

The WAUCTION\_ASSIGNMENT algorithm is a target-oriented weapon-to-target assignment algorithm with the objective of minimizing the expected value of surviving targets [16]. ALPHATECH's solution to this non-linear, NP-complete problem is Iterative Linear Network programming (ILINE), which approximates the non-linear problem iteratively with a linear one [16]. Their formulation of ILINE is as follows:

Step 0: Initialize for all targets and weapons:

$$x^{p_{i,j}} \leftarrow 0$$

(the number of interceptors permanently assigned from weapon j to target i)

Step 1: Solve the linear programming problem:

$$\begin{aligned} \max_{x_{i,j}} \sum_{i} \sum_{j} v_i p_{i,j} x_{i,j} \\ \sum_{i} x_{i,j} &\leq m_j \text{ for every weapon } j \\ \sum_{i} x_{i,j} &\leq 1 \text{ for every target } i \end{aligned}$$

- Step 2: Locate the weapon-target pair  $j^*$ ,  $i^*$  yielding the largest value of  $(v_i \cdot p_{i,j} \cdot x_{i,j})$  from the LP solution.

- Step 3: Update the permanent assignments, weapon capacity, and target value; check for termination:

$$x^{p_i \bullet_{,j} \bullet} \leftarrow x^{p_i \bullet_{,j} \bullet} + 1$$

$$n_{j \bullet} \leftarrow n_{j \bullet} - 1$$

$$v_{i \bullet} \leftarrow v_{i \bullet} (1 - p_{i \bullet_{,j} \bullet})$$

Stop if all interceptors from all weapons have been allocated.

Otherwise, return to Step 1.

WAUCTION\_ASSIGNMENT implements ILINE using a modified auction strategy to produce the linear programming solution in Step 1. This auction strategy is based on the auction algorithm developed by Bertsekas [16]. The weapons, targets, and the feasible matchings between them form a network. Initial values are assigned to each target and a minimum bid increment is specified. Cycles of bidding in which targets bid for weapons alternate with assignment phases. The initial value of a target is updated to an expected value after the target is assigned to a weapon. These expected values are computed as the product of target value and the kill probability of the weapontarget pair. The bidding phases along with the assignment of expected values and the specified minimum bid increments allow alternative weapon-target assignments to be considered, thus increasing the optimality of the solution. The bidding-assignment phases are conducted iteratively within an outer, non-linear iteration until all interceptors from all weapons have been allocated to targets and the targets of greatest value have been assigned. The inputs to the WAUCTION\_ASSIGNMENT algorithm are the number of weapons, number of targets, number of assignments to be made per iteration, the bid scaling constant, the kill probability matrix, the initial target values, the number of interceptors per weapon, and the minimum kill value threshold. The outputs from the algorithm are the assignment matrix of number of shots per weapon i assigned to target j and the expected surviving value of each target. A data flow graph of WAUCTION\_ASSIGNMENT is shown in Figure 3.4.

#### 3.2. Architectures

The primary goal of this research is to determine the nature and requirements of system engineering tools for the performance analysis of algorithm/architecture combinations. Since the specific algorithms are "representative", their absolute performance is not by itself of much value. Of greater interest is the structure of the algorithms and the techniques and associated tools used to analyze the target architectures.

In order to increase the coverage of tool and methodology areas of interest, three systems representative of distinct classes of architectures were analyzed. The JPL Mark III Hypercube represents a class of distributed-memory, loosely coupled architectures. A major issue in the design of efficient parallel algorithms for such machines is the minimization of interprocessor communication. Solutions to related problems such as algorithm partitioning, mapping, and scheduling, attempt to achieve this goal. The Encore Multimax represents the class of shared-memory, tightly coupled architectures. One of the principal determinants of machine performance is conflicts in accessing of shared-memory. These conflicts occur because of contention for the

Figure 3.4. WAUCTION\_ASSIGNMENT Data Flow Diagram

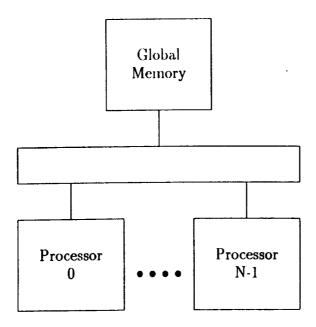

processor-memory bus, or in access to shared variables. Again, solutions to related problems attempt to minimize such access conflicts. The Charles Stark Draper Laboratory Fault-Tolerant Parallel Processor represents the class of architectures designed for fault tolerance. It is a Byzantine Resilient Multiple Instruction stream Multiple Data stream computer designed to produce orders of magnitude more processing power than current highly reliable systems. The fault tolerance mechanisms of this architecture are of particular interest, especially the impact of increased communications requirements on performance.

One of the advantages of choosing fundamentally different types of architectures is the differing demands they will place on the system analysis tools. Let us consider the algorithm representations described in the previous section. Two nodes in this graph that are ready to fire cannot do so if they both require the same resource. In distributed memory architectures, tasks executing on distinct processors utilize separate processor-memory paths. Only tasks (communication nodes) mapped to the same processing element (link or intermediate routing node) are so constrained. Thus, for a given mapping algorithm, the resolution of the simulation can be that of the firing delay of the smallest task. The accuracy of the firing delays themselves can be computed based upon detailed knowledge of the operation counts of the tasks and the architecture of the individual node. Based on these characteristics, the GIPSIM utility of ADAS is suitable to analyze the performance of the Mark III Hypercube.

By definition, processors in bus-based shared-memory architectures require access to a shared resource on potentially every instruction execution cycle. The execution of every instruction competes with each other since they all require the use of the global bus for memory access. Multiple processors can also conflict on every cycle in the access to shared memory. Thus, these architectures are very dependent upon the mapping of (shared) data structures into the memory modules. Furthermore, memory modules tend to be heavily interleaved to match the processor/bus bandwidth. The normal approach to achieving high simulation resolution is to map tasks to processors and all communication nodes to the bus, essentially serializing all communication. However, most architectures use some form of a cache to alleviate the processor/bus/memory bottleneck. The performance depends very heavily on the use of the cache. In the case of the Encore Multimax, modeling is further complicated by the fact that pairs of processors share access to a single cache. Cache coherency control adds to the memory traffic in a non-trivial way and must be a part of the analysis. The interactions between the processor, cache, bus and memory are at the level of the fastest device (typically the cache or bus), and this dictates the level of resolution of the simulation. Since phenomenon such as cache hit rates and bus arbitration are generally non-deterministic, an approach to simulation must enable behavioral modeling while explicitly preserving the structure of the architecture. Therefore, the CSIM facility of ADAS is required to attain the necessary simulation resolution.

To summarize, the simulation resolution that can be achieved depends upon the granularity of parallelism being modeled. High-level resolution simulations are possible for loosely coupled systems, and a relatively simpler, purely structural simulation, is possible (GIPSIM). For modeling tightly coupled, fine-grained architectures, one needs low-level simulation resolution. Furthermore, the introduction of a non-deterministic phenomena such as cache operation requires the capability for modeling stochastic behavior (CSIM).

## 3.2.1. JPL Mark III Hypercube

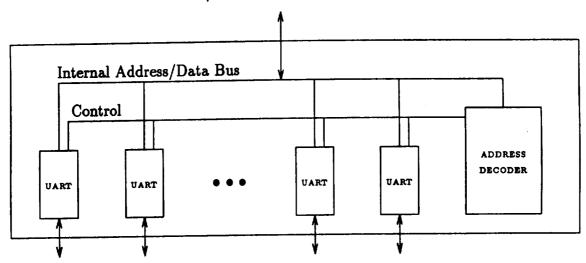

A binary k-cube of  $P = 2^k$  processing elements (PE) is arranged as a  $p = log_2P$  dimensional hypercube. Each processing element is represented by a binary address  $p_{n-1}p_{n-2},...,p_1p_0$ , and is connected to all processing elements whose address differs from it in exactly one bit, i.e.,  $p_{n-1}p_{n-2},...,\overline{p_i},...,p_1p_0$ , for all *i*. The topology of a sixteen-node hypercube is shown in Figure 3.5. The architecture of each hypercube node or PE is illustrated in Figure 3.6. The node architecture is comprised of three basic blocks: the communication processor, the data processor, and the floating point array processor.

The communication processor (CP) is a 32 bit MC68020 and is dedicated to handling interprocessor communication and node I/O. Each node is interconnected to its neighbors by channels. Associated with each channel is a 64-byte buffer. Interprocessor communication is achieved by reading/writing the channel buffers as 64-byte packets. Thus, if processing element 1 in Figure 3.5 is to send a packet of data to processing element 0, a packet of data is transferred from the memory of PE 1 to the input buffer of PE 0 on the appropriate channel. This sequence is repeated several times for multipacket transfers. When transferring data from local memory to a channel buffer (or vice-versa) the CP has higher priority access to local memory than the data processor, and the latter stalls. The CP static RAM holds the node operating system which is responsible for interprocessor communication and synchronization. On receiving a packet in one of its buffers, the CP checks the destination. If it is local, it is transferred to local memory. If it is not, it is transferred to a buffer on the appropriate channel as defined in its destination or routing tag. Thus the three modes of data (or equivalently, packet) motion the CP is responsible for are local-memory-to-channelbuffer, channel-buffer-to-channel-buffer, and channel-buffer-to-local-memory. These are the modeling parameters of interest.

Figure 3.5. 16 Node Binary Hypercube

The data processor is also a MC68020 and operates with the MC68851 conventional memory management unit and a MC68881/2 floating point co-processor. In addition, there is an array processing unit built around a 30 Mflop Weitek chip set. This processor runs as a slave to the data processor. The modeling parameters of interest are the interrupt latency to respond to the presence of a message, the speed of the processor, the speed of the array processor, and the memory access latency.

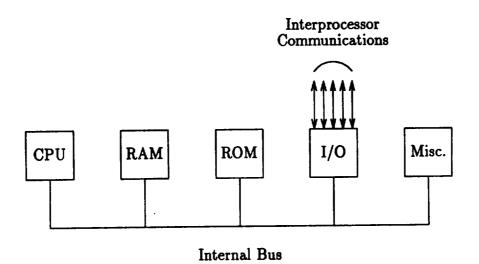

# 3.2.2. Encore Multimax

The Encore Multimax is a shared memory tightly coupled multiprocessor architecture. The overall organization is illustrated in Figure 3.7. The principal components are the Dual Processor Card (DPC), the Shared Memory Card (SMC), and the System Control Card (SCC). The remaining components are not of direct interest from the point of view of computing performance. All of the components are configured around the 100 Mbytes/sec nanobus. Current configurations provide up to twenty processors.