NILL

126248 R121

JA1 0125278

1001

¢.

UATA

URRFC L nu

Ű

MAGA-C2-190542)

S S

# AN INVESTIGATION OF ERROR CORRECTING TECHNIQUES FOR OMV DATA

NASA Grant: NAG8-104

## Final Report

September 15, 1992

N93-12634 Submitted to: Uncles NASA/Marshall Space Flight Center Mr. Dave Harris Mr. Reggie Inman Mrs. Lee Ann Thomas EB-33 MSFC, Alabama 35812 a Cu AN INVLSTIGATION  $\boldsymbol{\omega}$ ECHNTUUC Submitted by: ssipp ្លា

Mississippi State University Department of Electrical and Computer Engineering Frank Ingels, Principal Investigator John Fryer, Assistant Investigator P. O. Drawer EE Mississippi State, MS 39762

# AN INVESTIGATION OF ERROR CORRECTING TECHNIQUES FOR OMV DATA

.

NASA Grant: NAG8-104

Final Report

September 15, 1992

Submitted to:

NASA/Marshall Space Flight Center Mr. Dave Harris Mr. Reggie Inman Mrs. Lee Ann Thomas EB-33 MSFC, Alabama 35812

Submitted by:

Mississippi State University Department of Electrical and Computer Engineering Frank Ingels, Principal Investigator John Fryer, Assistant Investigator P. O. Drawer EE Mississippi State, MS 39762

# **REPORTS CONTENTS**

| SECTION          | TITLE                                                                                                                                                            | PAGE               |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 1.0 INTRODUCTION |                                                                                                                                                                  | 3                  |

| ATTACHMENT #1    | Considerations of Testing the OMV System                                                                                                                         | 5                  |

| ATTACHMENT #2    | OMV Class Test Results (First Go Around),<br>Monthly Report, May 12, 1989                                                                                        | 32                 |

| ATTACHMENT #3    | Equivalent System Gain Available From R-S<br>Encoding Versus a Desire to Lower the Power<br>Amplifier From 25 Watts to 20 Watts for OMV,<br>Memo, 27 August 1989 | 58                 |

| ATTACHMENT #4    | Command Word Acceptance/Rejection Rates<br>for OMV, Memo Included in 12 November 1989<br>Monthly Report                                                          | 68                 |

| ATTACHMENT #5    | A Memo Concerning Energy-to-Noise Ratio for<br>the Viterbi-BSC Channel and the Impact of Manchester<br>Coding Loss, Memo. 22 January 1990                        | 89                 |

| ATTACHMENT #6    | Probability of False Polynomial Division<br>Synchronization Using Shortened Cyclic Codes,<br>Included in 16 May 1991 Monthly Report                              | 104                |

| ATTACHMENT #7    |                                                                                                                                                                  | parate<br>nd Cover |

| ATTACHMENT #8    |                                                                                                                                                                  | parate<br>nd Cover |

## 1.0 INTRODUCTION

\*

The grant, NAG8-104, was instituted May 12, 1988, with a first-year funding of \$35,995. A second funding for \$46,145 was awarded on May 12, 1989, and a final funding for \$50,350 was awarded on June 7, 1990. Originally proposed as a three-year grant to study error correcting techniques for OMV, the investigation took several interesting turns due to redirection of the OMV project and then cancellation of the OMV project. After the OMV project was cancelled, the investigation turned toward investigative support of the WISP project. Several no-cost extensions were requested throughout the life of the grant, and the final expiration of the grant is September 1992, some four and a quarter years after the initiation of the grant.

Mississippi State has felt that the no-cost extension allowed a better use of resources and resulted in more effort and hopefully more results for the dollar expenditure for NASA/MSFC. The average cost per year of this grant has been \$29,442, as opposed to the originally proposed average cost per year of \$44,163, yet the work has been steady and at times it was felt to be fruitful.

Whereas the original investigations revolved around studies and simulations of the error protection for the OMV image compression data link, other interesting and related issues were addressed as well, including an analysis of OMV command word acceptance/rejection rates, the OMV transponder lock spin/dock problem, some CCSDS issues relating to OMV and AXAF, testing of AHA/NASA Reed-Solomon ECC chips and Investigation of the Electromagnetic Field Structure in the Space Shuttle Cargo Bay due to the WISP antenna.

Several reports have been delivered during the performance of this grant. In particular, the following reports concerned specific topics and/or present the culmination of work on a topic:

- 1. Considerations of testing the OMV system with Class, Monthly Report, February 12, 1989, Attachment 1.

- 2. OMV Class Test Results (first go around), Monthly Report, May 12, 1989, Attachment 2.

- 3. Equivalent System Gain Available From R-S Encoding Versus a Desire to Lower the Power Amplifier from 25 Watts to 20 Watts for OMV, Memo to L. A. Thomas, 27 August 1989, Attachment 3.

- 4. Command Word Acceptance/Rejection Rates for OMV, Memo to L. A. Thomas, 30 September 1989, and again on 12 November 1989, Attachment 4.

- 5. A memo concerning Energy-to-Noise Ratio for the Viterbi-BSC Channel and the Impact of Manchester Coding Loss, Memo to L. A. Thomas, 22 January 1990, Attachment 5.

- 6. Probability of False Polynomial Division Synchronization Using Shortened Cyclic Codes, Anna Lynn Schauer and Frank M. Ingels, Report to L. A. Thomas, April 1991, (an in-depth analysis extending the work of report two listed above), Attachment 6.

- An Investigation of Error Correcting Techniques for OMV and AXAF (Testing of AHA/ NASA Reed-Solomon ECC Chips), Final Report, John N. Fryer, Ken Lawrence and Frank Ingels, September 28, 1991 (included in November 16, 1991 Quarterly Report). Separate cover.

- 8. A Determination of the Near Field Strengths of the WISP Antenna in the Space Shuttle Orbiter Bay, September, 1992.

While a diverse topic range was covered during the performance of the Grant, the work was interesting, informative, and it was hoped that it was beneficial to NASA/MSFC.

# ATTACHMENT 1

Considerations of Testing the OMV System With Class, Monthly Report, February 12, 1989

### AN INVESTIGATION OF ERROR CORRECTING TECHNIQUES FOR OMV DIGITIZED DATA

NASA GRANT: NAG8-104 QUARTERLY REPORT February 12, 1989

SUBMITTED TO:

Mrs. Lee Ann Thomas Mr. Glenn Parker EB33 NASA/MSFC MSFC, AL 35812 205+544-3662

SUBMITTED BY:

Frank Ingels, Ph.D. Principal Investigator Mississippi State University Mississippi State, MS 39762 601+325-3912

#### 1.0 Work Summary (November 1988 - February 1989)

During the last of October and early November, a three-day meeting of the OMV Video Compression data link design, development and CLASS testing principals was held at NASA/MSFC.

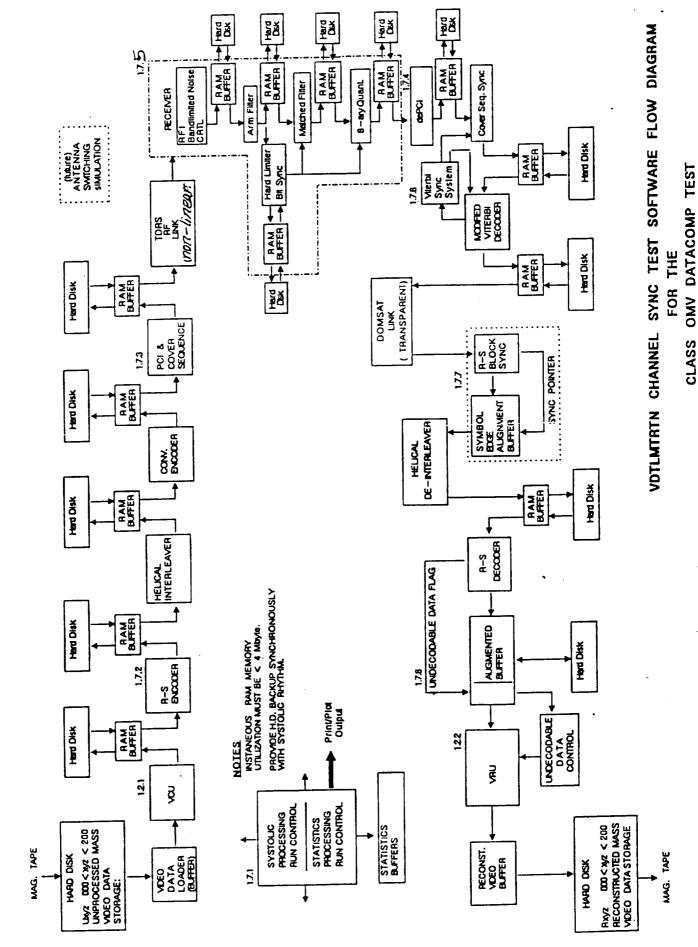

The major topic was the actual hardware concept/design versus software simulation for CLASS testing of the VCU, R-S encoder, helical interleaver, TDRS link (including the convolutional encoder-interleaver and the Viterbi decoder interleaver), R-S decoder and deinterleaver sync and the VRU including subframe replacement.

Fairchild, LinCom, CYCLOTOMICS, TRW, NASA/GSFC and NASA/MSFC were represented at this meeting. Preparation for the meeting included compiling a question list, informing the participants of the need to prepare a briefing and laying out a schedule including time for in-depth discussion of details raised during the briefing. Mrs. Lee Ann Thomas took the lead in the meeting preparation and conduct.

The results were satisfactory in many ways. Details of tape conversions were solved, details in technical operations were uncovered, discussed and agreed upon by all parties. A tentative schedule of procedures to CLASS test was agreed upon, as were the CLASS test requirements and desired data outputs.

In the appendix to this report is a typed copy of the notes taken during this meeting. These notes are not edited but are preserved as taken to serve as a memory aid in recalling the meeting particulars.

Pertinent results of this meeting are noted below:

Hardware is not complete, thus modeling will be as faithful as possible but not 100% accurate. Variable rate buffer finished in strategy is not yet fixed in final design. R-S synchronizer strategy is fixed but final choice of counter presets and thresholds are not fixed.

Until hardware finalized and tested against CLASS with RFI and random errors, the system is not frozen. Hence, software details must be flexible to allow variations.

- 2. Probability of false synch lock in R-S synch strategy is very low. P(of .8 bits of data looking like R-S synch word) =  $2^{-8}$  =  $3.9x10^{-3}$ .

- P(of X consecutive sets of 8 bits of data looking like synch) ~  $(3.9x10)^{X}$ .

Thus, 16 successive sets of 8 bits of data to pass synch thereby making a count of 16 in the threshold counters thereby creating a false synch lock. The probability of this happening is

P(False Synch) =  $(3.9x10^{-3}) = 2.94x10^{-39}$ . For a Viterbi output random error rate of  $10^{-5}$ , the probability of counting up to 16 from a starting count of 0 is

$P(Sync Lock) \sim (1 - 10^{-5})^{8} = .99872.$

For a threshold count of 10 rather than 16, the corresponding probability of false lock and of successively acquiring lock is respectively

P(false lock) =

$$(3.9 \times 10^{-3})^{10} = 8.14 \times 10^{-25}$$

and

$P(sync lock) = (1 - 10^{-5})^8 = .9992.$

Thus, a tradeoff of the false lock probability versus successful synch lock for a threshold setting is illustrated. The threshold setting is not yet determined.

- 3. A standardization of word sending structure (least significant bit first, most significant bit last) was agreed upon. A copy of this structure is appended to this report.

- 4. LinCom and Fairchild apparently worked out most difficulties in transferring code. Not all problems were solved, however. It would be best for Fairchild's computer software programmer to go to LinCom/NASA/GSFC to oversee changes necessary.

- 5. Use of the RS undecodeable flag is not presently incorporated in the VRU.

- 6. A set of test vectors is being constructed for use by Fairchild and LinCom. These test vectors will be used to validate the R-S coder/decoder software.

- 7. Output of CLASS test tape format agreed upon.

- Root polynomial and root used to generate R-S field is to be (has been) provided to LinCom and NASA/MSFC.

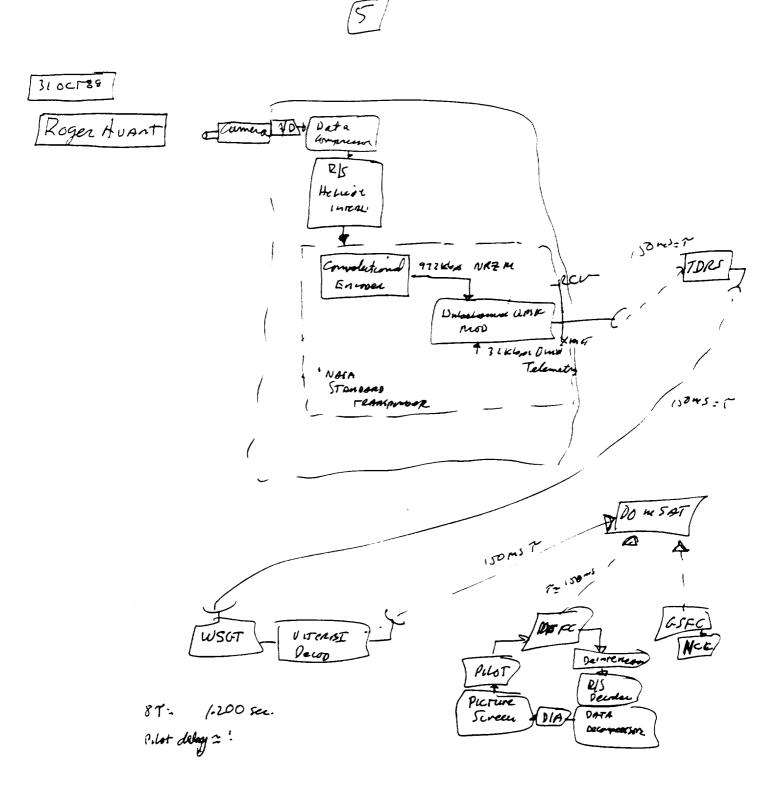

- 9. The functional software flow and functional software construction in modular form provided by LinCom is illustrated in Figure A.1 in the Appendix.

- 10. A list of questions developed for the meeting is attached to this memo.

Since the meeting at MSFC during 30 October 1988 to 2 November 1988, a series of telecons have been held so as to monitor the progress to test data. These telecons have extended through February 1989. A meeting was held in December at NASA MSFC between Lee Ann Thomas, Glenn Parker and Frank Ingels.

Several items were uncovered during the software conversion by LinCom. The non-use of the R-S undecodable flag has been bandied about and to date is not incorporated into the VRU. The channel ID which determines the alternate camera frames was not incorporated into the VRU software. This is being fixed so that two different scenes may be simulated and camera demultiplexing tested during CLASS testing.

A software anomoly in the 4 and 10 bit line subframe replacement was uncovered and is being fixed. It is normal to experience a small boundary disturbance between subframes due to change from 2 dimensional encoding to 1 dimensional encoding.

A new bit rate controller design is to be incorporated into the software. This design takes double the memory of the original design.

Full configuration 1 testing is absolutely recommended. It is necessary to see and study the results of configuration 1 testing before relinquishing this demand. Consistent test results for sync loss and recovery time are the most important guidelines for success of configuration 1 testing. Testing is now scheduled to start in early March, 1989.

### QUESTIONS PREPARED BY MS. LEE ANN THOMAS FOR NOV 88 MEETING

- 1. How is the sync circuit of the R/S modeled? LinCom stated that Cyclotomics has not yet decided on the counter for this circuit; has LinCom allowed for this by using variables as counters?

- 2. What type of RF channel testing is planned for the CLASS test?

- 3. What type of video display and error statistics are being used by LinCom for presenting reconstructed video?

- 4. Does LinCom now have all the data, algorithms and schematics necessary for development of the R/S sync/encoder/decoder/helical interleaver/deinterleaver/bit sync/Viterbi/video subframe sync?

- 5. Does LinCom feel that there is a problem with the 'windowing' scheme necessary for achieving the 24-bit sync word for the video sub-frames? Has this been incorporated into the model?

- 6. What is necessary for interfacing various hardware/software for the test? Who coordinates this effort? What is the status concerning interfaces of the Fairchild code, the LinCom code and the CLASS code?

- 7. How is the flag indicating uncorrectable errors handled by the VRU? Has this been coordinated between Fairchild and LinCom?

- 8. How is the sub-frame replacement handled?

- 9. Exactly what functions does the McIntosh perform? What algorithms/answers are used? Are error characteristics of the burst evaluated at the input of the Viterbi, the output of the Viterbi, and the output of the R/S decoder.

- 10. What steps occur between the VRU software and the actual display of the video?

- 11. Define 'real-time' and discuss how this applies to the OMV CLASS test.

- 12. What are the factors involved in the selection of techniques (why was a burst error generator designed to use for testing instead of using the RF link?

- 13. What is the status of the tape transfer from VAX/VMS to HP/UNIX?

- 14. LinCom stated that they did not have the correct R/S sync word from Cyclotomics. Verify that they have obtained the correct word.

- 15. How is the video sub-frame sync modeled?

- 16. LinCom stated that interfaces must be developed between the bit sync, Viterbi decoder, and the R/S sync. Please define this problem and describe algorithms necessary to obtain these interfaces.

- 17. Define all computers/interfaces necessary to achieve the CLASS test.

- 18. Does the video software model the bit filler/elastic buffer/change of rate?

- 19. Where will the hooks for the CLASS test be located for the VCU, VRU, R/S encoder/decoder, CLASS system?

- 20. Do we have the ability to take a burst hit on every sync (bit sync, Viterbi, R/S decoder, and video sub-frame sync) and go back and reacquire sync in all cases?

- 21. CLASS Model

- What is the degree of fidelity between the software model and the actual hardware implementation (this includes all hardware modeled end-to-end for the CLASS)?

- How are the four levels of sync modeled?

- What is meant by transient environment?

- How is the receiver modeled?

- What happens when there is receiver saturation?

- How is the Costas Loop simulated?

- How is the bit-by-bit decoding after bit sync accomplished?

- Does the Viterbi use hard or soft decision?

- How is the convolutional coding accomplished?

- How is the periodic interleaver/deinterleaver modeled?

- 22. LinCom listed four or five possible reasons for losing video sub-frame sync. Will the software model allow the user to identify which of these possibilities actually caused the loss of sync?

- 23. Has LinCom contacted Cyclotomics to verify that the use of a different primitive root in the R/S model will have no affect on the CLASS test?

- 24. What is Stanford's involvement in the CLASS test?

- 25. What type of computers will be used for the CLASS test? Since LinCom (Stanford) is converting the Fairchild VAX/VMX/Fortran 77 to the HP9000/UNIX, will this code undergo another software conversion?

- 26. How will integration/verification of all these computational modules be accomplished? Who will write/approve this?

- 27. Where is the data from the CLASS being analyzed? Name the specific points where data will be available for evaluation of system performance.

- 28. Can Goddard develop test cases to validate their model?

- 29. What hardware verifications have been performed to validate the CLASS?

- 30. Will CLASS tell if the error correction (Viterbi and R/S) scheme is (optimum? non-optimum?) in performance under normal and adverse (RFI and dropouts) conditions?

- 31. Does CLASS have to be re-initialized with another sub-routine if a data dropout occurs?

- 32. Will CLASS model the WSGT receiver under adverse conditions?

- How long of a dropout can be tolerated without unlocking the receiver?

- How long does it take to relock the signal?

- The NASCOM to JSC hop contains Doppler effects from the satellites buffering on the ground takes out these effects; is this modeled for CLASS?

- How is the clock handled for the bit sync, Viterbi, R/S? The Viterbi and R/S are at two different locations - how is this clock modeled for CLASS? Is this similar to the actual technique implemented?

- 33. What hardware/software configuration is necessary to demonstrate the Fairchild tape (end-to-end)? Does CLASS have a hardware configuration to support this?

- 34. Description of 'hooks' in Fairchild tape.

- 35. Does Cyclotomics have a software model for the R/S encoder/decoder?

- 36. Does LinCom have all information and complete code from Fairchild?

- 37. What is the status of concatenated channel error pattern generator algorithm?

- 38. Why was LinCom planning on using a <u>statistical</u> sub-frame corruption generator instead of RF link?

- 39. What is the status of STI?

- 40. What is the MacII being used for?

- 41. What is the status of Run Control, R/S subsystem, PCI, dePCI, Receiver, Viterbi sync, sub-frame sync?

- 42. Verification by Fairchild to LinCom the following:

- 1) RAM size

- 2) disk size necessary

#### UNEDITED FIGURES AND

# 31 OCTOBER 1988 NOTES TAKEN DURING ONV NASA/MSFC CLASS TEST MEETING

#### Steve Jones:

Launch scheduled for late 93-94, trying to go for <u>Late Qtr 93</u>. CDR slipped from <u>1990</u> to <u>1991</u>. Steve will push for hardware test following CLASS. Our objective here to be ready for CLASS/HARDWARE test. (Phone Mess. 544-3626)

#### Lee Ann Thomas:

5 Objectives:

- 1. Evaluate present software approach used for CLASS testing.

- 2. Determine if present CLASS system can be modified to be HI FI model of OMV video downlink.

- 3. Detailed review of software/hardware tests on algorithms.

- 4. Verify all hardware/software.

- 5. Discuss additional hardware/software test plans.

#### Bob Godfrey:

Discussion of CLASS Communications Link Analysis and Simulation System.

Question in CLASS models: to what detail is modeling? Bit-by-bit or statistical estimate.

Function - combines several components together (speedy). Simulator - bit-by-bit full <u>Hardware Emulation</u> (validation).

R/S can be done either way. Originally planned to be functional. 1st CLASS test was functional.

If 200-300 bits in error, then there will be no cycle slip. 1500-1600 average bits in error for cycle slip assuming sufficient SNR to resync.

TDRS requires PCI at these data rates.

Takes longer to recover sync if low SNR.

Almost never in standard Gaussian environment with TDRS.

Purpose of PN cover sequence is to prevent Viterbi decoder to

false lock-up on wrong bit pairs.

Bob Godfrey has more faith in functional test with TDRS portion. Because not all hardware is finished in design! Good point. Also each specific box is different. Which do you simulate? Functional covers global results.

Full simulator approach is being planned after last two telecons. Functional test also available. RFI is statistical emulation and nonstationary.

Robert Godfrey recommends functional use simulation to validate functional.

Some pieces (RFI) are only statistical models. If any part is statistical, then functional is best. Functional is (analytic/hybrid with hardware) average over some set of bits. Simulation is watching a bit all the way through.

RFI updated in 3-month intervals if necessary.

Is channel environment (XMIT and RCVR) modeled OMV output to WS input? Transients modeled.

#### 2 MAJOR WAYS TO USE CLASS:

<u>Static</u>: (Put user in orbit and set up environment and go). Select any set of parameters you want (once in 100 years).

<u>Dynamic</u>: In <u>normal mode</u> environment is anticipated designed for typical flight condition. Could put in once in 100 year occurrence using override.

We can worst case environment until we kill ourselves. Antenna switching is modeled.

CLASS models forward link.

Validation tests on down link were within 1/2 db of actual.

Validation tests on forward link were within .01 db of actual.

31 OCTOBER 1988

GAR LEWIS in place of JERRY O'CONNER

Cyclotomics test vectors being made up.

FW gives to NASA/GSFC and then FW wants test vectors back.

CAN WE HAVE TEST VECTORS APPROPRIATE TO EACH:

FW

Ask

CODE EMULATIONS??

LinCom

Cyclotomics

The Cyclotomics sync is clever!! Combined with undecodable error flag!

Preload R/S sync counters with unknown number?

What is R/S sync codeword (8 bits)?

Can R/S be set to sync up with less than 16 R/S sync patterns?

In Cyclotomics algorithm 'clear sync counters . . .' means?

CURRENT FW ENCODER INTERLEAVES DATA AS WELL AS PARITY.

31 OCTOBER 1988

JERRY O'CONNER

BIT RATE CONTROLLER

| 14334 | = High Alarm Point, to to Scaler<br>value of 40                        |  |

|-------|------------------------------------------------------------------------|--|

| 806Z  | VALUE OF 70                                                            |  |

| 7038  | TF Buster Stays in this range No<br>Scaler change in DRCM.             |  |

|       | - Lower Set Points to to Server.<br>MALue of 8, Bit stuffing milioted. |  |

FW has yet to find a picture which overflows the buffer!

If the buffer overflows, you will recover, but old data used for recover period.

> Roger says some function calls are missing in their code. But FW says they don't use image processing in the code that went to LinCom.

How to find

Glenn said 'What do we need at MSFC to run FW tapes with software/hardware test here at MSFC?' FW said MSFC needs a buffer to store 150 frames, and VAX will do it.

RAM requirements are 64 K Bytes x 16 = 1024 M Bytes. Side discussion 30 minutes Roger and Jerry code conversion!!

OMO VIDEO/TOLOMORY CITAMOL.

To run full simulation for 150 frames, computing time would be 2 weeks for 1 mth. This would be 56 different test configurations  $x \ 1 \ mth$ .

Statistical burst generator can shorten this time if you are synced up!!

Could add concatenated channel statistical error pattern Gen. and by pass

#### Error Performance

Total Pixel Errors vs EIRP Ratio Pixel SNR vs EIRP Ratio Error Propagation Statistics vs EIRP Subjective

THESE ARE IMPORTANT:

Sync transient curves: How long were you out of sync, etc.?

What caused the errors?

#### 1 NOVEMBER 1988

Bob Law - Cyclotomics and Tze-Hwa Liu

GCC Hardware:

- 1. R/S decoder (No. PLL) upgraded (to space level?)

- 2. Bit error monitor included.

- 3. Super channel monitor.

- 4. Update/report bit errors and undecodables.

- 5. BCD displayed.

- 6. OP code defined by customer.

COMPATABILITY TO OMV OF MODIFIED 888C UNIT AT MSFC

Difference of OMV and 888C at MSFC

(Functionally: same) (Same sync, same helical interleaver, same decoding

algorithm)

- 1. Interface: bursty data vs continuous data

- 2. Clock: No. PLL

- 3. Interleaving depth fixed to 8

- 4. Same helical interleaving

- 5. Undecodable flag: indicate following block is wrong

- 6. Data rate: 1.544 Mbps vs 972 (OMV) Kbps, master/slave driven by user

- 7. Byte: separate byte for OMV (built-in test equipment)

# LINCOM TREATS THE R/S SYSTEM AS FIVE UNITS

1. R/S Encoder

\_\_\_\_\_

- 2. Helical Interleaver

- 3. R/S Sync Circuit

- 4. Helical Deinterleaver

- 5. R/S Decoder

Primitive or root poly.Test vectors must beWhich roots used to generate field?different for differentTwo polynomials:Primitive Poly.roots.

Parity Generator Poly.

\_\_\_\_\_

### 1 NOVEMBER 1988

### QUESTIONS:

LSB or MSB 1st

Which symbol comes first?

Massey-Berlekamp versus Berlekamp. Differences?

Test vector impact!

Where in sync block is <u>FW ID</u>?

What is FW ID channel 1?

What is FW ID channel 2?

# TEST VECTOR SIGNATURE ANALYSIS

```

Generate a periodic 2040x8 test pattern

Unknown phases

```

# THE LEGAL ASPECTS OF TEST VECTORS

I recommended two sets: to go from FW to LinCom A. 1 with answers B. 1 with no answers This agreed to by Gar Lewis and Bob Law. By 18 Nov 88 these vectors will be sent to LinCom by FW. Steve entered the discussion. 1 NOV 88

Dennis asks one more question regarding test vector.

### AGREED FORMAT FOR TEST VECTORS

## R/S FORMAT:

$$\frac{\text{Sync}}{\text{R/S Word I}} \xrightarrow{M_{237} M_{236}} \cdots \xrightarrow{M_0 C_{15} C_{14}} \cdots \xrightarrow{C_{01}} \frac{\text{Sync}}{\text{M}_{237}} \xrightarrow{M_{237}} \cdots \xrightarrow{M_{237}} \cdots \xrightarrow{R/S \text{Word}} 1 + 1$$

First Received M<sub>237</sub>, Second Received M<sub>236</sub>, etc.

Sync is 0 0 0 1 0 1 1 1 = 1,7 as above.

OUTPUT FORMAT SAME AS ABOVE.

| 1 | UNDECODABLE PATTERN | 1ST BYTE               |

|---|---------------------|------------------------|

| 0 |                     | 2ND BYTE               |

| • |                     | •                      |

| • |                     | •                      |

| • |                     | •                      |

| 0 |                     | 255TH BYTE SYNC (1,7)  |

| • |                     | •                      |

| • |                     | •                      |

| • |                     | •                      |

| 0 |                     | 2040TH BYTE SYNC (1,7) |

1 NOV 88

### SYNC BLOCK

.... 255 SYNC (2,7) CHANNEL ID SYNC (1,7) 2 7 1 RSW8 RSW1 RSW2 . . . . RSW3 RSW2 RSW1 1st Byte 31st Byte 64th Byte This is not 255th Byte of a R/S word.

#### SUB-FRAME SYNC

- Hardware won't look for sub-frame sync until opening window near bottom of sub-frame. This prevents compressed video from looking like subframe. This windowing doesn't occur until sync is acquired.

- 2. If you don't get garbage look with window (if not sync'd Huffman decoding fails).

- 3. If you don't get sync open window to find sync. Then go back to window.

- 4. Where to reinsert undecodable flag in VRU?

- 5. Test points in VRU and VCU.

- 6. Process 150 frames of data. Results? Can we count <u>pixel errors</u>? Rather than just sub-frame replacement? As it stands now, 1 pixel error can cause sub-frame replacement. However, after one pixel in error, the VRU stops! All pixels after are bad.

- 7. Bit sync Viterbi Sync RS Sync Sub-frame sync Lose Δ value, lose pixel, lose Huffman table Lose channel ID (Rare! - it has multiple cks and flywheels if you miss one.)

Channel 1 1 0 1 1 1 0 0 0 ID 8-bit Irig Unique Word Channel 2 0 1 0 0 0 1 1 1 ID 8-bit Irig Unique Word LSB?

- 8. Can we determine which problem caused loss of picture, i.e., which sync?

- 9. Can we determine re-sync acq time for each? For inter-reaction of sync's? Interdependence, etc.

10. Simulation is done in NRZ-M.

2 NOV 88

What equipment is being tested, where, what?

VCU/VRU Compatibility test

Then tied together as unit including camera. No end-to-end test.

Suggest end-to-end test using Goddard Test Van Fairchild. Goddard has req for end-to-end using only compatibility test and test van.

Compatibility test (is pre-flight readiness) is not performance test but only run with usually low power testing to see data format and all connectors, etc. are compatible with TDRS link. Channel environment and flight dynamics are not simulated in NASA/GSFC compatibility test van. Assures signals will pass through TDRS.

User does not drive these tests. They are wet and dried tests. It is certification process required before actual TDRS usage.

To schedule van. 1 year lead time. 1 week typical max usage at time. Could use your own transponder and dish and schedule TDRS time. Ironically, it is much easier to schedule TDRS time than to schedule the compatibility test van.

TRW will define the requirements for compatibility and other tests while in the van.

Glenn: Is anybody here running the system level BER tests?, i.e., duplicating CLASS with hardware to check hardware.

2 NOV 88

TEST PLAN

#### Boris

Objectives:

Model OMV video interleaver to CLASS perform end-to-end

### SIM TEST

| 1. Sync versus E /No. Viterbi and PCI<br>b | $E_b = Channel Bit$         |

|--------------------------------------------|-----------------------------|

| 2. RS frame sync                           | or Channel Symbol           |

| 3. Helical deinterleaving and RS coding    | $\therefore$ ~ .5 µsec wide |

| 4. Reconstruct sub-frames                  |                             |

|                                            |                             |

5. Verify video picture quality

#### INDWT

DATA TO RUN TEST ON DIGITIZED RS-170 VIDEO DATA TEST PATTERN(S) FOR CALIBRATION - illustrate freq response LinCom/GSFC (30 seconds = 150 frames) (10 seconds = 50 frames) <u>10 seconds of static space craft scene FWSI</u> <u>10 seconds of static rotating space craft scene FWSI</u> (This is 6 tapes 150 frame tape FW) <u>N seconds of TBD scene from NASA/MSC</u> (No docking tape - this could be docking) Comment 200 frames required to get good, stable statistics

.

.'. Run 40 seconds - recommended

Tape Record

VRU output R/S Enod/nter Output

Input to R/S

<u>Records</u>

Time for R/S sync (Lee Ann will give me copy)

(Phase II testing = dynamics test -- <u>not</u> sure we'll run!)

Additional time to modify VRU to give sub-frame replacement statistics and accept R/S undecodable flag.

.

3106 7 38

11

D010.GEM

# ATTACHMENT 2

OMV Class Test Results (First Go Around), Monthly Report, May 12, 1989

## AN INVESTIGATION OF ERROR CORRECTING TECHNIQUES FOR OMV DIGITIZED DATA

•

## NASA GRANT: NAG8-104 QUARTERLY REPORT MAY 12, 1989

÷

#### SUBMITTED TO:

Mrs. Lee Ann Thomas EB33 NASA/MSFC MSFC, AL 35812 205+544-3662

#### SUBMITTED BY:

Frank Ingels, Ph.D. Principal Investigator Mississippi State University Mississippi State, MS 39762 601+325-3912

#### WORK SUMMARY - FEBRUARY 12, 1989 - MAY 12, 1989

During this period, several meetings at NASA/GSFC were attended. These meetings concerned CLASS simulation test runs for OMV. In Addendum 1 is a report that was submitted concerning the 26-30 March 1989 meeting at NASA/GSFC, and in Addendum 2 is a report that was submitted concerning the 17 April 1989 meeting.

Other factors have arisen since the 17 April 1989 meeting. These factors concern the User Signal Constraint budget as delineated by TRW memo of 11 April 1989 from C. Y. Yoon to B. Dobrotin and the Modified OMV Return Link Calculation as performed by Ted Kaplan, 17 May 1989 (telephone 301+464-8900).

On the first item, User Signal Constraint budget, I have requested the TRW IOC on "The Effect of Gain/Phase Imbalance on the Performance of the DBS, Part II," by C. Yoon, February 11, 1983. The data of Figure 1, Degradation Due to Modulator Imbalance in the 11 April 1989 memo from C. Y. Yoon is, I hope, verified in the above requested IOC report.

A question as to the Gain Slope of .1 db/MHz or .2 db/MHz has been discussed in a telecon held 16 May 1989. C. Y. Yoon has stated that the test data meets the 0.1 db/MHz figure although the 0.2 db/MHz figure has been used in the past. THIS ISSUE IS NOT OFFICIALLY RESOLVED AS YET.

The second item, the Modified OMV Return Link Calculation, it is noticed that despite the discussion in the 16 May 1989 telecon, there is no antenna calibration factor of 0.5 db taken off the antenna gain as recommended by Mr. Lee Malone. (In a telephone contact with Mr. Ted Kaplan on 19 May 1989, Mr. Kaplan stated he did not include that since he wasn't sure what number to use or even if that factor had been agreed upon.)

The Q channel power is listed as 14 dbw, but note that in the Return Link Calculation item 6, User Data/Total Power Ratio, subtracts 1.0 db for power sharing. This is appropriate since it effectively reduces the 25 watts (14 dbw) in Q channel to 20 watts (13 dbw) in the Q channel.

Finally, note that the Effective User Margin, item 14, states that there is 3.7 db. However, we must keep in mind that the NASA/MSFC specification requires 3.0 db Effective User Margin. Hence, TRW has .7 db extra margin above the NASA/MSFC requirement. If we deduct Mr. Malone's 0.5 db, then TRW has a .2 db extra.

#### ADDENDUM 1

#### TRIP REPORT - CLASS TEST SCHOOL 26-30 MARCH 1989

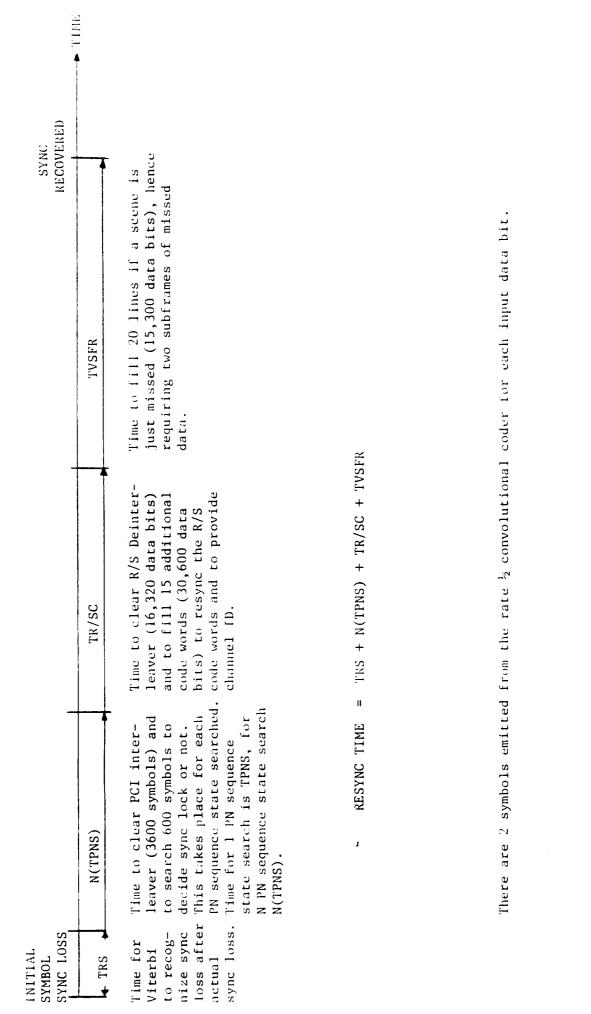

At the 26-30 March 1989 CLASS Test School, the time to recover from synchronization loss was discussed. Since it appears that simulating a bit synchronizer bit slip during an otherwise usable channel does not appear feasible in the immediate future, this investigator has estimated some synchronization recovery times due to various parts of the system.

#### Viterbi Decoder Recovery Time From Bit Synchronizer Slip

#### Worst Case Estimate

Conceivably it might be necessary to search all 30 PN cover sequence states and to clear the interleaver contents before each state search. The interleaver buffer contains 3,600 Viterbi input symbols<sup>#</sup> (equivalent to 1,800 bits) of interleaved information. Furthermore, approximately 600 input symbols are searched to determine if the error metrics are indicating correct PN sequence lock. Thus, it could take, for a search of all 30 PN sequence states,

30 (3600 + 600) = 126,000 symbols

to recover from a symbol sync loss. Each symbol is equivalent to approximately 0.514 usec (Mode-A), hence a <u>total worst case recovery</u> <u>time is estimated to be 65 ms</u>. (At the slower data rate of 486 Kbps (Mode-C), the recovery time is approximately 130 ms.)

#### Average Case Estimate

On the average, a PN cover sequence search could encompass only 2 states. For this case, the number of bits required would be

2(3600 + 600) = 8,400 symbols

to recover, and an <u>average recovery time is estimated to be 4.32 ms</u> for the two camera (Mode-A) data rate of 972 Kbps and 8.64 ms for the one camera (Mode-C) data rate of 486 Kbps.

\* A symbol is the output of the rate 1/2 convolutional encoder. The symbol rate is 2 times the data rate.

## Reed/Solomon (R/S) Deinterleaver and Decoder Recovery Time From Bit Synchronizer Slip

There are 2,040 bits per R/S word and a depth 8 interleaving, thus 16,320 bits (at 2.06 usec per bit) per R/S interleaved block.

Assuming the need to first clear the interleaver and then to fill at least 15 additional code words to resynch the R/S code word to provide and channel ID, the estimated resynchronization time of the R/S deinterleaver/decoder is

16,320 bits at 2.06 usec per bit = 33.62 ms Clear Interleaver 30,600 bits at 2.06 usec per bit = 63.00 ms Resynch R/S Counters 2,040 bits at 2.06 usec per bit = 4.20 ms To provide Channel ID.

Thus, we have:

<u>Maximum Total R/S Recovery Time = 100.82 ms</u> (Mode-C) <u>Maximum Total R/S Recovery Time = 50.41 ms</u> (Mode-A).

#### VRU Subframe Replacement Sync Loss Recovery Time

#### 20 Line Subframes

Approximately 15,300 bits fill 20 lines and if a scene is just missed, hence requiring two subframes of missed data, then the worst case recovery time would be

<u>30.600 bits at 2.06 usec per bit = 62.9 ms</u> (Mode-C),

and the best case recovery time would be

<u>15.300 bits at 2.06 usec per bit = 31.5 ms</u> (Mode-C).

A scenario of recovery times is now estimated as:

MODE-C (486 Kbps data rate, 972 Kbps RF Symbol Rate)

| SCENARIO                                                                           | ESTIMATED BIT SYNC LOSS RECOVERY TIME              |

|------------------------------------------------------------------------------------|----------------------------------------------------|

| A. Worst Case Viterbi<br>plus worst case sub-<br>frame replacement<br>sync.        | 130 ms + 100.8 ms + 62.9 ms = <u>293.72 ms</u>     |

| B. Average Viterbi<br>(2 State Search)<br>plus worst subframe<br>replacement sync. | 3.64 ms + 100.82 ms + 62.9 ms = <u>172.36 ms</u>   |

| C. Average Viterbi<br>(2 State Searcn)<br>plus best subframe<br>replacement sync.  | 3.64 ms + 100.82 ms + 31.5 ms = <u>140.96 ms</u> . |

Mode-A recovery times are approximately one-half that of the Mode-C recovery times. The above recovery times do not include the 400 to 700 symbols it takes the Viterbi to detect synchronization loss after an actual symbol synchronization loss occurs. This would add a maximum of 0.36 ms for Mode-A and 0.72 ms for Mode-C operation, not a significant factor in either case. Figure 1 illustrates synchronization recovery procedures.

A constant source of confusion has been the EIRP and EIRP Margin terminology. In an effort to straighten this out, the following exposition is offered.

Figure 2 illustrates a simplified view of the CMV to TDRS to White Sands facility and the three important system points concerning EIRP, EIRP Margin, SNR and expected Viterbi decoded and deinterleaved bit error rate (BER). As noted on the figure, an OMV EIRP adjusted for 46,000 Km free space propagation loss only results in 7.12 db EIRP Margin at TDRS for the 25-watt OMV transmitter.

However, it must be remembered that any waveform distortions (user constraint) polarization losses, plume loss, RFI loss effects and dynamic motion losses are <u>not</u> included as yet. If, at White Sands, a .3 db polarization loss is assumed, and 2.0 db losses assumed for the combination

FIGURE 1 - SYNC RECOVERY TIME

(-168.02 dbw required to achieve 10 2 BER at Viterbi output at White Souds) SOFT DECISION DECODED BER 3 BIT A/D THING TO SAMPLER DECODER V UTERB I BIT SYNC TIMING 0 EIRP Margin at TDRS is roughly equivalent to 2.5 db SNR at Viterbi MATCHED FILTER An SNR of 2.2 db yields a Viterbi output error rate of 10-5. Thus, AND SAMPLER SNR RECOVERY CARRIER 1.00P FILTER input. TDRS to RFI, user constraint losses, polarization The above does not include degradation due losses, plume loss, dynamic motion losses. -192.9 db at 46,000 Km Range XMIT power (dbw) + Gimbal loss loss = -160.9 dbw for 25 watt transmitter il. EIRP Required at TDRS to achieve Viterbi + RF combiner loss + cabling loss + VSWR losses + antenna XMIT power (dbw) - 1.6 - 1.8 transmitter is -160.9 dbw + 168.02 dbw EIRP from ONV -192.9 db propagation EIRP Margin at TDRS for 25 watt OMV = XHIT power (dbw) + 19 db For 25 walt transmitter (20 walls output BER of 10-5 is -168.02 dbw PROPAGATION LOSS - .9 - .3 + 23.6 ONV EIRP Q channel XM1T power) ONV EIRP = 32 dbw gain OMV EIRP = 11 Υ 0110 7.12 db

FIGURE 2 - SIMPLIFIED OMV-TDRS-W.S. LINK

of user constraint losses, plume loss and dynamic motion losses, then the resulting EIRP Margin at TDRS is reduced to 4.82 db for the 25-watt OMV transmitter!

For no RFI, this would be a healthy margin, but if RFI is assumed to create an apparent 2.7 db loss on the average, then the EIRP Margin at TDRS is reduced to 2.12 db, just above that required for a  $10^{-5}$  BER out of the Viterbi decoder. What does this mean to the OMV video system? Figure 3 illustrates a video frame that might have been corrupted by a subframe replacement (4 line subframe) caused by undecodable R/S words. The R/S word errors resulted in a simulation of a channel which had assumed an EIRP Margin at TDRS of 0 db. The channel simulation included RFI effects which actually created an apparent 2.7 db loss (high RFI used) for an effective EIRP Margin (RFI adjusted) of -2.7 db. From this, we might conclude that the 25-watt OMV transmitter situation will produce a very healthy video, better than that of Figure 3.

Once again, we must exercise caution! Subject to waveform distortion measurements of the OMV 25-watt transmitter high power amplifier, we might have as little as 0 db loss or as much as 2.5 db loss due to waveform distortion (user constraint) losses alone! Thus, the above assumed 2.0 db assumed for the combination of user constraint, plume loss and dynamic motion losses might prove to be underestimated.

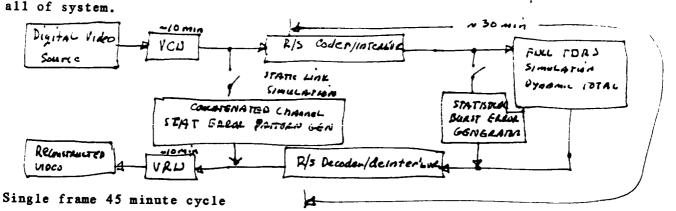

To ascertain the possible video degradation effects, a series of simulations are planned using CLASS. Phase 1.0 will include only a "static test", i.e., (see page 28 of "Class Testing of the CMV Video Telemetry Channel," by R. Avant, 2nd Draft, 27 January 1989) no dynamic motion, no signal frequency or power level or data rate variations, full synchronization lock conditions. RFI effects will be considered.

The OMV EIRP levels and RFI situation planned is listed on page 52 of "CLASS Testing of the OMV Video Telemetry Channel" mentioned above. These values are listed in Table 1, along with EIRP Margin at TDRS and the Effective Margin at TDRS adjusted for 0.3 db polarization loss and 2.0 db total combined other losses (not including RFI).

From Table 1 we observe that Test 1 is planned with a -1.0 db RFI adjusted level. This will not be as much channel degradation as the channel for the situation depicted in Figure 3.

TABLE 1

# PHASE 1 PLANNED TEST PARAMETERS

(Excerpts from "CLASS Testing of the OMV Video Telemetry Channel," by R. Avant, 2nd Draft, 27 Jan 1989, p. 52)

| Range     |

|-----------|

| Km        |

| 46,000    |

| 46        |

| 972 Kbps, |

| 972       |

| Rate      |

| Data      |

| Mode-A,   |

| VCU M     |

|           |

| Сазе      |

| Worst     |

| SSA       |

| (TDRS-E   |

| -         |

| Level     |

| RFI       |

| •         |

| O. Channel Power         OMV_EIRP*           12 W         28.9 dbw           16 W         31.1 dbw |

|----------------------------------------------------------------------------------------------------|

|                                                                                                    |

|                                                                                                    |

|                                                                                                    |

- \* OMV EIRP does not include: user constraint losses, dynamic motion losses, polarization losses, plume losses or RFI effects.

- \*\* Effective EIRP Margin includes: .3 db polarization losses and 2.0 db other combined losses.

- \*\*\* RFI adjusted EIRP Margin is effective EIRP Margin plus an additional 2.7 db of losses due to kFI effects.

- \*\*\*\* Effective EikP Margin includes: .3 db polarization losses and .3 antenna pointing loss and .5 user constraint losses.

| <u>e Cliansi a</u>                            | VIT MATH AN                                                        | TYSTS                                 |

|-----------------------------------------------|--------------------------------------------------------------------|---------------------------------------|

|                                               |                                                                    | HONITOR                               |

|                                               | Carr Sync- Forlal:                                                 |                                       |

|                                               | Code Syncr Poh.r.;                                                 | Ontr:                                 |

|                                               | Pata Synch Paylel:                                                 | Cinter:                               |

|                                               | Chroated BER - Per (conor:                                         |                                       |

|                                               | With See Synce Out Bits:                                           |                                       |

|                                               | Review Sold Control Association<br>Retail Dec. Survey Max, C. 4. 1 |                                       |

|                                               |                                                                    | humlt.                                |

|                                               | NYS Lines Large Unspec                                             | h byna – Chtr:<br>1 syna – Chtr:      |

|                                               | Cur Er Follern Ito Door<br>VRU Subfinishiis- S.Sifr:               | · · · · · · · · · · · · · · · · · · · |

|                                               |                                                                    |                                       |

|                                               |                                                                    |                                       |

| BIMULATION PAPARATERS                         |                                                                    |                                       |

| anfiguration: 0.3                             |                                                                    |                                       |

| Frances Usis Heartha out - Bearlai            |                                                                    |                                       |

| umment Video Frame:<br>DFB:                   |                                                                    |                                       |

|                                               |                                                                    |                                       |

| IRP:'- L dEW - EIRP Mangin: '- d<br>amue: stm |                                                                    |                                       |

| H Cond: M 2 3 4 5 5 7                         |                                                                    |                                       |

| IRS Model: GLFC                               |                                                                    |                                       |

| 10 Mode: A B Da B                             |                                                                    |                                       |

| Naonel IE: 2                                  |                                                                    |                                       |

|                                               |                                                                    |                                       |

# ORIGINAL PAGE COLOR PHOTOGRAPH

FIGURE 3 - A SIMULATION RESULT FOR HIGH LEVEL RFT

CONSIDERING THE LACK OF DYNAMIC MOTION LOSSES AND OTHER FACTORS NOT INCLUDED IN PHASE 1.0, IT IS RECOMMENDED THAT A TEST WITH HIGH RFI (LEVEL 1) WITH -3.0 EIRP MARGIN (TDRS), HENCE AN EFFECTIVE EIRP MARGIN (TDRS) OF -5.3 dB (ADJUSTED FOR POLARIZATION AND USER LOSSES OF .3 dB AND 2.0 dB, RESPECTIVELY) AND AN RFI ADJUSTED EIRP MARGIN OF -8.0 dB BE CONDUCTED. THIS WOULD BE 3.0 dB WORSE THAN THE SIMULATION WHICH PRODUCED FIGURE 3.

#### SOFTWARE ANOMALIES UNCOVERED (OCT/NOV 1988 - APRIL 1989)

At an October/November 1988 meeting in Huntsville, Alabama, a consortium of OMV personnel gathered to review the upcoming (Dec 88) OMV Since that meeting, many anomalies of the software/CLASS test CLASS test. development effort have been uncovered. The actual OMV CLASS test is being (will be) initiated March 26-31, 1989. A partial list of problem anomalies discovered by NASA/MSFC, NASA/GSFC, Fairchild and TRW is given below. These problems would not have been discovered until well into the hardware development had the OMV CLASS test not been insisted upon and insisted upon to the fidelity required by NASA/MSFC personnel. At the close of the October/November 1988 meeting, it was felt that the OMV CLASS test could be held December 1989 and that the software was complete by Fairchild and all software conversion could be expected to proceed (finally) by a two to three week date. Since that date, a series of telecons were held and an in-person meeting conducted in December, 1988, at NASA/MSFC with Dr. Frank Ingels, Mrs. Lee Ann Thomas and Mr. Glenn Parker.

Telecons and/or telephone discussions were held on the following dates:

4 January 1989 T1. Τ2. 5 January 1989 T3. 12 January 1989 19 January 1989 Τ4. 1 February 1989 T5. 14 February 1989 т6. Τ7. 1 March 1989 7 March 1989 т8. 14 March 1989 T9. T10. 20 March 1989

The following items were brought to light in pursuit of a high fidelity OMV CLASS test:

- Lack of correct interleaving/deinterleaving when using two different video scenes. Different scene usage insisted on by NASA/MSFC/MSU.

- 2. Use of and thus test of 4 and 10 line subframe replacement. This feature was insisted on by NASA/MSFC/MSU. This feature did not function properly when tried the first time! It was inadvertently commented out.

- 3. Use of R/S decoder erroneous decoding (invalid data) flag was not incorporated in Fairchild software! This feature insisted on by NASA/MSFC/MSU. Decided it would be incorporated in hardware in May or July, 1990.

- 4. It was discovered that Huffman tables in the software were not correct! Evidently cross-loaded in software!

- 5. New buffer/step size control algorithm was uncovered! OMV CLASS test will not utilize this feature but will utilize the old feature.

- 6. When the ten line subframe replacement feature was successfully integrated, it was found the four line subframe replacement feature was not acting properly.

- 7. Use of two different data rates (48 Kbps and 972 Kbps) were not integrated at first. This was accomplished later.

- VRU apparently did not contain channel ID check. The assumption was that every other code word is in every other camera! This created a problem of sync lost! This was fixed.

- 9. Only after use of very different scenes did. When VCU.1 and VCU.2 produced different bit counts per frame, it was discovered that the position of both ends of residual bits were not being properly identified and tagged! This was fixed.

- 10. Bit rate controller was not being kept operational for all two channel modes of operation! This was fixed.

- SSA end-to-end calibration BER performance was reviewed by R. Godfrey in a memo to NASA/MSFC/MSU. This gave us more confidence in the CLASS calibration than I felt before.

- 12. An unknown VCU/VRU software problem (as of 27 March 1989).

- 13. Throughout the postponement of OMV CLASS test from December, 1988, to mid-January, 1989 to mid-February, 1989 to mid-March, 1989, the NASA/MSFC/MSU contingent successfully withstood all requests to go to configurations 2 and 3 testing after very few (if any) configuration 1 tests. We keep in mind the following:

- 1. Only in configuration 1 can we judge resynchronization time after bit slip.

- 2. Only configuration 1 uses the RF link equipment and the Viterbi decoder and the PCI decoder.

- 14. It was also discovered CLASS Viterbi software was not originally written in sufficient detail to allow synchronization and resynchronization studies on a bit-by-bit basis.

- 15. It was discovered that in a hurry to perform a 10 frame test run for CLASS school demonstration the CLASS software concerning the R/S decoder was modified but not revalidated using the test vectors. This illustrates the need for careful validation of each software setup!

#### ADDENDUM 2

#### Report: Meeting at GSFC, 17 April 1989

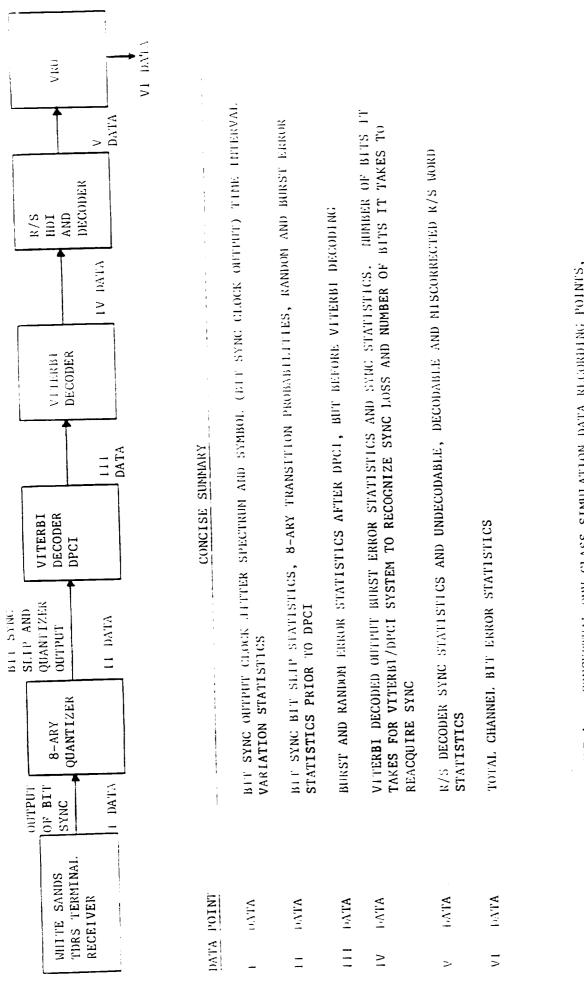

A visit was made to GSFC on Monday, 17 April 1989, to inspect an initial few configuration 1 data runs for CLASS simulation testing of the OMV system. Mr. R. Godfrey kicked off the meeting, answered some questions I had prestored and let Mr. Ted Kapplan (301+464-8900) and Mr. Dave Wampler (301+286-6767) guide me through the maze of detailed statistics for a configuration 1 data run. The statistics that will be available for a configuration 1 run are tabulated in TABLE 1. Figure 1 depicts the system points at which data will be taken in a configuration 1 run. Figure 2 is a condensed summary of the error statistics for the 50-frame runs with 0 db and -2 db EIRP margin at TDRS (relative to no RFI) respectively.

A set of 10-frame runs were conducted to determine the approximate EIRP margin (TDRS) at which the video reconstruction would deteriorate to an unusable picture. The runs were made for 0 db, -1 db and -2 db. No detailed statistical results were kept. These short runs were made to determine at what EIRP margin the 50-frame runs should be made. A comparison of the error rate out of the Viterbi decoder for the 10- and 50-frame runs is of interest because it can indicate whether 50-frames will be sufficient to prove a statistical sample. These results are indicated in TABLE 3.

The results of TABLE 3 indicate that the error statistics after the Viterbi decoder are roughly the same for the 10-frame and 50-frame runs. However, there are no available statistics on the random/burst mixture, so we cannot make any judgement on 50-frame statistics for random/burst

mixture. A-200 frame run is planned to compare with the 50-frame runs. Perhaps the 10-frame runs could be repeated and the detailed statistics of TABLES 1 and 2 could be recorded and compared to the 50-frame runs to allow judgement of the sufficiency of the statistical sample size of 50 frames.

Also from TABLE 3, it is apparent that the video link is tracked between -1 db and -2 db EIRP margin (TDRS). It is unfortunate that a 50-frame run was not made at a EIRP margin (TDRS) that provided some frames with replacements and some frames with no replacements, probably around -1.5 db EIRP margin (TDRS). I recommend this be done.

TABLE 2 illustrates the system performance for a good working video link (0 db) and a completely trashed video link (-2 db). In fact, at -2 db EIRP margin (TDRS), there were <u>no</u> video frames reconstructed. That this should be the case is logical. The following discussion will explain why we expect the results in TABLE 2 for both the 0 db case and the -2 db case.

First, one must realize that deinterleavers of any type will dispense a long burst of errors into smaller bursts distributed more or less on a periodic basis throughout the deinterleaved symbol stream. Also, a uniformly random distribution of error events into a deinterleaver produces a uniformly random distribution of errors in the output symbol stream and a uniformly random distribution of short bursts input will create an approximate uniform random distribution of small bursts in the output symbol stream. With this in mind, let's look at the data in TABLE 2.

We see that the statistics into the DPCI are a random mixture of random and burst error events. The mean length,  $\overline{L}$ , of the bursts for both 0 db and -2 db runs are fairly short, of the order of 11 to 18 symbols long. Even with two standard deviations, the burst error lengths are only of the order

of 26 and 44 symbols. After the DPCI, we see the error events are still a rather random mixture of random and burst error events with bursts of mean lengths 12 and 18 symbols and two standard deviation lengths of 30 and 48 symbols, respectively.

The Viterbi decoder with a free distance of 10 across the constraint length of about 64 symbols can correct most error bursts of 4 to 5 symbols in a span of about 64 symbols. The output of the DPCI for the 0 db runs produces a burst event on the average of 1.6 burst events every 100 symbols. These bursts have an average length of 12 symbols and an average of 3 errors per burst. Thus, the Viterbi should be able to correct most of these error events; and it does a good job, reducing the cumulative error rate from  $6.478 \times 10^{-2}$  to  $3.335 \times 10^{-4}$  (a factor of 200 reduction).

However, at -2 db EIRP margin (TDRS), the burst error events out of the DPCI occur at a rate of 2.2 per 100 symbols with an average length of 18 symbols and an average of 4 to 5 errors per burst. Now we see the Viterbi should start having trouble decoding the average burst, especially with an occasional random error included in the 64 symbol constraint length, and it does have trouble reducing the cumulative error rate from  $11 \times 10^{-2}$  to only 2.4x10<sup>-2</sup> (a factor of 5 reduction).

The error statistics out of the Viterbi indicate a fairly uniform mixture of random and burst error events and after the R/S deinterleaver we expect a similar error makeup (there are no long strings of bursts to deinterleave!).

As a result, the probability of symbol errors in a 2040 bit R/S codeword is conservatively approximated by assuming all error events are simply

random events. Thus, a cumulative error event rate of  $(6.74 \times 10^{-5} \text{ plus} 7.48 \times 10^{-5})$  14.225 $\times 10^{-5}$  (0 db margin case) will produce an average of .29 errors per 2040 bits, hence the R/S decoder should correct these, and it does! (No subframe replacements occurred and no R/S codewords failed to decode after initial synchronization was achieved.)

However, for the -2 db margin runs, the Viterbi output error event rate  $(1.879 \times 10^{-3} \text{ plus } 3.789 \times 10^{-3})$  of  $5.668 \times 10^{-3}$  produces an average of 11.56 error events per 2040 bits or 11.56 errored R/S symbols. Now we expect the R/S decoder to fail to decode the errors, and it does! (All video frames failed to reconstruct.)

The above is a heuristic discussion to provide insight into how the system should work. The system test results for this <u>STATIC</u> case agree with the "gut" feeling. One must remember that the <u>DYNAMIC</u> case will produce non-linear situations and will be the <u>REAL</u> test!

It must be remembered that 0 db EIRP margin at TDRS (relative to no RFI) corresponds to an <u>EFFECTIVE\_OMY\_EIRP</u> of 24.88 dbw after all losses are accounted for in the OMV budget analysis. We and TRW must be absolutely sure to be fair and objective in accounting for all possible losses.

An interesting observation from the TABLE 2 test results is that a 0 EIRP margin (TDRS) with no RFI should produce  $10^{-5}$  error rate after the Viterbi decoder. In the 10- and 50-frame test, HRFI runs, the Viterbi decoder error rate at 0 EIRP margin (TDRS) was approximately  $3 \times 10^{-4}$ . Thus, the RFI raises the average error rate by a factor of approximately thirty (30).

An estimate of synchronization time was made in my report of 5 April 1989. I estimated for the average Viterbi search and best subframe replacement synchronization case that 140 ms would be the acquisition time. The test runs for 50 frames took 30 R/S codewords to acquire synchronization. This is 68,040 bits. At a bit rate of 486,000 bits per second, 140 ms is 68,040 bits! What a lucky coincidence. In fact, though the first two video frames (one of each channel) are lost due to the need to have a correct frame header for each frame and the fact that channel frames are interleaved.

Another interesting observation is that after initial synchronization, neither the bit sync, Viterbi sync, nor R/S sync were dropped in the -2 db runs. Although "hits" were occurring in the R/S sync words, there was never a danger of losing R/S sync; the video was lost because there were simply too many errors to correct!

#### TABLE 1

- I. Bitsync.dat

- 1) mean & standard deviation of symbol interval as a fraction of the symbol time

- 2) clock jitter spectrum

- II. Quansync.dat & PCI.dat

- 1) slip rate = # of slips/# of sym

- 2) random error rate

- 3) # of bursts

- 4) burst characterization

- i) mean & standard deviation of burst duration

- ii) histogram of burst duration

- iii) # of errors/burst (mean & standard deviation)

- iv) spacing between errors in a burst (mean & standard dev.)

- 5) 8-ary transition probabilities (Helps to check ops of VA decoder, also to see the type of channel noise)

- III. Vsync.dat & CCPCI.dat (ALL OF THESE STATISTICS ARE AFTER DPCI BUT BEFORE VITERBI DECODER)

- 1) random error rate (should go up relative to burst errors)

- 2) # of bursts (should go down after de-interleaving)

- 3) burst characterization same as II-4

- Note: Any two erroneous symbols which have <12 error-free symbols between them are considered to be in the same burst.

- IV. Vbit.dat & Helicc.dat (AFTER VA DECODER)

- 1) # of bits it takes for initial acquisition

- 2) sync statistics table

| Out-of-Sync<br>Counter | <pre># of bits it takes     to detect sync     loss input to DPCI     to output of VIT         decoder</pre> | <pre># of bits it takes to re-acquire sync</pre> | <pre># of DPCI commutator shifts</pre> |

|------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------|

| 1                      |                                                                                                              |                                                  |                                        |

| 2                      |                                                                                                              |                                                  |                                        |

| •                      |                                                                                                              |                                                  |                                        |

| •                      |                                                                                                              |                                                  |                                        |

| •                      |                                                                                                              |                                                  |                                        |

Note: If the commutator shifts a multiple of 30, declare the out-of-sync a false alarm! Have to search for this visually.

- 3) total number of bursts

- 6 data bits equal burst window (after decoding)

- 4) histogram of number of bursts versus burst length

- 5) histogram of mean of erroneous bits within a burst

- 6) histogram of standard deviation of erroneous bits within a burst

- 7) bit error rate for "in sync" bits static statistic

- V. Rssync.dat (Reed/Solomon Coder) (See table in CLASS book at end on R/S sync positions.)

| Codeword<br>Cntr                | Sync<br>Position                | Cntr starting<br>at sync pos.                                 | Adjacent<br>Values | Sync<br>Cntr<br>Value      | Adjacent<br>Values<br>+ ++ |

|---------------------------------|---------------------------------|---------------------------------------------------------------|--------------------|----------------------------|----------------------------|

| counts<br>each<br>code-<br>word | stores<br>the cur-<br>rent sync | counts the no.<br>of codewords<br>while at a<br>sync position |                    | m <b>ax</b><br>value<br>15 |                            |

#### 1) Table - Sync Position

#### 2) Table - Freewheeling

| Freewheeling | Location                 | # of      | Lowest Freewheeling | - |

|--------------|--------------------------|-----------|---------------------|---|

| Count        | (Codeword)               | Codewords | Value               |   |

|              | of Freewheeling<br>Event |           |                     | _ |

| Out-of-Sync | Out-of-Sync | # of Codewords |

|-------------|-------------|----------------|

| Count       | Location    |                |

4) # of decodable codewords during in-sync

- 5) # of decodable codewords during out-of-sync

- 6) # of undecodable codewords during in-sync

- 7) # of undecodable codewords during out

- 8) # of miscorrections

- 9) miscorrection table

| Transmitted | Codeword in    | Miscorrected | # of Bit   |

|-------------|----------------|--------------|------------|

| Codeword in | Hex Before the | Codeword in  | Errors in  |

| Hex         | R/S Decoder    | Hex          | the Mis-   |

|             |                |              | correction |

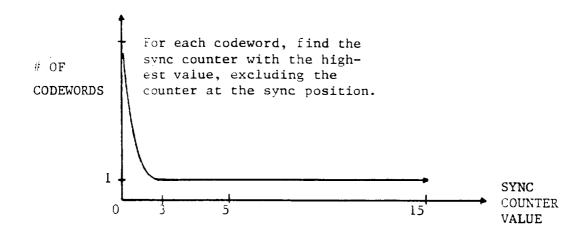

#### 10) Histogram of max sync entr's for each codeword

VI. RSVRV.dat

1) total channel bit error rate

FIGURE 1 - CONCEPTUAL ONV CLASS SIMULATION DATA RECORDING POINTS, CONFIGURATION 1 RUNS

| STATISTIC                                          | BEFORE DPCI (II DATA)             | L DATA)                          | AFTER DPCI (III DATA)             | II_DATA)_             | VITERBI DE             | VITERBL DECODER OUTPUT |

|----------------------------------------------------|-----------------------------------|----------------------------------|-----------------------------------|-----------------------|------------------------|------------------------|

| EIRP MARGIN<br>1. Rit Slip Rate                    | 0 db<br>-0-                       | -2 db<br>-0-                     | 0 db<br>-0-                       | -2 db<br>- <b>0-</b>  | 0 db<br>-0-            | -2 db                  |

| 2. Number of Random Errors<br>3. Random Error Rate | 112,390<br>1.229x10 <sup>-2</sup> | 86,646<br>9.447×10 <sup>-3</sup> | 135,688<br>1.484×10 <sup>-2</sup> | <u>-</u> 8            | 6 74×10-5              | -u-<br>1 870~10-3      |

| 4. Number of Burst Errors                          | 126,137                           | 192,000                          | 147,850                           |                       |                        | 014610.1               |

| 5. Burst Error Rate                                | 1.379×10 <sup>-4</sup>            | 2.1x10 <sup>-2</sup>             | 1.617×10 <sup>-2</sup>            | 2.21x10 <sup>-2</sup> | $7.48 \times 10^{-5}$  | 3.789×10 <sup>-3</sup> |

| 6. Total Number of Errors                          | 592,311 7                         | 1,010,088                        | 592,104                           | 1,009,729             | <u>-</u>               |                        |

| 7. Cumulative Error Rate                           | 6.478x10 <sup>-c</sup>            | .1105                            | 6.478×10 <sup>-2</sup>            | .1105                 | 3.335×10 <sup>-4</sup> | 2.461x10 <sup>-2</sup> |

| 8. Average Error Burst                             | 10.694                            | 16.66                            | 12.109                            | 18.514                | 5.657                  |                        |

| Length, L                                          |                                   |                                  |                                   |                       | •                      |                        |

| 9. Std. Dev. of L                                  | 8.0824                            | 14.16                            | 9.206                             | 15.983                | 3.837                  | 9.64                   |

| 10. Average Errors Per                             | 3.8047                            | 4.809                            | 3,087                             | 4.61                  | 3.555                  | 5.998                  |

| Burst, Ē7B                                         |                                   | I                                | -                                 | 6<br>1<br>-           |                        |                        |

|                                                    | 2.173                             | 3.342                            | 1.502                             | 3.07                  | 1.938                  | 5.366                  |

| 12. Average Error Spacing                          | 2.921                             | 3.39                             | 4.316                             | 3.856                 |                        |                        |

| Par Burst, ES/B                                    |                                   |                                  | •                                 |                       |                        |                        |

| 13. Std. Dev. of ES/B                              | 3.051                             | 3.06                             | 3.116                             | 3.034                 |                        |                        |

|                                                    |                                   |                                  |                                   |                       | 3.335x10 <sup>-4</sup> | 2.46x10 <sup>-2</sup>  |

| Rate                                               |                                   |                                  |                                   |                       |                        |                        |

| 15. Number of Bits for                             |                                   |                                  |                                   |                       | No Svne Dron           | Dron                   |

| Viterbi to Reacquire                               |                                   |                                  |                                   |                       |                        |                        |

| Syna                                               |                                   |                                  |                                   |                       |                        |                        |

| 16. Number of Video Frames                         |                                   |                                  |                                   |                       | None                   | No Video               |

| With Subframe Replace-                             |                                   |                                  |                                   |                       |                        | Frames Re-             |

| mants                                              |                                   |                                  |                                   |                       |                        | constructed            |

|                                                    |                                   |                                  |                                   |                       |                        |                        |

STATISTICS FOR TWO 50 FRAME RUNS 17 APRIL 1989

#### TABLE 3

#### COMPARISON OF 10 FRAME AND 50 FRAME RUNS (CONFIGURATION 1)

| No. of Frames/Run                                                       | EIRP#: 0 db           | <u>-1 db</u>          | <u>-2 db</u>          |

|-------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|

| Subframe Replacements:                                                  |                       |                       |                       |

| 10 Frame Run<br>50 Frame Run                                            | 0<br>0                | 0<br>-                | ALL<br>ALL            |

| Bit Error Rate After<br>Viterbi Decoder:                                |                       |                       |                       |

| :0 Frame Run                                                            | 3.09x10 <sup>-4</sup> | 2.43x10 <sup>-3</sup> | 2.33x10 <sup>-2</sup> |

| 50 Frame Run                                                            | 3.34x10 <sup>-4</sup> |                       | 2.46x10 <sup>-2</sup> |

| Bit Error Rate After<br>Bit Sync and Matched<br>Filter But Before DPCI: |                       |                       |                       |

50 Frame Run

$6.478 \times 10^{-2}$

$11.04 \times 10^{-2}$

25 frames per camera channel, 50 frames total, statistics based on 50 frames. 20 lines per subframe, 12 subframes per frame. approximately 20 R/S codewords per frame.

\* EIRP margin at TDRS for no RFI. (The high RFI channel model was used for the runs.)

# ATTACHMENT 3

Equivalent System Gain Available From R-S Encoding Versus a Desire to Lower the Power Amplifier From 25 Watts to 20 Watts for OMV, Memo, 27 August 1989

# MISSISSIPPI STATE UNIVERSITY COLLEGE OF ENGINEERING

DEPARTMENT OF ELECTRICAL ENGINEERING DRAWER EE MISSISSIPPI STATE, MISSISSIPPI 39762 PHONE (601) 325-3912

27 August 1989

To: Ms. Lee Ann Thomas

Subject: Memo From Boris Dobrotin, 20 July 1989, Concerning Equivalent System Gain Available From R-S Encoding <u>AND</u> B. Dobrotin's Desire to Lower the Power Amplifier From 25 Watts to 20 Watts

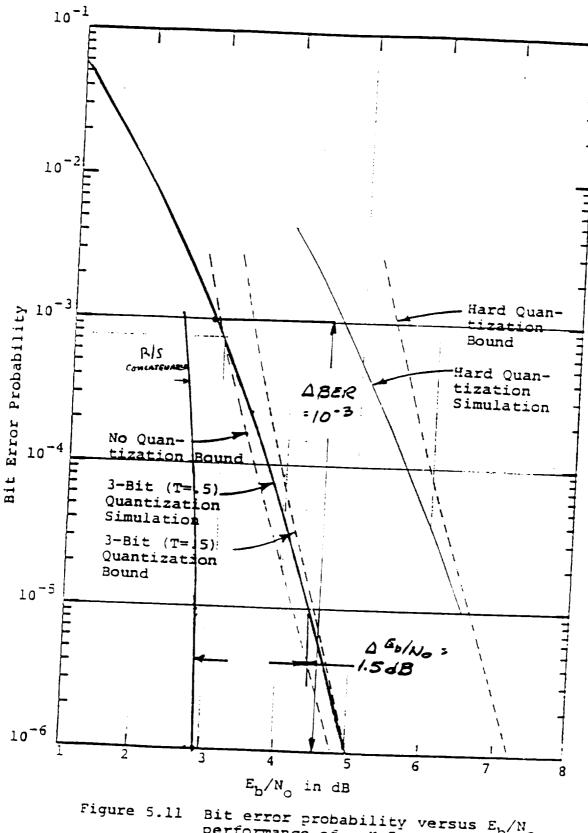

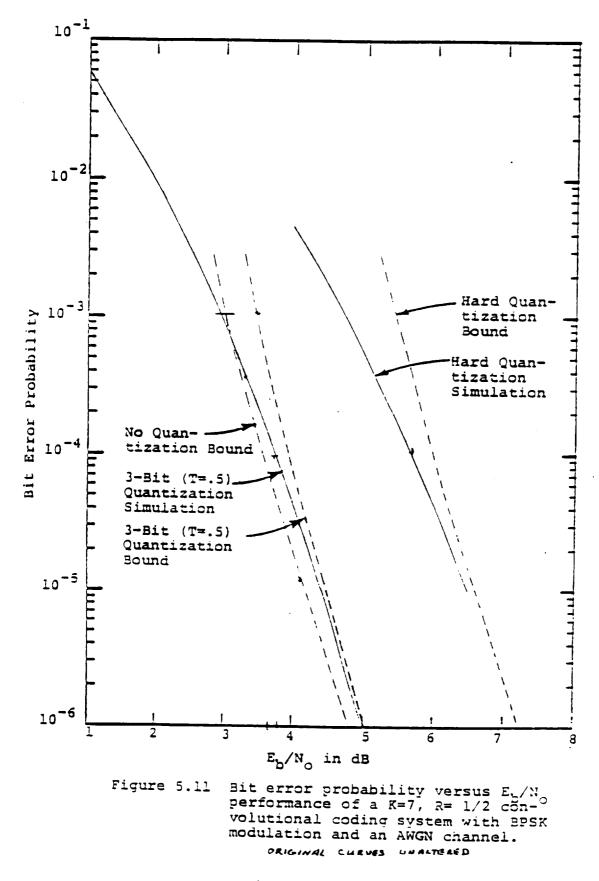

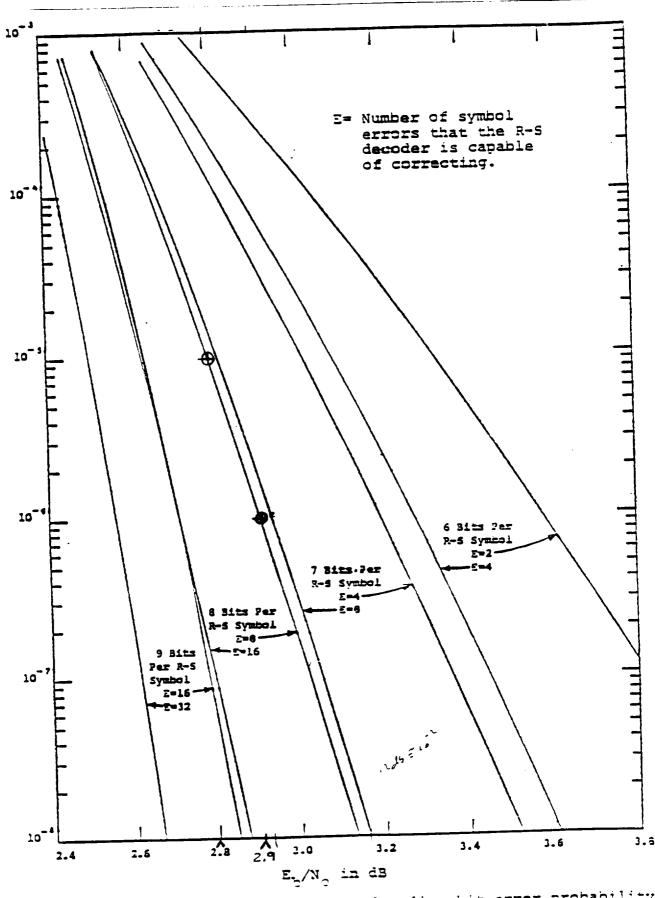

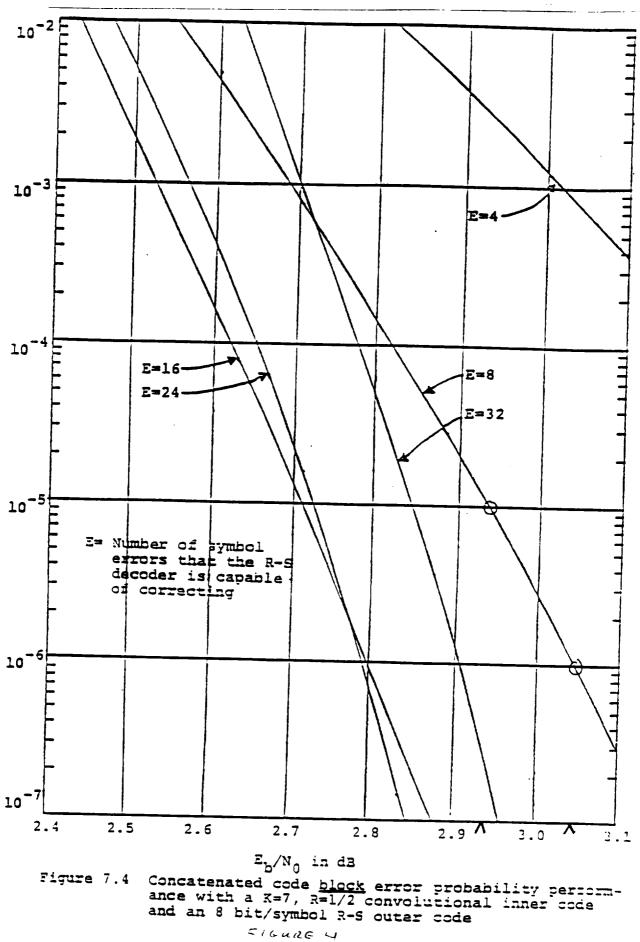

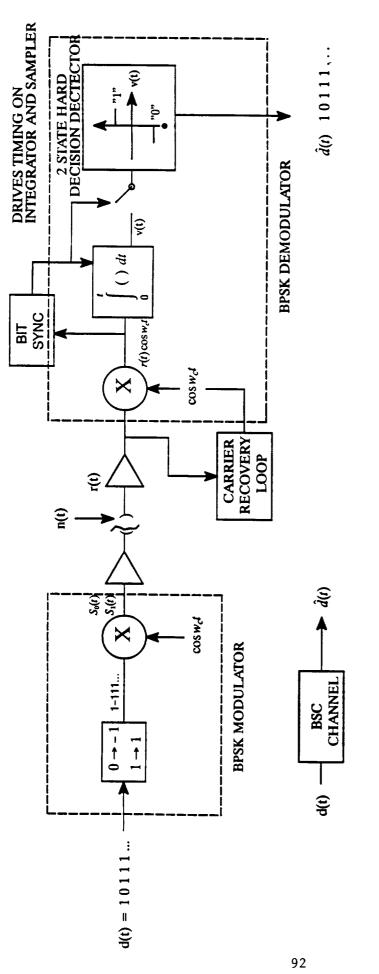

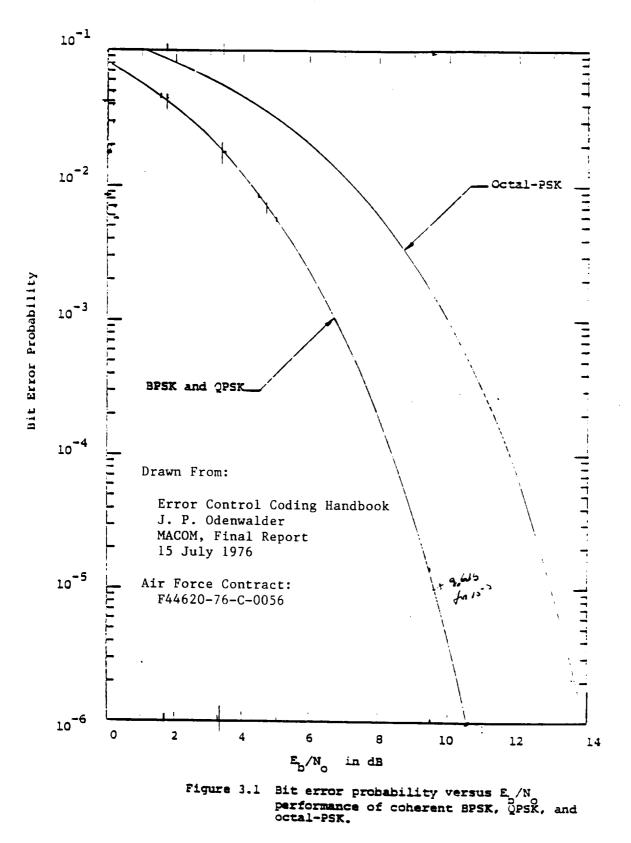

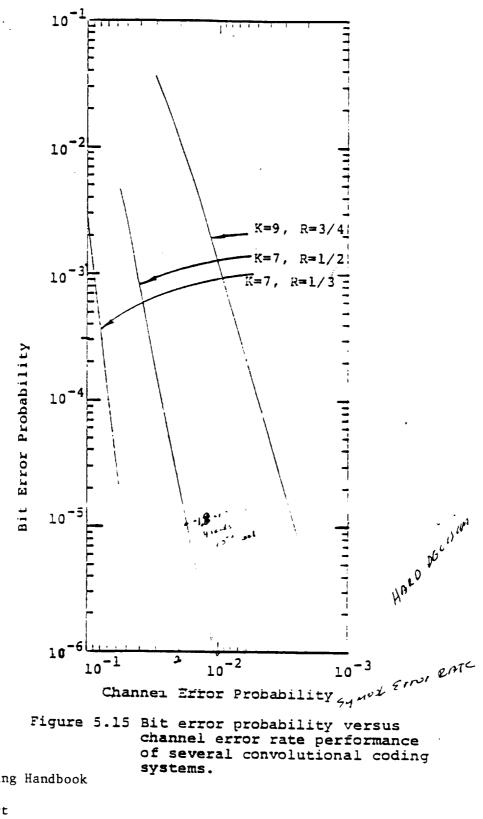

The memo references two reports by Joe Oldenwalder concerning Error Control Coding. These references are the references 1 and 2 at the end of this report. Mr. Dobrotin's memo contains a curve drawn from reference 1 (Figure 5-11, page 124 of reference 1) which I have included herein as Figure 1. Figure 2 of this report depicts the unaltered curves of Figure 1 drawn from my own copy of reference 1. Figure 3 of this report depicts the unaltered curves of Figure 7.4, page 198 of reference 1 for concatenated code block error probability performance for K = 7, rate = 1/2 convolutional inner codes and various R/S, 8 bit/symbol, codes for the outer code. Figure 4 of this report depicts the bit error probability performance for K = 7, rate = 1/2 convolutional code inner codes and various R/S, 8 bit/symbol, codes for the outer code.

Inspection of the curves of Figure 1 and Figure 3 of this report and noting the circled points of Figure 3, we see Mr. Dobrotin's added curve for the R/S concatenated 8 bits per symbol, 8 symbol correcting outer code has been transposed correctly with 2.8 dB  $E_b/N_o$  required to achieve Bit Error Probability of 10<sup>-5</sup> for the concatenated system and approximately 4.4 dB  $E_b/N_o$  required for the Viterbi soft decision Rate 1/2 K = 7 coding along. Thus the conclusion by Mr. Dobrotin that the concatenation of the

R/S code on the convolutional code does result in a Bit Error Probability of about  $10^{-5}$  for an apparent reduction in  $E_b/N_b$  of 4.4 dB - 2.8 dB = 1.6 dB.

(One might be interested in knowing that the same curve as Figure 3 of this report (Figure 7.3, page 197 of Reference 1) appears in many literature sources and, in particular, occurs in Figure 17.3, page 536 of Reference 3).

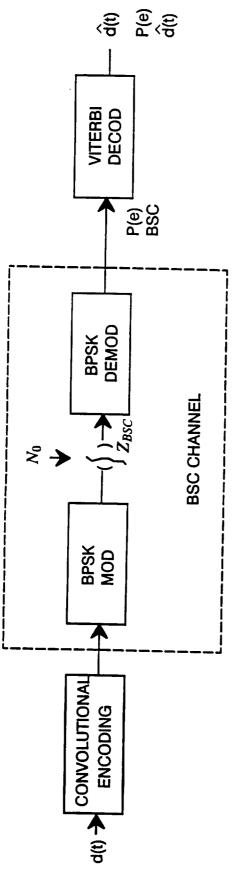

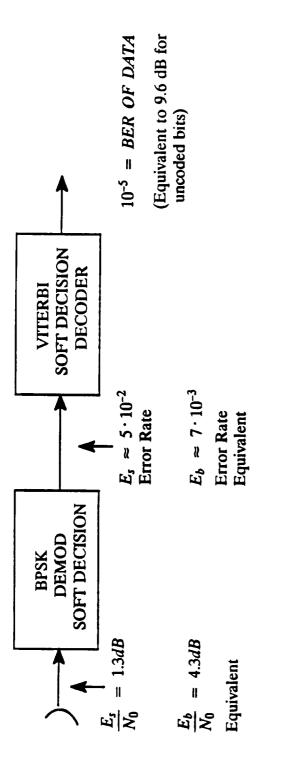

So, Mr. Dobrotin's conclusion is verified **if** all synchronization has been achieved. A VERY BIG IF! The carrier recovery loop and the bit synchronizer and the Viterbi decoder work with raw  $E_b/N_o$  levels. By lowering the Power Amplifier from 25 watts to 20 watts (a .96910013 or approximately a 1.0 dB loss), approximately 1 dB loss in raw  $E_b/N_o$  is incurred at the carrier recovery loop and bit synchronizer input and the error rate of the BPSK demodulated data to the Viterbi decoder will now correspond to a 1 dB lower  $E_b/N_o$  BPSK signal. The bit error rate into the Viterbi is about  $5.10^{-2}$  (based on 5 dB  $E_b/N_o$  input approximately), and a 1 dB reduction yields a bit error rate of about  $8.10^{-1}$  for the BPSK signal, NOT INCLUDING POSSIBLE SYNC LOSS AT CARRIER RECOVERY LOOP OR AT BIT SYNC OR VITERBI NODE SYNC LOSS.

Table 5.3, page 135, of Reference 1 depicts Average Error Burst Length in Bits and Average Number of Errors per Burst for the K = 7 Rate 1/2 system with soft decision. Inspecting the Table (Table 1 of this report) we see a reduction of 1 dB in  $E_b/N_o$  from 4 dB to 3 dB would cause a burst length increase of only 1.4 bits on the average from 6.2 bits to 7.6 bits. However, a decrease of 1 dB from 3.0 dB to 2.0 dB in  $E_b/N_o$ would cause an average burst length increase of 3.3 bits from 7.6 to 10.9 bits.