JPL Publication 92-18

# Design and Qualification of the SEU/TD Radiation Monitor Chip

Martin G. Buehler Brent R. Blaes George A. Soli Nasser Zamani

Kenneth A. Hicks

October 1, 1992

Prepared for

Lincoln Laboratory

Massachusetts Institute of Technology

Defense Advanced Research Projects Agency

U.S. Department of Defense

and

National Aeronautics and Space Administration

by

Jet Propulsion Laboratory California Institute of Technology Pasadena, California A-CR-192797) DESIGN AND IFICATION OF THE SEU/TO ATION MONITOR CHIP (JPL) 52

| 1. Report No. JPL Pub 92-18                                                                                                                                                                                                                                                       | 2. Government Accession No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3. Re                                                                           | cipient's Catalog N                                                                                           | o.                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| 4. Title and Subtitle                                                                                                                                                                                                                                                             | Land to the state of the state | 5. Re                                                                           | port Date                                                                                                     |                                                                               |

| Design and Qualification o                                                                                                                                                                                                                                                        | f the SFU/TD Radiation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                 | ctober 1, 1992                                                                                                |                                                                               |

| Monitor Chip                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                 | rforming Organizatio                                                                                          | in Code                                                                       |

| 7. Author(s)Martin G. Buehler,<br>Soli, Nasser Zamani, and Ke                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8. Pe                                                                           | rforming Organizatio                                                                                          | n Report No                                                                   |

| 9. Performing Organization Name ar                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10. W                                                                           | ork Unit No.                                                                                                  |                                                                               |

| JET PROPULSION LAB                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 11 Cc                                                                           | entract or Grant No                                                                                           |                                                                               |

| California Institu<br>4800 Oak Grove Dri                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                 | NAS7-918                                                                                                      | •                                                                             |

| Pasadena, Californ                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 13. Ty                                                                          | pe of Report and Pe                                                                                           | riod Covered                                                                  |

| 12. Sponsoring Agency Name and Ad                                                                                                                                                                                                                                                 | dress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | J                                                                               | PL Publication                                                                                                |                                                                               |

| NATIONAL AERONAUTICS AND                                                                                                                                                                                                                                                          | SPACE ADMINISTRATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 14 50                                                                           | onsoring Agency Co                                                                                            |                                                                               |

| Washington, D.C. 20546                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                 | 1 BW-397-70-00-0                                                                                              |                                                                               |

| This report describes the describes the describes and the Mid-Course Space consists of a custon-design for monitoring total dose.  In addition the Radiation Me Process Monitor and the Reliof the CMOS fabrication profunctional yield of 94.6 per MOSFETs passed the hermetical | on Monitor chip. The Rade Experiment Satellite (MS) ed 4-bit SRAM for heavy iconitor chip was tested alconitor and Fault chips. cess. The SEU/TD Radiation cent. Forty-three (43) Second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | iation I<br>(). The<br>on detection<br>ong wit<br>These<br>on Monic<br>SEU SRAI | Monitor is schede Radiation Moniction and three three diagnost chips revealed tor chip had an Ms and 14 Total | uled to<br>tor chip<br>MOSFETs<br>ic chips:<br>the quality<br>initial<br>Dose |

| 17. Key Words (Selected by Author(s) Components Electronics and Electrical I Quality Assurance and Relial                                                                                                                                                                         | Engineering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                 | ment<br>fied Unlimited                                                                                        |                                                                               |

| 19. Security Classif. (of this report)                                                                                                                                                                                                                                            | 20. Security Classif. (of this                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | page)                                                                           | 21. No. of Pages                                                                                              | 22. Price                                                                     |

| Unclassified                                                                                                                                                                                                                                                                      | Unclassified                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                 | 43                                                                                                            |                                                                               |

| one rassified one rassified                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                                                                               |                                                                                                               | 1                                                                             |

•

## Design and Qualification of the SEU/TD Radiation Monitor Chip

Martin G. Buehler Brent R. Blaes George A. Soli Nasser Zamani Kenneth A. Hicks

October 1, 1992

#### Prepared for

Lincoln Laboratory

Massachusetts Institute of Technology

Defense Advanced Research Projects Agency

U.S. Department of Defense

and

National Aeronautics and Space Administration

by

Jet Propulsion Laboratory California Institute of Technology Pasadena, California The research described in this publication was carried out by the Center for Space Microelectronics Technology, Jet Propulsion Laboratory, California Institute of Technology, and was sponsored by the Lincoln Laboratory (LL), Massachusetts Institute of Technology; the U. S. Defense Advanced Research Agency (DARPA); the U. S. Department of Defense (DoD); and the National Aeronautics and Space Administration (NASA). The Radiation Monitor effort was sponsored by LL under Task Plan No. 80-3256 (RE152/A-472). The other portions of this effort were developed under Task Plan No. 50-2382D (NAS7-918 #RE191) where the Process Monitor was sponsored by NASA, the Reliability Chip was sponsored by DARPA, and the Fault Chip was sponsored by DoD.

Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not constitute or imply its endorsement by the United States Government; Lincoln Laboratory, Massachusetts Institute of Technology; or the Jet Propulsion Laboratory, California Institute of Technology.

#### **EXECUTIVE SUMMARY**

This report describes the design, fabrication, and testing of the Single-Event Upset/Total Dose (SEU/TD) Radiation Monitor chip and three diagnostic chips. The Radiation Monitor is scheduled to fly on the Mid-Course Space Experiment Satellite (MSX). The Radiation Monitor chip consists of a custom-designed 4-kbit SRAM for heavy ion detection and three MOSFETs for monitoring total dose. They were fabricated in a  $1.6\mbox{-}\mu\text{m}$  n-well double-level metal CMOS process brokered by MOSIS as run NO6J. These chips were fabricated with diagnostic chips on three wafers.

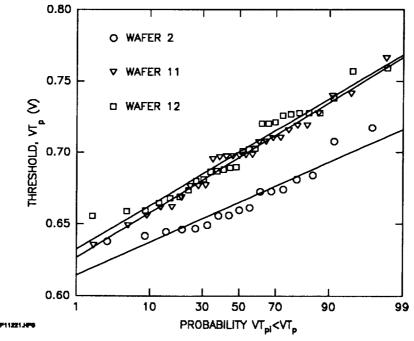

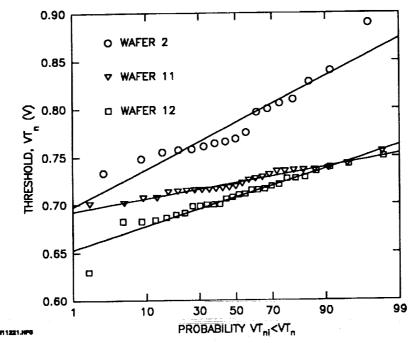

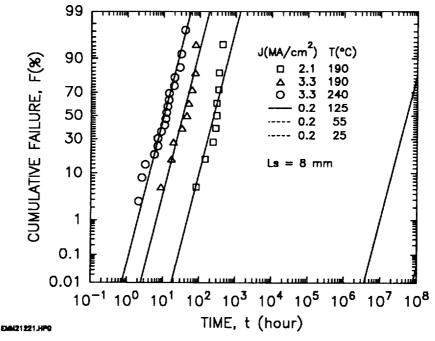

The diagnostic chips are the Process Monitor and the Reliability and Fault chips. The following results were measured from wafers 2, 11, and 12. Metal1 had no breaks in 9.0 meters and no metal bridges in 1.8 meters. Metal2 had no breaks in 7.6 meters and no metal bridges in 1.5 meters. Poly had 1 break in 13.6 meters and 2 poly bridges in 2.7 meters. Oxide pinhole density for n-MOSFETs was 17 defects/cm² and for p-MOSFETs was 5 defects/cm². Poly, Metal1, and Metal2 step resistances were excellent, being about a few percent. Metal2 electromigration results were excellent with  $t_{0.01}$  = 416 years. Standard deviations for p-Poly, n-Poly and n-Diff contact resistances were higher than expected.

To choose superior wafers, it is necessary to acquire data identified by wafer. In addition, the calibration of the Radiation Monitor's SRAM particle response requires accurate intra-chip data. Inter-wafer process monitor MOSFET threshold voltages varied widely from 14 to 37 mV depending on the wafer and overestimated the SRAM threshold variability. In addition results from wafers 2 were distinctly different from wafers 11 and 12. Inter-chip inverter-matrix thresholds were tight and varied from 2 to 8 mV depending on inverter geometry. For the same geometry these inter-chip results agreed closely with SRAM thresholds, which varied by 10 mV.

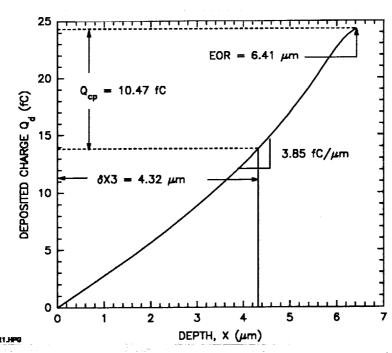

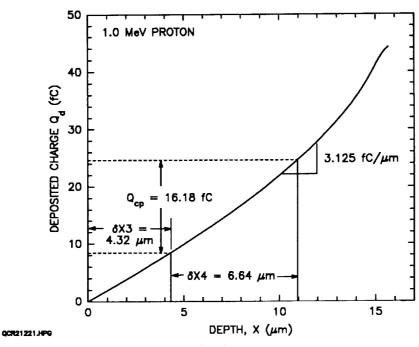

The 4-kbit SEU SRAM was designed to monitor the heavy ion upset rate. The SRAM has an externally adjustable offset voltage,  $V_0$ . The SRAM was irradiated with 0.55 and 1.0 MeV protons and 4.7 MeV alpha particles. From an analysis of the SRAM particle upset rate, it was determined that the overlayer thickness is 4.32  $\mu$ m and collection depth is 6.64  $\mu$ m. Using this data a LET = 2.88 MeV·cm²/mg is estimated for the MSX operating conditions of  $V_0$  = 5 V.

The total dose MOSFETs are a calibrator p-MOSFET, a floating gate p-MOSFET, and a standard n-MOSFET. The calibrator and standard MOSFETs monitor total dose via the threshold shift due to radiation-induced oxide charging. The floating gate MOSFET monitors dose via the channel conductance shift of the floating gate p-MOSFET due to the accumulation of gate charge.

The SEU/TD Radiation Monitor chip had an initial functional yield of 94.6 percent. SRAM electrical tests consisted of power up, walking ones, checker board, access time, and standby power tests. The chips were given a static powered burn-in for 24 hours at 125°C. During electrical tests, various failure modes were detected including stuck memory cells, large chip stand-by leakage, and large transistor leakage. It should be noted that the total dose MOSFETs have unprotected gates and 29 MOSFETs were lost during the hermetic seal lidding operation. It appears that normal ESD prevention practices were not sufficient to protect MOSFETs with unprotected gates. Forty-three (43) SEU SRAMs and 14 Total Dose MOSFETs passed the hermeticity and final electrical tests and were delivered to LL.

#### **ABSTRACT**

This report describes the design, fabrication, and testing of the Single-Event Upset/Total Dose (SEU/TD) Radiation Monitor chip. The Radiation Monitor is scheduled to fly on the Mid-Course Space Experiment Satellite (MSX). The Radiation Monitor chip consists of a custom-designed 4-kbit SRAM for heavy ion detection and three MOSFETs for monitoring total dose.

In addition the Radiation Monitor chip was tested along with three diagnostic chips: Process Monitor and the Reliability and Fault chips. These chips revealed the quality of the CMOS fabrication process. The SEU/TD Radiation Monitor chip had an initial functional yield of 94.6 percent. Forty-three (43) SEU SRAMs and 14 Total Dose MOSFETs passed the hermeticity and final electrical tests and were delivered to LL.

#### **ACKNOWLEDGMENTS**

The chips described in this report were fabricated by commercial CMOS foundries through the efforts of the University of Southern California, Information Sciences Institute, Metal-Oxide-Silicon Implementation Service (MOSIS). The efforts of Vincent Sferrino, Lincoln Laboratory, in providing the opportunity to fly the SEU/TD Radiation Monitor chip and in serving as the interface to the satellite system are gratefully acknowledged. Finally the authors wish to recognize the enthusiasm of Paul Robinson in encouraging the use of his FET probe as a radiation monitor.

#### Table of Contents

| 1.0 INTRODUCTION 1.1 Overview 1.2 Scope of Work                                                                                                                                                                                                                                                                           | 1<br>1<br>5                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 2.0 DIAGNOSTIC TEST CHIPS 2.1 Fault Chip 2.2 Process Monitor 2.3 Reliability Chip 2.4 Diagnostic Test Chip Conclusions                                                                                                                                                                                                    | 5<br>6<br>11<br>14<br>16                           |

| 3.0 SEU/TD RADIATION MONITOR 3.1 SEU SRAM Cell 3.2 SEU SRAM Analysis 3.2.1 Layer Thickness Analysis 3.2.2 Layer Thickness Dispersion Analysis 3.3 MOSFET Total Dose Dosimeters 3.3.1 Calibrator p-MOSFET Dosimeter 3.3.2 Floating Gate p-MOSFET Dosimeter 3.3.3 Standard n-MOSFET Dosimeter 3.4 Advanced MOSFET Dosimetry | 16<br>16<br>23<br>24<br>26<br>31<br>31<br>32<br>33 |

| 4.0 SEU/TD RADIATION MONITOR SCREENING PROCEDURES                                                                                                                                                                                                                                                                         | 38                                                 |

| 5.0 SEU/TD SYSTEM INTERFACE CIRCUITRY                                                                                                                                                                                                                                                                                     | 40                                                 |

| 6.0 REFERENCES                                                                                                                                                                                                                                                                                                            | 42                                                 |

| Figures                                                                                                                                                                                                                                                                                                                   |                                                    |

| 1. Photomicrograph of SEU/TD radiation monitor chip.                                                                                                                                                                                                                                                                      | 2                                                  |

| 2. Schematic diagram for SEU/TD chip showing the four devices.                                                                                                                                                                                                                                                            | 4                                                  |

| 3. Cross section of SEU SRAM.                                                                                                                                                                                                                                                                                             | 4                                                  |

| 4. Chips fabricated on MOSIS run NO6J.                                                                                                                                                                                                                                                                                    | 6                                                  |

| 5. Inverter threshold voltage dependence on the MOSFET geometry factor $\ensuremath{\beta_{\text{r}}}.$                                                                                                                                                                                                                   | 8                                                  |

| 6. Distribution of p-MOSFET threshold voltage for Wafers 2, 11, a                                                                                                                                                                                                                                                         | and 12. 13                                         |

| 7. Distribution of n-MOSFET threshold voltage for Wafers 2, 11, a                                                                                                                                                                                                                                                         | and 12. 14                                         |

| 8. Metal2 electromigration failure rates shown for three stress p                                                                                                                                                                                                                                                         | points. 15                                         |

| 9. The SEU SRAM circuit biased in the sensitive or capture state.                                                                                                                                                                                                                                                         | . 19                                               |

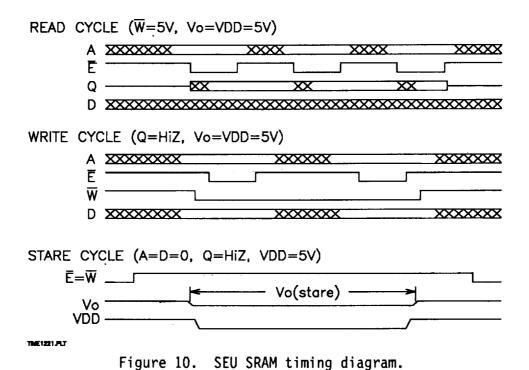

| 10. | SEU SRAM timing diagram.                                                                                                                    | 19 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------|----|

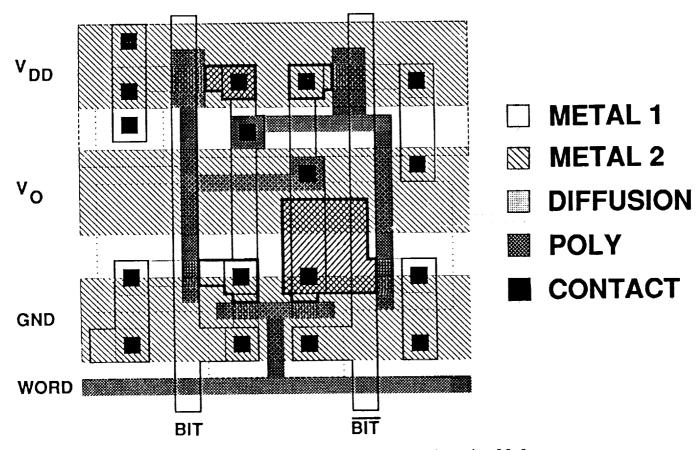

| 11. | Memory cell layout.                                                                                                                         | 20 |

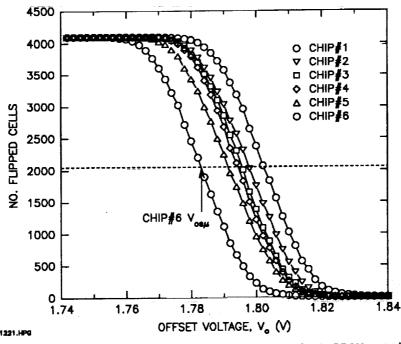

| 12. | SRAM spontaneous flip response for six SEU SRAMs taken from Wafer 2.                                                                        | 20 |

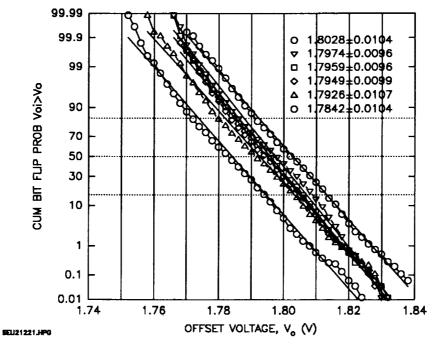

| 13. | Detector response shown in Figure 12 is shown here as a cumulative distribution.                                                            | 21 |

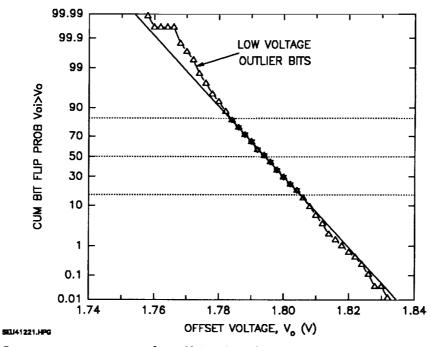

| 14. | Detector response for Chip #4 shown in Figure 12 where outlier points are included.                                                         | 21 |

| 15. | The temperature dependence of the inverter threshold voltage.                                                                               | 22 |

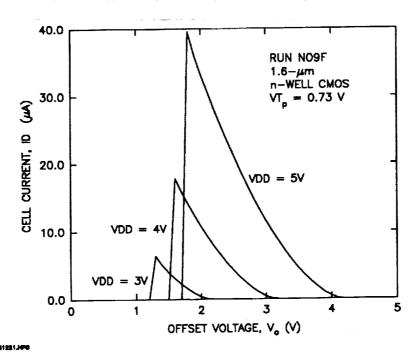

| 16. | Current drawn by the memory cell.                                                                                                           | 22 |

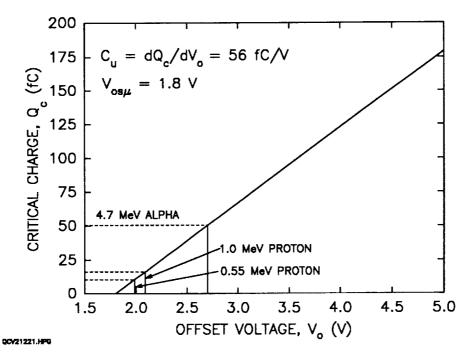

| 17. | SRAM critical charge response for Node-V2 of Figure 9 calculated using SPICE Level-2.                                                       | 29 |

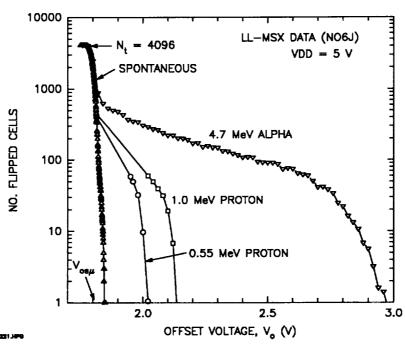

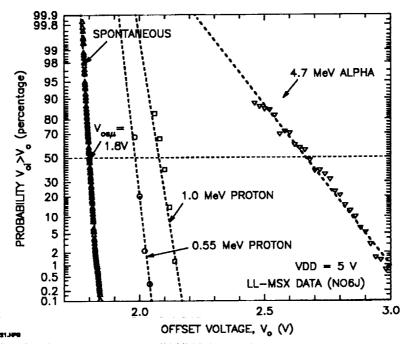

| 18. | Number of flipped cells for alpha particles and protons shown relative to the spontaneous bit flip response for a stare time of one second. | 29 |

| 19. | SRAM upset probability distribution for alpha particles and protons shown relative to the spontaneous bit flip response.                    | 30 |

| 20. | Charge deposited by 0.55 MeV protons in silicon. This charge is used to calculate the overlayer thickness, $\delta$ X3.                     | 30 |

| 21. | Charge deposited by 1.0 MeV protons in silicon.                                                                                             | 31 |

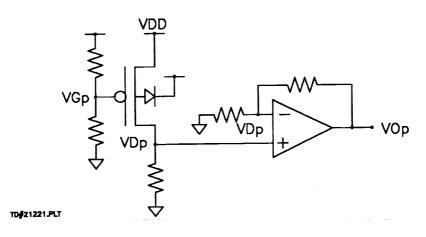

| 22. | Calibrator p-MOSFET operated as a total dose dosimeter.                                                                                     | 36 |

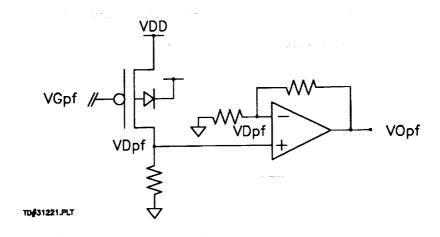

| 23. | Floating gate p-MOSFET operated as a total dose dosimeter.                                                                                  | 36 |

| 24. | Standard n-MOSFET operated as a total dose dosimeter.                                                                                       | 37 |

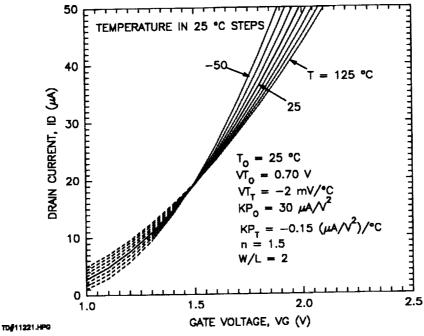

| 25. | p-MOSFET operated as a total dose dosimeter where the gate voltage is proportional to the dose.                                             | 37 |

| 26. | Temperature dependence of the p-MOSFET dosimeter showing the temperature independent point at ID $_0$ = 19.2 $\mu$ A and VG $_0$ = 1.5 V.   | 38 |

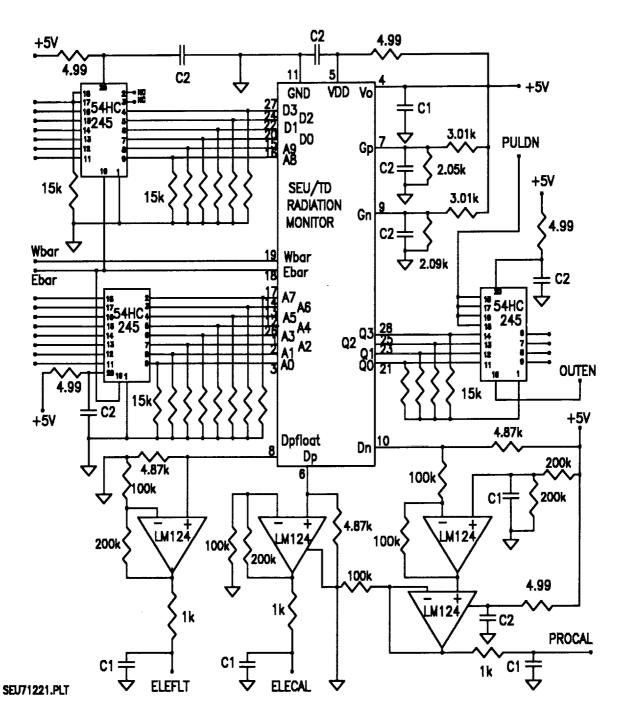

| 27. | Diagram of the MSX Radiation Experiment SEU/TD computer interface electronics.                                                              | 41 |

|     | Tables                                                                                                                                      |    |

| 1.  | Pinout of the SEU/TD chip.                                                                                                                  | 3  |

| 2.  | Defect density test structure test results.                                                                                                 | 9  |

| 3   | CMOS gate-oxide pinhole data base.                                                                                                          | 9  |

| 4.  | Matrix test structure results.                                  | 10 |

|-----|-----------------------------------------------------------------|----|

| 5.  | Process monitor test results (Part 1).                          | 11 |

| 6.  | Process monitor test results (Part 2).                          | 12 |

| 7.  | Threshold voltage values for Wafers 3, 11, and 12.              | 13 |

| 8.  | Metal2 electromigration data base.                              | 15 |

| 9.  | Dimensions of SEU SRAM MOSFETs and drain areas.                 | 23 |

| 10. | SEU SRAM V <sub>OS</sub> results.                               | 23 |

| 11. | Inverter matrix and SEU SRAM test result comparison.            | 23 |

| 12. | Schematic view of the proton paths from the source to the SRAM. | 28 |

| 13. | $\delta$ X3, $\delta$ X4, and LET values.                       | 28 |

| 14. | Dimensions of total dose MOSFETs.                               | 35 |

| 15. | Chip inventory.                                                 | 39 |

| 16. | Parts screening procedures.                                     | 40 |

TELEMENT OF THE THEORY OF THE PROPERTY OF THE

### Design and Qualification of the SEU/TD Radiation Monitor Chip

#### 1.0 INTRODUCTION

This document describes the development of a Single-Event Upset (SEU) and Total Dose (TD) Radiation Monitor chip which was delivered to the Massachusetts Institute of Technology's Lincoln Laboratory (LL) by the Jet Propulsion Laboratory (JPL). This chip is scheduled to be flown on the Mid-Course Space Experiment Satellite (MSX) scheduled to launch in 1992.

This chip was developed by JPL's VLSI Technology Group as part of an on-going program devoted to the development of qualification techniques for VLSI circuits. This chip provides a means of establishing the connection between ground test results and space test results. The Group has developed several chips for flight test. The first test chip was delivered in March of 1986. Twelve test chips were delivered to the Air Force Geophysics Laboratory (AFGL) and were included on the Combined Release and Radiation Effects Satellite (CRRES) launched July 25, 1990 [1,2].

Currently a radiation monitor (RADMON) is being developed for flight on the Space Technology Research Vehicle (STRV), which is scheduled for launch in December 1993. It consists of a total dose monitor and a 14 chip, 3-bin particle spectrometer. Our long range goal is to develop the RADMON so that it can serve as a SEU/TD Radiation Monitor on a spacecraft to alert the control system to radiation hazards and to explain radiation-induced system upsets. In addition the data accumulated from these chips will allow mapping of the proton and cosmic-ray environments.

#### 1.1 Overview

The objective of this task is to develop a custom radiation monitor with the same (CMOS) technology used to fabricate the circuitry used in the spaceborne computers and signal processors. Thus the results observed from the radiation monitor can be directly related to the functionality of the spaceborne electronics. The SEU/TD Radiation Monitor will be used to determine the total accumulated dose and SEU rates. These results will be compared to the performance of the signal processor chips developed by Lincoln Laboratory.

The space radiation effects of concern to modern microcircuits are Single-Event Upsets (SEUs) and Total Ionizing Dose (TD). In the SEU effect, cosmic rays and high energy protons, that undergo electronic reactions with the integrated circuits, deposit sufficient charge in memory cells and latches to flip bits and corrupt data. Such events do not induce any physical damage and thus are nondestructive. On the other hand, in the TD effect, gate oxides are charged, which is a permanent change. This shifts transistor threshold voltages and

reduces the channel mobility. A change in these parameters degrades the performance of CMOS integrated circuits (ICs) by changing the propagation delay [3].

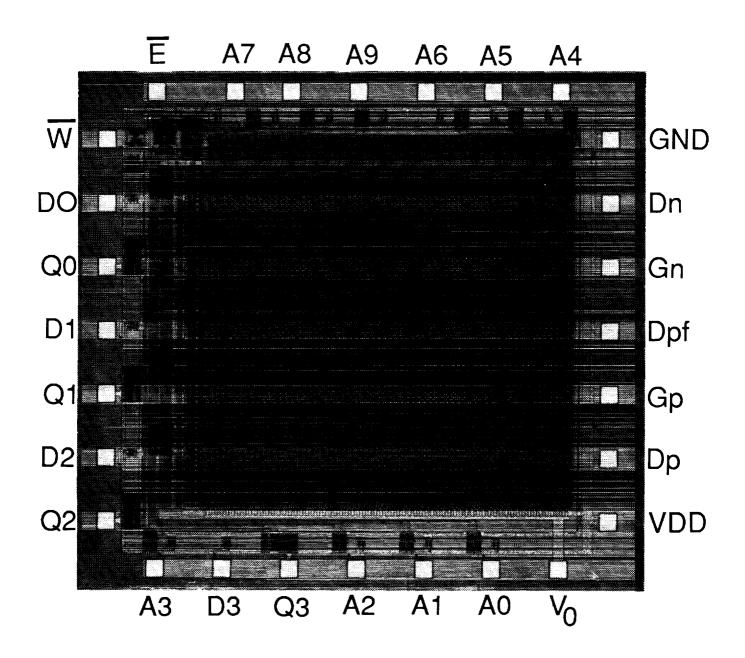

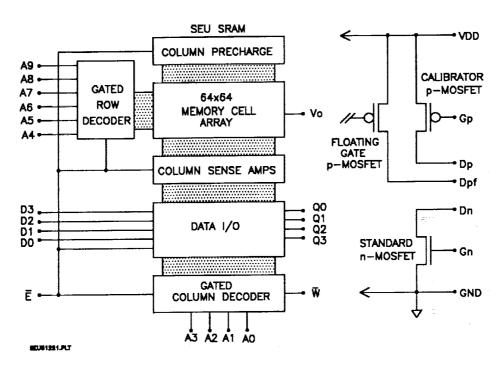

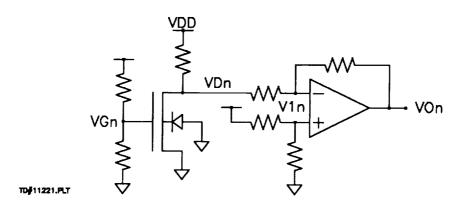

A photomicrograph of the 28-pin chip is shown in Figure 1 and the pin numbers are listed in Table 1. A block diagram of the chip is shown in Figure 2, where it is seen that the chip contains the following devices: (a) SEU SRAM, (b) standard n-MOSFET, (c) calibrator p-MOSFET, and (d) floating gate p-MOSFET.

The floating gate MOSFET experiences channel-conductance shifts, which are due to radiation-induced gate charge. To monitor total ionizing dose effects, floating gate drain current is measured and compared to the drain current from a calibrator MOSFET so the radiation-induced floating gate charge can be determined.

Table 1. Pinout of the SEU/TD chip.

| PIN DESCRIPTION PIN        | DESIGNATION | PIN NO.           |

|----------------------------|-------------|-------------------|

| Power: VDD = 5 V           | VDD         | 5                 |

| Ground: 0 V                | GND         | 11                |

| Offset Voltage: Vo = 5 V   | Vo          | 4                 |

| SRAM Control:              | Ebar        | 18                |

|                            | Wbar        | 19                |

| SRAM Data In:              | D0          | 20                |

|                            | D1          | 22                |

|                            | D2          | 24                |

|                            | D3          | 27                |

| SRAM Data Out:             | Q0          | 21                |

|                            | Q1          | 23                |

|                            | Q2          | 25                |

|                            | Q3          | 28                |

| SRAM Address:              | <b>A</b> 0  | 28<br>3<br>2<br>1 |

|                            | A1          | 2                 |

|                            | A2          |                   |

|                            | A3          | 26                |

|                            | A4          | 12                |

|                            | A5          | 13                |

|                            | A6          | 14                |

|                            | A7          | 17                |

|                            | <b>A8</b>   | 16                |

|                            | A9          | 15                |

| n-MOSFET Standard Gate     | Gn          | 9                 |

| n-MOSFET Standard Drain    | Dn          | 10                |

| p-MOSFET Calibrator Gate   | Gp          | 7                 |

| p-MOSFET Calibrator Drain  |             | 6                 |

| p-MOSFET Floating Gate Dra | ain Dpfloat | 8                 |

Figure 1. Photomicrograph of SEU/TD radiation monitor chip which is  $3.12 \text{ mm} \times 3.29 \text{ mm}$ .

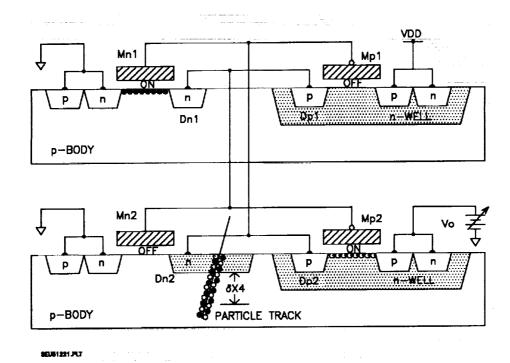

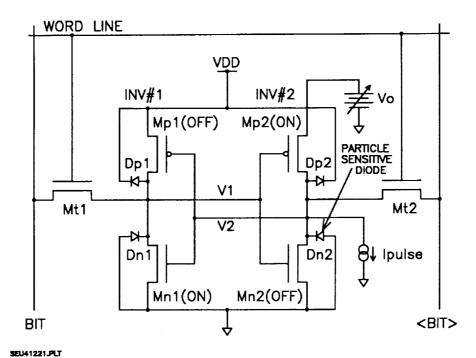

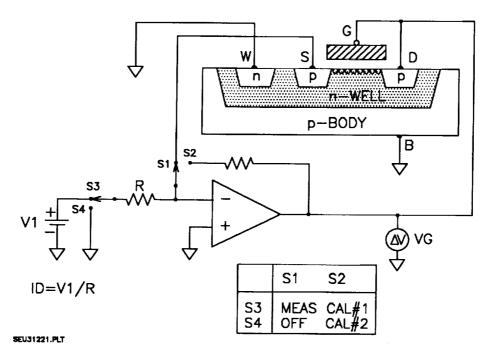

The SRAM is a classical six-transistor cell that has been customized as indicated by the cross-sectional diagram shown in Figure 3. The cell was modified by adding an offset voltage,  $V_0$ , to one side of the memory cell. This allows the sensitivity of the cell-to-particle upset to be adjusted externally. In addition the drain, Dn2, was enlarged to increase the cell cross-section-to-particle capture. In the LL spacecraft implementation,  $V_0$  is connected to VDD in order to simplify the drive circuitry. Thus the SRAM sensitivity is fixed so that the cells can be upset by particles with a LET (Linear Energy Transfer) in excess of 2.88 MeV·cm²/mg. The  $V_0$  was used in ground tests, however, to select SRAMs with tight initial upset characteristics and to calibrate the cell response with proton and alpha particle radiation.

Figure 2. Schematic diagram for SEU/TD chip showing the four devices.

Figure 3. Cross section of SEU SRAM showing a particle track through diode Dn2 which can initiate a bit flip. The n-MOSFETs, Mn1 and Mn2, and p-MOSFETs, Mp1 and Mp2, are also shown in the circuit schematic in Figure 9.

#### 1.2 Scope of Work

This chip was fabricated through MOSIS (Metal Oxide Silicon Implementation Service) in a  $1.6-\mu m$  double-level metal n-well CMOS process where the p-MOSFETs substrate was doped to  $5 \times 10^{14}$  cm<sup>-3</sup>. The chips were fabricated on 4-inch diameter wafers which contained about 25 complete chips. JPL received three wafers from MOSIS. These wafers were scribed and assembled into 75 packages. Six unscreened parts were delivered to LL for prototyping purposes. Then 50 were hermetically sealed, screened, and 43 parts were delivered to LL. The following scope of work was established between JPL and LL.

- 1) JPL will design the SEU/TD Radiation Monitor, submit the design to a CMOS foundry for fabrication, and package in 75, 600-mil wide, 28-pin ceramic Dual Inline Packages (DIPs) with lids.

- 2) JPL will perform initial functional testing of the monitor and deliver 6 unscreened and unlidded parts to LL.

- 3) JPL will see that the packaged parts are hermetically sealed and will perform screening tests, which are a subset of MIL-STD-883C screening procedures for Class-B devices.

- 4) JPL will perform final functional testing, monitor grading, and conduct a preshipment review.

- 5) JPL will deliver up to 50 screened parts to LL.

- JPL will deliver test documentation to LL.

- 7) JPL will calibrate the monitor as a particle detector.

- 8) LL will provide JPL with all ground test and satellite data acquired from the monitor in a format convenient for JPL analysis.

- 9) LL will provide JPL with specific satellite orbital information to allow JPL to correlate the radiation monitor data to known space environmental data.

It should be noted that only 43 screened parts were delivered to LL when 50 were requested. The number of 43 was an acceptable number since only one part was intended for flight. The remaining parts were used by LL for ground radiation tests.

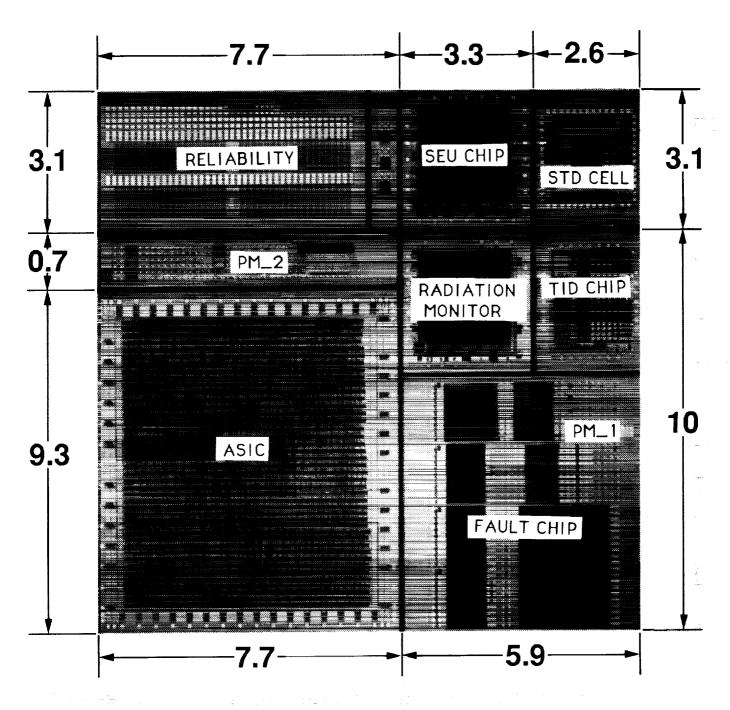

#### 2.0 DIAGNOSTIC TEST CHIPS

A comprehensive set of diagnostic test structures was included with the SEU/TD Radiation Monitor chip as seen in Figure 4. These chips were included on the MOSIS NO6J fabrication run and were used to analyze the quality of the fabrication run. As seen in the figure, the diagnostic test chips consist of Process Monitors PM 1 and PM 2, Reliability Chip, the Fault Chip, the Total Ionizing Dose (TD) Chip, and the Single-Event-Upset (SEU) chip. In order to reduce the cost of the fabrication, this run was shared with an ASIC chip and a standard cell (STD CELL) chip. A brief description follows of the test structures and their test results.

Figure 4. Chips fabricated on MOSIS run NO6J. Dimensions in mm.

#### 2.1 Fault Chip

The fault chip consists of a set of test structures which provide statistics on the VLSI defect densities and distributions of component characteristics. The defect densities measured on the fault chip are (a) gate oxide pinholes, (b) Poly-Metal pinholes, (c) Poly-Poly shorts, (d) Metall-Metall shorts, (e) Metall-Metall shorts, (f) Poly wire opens, (g) Metall wire opens, and (h) Metall wire opens.

A summary of the results obtained from fault chip defect density test structures is given in Table 2. The most troublesome defect is the gate oxide defect. An analysis for the gate oxide defect density follows from the Poisson yield expression:

(1)

$$Y = \exp(-DA)$$

where D is the defect density and A is the gate oxide area. The yield can be expressed in terms of the failure rate, F or Y = 1-F. For very small failure rates, D = F/A. In obtaining this relationship, the approximation  $\ln(1-x) \approx -x$  was used. In calculating the gate oxide area, A, the dimensions 1.6  $\mu$ m by 2.4  $\mu$ m were used. The defect density for n-pinholes is D<sub>n</sub> = 17 defects/cm<sup>2</sup> and for p-pinholes D<sub>p</sub> = 5 defects/cm<sup>2</sup>.

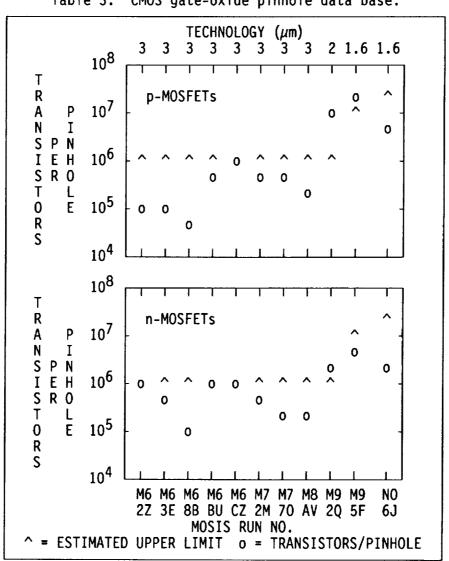

These pinhole densities are typical of values previously obtained from MOSIS fabrication runs as seen in Table 3. Such defects should be caught at test time and should represent only a yield loss. Overall the results from the defect density test structures are typical of other CMOS fabrication runs we have analyzed and are acceptable for this application.

The other test structures found on the fault chip are the matrix test structures. These structures are used to assess parameter variability, which is an indicator of the local control obtained in the fabrication process. The structures are: (a) Linewidth/Step Matrix [4], (b) Contact Matrix [5], and (c) Inverter Matrix [6]. The results are listed in Table 4.

A discussion of these results leads to the following conclusions. Results from the Linewidth/Step Matrix reveal that step-coverages are acceptable for the step; resistance percentage is satisfactorily low, being less than 3 percent. Results from the Contact Matrix indicate that the contact resistance standard deviations are high for Metall-p-Poly, Metall-n-Poly, and Metall-n-Diff. Although these standard deviations are high, they are not judged to compromise the devices fabricated on this run.

The standard deviations for the Inverter Matrix [4] are of interest because they are directly related to the variations seen in the offset voltages of the SEU SRAM. The inverter threshold voltage is given by:

(2)

$$VT_{inv} = \frac{VDD + VT_n\sqrt{B_r} - VT_p}{1 + \sqrt{B_r}}$$

where  $\text{VT}_{\text{n}}$  is the n-MOSFET threshold voltage, and  $\text{VT}_{\text{p}}$  is the magnitude of the p-MOSFET threshold voltage. The Beta factor is:

(3)

$$\beta_r = \frac{\beta_n}{\beta_p} = \frac{KP_n(W_n - \Delta W_n)(L_p - \Delta L_p)}{KP_p(W_p - \Delta W_p)(L_n - \Delta L_n)}$$

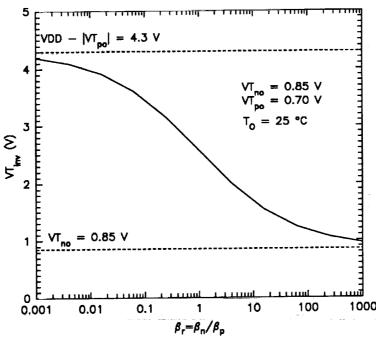

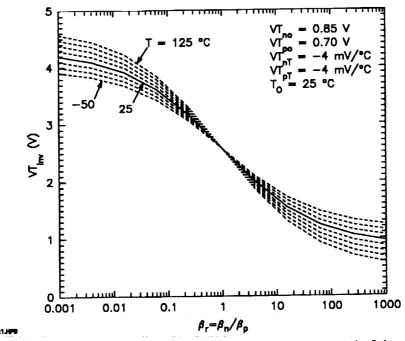

where KP =  $\mu_0 C_{OX}$ ,  $\mu_0$  is the channel mobility,  $C_0$  is the gate oxide capacitance/area, W and L are the as-drawn channel width and channel length, respectively, and  $\Delta W$  and  $\Delta L$  are the deviations from the as-drawn values. The inverter threshold equation is plotted in Figure 5 and shows that for  $\beta_r \rightarrow 0$ ,  $VT_{inv} = VDD - VT_p$  and for  $\beta_r \rightarrow \infty$ ,  $VT_{inv} = VT_n$ .

A useful parameter is the geometry factor,  $G_{ro}$ , which is calculated using as-drawn MOSFET dimensions:

$G_{ro} = W_n L_p / (W_p L_n)$ . The variance of the inverter threshold voltage is:

(4)

$$VT_{inv\sigma}^2 = \frac{VT_{p\sigma}^2}{(1 + \sqrt{\beta_r})^2} + \frac{\beta_r VT_{n\sigma}^2}{(1 + \sqrt{\beta_r})^2} + \frac{\beta_r G(VDD - VT_n - VT_p)^2}{4(1 + \sqrt{\beta_r})^4}$$

where

(5)

$$G = \frac{W_{n\sigma}^2}{W_{en}^2} + \frac{W_{p\sigma}^2}{W_{ep}^2} + \frac{L_{n\sigma}^2}{L_{en}^2} + \frac{L_{p\sigma}^2}{L_{ep}^2}$$

where W<sub>e</sub> = W -  $\Delta$ W and L<sub>e</sub> = L -  $\Delta$ L. These equations show that for  $\beta_r$  = 0,  $VT_{inv}$  =  $(VDD - VT_{p\mu}) \pm VT_{p\sigma}$  and for  $\beta_r$  =  $\infty$ ,  $VT_{inv}$  =  $VT_{n\mu} \pm VT_{n\sigma}$ . Thus from Table 4, the standard deviation for  $VT_{p\sigma}$  = 6 mV and  $VT_{n\sigma}$  = 3 mV. Also the deviation for the "FAT FET" inverter is 2 mV and this indicates good local control of the ion implantation which controls the threshold voltages. These values are typical of those seen on previous MOSIS runs.

Figure 5. Inverter threshold voltage dependence on the MOSFET geometry factor  $\beta_r$ .

Table 2. Defect density test structure test results

| TEST STRUCTURE      | DEFECT TYPE          | NUMBER<br>DEFECTS | LENGTH<br>meters | NO. MOSFETs<br>MEASURED        |

|---------------------|----------------------|-------------------|------------------|--------------------------------|

| COMB RESISTOR       | METAL1-METAL1 SHORTS | 0                 | 1.8              |                                |

|                     | METAL2-METAL2 SHORTS | 1                 | 1.5              |                                |

|                     | POLY-POLY SHORTS     | 2                 | 2.7              |                                |

| SERPENTINE RESISTOR | METAL1 WIRE OPENS    | 0                 | 9.0              |                                |

|                     | METAL2 WIRE OPENS    | 0                 | 7.6              |                                |

|                     | POLY WIRE OPENS      | 1                 | 13.6             |                                |

| p-PINHOLE CAPACITOR | METAL1-POLY SHORT    | 1                 | 75.2             | _                              |

|                     | GATE OXIDE PINHOLES  | 3                 |                  | 15.6x10 <sup>6</sup> p-MOSFETs |

| n-PINHOLE CAPACITOR | METAL1-POLY SHORT    | Ö                 | 75.2             | _                              |

|                     | GATE OXIDE PINHOLES  | 10                |                  | 15.6x10 <sup>6</sup> n-MOSFETs |

Table 3. CMOS gate-oxide pinhole data base.

Table 4. Matrix test structure results.

| TEST STRUCTURE U                                        | NITS            | MEAN±STDEV                             |                                          | TEST<br>POINTS |

|---------------------------------------------------------|-----------------|----------------------------------------|------------------------------------------|----------------|