https://ntrs.nasa.gov/search.jsp?R=19930022680 2020-03-17T05:19:28+00:00Z

1N-66

174951

NASA Technical Paper

<u>J</u>uly 1993

# Automatic Specification of Reliability Models for Fault-Tolerant Computers

Carlos A. Liceaga and Daniel P. Siewiorek

(NASA-TP-3301) AUTOMATIC SPECIFICATION OF RELIABILITY MODELS FOR FAULT-TOLERANT COMPUTERS (NASA) 70 D N93-31869

**Unclas**

H1/66 0174951

## NASA Technical Paper 3301

1993

# Automatic Specification of Reliability Models for Fault-Tolerant Computers

Carlos A. Liceaga Langley Research Center Hampton, Virginia

Daniel P. Siewiorek Carnegie Mellon University Pittsburgh, Pennsylvania

National Aeronautics and Space Administration

Office of Management

Scientific and Technical Information Program

The use of trademarks or names of manufacturers in this report is for accurate reporting and does not constitute an official endorsement, either expressed or implied, of such products or manufacturers by the National Aeronautics and Space Administration.

### Contents

| Summary                                                      | . 1      |

|--------------------------------------------------------------|----------|

| 1. Introduction                                              | . 1      |

| 1.1. Background                                              | . 2      |

| 1.2. Previous Work                                           | . 7      |

| 1.3. Motivation                                              |          |

| 1.4. Organization                                            |          |

| 2. Graphical User Interface (GUI) Definition                 |          |

|                                                              |          |

| 2.1. Graphs                                                  | 11<br>11 |

| 2.1.1.1 External                                             | 12       |

| 2.1.1.2. Internal                                            | 12       |

| 2.1.2. Hierarchy                                             | 12       |

| 2.1.2.1. Physical                                            | 13       |

| 2.1.2.2. Logical                                             | 14       |

| 2.1.3. System Reconfiguration                                | 14       |

| 2.1.4. Requirement                                           | 15       |

|                                                              |          |

| 2.2. Parameters                                              | 15       |

| 2.2.1. Active Component                                      | 17       |

| 2.2.2. Spare Component                                       | 17       |

| 2.2.3. Component Repair                                      | 19       |

| 2.2.4. Subsystem Recovery                                    | 19       |

| 2.2.5. System Reconfiguration                                | 19       |

| 2.2.6. Model Generation                                      | 22       |

| 2.2.7. Model Evaluation                                      | 22       |

| 2.3. Summary and Recommendations                             | 22       |

| 3. Automated Reliability Modeling (ARM) Implementation       | 23       |

| 3.1. Graphical User Interface                                | 23       |

| 3.1.1. Graphical Editing Windows                             | 23       |

| 3.1.2. Parameter Specification and Action Selection Windows  | 25       |

|                                                              | ٥,       |

| 3.2. Reading and Processing the System Description           | 25       |

| 3.2.1. Detection of Symmetry in the External Structure Graph | 26<br>28 |

| 3.2.2. Determining the Subsystem Hierarchies                 | 28       |

| 3.3. Specifying the System Reliability Model                 | 28       |

| 3.3.1. Constants                                             | 29       |

| 3.3.2. State Space Variables and the Start State             | 29       |

| 3.3.3. Functions and Final State Conditions                  | 30       |

| 3.3.4. Failure Transitions                                   | 31       |

| 3.3.4.1. Logical subsystem component failures                | 31       |

| 3.3.4.2. Spare failures                                      | 32       |

| 3.3.4.3. Dependents in logical subsystems                    | 32       |

| 3.3.5. Potentially General Transitions                       | 32       |

| 3.3.5.1. Spare recoveries                                    | 33       |

| 3.3.5.2. Component repairs                                   | 33       |

| 3.3.5.3. Logical subsystem recoveries                        | 33       |

| 3.3.5.4. Reconfigurations that retire a subsystem            | 34       |

| 3.3.5.5. Reconfigurations that degrade a subsystem           | 34       |

| 3.4. Advanced Features Not Yet Implemented                                                                          |   |   |   |   |   |   |   |   | 35<br>35       |

|---------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|---|---|----------------|

| 3.4.2. Mission Phase Change Reconfigurations                                                                        |   |   |   |   |   |   |   |   | 35             |

| Application Examples and Results                                                                                    | ٠ | ٠ | • | • | • | ٠ | • | • | 35             |

| 4.1. Comparison With Example Multiprocessor Results                                                                 | • | • |   |   |   |   |   |   | 35             |

| 4.2. Application to Systems Described in the Literature 4.2.1. Software Implemented Fault-Tolerance (SIFT) Computer |   |   |   |   |   |   |   |   | 36<br>36       |

| 4.2.2. Comparison With Self-Generated Results                                                                       |   |   |   |   |   |   |   |   | 42             |

| 4.2.2.1. Tandem computer                                                                                            |   |   |   |   |   |   |   |   | 42<br>42       |

| 6. Analysis                                                                                                         |   |   |   |   |   |   |   |   | 50             |

| 5.1. Summary of Assumptions                                                                                         |   |   |   |   |   |   |   |   | 50             |

| 5.2. Utility                                                                                                        |   |   |   |   |   |   |   |   | 51<br>51<br>51 |

| 5.3. Performance                                                                                                    |   |   |   |   |   |   |   |   | 53             |

| 5.4. Validation                                                                                                     |   |   |   |   |   |   |   |   | 53             |

| 5.5. Lessons Learned                                                                                                |   |   |   |   |   |   |   |   | 55             |

| 6. Conclusions                                                                                                      |   |   |   |   |   |   |   |   | 55             |

| 6.1. Summary of Work and Contributions                                                                              |   |   |   |   |   |   |   | ٠ | 55             |

| 6.2. Future Work                                                                                                    |   |   |   |   |   |   |   |   | 55             |

| Appendix—ARM Program Algorithms                                                                                     |   |   |   |   |   |   |   |   | 57             |

| A1. Symmetry Detection                                                                                              |   |   |   |   |   |   |   |   | 57             |

| A2. Determining the Subsystem Hierarchies                                                                           |   |   |   |   |   |   |   |   | 58             |

| A3. Specifying Potentially General Transitions                                                                      |   |   |   |   |   |   |   |   | 59             |

| Poforonaga                                                                                                          |   |   |   |   |   |   |   |   | ഗ              |

### Tables

| Table 1.1. Summary of Previous Work                                                            |

|------------------------------------------------------------------------------------------------|

| Table 2.1. Categories of Subsystems and Components                                             |

| Table 2.2. Sources of Major GUI Input Categories                                               |

| Table 3.1. File Name Suffixes for Each Class of Graph                                          |

| Table 3.2. File Name Suffixes for Each Class of Parameters                                     |

| Table 3.3. State Space Variable Functions                                                      |

| Table 4.1. All Permanent Failure Rates of the Multiprocessor                                   |

| Table 4.2. Some Spare Component Parameters of the Multiprocessor                               |

| Table 4.3. Reliability Model Statistics for the Multiprocessor                                 |

| Table 4.4. Probability of Failure Results for the Multiprocessor                               |

| Table 4.5. Reliability Model Statistics for a SIFT Computer                                    |

| Table 4.6. Probability of Failure Results for a SIFT Computer                                  |

| Table 4.7. Some Active Component Parameters of a Tandem Computer 46                            |

| Table 4.8. Some Component Repair Parameters of a Tandem Computer 46                            |

| Table 4.9. Some System Reconfiguration Parameters of a Tandem Computer 46                      |

| Table 4.10. Reliability Model Statistics for a Tandem Computer                                 |

| Table 4.11. Probability of Failure Results for a Tandem Computer                               |

| Table 4.12. Some Active Component Parameters of a Stratus Computer 49                          |

| Table 4.13. Some Component Repair Parameters of a Stratus Computer                             |

| Table 4.14. Some System Reconfiguration Parameters of a Stratus Computer 49                    |

| Table 4.15. Reliability Model Statistics for a Stratus Computer                                |

| Table 4.16. Probability of Failure Results for a Stratus Computer                              |

| Table 5.1. Effect of Simple Changes in the System Description on a Manual ASSIST File          |

| Table 5.2. Probability of Failure Results for Some Variations of a Stratus  Computer           |

| Table 5.3. Probability of Failure Results for Some Variations of a SIFT  Computer              |

| Table 5.4. ARM Model Specification Performance                                                 |

| Table 5.5. Effect of Coverage on the Probability of Failure of a SIFT Computer 54              |

| Table 5.6. Effect of the Failure Rate on the Probability of Failure of a SIFT  Computer        |

| Table 5.7. Effect of the Reconfiguration Rate on the Probability of Failure of a SIFT Computer |

### Figures

| Figure 1.1. Statically redundant processor triad                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2. Dynamically redundant active processor with $m$ spares $\dots \dots \dots$ |

| Figure 1.3. Hybrid redundant triad of active processors with $m$ spares                                                                                                                |

| Figure 1.4. Adaptive voting with $n$ processors                                                                                                                                        |

| Figure 1.5. Adaptive hybrid $n$ -tuple of active processors with $m$ spares                                                                                                            |

| Figure 1.6. Reliability graph (state transition diagram) of a triad 6                                                                                                                  |

| Figure 1.7. Hierarchy of Markov models                                                                                                                                                 |

| Figure 2.1. System description hierarchy                                                                                                                                               |

| Figure 2.2. Main window                                                                                                                                                                |

| Figure 2.3. Graphs menu                                                                                                                                                                |

| Figure 2.4. Parameters menu                                                                                                                                                            |

| Figure 2.5. Model menu                                                                                                                                                                 |

| Figure 2.6. External structure of a multiprocessor                                                                                                                                     |

| Figure 2.7. Internal structure of each of the six memory components                                                                                                                    |

| Figure 2.8. Physical hierarchy of the multiprocessor                                                                                                                                   |

| Figure 2.9. Physical hierarchy of the printed circuit board subsystem type 13                                                                                                          |

| Figure 2.10. Logical hierarchy of the multiprocessor                                                                                                                                   |

| Figure 2.11. Logical hierarchy of the triad (T) subsystem class                                                                                                                        |

| Figure 2.12. Reinitialization of the multiprocessor                                                                                                                                    |

| Figure 2.13. Degradation of the multiprocessor                                                                                                                                         |

| Figure 2.14. Requirements of the multiprocessor                                                                                                                                        |

| Figure 2.15. Requirement of the printed circuit board subsystem type 16                                                                                                                |

| Figure 2.16. Requirements of the triad subsystem class                                                                                                                                 |

| Figure 2.17. Active component parameters with example values                                                                                                                           |

| Figure 2.18. Spare component parameters with example values                                                                                                                            |

| Figure 2.19. Component repair parameters with example values                                                                                                                           |

| Figure 2.20. Subsystem recovery parameters with example values                                                                                                                         |

| Figure 2.21. Partial Markov model of a processor dual with $m$ cold spares and repair                                                                                                  |

| Figure 2.22. System reconfiguration parameters with example values                                                                                                                     |

| Figure 2.23. Model generation parameters with default values                                                                                                                           |

| Figure 2.24. Model evaluation parameters with default values                                                                                                                           |

| Figure 3.1. Graphical editor window                                                                                                                                                    |

| Figure 3.2. Tools window                                                                                                                                                               |

| Figure 3.3. Drawing tools window                                                                                                                                                       |

| Figure 3.4. External structure with symmetry                                                                                                                                           |

| Figure 3.5. Equivalence class graph                                                |   | 28 |

|------------------------------------------------------------------------------------|---|----|

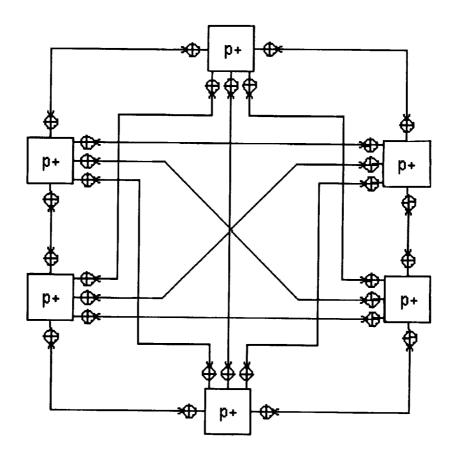

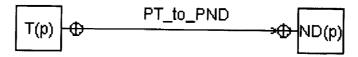

| Figure 4.1. External structure of a SIFT computer                                  |   | 37 |

| Figure 4.2. Logical hierarchy of a SIFT computer                                   |   | 37 |

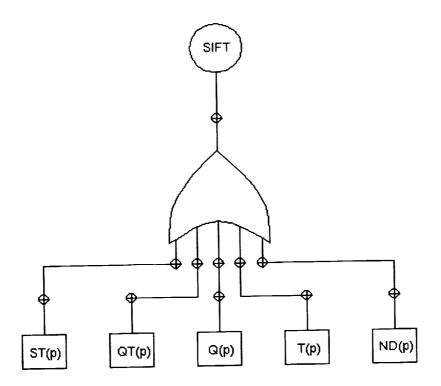

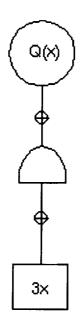

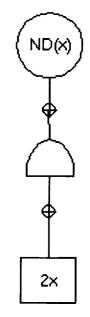

| Figure 4.3. Logical hierarchy of the sextuple subsystem class                      |   | 37 |

| Figure 4.4. Logical hierarchy of the quintuple (QT) subsystem class                |   | 38 |

| Figure 4.5. Logical hierarchy of the quad (Q) subsystem class                      |   | 38 |

| Figure 4.6. Logical hierarchy of the nonreconfigurable dual (ND) subsystem class . |   | 38 |

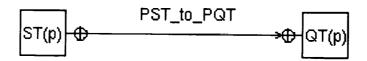

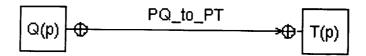

| Figure 4.7. Degradation from a processor sextuple (PST) to a quintuple (PQT)       |   | 39 |

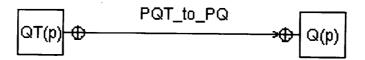

| Figure 4.8. Degradation from a processor quintuple to a quad (PQ)                  |   | 39 |

| Figure 4.9. Degradation from a processor quad to a triad (PT)                      |   | 39 |

| Figure 4.10. Degradation from a processor triad to a nonreconfigurable dual (PND)  |   | 39 |

| Figure 4.11. Requirements of a SIFT computer                                       |   | 40 |

| Figure 4.12. Requirements of the sextuple subsystem class                          |   | 40 |

| Figure 4.13. Requirements of the quintuple subsystem class                         |   | 40 |

| Figure 4.14. Requirements of the quad subsystem class                              |   | 41 |

| Figure 4.15. Requirements of the nonreconfigurable dual subsystem class            |   | 41 |

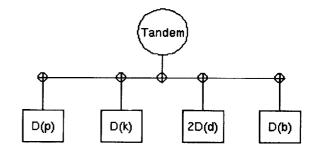

| Figure 4.16. External structure of a Tandem computer                               |   | 41 |

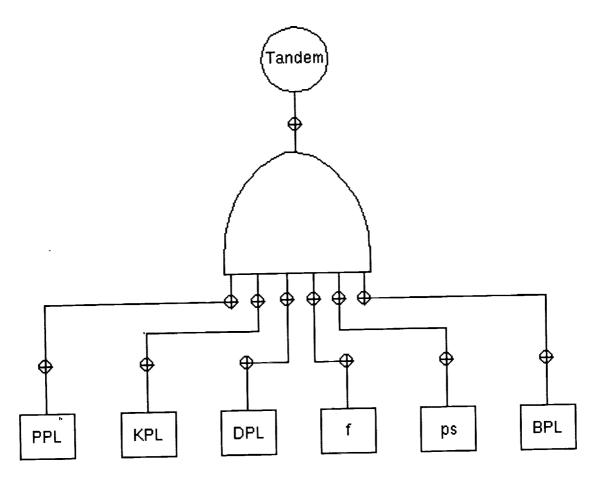

| Figure 4.17. Logical hierarchy of a Tandem computer                                |   | 41 |

| Figure 4.18. Logical hierarchy of the dual subsystem class                         |   | 43 |

| Figure 4.19. Logical hierarchy of the simplex subsystem class                      |   | 43 |

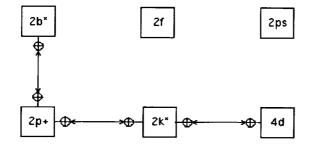

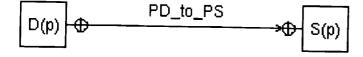

| Figure 4.20. Degradation from a processor dual (PD) to a simplex (PS)              |   | 43 |

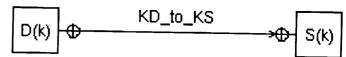

| Figure 4.21. Degradation from a disk controller dual (KD) to a simplex (KS)        |   | 43 |

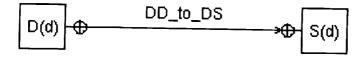

| Figure 4.22. Degradation from a disk drive dual (DD) to a simplex (DS)             |   | 43 |

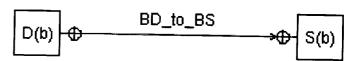

| Figure 4.23. Degradation from a bus dual (BD) to a simplex (BS)                    |   | 43 |

| Figure 4.24. Requirements of a Tandem computer                                     |   | 44 |

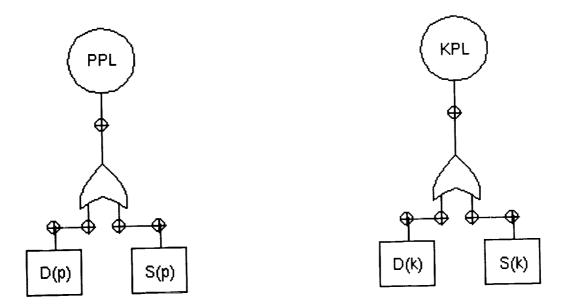

| Figure 4.25. Requirements of the PPL performance level                             |   | 44 |

| Figure 4.26. Requirements of the KPL performance level                             | , | 44 |

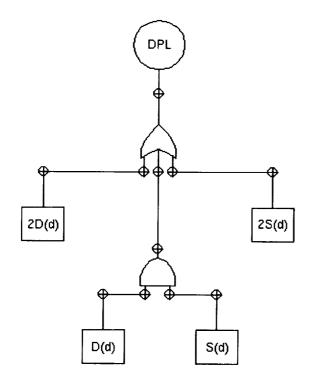

| Figure 4.27. Requirements of the DPL performance level                             |   | 45 |

| Figure 4.28. Requirements of the BPL performance level                             |   | 45 |

| Figure 4.29. Requirements of the dual subsystem class                              |   | 45 |

| Figure 4.30. Requirements of the simplex subsystem class                           |   | 45 |

| Figure 4.31. External structure of a Stratus computer                              |   | 47 |

| Figure 4.32. Physical hierarchy of a Stratus computer                              |   | 47 |

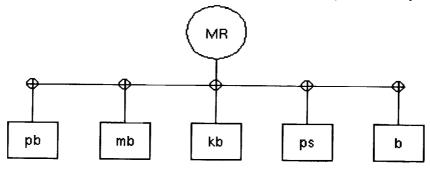

| Figure 4.33. Physical hierarchy of the MR subsystem type                           |   | 47 |

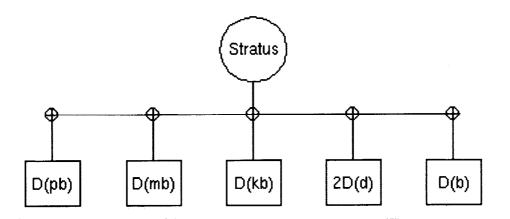

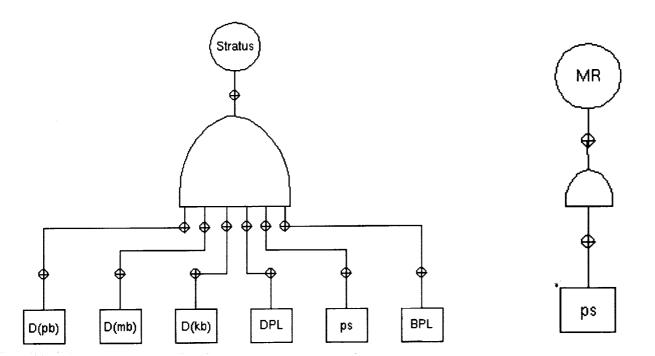

| Figure 4.34. Logical hierarchy of a Stratus computer                               |   | 48 |

| Figure 4.35. Requirements of a Stratus computer                                    |   | 48 |

| Figure 4.36. Requirements of the MR subsystem type                                 |   | 48 |

#### Summary

The calculation of reliability measures using Markov models is required for life-critical processor-memory-switch (PMS) structures that have standby redundancy or that are subject to transient or intermittent faults or repair. The task of specifying these models is tedious and prone to human error because of the large number of states and transitions required in any reasonable system. Therefore, model specification is a major analysis bottleneck, and model verification is a major validation problem. The general unfamiliarity of computer architects with Markov modeling techniques further increases the necessity of automating the model specification.

Automation requires a general system description language (SDL) that can accommodate new fault-tolerant techniques and system designs. For practicality, this SDL should also provide a high level of abstraction and be easy to learn and use.

This paper presents the first attempt to define and implement an SDL with those characteristics. The problems involved in the automatic specification of Markov reliability models for arbitrary interconnection structures at the PMS level are identified and analyzed. Solutions to these problems are generated and implemented.

A program named ARM (Automated Reliability Modeling) has been constructed as a research vehicle. The ARM program uses a graphical user interface (GUI) as its SDL. This GUI is based on a hierarchy of windows. Some windows have graphical editing capabilities for specifying the system's communication structure, hierarchy, reconfiguration capabilities, and requirements. Other windows have text fields, pulldown menus, and buttons for specifying parameters and selecting actions.

The ARM program outputs a Markov reliability model specification formulated for direct use by programs that generate and evaluate the model. The advantages of such an approach include utility to a larger class of users, who are not necessarily expert in reliability analysis, and lower probability of human error in the calculation.

#### 1. Introduction

Computer systems are growing in complexity and sophistication as multiprocessors and distributed computers are coming into widespread use to achieve higher performance and reliability. This growth, which is being assisted by the availability of successively more complex building blocks, has increased the importance of fault tolerance and system reliability as design parameters. Thus, the calculation of system reliability measures has become one of the system design tasks. Several efforts have been reported in the literature and are in progress to make computing system reliability measures easier and more efficient by providing designers with reliability evaluation tools.

The analysis and evaluation of system reliability for complex computer systems is very tedious and prone to error even for experienced reliability analysts. The model of a system with n components can have up to  $2^n$  states if it only has permanent faults and they are not removed. Therefore, the model of a system with just 10 components can have more than 1000 states.

With the exception of the ADVISER (Advanced Interactive Symbolic Evaluator of Reliability) and the RMG (Reliability Model Generator) programs, discussed in subsection 1.2, existing software tools usually assume an understanding of the failure modes and therefore are more in the nature of computational aids once the preliminary system decomposition and analysis have been manually achieved. Although ADVISER does not make this assumption, it uses combinatorial techniques, and it is therefore limited in the complexity of systems and fault types which it can analyze. The RMG program lacks a high-level system description language (SDL) that is easy to learn and use.

More advanced techniques are required to analyze computer architectures that use standby redundancy, can be repaired, or are susceptible to transient or intermittent faults. One possibility is the Markov model, which is discussed in subsection 1.1. The advantages offered by Markov models are that they are widely used among reliability analysts and that several programs, which are discussed in subsection 1.2, have been developed to solve them. However, Markov models cannot be used to analyze nonexponentially distributed concurrent events. For example, a fault that arrives while the system is reconfiguring itself around a previous fault would be represented by a transition to a state in which two faults are present. This new state would not take into account the time that the system has already spent reconfiguring from the first fault.

Another analysis possibility is the extended stochastic Petri net (ESPN) described in Dugan et al. (1984). The advantages offered by the ESPN are that it can analyze concurrent events and can model systems at a lower level of detail than Markov models. The ESPN "tokens" can be simultaneously enabled to move concurrently at independent transition times. The low-level modeling capability is due to mechanisms, such as queues and counters, which can simulate the algorithm of the process being modeled. To analytically or numerically solve an ESPN, it must be converted to a Markov model. However, if tokens are moving concurrently at independent transition times that are not exponentially distributed, the process becomes non-Markovian (i.e., the transition probabilities depend on past states). This situation makes the conversion impossible. In general, an ESPN must be solved by simulation.

Simulations can include any level of detail, and they are thus flexible; however, for straightforward Monte Carlo simulations, many repetitions are needed to ensure accuracy. For example, in lifecritical applications that require a probability of failure of  $10^{-9}$  with a relative error of no more than 10 percent within a confidence interval of 95 percent, approximately  $3.8 \times 10^{11}$  simulation repetitions are necessary (Liceaga 1992). In general, these applications require a Markov model because it can be solved analytically or numerically.

This paper defines a general, high-level SDL that is easy to learn and use, identifies and analyzes the problems involved in the automatic specification of Markov reliability models for arbitrary interconnection structures at the processor-memory-switch (PMS) level, and generates and implements solutions to these problems. The results of this research have been implemented and experimentally validated in the ARM (Automated Reliability Modeling) program.

The ARM program uses a graphical user interface (GUI) as its SDL. This GUI is based on a hierarchy of windows implemented in the C programming language using the Transportable Application Environment Plus (TAE Plus) user interface development tool for building X window-based applications (Szczur 1990). Some windows have graphical editing capabilities for specifying the system's communication structure, hierarchy, reconfiguration capabilities, and requirements. These windows have been implemented using the schematic drawing editor Schem (Vlissides 1990). Other windows have text fields, pull-down menus, and buttons for specifying parameters and selecting actions.

The ARM software outputs a Markov reliability model specification formulated for direct use by programs that generate the model. The advantages

<sup>1</sup> Components are not limited to being a processor, memory, or switch.

of such an approach are utility to a larger class of users, who are not necessarily expert in reliability analysis, and lower probability of human error in the calculation.

A brief background on reliability calculation at the PMS level using Markov models is presented in subsection 1.1. Previous work in the specification, generation, and evaluation of reliability models is surveyed in subsection 1.2. The goals for ARM are stated and compared with those of previous efforts in subsection 1.3. The organization of this paper is presented in subsection 1.4.

#### 1.1. Background

Present-day computer systems and the process of designing and analyzing them can be viewed at various levels of detail. Four levels, which are defined in work by Siewiorek et al. (1982), range from the circuit level, through the logic and programming levels, to the PMS level. The PMS-level view of digital systems is one in which the primitives include processors, memories, switches, and transducers, as opposed to the logic level in which the primitives include gates, registers, and multiplexers.

Hardware components are susceptible to hard and soft faults as discussed by Siewiorek and Swarz (1992). A fault is an incorrect state of hardware or software resulting from a physical change in the hardware, interference from the environment, or design mistakes (Laprie 1985). Hard or permanent faults are continuous and stable, and they result from an irreversible physical change. Soft faults can be transient or intermittent. Transient faults result from temporary environmental conditions. Intermittent faults are occasionally active because of unstable hardware or varying hardware or software states (e.g., as a function of load or activity). Depending on whether the intermittent fault is benign or active, the output of the component will be correct or not, respectively.

Fault-tolerant computer systems can be affected by a limited set of faults without interruptions in their operation. Some computer systems achieve fault tolerance by using redundant groups of components to perform the same operations. The system must determine which is the correct output using diagnostics or majority voting. The various redundancy techniques are discussed in Siewiorek and Swarz (1992), and the more relevant ones are defined below:

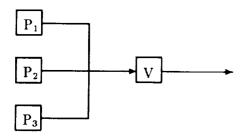

Static redundancy: Faults are masked through a majority vote involving a fixed group of redundant components. Thus, when the number of faulty components reaches the maximum that can be tolerated, any further faults will cause errors at the output. Figure 1.1 illustrates a statically redundant processor (P) triad (a group of three components) and its voter (V).

Figure 1.1. Statically redundant processor triad.

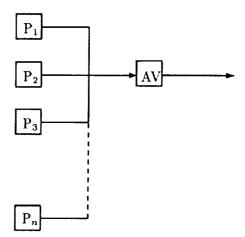

Dynamic redundancy: Faults are not masked from causing errors at the output, but the faulty components are detected, isolated, and reconfigured out of the system. The faulty components are replaced when spares are available. Figure 1.2 illustrates a dynamically redundant active processor (AP) with m spares (SP).

Figure 1.2. Dynamically redundant active processor with m spares.

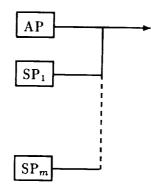

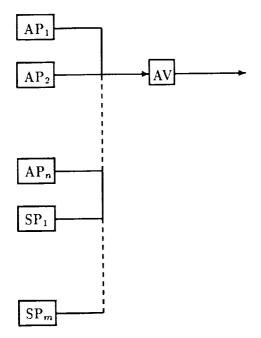

Hybrid redundancy: Faults are masked through a majority vote involving a group of redundant components which are reconfigured when spares are available. Thus, when the number of faulty components reaches the maximum that can be tolerated, any further faults that occur before a faulty component is replaced by a spare will cause errors at the output. Figure 1.3 illustrates a hybrid-redundant triad of active processors with m spares.

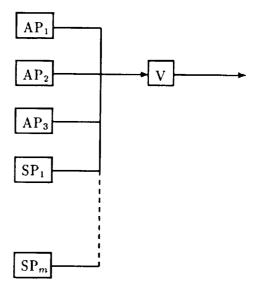

Adaptive voting: Faults are masked through a majority vote involving a variable group of redundant components without spares. Faulty

components are reconfigured out of the system by excluding them from the voting process. Thus, when the number of faulty components reaches the maximum that can be tolerated, any further faults that occur before a faulty component is reconfigured out of the voting process will cause errors at the output. Figure 1.4 illustrates adaptive voting with n processors and their voter (AV).

Figure 1.3. Hybrid-redundant triad of active processors with m spares.

Figure 1.4. Adaptive voting with n processors.

Adaptive hybrid: Faults are masked through a majority vote involving a variable group of redundant components which are replaced when spares are available. If spares are not available, faulty components are reconfigured out of the system by excluding them from the voting process. Thus, when the number of faulty components reaches the maximum that

can be tolerated, any further faults that occur before a faulty component is replaced by a spare or reconfigured out of the voting process will cause errors at the output. Figure 1.5 illustrates an adaptive hybrid n-tuple of active processors with m spares.

Figure 1.5. Adaptive hybrid *n*-tuple of active processors with *m* spares.

For example, if a triad that uses hybrid redundancy "recovers" from a fault by replacing the faulty component with a spare, it can then tolerate a second fault. The following two definitions are those that will be used in this paper, but neither term has a universally accepted definition:

Recovery: The process of detecting, isolating, and reconfiguring a faulty component out of the system.

Coverage: The probability that the system can survive a fault in a component and successfully recover. (If the system can always recover, it has a "perfect" coverage of 1.)

Spares are sometimes left unpowered until they become part of the active configuration to reduce their failure rates (Avižienis et al. 1971). They are sometimes said to be cold if their failure rates are assumed to be 0, warm if their failure rates are reduced but not 0, or hot if their failure rates are not reduced (Butler and Johnson 1990).

Reliability measures are defined in terms of probabilities because the failure processes in hardware

components are nondeterministic. These various measures are discussed in Siewiorek and Swarz (1992). The more relevant ones are defined below:

Reliability: The conditional probability R(t) that the system is operational throughout the interval [0,t] given that it was operational at time 0. (This measure is a nonincreasing function whose initial value is 1.)

Availability: The probability A(t) that the system is operational at time t.

Mean time to failure (MTTF): The expected time of the first system failure assuming a new (perfect) system at time 0.

Mean time to repair (MTTR): The expected time for repair of a failed system.

Mean time between failures (MTBF): The expected time between failures in systems with repair.

Availability is typically used as a figure of merit in systems in which service can be delayed or denied for short periods to perform preventive maintenance or repair without serious consequences. The availability is important in the calculation of system life-cycle costs. If the limit of A(t) exists as t goes to infinity, it expresses the expected fraction of time that the system is available to perform useful computations and has the following form:

$$\lim_{t \to \infty} A(t) = \frac{\text{MTTF}}{\text{MTBF}}$$

The MTBF is given by:

$$MTBF = MTTF + MTTR$$

Reliability is used to describe systems in which repair is typically infeasible, such as space applications. The MTTF can be derived from R(t) as follows:

$$MTTF = \int_0^\infty R(t) \ dt$$

The most commonly used reliability function for a single component, which is based on a Poisson process with an exponential distribution, is called the exponential reliability function, and it has the form

$$R\left(t\right) = e^{-\lambda t}$$

where  $\lambda$  is the hazard or failure rate. The failure rate is a constant that reflects the quality of the component and is usually expressed in failures per million

hours for high-quality components. The exponential reliability function is used when the failure rate is time independent, such as when components do not age. After a burn-in period, permanent faults in electronic components often follow a relatively constant failure rate. The MTTF for the exponential reliability function has the following form:

$$MTTF = \frac{1}{\lambda}$$

Many other reliability functions have been formulated. The second most common reliability function, which is based on the Weibull distribution, is called the Weibull reliability function, and it has the form

$$R\left(t\right) = e^{-\left(\lambda t\right)^{\alpha}}$$

where  $\lambda$  in this case is the scale parameter and  $\alpha$  is the shape parameter. (Other reparameterized forms are also common.) It is equivalent to the exponential function when  $\alpha$  is 1. The Weibull reliability function is used when the failure rate is time dependent. Permanent faults for components that age can be described using an increasing failure rate ( $\alpha > 1$ ). In that case, the system is not as good as new when repair takes place. Data presented in McConnel (1981) and Castillo, McConnel, and Siewiorek (1982) indicate that transient faults follow a decreasing failure rate ( $\alpha < 1$ ).

The failure processes of different components are assumed to be independent of one another. This assumption is not strictly true, such as when electrical, mechanical, or thermal conditions in one component affect other components in its proximity. However, the assumption is close enough in practice to be used to simplify the analysis.

The state of a system represents all that must be known to describe the system at any instant. As the system changes, such as when components fail or are repaired, so does its state. These changes of state are called state transitions. If all possible states are assumed to be known, a discrete-state system model is used; if this assumption is not made, a continuous-state system model is used. If the state transition times are assumed to be restricted to some multiple of a given time interval, a discrete-time system model is used. If it is assumed that state transitions can occur at any time, a continuous-time system model is used. Systems can be classified according to their state space and time parameter as the following:

discrete state and discrete time discrete state and continuous time continuous state and discrete time

continuous state and continuous time

For a discrete-state system, a state transition diagram (STD) may be drawn. This transition diagram is a directed graph. The nodes correspond to system states, and the directed arcs indicate allowable state transitions. Each arc has a label that identifies the distribution of the conditional probability that the system will go from the originating node to the destination node of that directed arc given the previous history of the system and that the system was initially at the originating node. The label used depends on the distribution. For example, the label could be the hazard rate for the exponential distribution, the scale and shape parameters for the Weibull distribution, or the mean and standard deviation for a general distribution.

If transitions are allowed from failed states to operational states, then the STD is an availability graph and A(t) may be obtained from it. The term R(t) may be obtained by specifically disallowing failed to working state transitions from the STD, thus making it a reliability graph.

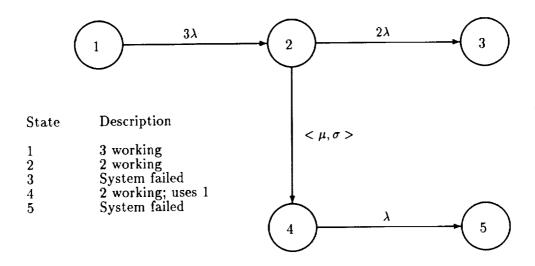

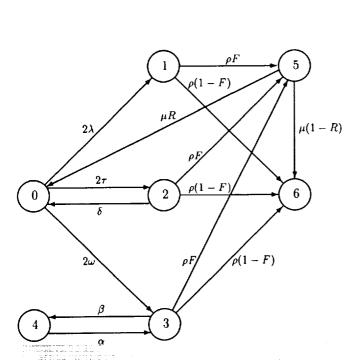

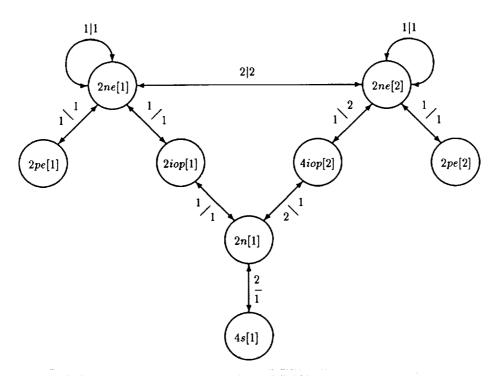

A reliability graph of a triad is given in figure 1.6. In this model, it is assumed that the components have a perfect coverage of 1. The horizontal transitions represent fault arrivals. These transitions follow an exponential distribution. Consequently,  $\lambda$  represents the constant hazard rate. The coefficients of  $\lambda$  represent the number of working processors being actively used in the configuration. The vertical transition represents recovery from a fault. This recovery follows a general distribution. Consequently,  $\mu$  and  $\sigma$  represent its mean and standard deviation. A competition exists between the two transitions that are leaving state 2. If the second fault wins the competition, then system failure occurs; however, if the removal of the first fault wins the competition, then the system reconfigures into a simplex (i.e., it only uses one of the two working components). Unless otherwise noted in the state descriptions, all working processors are being actively used in the configuration.

The information conveyed by the STD is often summarized in a square matrix called the state transition matrix (STM). The STM element in row i and column j is the label on the arc from state i to state j.

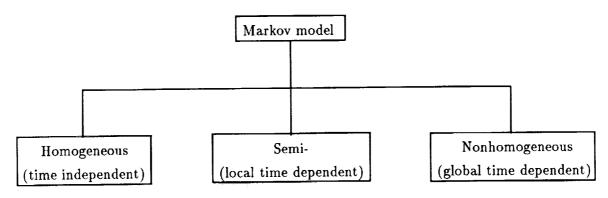

The terminology used in this paper to denote the various types of Markov models and the assumptions they are based on are defined below. The hierarchy of Markov models is illustrated in figure 1.7.

Figure 1.6. Reliability graph (state transition diagram) of a triad.

Figure 1.7. Hierarchy of Markov models.

Markov model: A stochastic process model whose future state depends only upon the present state and not upon the state history that led to its present state.

Homogeneous Markov model: A Markov model whose state transition probabilities are time independent. For the continuous-time homogeneous Markov model, this implies that the state transition times follow an exponential distribution. This type of model is discussed in Chung (1967) and Romanovsky (1970) and applied to computer systems in Makam and Avižienis (1982).

Semi-Markov model: A Markov model whose state transition probabilities depend upon the time spent in the present state, which is called the local time. For the continuous-time semi-Markov model, this implies that the state transition times do not follow an exponential distribution; they might follow a Weibull distribution or any other distribution. This

type of model is discussed and applied to computer systems in White (1986).

Nonhomogeneous Markov model: A Markov model whose state transition probabilities depend upon the time since the system was first put into operation, which is called the global time. For the continuous-time non-homogeneous Markov model, this implies that the state transition times do not follow an exponential distribution. Often these times are assumed to follow a Weibull distribution, but they can follow any other distribution. This type of model is discussed and applied to computer systems in Trivedi and Geist (1981).

The probability of being in a particular state for a discrete-state, continuous-time Markov model can be expressed with a differential equation. The set of simultaneous differential equations which describe these models are called the continuous-time Chapman-Kolmogorov equations. For homogeneous

Markov models, these equations can be solved using matrix or Laplace transformations.

If the state transition probabilities are time dependent, it may be quite difficult to obtain explicit solutions to the continuous-time Chapman-Kolmogorov equations. Obtaining the exact probability of reaching a state through a particular path of transitions requires the solution of a multiple integral, in which each integral represents the probability of making one of the transitions in the path. Often the integrals are approximated using numerical integration techniques (Stiffler, Bryant, and Guccione 1979). An alternative method is to approximate the continuous-time model with discrete-time equivalents (Siewiorek and Swarz 1992). The major difficulty with the second method is that many transition rates that are effectively zero in the continuoustime model assume small, but nonzero, probabilities in a discrete-time model.

#### 1.2. Previous Work

Several programs exist, such as ARIES, SURF, CARE III, HARP, SURE, PAWS, STEM, and ASSURE, which use Markov models to evaluate the reliability and/or availability of systems that use standby redundancy or can be repaired and that are susceptible to hard, transient, or intermittent faults. All these programs can evaluate reliability. The ARIES, SURF, and HARP programs can also evaluate availability. Except for CARE III and ASSURE, they all have the state transition matrix as one of the system specification methods.

The ADVISER (Advanced Interactive Symbolic Evaluator of Reliability) program, described in Kini and Siewiorek (1982), automatically generates symbolic reliability functions for PMS structures. The program assumptions are that all the faults are permanent and stochastically independent, the PMS system has a perfect coverage, and the failed components are not repaired and returned to a nonfaulty state. The program's primary input is the interconnection graph of the PMS structure. Other program inputs describe the components of the PMS structure by their types, reliability functions, internal port connections, and ability to communicate with components of the same type. The program also takes as input the requirements for the system and its subsystems or clusters in the form of modified Boolean expressions.

The ARIES (Automated Reliability Interactive Estimation System) program, described in Makam, Avižienis, and Grusas (1982), is restricted to homogeneous Markov models. The system can be specified using a state transition matrix or as a series of independent subsystems each containing identical modules that either are active or serve as spares. The program uses a matrix transformation solution technique that assumes distinct eigenvalues for the state transition matrix.

Described in Landrault and Laprie (1978), the SURF program can solve semi-Markov models that use exponential distributions or nonexponential distributions that are related to the exponential (e.g., Gamma, Erlang, and others). The method of stages (Cox and Miller 1965) is used to produce a homogeneous Markov model. Matrix transformations are used to obtain time-independent values, such as MTTF and the limiting availability. The Laplace transform is used to obtain time-dependent values, such as availability and reliability.

The CARE III (Computer-Aided Reliability Estimation) program, described in Bavuso, Petersen, and Rose (1984), can evaluate the reliability of systems that use reconfiguration to tolerate component faults but that do not repair the faulty compo-The program uses a behavioral decomposition/aggregation solution technique described in Trivedi and Geist (1981). This technique assumes the fault-occurrence behavior is composed of relatively infrequent (slow) events, and the fault-handling behavior is composed of relatively frequent (fast) events. The fault-handling behavior is separately analyzed using a fixed semi-Markov model that can use exponential and uniform distributions. fault-occurrence behavior is analyzed using an aggregate nonhomogeneous Markov model that can use exponential and Weibull distributions. The faulthandling behavior is reflected by parameters in the aggregate nonhomogeneous Markov model. Numerical integration techniques are used to solve these Markov models. The fault-occurrence behavior is specified using extended fault trees, which are automatically converted to the nonhomogeneous Markov The fault-handling behavior is specified by providing the transition parameters of the fixed semi-Markov model.

For HARP (Hybrid Automated Reliability Predictor), described in Dugan et al. (1986) and Howell et al. (1990), the state transition probabilities can have exponential, uniform, Weibull, or general distributions. (A histogram must be provided for general distributions.) If the state transition matrix is given by the user, HARP can only evaluate the availability of systems with constant repair rates. The HARP program has several additional methods of specifying the fault-occurrence behavior (e.g., fault trees), all of which are automatically converted to a

nonhomogeneous Markov model. The fault-handling behavior can also be specified by providing the transition parameters of one of several models. The program uses the same behavioral decomposition/aggregation solution technique as CARE III, but the various models are solved in a hybrid fashion. Markov models are solved using numerical integration techniques, and extended stochastic Petri nets are solved by simulation.

The SURE (Semi-Markov Unreliability Range Evaluator) program, described in Butler (1992), evaluates the unreliability upper and lower bounds of semi-Markov models. It uses new mathematical theorems proved in White (1986) and Lee (1985). These theorems provide a technique for bounding the probability of traversing a specific path in the model within a specified time. By applying the theorems to every path of the model, the probability that the system reaches any death state can be determined within usually very close bounds. These theorems assume that slow (with respect to the mission time) exponential transitions describe the occurrence of faults, and fast transitions that follow a general distribution specified by its mean and standard deviation describe the recovery process. The program provides the option of pruning the model during its evaluation by conservatively assuming system failure once the probability of reaching a state falls below a specified or automatically selected prune level. Faults can be modeled as permanent, transient, or intermittent as long as there are no loops in the model which only have fast transitions. The only input method of the program is the state transition matrix.

Described in Butler and Stevenson (1988), the PAWS (Padé Approximation With Scaling) and STEM (Scaled Taylor Exponential Matrix) programs evaluate the unreliability of homogeneous Markov models. The input language for these two programs is essentially the same as for the SURE program. Although the numerical techniques used in these programs are not as fast as the SURE technique, they are suitable for loops with only fast transitions.

The ASSIST (Abstract Semi-Markov Specification Interface to the SURE Tool) program, which uses an abstract language for specifying Markov reliability models, is described in Butler (1986). The language has statements to specify the state space, by defining the state variables and their range; the start state, by the initial values of the state variables; the death states, by a Boolean expression of the state variables; and the state transitions, by a set of if-then rules that define, in terms of the state variables, the possible transitions, their rates, and their destina-

tion states. This language has been implemented in the ASSIST program to generate Markov reliability models in the SURE input language (Johnson 1986). The implementation provides three optional state space reduction techniques. The first technique is pruning the model during its generation by conservatively assuming system failure once a state satisfies a prune condition specified as a Boolean expression of the state variables (Johnson 1988). The second technique is trimming the model by conservatively altering states with outgoing recovery transitions (White and Palumbo 1990). The outgoing failure transitions of the altered states that do not go to death states are changed to go to a single trim state. The third technique combines pruning and trimming by changing all states that meet a prune condition to trim states. Each trim state has a single transition to a death state at some trim rate. The trim rate must be the sum of the failure rates of all remaining components.

The ASSURE program, described in Palumbo and Nicol (1990), translates an extension of the ASSIST language into C code, which is linked with SURE solution procedures and executed to generate and solve the model. This reduces the storage required because completely expanded states are discarded since the only state of consequence at any time is the state being expanded. The extended ASSIST language allows the use of user-defined C functions to specify the death states and the state transitions. This specification increases the size and complexity of the systems that can be practically modeled because it makes the model specification more compact.

The RMG (Reliability Model Generator) program is specified in Cohen and McCann (1990). As it is now implemented, LISP expressions are required to specify the system failure conditions whose probabilities are to be evaluated and each component's local reliability model (LRM) and function. An LRM is specified in terms of the component modes, the transitions between modes, and the characteristic (good, bad, or none) of the outputs in terms of the modes and the value or characteristic of the inputs. A graphical input is used to specify the interconnection graph of the PMS structure. It aggregates the LRM's to specify a Markov reliability model in the ASSIST language for the system failure conditions given.

Table 1.1 gives the primary inputs and outputs of the programs described in this subsection. None of these programs is able to generate a Markov model or its specification using a high-level SDL that is easy to learn and use.

Table 1.1. Summary of Previous Work

| Program name | Primary inputs                                      | Primary outputs                      |

|--------------|-----------------------------------------------------|--------------------------------------|

| ADVISER      | PMS structure                                       | Symbolic reliability function        |

| ARIES        | Homogeneous Markov model                            | Reliability or availability estimate |

| SURF         | Semi-Markov model                                   | Reliability or availability estimate |

| CARE III     | Fault tree and semi-Markov model parameters         | Reliability estimate                 |

| HARP         | Fault tree or nonhomogeneous Markov model           | Reliability or availability estimate |

| SURE         | Semi-Markov model                                   | Reliability bounds                   |

| PAWS/STEM    | Homogeneous Markov model                            | Reliability estimate                 |

| ASSIST       | Semi-Markov model specification                     | Semi-Markov model                    |

| ASSURE       | Semi-Markov model specification                     | Reliability bounds                   |

| RMG          | LRM's, PMS structure, and system failure conditions | Semi-Markov model specification      |

#### 1.3. Motivation

The goal of this research and development effort is to provide the computer architect a powerful and easy-to-use software tool that will assume the burden of an advanced reliability analysis that considers intermittent, transient, and permanent faults for computer systems of high complexity and sophistication. The PMS level of computer system description was selected because it is the highest level view of digital systems and therefore the easiest to specify and it is well known to computer architects. The Markov model technique was selected because it is powerful enough to accurately model most situations, it is widely used among reliability analysts, and these models can be evaluated by several programs that have been developed.

Previous efforts have been limited in one of three ways. Most efforts provided a computational aid once the preliminary system decomposition and reliability analysis had been manually achieved. Alternatively, computer systems of less complexity and sophistication were considered without transient and intermittent faults, or they did not provide a high-level SDL that is easy to learn and use.

#### 1.4. Organization

The GUI is defined and illustrated in section 2. The problems involved in the automatic specification of Markov reliability models are identified and analyzed in section 3. Examples of GUI applications and their results are given in section 4. An analysis of this approach is presented in section 5. Conclusions are

drawn in section 6. The algorithms used by the ARM program are shown in the appendix.

#### 2. Graphical User Interface (GUI) Definition

The GUI is the first of four steps in the automated reliability modeling process proposed in this paper. The second step is the automated specification of the model in the ASSIST language. This step was implemented in the ARM program. The last two steps, the automated generation and evaluation of the model, have already been implemented. The third step has been implemented in the ASSIST program, and the fourth step has been implemented in the SURE, PAWS, and STEM programs.

In order of importance, the major goals of the GUI are defined below:

General: To allow current and future faulttolerant techniques and system designs to be accommodated

*Hierarchical:* To allow systems and subsystems to be defined in terms of their subsystems and components, respectively

Compact: To allow subsystem classes to only be defined once with their component types as formal parameters

Subsystems are in the same class if they have the same hierarchy and requirements (e.g., triads that require two of their three components). Subsystems are of the same type if they are in the same class, are

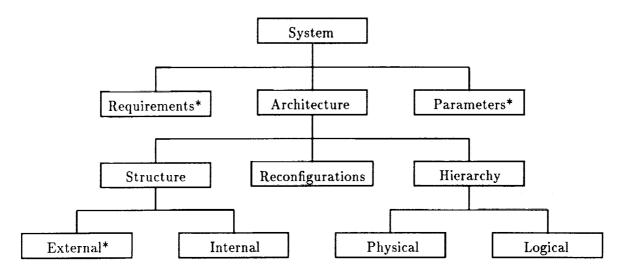

Figure 2.1. System description hierarchy. (The asterisk (\*) denotes parts that are always required.)

composed of the same component types, and have the same recovery parameters, if any (e.g., processor triads). Components are of the same type if they have the same function and parameters (e.g., processors). These categories of subsystems and components are summarized in table 2.1. For the sake of generality, the GUI does not predefine any category.

Table 2.1. Categories of Subsystems and Components

| Category        | Common attributes                                         |

|-----------------|-----------------------------------------------------------|

| Subsystem class | Hierarchy<br>Requirements                                 |

| Subsystem type  | Subsystem class<br>Component types<br>Recovery parameters |

| Component type  | Function<br>Parameters                                    |

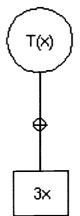

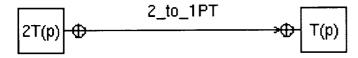

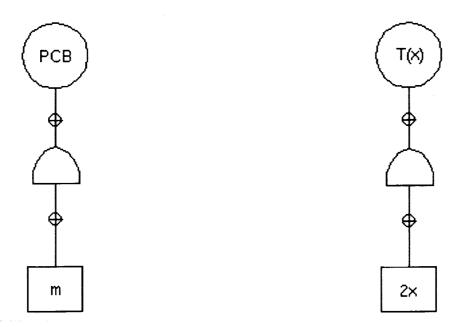

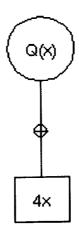

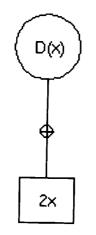

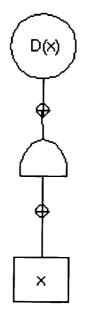

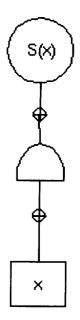

Each category is represented by an identifier that starts with a letter and can contain letters, underscores (\_), and digits (e.g., a component type could be represented by p). A subsystem identifier can also end with a set of parentheses that enclose a list of parameters separated by commas. Formal parameters, which are identifiers that are not used to represent a category or anything else, are used in the identifier of a subsystem class (e.g., T(x)). Component types are used instead of the formal parameters in the identifier of a subsystem type (e.g., T(p)).

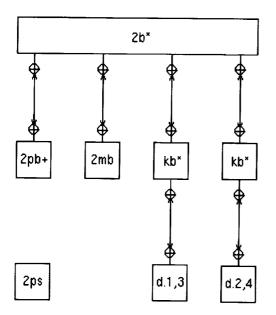

Type identifiers can be either (a) preceded by an integer greater than 1 to represent multiple elements of the same type (e.g., 2T(p)) or (b) followed by a period and a list of subranges and/or integer numbers

in the range from 1 to the number of elements of that type, which are separated by commas to represent specific elements of the same type (e.g., T(p).1,2), but not both (a) and (b). A subrange would be specified by two positive integer numbers separated by a dash, with the larger one on the right (e.g., p.1-3). Unless elements are assigned specific numbers, they are given the lowest positive numbers available (e.g., the components represented by 2p could be assigned the numbers 1 and 2).

The system's description is divided into requirements, architecture, and parameters. The requirements depend on the application of the system. How the system was designed determines the architecture. The technology used to implement the system components determines the parameter values (e.g., failure rates). The sources of the major GUI input categories are summarized in table 2.2. Figure 2.1 shows the hierarchy of the system description. The actual GUI inputs are the leaves of the tree shown in figure 2.1.

Table 2.2. Sources of Major GUI Input Categories

| Major GUI input category | Source                    |

|--------------------------|---------------------------|

| Requirements             | Application               |

| Architecture             | Design                    |

| Parameters               | Implementation technology |

The GUI starts by displaying the main window shown in figure 2.2. It contains text fields for entering the system name and the name of the current selection; the graphs, parameters, and model pull-down

| <b>■</b> AR | LM                             |  |

|-------------|--------------------------------|--|

|             | Automated Reliability Modeling |  |

| _           | m Name:                        |  |

| Graphs      | s Parameters Model QUI         |  |

Figure 2.2. Main window.

menus; and a button to quit the GUI. The current selection, which is the initial name used by windows that describe a component type, subsystem type, or reconfiguration, changes automatically to the last name entered in the first text field of any such window, but it can also be changed manually.

The graphs menu, shown in figure 2.3, displays a window for editing the graphs described in subsection 2.1. The parameters menu, shown in figure 2.4, displays windows, with text fields and buttons for parameter specification, which are described in subsection 2.2. The model menu, shown in figure 2.5, executes the programs that specify, generate, and evaluate the Markov model, based on the system description given through the GUI. The ARM program will notify the user if the system description is incomplete (e.g., if the external structure has not been given) and not specify the model. Subsection 2.3 presents a summary of the GUI and recommendations on how to reduce the number of errors in the system description.

#### 2.1. Graphs

The following subsections describe the graphs used for specifying the system's communication structure, hierarchy, reconfiguration capabilities, and requirements.

#### 2.1.1. Structure

Graphs with unidirectional and bidirectional edges describe the system's external and internal communication structures. It is assumed that components which communicate and are critical (i.e., required for the system to be operational) must be

External Structure

Internal Structure

Physical Hierarchy

Logical Hierarchy

System Reconfiguration

Requirement

Figure 2.3. Graphs menu.

Active Component

Spare Component

Component Repair

Subsystem Recovery

System Reconfiguration

Model Generation

Model Evaluation

Figure 2.4. Parameters menu.

Specify Generate Evaluate

Figure 2.5. Model menu.

able to continue communicating. If this assumption is not true, the result will be conservative. The main purpose of the communication structure description is to analyze which component failures will prevent communication between critical components and therefore cause system failure.

2.1.1.1. External. A system's external structure is defined as the communication interconnection of all its components. The external structure graph is required for all systems because it is also used to identify the system components, their types, and their connectivity equivalence classes (defined in subsection 3.2.1). In the external structure graph, the nodes represent one or more components of the same type. Unless specific numbers are assigned, the components represented by the same node are assigned a continuous range of numbers (e.g., the components represented by a node labeled 3p could be assigned the numbers 1 through 3). A unidirectional edge between two nodes indicates that all the components of the source node can communicate with all the components of the target node. A bidirectional edge between two nodes indicates that all the components of one node can communicate with all the components of the other node and vice versa.

A plus sign (+) at the end of a component identifier indicates that this is a self-talking component. A majority of components of the same type are passive, and they do not need to communicate. Examples of passive components are memories, buses, and input/output transducers. Self-talking components need to exchange information amongst one another. Examples of self-talking components are processors, direct-memory-access device controllers, and other "smart" controllers. If not specified, the default is for components to be passive and not communicate with their own type. This information is needed to prevent ARM from requiring communication paths between components of the same type that never exchange information. Not taking this behavior into account would lead to a pessimistic evaluation of the system reliability.

An asterisk (\*) at the end of a component identifier indicates that every input port of this component is internally connected to all output ports of the component. Most buses have this internal structure. If not indicated in this way or as described in subsection 2.1.1.2, the default is for every port of a component to be disconnected from the other ports of the component.

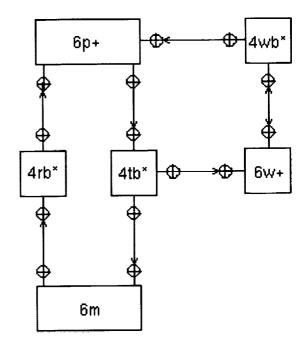

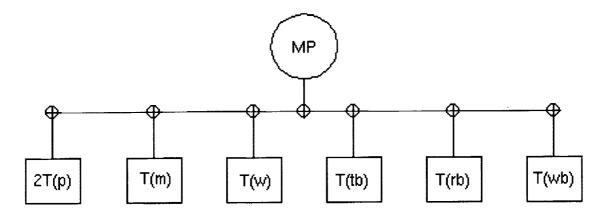

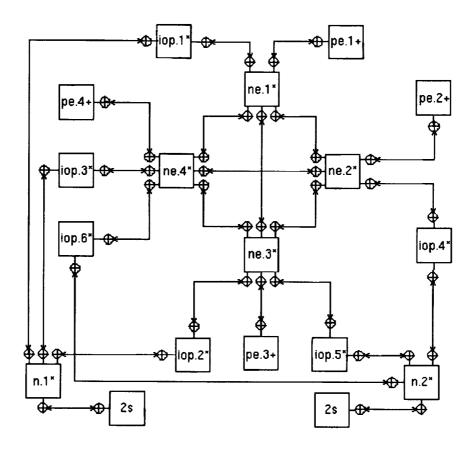

The graph in figure 2.6 describes the external structure of a multiprocessor composed of six processors p, six memories m, six watchdog timers w, four transmit buses tb, four receive buses rb, and four watchdog buses wb. The processors and watchdog timers need to communicate with components of their own type. The processors communicate through the memory as described in subsection 2.1.1.2. The watchdog timers communicate through the watchdog bus. All the buses have the

typical internal structure described above. This multiprocessor will be used as a running example throughout this section.

Figure 2.6. External structure of a multiprocessor.

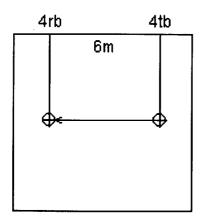

2.1.1.2. Internal. A component's internal structure is defined as the communication interconnection of its ports. This internal structure of one or more components can be described by a graph inside a component with its external port connections labeled on the outside of the component. The absence of an edge between two ports indicates that they cannot communicate through this component.

The internal structure graph of a component is used to determine which of its neighbors can communicate through it. Two components are neighbors if they are interconnected in the external structure graph. If none of a component's neighbors can communicate through it, no internal structure needs to be specified because by default a component cannot be used for communication by its neighbors.

The internal structure of each of the six memories is described by the graph in figure 2.7. This structure indicates that the processors can communicate through the memory.

#### 2.1.2. Hierarchy

A system can have physical and/or logical hierarchies that contain physical and logical subsystems, respectively. These hierarchies are different partial

Figure 2.7. Internal structure of each of the six memory components.

views of the same system; therefore, a component of a physical subsystem may also be a component of a logical subsystem. The difference between a physical and a logical subsystem is in their ability to be reconfigured and in how their failure affects the system's operation, as explained in the next two subsections. If present, the system hierarchies show what subsystems are in the initial system configuration and define the composition of the subsystems that may be part of those hierarchies.

A group of components with its own set of requirements constitutes a subsystem. If a subsystem does not meet its requirements, then none of its components are able to perform their function. If a subset of the system components, but not all of them, depends on one or more components in the subset, the subset needs to be defined as a subsystem by giving its hierarchy and requirement graphs. The subsystem defined for the subset must be placed in either the appropriate system hierarchy graph (if it is part of the initial system configuration) or the destination node of a system reconfiguration graph (if it can be part of a future system configuration). The system physical or logical hierarchy graphs can only be given if there are physical or logical subsystems, respectively.

Redundant subsystems are composed of multiple components with the same function to increase their reliability or availability. Some of these redundant subsystems may be part of the initial system configuration, while others serve as alternatives for system reconfiguration (e.g., a quad subsystem that reconfigures into a triad).

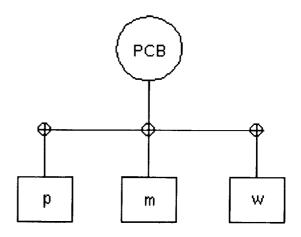

A system hierarchy is described by nondirectional tree graphs. Root nodes (identified by a circle) represent the system or one of its subsystems. Other

nodes (identified by a rectangle) represent one or more identical subsystems or components.

Unless they are assigned specific components, subsystems are assigned components with the lowest numbers available. For example, if there were six processors, numbered 1 through 6, and two processor triads, one triad would be assigned processors 1 through 3 and the other triad would be assigned processors 4 through 6.

2.1.2.1. Physical. Physical subsystems cannot be reconfigured. However, the failure of a physical subsystem does not preclude the system from operating, as long as the system requirements are met.

Figure 2.8. Physical hierarchy of the multiprocessor.

Figure 2.9. Physical hierarchy of the printed circuit board subsystem type.

Figures 2.8 and 2.9 describe the physical hierarchy of the multiprocessor (MP). Initially, the multiprocessor contains six printed circuit boards (PCB's), which belong to the same physical subsystem type.

Figure 2.10. Logical hierarchy of the multiprocessor.

Each board contains a processor, memory, and a watchdog timer.

2.1.2.2. Logical. Logical subsystems can be reconfigured. Before component failures cause them to fail, they can recover by replacing the failed components with spares. If not enough spares are available, the system can degrade to a lesser number of subsystems or a less redundant subsystem. When a logical subsystem fails, the system also fails unless it can be reinitialized by a separate subsystem or component.

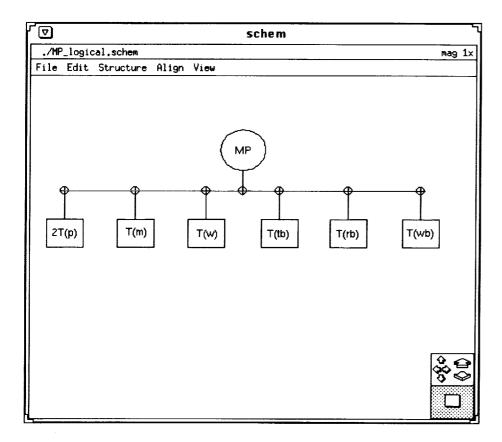

Figures 2.10 and 2.11 describe the logical hierarchy of the multiprocessor. Initially, the multiprocessor contains two processor triads, one memory triad, one watchdog triad, one transmit bus triad, one receive bus triad, and one watchdog bus triad. These triads are each composed of three components of the same type.

Figure 2.11. Logical hierarchy of the triad (T) subsystem class.

The ARM program will automatically determine what components are spares by comparing the external structure with the logical hierarchy; any extra

instances of components in the external structure, beyond what is included in the logical hierarchy, will be assumed to be spares. Therefore, from figures 2.6 and 2.10, the spare components are assumed to be three memories, three watchdog timers, one transmit bus, one receive bus, and one watchdog bus.

#### 2.1.3. System Reconfiguration

The future system configurations are described in terms of the reconfigurations allowed. A change in the system's configuration in response to some triggering event is defined as a reconfiguration. A reconfiguration occurs when the system is reinitialized because of a logical subsystem failure or when the system degrades to a lesser number of subsystems or a less redundant subsystem because no spares exist to replace a failed component. Also, the mission phase may change, thus causing the system to reconfigure. If the system is to be reinitialized because of a logical subsystem failure, only one reconfiguration must do so. To simplify the model specification, a single reconfiguration will only be allowed to degrade a subsystem to, at most, two less components. For example, one reconfiguration could take a subsystem from a quintuple to a triad, and a subsequent reconfiguration could take it to a simplex.

A reconfiguration is described in part by one or more unidirectional graphs. A source node represents one or more of the components or subsystems (physical or logical) which must be active before the reconfiguration. A destination node represents either the reinitialized system or one or more of the logical subsystems that will be active after the reconfiguration in place of the logical subsystems identified by its source node. Each edge is labeled with the name of a specification that will provide the triggering event and the rest of the reconfiguration parameters, described in subsection 2.2.5, which will complete the

description of the reconfiguration. The specification name can contain letters, underscores, and digits in any order.

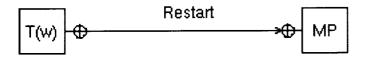

Figure 2.12 describes the reinitialization of the multiprocessor by the watchdog triad. Figure 2.13 describes the degradation of the multiprocessor from two processor triads (PT's) to one. If the recovery rate of the remaining triad is specified as being greater than 0, the working processors in the deactivated triad are assumed to become spares.

Figure 2.12. Reinitialization of the multiprocessor.

Figure 2.13. Degradation of the multiprocessor.

Currently, only the reconfigurations that degrade the system have been implemented. Therefore, at the present time, reconfiguration graphs are needed only for systems that have logical subsystems and can degrade to a lesser number of logical subsystems and/or to less redundant logical subsystems.

#### 2.1.4. Requirement

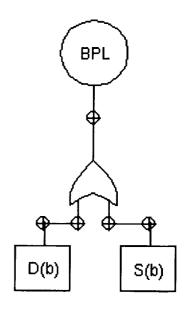

The requirement of a system or subsystem is defined as the minimum set of subsystems and components needed. Performance levels can be used to identify the nondegraded mode and the various degraded modes of operation a system might have.

This requirement is described by one or more success trees. Root nodes (identified by a circle) represent the system, one of its subsystems, or a performance level. Other nodes (identified by a rectangle) represent one or more identical subsystems, a performance level, or one or more identical components. It is assumed that components in the system success tree are not in any logical subsystem. A success tree is required for all systems, subsystems, and performance levels.

Success trees and fault trees use the same notation, but they define the combination of events that will cause the system to succeed or fail, respectively. The advantages of success trees over fault trees are

that (1) they are more intuitive for a computer engineer who is concerned with making the system work and not with how it can fail and that (2) a conservative reliability estimate is produced if some modes of operation are left out of the success tree, because system failure is assumed for those modes of operation, whereas an optimistic reliability estimate is produced if a failure mode is left out of a fault tree.

The graphs in figures 2.14 to 2.16 describe the system and subsystem requirements of the multiprocessor. This multiprocessor can operate at one of two performance levels. To achieve full performance (FP), both processor triads, the watchdog triad, and the memory triad must be operational. The requirements for degraded performance (DP) are the same except that only one processor triad is needed. Each printed circuit board requires that its memory be working for it to be operational. Subsystems of the triad class require two of their three components to operate.

#### 2.2. Parameters

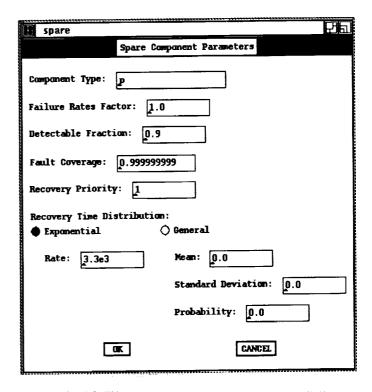

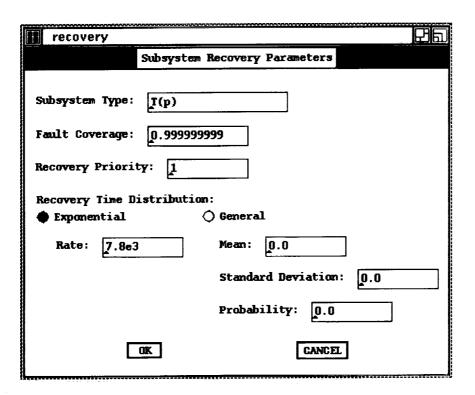

The following subsections describe the parameter specification windows. Any time unit may be used for the parameter values as long as it is the same one for all of them. The time unit used for ARM parameters throughout this paper is hours. The OK and CANCEL buttons in each window save and discard the parameter changes made, respectively. Selecting either button makes the window disappear.

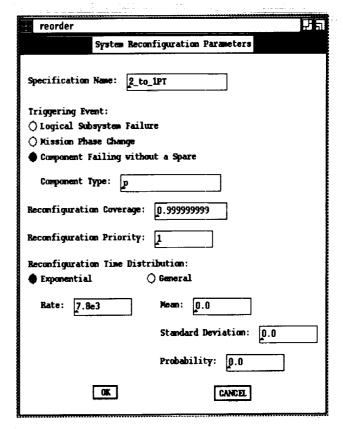

The ARM program will assume that a transition which reconfigures components and/or subsystems in or out of the system describes sequential processes. For example, if n faults exist in one or more subsystems of the same type with recovery rate  $\rho$ , the rate at which one of the faulty components is replaced by a spare is assumed to be  $\rho$  not  $n\rho$ . If this assumption is not true, the result will be conservative. Typically, these transitions are fast, in which case this assumption being false would have little effect.