https://ntrs.nasa.gov/search.jsp?R=19930023050 2020-03-17T05:13:52+00:00Z

P-182

#### NASA-CR-193619

**IMPLEMENTATION OF INTERCONNECT SIMULATION TOOLS IN SPICE**

by

H. Satsangi J. E. Schutt-Aine

Department of Electrical and Computer Engineering University of Illinois 1406 W. Green Street Urbana, IL 61801

> Technical Report August 1993

> > Prepared for

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION NASA-Ames Research Center Moffett Field, CA 94035-1000

#### Grant No. NASA NAG2-823

#### (NASA-CR-193619) IMPLEMENTATION OF INTERCONNECT SIMULATION TOOLS IN SPICE (Illinois Univ.) 182 p

N93-32239

**Unclas**

G3/61 0179682

Electromagnetic Communication Laboratory Report No. 93-4

#### IMPLEMENTATION OF INTERCONNECT SIMULATION TOOLS IN SPICE

by

H. Satsangi J. E. Schutt-Aine

Department of Electrical and Computer Engineering University of Illinois 1406 W. Green Street Urbana, IL 61801

> Technical Report August 1993

> > Prepared for

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION NASA-Ames Research Center Moffett Field, CA 94035-1000

Grant No. NASA NAG2-823

Electromagnetic Communication Laboratory Department of Electrical and Computer Engineering Engineering Experiment Station University of Illinois at Urbana-Champaign Urbana, Illinois 61801

## ABSTRACT

Accurate computer simulation of high speed digital computer circuits and communication circuits requires a multimode approach to simulate both the devices and the interconnects between devices. Classical circuit analysis algorithms (lumped parameter) are needed for circuit devices and the network formed by the interconnected devices. The interconnects, however, have to be modeled as transmission lines which incorporate electromagnetic field analysis.

An approach to writing a multimode simulator is to take an existing software package which performs either lumped parameter analysis or field analysis and add the missing type of analysis routines to the package. In this work a traditionally lumped parameter simulator, SPICE, is modified so that it will perform lossy transmission line analysis using a difference model approach.

Modifying SPICE3E2 or any other large software package is not a trivial task. An understanding of the programming conventions used, simulation software, and simulation algorithms is required. This thesis was written to clarify the procedure for installing a device into SPICE3E2. The installation of three devices is documented and the installations of the first two provide a foundation for installation of the lossy line which is the third device. The details of discussions are specific to SPICE, but the concepts will be helpful when performing installations into other circuit analysis packages.

----------------

# TABLE OF CONTENTS

------

\_\_\_\_\_

| 1. | INTRODU       | JCTION                                                       | 1  |

|----|---------------|--------------------------------------------------------------|----|

|    | 1.1.          | Background                                                   | 1  |

|    | 1.2.          | Purpose                                                      | 2  |

|    | 1.3.          | Contents                                                     | 2  |

|    | 1.4.          | SPICE3E2 Comments                                            | 3  |

| 2. | GENERA        | L OPERATION OF A STAMP ORIENTED SIMULATOR                    | 4  |

|    | 2.1.          | General Circuit Simulator Flow Chart                         |    |

|    | 2.2.          | Circuit Description                                          |    |

|    | 2.2.          | Construction of Circuit Matrix                               | 7  |

|    | 2.01          | 2.3.1. Linear resistor stamp                                 | 10 |

|    |               | 2.3.2. Independent voltage source stamp                      | 11 |

|    | 2.4.          | Matrix Solution Techniques and Sparsity                      | 15 |

|    | 2.5.          | Output of Results                                            | 16 |

|    | 2.5.          | Notes on Transient and Nonlinear Analysis                    | 16 |

|    | 2.7.          | Summary                                                      | 20 |

| 3. | <b>ΝΕΡΙΛΆ</b> | TION OF TRANSMISSION LINE STAMPS                             | 21 |

| 5. | 3.1.          | Number of Device Nodes and Stamp Size                        |    |

|    | 3.1.          | 3.1.1.       One-port devices                                | 22 |

|    |               | 3.1.2. Two-port stamps                                       | 23 |

|    | 2 0           | Voltage Source/Impedance Stamp for the Lossless Transmission |    |

|    | 3.2.          | Line                                                         | 23 |

|    | 3.3.          | Current Source/Admittance Stamp for a Transmission Line      | 26 |

|    | 5.5.          | 3.3.1. Independent current source stamp                      | 26 |

|    |               | 3.3.2. Lossless transmission line stamp                      | 27 |

|    |               | 3.3.3. Transient analysis of a lossy transmission line       | 29 |

|    | 3.4.          | Stamp Comparison                                             | 29 |

|    | 3.5.          | Summary                                                      | 30 |

|    | 2.2.          | <u> </u>                                                     |    |

| 4. | OVERVI<br>INSTALI | EW OF ASPECTS OF SPICE3E2 RELEVANT TO DEVICE                   | 31 |

|----|-------------------|----------------------------------------------------------------|----|

|    | 4.1.              | Organization and Conventions in SPICE3E2 Relevant to Device    |    |

|    |                   | Installation                                                   |    |

|    |                   | 4.1.1. Packages                                                |    |

|    |                   | 4.1.2. Interpackage communication                              |    |

|    |                   | 4.1.3. Package function naming conventions                     |    |

|    |                   | 4.1.4. Devices, models, and instances                          |    |

|    |                   | 4.1.5. The CKT data structure                                  |    |

|    |                   | 4.1.6. Summary of relevant organizations and conventions       |    |

|    | 4.2.              | SPICE3E2 Directory Structure                                   |    |

|    | 4.3.              | Loading a Device Stamp into the Circuit Matrix in Spice3e2     |    |

|    |                   | 4.3.1. Storage of instance specific data                       |    |

|    |                   | 4.3.2. Insertion of a device stamp into the circuit matrix     |    |

|    | 4.4.              | Loading of Device Data from the Input File                     |    |

|    | 4.5.              | Summary                                                        | 45 |

| 5. | DEVICE            | INSTALLATION STRATEGY                                          | 47 |

|    | 5.1.              | General Approach                                               | 47 |

|    | 5.2.              | Specific Strategy                                              |    |

|    | 5.3.              | Twelve-Step Plan                                               |    |

|    | 5.4.              | Summary                                                        |    |

| 6. | INSTALI           | LATION OF A NEGATIVE RESISTOR                                  | 52 |

|    | 6.1.              | Description of the Negative Resistor Stamp                     |    |

|    | 6.2.              | Description of the Negative Resistor Input File Line           |    |

|    | 6.3.              | Details of the Twelve-Device Installation Steps for a Negative |    |

|    | 0.5.              | Resistor                                                       | 54 |

|    |                   | 6.3.1. Create negative resistor directory                      |    |

|    |                   | 6.3.2. Copy files of ordinary resistor                         |    |

|    |                   | 6.3.3. Change names in copied device files                     |    |

|    |                   | 6.3.4. Change names in copied header files                     |    |

|    |                   | 6.3.5. Change names in copied parser file                      |    |

|    |                   | 6.3.6. Modify parser header file                               |    |

|    |                   | 6.3.7. Modify main parsing routine                             |    |

|    |                   | 6.3.8. Modify simulator files                                  |    |

|    |                   | 6.3.9. Modify files used by make                               |    |

|    |                   | 6.3.10. Verify establishment of communication with the main    |    |

|    |                   | code                                                           | 59 |

|    |                   | 6.3.11. Modify operation of copied device code                 |    |

|    |                   | 6.3.12. Check new device operation                             |    |

|    | 6.4.              | Summary                                                        |    |

| 7. | INSTALI<br>TRANSI     | LATION (<br>ENT ANA                                                                                                              | OF A LOSSLESS TRANSMISSION LINE MODEL FOR<br>ALYSIS                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|----|-----------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|    | 7.1.                  | Lossles                                                                                                                          | s Transmission Line Models Revisited                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

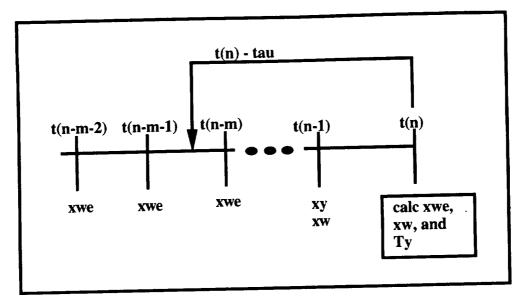

|    | 7.2.                  |                                                                                                                                  | cing Previous Values                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|    |                       | 7.2.1.                                                                                                                           | The delay table                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|    |                       | 7.2.2.                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|    |                       | 7.2.3.                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|    |                       | 7.2.4.                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|    | 7.3.                  |                                                                                                                                  | source/Impedance Model vs. Current Source/Admittance                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|    | 7.51                  | Model                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|    | 7.4.                  |                                                                                                                                  | ry of Steps 1 Through 10 of the Installation                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|    | 7.5.                  |                                                                                                                                  | s Comprising Step 11                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|    |                       | 7.5.1.                                                                                                                           | Modifications to ntradefs.h                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|    |                       | 7.5.2.                                                                                                                           | Modification to ntrasetup.c                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|    |                       | 7.5.3.                                                                                                                           | Modifications to ntraask.c                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|    |                       | 7.5.4.                                                                                                                           | Modification of ntraload.c                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|    |                       | 7.5.5.                                                                                                                           | Modifications to ntraacct.c                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|    |                       | 7.5.6.                                                                                                                           | Modifications to intraduce                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|    | 7.6.                  |                                                                                                                                  | ary                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| ο. |                       | ENT ANA                                                                                                                          | DF A LOSSY TRANSMISSION LINE MODEL FOR<br>LYSIS                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|    | 8.2.                  |                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|    | 8.3.                  |                                                                                                                                  | Requirements of the Source Function                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|    | 8. <i>3</i> .<br>8.4. |                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|    | 0.4.                  |                                                                                                                                  | cation Strategy74                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|    |                       | Convers                                                                                                                          | cation Strategy74<br>sion to Lossy Line Model Part I74                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|    |                       | Convers<br>8.4.1.                                                                                                                | cation Strategy                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|    |                       | Convers<br>8.4.1.<br>8.4.2.                                                                                                      | cation Strategy                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|    |                       | Convers<br>8.4.1.<br>8.4.2.<br>8.4.3.                                                                                            | cation Strategy                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|    |                       | Convers<br>8.4.1.<br>8.4.2.<br>8.4.3.<br>8.4.4.                                                                                  | cation Strategy                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|    |                       | Convers<br>8.4.1.<br>8.4.2.<br>8.4.3.<br>8.4.4.<br>8.4.5.                                                                        | cation Strategy                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|    |                       | Convers<br>8.4.1.<br>8.4.2.<br>8.4.3.<br>8.4.4.<br>8.4.5.<br>8.4.6.                                                              | cation Strategy                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|    |                       | Convers<br>8.4.1.<br>8.4.2.<br>8.4.3.<br>8.4.4.<br>8.4.5.<br>8.4.5.<br>8.4.6.<br>8.4.7.                                          | cation Strategy                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|    |                       | Convers<br>8.4.1.<br>8.4.2.<br>8.4.3.<br>8.4.4.<br>8.4.5.<br>8.4.6.                                                              | cation Strategy                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|    |                       | Convers<br>8.4.1.<br>8.4.2.<br>8.4.3.<br>8.4.4.<br>8.4.5.<br>8.4.5.<br>8.4.6.<br>8.4.7.                                          | cation Strategy                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|    | 8.5.                  | Convers<br>8.4.1.<br>8.4.2.<br>8.4.3.<br>8.4.4.<br>8.4.5.<br>8.4.6.<br>8.4.7.<br>8.4.8.<br>8.4.9.                                | cation Strategy.74sion to Lossy Line Model Part I.74Insert parameter fields into device data structure.75Modify ntraitf.h.75Modify ntraparam.c75Modify ntrasetup.c76Modify ntraload.c.76Modify ntratrunc.c.78Modify ntratrunc.c.78Update spice3e2/src/lib/dev/ntra directory, and modify79Verify the model gives the correct results for the specific79                                                                                       |  |  |

|    | 8.5.                  | Convers<br>8.4.1.<br>8.4.2.<br>8.4.3.<br>8.4.4.<br>8.4.5.<br>8.4.6.<br>8.4.7.<br>8.4.8.<br>8.4.9.                                | cation Strategy.74sion to Lossy Line Model Part I.74Insert parameter fields into device data structure.75Modify ntraitf.h.75Modify ntraparam.c75Modify ntrasetup.c76Modify ntraload.c.76Modify ntratrunc.c.78Update spice3e2/src/lib/dev/ntra directory, and modify79Verify the model gives the correct results for the specific79ion to Lossy Line Model Part II.79                                                                          |  |  |

|    | 8.5.                  | Convers<br>8.4.1.<br>8.4.2.<br>8.4.3.<br>8.4.4.<br>8.4.5.<br>8.4.6.<br>8.4.7.<br>8.4.8.<br>8.4.9.<br>Convers                     | cation Strategy.74sion to Lossy Line Model Part I.74Insert parameter fields into device data structure.75Modify ntraitf.h.75Modify ntraparam.c75Modify ntrasetup.c76Modify ntraload.c.76Modify ntratrunc.c.78Modify ntratrunc.c.78Update spice3e2/src/lib/dev/ntra directory, and modify79Verify the model gives the correct results for the specific79ion to Lossy Line Model Part II.79Write the function fileread80                        |  |  |

|    | 8.5.                  | Convers<br>8.4.1.<br>8.4.2.<br>8.4.3.<br>8.4.4.<br>8.4.5.<br>8.4.6.<br>8.4.7.<br>8.4.8.<br>8.4.9.<br>Convers<br>8.5.1.           | cation Strategy.74sion to Lossy Line Model Part I.74Insert parameter fields into device data structure.75Modify ntraitf.h.75Modify ntraparam.c.75Modify ntrasetup.c.76Modify ntraload.c.76Modify ntratrunc.c.78Update spice3e2/src/lib/dev/ntra directory, and modify79Verify the model gives the correct results for the specific79ion to Lossy Line Model Part II.79Write the function fileread80Modify ntra.c to include a new parameter80 |  |  |

|    | 8.5.                  | Convers<br>8.4.1.<br>8.4.2.<br>8.4.3.<br>8.4.4.<br>8.4.5.<br>8.4.6.<br>8.4.7.<br>8.4.8.<br>8.4.9.<br>Convers<br>8.5.1.<br>8.5.2. | cation Strategy.74sion to Lossy Line Model Part I.74Insert parameter fields into device data structure.75Modify ntraitf.h.75Modify ntraparam.c75Modify ntrasetup.c76Modify ntraload.c.76Modify ntratrunc.c.78Modify ntratrunc.c.78Update spice3e2/src/lib/dev/ntra directory, and modify79Verify the model gives the correct results for the specific79ion to Lossy Line Model Part II.79Write the function fileread80                        |  |  |

.

| 8.6.      | Transient Analysis Run of the Lossy Line        |

|-----------|-------------------------------------------------|

| 0.01      | 8.6.1. Formulate circuit                        |

|           | 8.6.2. Place line specifications in a file      |

|           | 8.6.3. Run vdmdiff                              |

|           | 8.6.4. Write SPICE input file                   |

|           | 8.6.5. Perform analysis                         |

| 8.7.      | Summary                                         |

| 0.7.      | Summary                                         |

| 9. CONCLU | USIONS                                          |

| 9.1.      | Direct Current and Alternating Current Analysis |

| 2.2.      | 9.1.1. dc analysis                              |

|           | 9.1.2. ac analysis                              |

| 9.2.      | Modifications to Increase Manageability         |

|           | 9.2.1. Modularizing NTRAload                    |

|           | 9.2.2. NTRAloadLHS                              |

|           | 9.2.3. NTRAdcLoad90                             |

|           | 9.2.4. NTRAloadUIC90                            |

|           | 9.2.5. NTRAloadUdc90                            |

|           | 9.2.6. NTRAinitDelTab90                         |

|           | 9.2.7. NTRAcalcRHS                              |

|           | 9.2.8. NTRAgetInterpExcit191                    |

|           | 9.2.9. CKTgetSol                                |

|           | 9.2.10. NTRAloadRHS                             |

|           | 9.2.11. CKTgetMode92                            |

| 9.3.      | Summary                                         |

|           |                                                 |

| APPEND    | IX A. RESISTOR CODE                             |

| A.1.      | Device Specific Files                           |

|           | A.1.1. Contents of nresload.c before renaming   |

|           | A.1.2. Contents of nresload.c after renaming94  |

|           | A.1.3. Contents of nres.c before renaming95     |

|           | A.1.4. Contents of nres.c after renaming        |

| A.2.      | Device Header Files97                           |

|           | A.2.1. nresdefs.h after renaming97              |

|           | A.2.2. nresext.h after renaming                 |

|           | A.2.3. nresitf.h after renaming100              |

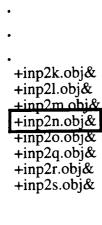

| A.3.      | INP2N102                                        |

|           | A.3.1. Contents of inp2n.c before renaming102   |

|           | A.3.2. Contents of inp2n.c after renaming105    |

| A.4.      | Parser Header File107                           |

| A.5.      | INPpas2108                                      |

| A.6.      | Main Parsing Routine                            |

|              | A.6.1.         | Contents of bconf.c after modification      | 109 |

|--------------|----------------|---------------------------------------------|-----|

|              | A.6.2.         | Contents of subckt.c after modification     | 110 |

| A.7.         | Files Use      | ed by Make                                  | 111 |

|              | A.7.1.         |                                             | 111 |

|              | A.7.2.         | Contents of msc51.bat before modification   | 112 |

|              | A.7.3.         | Excerpt from defaults after modification    | 112 |

|              | A.7.4.         | Excerpt from response.lib after modication  | 113 |

| A.8.         | NRESlo         | ad                                          | 113 |

|              | A.8.1.         | Excerpt from nresload.c before modification | 113 |

|              | A.8.2.         | Excerpt from nresload.c after modification  | 114 |

|              |                | OSSLESS TRANSMISSION LINE CODE              | 115 |

|              |                |                                             |     |

| <b>B</b> .1. | Device         | Data Structure                              | 115 |

|              |                | Contents of ntradefs.h before modification  |     |

|              |                | Contents of ntradefs.h after modification   |     |

| B.2.         | NTRAsett       | 1p                                          | 120 |

|              | B.2.1.         | Contents of ntrasetup.c before modification | 120 |

|              | B.2.2.         | Contents of ntrasetup.c after modification  | 122 |

| <b>B</b> .3. | NTRAask        |                                             | 124 |

| <b>B</b> .4. |                | d                                           | 124 |

|              | <b>B.4</b> .1. |                                             |     |

|              |                | Contents of ntraload.c after modification   |     |

| B.5.         |                | Aacct                                       |     |

|              |                | Contents of ntraacct.c before modification  |     |

|              | B.5.2.         |                                             |     |

| <b>B.6</b> . |                | nc                                          |     |

|              | <b>B</b> .6.1. |                                             |     |

|              | B.6.2.         | Contents of ntratrunc.c after modification  | 133 |

| APPENI       | DIX C. I       | LOSSY TRANSMISSION LINE CODE                | 135 |

| C.1.         |                | n Decleration and Argument Description of G |     |

| C.2.         | Content        | s of an Example Difference Parameters File  | 138 |

| C.3.         | Header         | Files                                       | 139 |

| 0.01         | C.3.1.         | Contents of ntradefs.h after modification   | 139 |

|              |                | Contents of ntraitf.h                       |     |

| C.4.         |                | aram                                        |     |

| C.5.         | NTRAS          | etup                                        | 143 |

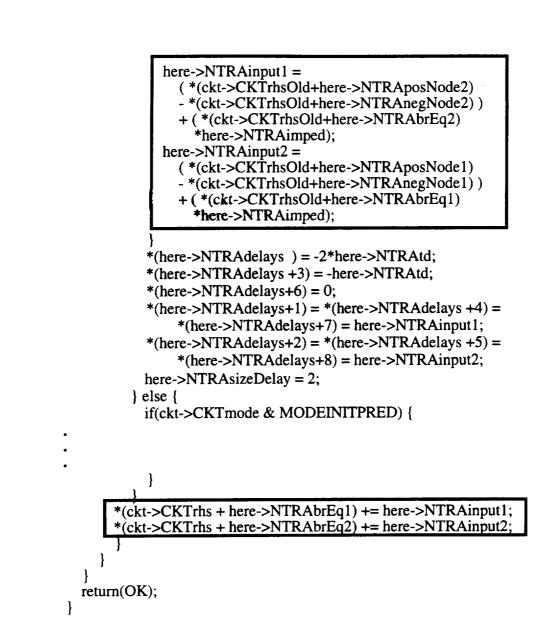

| C.6.         | NTRA           | oad                                         | 147 |

| 0.0.         | C.6.1.         | Contents of ntraload.c before modification  | 147 |

|              | C.6.2.         |                                             |     |

| C.7.         |                | acct                                        |     |

| 0            | C.7.1.         | Contents of ntraacct.c before modification  | 155 |

|                | C.7.2. Contents of ntraacct.c after modification                 | 155 |

|----------------|------------------------------------------------------------------|-----|

| C.8.           | NTRAtrunc                                                        | 156 |

|                | C.8.1. Contents of ntratrunc.c before modification               | 156 |

|                | C.8.2. Contents of ntratrunc.c after modification                | 157 |

| C.9.           | Listing of the Function fileread                                 | 158 |

| <b>C</b> .10.  | IFparm Table                                                     | 160 |

| C.11.          | NTRAparam                                                        | 161 |

| APPEND<br>D.1. | VIX D. FUTURE CODE MODIFICATIONS<br>Complete listing of NTRAload |     |

|                |                                                                  |     |

| D.2.           | Modified NTRAload                                                |     |

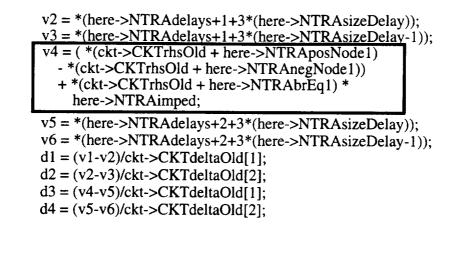

|                | NTRAcalcRHS                                                      |     |

| D.4.           | NTRAgetInterpExcit1                                              | 169 |

| D.5.           | NTRAgetDelTabIndGrtr                                             | 170 |

| REFERENCE      | ES                                                               | 172 |

## 1. INTRODUCTION

### 1.1. Background

Computer simulation of circuits has been used for years to test and verify circuit designs at the gate level or transistor level. Interconnections were originally modeled as lumped parameter shorts. As device speeds became faster and integrated circuits became smaller and denser, interconnects could no longer be modeled as lumped parameter shorts. Instead, the interconnects are now modeled as transmission lines to take into account cross-talk noise, wave-form distortion, and signal attenuation effects [1].

Simulating circuits at the transistor level which contain interconnects requires that a circuit simulator have the capability of handling ordinary circuit analysis and electromagnetic analysis. Simulators which handle both types (or three types if gate level is included) are termed multimode.

One approach used in writing a multimode simulator is to utilize a standard circuit analysis package which works for one type of analysis and to add in components which perform the other analysis types. In this work, transmission line models have been inserted into a traditionally lumped parameter simulator. The insertion of devices into an existing circuit analysis package is not a trivial task. Accurate and detailed documentation of the analysis package is required along with an understanding of the general algorithm driving the circuit analysis program. An understanding of the programming conventions used in large software packages is also required.

## 1.2. Purpose

This thesis describes the insertion of a lossy transmission line model for transient analysis into the SPICE3E2 circuit analysis program. A lossless and lossy transmission line model already exist in SPICE3E2 (see [2] for SPICE3E2 lossy line background). A good introduction to transmission line analysis is found in [3] and much more detail is found in [4]. The concern of this thesis is not to compare the SPICE indigenous models with the models to be installed, but to detail the installation procedure for the step invariant difference model of the lossy transmission line. The thesis has two main purposes. The first is to document the modifications made to SPICE3E2 in order to incorporate a new lossy line model, and the second is to elucidate the device installation procedure with respect to SPICE3E2. The installation of a device into SPICE3E2 (see [5] - [11]) is not up to date with the release and assumes that the reader has a level of familiarity with the functioning of a circuit simulator code. The documentation which comes standard with SPICE3E2 is the documentation for SPICE3C, and in the device installation section there is an omission of one important step.

This thesis can by itself be used as a "how to guide" with respect to device installation. It is, however, not a replacement for the SPICE3E2 manuals in any other way, but can be used in conjunction with the SPICE3E2 manuals to gain a better understanding of the functioning of the SPICE3E2 circuit simulator.

#### 1.3. Contents

Two purposes of the thesis were mentioned in the previous section. The second purpose was to serve as a device installation tutorial with respect to SPICE3E2. To this end the thesis is organized in the following fashion: circuit simulator information and device installation information. Chapter 2 contains general information on circuit analysis programs such as the general circuit analysis program algorithm and techniques for implementing each step of the algorithm. Chapter 3 is an extension of Chapter 2 and is specifically concerned with transmission lines. Chapter 4 discusses the SPICE3E2 circuit analysis program and, in particular, the background information necessary with respect to device installation. Chapter 5 gives an overview of the device installation process, and Chapters 6 through 8 are step by step examples of device installations. Chapter 6 details the installation procedure for a contrived device to illustrate the bookkeeping portion common to all device installations. Chapter 7 lays the foundation for the lossy line by detailing the installation steps for a lossless transmission line model for transient analysis. Chapter 8 details the installation of the lossy transmission line model for transient analysis into SPICE3E2 by converting the routines of the lossless transmission line installed in Chapter 7. Chapter 9 is the concluding chapter and it discusses and suggests some extensions and modifications to SPICE3E2, which would increase the manageability of the code.

### 1.4. SPICE3E2 Comments

The source code for SPICE3E2 is available from UC Berkeley free of charge. The program is written in the C programming language [12]. In order to make modifications to the source code, the programmer must be proficient in the C language. The source was modified when installing the lossy transmission line. Listings of the source code involved in or modified during device installation are given in the appendices. To conserve space, only relevant portions of the code listings are shown, and in many cases the header files associated with a function were not shown. In all cases, a copyright statement associated with each code listing was not shown. Most of the code that will be shown was originally written by T. Quarles and the copyright statement associated with the code is shown below.

/\*\*\*\*\*\*\*\*

Copyright 1990 Regents of the University of California. All rights reserved. Author: 1985 Thomas L. Quarles

## 2. GENERAL OPERATION OF A STAMP ORIENTED SIMULATOR

This chapter discusses the basics of circuit simulator operation. The general algorithm and each of its components are examined. The discussion is within the framework of linear device analysis and confined to resistors and independent voltage sources. The examples in this chapter apply to SPICE3E2, but the concepts are general. Implementation details and low level algorithms have been deferred to Chapters 4, 6, 7, and 8.

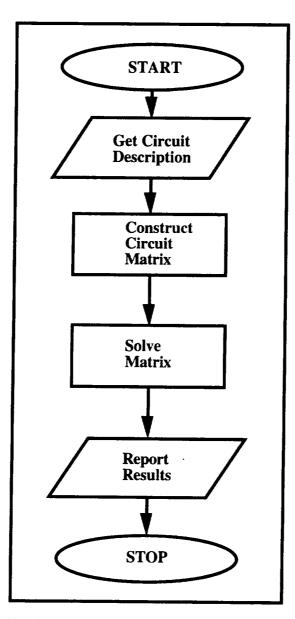

# 2.1. General Circuit Simulator Flow Chart

A general flow chart indicating the major steps in the execution of a circuit analysis program is shown in Figure 2.1. First, the circuit and simulation descriptions are obtained from user input. The information from the user is organized in a form most suitable for the steps to follow. Once the input information is appropriately organized, a matrix equation

$$\mathbf{A}\mathbf{x} = \mathbf{b}, \tag{2.1}$$

where A is an n x n matrix, is constructed. The matrix equation is solved for x, and the results are made available. Depending on the type of analysis, steps Construct Circuit Matrix and Solve Matrix may be executed multiple times before all or any of the results are available.

Figure 2.1. Circuit analysis algorithm in flow chart form.

The details of the algorithms and programming differ from simulator to simulator, but the overall steps are the same. In the following sections, each of the steps is examined, and strategies or algorithms are presented. The most important step with respect to this thesis is the second, Construct Circuit Matrix. The modifications that will be discussed in the subsequent chapters primarily concern this second step.

#### 2.2. Circuit Description

Analysis of a circuit commences after the circuit and simulation information are provided by the user. User input is often obtained through a graphical interface. Alternatively, a text file may be filled by the user, listing the devices, device parameters, interconnections of the devices, and simulation specifications. Regardless of the manner used to communicate circuit and simulation descriptions, the information is stored in simulator data structures for later referral by the matrix construction circuit simulation routines. The format of the data structure containing the circuit information is the subject of this section.

Data structure formats are dictated by the algorithms and routines accessing the structure. Matrix construction algorithms, discussed further in the following section, access and, therefore, define the format of the circuit description structures.

Equations for a circuit may be written using a node by node application of Kirchoff's Current Law (KCL). A node by node approach results in a data structure comprised of a linked list containing elements associated with each node. Among the fields of the list element would be fields containing node identification information, fields associated with all elements branching from the node, and fields containing neighbor node information. Considering a device connected between nodes a and b, the node by node algorithm references the device once at node a and once at node b. Therefore, the matrix fill routines must be accessed twice for each device in the circuit.

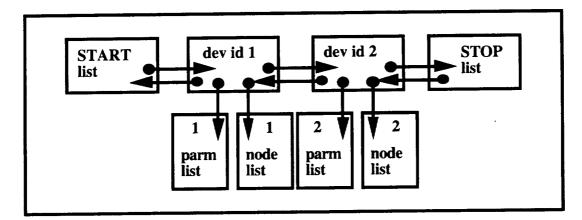

A more popular algorithm for filling a circuit matrix accesses the matrix fill routines only once per device. This method employs a device by device approach, and is discussed in more detail in the following section. The device by device routine requires a linked list similar to that shown in Figure 2.2. In the data structure of Figure 2.2 link elements include the device identification, a pointer to a device parameter list, a pointer to a list of nodes connected to the device, a forward pointer, and a backward pointer as a minimum. Other fields, needed for overhead, are not shown.

Figure 2.2. Linked list structure used with device by device matrix fill algorithm for storing circuit description.

## 2.3. Construction of Circuit Matrix

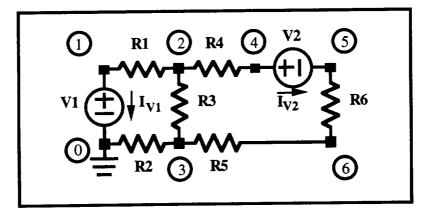

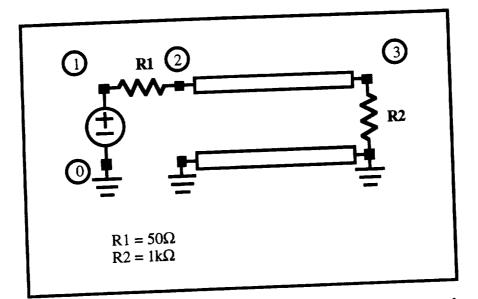

Equations describing a circuit can be written by employing KCL or Kirchoff's Voltage Law (KVL) analysis [13]. KCL is used in circuit simulators. Nodal analysis of the circuit given in Figure 2.3 yields Equations (2.2) - (2.9).

Figure 2.3. Example Circuit 1. Nodes are labeled by encircled numbers.

$$\frac{V_1 - V_2}{R_1} + I_{V_1} = 0 \tag{2.2}$$

$$\frac{V_2 - V_1}{R1} + \frac{V_2 - V_3}{R3} + \frac{V_2 - V_4}{R4} = 0$$

(2.3)

$$\frac{\mathbf{V}_3 - \mathbf{V}_2}{\mathbf{R}^3} + \frac{\mathbf{V}_3}{\mathbf{R}^2} + \frac{\mathbf{V}_3 - \mathbf{V}_6}{\mathbf{R}^5} = 0$$

(2.4)

$$\frac{V_4 - V_2}{R4} + I_{V2} = 0 \tag{2.5}$$

$$\frac{V_5 - V_6}{R6} - I_{V2} = 0 \tag{2.6}$$

$$\frac{V_6 - V_5}{R6} + \frac{V_6 - V_3}{R5} = 0 \tag{2.7}$$

$$V_1 = V1 \tag{2.8}$$

$$V_4 - V_5 = V2$$

(2.9)

Equations (2.2) - (2.9) can be rewritten in the following form:

$$\left(\frac{1}{R_1}\right)V_1 + \left(\frac{-1}{R_2}\right)V_2 + (1)I_{V_1} = 0$$

(2.10)

$$\left(\frac{1}{R1} + \frac{1}{R3} + \frac{1}{R4}\right)V_2 + \left(\frac{-1}{R1}\right)V_1 + \left(\frac{-1}{R3}\right)V_3 + \left(\frac{-1}{R4}\right)V_4 = 0$$

(2.11)

$$\left(\frac{1}{R^3} + \frac{1}{R^2} + \frac{1}{R^5}\right) V_3 + \left(\frac{-1}{R^3}\right) V_2 + \left(\frac{-1}{R^5}\right) V_6 = 0$$

(2.12)

$$\left(\frac{1}{R4}\right)V_4 + \left(\frac{-1}{R4}\right)V_2 + (1)I_{V2} = 0$$

(2.13)

$$\left(\frac{1}{R6}\right)V_5 + \left(\frac{-1}{R6}\right)V_6 + (-1)I_{V2} = 0$$

(2.14)

$$\left(\frac{1}{R6} + \frac{1}{R5}\right)V_6 + \left(\frac{-1}{R6}\right)V_5 + \left(\frac{-1}{R5}\right)V_3 = 0$$

(2.15)

$$(1)V_1 = V1 (2.16)$$

$$(1)V_4 + (-1)V_5 = V2 \tag{2.17}$$

The equations can be solved systematically by putting them into a matrix of the form of Equation (2.1) with  $\mathbf{x} = \mathbf{v}$ , and  $\mathbf{b} = \mathbf{s}$ , where  $\mathbf{v}$  is the voltage and current vector, or the values of the voltages at all the different nodes and currents in particular branches, and  $\mathbf{s}$  is the source vector or the values of independent sources in the circuit.

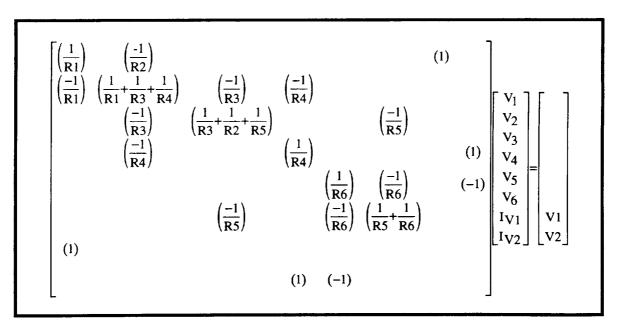

The resulting matrix is shown in Figure 2.4. This matrix can be solved for the node voltages  $V_1$  to  $V_6$  and the branch currents  $I_{v1}$  and  $I_{v2}$ . Any other branch currents can be obtained by using the node voltages and component values. All of which are known after solving the matrix.

Figure 2.4. Matrix for Example Circuit 1.

In a circuit analysis program the construction of a matrix, such as shown in Figure 2.4, follows the conversion of user input into a circuit representation (ref. Figure 2.1). A popular method to construct the matrix employed by circuit simulators, including SPICE, takes advantage of the fact that each device in the circuit makes an independent contribution to the circuit matrix. The pattern representing this contribution is termed a stamp.

#### 2.3.1. Linear resistor stamp

A linear resistor contributes to the circuit equations in the same manner for dc, ac, and transient analysis. The stamp derived in this section is valid for all linear resistors obeying Equation (2.18) [14].

$$\mathbf{v} = \mathbf{iR} \tag{2.18}$$

Refer to nodes 2, 3, and the resistor R3 between the two nodes from the circuit of Figure 2.3. It is seen from the matrix (Figure 2.4) that R3 is present only in the rows corresponding to nodes 2 and 3. R3 is not included in the KCL equation at nodes other than 2 and 3 since it is connected to only nodes 2 and 3 and is not a control for a dependent device. KCL at a node takes the form of Equation (2.19).

$$i_1 + i_2 + i_3 + \dots + i_n = 0$$

(2.19)

The numbers 1, 2, 3, and n are indices for the branches connected to the node of interest. All of the currents are assumed to be going out of the node. At node 2,  $i_1$  will be assigned the current going through R1,  $i_2$  the current going through R4, and  $i_3$  the current going through R3. The equation for current  $i_3$  is shown below, assuming resistor R3 has value R3.

$$i_3 = \frac{V_2 - V_3}{R3} \tag{2.20}$$

The branch current,  $i_3$ , is the only expression involving R3 in the KCL equation written at node 2. Applying KCL at node 3 with  $i_3$  assigned to the current flowing through R3, and out of node 3, as opposed to out of node 2, yields

$$i_3 = \frac{V_3 - V_2}{R3}.$$

(2.21)

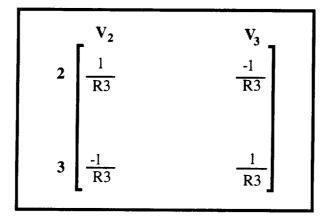

Equations (2.20) and (2.21) are the only two expressions including R3. Equation (2.20) is part of the KCL at node 2, and (2.21) part of the KCL at node 3. Therefore, R3 affects the KCL equations at nodes 2 and 3 only, as shown by the pattern or stamp in Figure 2.5.

Figure 2.5. Stamp for resistor R3 from Example Circuit 1.

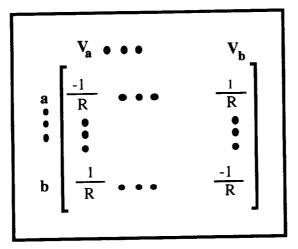

Examining the circuit matrix (Figure 2.4) will show that the rest of row 2 can be constructed by superposing the stamps for the remaining resistors attached to node 2. The stamp for R1 looks like Figure 2.5 except the rows involved are 2 and 1, the columns are  $V_2$  and  $V_1$  and the resistor value is R2. Similarly, resistor R4 has a stamp of the form shown in Figure 2.5 except that all of the 3's are replaced by 4's. The stamps for R1 and R4 also affect rows 1 and 4. A general stamp for a resistor of value R is shown in Figure 2.6. In the figure, a and b refer to arbitrary rows which are not necessarily adjacent.

#### 2.3.2. Independent voltage source stamp

The stamp for an independent voltage source is derived in this section. The derived stamp is valid for dc, ac, and transient analyses. When writing KCL, the variables are usually the voltages at the nodes used in expressions for the currents at the node of interest, and equations are written at every node. This approach produces n equations, one at each of the n nodes, with n unknowns, the n unknown node voltages. In the case of voltage

sources, the current through the voltage source is not expressible in terms of node voltages and instead must be declared as a variable.

Figure 2.6. General stamp for a linear resistor of value R connected between two nodes a and b.

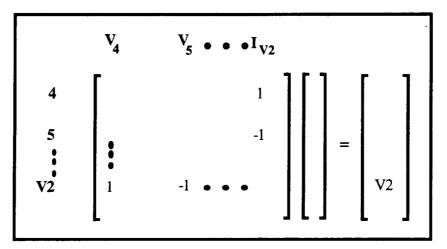

Examine the voltage source V2 connected between nodes 4 and 5 of the circuit in Figure 2.3. When writing KCL at node 4, the current through the voltage source is written as  $I_{v2}$ . This is seen as +1 at matrix position (4,  $I_{v2}$ ) in Figure 2.7. When considered from node 5, the current is  $-I_{v2}$ . This produces the -1 at matrix position (5,  $I_{v2}$ ). The current through the voltage source contributes an extra variable to the matrix. The system of equations becomes n equations in n+1 unknowns. Equation n+1 is obtained by using the value of the voltage source. The equation is

$$V_4 - V_5 = V2.$$

(2.22)

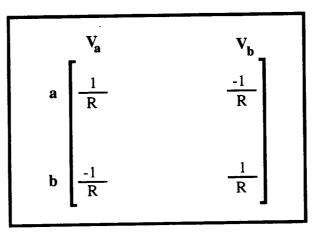

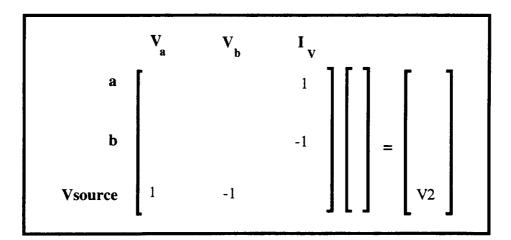

Equation (2.22) appears as a +1 and a -1 at matrix positions (V2, V4) and (V2, V5), respectively, and a V2 at matrix position (V2, sources). Therefore, the pattern that voltage source V2 contributes is shown in Figure 2.7. The general stamp of an independent voltage source is shown in Figure 2.8. where V corresponds to the value of the voltage source which is connected between nodes a and b, with a as the positive node.

The circuit matrix of Figure 2.4 can be constructed by combining the stamps of the various resistors and voltage sources involved. Whenever an element of a stamp occupies the same position in the matrix as an element of another stamp, they are combined by

addition. Notice that for R2 and V1 the section of the stamp relating to node 0 (row 0 and column  $V_0$ ) is not present in the matrix, because R2 and V1 are connections to ground. The voltage at node 0 is already known to be zero and the rows and columns associated with node 0 can be eliminated.

Figure 2.7. Specific voltage source stamp for V2 of Example Circuit 1.

Figure 2.8. General stamp for a voltage source connected between nodes a and b, with a as the positive node.

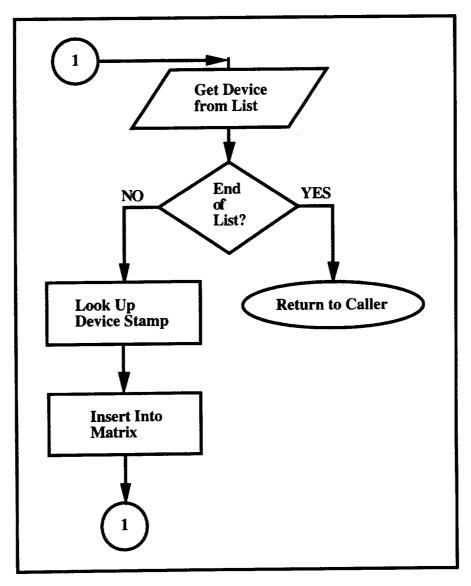

The basic algorithm employing stamps for filling a matrix is shown as a flow chart in Figure 2.9. A problem may seem to exist with respect to the stamp approach since the matrix size is not known a-priori. The capability in particular programming languages to dynamically allocate memory allows the matrix to start out with a size of zero and grow dynamically in cell size or have existing entries appended with the insertion of each device stamp. Before entering the stamp of a device into the circuit matrix the row and column entries that the device will affect are checked for previous allocation. If space in the matrix has already been allocated for an entry, then the stamp information is added to the entry. If space has not been allocated in the matrix, then space is allocated for the entry and the stamp information is used to fill the entry.

Figure 2.9. Flow chart for device by device matrix fill algorithm.

# 2.4. Matrix Solution Techniques and Sparsity

Many techniques, both direct and iterative, are available for solving matrices. Whether a specific circuit matrix is solved just once, the direct technique, or is solved multiple times until the solution is deemed valid, the iterative technique, depends on the type of analysis desired. Direct techniques are used for operating point analysis or dc analysis. Iterative techniques are used for nonlinear device analysis. In transient analysis (see Section 2.6) the matrix is solved either directly or iteratively at each time step, depending on the type of devices in the circuit.

The direct matrix solving technique of Gaussian elimination, or a permutation of Gaussian elimination, such as LU factorization, is often used [14]. The details and complexity of matrix solving routines vary with the structure of the matrix. The characteristic of matrix sparsity is discussed in the remainder of this section.

The majority of the entries in the matrix of Figure 2.4 are zeroes. The characteristic of having many empty or zero entries in a matrix is termed sparsity. Special matrix solving techniques exist to take advantage of and retain sparsity of a matrix during the solution process [15].

Rows of a circuit matrix represent nodes at which KCL or device equations are being written, and each of the columns represent either a node voltage or a branch current involved. The number of entries per row related to a node is proportional to the number of branches emanating from the node. For circuits with many elements, where the nodes are not highly interconnected and the device equations involve few variables, the matrix representing the circuit will be sparse. Many simulators, including SPICE3E2, have a sparse matrix package which exploits and perpetuates the sparsity of the matrix.

In contrast to dense matrices, ordinarily stored in two-dimensional arrays, linked list structures are employed for sparse matrices. There is no need to waste memory on storing an entry of zero. When referencing the structure, if a list element corresponding to a particular matrix location does not exist, then the matrix entry is assumed to be zero.

# 2.5. Output of Results

Once the matrix has been solved, the results are available in output data structures. Routines which interface from the simulator to the output package access the data structure and present the simulation results to the output package structures.

# 2.6. Notes on Transient and Nonlinear Analysis

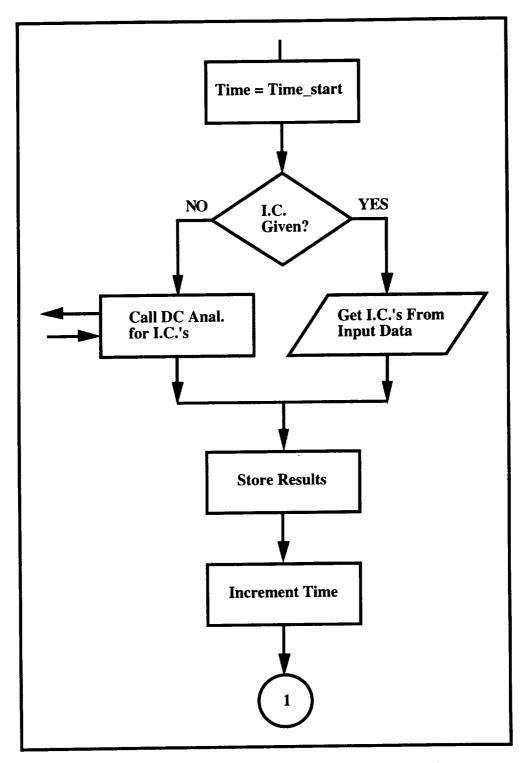

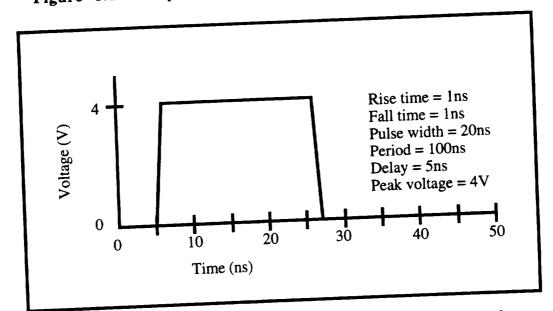

The details of the third step of Figure 2.1, Solve Matrix, vary with different types of analysis. The general flow chart for a transient analysis is shown in Figures 2.10 and 2.11. At the beginning of transient analysis, the current through inductors and transmission lines, and the voltage across capacitors and p/n junctions must be known. If this initial condition or operating point data is not specified by the user, a dc analysis is performed to obtain the state of the circuit before transient analysis proceeds.

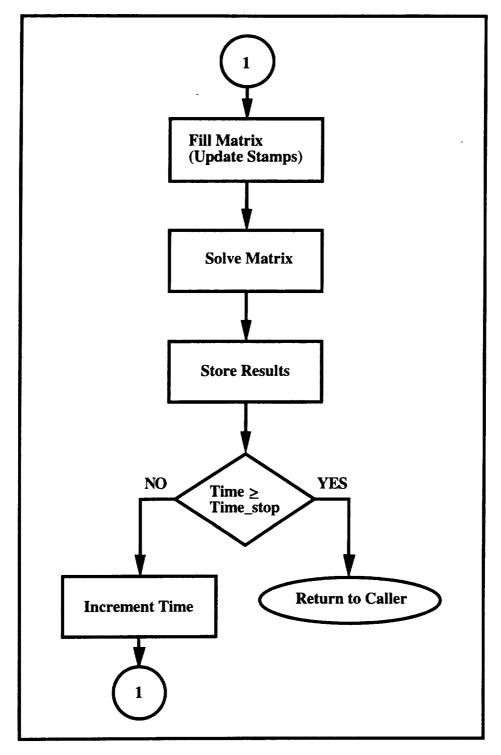

Transient analysis starts at an initial time  $Time\_start$  and finishes at a time  $Time\_stop$ . In the figures, Time is the variable keeping track of the simulation time. The matrix is set up and solved at a finite number of time points in between the start and stop times, therefore, discretizing the continuum between Time\_start and Time\_stop. Consecutive time points at which the solution is calculated are separated by fixed or variable time steps. In the fixed scheme the time step is set a-priori and does not change. In the variable method the appropriate step is calculated at the present time point  $t_i$  to reach the next time point  $t_{i+1}$ . The significance of time step size will be discussed later in this section.

Once Time increases beyond Time\_stop the simulation ends. At times less than Time\_stop, Increment Time appropriately updates the simulation time by either the fixed or variable methods, and control is passed to Fill Matrix. The process is repeated until completion. The first step of Figure 2.11 is Fill Matrix, with the subheading Update Stamps. The stamps presented in Section 2.3 were uncomplicated, depending only on known device parameters which remained constant. In contrast, many devices have stamps which depend on parameters which change from time point to time point and, hence, rec-

Figure 2.10. Flow chart for transient analysis, part I.

Figure 2.11. Flow chart for transient analysis, part II.

uire updating before each matrix fill. For example, a linear capacitor has a transient analysis stamp which requires information about the voltage across it at time  $t_{i-1}$  for a matrix fill at time  $t_i$ . At the first iteration of Figure 2.11, the stamp is constructed for the capacitor based on the initial condition values. Once the matrix is solved, the voltages at the nodes of the capacitor and, therefore, the voltage across the capacitor are available and will be used in computing the capacitor stamp at the next time step.

The transient analysis formulae for devices are a result of the discretization of the differential equation representing the voltage/current relationship for the device. The resulting formulae are referred to as linear multistep formulae [17], which have stability requirements, dictating the time step size. The requirements change with the activity of the circuit. Larger time steps can be taken when the voltage or current are not changing rapidly in the circuit. Smaller steps are needed when the circuit is rapidly changing. Variable time steps have the advantage of reducing the number of matrix evaluations by utilizing larger time steps where possible. Variable time steps, however, are more difficult to program and entail extra overhead in the main code. In contrast, fixed time steps require much less overhead and are significantly easier to program, but lead to unnecessary extra matrix evaluations. See [6], [7], and [14] - [17] for details.

This section has centered on linear devices which require the matrix to be solved once at a particular time point. If any of the devices are nonlinear the Solve Matrix step of Figure 2.11 is not a simple matrix evaluation, but multiple evaluations. See [15] for further discussion.

### 2.7. Summary

A circuit simulator has four basic operations: obtain the circuit description, construct the circuit matrix, solve the matrix, and report the results. Operations two and three may be executed multiple times depending on the type of analysis. Once the circuit description is defined by the user and stored in linked list data structures by the simulator, the matrix is constructed. A popular method of matrix construction in circuit simulators is the stamp method, in which the matrix is filled device by device based on the contributions each device makes to a circuit matrix. The stamp for a resistor connected between two nodes a and b is shown in Figure 2.6. Once the matrix is filled, LU factorization can be used to solve the matrix. Transient analysis occurs over an interval. The matrix is constructed and solved at a finite number of time points in the interval. Some stamps may depend on values from a previous time point. This requires updating stamps before filling a matrix. More information on computer analysis of circuits is found in [14] - [17].

### 3. DERIVATION OF TRANSMISSION LINE STAMPS

Two stamps used in transient analysis of a lossless transmission line are examined. Section 3.1 supplies the background on the number of device nodes vs. stamp size to set the foundation for comparing the two stamps. Sections 3.2 and 3.3 describe the stamps, and Section 3.4 compares them.

### 3.1. Number of Device Nodes and Stamp Size

In this section the relationship between device nodes and stamp size is examined. Every circuit element has an associated model. Complex devices have models comprised of the models of simpler devices. All models have external nodes, the nodes the device shares with the rest of the circuit, and possible internal nodes and branch currents which only the device uses (if there are no other circuit elements being controlled by the internal values). Internal nodes and branch currents are a result of the joining of simple models to construct a more complex model. There is an important difference with respect to stamp size between external nodes and internal nodes and internal branch currents.

Stamp size depends on both external and internal nodes and internal currents. Larger stamps result in larger circuit matrices, which take longer to solve, and more memory to store. It is desirable to make device stamps as small as possible to obtain smaller circuit matrices resulting in shorter solution times and better memory utilization.

Stamps can be made smaller by eliminating rows and columns. Row and column elimination translates into eliminating variables (nodes or currents). It is impossible to eliminate the rows and columns related to the external nodes since this would disconnect a device from the circuit. The only choice is eliminating internal nodes or currents. This can sometimes be done by rewriting a device model, and will be demonstrated in Section 3.3.

#### 3.1.1. One-port devices

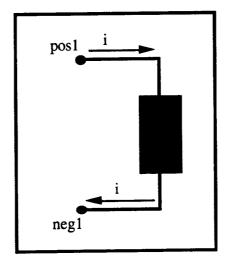

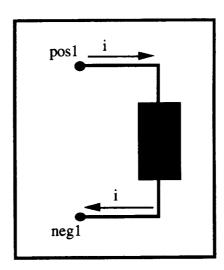

A one-port device (see Figure 3.1) has two nodes that connect it with the outside circuit. A stamp for such a device will contain at least a row and column for each node. Therefore, for a one-port device the stamp is at least  $2x^2$ . This is the case for the resistor (see Figure 2.6). The voltage source (see Figure 2.8) required an extra row and column making the matrix  $3x^3$ .

Figure 3.1. One-port device.

If there are no controlled devices depending on the current through the voltage source, the third row (Vsource) and column  $I_V$  in Figure 2.8 will not be used in the overall circuit matrix by other devices. The third row and column are necessary to handle the current through the voltage source only. The first two rows and columns in Figure 2.8, which relate to the external nodes of the device, are used in the overall circuit matrix by the other devices. The voltage source will share the external nodes as points of connection in the circuit (see Figure 2.4). Therefore, a voltage source will share two rows and columns with other devices, and will add an extra row and column to the circuit matrix for exclusive use.

In the remainder of this thesis the rows and columns in a stamp representing the internal nodes and internal currents of a device will be referred to as extra or added on, because the rows and columns are only used by the device to which they are internal, and

increase the stamp size for the device beyond the size indicated by the external nodes of the device.

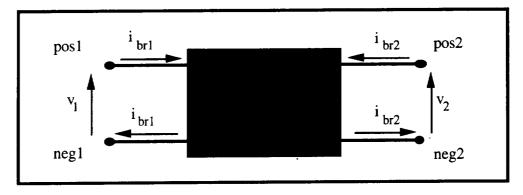

#### 3.1.2. Two-port stamps

A diagram representing a two-port is shown in Figure 3.2. A two-port has four external nodes, and the stamp will be at least 4x4.

Depending on the specific two-port device there may be internal nodes or branch currents that will increase the stamp size beyond 4x4. Assuming no controlled elements these internal nodes and currents will not be used by any other device of the overall circuit.

Figure 3.2. Two-port device.

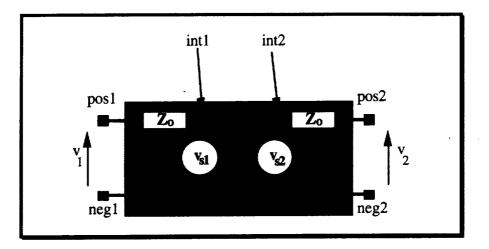

# 3.2. Voltage Source/Impedance Stamp for the Lossless Transmission Line

A valid model for a lossless transmission line is shown in Figure 3.3 and Equations (3.1) and (3.2). In the equations  $\tau$  is the transmission line delay. This is the time for a signal to travel once from one end of the line to the other. The voltage source/impedance model is used in the lossless transmission line module that comes with SPICE3E2. The nodes in the figure have been named using the node naming convention employed in SPICE3E2. All subsequent circuit diagrams and stamps presented will utilize this naming convention [5].

$$v_{s1}(t) = 2v_2(t-\tau) - v_{s2}(t-\tau)$$

(3.1)

$$v_{s2}(t) = 2v_1(t-\tau) - v_{s1}(t-\tau)$$

(3.2)

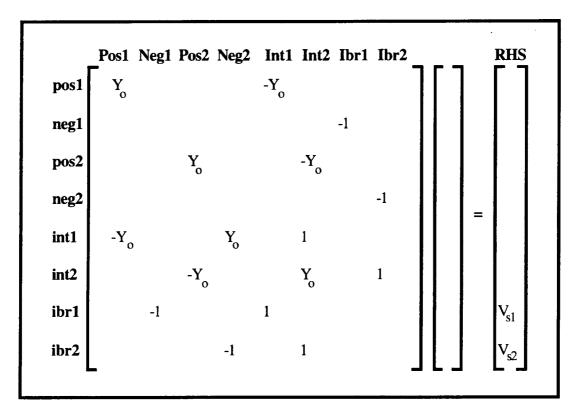

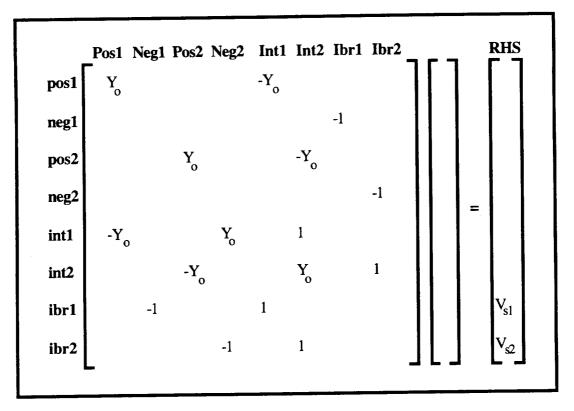

In Chapter 2 it was pointed out that the matrix in Figure 2.4 can be constructed by superposing stamps for the resistors and the voltage sources. Similarly, impedance or admittance stamps and voltage source stamps can be used to construct the stamp of the model shown in Figure 3.3. The stamp of the Figure 3.3 schematic is shown in Figure 3.4.

Note that neg1 and neg2 should not be assumed to be grounded. Also, Equations (3.1) and (3.2) have no bearing on the form of the stamp, only on the values of  $V_{s1}$  and  $V_{s2}$  which appear on the right-hand side of the equality. The independent voltage source equation is

$$\mathbf{v}_{\text{int1}} - \mathbf{v}_{\text{neg1}} = \mathbf{v}_{\text{s1}} \tag{3.3}$$

This is the same as Equation (2.22) with the nodes and source renamed. Equation (3.3) is useful when deriving the form of the stamp. Equations (3.1) and (3.2) are useful when filling the stamp with numerical values.

The row and column naming in Figure 3.4 are consistent with SPICE3E2; therefore, the row label ibr1 still marks a voltage source equation of the form of Equation

(3.3). This stamp was formed using  $Y_0$ ; the admittance is used as opposed to  $1/Z_0$  as was done in Chapter 2.  $Y_0$  is used since in the SPICE3E2 code that will be discussed in Chapter 4, and Chapters 6 through 9, the stamps are filled using admittance values as opposed to the reciprocal of the impedance.

Figure 3.4. Voltage source/impedance stamp for a lossless transmission line.

The voltage source/impedance stamp is an 8x8 matrix with 18 nonzero entries. The size and number of nonzero entries are due to the voltage source connected in series with the impedance. The currents through the voltage source contribute the rows and columns Ibr1 and Ibr2. The series connection contributes the internal nodes Int1 and Int2.

Both the internal nodes and the rows and columns associated with ibr can be eliminated by converting to a current source in parallel with an impedance which is commonly called the current source/admittance model. This model is the subject of the next section.

### 3.3. Current Source/Admittance Stamp for a Transmission Line

Before the stamp for the current source/admittance model is discussed in Section 3.3.2, the stamp for a current source is derived in Section 3.3.1.

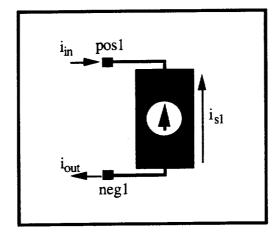

#### 3.3.1. Independent current source stamp

In Figure 3.5,  $i_{in}$  and  $i_{out}$  represent the current from outside the source coming into the top node and going out of the bottom node. The currents  $i_{in}$  and  $i_{out}$  are due to the rest of the circuit, and are not being contributed by the current source  $i_{s1}$ . The current  $i_{s1}$ feeding into the top node and out of the bottom node is the contribution from the current source. The position of  $i_{s1}$  in the nodal equations for the top and bottom nodes determines the stamp for the independent current source.

Figure 3.5. Current source diagram used in stamp derivation.

KCL at the top node yields

$$-i_{in} - i_{s1} = 0. (3.4)$$

Transferring is1, since it is known, to the right-hand side yields

$$-i_{in} = i_{s1}.$$

(3.5)

Similarly, KCL at the bottom node results in

$$i_{in} + i_{s1} = 0$$

(3.6)

$i_{in} = -i_{s1}$ .

Figure 3.6. (a) Stamp for an independent current source. (b) Conventional representation of independent current source stamp.

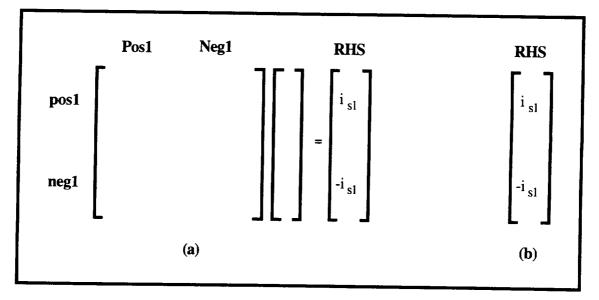

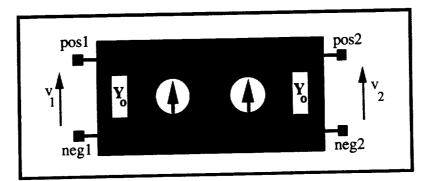

#### Lossless transmission line stamp 3.3.2.

The current source/admittance model for a lossless transmission line is given in Figure 3.7 and Equations (3.8) through (3.9), where  $Y_0$  is the characteristic admittance,  $\tau$

(3.7)

or

а

is the delay of the line, and  $i_{s1}$  and  $i_{s2}$  are the currents from the source on the left and right respectively. These can be derived from the voltage source/impedance model by finding the Norton equivalent circuit.

Figure 3.7. Current source/admittance model.

$$i_{s1}(t) = 2Y_0 v_2(t-\tau) - i_{s2}(t-\tau)$$

(3.8)

$$i_{s2}(t) = 2Y_0 v_1(t-\tau) - i_{s1}(t-\tau)$$

(3.9)

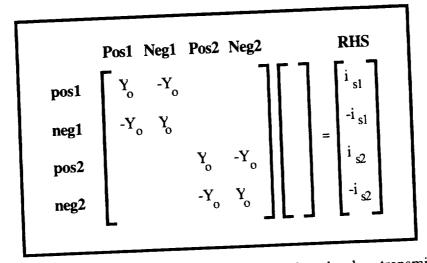

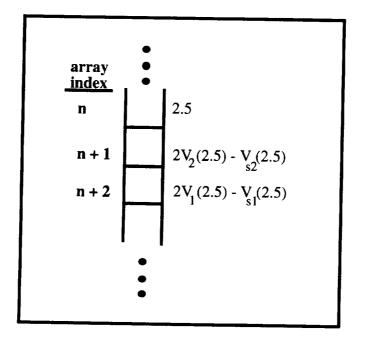

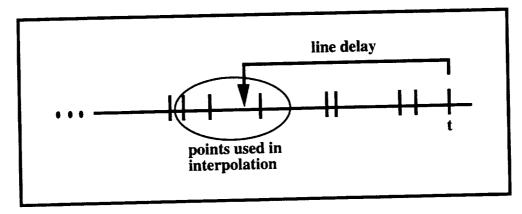

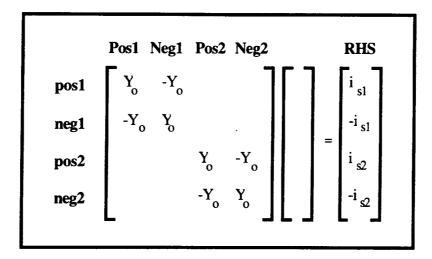

The stamp for the model in Figure 3.7 is shown in Figure 3.8. This stamp was derived by using the current source stamp and the impedance stamp. Notice that only rows and columns associated with the external nodes remain. The current source/admittance stamp requires a  $Y_0$ ,  $i_{s1}$ , and  $i_{s2}$ .  $Y_0$  is the characteristic admittance of the line and remains constant through the transient analysis. The two currents  $i_{s1}$  and  $i_{s2}$  are computed as given in Equations (3.8) and (3.9). The equations indicate that the currents  $i_{s1}$  and  $i_{s2}$  require port voltage and source current from one line delay prior to the present time. The details of storing values at the present time to be referred to one line delay later are found in Chapter 6.

Figure 3.8. Current source/admittance stamp for a lossless transmission line.

# 3.3.3. Transient analysis of a lossy transmission line

The lossy transmission line model is very similar to the lossless model. The following discussion will mention only the current source/admittance stamp, but also applies in analogous fashion to the voltage source/impedance model. The stamp for the lossy model is as shown in Figure 3.8, but the expressions for  $i_{s1}$  and  $i_{s2}$  are not as given in Equations (3.8) and (3.9).

In this work, once the framework for a lossy line was established by implementing a current source/admittance model for the lossless line, the values for  $i_{s1}$ , and  $i_{s2}$  were supplied by a subroutine developed by D. Kuznetsov. See Kuznetsov and Schutt-Aine for details on models of lossy and lossless single- and multi-conductor lines [4].

### 3.4. Stamp Comparison

The voltage source/impedance stamp is shown in Figure 3.4 and the current source is shown in Figure 3.8. Notice that the current source/admittance stamp is 4x4, four times smaller than the voltage source/impedance stamp. The overall circuit matrix will be smaller when using the current source/admittance stamp and, therefore, will take less time to solve.

In addition to matrix size, the current source/admittance matrix has only 12 nonzero elements as opposed to the 18 of the voltage source/impedance stamp. With fewer nonzero elements, the current source/admittance stamp will have fewer memory references when being loaded into the overall circuit matrix and, therefore, will be loaded faster.

·· \_\_\_

### 3.5. Summary

A device stamp will be at least  $n \ge n$ , not including the right-hand side vector, where n is the number of nodes. Extra nodes can sometimes be eliminated by rewriting the equations representing the device. The voltage source/impedance stamp for transient analysis of the transmission line is larger and has more nonzero entries than for the current source/admittance stamp. Transient analysis for a lossy transmission line and lossless line differ only in the expressions for the independent sources.

### 4. OVERVIEW OF ASPECTS OF SPICE3E2 RELEVANT TO DEVICE INSTALLATION

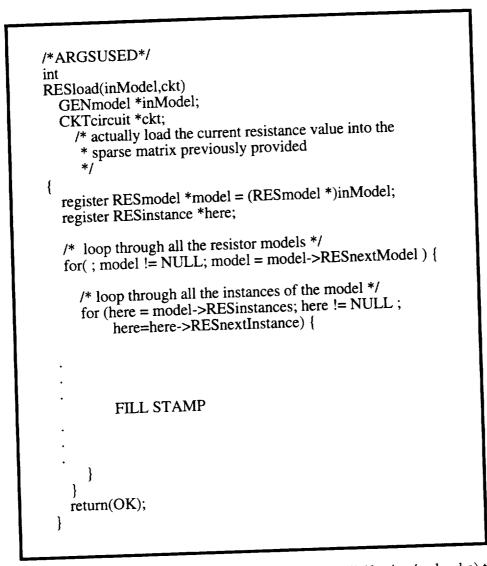

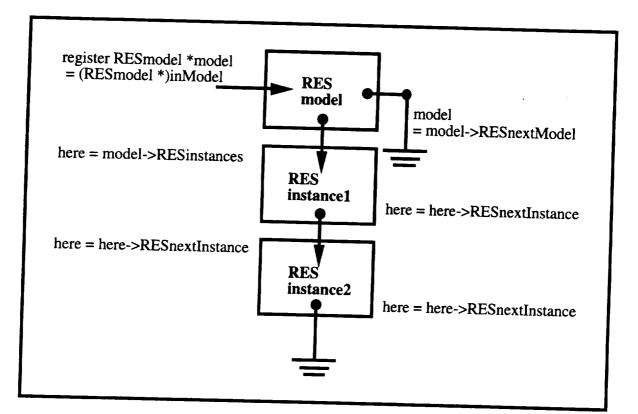

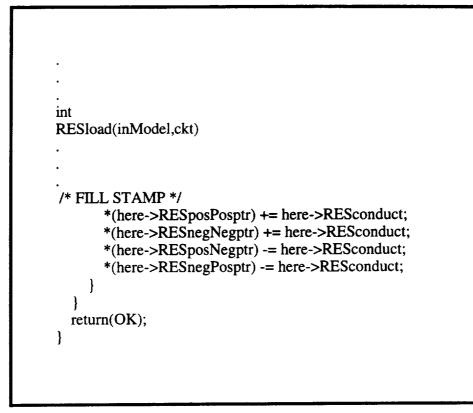

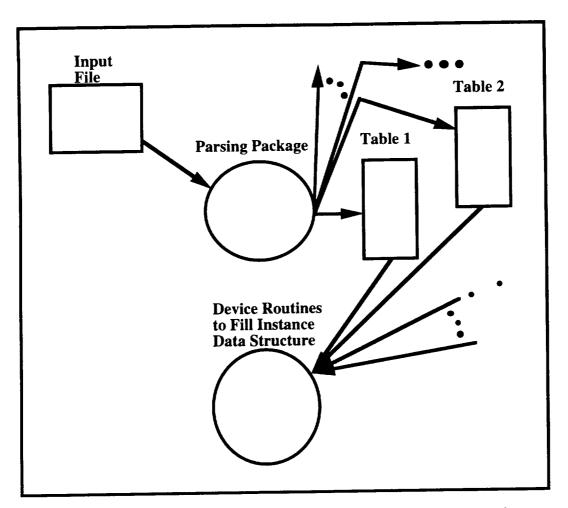

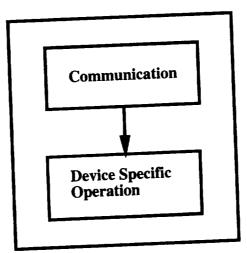

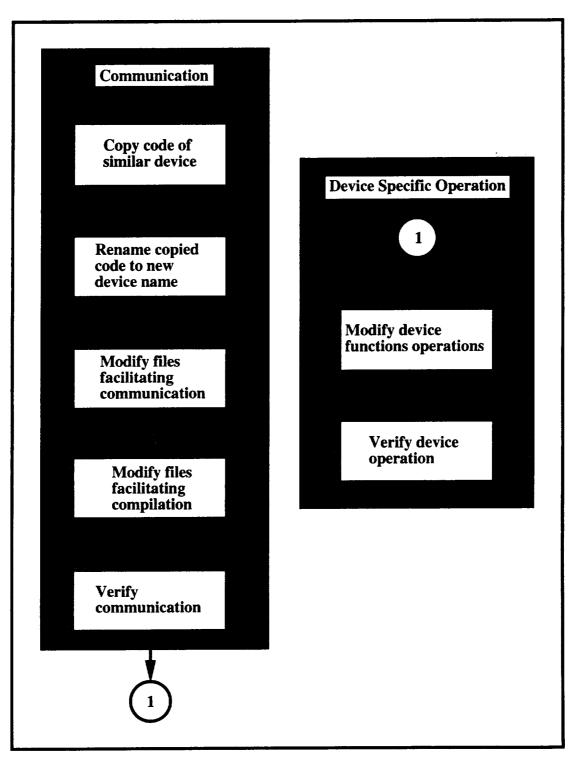

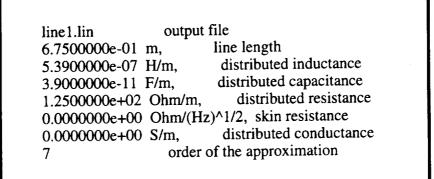

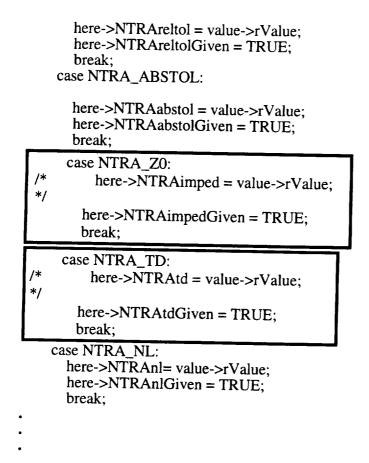

The purpose of this chapter is to supply the necessary background information on SPICE3E2 requires in device installation. All of the details of SPICE3E2 code operation are not presented. Complementary information is found in [6] and [7].