# Phase Aligner for the Electronically Scanned Thinned Array Radiometer (ESTAR) Instrument

William A. Chren, Jr., and Brian G. Zomberg Goddard Space Flight Center Greenbelt, Maryland

Grand Valley State University Grand Rapids, Michigan

(NASA-TM-4518) PHASE ALIGNER FOR THE ELECTRONICALLY SCANNED THINNED ARRAY RADIOMETER (ESTAR) INSTRUMENT (NASA) 16 p

N94-13878

Unclas

H1/33 0187788

National Aeronautics and Space Administration

Goddard Space Flight Center Greenbelt, Maryland 20771

| 1                                     |  | Ę  |

|---------------------------------------|--|----|

| -                                     |  |    |

|                                       |  | ž· |

|                                       |  | •  |

|                                       |  |    |

|                                       |  |    |

|                                       |  |    |

|                                       |  |    |

|                                       |  |    |

|                                       |  |    |

|                                       |  |    |

|                                       |  |    |

|                                       |  |    |

| 1                                     |  | į. |

| -                                     |  | ·  |

|                                       |  |    |

| · ·                                   |  | •  |

| · · · · · · · · · · · · · · · · · · · |  | ·  |

| · ·                                   |  | •  |

|                                       |  | •  |

|                                       |  | ₹. |

|                                       |  | •  |

|                                       |  | ₹. |

|                                       |  | ₹. |

|                                       |  | ₹. |

## CONTENTS

| 1. | Introduction                                | 2      |

|----|---------------------------------------------|--------|

|    |                                             | _      |

| 2. | ESTAR Background                            | 2      |

|    |                                             | _      |

|    | 2.1 Major Digital Data Subsystem Components | ن<br>د |

|    | 2.2 Phase Aligner Requirements              | 4      |

| 3. | Phase Aligner Design                        | 6      |

|    |                                             |        |

|    | 3.1 General Description                     | 6      |

|    | 3.2 Circuit Operation                       | 9      |

| 4. | Specifications                              | 10     |

|    |                                             |        |

|    | 4.1 Electrical Specifications               | 11     |

| 5  | Signal Descriptions                         | 1.4    |

| J. | Olginal Descriptions                        | 17     |

|    | 5.1 Control Inputs                          | 14     |

|    | 5.2 Control Outputs                         | 14     |

|    | 5.3 Data Inputs                             |        |

|    | 5.4 Data Outputs                            | 15     |

| 6. | Package Type                                | 15     |

| -  | <del></del>                                 |        |

| 7. | References                                  | 15     |

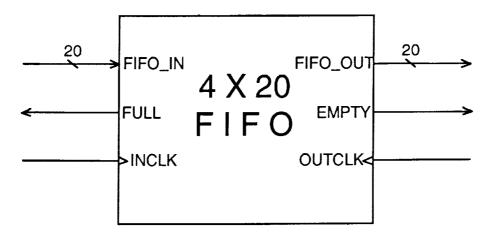

Abstract: A prototype Phase Aligner (PA) for the ESTAR (Electronically Scanned Thinned Array Radiometer) instrument has been designed and tested. Implemented in a single Xilinx XC3042PC84-125 Field Programmable Gate Array (FPGA), it is a dual-port register file which allows independent storage and phase coherent retrieval of antenna array data by the Central Processing Unit (CPU). It has dimensions of 4 X 20 bits and can be used at clock frequencies as high as 25 MHz.

#### 1. Introduction

ESTAR (Electronically Scanned Thinned Array Radiometer) is a passive synthetic-aperture radiometer designed to sense soil moisture and ocean salinity in L-band. It is being developed as an earth probe mission intended for launch in the late 1990's as part of the Earth Observing System (EOS).

A recent feasibility study [1] of the ESTAR concept recommended that a two-dimensional prototype be built in order to study further the design issues involved. Grand Valley State University Professor William A. Chren, Jr. was awarded NASA JOVE Grant NAG 8-226 to design and build four subsystems that will be part of the digital data subsystem (DDS) in this prototype. The third of these four subsystems, the Phase Aligner (PA), has been completed and is the subject of this memorandum. Two previous memoranda [2,3] presented the specifications of the first two of the subsystems, called the Output Data Formatter (ODF) and Walsh Function Generator (WFG).

Section 2 is a presentation of background information about the ESTAR. Subsequent sections present the details of the PA.

### 2. ESTAR Background

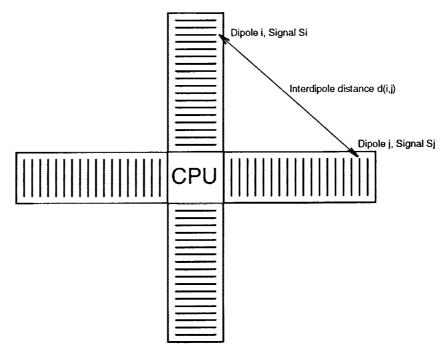

The synthetic aperture sensing technique employed by ESTAR is a method whereby the high spatial resolution and sensitivity of a large dish antenna can be duplicated with a small, lightweight cross-shaped array of dipole antennas (see Figure 1).

Figure 1: Dipole Antenna Locations on ESTAR Instrument

Such a duplication yields size and weight advantages which make it attractive for use on earth-sensing spacecraft. It is made possible by the calculation, for all pairs (i,j), of the pairwise complex correlation between dipole signals S<sub>i</sub> and S<sub>i</sub> using the formula

$$\langle S_i, S_j \rangle = \frac{1}{T} \int_0^T S_i(t) S_j^*(t) dt,$$

(1)

in which "\*" denotes the complex conjugate and T is a suitably chosen integration period. It can be shown that each of these correlations is a sample, in frequency space, of the spatial Fourier Transform of the brightness temperature distribution over the field-of-view (FOV) of the antenna. Consequently, the visibility function in the FOV can be computed by inverting the sampled transform. Furthermore, the location of the sample in frequency space is determined only by the inter-dipole distance and not by the absolute locations of the dipoles themselves [4].

The data processing system on ESTAR will compute, in real time, these correlations for each dipole pair (i,j). Sensitivity and resolution specifications dictate that 145 dipoles (73 on each leg of the cross) must be used for a full ESTAR mission, or 73 (37 on each leg) for a reduced mission [5]. The correlations will be done digitally at a centrally located processing unit called the CPU, as shown in the figure. The results will then be sent to earth where the inverse transform will be computed. Necessary dipole signal preprocessing, including downmixing and A/D conversion, will be done at each dipole by circuitry contained in a "Front End Module" (FEM).

## 2.1 Major Digital Data Subsystem Components

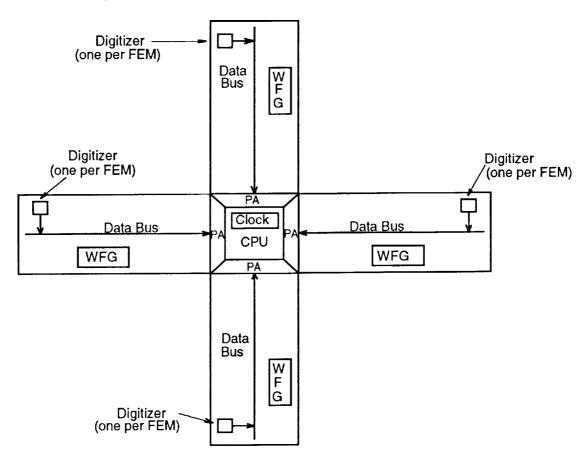

At the functional level, the digital data subsystem (DDS) consists of six major components [6]. The first of these, the Digitizer, must convert the FEM data to digital form before sending it to the CPU. This will be done by an A/D converter in each FEM. The second, the Data Bus, must transport the digitized data from the FEMs to the CPU. The third, the CPU, must compute the correlations for each pair of FEMs. It is also responsible for overall control of the DDS. Furthermore, it must interface with the Small Explorer Data System (SEDS), which is a software and hardware "operating system" on the space vehicle. Among other tasks, SEDS performs overhead functions such as data error immune encoding and transmission to earth, earth command processing and system test. The CPU must pass the correlation products to SEDS for transmission to earth. The fourth component, the System Clock, is necessary to ensure that dipole data samples are generated synchronously by all FEMs. In effect, the Clock signals the FEMs to generate data samples at the same instant of time. The fifth part, the Phase-Aligner (PA), removes the phase differences between FEM samples when they arrive at the CPU. These differences are caused by unequal data propagation times to the CPU from distant and nearby FEMs. The PA must hold the earlyarriving data until the late-arriving data is available. Only when all FEM data for a particular sample time have arrived at the CPU will the PA signal the CPU that the data is ready for correlation. The sixth component, the Walsh Function Generator (WFG), generates a unique

Walsh function signal for each FEM. This signal is used to cancel low frequency noise generated by the analog circuitry in the FEM.

These six components fit together as shown in Figure 2. Note that the Phase Aligner completely surrounds the CPU so as to effect phase adjustment for all four legs of the array. As will soon be discussed, the CPU must generate a single data retrieval clock signal which will access simultaneously the phase-aligned data from all four sections of the PA.

Figure 2: Six Major Components of the DDS

į.

# 2.2 Phase Aligner Requirements

As mentioned above, the Phase Aligner must store early FEM data until late data can arrive. Typically, the device used for such applications is a synchronous First-In First-Out (FIFO) stack. It is essentially a dual port static RAM with two separate and independent addressing and data ports [7]. The output data is read in the order it was stored. It allows an "upstream" device to store data independently of a reading "downstream" device. The stored data can be read at any time. As long as the average input and output data rates are equal the FIFO will not overflow. Extra circuitry is included on chip to monitor capacity and set external "empty" and "full" flags.

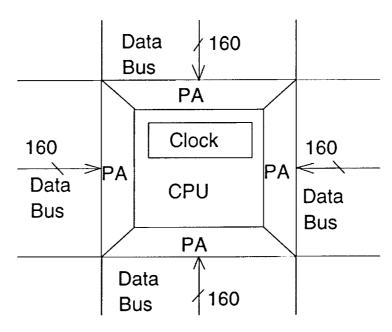

Each of the four parts (one for each leg of the cross in Figure 2) of the PA must be wide enough to accommodate the Data Bus outputs. The Data Bus will be implemented using

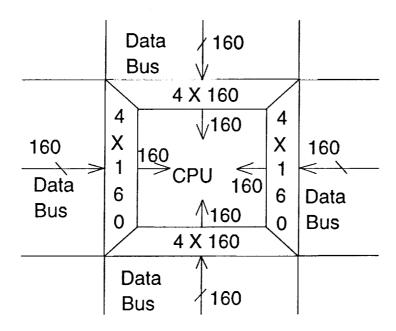

differential coaxial cable and some number of 1.2 Gbaud transmitter/receiver chips called *G-Taxis*. These chips, from Vitesse Semiconductor, implement all the communication link overhead such as error detection/correction, data packing/unpacking and formatting. Each G-Taxi transmitter has 40 parallel data input and output pins. Every FEM produces digitized quadrature data encoded in two bits/channel, and therefore one G-Taxi chipset is needed for every ten FEMs. In the full (reduced) ESTAR deployment, we will therefore need 4 (2) G-Taxis per leg, and consequently each of the four legs of the Phase Aligner must be 160 (80) inputs wide. Figure 3 shows the number of inputs to the Phase Aligner for a full ESTAR deployment.

Figure 3: Phase Aligner Inputs for a Full ESTAR Deployment

The depth of the PA FIFO must be computed from the worst case travel time for data to traverse one leg of the cross. The legs are 5m (2.5m) long in the full (reduced) versions. Assuming a worst case propagation velocity of 5 nsec/meter for the FEM data, we conclude that the worst case transit time for the data is 25 (12.5) nsec. The prototype is to be operated at a maximum frequency of 25MHz, and therefore the transit time is equal to a maximum of .63 (.32) clock periods. Consequently, we require a storage depth of at least 1 in both full and reduced versions of the PA. In order to allow for design expansion, the Phase Aligner FIFO was implemented with a depth of 4 so that higher clock speed versions of the ESTAR can be built. With a depth of 4 the maximum clock frequency that can be used in the full ESTAR deployment is

$$f_{\text{max}} = \frac{4}{25} = 160 \text{ MHz},$$

although the PA prototype has been designed for a maximum frequency of 25 MHz. Figure 4 summarizes the input/output and depth requirements of the Phase Aligner. Note that

Figure 4: Phase Aligner Inputs, Outputs and Depth for a Full ESTAR Deployment a partial ESTAR deployment would halve the number of input and output lines.

## 3. Phase Aligner Design

## 3.1 General Description

The Phase Aligner will be built using 32 of the 4 X 20 FIFO prototypes depicted in Figure 5. As can be seen in the figure, the prototype has separate, independent input and output

Figure 5: Phase Aligner FIFO Input/Output Configuration

leading edge clocking which will be controlled by the Data Bus and CPU respectively. The positive logic FULL and EMPTY outputs indicate to the Data Bus and CPU controller,

respectively, that the appropriate condition has occurred. The Data Bus and Controller will be designed to cease further clocking under this condition, until it no longer exists. The 20 input and output lines are positive logic and are fully buffered.

Operation of the prototype is as follows. A positive-going transition on INCLK strobes the data on the FIFO\_IN lines into one of four internal 20-bit data registers. A positive-going transition on OUTCLK causes the data stored in one of the internal data registers to be placed on the output lines FIFO\_OUT. Which of these four internal 20-bit wide data registers receives the input data or is the source of the output data is determined by internal address registers whose operation will be discussed below. The FULL flag is asserted when four transitions on INCLK occur in a row, without an intervening transition on OUTCLK. This corresponds to the situation where all four internal data registers have been filled with input data. The EMPTY flag is asserted when four transitions on OUTCLK occur in a row, without an intervening transition on INCLK. This corresponds to the situation where all four internal data registers have had their data strobed onto the FIFO\_OUT lines.

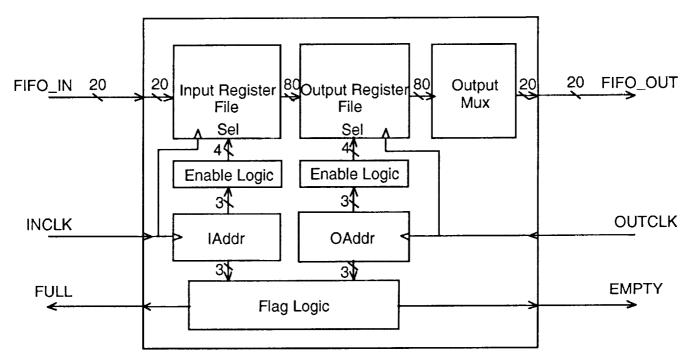

Figure 6 depicts the internal structure of the FIFO prototype. In the figure, the Input and

Figure 6: Phase Aligner Prototype Internal Architecture

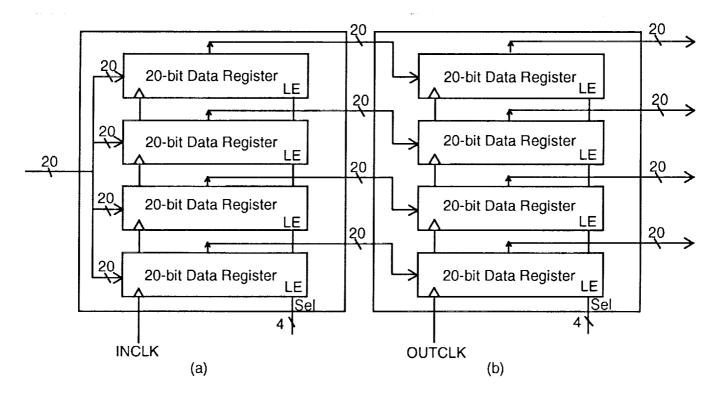

Output Register Files are identical banks of four 20-bit wide registers whose internal architecture is shown in Figure 7. From the latter figure, it can be seen that the Input

Figure 7: a) Input and b) Output Register File Internal Architecture

Register File, clocked by the INCLK, has all of its stored data (80 bits) fed to the Output Register File, which is clocked by the OUTCLK. The four Sel lines determine which of the four registers in each file responds to the clock signal. These lines are encoded using a "one hot" code so that only one register is enabled at any time. The outputs of the others are zero. The dual file structure was chosen because it allowed independent assertion of the clock inputs while not requiring any clock gating.

From Figure 6 it can also be seen that the 80-bit output from the Output Register File is input to the Output Mux, which selects the proper register data for the FIFO\_OUT data lines. Note that the proper output register is selected by the four Sel lines, which are encoded using the "one hot" code mentioned above. Note that no "select" inputs are needed for the Output Mux because only one of the Output Register File registers is enabled at any time. This fact allows the Output Mux to be implemented using an array of twenty 4-input OR gates.

The clocking signals INCLK and OUTCLK are also fed into identical 3-bit address registers IADDR and OADDR, which perform data storage management. At any time, IADDR contains the address of the next register in the Input Register File that is available for input data storage. Similarly, the OADDR register points to the next register in the Output Register File whose data is to be output. The counting sequence of these address registers is the 3-bit Gray code shown in Table 1. In the table, the present count value is denoted by the unstarred state

| Table 1: Counting Sequence for Address Registers IADDR and OADDR |

|------------------------------------------------------------------|

|------------------------------------------------------------------|

| Present State |       |       | ľ   | Next State      | е   |

|---------------|-------|-------|-----|-----------------|-----|

| $Q_0$         | $Q_1$ | $Q_2$ | Q*n | Q* <sub>1</sub> | Q*2 |

| 0             | 0     | 0     | 1   | 0               | 0   |

| 1             | 0     | 0     | 1   | 1               | 0   |

| 1             | 1     | 0     | 0   | 1               | 0   |

| 0             | 1     | 0     | 0   | 1               | 1   |

| 0             | 1     | 1     | 1   | 1               | 1   |

| 1             | 1     | 1     | 1   | 0               | 1   |

| 1             | 0     | 1     | 0   | 0               | 1   |

| 0             | 0     | 1     | 0   | 0               | 0   |

variables. The Gray code was used rather than the binary code because its sequence adjacency property minimizes the possibility of count glitches when the design is placed and routed on the FPGA.

The output of the IADDR and OADDR registers is fed to two different subsystems, as can be seen in Figure 6. One of these, the Enable Logic, is a decoder which converts the Gray code to a "one hot" code for use as the select inputs for the register files. The internal architectures of the Enable Logic blocks are identical, and are a straightforward decode function.

The other type of subsystem in Figure 6 is the Flag Logic, which produces the active high outputs FULL and EMPTY. The Flag Logic asserts the EMPTY flag when the addresses in the IADDR and OADDR are the same. This corresponds to the situation where there is no data stored in the FIFO. The Full flag is asserted when the addresses are separated by four transitions on INCLK (i.e., loosely speaking, when the "IADDR address exceeds the OADDR address by 4"). This corresponds to the state when four consecutive INCLK transitions have been received. It is the responsibility of the external circuitry to avoid asserting INCLK when FULL is asserted, and OUTCLK when EMPTY is asserted.

The architecture of the Flag Logic is a straightforward implementation of the equations

$$EMPTY = (Q_0^I \oplus Q_0^O)'(Q_1^I \oplus Q_1^O)'(Q_2^I \oplus Q_2^O)'$$

$$FULL = (Q_0^I \oplus Q_0^O)^{'} (Q_1^I \oplus Q_1^O) (Q_2^I \oplus Q_2^O)$$

where superscripts denote bit membership in either IADDR or OADDR, and 'denotes complementation. These expressions can be shown to be minimal implementations of the full and empty conditions discussed above.

## 3.2 Circuit Operation

Initialization or Reset

Input Storage/Output Retrieval

Positive-going transitions on INCLK strobe the 20-bit data words on the FIFO\_IN lines into successive internal 20-bit data registers. Positive-going transitions on OUTCLK cause the data stored to be placed on the output lines FIFO\_OUT in the same order in which it was strobed in. Which of the four internal 20-bit wide data registers receives the input data, or which becomes the source of the output data is determined by internal address registers IADDR and OADDR. The former always points to the next register available for strobing data into, and the latter always points to the next register whose data is to be strobed out. Active high output flag FULL is asserted when four transitions on INCLK occur in a row, without an intervening transition on OUTCLK. This corresponds to the situation where all four internal data registers have been filled with input data. Active high output flag EMPTY is asserted when four transitions on OUTCLK occur in a row, without an intervening transition on INCLK. This corresponds to the situation where all four internal data registers have had their data strobed onto the FIFO\_OUT lines. It is the responsibility of the external controlling circuitry to avoid asserting INCLK (OUTCLK) when the FULL (EMPTY) flag is asserted.

## 4. Specifications

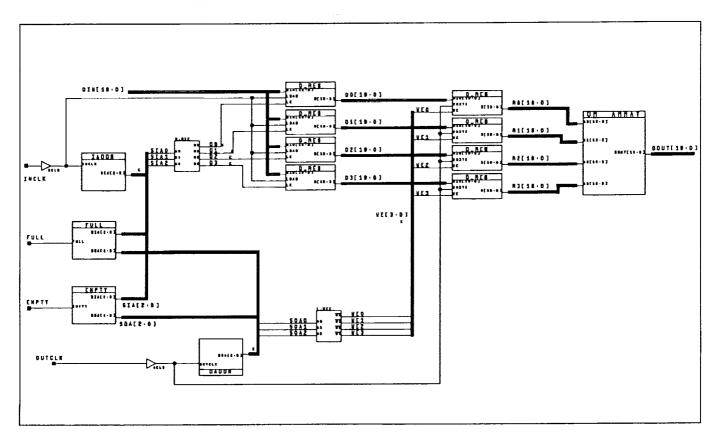

The schematic diagram of the Phase Aligner prototype FIFO is shown in Figure 8.

Figure 8: Phase Aligner FIFO Prototype Schematic Diagram

# 4.1 Electrical Specifications

# Maximum Absolute Ratings:

| Symbol           | Description                      | Value            | Units                 | Conditions |

|------------------|----------------------------------|------------------|-----------------------|------------|

| V <sub>cc</sub>  | Supply<br>Voltage                | 5 to +7.0        | V                     |            |

| V <sub>in</sub>  | Input Voltage                    | 5 to Vcc +       | V                     |            |

| V <sub>TS</sub>  | Tri-state<br>applied<br>voltage  | 5 to Vcc +<br>.5 | V                     |            |

| T <sub>STG</sub> | Storage<br>Temperature           | -65 to +150      | Degrees<br>Centigrade |            |

| T <sub>SOL</sub> | Max.<br>Soldering<br>Temperature | +260             | Degrees<br>Centigrade |            |

| TJ               | Junction<br>Temperature          | +125             | Degrees<br>Centigrade |            |

# Recommended Operating Conditions:

| Symbol          | Description                      | Min  | Max  | Units | Conditions |

|-----------------|----------------------------------|------|------|-------|------------|

| V <sub>cc</sub> | Supply<br>Voltage 0°C<br>to 70°C | 4.75 | 5.25 | V     |            |

| VIHT            | TTL High-<br>Level Input         | 2.0  | Vcc  | V     |            |

| VILT            | TTL Low-<br>Level Input          | 0    | 0.8  | V     |            |

| VIHC            | CMOS High-<br>Level Input        | 70%  | 100% | V     |            |

| VILC            | CMOS Low-<br>Level Input         | 0    | 20%  | V     |            |

| T <sub>IN</sub> | Input<br>Transition<br>Time      |      | 250  | ns    |            |

# DC Characteristics Over Operating Conditions:

| Symbol          | Description                     | Min  | Max_ | Units | Conditions                                        |

|-----------------|---------------------------------|------|------|-------|---------------------------------------------------|

| VOH             | High-Level<br>Output<br>Voltage | 3.86 |      | V     | I <sub>OH</sub> =<br>4.0mA<br>V <sub>CC</sub> min |

| VOL             | Low-Level<br>Output<br>Votage   |      | .32  | V     | I <sub>OL</sub> =4.0<br>mA<br>V <sub>CC</sub> max |

| VCCPD           | Power-Down<br>Supply<br>Voltage | 2.3  |      | V     |                                                   |

| ICCPD           | Power-Down<br>Supply<br>Current |      | 120  | μА    | V <sub>CC</sub> max                               |

| IIL             | Input<br>Leakage<br>Current     | -10  | +10  | μА    | ·                                                 |

| C <sub>IN</sub> | Input<br>Capacitance            |      | 10   | pF    | Sample<br>Tested                                  |

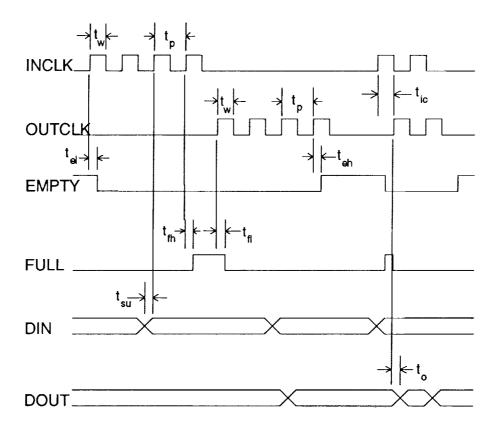

# AC Electrical Characteristics Over Operating Conditions:

| Symbol            | Description                                                  | Min | Max | Units | Conditions                 |

|-------------------|--------------------------------------------------------------|-----|-----|-------|----------------------------|

| t <sub>rise</sub> | Input rise<br>time                                           |     | 250 | ns    | Worst case <sup>1</sup>    |

| tfall             | Input fall time                                              |     | 250 | ns    | Worst<br>case <sup>1</sup> |

| t <sub>w</sub>    | High time<br>INCLK and<br>OUTCLK                             | 3   |     | ns    | Worst<br>case <sup>1</sup> |

| t <sub>D</sub>    | Period INCLK and OUTCLK                                      | 40  |     | ns    | Worst<br>case <sup>1</sup> |

| tic               | Interedge<br>time INCLK<br>and OUTCLK                        | 02  |     | ns    | Worst<br>case <sup>1</sup> |

| t <sub>el</sub>   | Time to valid<br>EMPTY from<br>INCLK                         |     | 28  | ns    | Worst<br>case <sup>1</sup> |

| <sup>t</sup> eh   | Time to valid<br>EMPTY from<br>OUTCLK                        |     | 37  | ns    | Worst<br>case <sup>1</sup> |

| <sup>t</sup> fh   | Time to valid<br>FULL from<br>INCLK                          |     | 32  | ns    | Worst<br>case <sup>1</sup> |

| tfI               | Time to valid<br>FULL from<br>OUTCLK                         |     | 30  | ns    | Worst<br>case <sup>1</sup> |

| t <sub>su</sub>   | Setup time for<br>FIFO_IN data<br>from edge of<br>INCLK      |     | 17  | ns    | Worst<br>case <sup>1</sup> |

| to                | Positive-<br>going<br>OUTCLK<br>edge to<br>FIFO_OUT<br>valid |     | 34  | ns    | Worst<br>case <sup>1</sup> |

| f                 | CLOCK<br>frequency                                           |     | 25  | MHz   | Worst<br>Case <sup>1</sup> |

## Notes:

- 1) 70° C and 4.75 volt supply.

- 2) Does not allow EMPTY and FULL to become valid.

# Timing Diagram:

# 5. Signal Descriptions

## 5.1 Control Inputs

OUTCLK Strobes data

Strobes data out of the FIFO on leading edge

**INCLK**

Strobes data into FIFO on leading edge

**5.2 Control Outputs**

**EMPTY**

Active high denotes no data stored

**FULL**

Active high denotes no more data can be stored

5.3 Data Inputs

FIFO\_IN[19:0]

20 data bits to be stored on assertion of

**INCLK**

## 5.4 Data Outputs

FIFO\_OUT[19:0] 20 data bits of stored data retrieved on assertion of OUTCLK

#### 6. Package Type

The WFG is implemented in a 84-pin PLCC package with a speed grade of 125 MHz (part number XC3042PC84-125). The FPGA gate density is 73% (105/144 available CLBs used); the pin density is 60% (44/74 available IOBs used).

#### 7. References

- [1] Levine, D. M., Hilliard, L., et. al., 1990, *Electronically Scanned Thinned Array Radiometer* (ESTAR) Earth Probe Concept: An Engineering Feasibility Analysis, Goddard Space Flight Center, page 9.

- [2] Chren, W. A., Jr., 1992, *Output Data Formatter for the ESTAR Instrument*, NASA Technical Memorandum #TM-4432.

- [3] Chren, W. A., Jr., 1992, Walsh Function Generator for the ESTAR Instrument, NASA Technical Memorandum #TM-4449.

- [4] Levine, D. M., Good, J. C., 1983, "Aperture Synthesis for Microwave Radiometers in Space", NASA TM 85033, page 1.

- [5] Levine, D. M., Gatlin, J., et. al., *Peer Review of LaRC Six-Month Study of "ESTAR" Small S/C Mission*, Langley Research Center/Goddard Space Flight Center internal document, 10/9/92.

- [6] A Digital Data Subsystem Design for an L-band ESTAR Instrument: A Summary of Research Performed in the JOVE Fellowship Program, 6/1/91 through 11/30/91, page 5, Appendix A of ESTAR Digital Data Subsystem Development, Chren, W. A., Jr., Grand Valley State University, 12/15/91.

- [7] Lin, J., Synchronous FIFO is the Solution for Data Buffering of Pipelined System Design, in 1992 Synchronous (Clocked) FIFO Design Guide, Integrated Device Technology, Inc., 1992, pp. 39-46.

## Form Approved REPORT DOCUMENTATION PAGE OMB No. 0704-0188 Public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instructions, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden, to Washington Headquarters Services, Directorate for Information Operations and Reports, 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202-4302, and to the Office of Management and Budget, Paperwork Reduction Project (0704-0188), Washington, DC 20503. 1. AGENCY USE ONLY (Leave blank) 2. REPORT DATE 3. REPORT TYPE AND DATES COVERED September 1993 Technical Memorandum 4. TITLE AND SUBTITLE 5. FUNDING NUMBERS Phase Aligner for the Electronically Scanned Thinned Array Radiometer (ESTAR) Code 740 Instrument 6. AUTHOR(S) William A. Chren, Jr. and Brian G. Zomberg 7. PERFORMING ORGANIZATION NAME(S) AND ADDRESS(ES) 8. PERFORMING ORGANIZATION REPORT NUMBER Goddard Space Flight Center 93E02368 Greenbelt, Maryland 20771 9. SPONSORING/MONITORING AGENCY NAME(S) AND ADDRESS(ES) 10. SPONSORING/MONITORING AGENCY REPORT NUMBER National Aeronautics and Space Administration Washington, D.C. 20546-0001 NASA TM-4518 11. SUPPLEMENTARY NOTES Authors Chren and Zomberg are currently at Grand Valley State University, Grand Rapids, Michigan. For additional information, contact Larry Hilliard, Code 740.4, NASA GSFC, Greenbelt, Maryland. 12a. DISTRIBUTION/AVAILABILITY STATEMENT 12b. DISTRIBUTION CODE Unclassified-Unlimited Subject Category 33 Report available from the NASA Center for AeroSpace Information, 800 Elkridge Landing Road, Linthicum Heights, MD 21090; (301) 621–0390. 13. ABSTRACT (Maximum 200 words) A prototype Phase Aligner (PA) for the Electronically Scanned Thinned Array Radiometer) instrument has been designed and tested. Implemented in a single Xilinx XC3042PC84-125 Field Programmable Gate Array (FPGA), it is a dual-port register file which allows independent storage and phase coherent retrieval of antenna array data by the Central Processing Unit (CPU). It has dimensions of 4 x 20 bits and can be used at clock frequencies as high as 25 MHz. The ESTAR is a passive synthetic-aperture radiometer designed to sense soil moisture and ocean salinity at L-band. 14. SUBJECT TERMS 15. NUMBER OF PAGES

field programmable gate arrays, Small Explorer data system, synthetic aperture radio-

OF THIS PAGE

Unclassified

meter, ESTAR, Earth Probes, Earth Observing System (EOS), thinned arrays, spacecraft instrumen-

18. SECURITY CLASSIFICATION 19. SECURITY CLASSIFICATION

OF ABSTRACT

Unclassified

OF REPORT

tation, on-board computer systems

17. SECURITY CLASSIFICATION

15

20. LIMITATION OF ABSTRACT

16. PRICE CODE

Unlimited

. . .