https://ntrs.nasa.gov/search.jsp?R=19940011074 2020-06-16T19:17:06+00:00Z

NASA-CR-194587

IN-33-CR 190610 83P

# NASA Space Engineering Research Center for VLSI Systems Design University of New Mexico/University of Idaho Grant NAGW-3293

Proposal and Annual Review

July, 1993

(NASA-CR-194587) NASA SPACE ENGINEERING RESEARCH CENTER FOR VLSI SYSTEM DESIGN Proposal and Annual Review (New Mexico Univ.) 83 p N94-15547

Unclas

G3 /33 0190610

and the set of the

· · · ·

## Contents

-

| 1 | Summary                                                             | 1  |

|---|---------------------------------------------------------------------|----|

|   | 1.1 Introduction                                                    | 1  |

|   | 1.2 Published Papers                                                | 1  |

|   | 1.3 Research Technology Transfer                                    | 2  |

|   | 1.4 Commercial Technology Transfer                                  | 3  |

|   | 1.5 Technical Support                                               | 3  |

|   | 1.6 Student Involvement                                             | 4  |

|   | 1.7 Outside Support                                                 | 4  |

|   | 1.8 Research Results                                                | 5  |

|   | 1.9 Space Experiment                                                | 5  |

|   | 1.10 Outreach Program                                               | 6  |

| 2 | VLSI Project Status                                                 | 7  |

|   | 2.1 Chip Summary                                                    | 7  |

|   | 2.2 Project Description                                             | 7  |

| 3 | Published Papers                                                    | 9  |

| 4 | NASA Symposium on VLSI Design 1992                                  | 12 |

| 5 | Contracts                                                           | 16 |

| • |                                                                     |    |

| 6 | Students                                                            | 17 |

|   | 6.1 Graduated Graduate Students                                     | 17 |

|   | 6.2 Current Graduate Students                                       | 17 |

|   | 6.3 Undergraduate Students                                          | 18 |

|   | 6.4 Minority Outreach                                               | 19 |

| 7 | University of New Mexico Research Report and Proposed Research      | 20 |

|   | 7.1 Test Results for SEU and SEL Immune CMOS Memory Circuits        | 20 |

|   | 7.2 Proposed Radiation Hard Electronics                             | 22 |

|   | 7.3 Flight Lossless Data Compression                                | 24 |

|   | 7.4 N-Modular Redundancy using the Theory of Error Correcting Codes | 28 |

|   | 7.5 Flight High Speed Reed Solomon Encoder                          | 30 |

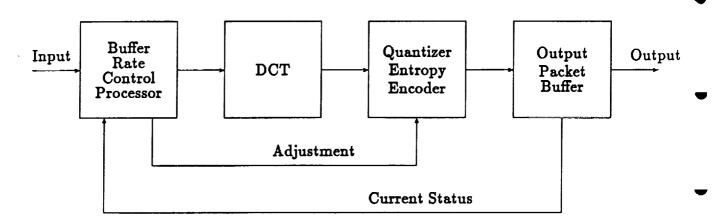

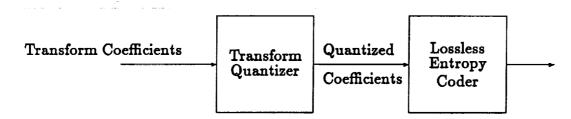

|   | 7.6 High Performance Lossy Data Compression System                  | 32 |

|   | 7.7 High Performance Correlator                                     | 38 |

|   | 7.8 Flash Analog-to-Digital Converter                               | 39 |

|   | 7.9 BUS ASIC                                                        | 40 |

|   | 7.10 Viterbi Decoder                                                | 40 |

|   | 7.11 Data Compression                                               | 42 |

|   | 7.12 Analog Conditioning of Digital Images                          | 43 |

,-

|    | 7.13 Nonlinear Prediction for Image Data Compression                         | 44 |

|----|------------------------------------------------------------------------------|----|

|    | 7.14 SOS VLSI                                                                | 44 |

|    | 7.15 The Decomposition of Synchronous Sequential Machines Using Regular and  |    |

|    | Repetitive Structures                                                        | 45 |

|    | 7.16 General Purpose CCSDS Packetizer                                        | 47 |

| 8  | University of Idaho Research Report and Proposed Research                    | 52 |

|    | 8.1 FY93 Progress Report and FY94 Proposals                                  | 52 |

|    | 8.2 Magnetic Bearing Control                                                 | 53 |

|    | 8.3 Neural Network Design and Application                                    | 54 |

|    | 8.4 Using Cross-correlation Techniques to Detect Linear System Degradation . | 55 |

|    | 8.5 Computer Modeling of Thermal Effects in Integrated Circuits              | 56 |

|    | 8.6 Wavelet Transformations                                                  | 56 |

|    | 8.7 Modeling the VHDL Signal Data Type                                       | 57 |

|    | 8.8 Reasoning about Microprocessor Pipelines                                 | 62 |

|    | 8.9 Electromagnetics Research.                                               | 64 |

|    | 8.10 Proposed Research for FY94                                              | 65 |

|    | 6.10 Proposed Research for P194                                              | 00 |

| 9  | Special Projects                                                             | 69 |

|    | 9.1 Radiation Hard Electronics Solid State Recorder EDAC                     | 69 |

|    | 9.2 Special Project Viterbi Decoder                                          | 70 |

|    | 9.3 Lossy Data Compression                                                   | 72 |

|    |                                                                              |    |

| 10 | NASA Secondary Teacher VLSI Program                                          | 73 |

|    | 10.1 Introduction                                                            | 73 |

|    | 10.2 Digital Design Course                                                   | 73 |

|    | 10.3 VLSI Design Program                                                     | 74 |

|    | 10.4 Summary of VLSI Projects                                                | 74 |

|    | 10.5 High School Digital Technology                                          | 76 |

|    | 10.6 CHIPS (Chips Help Invigorate Students)                                  | 77 |

|    | 10.7 Summary                                                                 | 80 |

|    | -                                                                            |    |

. . .

- 7 3

·

## 1 Summary

### **1.1** Introduction

This annual report outlines the activities of the past year at the NASA SERC on VLSI Design. Highlights for this year include:

- A significant breakthrough was achieved in utilizing commercial IC foundries for producing flight electronics.

- The first two flight qualified chips were designed, fabricated, tested and now being delivered into NASA flight systems.

- A new technology transfer mechanism has been established to transfer VLSI advances into NASA and commercial systems.

### **1.2 Published Papers**

A summary of all referred papers that have been published in conferences and journals is given in Section 3. The number of papers published per year is shown in Table 1.

| Year | Number of Papers |

|------|------------------|

| 1989 | 14               |

| 1990 | 19               |

| 1991 | 41               |

| 1992 | 25               |

| 1993 | 14               |

Table 1: Paper Summary

Data covering the four symposia on VLSI Design is provided in Section 4. Table 2 presents a summary of papers presented at the four symposia. Next years symposium will be held in Albuquerque on November 4 and 5, 1993. Greater attendance is anticipated being closer to national laboratories.

|               | Date     | SERC Authors | <b>Outside Authors</b> | Total Papers |

|---------------|----------|--------------|------------------------|--------------|

| 1st Symposium | Jan 1990 | 18           | 7                      | 25           |

| 2nd Symposium | Nov 1990 | 19           | 16                     | 35           |

| 3rd Symposium | Oct 1991 | 23           | 23                     | 46           |

| 4th Symposium | Oct 1992 | 17           | 27                     | 44           |

Table 2: Symposium Summary

#### **1.3 Research Technology Transfer**

Technology transfer from the laboratory to NASA is a high priority SERC activity. Table 3 shows a list of projects that have been or are being transferred to space data systems.

| Project              | Mission            | Application               |

|----------------------|--------------------|---------------------------|

| Flight CCSDS Encoder | XTE TRMM ACE       | Communication             |

| Bus Controller       | XTE TRMM HST       | Microprocessor Controller |

| Lag Correlator       | Arecibo, Greenbank | Science                   |

| Data Compression     | Landsat 7          | Communication             |

Table 3: Processors In NASA Systems

- Flight CCSDS Encoder The encoder is a custom processor designed with UTMC flight qualified electronics. The chip was delivered to GSFC and JPL in September 1992, tested in NASA systems, radiated at Brookhaven National Laboratories, and approved for flight use. The chip is being fabricated and qualified for use in XTE, TRMM and ACE.

- Bus Controller The microprocessor bus controller is a custom processor designed with UTMC flight qualified electronics. The chip was delivered to GSFC in October 1992, tested in NASA systems, and approved for flight use. The chip is being fabricated and qualified for use in XTE, TRMM and HST.

- Lag Correlator This chip contains over a million transistors, realizing a 1024 lags, is scheduled for astro physics use at the radio telescopes at Arecibo and Greenbank. This project was funded by the SERC program, NRL, NIAC and NRAO. The chip is in fabrication.

- Lossless Data Compression The flight qualified lossless data compression processor is being designed and is in the critical path for Landsat 7. The chip is scheduled for release to fabrication in Augest 1993.

Processors in research and development include:

- 1. Flight Reed Solomon CCSDS Decoder

- 2. Lossy Data Compression

- 3. High Performance Flight Viterbi Decoder

- 4. Flight A/D Converter

- 5. High Performance Auto Correlator

- 6. Flight hardware using Navy's SOS foundry

- 7. CCSDS Packetizer

### 1.4 Commercial Technology Transfer

The working relationship with NASA toward developing new technology is described next.

- Chip Development NASA scientists and engineers develop the fundamental algorithms and identify the system needs. The SERC and the NASA center jointly develop the chip specification. The SERC designs and has the chip fabricated and tested; testing normally takes place at the SERC facilities. NASA integrates the tested prototype into a system and tests the complete system.

- Flight Parts After the chip has been tested and proven to meet system requirements, flight parts need to be obtained. There are several ways.

- 1. Commercial Companies Must develop internal expertise, which often times they do not wish to do for market reasons.

- 2. GFE to Contractors This sometimes presents a problem for the government to furnish equipment to contractors.

- 3. Separate Company An option that was exercised in New Mexico.

- New Company Solution The University of New Mexico started a new company with the following goals:

- Establish Company to Support SERC Technology

- Contract Fabrication/Testing/Qualification to Government Certified Sources

- Provide long term technical support for SERC developed technology.

- New Mexico Company Integrated Circuit Solutions This company has been formed in Albuquerque. It is currently supplying 2 chips to GSFC.

#### **1.5 Technical Support**

The SERC has provided technical support to NASA GSFC on two projects.

- 1. VLSI ASIC Design Review Dr. Kelly Cameron attended 3 design reviews in California to identify problems with the Mickelson Doppler Interferometer instrument. Dr. Cameron accompanied Steve Pszcolka, David Langjahr and James Shannon of GFSC as a VLSI expert. He helped identify problems in the design of the ASIC chip.

- 2. Analog to Digital Converter Sipex is building an analog to digital converter which is an integral part of the of the Fine Pointing Sun Sensor in the International Solar-Terrestrial Physics Project. Sipex supplies the ADC to Adcole, who builds the Fine Pointing Sun Sensor for NASA, who is sharing the technology with ESA. The Sun Sensor ADC is a Sipex standard product with a special linearity specification and a slightly lower conversion rate. The ADC is a hybrid module consisting of a

rad hard gate array, a Harris 12-bit Digital to Analog Converter (DAC), an 8-bit DAC, an opamp, a counter, and various discrete components. The DAC's are used together with a comparator and a successive approximation register in the gate array to form a successive approximation ADC. The 12-bit Harris DAC is laser trimmed by Sipex so that the ADC meets the 16-bit linearity specifications.

The problem is that the linearity of the ADC no longer meets the specification after the part is burned in. The most likely place for the problem is in the Harris 12bit DAC, since DAC linearity in a successive approximation ADC directly affects ADC linearity. A residual gas analysis found the moisture content inside some of the hybrid ADC's to be above specification by almost a factor of two, but this is still very dry, and probably not the problem.

The purpose of the meeting was to determine what should be done next to solve the shifting linearity problem. Suggested were made by Don Thelen of the SERC staff. The end result is unknown.

### **1.6 Student Involvement**

Education is a key element in the SERC activities. Student involvement remains high and includes the following:

- Three Ph.D students graduated in Electrical Engineering in the last year. Nine Master of Science students graduated in Electrical Engineering and Computer Engineering in the last year. These are listed in Section 6.1.

- Thirty seven undergraduate students are currently involved in the NASA program. The NASA Scholars are listed in Section 6.3.

- Nine Master of Science students are currently pursuing advanced degrees and research in Electrical and Computer Engineering. These graduate students are listed in Section 6.2.

- Five Ph.D students are currently pursuing advanced degrees in Electrical Engineering. These graduate students are listed in Section 6.2.

- Sixteen new high school teachers were exposed to digital logic design SERC NASA program this year.

- Ten high school teachers designed their own VLSI chip with the chips being fabricated at NSF's MOSIS foundry this year.

### 1.7 Outside Support

\$2,509,597 in non-SERC contracts are in force this year to support the SERC activities. These are itemized in Section 5.

#### **1.8 Research Results**

Research summaries and proposed research activities are described in Section 7 and Section 8. The major result is summarized here.

• Low Cost High Performance Flight Electronics A new breakthrough has been achieved in producing flight electronics with commercial foundries. For years it has been believed that flight electronics could only be produced with specialized foundries. It has been demonstrated that now flight electronics can be realized with commercial foundries.

#### Significance

- Produce flight electronics with commercial non-radiation hard foundries

- Reduce Cost of flight electronics by one or two orders of magnitude.

- Design with latest IC technologies to produce faster more dense ICs

- No government investment needed to develop new IC processes (follow and use commercial foundries)

- Test Results Test cells were designed and processed using the Hewlett Packard 1.0 micron CMOS commercial process. The cells were tested at Brookhaven National Laboratory for single event upset (SEU) and single event latchup (SEL). NASA accepts an LET = 40 as sufficient for flight electronics. The test cells demonstrated an LET greater than 120 and in fact did not upset or latchup under any conditions.

Following is an example illustrating the difference today in producing flight electronics using special foundries and commercial foundries. The SERC was asked to provide a high performance EDAC for future NASA solid state recorders. A total of 55 chips were required to be delivered. The comparison is shown next with a savings of approximately \$500,000.

| Item        | <b>Current Solution</b> | New Solution |

|-------------|-------------------------|--------------|

| Engineering | \$122,000               | \$104,400    |

| Fabrication | 556,750                 | 190,000      |

| Total       | \$893,500               | \$400,000    |

### **1.9 Space Experiment**

Microelectronic and Photonic Test Bed A new test bed is being proposed to continue experimentation initiated in the CRRES program. The sponsors for the new space test bed are:

- 1. Defense Nuclear Agency

- 2. Naval Research Laboratory

- 3. USAF Phillips Laboratory

The test bed program consists of:

- Joint Space "Piggy back" Experiment

- Assess Device Performance in Space Radiation Environment

- Modeled after 1990-91 CRRES Space Experiment

- Launch in 1996

The NASA SERC has been asked to provide special purpose processors to be used in this test bed.

#### 1.10 Outreach Program

The one week digital logic program was repeated this year with 16 new teachers. The teachers left with great enthusiasm. This program will be continued in Albuquerque.

The four week VLSI design project was conducted again this year. Five chips were designed by the teachers. The teachers had to master the following skills - logic specification, logic design with VLSI standard cells, logic simulation, layout, design rule check and verification. This experience had a remarkable effect on the teachers. A great deal of publicity should result since each teacher will present his experiences at regional meetings. It is likely that these are the only high school teachers in the country to design a VLSI chip. Moreover, they may now have more VLSI skills than many graduates from EE programs. They left feeling very proud and highly motivated. Details can be found in Section 10.

A third phase is completed. The teachers feel that the introduction of digital electronics to public schools can have a major impact, not only on the high achievers, but on the broad spectrum of students. Vocational education can greatly benefit from knowing this technology. The teachers feel that the information gained at this workshop can affect the entire country. Therefore, they would like to try to design a curriculum, write a proposal for funding and investigate delivery mechanisms. A proposal was written to US Army Research Office for funding next year. The goal is to transfer digital electronics and CAD systems into the high school programs. Text book material needs to be created.

6

## 2 VLSI Project Status

## 2.1 Chip Summary

| Chip Project                | Status            | Expected Date | Application        |

|-----------------------------|-------------------|---------------|--------------------|

| Flight CCSDS Encoder        | Delivered         | Sept 1992     | XTE TRMM ACE       |

| Bus Controller              | Delivered         | Oct 1992      | XTE TRMM HST       |

| Hewlett Packard ECC         | Delivered         | Nov 1992      | Disc Drives        |

| Flight Custom CCSDS Decoder | Initial Stage     |               | EOS                |

| 1024 Lag Correlator         | Design            | Aug 1993      | Arecibo, Greenbank |

| High Performance Correlator | Design            | Jan 1994      | MIT Haystack       |

| Flight Lossless Data Comp   | Design            | Nov 1993      | Landsat 7          |

| Lossy Data Compression      | Initial Stage     |               |                    |

| Flight A/D                  | Test Cells In Fab |               |                    |

| CCSDS Packetizer            | Design            | January 1994  |                    |

| Viterbi Decoder             | Specification     |               |                    |

| Hewlett Packard uP          | Design            | Dec 1993      | Commercial         |

## 2.2 **Project Description**

- Bus Controller A bus controller for several missions, including XTE, TRMM and HST, was designed using a UTMC space qualified gate array. This chip is part of the system that contains the new flight qualified Mongosse microprocessor realized by Harris and GSFC.

- Flight CCSDS Encoder A low speed flight Reed Solomon encoder was designed with a UTMC space qualified gate array. It operates at 200 Mbits/second. The interleaving depth is programmable up to 8. This processor is being ordered for the XTE, TRMM and ACE flight projects. Fully tested and qualified flight parts should be delivered to GSFC July 1993.

- Hewlett Packard ECC High performance Error Correction Module designed in HP's 0.8 micron process that should be installed in future disc drive products. The layout of this design used an automatic tiling system to assemble the base cells.

- High Performance Correlator A 100 MHz 1024 channel time-lag correlator is being developed. The chip will contain SEU immune circuitry.

- Flight Lossless Data Compression An enhanced version of the military grade compression is being designed for flight use. The data rate is specified up to 200 Mbits/sec and it has enhanced features for data compression performance. It is being implemented to meet the specific needs of Landsat.

- Lossy Data Compression New algorithms and chip architectures are being investigated to produce a variable rate lossy data compression system.

- Flight A/D Converter The goal is to design a 18 bit 50 Khz sampling A/D converter which can be used in a low earth orbit. This processor is designed to be immune to SEU and SEL radiation impacts. The test cells have been sent for fabrication.

- CCSDS Packetizer The CCSDS packetizer will accept variable length, variable word width instrument data. Input data rates are specified to be 20 Mbits/second. The packetizer will output CCSDS packets and MPDU data formats.

- High Performance Viterbi Decoder An initial design has been completed on the realization of a constraint length 15 Viterbi decoder. The final system is estimated to have up to 128 chips, each chip having 4096 processors.

- Hewlett Packard uP A general purpose microprocessor that can be used in disc drives is being designed in accordance with specifications given by HP. This processor is exceedingly flexible and should yield a competitive commercial advantage to HP.

## **3** Published Papers

J. Sarker and J. Purviance, "Yield Sensitivity Study of AlGaAs/ GaAs High Electron Mobility Transistor," International Journal of Microwave and Millimeter-Wave Computer Aided Engineering, Vol. 2, No.1, January, 1992.

M. Beale and H. Demuth, "Training Functions in a Neural Network Design Tool", Proceedings of the Workshop on Neural Networks, Auburn University, Auburn, Alabama, Feb. 10-12, 1992.

M. Beale and H. Demuth, "Building a Neural Network", Scientific Computation and Automation, May, 1992, pp. 19-21.

H. Demuth and M. Beale, "Neural Network Users Guide", The Mathworks, Natick, Massachusetts, approx. 300 pp., June, 1992.

M. Meehan and J. Purviance, "Statistical Performance Sensitivity – A Valuable Measure for Manufacturing Oriented CAD," 1992 IEEE Microwave Theory and Techniques International Microwave Symposium, June, 1992.

J. Sarker and J. Purviance, "Yield Sensitivity of HEMT Circuits to Process Parameter Variations, *IEEE Transactions on Microwave Theory and Techniques*, Vol. 40, No. 7, July, 1992.

N. Liu and S. Whitaker, "Low Power SEU Immune CMOS Memory Circuits", *IEEE Conference on Nuclear and Space Radiation Effects*, New Orleans, LA, PA7, July 1992.

M. Beale and H. Demuth, "Preparing Controllers for Nonlinear Systems," AI Expert, July 1992, pp. 42-46.

K. Cameron, J. Canaris and S. Whitaker, "A Video Image Processor for Realtime Centroid Calculation", *Proceedings of the IEEE ASIC Conference and Exhibit*, Rochester, NY, pp. 201-204, Sept. 1992.

S. Whitaker and G. Maki, "Self Synchronized Asynchronous Sequential Pass Transistor Circuits", *IEEE Transactions on Computers*, vol. 41, no. 10, pp. 1344-1348, Oct. 1992.

G. Maki, "Special Purpose High Performance VLSI: Impacts on Mission Strategies", Space Exploration Science and Technologies Research: ASME, AD-Vol. 31, pp 43-48, November 1992.

N. Liu and S. Whitaker, "Low Power SEU Immune CMOS Memory Circuits", IEEE Transactions on Nuclear Science, vol. 39, no. 6, pp. 1679-1684, Dec. 1992.

J. Venbrux, Pen-Shu Yeh, and M. N. Liu, "A VLSI Chip Set for High Speed Lossless Data Compression", IEEE Transactions on Circuits and Systems for Video Technology, December 1992.

M. Liu, K. Liu, G. Maki and S. Whitaker, "Automated ILA Design for VLSI Synchronous State Machines", *IEEE 35th Midwest Symposium on Circuits and Systems*, Washington, DC, pp. 851-854, Dec. 1992.

G. Maki, J. Gibson, J. Gambles, J. Canaris, S. Whitaker and J. Venbrux, "NASA Secondary Teacher VLSI Program", 1992 Annual Conference Proceedings of the American Society for Engineering Education.

M. Meehan and J. Purviance, "Yield and Reliability in Microwave Circuit and System Design," ARTECH, Inc., 1992.

D. Janson and J. Frenzel, "Application of Genetic Algorithms to the Training of Higher Order Neural Networks," *Journal of Systems Engineering*, Vol. 2, pp. 272–276, 1992

J. Young, "A time-domain weighted residual formulation of Maxwell's equations," 31st American Institute of Aeronautics and Astronautics (AIAA) Symposium, Reno, Nevada, January, 1993.

J. Canaris, "A VLSI Architecture for the Real Time Computation of Discrete Trigonometric Transforms", The Journal of VLSI Signal Processing, January 1993.

M. Shamanna and S. Whitaker, "A Carry Select Adder with Conflict Free Bypass Circuit", Proceedings of the 6th International Conference on VLSI Design, Bombay, India, pp. 363-366, Jan. 1993.

E. Ingermann and J. Frenzel, "Sensitivity Analysis of a Radiation Immune CMOS Logic Family under Defect Conditions," *Proceedings of the 11th IEEE VLSI Test Symposium*, pp. 355–357, April 1993.

D. Lamet and J. Frenzel, "Defect-Tolerant Cache Memory Design," Proceedings of the 11th IEEE VLSI Test Symposium, pp. 159–163, April 1993.

J. Gambles and P. Windley, "Reasoning About the Standard Logic Package Signal Data Type", CHDL '93: The IFIP Conference on Hardware Description Languages and their Applications, Ottowa, Canada, April, 1993.

D. Wiseman, J. Canaris, N. Liu, S. Whitaker, K. Liu, J. Venbrux, K. Cameron, K. Arave and L. Arave, "Design and Testing of SEU/SEL Immune Memory and Logic Circuits in a Commercial CMOS Process", accepted for publication at the IEEE NSREC. May 1993

G. Maki, S. Whitaker, J. Gambles, J. Canaris and J. Venbrux, "NASA High School Teacher VLSI Program", accepted for publication in the Proceedings of the 10th Bienial University/Government/Industry Microelectronics Symposium. May 1993

P. Windley, "A Theory of Generic Interpreters," Proceedings of the 1993 Conference on Correct Hardware Design Methodologies (CHARME), Arles, France, 1993.

P. Windley, "Abstract Theories in HOL," Proceedings of the 1992 International Workshop on the Higher-Order Logic Theorem Proving and its Applications, L. J. M. Claesen and M. J. C. Gordon, editors, North-Holland, 1993.

J. Frenzel and P. Windley, "Microprocessor Applications," The Electrical Engineering Handbook, Chapter 76.2, CRC Press. (in publication)

J. Frenzel, "Supply Current Diagnosis of VLSI Circuits," IEEE Transactions on Reliability. (accepted for publication)

David J. Janson and James F. Frenzel, "Training Product Unit Neural Networks with Genetic Algorithms," *IEEE Expert Magazine*. (accepted for publication)

J. Young, "Characterizing radio wave interactions with ionized fluids using a weighted residual, time-domain method." A conference abstract has been accepted for presentation at the Progress in Electromagnetic Research Symposium.

10

## 4 NASA Symposium on VLSI Design 1992

- Waleed K Al-Assadi. Y. Malaiya and A. Jayasumana, "Detection of Feed-Through Faults in CMOS Storage Elements," Fourth NASA VLSI Design Symposium, 1992.

- Kari Arave, John Canaris, Lowell Miles and Sterling Whitaker, "Schematic Driven Layout of Reed Solomon Encoders," Fourth NASA VLSI Design Symposium, 1992.

- Grant Beagles, Kel Winters and A.G. Eldin, "Bit-Systolic Arithmetic Arrays Using Dynamic Differential Gallium Arsenide Circuits," Fourth NASA VLSI Design Symposium, 1992.

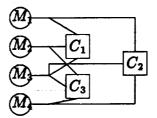

- V. Bobin, S. Whitaker, and G. Maki, "Links between N-Modular Redundancy and the Theory of Error-Correcting Codes," Fourth NASA VLSI Design Symposium, 1992.

- Lowell Campbell and John Purviance, "Interpolative Modeling of GaAs FET Sparameter Data Bases for Use in Monte Carlo Simulation," Fourth NASA VLSI Design Symposium, 1992.

- John Canaris, "NASA SERC Digital Correlator Projects," Fourth NASA VLSI Design Symposium, 1992.

- Kumar Chandra and William J. Wilson, "Low Power, CMOS Digital Autocorrelator Spectrometer for Spacebourne Applications," Fourth NASA VLSI Design Symposium, 1992.

- A.G. Eldin, "A DRAM Compiler Algorithm for High Performance VLSI Embedded Memories," Fourth NASA VLSI Design Symposium, 1992.

- Arai Eshraghi, Terri Fiez, Kel Winters and Thomas Fischer, "Design of a New Squaring Function for the Viterbi Algorithm," Fourth NASA VLSI Design Symposium, 1992.

- Joseph J. Feeley and Daniel Ahlstrom, "A New Eddy Current Model for Magnetic Bearing Control System Design," Fourth NASA VLSI Design Symposium, 1992.

- Jody W. Gambles and Phillip J. Windley, "HDL to Verification Logic Translator," Fourth NASA VLSI Design Symposium, 1992.

- J.A. Gunawardena, "A Novel Cache Mechanism," Fourth NASA VLSI Design Symposium, 1992.

- David K. Probst and Hon F. Li, "A Simple Modern Correctness Condition for

- Jon Hagen, "Applications of Correlator Chips in Radio Science," Fourth NASA VLSI Design Symposium, 1992.

- K. Hebbalalu, S. Whitaker and K. Cameron, "On the Decomposition of Synchronous State Machines Using Sequence Invariant State Machines" Fourth NASA VLSI Design Symposium, 1992.

- Erik H. Ingermann and James F. Frenzel, "Defect-Sensitivity Analysis of an SEU Immune CMOS Logic Family," Fourth NASA VLSI Design Symposium, 1992.

- Byung Wook Jeon and Chidchanok Lursinsap, "A Statistical-based Scheduling Algorithm in Automated Data Path Synthesis," Fourth NASA VLSI Design Symposium, 1992.

- Byung Wook Jeon and Chidchanok Lursinsap, "Micro-rollback and Self-recovery Synthesis," Fourth NASA VLSI Design Symposium, 1992.

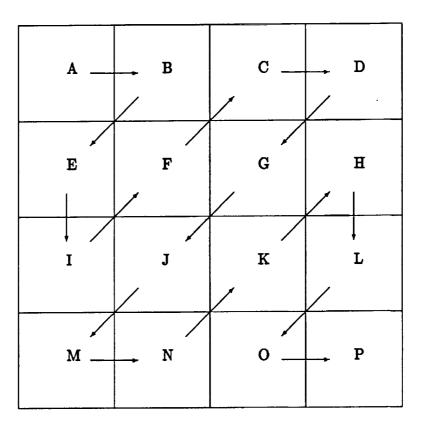

- S. Kamath, Doug Lynn and Sterling Whitaker, "A VLSI Implementation of DCT Using Pass Transistor Technology," Fourth NASA VLSI Design Symposium, 1992.

- James D. Kinnison, "Single Event Phenomena: Testing and Prediction," Fourth NASA VLSI Design Symposium, 1992.

- Dan Lamet and James F. Frenzel, "A Set-Associative, Fault-Tolerant Cache Design," Fourth NASA VLSI Design Symposium, 1992.

- John Lenell, Steve Wallace and Nader Bagherzadeh, "A 20MHz CMOS Reorder Buffer for a Superscalar Microprocessor," Fourth NASA VLSI Design Symposium, 1992.

- Xueqin Li and H.D. Cheng, "A Novel Visual Hardware Behavioral Language," Fourth NASA VLSI Design Symposium, 1992.

- Priscilla L. McKerracher, Russel P. Cain, Jon C. Barnett, William S. Green and James D. Kinnison, "Design and Test of Field Programmable Gate Arrays in Space Applications," Fourth NASA VLSI Design Symposium, 1992.

- T.R. McKnight, D.E. Rodriguez, J.C. Barnett, and C.R. Valverde, "System Development Using VLSI for Space Applications," Fourth NASA VLSI Design Symposium, 1992.

- Sankaran M. Menon, Yashwant K. Malaiya and Anura P. Jayasumana, "Behavior of Faulty Double BJT BiCMOS Logic Gates," Fourth NASA VLSI Design Symposium, 1992.

- Gulam Mohamed, Tan Han Ngee and Chng Chew Lye, "A Heuristic-Based Scheduling Algorithm for High Level Synthesis," Fourth NASA VLSI Design Symposium, 1992.

- Bruce Offord, "Fully Depleted Silicon-on-Sapphire and Its Application to Advanced VLSI Design," Fourth NASA VLSI Design Symposium, 1992.

- Ramesh Panwar and Leon Alkalaj, "Low Energy CMOS for Space Applications," Fourth NASA VLSI Design Symposium, 1992.

- A. Benjamin Premkumar and T. Srikanthan, "A Real Time Correlator Using Distributed Arithmetic Principles," Fourth NASA VLSI Design Symposium, 1992.

- David K. Probst and Hon F. Li, "A Simple Modern Correctness Condition for a Space-Based High-Performance Microprocessor," Fourth NASA VLSI Design Symposium, 1992.

- Jogendra Sarker and John Purviance, "Dimension Scaling Effects on the Yield Sensitivity of HEMT Digital Circuits," Fourth NASA VLSI Design Symposium, 1992.

- E. Thomas Schubert, "A Mechanized Process Algebra for Verification of Device Synchronization Process," Fourth NASA VLSI Design Symposium, 1992.

- Manju Shamanna and Sterling Whitaker, "On Fast Carry Select Adders," Fourth NASA VLSI Design Symposium, 1992.

- Donald C. Thelen, "An 18 Bit 50 kHz ADC for Low Earth Orbit," Fourth NASA VLSI Design Symposium, 1992.

- C. Timoc, T. Tran and J. Wongso, "A 1 GHZ Sample Rate, 256-Channel, 1-Bit Quantization, CMOS, Digital Correlator Chip," Fourth NASA VLSI Design Symposium, 1992.

- M. Kemal Unaltuna and Vijay Pitchumani, "A Mean Field Neural Network for Hierarchical Module Placement," Fourth NASA VLSI Design Symposium, 1992.

- Paul Vincent and Jea Park, "Analog/Digital pH Meter System I.C.," Fourth NASA VLSI Design Symposium, 1992.

- Larry Volkening, "Teaching VLSI in High School," Fourth NASA VLSI Design Symposium, 1992.

- Abdul Wahab, S.S. Erdogan and A.B. Premkumar, "Evaluation of Floating Point Sum or Difference of Products in Carry Save Domain," Fourth NASA VLSI Design Symposium, 1992.

- K.C. Wang and D.T. Cheung, "Heterojunction Bipolar Transistor Technology for Data Acquisition and Communication," Fourth NASA VLSI Design Symposium, 1992.

- Phillip J. Windley, "Instruction Set Commutativity," Fourth NASA VLSI Design Symposium, 1992.

- Don R. Wiseman and Sterling Whitaker, "A High Speed CMOS A/D Converter," Fourth NASA VLSI Design Symposium, 1992.

- Gregary C. Zweigle and Roberto Bamberger, "Reduction of Blocking Effects for the JPEG Baseline Image Compression Standard," Fourth NASA VLSI Design Symposium, 1992.

## 5 Contracts

| Title                               | P.I.        | Funding Agency            | Amount      |

|-------------------------------------|-------------|---------------------------|-------------|

| VLSI Bus ASIC                       | S. Whitaker | NASA GSFC                 | \$146,750   |

| Space Qualified Reed Solomon Codex  | S. Whitaker | NASA GSFC                 | 300,000     |

| RS1 and RS3 Encoder Macrocell       | S. Whitaker | HP DMD                    | 107,000     |

| Radiation Hardened VLSI Electronics | S. Whitaker | NASA GSFC                 | 212,500     |

| RAD Testing of Lossless Data Comp   | J. Venbrux  | NASA GSFC                 | 154,150     |

| Flight Data Compression             | J. Venbrux  | NASA GSFC                 | 130,000     |

| Lossy Data Compression              | K. Cameron  | NASA GSFC                 | 100,000     |

| High Performance Correlator         | J. Canaris  | MIT                       | 215,227     |

| High Performance Correlator         | J. Canaris  | NRL                       | 30,000      |

| High Performance Correlator         | J. Canaris  | NAIC                      | 30,000      |

| High Performance Correlator         | J. Canaris  | NRAO                      | 30,000      |

| Correlator Chip Testing             | J. Canaris  | Aerojet                   | 2,062       |

| EDAC Microprocessor                 | K. Cameron  | HP DMD                    | 300,000     |

| Hardware Verification               | P. Windley  | Boeing                    | 14,938      |

| Hardware Verification               | P. Windley  | NSF                       | 34,818      |

| Hardware Verification               | P. Windley  | NSA                       | 41,150      |

| Test Pattern Generation             | J. Frenzel  | <b>UoI Research Grant</b> | 6,000       |

| SEU-Immune State Machines           | J. Frenzel  | Idaho Space Grant         | 5,000       |

| Research Center Support             | J. Feeley   | State of Idaho            | 100,000     |

| Research Center Support             | G. Maki     | UNM                       | 550,000     |

| Total                               |             |                           | \$2,509,597 |

## **6** Students

Ŷ

V

ÿ

$\checkmark$

## 6.1 Graduated Graduate Students

-

| Student              | Degree | Year | Thesis Title                                                       |

|----------------------|--------|------|--------------------------------------------------------------------|

| Vijay Bobin          | PhD EE | 1992 | Application of the Theory of Linear                                |

|                      |        |      | Codes to Modular Redundancy.                                       |

| Kristen Chen         | MS CE  | 1992 | Pulse Mode VLSI Asynchronous Se-                                   |

|                      |        |      | quential Circuits.                                                 |

| Lowell Campbell      | PhD EE | 1992 | Interpolative Modeling for MonteCarlo                              |

| Jody Gambles         | MS CE  | 1992 | Simulation of GaAs FETs.<br>Incorporating Formal Verification into |

|                      |        | 1001 | VLSI Design Methodology.                                           |

| Ganesh Gursuswamy    | MS EE  | 1992 | A Modified Reconfigurable Data Path                                |

| -                    |        |      | Processor.                                                         |

| Kumar Hebbalalu      | MS EE  | 1992 | The Decomposition of Synchronous Se-                               |

|                      |        |      | quential Machines in VLSI Controllers.                             |

| Seetaram Kamath      | MS EE  | 1992 | A VLSI Implementation of Discrete                                  |

|                      |        | ·    | Cosine Transform (DCT) Using Pass                                  |

| <i></i>              |        |      | Transistor Logic.                                                  |

| Jiasui Li (Gary Lee) | PhD EE | 1992 | Parallel Algorithms and Processors for                             |

|                      |        |      | Optimization and Optimal Control.                                  |

| George Niederuaer    | MS EE  | 1992 | An Efficient Fuzzy Control Algorithm.                              |

| John Pendleton       | MS EE  | 1992 | SEU Immune Data Compressor.                                        |

| Don Wiseman          | MS EE  | 1992 | High Speed CMOS A/D Converter.                                     |

| Fang Zhuo            | MS CS  | 1992 | A Comparison of Software Maintain-                                 |

| -                    |        |      | ability Indices.                                                   |

## 6.2 Current Graduate Students

| Student         | Degree | Year | Thesis Title                             |

|-----------------|--------|------|------------------------------------------|

| Mark Beale      | MS CE  | ĪP   |                                          |

| Michael Coe     | MS CS  | IP   | an a |

| John Canaris    | PhD EE | IP   | Single Event Upset Immune Circuit        |

|                 |        |      | Design Techniques for CMOS VLSI          |

|                 |        |      | Memory and Logic Circuits.               |

| Mike Dallabetta | MS EE  | IP   |                                          |

| Jon Gibson      | PhD EE | IP   | Delay Analysis of Combinations of Pass   |

|                 |        |      | Transistors and Classical Logic Gates.   |

| Nabeel Ijaz     | MS EE  | IP   |                                          |

| Erik Ingermann  | MS EE  | IP   |                                          |

| Kraig Kaiser    | MS EE  | IP   |                                          |

| Navid Madani    | MS CE  | IP   | Behavioral Model Simulation Encoder.     |

| Noman Rangwala     | MS EE  | IP |                                     |

|--------------------|--------|----|-------------------------------------|

| Manjunath Shamanna | PhD EE | IP | VLSI Hardware Acceleration.         |

| Don Thelen         | PhD EE | IP | Integrated CMOS Analog Design Tech- |

|                    |        |    | niques for Space Applications.      |

| Feng Yu            | MS EE  | IP | Testing of ILA VLSI Circuits        |

| Greg Zweigle       | PhD EE | IP | Lossly Data Compression             |

|                    |        |    |                                     |

## 6.3 Undergraduate Students

.

NASA Scholars supported by SERC:

| 1                 |      |                               |

|-------------------|------|-------------------------------|

| Clinton Alter     | B.S. | Computer Science              |

| Amy Anderson      | B.S. | Computer Science              |

| Matthew Baca      | B.S. | <b>Electrical Engineering</b> |

| Eric Cameron      | B.S. | Computer Engineering          |

| Brandon Carlson   | B.S. | <b>Electrical Engineering</b> |

| Kenneth Chapman   | B.S. | <b>Electrical Engineering</b> |

| Dee Lee Chou      | B.S. | Electrical Engineering        |

| James Clough      | B.S. | Computer Science              |

| Brenda Daniel     | B.S. | Chemical Engineering          |

| Michael Fisch     | B.S. | Electrical Engineering        |

| Brad Fitzgerald   | B.S. | Electrical Engineering        |

| Cade Greenup      | B.S. | Computer Engineering          |

| Chad Hale         | B.S. | Electrical Engineering        |

| Brian Haler       | B.S. | Computer Science              |

| Eric Hewitt       | B.S. | Electrical Engineering        |

| Sheryl Hoene      | B.S. | Computer Science              |

| Kirk Kludt        | B.S. | Electrical Engineering        |

| Vernon Koehler    | B.S. | Computer Science              |

| Matt Langenbahn   | B.S. | Electrical Engineering        |

| Walter McNall     | B.S. | Electrical Engineering        |

| Shad Miller       | B.S. | Architecture                  |

| James Morasch     | B.S. | Computer Engineering          |

| Savanah Partridge | B.S. | Electrical Engineering        |

| Teresa Ratts      | B.S. | Computer Engineering          |

| Emily Rehwinkel   | B.S. | Civil Engineering             |

| Jason Rubero      | B.S. | Electrical Engineering        |

|                   |      | 0                             |

#### NASA Scholars supported by SERC:

| Aimee Schmidt            | B.S. | Computer Science              |

|--------------------------|------|-------------------------------|

| <b>Robert Schoefling</b> | B.S. | <b>Computer Engineering</b>   |

| Brett Shelton            | B.S. | <b>Computer Engineering</b>   |

| Nathan Shiflet           | B.S. | Electrical Engineering        |

| Eben Sutton              | B.S. | <b>Computer Engineering</b>   |

| Tammy Teuscher           | B.S. | <b>Electrical Engineering</b> |

| Dan Tintzman             | B.S. | <b>Electrical Engineering</b> |

| Chad Vandemeer           | B.S. | <b>Computer Engineering</b>   |

| Shannon Wade             | B.S. | Computer Science              |

| Wendy Wahl               | B.S. | <b>Electrical Engineering</b> |

| Lance Wasem              | B.S. | <b>Electrical Engineering</b> |

### 6.4 Minority Outreach

anan a shaka a sh

The University of New Mexico is identified as a Minority Institution defined by the requirements of the Higher Education Act of 1965 (20 U.S.C 1058) and FAR 252.226-7001.

The Idaho Science Camp is organized in the college of engineering to attract minorities into science and engineering professions. The Science Camp consists of mostly junior high school Native Americans who come to campus during the summer for a one week program.

The SERC is pursuing a longer term program through building an infrastructure among the high school science teachers. Over forty teachers are already part of this structure who are active in helping to recruit good science students. The teachers have been on campus and understand the NASA SERC program and activities.

## 7 University of New Mexico Research Report and Proposed Research

## 7.1 Test Results for SEU and SEL Immune CMOS Memory Circuits

Don Wiseman, John A. Canaris, Sterling R. Whitaker, Jack Venbrux, Kelly Cameron, Kari Arave, and Larry Arave

Abstract – Test results for three recently proposed SEU logic/circuit hardened CMOS memory circuits verify upset and latch-up immunity for two configurations to be in excess of 120 MeV  $\cdot$  cm<sup>2</sup>/mg using a commercial, nonradiation hardened CMOS process.

#### Summary

It is well known that special radiation resistant integrated circuit (IC) processes exist that are designed to provide protection against single event latch-up (SEL) and single event upset (SEU) phenomena. An experiment is reported in this paper which demonstrates that it is possible to provide a high degree of SEL and SEU immunity using a commercial, non-radiation hardened, CMOS process.

A test IC was designed consisting of five shift registers. Three of the shift registers utilized memory cells designed to be tolerant of SEU's through three different logic/circuit design hardening techniques [2,3,4]. The other two were normal shift register designs to be used for comparisons. All of the structures were built using latch-up hardening techniques. The IC was hardened against single event induced latch-up through guard barring, layout techniques, and the use of a starting material with an epitaxial layer. The test samples were processed through MOSIS in Hewlett Packard's commercial  $1\mu m$  double metal CMOS (CMOS34) process at the Corvallis, Oregon facility.

Tests to determine the SEU susceptibility of the specially designed memory cells were conducted at Brookhaven National Laboratories (BNL) on January 13, 1993. The objective was to determine the threshold linear energy transfers (LETs) and cross-sections for SEU and latch-up due to heavy ions. The Single Event Upset Test Facility (SEUTF) utilizes a Tandem Van De Graaff accelerator for providing various ions and energies. The ion beam is directed at a test board mounted inside a vacuum chamber. The facility provides a computer-driven monitor and control program for the ion beam and test board setup.

Four of the test chips were placed on a wire-wrapped board, along with additional control logic, and mounted into the radiation test chamber at BNL. Three of the chips, with their die exposed, were placed in a heavy ion beam and individually irradiated. The outputs of the part being irradiated were compared in real time with the outputs of the fourth chip; the fourth chip acted as a control unit. Counters were placed at the output of the board to record differences between the outputs of the chip being irradiated, and the outputs of the control chip. In this manner, upsets due to the heavy ion beam could be observed and quantified. The data sent through the shift register was comprised of an equal number of 1's and 0's. However, at any given time, different data patterns were sent through each register, to illuminate possible data dependent effects.

The current drawn by the chips was continuously monitored during the tests. Also, a current limit was placed on the voltage source such that if latch-up occurred in any of the parts, the power would be removed from the entire test board. The test board and chips were running at 1 MHz with a 5 volt supply. The board drew a total of 10 mA of current while operating under these conditions. The test board also included circuitry that would emulate upsets. By using this circuitry, the counters could be calibrated, and the functionality of the entire test set-up could be verified.

Experiments were conducted using Cl-35 at 206 MeV, Ni-58 at 265 MeV, I-270 at 320 MeV, and Au-197 at 350 MeV ions, beamed at various angles. The LET was steadily increased from 20 to 120 over the course of the experiment. The ion used for the beam was changed whenever the depth of the beam for the desired LET would be less than 20  $\mu m$ . The non-hardened designs exhibited upsets under every condition. One of the hardened designs [3] exhibited an SEU threshold of LET=35 while the threshold of the other two designs [2,4] exceeded 120 MeV  $\cdot$  cm<sup>2</sup>/mg. No latch-up was observed in any of the 10 parts subjected to radiation, demonstrating an SEL threshold in excess of 120 MeV  $\cdot$  cm<sup>2</sup>/mg. A previous run of the same test chip without guard barring and SEL hardening layout techniques showed an SEL threshold of approximately 31 MeV  $\cdot$  cm<sup>2</sup>/mg. Table 1 summarizes the experimental data for one of the test chips. Sec. 1 is the hardened design based on [4], Sec. 2 and 3 are the non-hardened designs. Sec. 4 was based on [3] while Sec. 5 was based on [2].

This paper would review the memory cell designs, describe the measurement techniques and report the results of the SEU testing. This would be the first report of actual test results for the new design techniques and demonstrates the possibility of designing circuits for space applications using high density, high perfomance commercial processes. Additional test ICs are currently in various stages of design and fabrication, including an adjustment of device sizes in the shift register based on [3] which should improve the present LET=35 threshold. These results should also be available by the conference and any additional information will be included in the poster presentation. As long as follow on test chip experiments confirm this data, this is a major break through.

The implications of the data taken in this experiment should not be underestimated. The data implies that standard, high density, commercial CMOS processes can achieve SEU and SEL protection equal to or better than expensive radiation hardened processes for space applications.

21

|                    |                     |            |              |                  |                |                        |                                          | Upsets | Upsets     | Upsets     | Upsets   | Upsets |

|--------------------|---------------------|------------|--------------|------------------|----------------|------------------------|------------------------------------------|--------|------------|------------|----------|--------|

| Raz                | Ion                 | Baergy     | Depth        | LBT <sup>1</sup> | Time           | Plaz                   | Finence                                  | Sec. 1 | Sec. 2     | Sec. 3     | Sec. 4   | Sec. B |

|                    |                     | MeV        | LM           |                  | 840            | #/cm2/sec              | #/cm2                                    | _      |            |            | _        |        |

| 1                  | C1-35               | 206        | 35.8         | 20.0<br>20.0     | 132.3          | 8.853B+04              | 1.1713+07<br>1.1823+07                   | 0      | 21<br>25   | 40<br>51   | 0        | 0      |

| 23                 | Cl-35<br>Cl-35      | 206<br>206 | 35.8<br>35.8 | 20.0             | 134.5<br>118.6 | 8.7863+04<br>9.9323+04 | 1.1783+07                                | ŏ      | 21         | -40        | ő        | ŏ      |

| 4                  | Cl-35               | 206        | 31.8         | 22.5             | 120.6          | 8.300B+04              | 1.0018+07                                | ŏ      | 28         | 50         | ŏ        | ŏ      |

| 5                  | Cl-35               | 206        | 31.8         | 22.5             | 112.7          | 8.893B+04              | 1.0028+07                                | ō      | 21         | 42         | ĩ        | ō      |

| 6                  | C1-35               | 206        | 31.8         | 22.5             | 131.6          | 7.6143+04              | 1.0028+07                                | ō      | 22         | 78         | ō        | Ō      |

| 7                  | C1-35               | 204        | 28.6         | 25.0             | 150.0          | 7.8148+04              | 1.1793+07                                | ō      | 35         | 5.5        | Ō        | 0      |

|                    | Cl-35               | 206        | 28.6         | 25.0             | 133.4          | 7.5138+04              | 1.0028+07                                | 0      | 23         | 87         | 0        | 0      |

| 9                  | Cl-35               | 206        | 26.0         | 27.5             | 138.5          | 7.230 <b>3</b> +04     | 1.0018+07                                | 0      | 30         | 62         | 0        | 0      |

| 10                 | C1-35               | 206        | 26.0         | 27.5             | 137.1          | 7.3063+04              | 1.0028+07                                | 0      | 34         | 64         | 0        | 0      |

| 11                 | C1-35               | 206        | 23.9         | 30.0             | 183.7          | 6.513B+04              | 1.0018+07                                | 0      | 24         | 83         | 0        | 0      |

| 12                 | C1-35               | 206        | 23.9         | 30.0             | 147.4          | 6.7933+04              | 1.0013+07                                | 0      | 39 ·<br>38 | 76<br>78   | 1        | 0      |

| 13<br>14           | Cl-35<br>Cl-35      | 206<br>206 | 23.9<br>22.0 | 30.0<br>32.5     | 147.9<br>166.5 | 6.7723+04<br>6.0153+04 | 1.002 <b>B</b> +07<br>1.001 <b>B</b> +07 | 0      | 29         | 78         | 1        | o      |

| 15                 | C1-35               | 206        | 22.0         | 32.5             | 161.5          | 6.198B+04              | 1.0013+07                                | ŏ      | 40         |            | ō        | ŏ      |

| 16                 | C1-35               | 206        | 22.0         | 32.5             | 164.2          | 6.0953+04              | 1.0013+07                                | ŏ      | 36         | 76         | ĩ        | ō      |

| 17                 | C1-35               | 206        | 20.4         | 35.0             | 175.8          | 8.695B+04              | 1.0018+07                                | ŏ      | 38         | 115        | 2        | ō      |

| 18                 | C1-35               | 206        | 20.4         | 35.0             | 174.8          | 5.726B+04              | 1.0018+07                                | 0      | 29         | 87         | 1        | 0      |

| 31                 | Ni-58               | 265        | 32.1         | 35.0             | 30.9           | 3.260B+05              | 1.0078+07                                | 0      | 40         | 97         | 4        | 0      |

| 32                 | Ni-58               | 265        | 32.1         | 35.0             | 30.7           | 3.2773+05              | 1.006B+07                                | 0      | 45         | 79         | 3        | 0      |

| 33                 | Ni-58               | 265        | \$2.1        | 35.0             | 31.6           | 3.1823+05              | 1.0063+07                                | 0      | 46         | 78         |          | 0      |

| 34                 | Ni-68               | 265        | 28.1         | 40.0             | 38.0           | 2.6453+05              | 1.0058+07                                | 0      | 45         | 107        | . 12     | 0      |

| 35                 | Ni-58               | 265        | 28.1         | 40.0             | 39.7           | 2.5293+05              | 1.0048+07                                | 0      | 43         | 105        | 13       | 0      |

| 36                 | Ni-58               | 265        | 24.9         | 45.0             | 42.7           | 2.3833+05              | 1.00BB+07                                | 0      | 63         | 146        | 28       | 0      |

| 37                 | NI-58               | 265        | 24.9         | 45.0<br>60.0     | 43.7<br>49.6   | 2.2963+05              | 1.0033+07<br>1.0043+07                   | 0      | 60<br>84   | 134<br>145 | 17<br>19 | 0      |

| 38<br>39           | Ni-58<br>Ni-58      | 265<br>265 | 22.4<br>22.4 | 60.0<br>60.0     | 50.1           | 2.0253+05<br>2.0063+05 | 1.0058+07                                | ŏ      | 75         | 135        | 10       | ŏ      |

| 3¥<br>40           | Ni-58               | 265        | 20.4         | 55.0             | \$5.5          | 1.8093+05              | 1.0048+07                                | ŏ      | 93         | 162        | 45       | 2      |

| 41                 | Ni-58               | 265        | 20.4         | 55.0             | 56.6           | 1.774B+05              | 1.0043+07                                | ŏ      | \$7        | 164        | 40       | ō      |

| 42                 | NI-58               | 265        | 20.4         | 55.0             | 57.6           | 1.743B+05              | 1.004B+07                                | ō      | 44         | 154        | 39       | ĩ      |

| 64                 | 1-127               | 320        | 31.0         | \$5.0            | 87.1           | 2.054B+05              | 1.173B+07                                | ō      | 86         | 162        | 17       | Ō      |

| 65                 | I-127               | 320        | 31.0         | 55.0             | 49.7           | 2.0218+05              | 1.004B+07                                | 0      | 72         | 143        | 12       | 0      |

| 66                 | I-127               | 320        | 28.4         | 60.0             | 58.8           | 1.7058+05              | 1.003B+07                                | 0      | 66         | 154        | 16       | 0      |

| 67                 | 1-127               | 320        | 28.4         | 60.0             | 60.1           | 1.668B+05              | 1.0028+07                                | 0      | 79         | 136        | 25       | 0      |

| 68                 | I-127               | 320        | 26.2         | 65.0             | 67.8           | 1.4793+05              | 1.0038+07                                | 0      | 69         | 154        | 25       | 0      |

| 69                 | I-127               | 320        | 26.2         | 65.0             | 69.3           | 1.4473 +05             | 1.0033+07                                | 0      | 87         | 153        | 26<br>30 | 9<br>0 |

| 70<br>71           | I-127<br>I-127      | 320<br>320 | 24.3<br>24.3 | 70.0<br>70.0     | 74.9<br>74.6   | 1.3393+05<br>1.3453+05 | 1.003B+07<br>1.002B+07                   | U<br>0 | 94<br>111  | 153<br>147 | 30       | 0      |

| 71                 | I-127<br>I-127      | 320        | 24.3         | 75.0             | 100.2          | 9.996B+04              | 1.0028+07                                | ő      | 113        | 159        | 23       | ő      |

| 73                 | I-127               | 320        | 22.7         | 75.0             | 84.3           | 1.1893+05              | 1.0028+07                                | ŏ      | 126        | 175        | 32       | ŏ      |

| 74                 | I-127               | 320        | 21.3         | 80.0             | 78.6           | 1.2768+05              | 1.0033+07                                | ŏ      | 116        | 159        | 33       | ō      |

| 75                 | I-127               | 320        | 21.3         | 80.0             | 75.2           | 1.334B+05              | 1.003B+07                                | ō      | 121        | 160        | 30       | ō      |

| 76                 | I-127               | 320        | 20.0         | 85.0             | 78.9           | 1.2728+05              | 1.0048+07                                | 1      | 136        | 154        | 32       | 0      |

| 77                 | 1-127               | 320        | 20.0         | 85.Ö             | 81.Å           | 1.2408+05              | 1.0098+07                                | 0      | 134        | 162        | 35       | 0      |

| 78                 | I-127               | 320        | 20.0         | 85.0             | \$0.6          | 1.2433+05              | 1.0028+07                                | 0      | 143        | 185        | 35       | 0      |

| 111                | Au-197              | 380        | 27.5         | 85.0             | 19.0           | 6.8913+05              | 1.3093+07                                | 0      | 121        | 186        | 31       | 0      |

| 112                | Au-197              | 350        | 27.5         | 85.0             | 14.6           | 6.9263+05              | 1.0118+07                                | 0      | 86         | 119        | 21       | 0      |

| 113                | An-197              | 350        | 26.0         | 90.0             | 16.1           | 6.2963+05              | 1.0148+07                                | 0      | 96         | 131<br>119 | 23<br>22 | 0      |

| 114                | Au-197<br>Au-197    | 360<br>360 | 26.0<br>24.6 | 90.0<br>95.0     | 15.4<br>15.8   | 6.6113+05<br>6.4243+05 | 1.0185+07<br>1.0185+07                   | ŏ      | 92<br>110  | 122        | 22       | 0      |

| 115<br>116         | Au-197<br>Au-197    | 360        | 24.6         | 95.0             | 16.8           | 6.019B+05              | 1.0118+07                                | ŏ      | 110        | 104        | 15       | 1      |

| 117                | Au-197              | 360        | 24.6         | \$5.0            | 17.6           | 5.768B+05              | 1.0158+07                                | ŏ      | 92         | 128        | 1.       | ő      |

| 118                | Au-197              | 350        | 23.4         | 100.0            | 16.6           | 6.103B+05              | 1.0138+07                                | ō      | 100        | 150        | 20       | 1      |

| 119                | Å a-197             | 350        | 23.4         | 100.0            | 16.6           | 6.095B+05              | 1.0128+07                                | ŏ      | 98         | 145        | 25       | ī      |

| 120                | Au-197              | 350        | 23.4         | 100.0            | 16.4           | 6.170B+05              | 1.012B+07                                | ō      | 98         | 131        | 21       | ō      |

| 121                | Au-197              | 350        | 21.3         | 110.0            | 18.6           | 5.450B+05              | 1.0148+07                                | Ø      | 122        | 135        | 1.       | Ō      |

| 122                | Au-197              | 350        | 21.3         | 110.0            | 18.5           | 5.4663+05              | 1.011B+07                                | 0      | 123        | 158        | 24       | 3      |

| 123                | Au-197              | 350        | 21.3         | 110.0            | 18.6           | 5.476B+05              | 1.013B+07                                | . 0    | .128       | 171        | 33       | 0      |

| 124                | Au-197              | 350        | 19.5         | 120.0            | 20.9           | 4.8303+05              | 1.009B+07                                | 0      | 124        | 146        | 38       | 0      |

| 125                | Au-197              | 350        | 19.5         | 120.0            | 20.3           | 4.9843+05              | 1.0128+07                                | 0      | 138        | 155        | 31       | 0      |

| <sup>1</sup> MeV - | cm <sup>2</sup> /mg |            |              |                  |                |                        |                                          |        |            |            |          |        |

7.2 Proposed Radiation Hard Electronics

### **Task Objective and Deliverables**

- Demonstrate that radiation hard CMOS can be produced in a non-radiation hard commercial foundry.

- Deliver commercially fabricated radiation hard CMOS gate array.

- Demonstrate new gate array technology is as radiation hard as gate arrays produced in special flight foundries.

- Deliver full custom radiation hard VLSI.

#### **Technology Description**

There are three radiation effects to consider:

- 1. Single event upset (SEU). SEU tolerance is achieved through electronic non-resistor feedback in the proposed designs. This technology was developed at the SERC during the past two years.

- 2. Single event latchup (SEL). SEL is achieved through specialized layout techniques, as demonstrated in recent tests.

- 3. Total dose. Total dose tolerance is achieved through IC fabrication. Many commercial foundries produce high total dose levels.

Initial developments have been made that show it is possible to produce radiation hard CMOS in a non-radiation hard foundry. Test cells have demonstrated an LET greater than 120. The proposed development will be to bring this technology to maturity.

#### <u>User Needs and Benefits</u>

The ability to produce radiation hard electronics with commercial foundries would yield:

- 1. One or two orders of magnitude reduction in flight electronics. The reason for this saving is that government electronics would represent only a small part of the product from a given line.

- 2. NASA can design with latest IC technologies to produce faster more dense ICs.

- 3. No government investment is needed to develop new IC processes. The commercial companies will bare this burden within their own programs.

#### <u>Current Status</u>

Initial test cells have been fabricated and tested at Brookhaven National Laboratories. The January 1993 test has shown that the "hard" cells are SEU and SEL immune for LET > 120.

#### State of Technology

The fundamental electronics is understood and has been demonstrated. The SEU technology was developed over the last two years and published in the NASA Symposium on VLSI Design. The SEL technology is a recent discovery and has been demonstrated at BNL in January 1993.

#### **Technical Approach**

- Refabricate and test 1.0 micron CMOS test cells.

- Redesign, fabricate and test 0.8 micron CMOS test cells.

- Repeat test with second commercial foundry.

- Design full custom chip. Likely candidates are a 1024 channel correlator or the RS16 decoder.

- Design gate array hardware.

- Design gate array software to interface with Mentor tools.

- Implement gate array designs to compare with UTMC/Honeywell designs. Likely candidates are the Reed Solomon encoder and the flight data compression chip.

#### **Potential Commercial Benefits**

The commercial benefits are primarily to NASA where low cost high performance VLSI can be obtained with commercial foundries.

| Milest | ones | 3        |                                 |

|--------|------|----------|---------------------------------|

| Level  | No   | Date     | Planned Accomplishment          |

| 3      | 1    | 8/01/93  | 1.0 micron test cells           |

| 3      | 2    | 11/01/93 | 0.8 micron test cells           |

| 3      | 3    | 3/15/94  | Gate Array Hardware             |

| 3      | 4    | 10/30/94 | Radiation testing of gate array |

| 4      | 5    | 3/15/95  | Full custom design complete     |

| 6      | 6    | 6/15/95  | CAD software complete           |

| 6      | 7    | 6/15/95  | Gate array designs complete     |

### 7.3 Flight Lossless Data Compression

#### Jack Venbrux

#### Abstract

This work will complement the activity being conducted in current research. A new architecture is being formulated to implement a new lossless data compression algorithm. While simulations and theoretical deductions can verify the results of the new work, the final proof of concept will be the fabrication and radiation testing of a space qualifiable component. Electronic protection against errors due to single event upsets (SEUs) is critical to the performance of the lossless compression algorithm since a single bit error can invalidate a large amount of data.

The new investigation will examine the impact of space radiation impacts on the VLSI architecture that realizes a powerful lossless data compression algorithm. The VLSI architecture that is being designed under current research is proposed to be fabricated and tested. The results of the radiation testing will demonstrate the viability of the new architecture for space applications.

#### **Lossless Data Compression**

The major objective for designing and fabricating the chip set is to provide real time lossless compression for satellite imagery. In order to compress satellite imagery it must adapt rapidly to changing scene statistics and compress image data over a wide entropy range.

The Rice algorithm is a lossless compression method that is rapidly adaptive and efficient over a wide range of entropy conditions. The structure of the algorithm can best be understood through the following argument. Assume that a particular encoder has, for example, 11 different Huffman codes to choose from. Each Huffman code is designed for a particular entropy range. The first codebook might be designed for an expected codeword length of 2 bits, while the next one might be designed for an expected codeword length of 3 bits, and so on in integer increments of one bit. By applying each of the 11 codebooks to the same data block of size J, and then choosing the codebook that produced the best compression would allow the coder to cover a wide entropy range: approximately 1.5 bits through 12.5 bits. By deciding which coder was the winner on a block by block basis, the coder would be adaptive to changes in data entropy.

One of Robert F. Rice's accomplishments was develop a compression algorithm that requires no codebooks [15], yet provides equivalent performance to the multiple Huffman codebook approach just described. The equivalence is only true for sources that have a Laplacian distribution. Fortunately, for many types of sampled data, especially imagery, the output from DPCM can be well modeled as a Laplacian distribution. The Rice algorithm has been shown mathematically to provide equivalent performance to using multiple, parallel Huffman codes, this was supported by extensive simulations [16]. An intuitive feel for this equivalence can be obtained by understanding two major components of the algorithm: a comma code Rice calls the Fundamental Sequence (FS), and sample splitting.

For low entropy data, direct coding of the data, without sample splitting, would pro-

duce the fewest number of coded bits. Higher entropy data will be more efficiently coded by using sample splitting. This reaffirms the assumption that as entropy increases the randomness (or information content) in the k least-significant bits prohibits compression. Therefore, using successive split bits combined with FS coding is equivalent to using Huffman codebooks that are designed for successive integer steps in entropy. Due to the simple structure of the FS code, however, no actual codebook is necessary for each code option.

### Encoder

The encoder has a fully pipelined architecture. After 64 clock cycles, data is available for output. It can continuously accept new data and process every sample in one clock cycle.

The chip architecture and the generic Rice architecture differ in three ways. First, on the chip, the DPCM and mapper functions were implemented in one hardware block. Second, the winner select section was broken up into two sections for the chip: the bit counts section and the winner select section. The bit counts section is the largest single block on the chip. It calculates the number of bits that will be required to code the input block (16 samples) for each of the 12 coding options. The winner select block selects which of the options will produce the smallest number of coded bits and also performs calculations needed for the coding sections. The final difference between the VLSI implementation and the generic architecture is sharing of hardware among 12 coding options: only 2 hardware blocks are necessary (FS and K/Default). Control is distributed throughout the chip, but is mainly found in the input control section and in the two coding blocks.

The data formatter concatenates the split bits with FS coded bits. It also prepends the 4 ID bits that specify which code option performed the coding. The output of the chip is a 16 bit parallel output with an asserted signal to flag the presence of data. The design reflects the requirements from NASA to output a contiguous block of compressed data that begins with a header word to specify the length of the block. An external packetizer should be used for concatenating the specified number of blocks to form a large data packet.

### **Proposed Research**

The current encoder compression chip was not designed with the space environment in mind. Specifically, it is subject to negative impacts due to Single Event Upsets (SEU). It is proposed to perform the following:

- Analyze the current architecture to identify impacts of SEUs on the current architecture and identify the critical areas.

- Identify solutions to provide SEU tolerance. Potential solutions involve the following:

- Selecting an IC foundry that is capable of producing flight qualified parts.

- Design all logic in SEU tolerant electronics.

26

- Design architecture with redundancy and necessary control circuitry such that the total system is tolerant of SEUs.

#### Enhancements

Features that the new architecture will have are:

- Low Entropy Improvements: Include a zero-run and a low-entropy option to yield improved performance for low entropy data.

- More Efficient Coding at Small Quantizations: Provide an optional 3-bit ID to improve coding performance for data that is quantized to less than 9-bits per sample. (The present design uses a fixed 4-bit ID independent of quantization.)

- Block Size Options: Besides the present 16 samples per block, allow coding an 8 sample block. This should allow more efficient entropy coding and rate control for coding outputs from lossy algorithms such as the frequency bins of a Discrete Cosine Transform.

- Study Impact of Decision Regions: Using decision regions is a method of choosing the winning code option using approximations instead of having to use exact counts. The present design uses exact counts which results in maximum performance but at a cost of using more chip area than if decision regions were used. This portion of the study would help answer the question, "What is the performance penalty for using decision regions versus using exact counts?"

### Proposal

The chief goal of this study will focus on the following elements:

- 1. Have the VLSI test structure which implements lossless data compression with SEU immune electronics fabricated.

- 2. Pursue functional and electrical testing over the space radiation range to carefully analyize any performance impacts. The new cells with SEU immunity must not have significant impact in performance.

- 3. Perform radiation testing to measure the effects of total dose immunity and SEU's.

<sup>°</sup>The current status is:

- A lossless algorithm with enhanced features to cover a larger entropy range has been proposed and tested for a large variety of images.

- A VLSI architecture is being designed with flight electronics that possess SEU immunity and is latchup free.

#### USE vs USES

Following are the differences between the flight and commercial foundry data compression chips. Some of the larger feature changes include and increased entropy range and prediction modes. USES is able to perform 2 dimensional and multispectral data compression.

| Metric           | USE                     | USES                          |

|------------------|-------------------------|-------------------------------|

| Foundry Type     | Commercial              | RAD Hard, Level S parts       |

| Technology       | 1.0uM custom            | 1.2 uM Gate Array             |

| Package Type     | 84 Pin PLCC             | 144 Pin flat-pack             |

| Quantization     | 4-14                    | 4-15 bits/sample              |

| Entropy Coverage | 1.5-12.5                | 0-14.5 bits/sample            |

| Prediction Modes | near. neighbor+external | also 2D, Multi-spectral       |

| MSamples/Sec     | 25 at MIL spec          | est. 18 at MIL spec           |

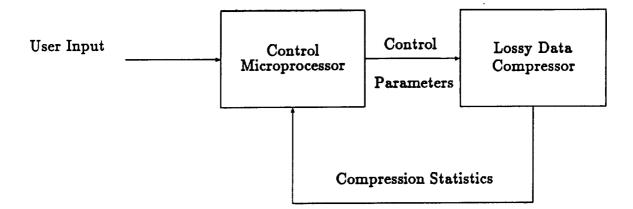

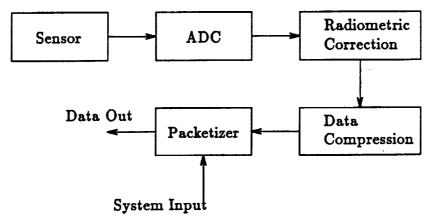

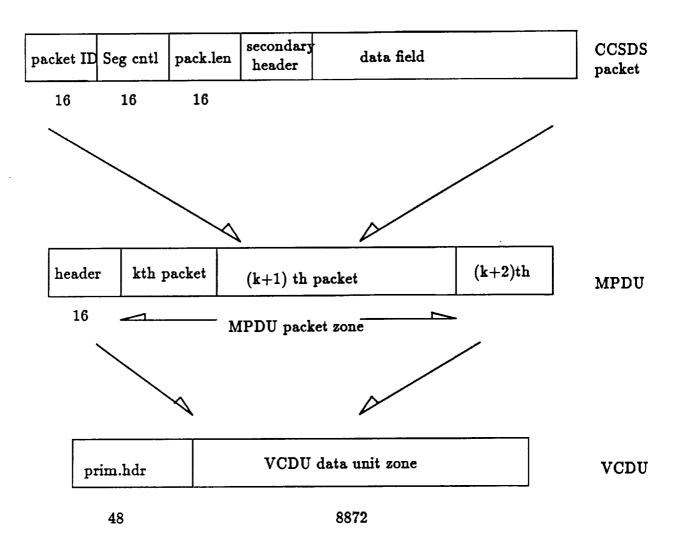

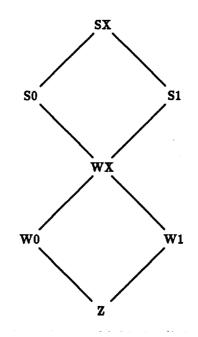

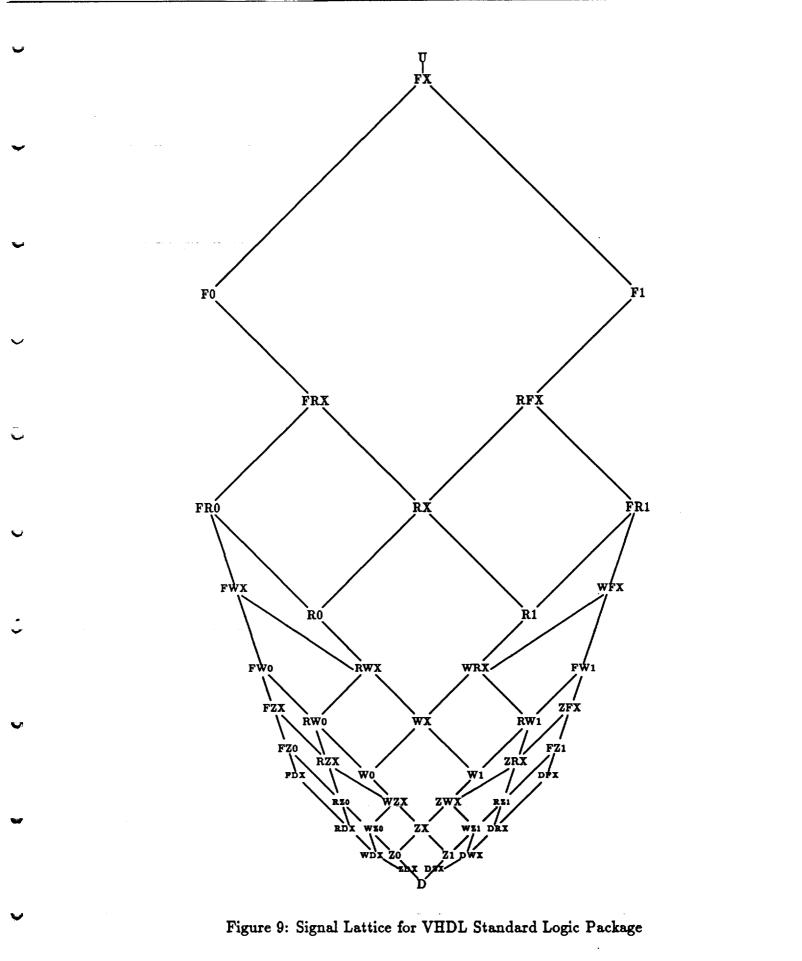

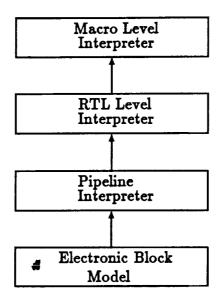

| Variable ID      | no, fixed 4bit          | 3bit ID if 8bits or less      |