NASA-CR-194591 NAGW-3293

# 4th NASA Symposium on VLSI Design

University of Idaho Moscow, Idaho

October 29-30, 1992

(NASA-CR-194591) THE 1992 4TH NASA SERC SYMPOSIUM ON VLSI DESIGN (Idaho Univ.) 422 p

N94-21694 --THRU--N94-21735 Unclas

G3/33 0191442

Welcome to the fourth annual NASA Symposium on VLSI Design, co-sponsored by the IEEE. Each year this symposium is organized by the NASA Space Engineering Research Center (SERC) at the University of Idaho and is held in conjunction with a quarterly meeting of the NASA Data System Technology Working Group (DSTWG). One task of the DSTWG is to develop new electronic technologies that will meet next generation electronic data system needs. The symposium provides insights into developments in VLSI and digital systems which can be used to increase data systems performance.

The NASA SERC is proud to offer, at its fourth symposium on VLSI design, presentations by an outstanding set of individuals from national laboratories, the electronics industry and universities. These speakers share insights into next generation advances that will serve as a basis for future VLSI design.

In spite of the present economic conditions, interest in the conference has remained steady with 42 papers in 10 categories included in this years proceedings. National Laboratories are represented by Rockwell International Science Center, NCCOSC Research and Development, Jet Propulsion Laboratory and the Johns Hopkins University Applied Physics Laboratory. Private industry is represented by Texas Instruments, Advanced Hardware Architectures and Spacebourne Inc. Universities are represented by Cornell University, Utah State University, University of Alabama, Washington State University, University of Calgary, University of Southwestern Louisiana, Nanyang Technological University, Syracuse University, Concordia University, University of California at Davis and Irving, California State University at Fullerton Colorado State University, University of Toledo, University of Peradeniya, University of New Mexico and the University of Idaho. In addition we are happy to welcome a number of papers presented by international authors.

There are individuals whose assistance was critical to the success of this symposium. Barbara Martin worked long hours to assemble the conference proceedings. The efforts of these professionals were vital and are greatly appreciated. I hope you enjoy your stay in Coeur d'Alene, Idaho.

Sterling R. Whitaker

#### Session 1 – Featured Presentations I

Applications of Correlator Chips in Radio Science

Jon Hagen

Single Event Phenomena: Testing and Prediction

James D. Kinnison

Heterojunction Bipolar Transistor Technology for Data Acquisition and

Communication

# Session 2 - VLSI Architectures

Chairman: Kelly Cameron

K.C. Wang and D.T. Cheung

Chairman: Gary Maki

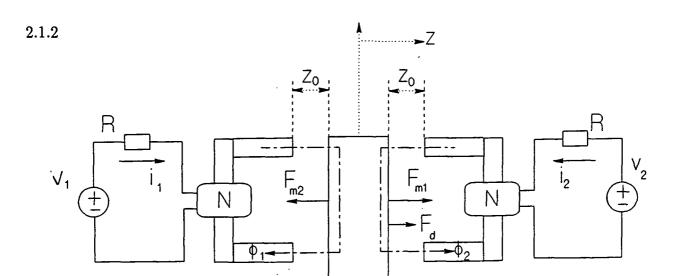

A New Eddy Current Model for Magnetic Bearing Control System Design2.1

Joseph J. Feeley and Daniel Ahlstrom

Design of a New Squaring Function for the Viterbi Algorithm

2.2

Arai Eshraghi, Terri Fiez, Kel Winters and Thomas Fischer

A 20MHz CMOS Reorder Buffer for a Superscalar Microprocessor 2.3 John Lenell, Steve Wallace and Nader Bagherzadeh

Analog/Digital pH Meter System I.C. 2.4

Paul Vincent and Jea Park

An 18 Bit 50 kHz ADC for Low Earth Orbit 2.5

Donald C. Thelen

NASA SERC Digital Correlator Projects

John Canaris

VLSI Design Bruce Offord 4.2

4.3

# Session 3 – Design Synthesis

| Chairman: James Frenzel                                                                                                                   |     |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

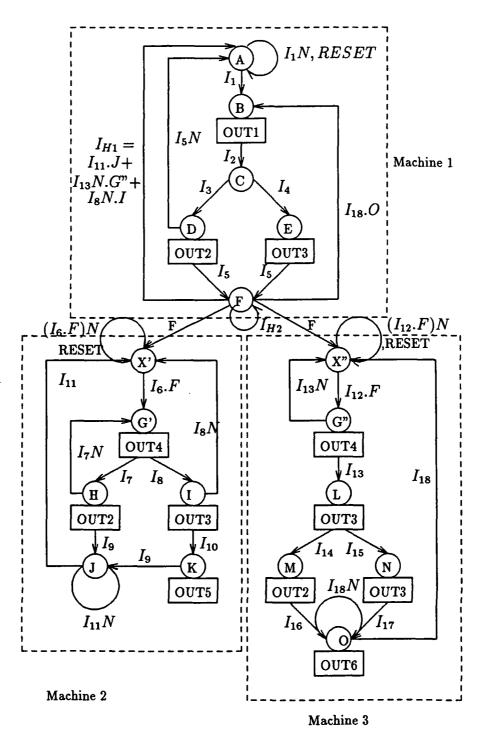

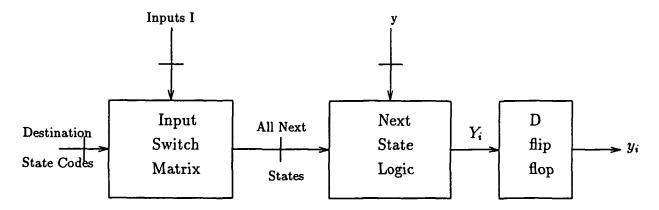

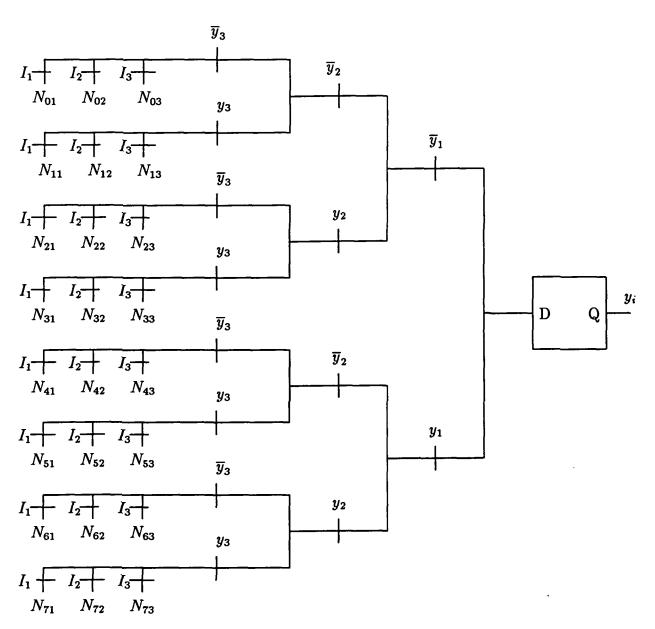

| On the Decomposition of Synchronous State Machines Using Sequence<br>Invariant State Machines<br>K. Hebbalalu, S. Whitaker and K. Cameron | 3.1 |

| A Heuristic-Based Scheduling Algorithm for High Level Synthesis<br>Gulam Mohamed, Tan Han Ngee and Chng Chew Lye                          | 3.2 |

| Evaluation of Floating Point Sum or Difference of Products in Carry<br>Save Domain<br>Abdul Wahab, S.S. Erdogan and A.B. Premkumar        | 3.3 |

| A Statistical-based Scheduling Algorithm in Automated Data Path<br>Synthesis<br>Byung Wook Jeon and Chidchanok Lursinsap                  | 3.4 |

| Micro-rollback and Self-recovery Synthesis Byung Wook Jeon and Chidchanok Lursinsap                                                       | 3.5 |

| Session 4 – Featured Presentations II                                                                                                     |     |

| Chairman: Sterling Whitaker                                                                                                               |     |

| System Development Using VLSI for Space Applications<br>T.R. McKnight, D.E. Rodriguez, J.C. Barnett, and C.R. Valverde                    | 4.1 |

Fully Depleted Silicon-on-Sapphire and Its Application to Advanced

# Session 5 – VLSI Design

| Chairman: Kel Winters                                                                                                                                   |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Design and Test of Field Programmable Gate Arrays in Space Applications  Priscilla L. McKerracher, Russel P. Cain, Jon C. Barnett, William S. Green and | 5.1 |

| James D. Kinnison                                                                                                                                       |     |

| Defect-Sensitivity Analysis of an SEU Immune CMOS Logic Family<br>Eric H. Ingermann and James F. Frenzel                                                | 5.2 |

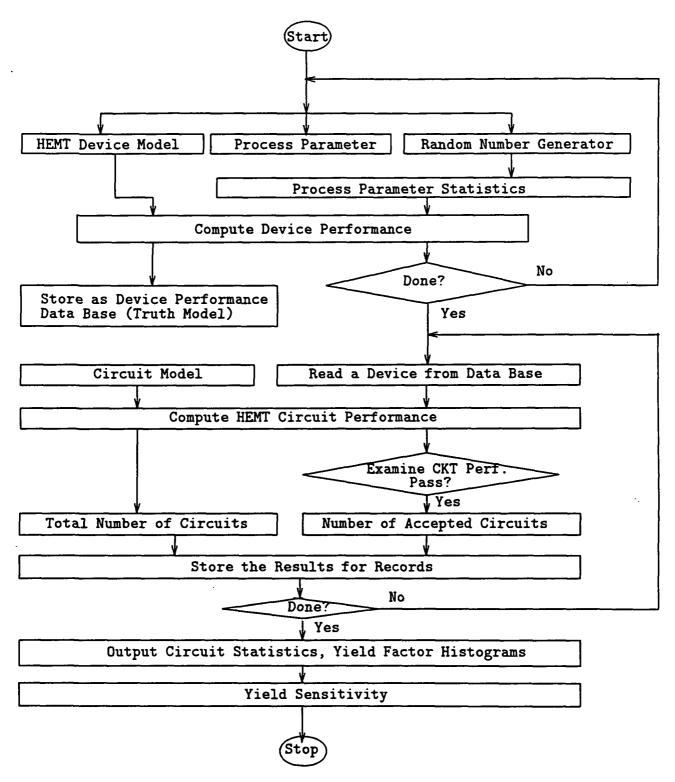

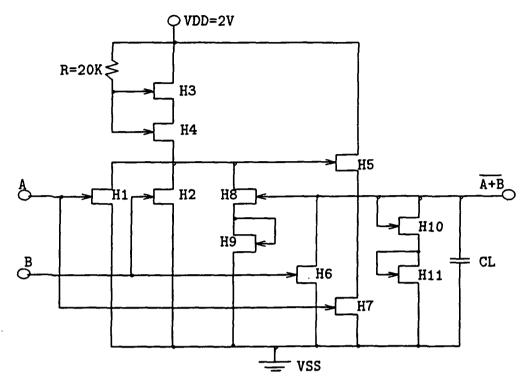

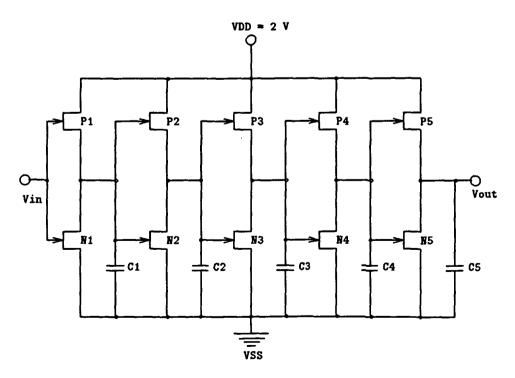

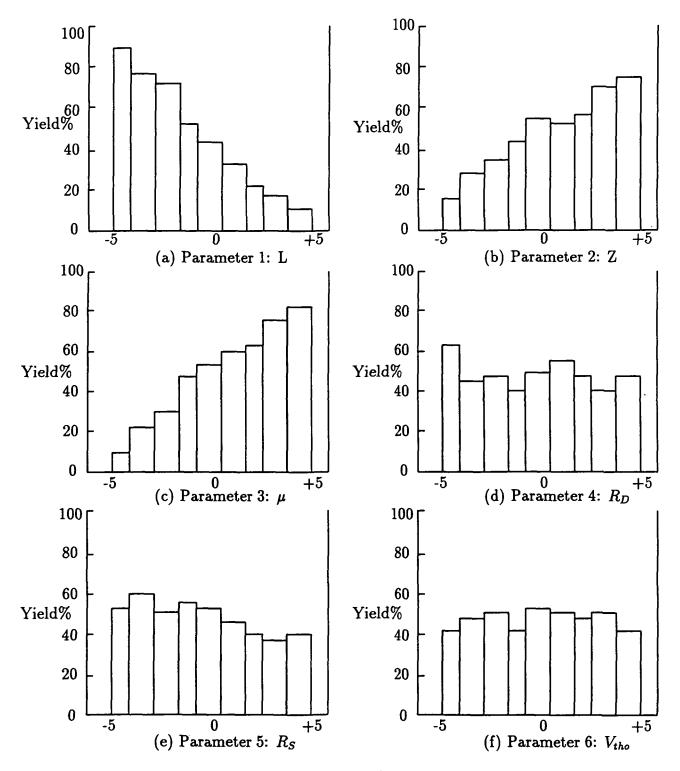

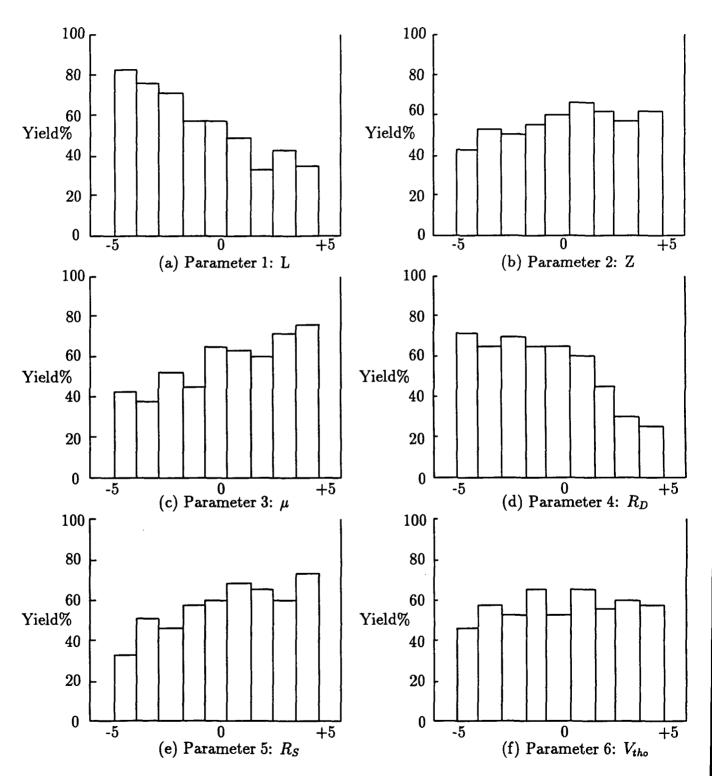

| Dimension Scaling Effects on the Yield Sensitivity of HEMT Digital<br>Circuits<br>Jogendra Sarker and John Purviance                                    | 5.3 |

| Links between N-Modular Redundancy and the Theory of Error-Correcting Codes V. Bobin, S. Whitaker, and G. Maki                                          | 5.4 |

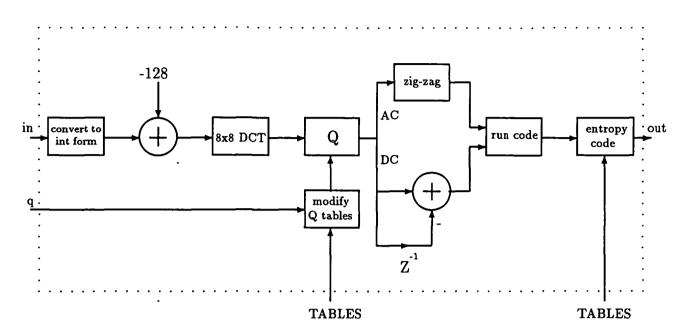

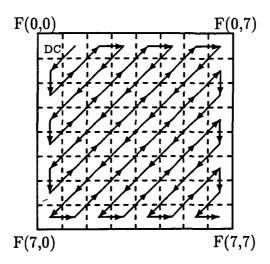

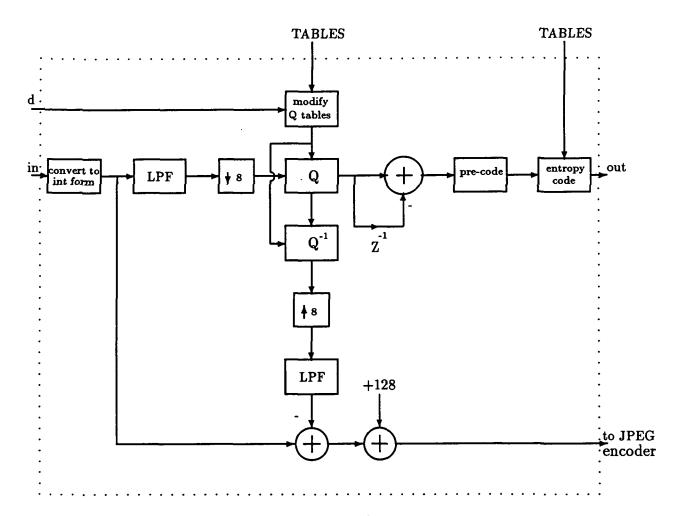

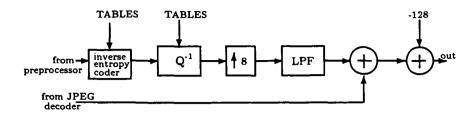

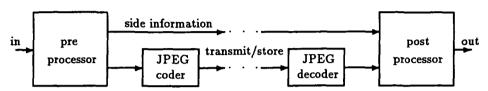

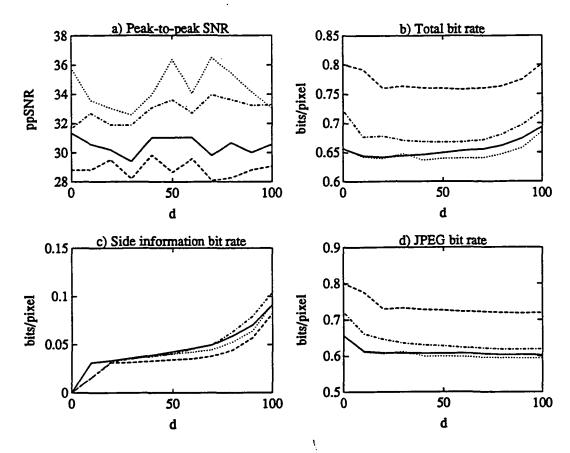

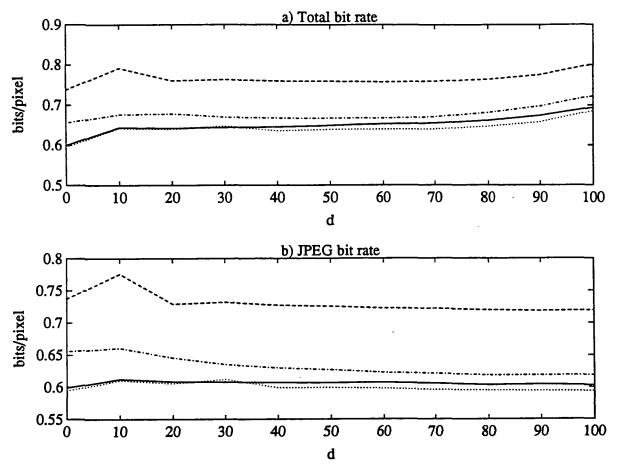

| Reduction of Blocking Effects for the JPEG Baseline Image Compression Standard Gregary C. Zweigle and Roberto Bamberger                                 | 5.5 |

| Session 6 – Verification                                                                                                                                |     |

| Chairman: Phil Windley A Novel Visual Hardware Behavioral Language Xueqin Li and H.D. Cheng                                                             | 6.1 |

| A Mechanized Process Algebra for Verification of Device Synchroniza-<br>tion Process<br>E. Thomas Schubert                                              | 6.2 |

| HDL to Verification Logic Translator Jody W. Gambles and Phillip J. Windley                                                                             | 6.3 |

|                                                                                                                                                         |     |

| A Simple Modern Correctness Condition for a Space-Based High-<br>Performance Microprocessor<br>David K. Probst and Hon F. Li                            | 6.4 |

# Session 7 – Tools and Methods

| Chairman: Jonathan Gibson                                                                                                      |     |

|--------------------------------------------------------------------------------------------------------------------------------|-----|

| A Mean Field Neural Network for Hierarchical Module Placement<br>M. Kemal Unaltuna and Vijay Pitchumani                        | 7.1 |

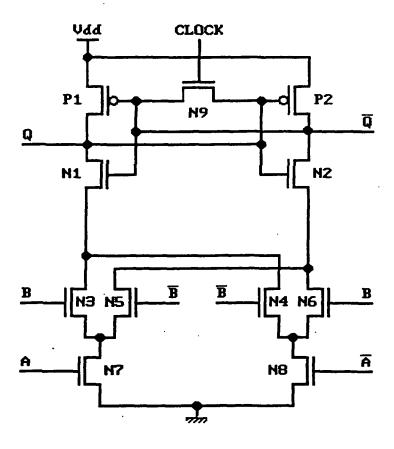

| Detection of Feed-Through Faults in CMOS Storage Elements<br>Waleed K Al-Assadi. Y. Malaiya and A. Jayasumana                  | 7.2 |

| Schematic Driven Layout of Reed Solomon Encoders<br>Kari Arave, John Canaris, Lowell Miles and Sterling Whitaker               | 7.3 |

| Interpolative Modeling of GaAs FET S-parameter Data Bases for Use in Monte Carlo Simulation Lowell Campbell and John Purviance | 7.4 |

| Teaching VLSI in High School Larry Volkening                                                                                   | 7.5 |

| Session 8 – VLSI Design                                                                                                        |     |

| Chairman: Jody Gambles                                                                                                         |     |

| Bit-Systolic Arithmetic Arrays Using Dynamic Differential Gallium Arsenide Circuits Grant Beagles, Kel Winters and A.G. Eldin  | 8.1 |

| A VLSI Implementation of DCT Using Pass Transistor Technology<br>S. Kamath, Doug Lynn and Sterling Whitaker                    | 8.2 |

| A High Speed CMOS A/D Converter Don R. Wiseman and Sterling Whitaker                                                           | 8.3 |

|                                                                                                                                |     |

| Behavior of Faulty Double BJT BiCMOS Logic Gates<br>Sankaran M. Menon, Yashwant K. Malaiya and Anura P. Jayasumana             | 8.4 |

# Session 9 – Cache Architectures

| Chairman: Joseph Feeley                                                                                                      |      |

|------------------------------------------------------------------------------------------------------------------------------|------|

| A DRAM Compiler Algorithm for High Performance VLSI Embedded Memories A.G. Eldin                                             | 9.1  |

| A Novel Cache Mechanism J.A. Gunawardena                                                                                     | 9.2  |

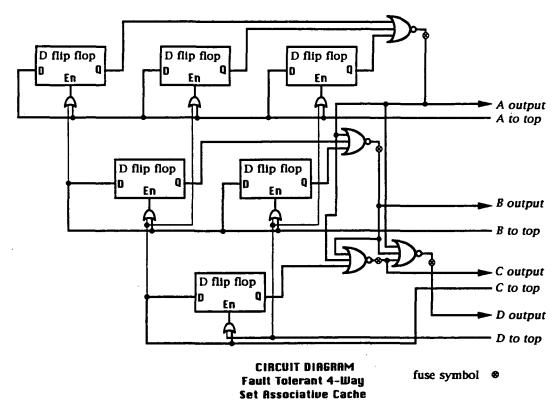

| A Set-Associative, Fault-Tolerant Cache Design Dan Lamet and James F. Frenzel                                                | 9.3  |

| Session 10 – Correlators                                                                                                     |      |

| Chairman: John Canaris                                                                                                       |      |

| A 1 GHZ Sample Rate, 256-Channel, 1-Bit Quantization, CMOS, Digital Correlator Chip C. Timoc, T. Tran and J. Wongso          | 10.1 |

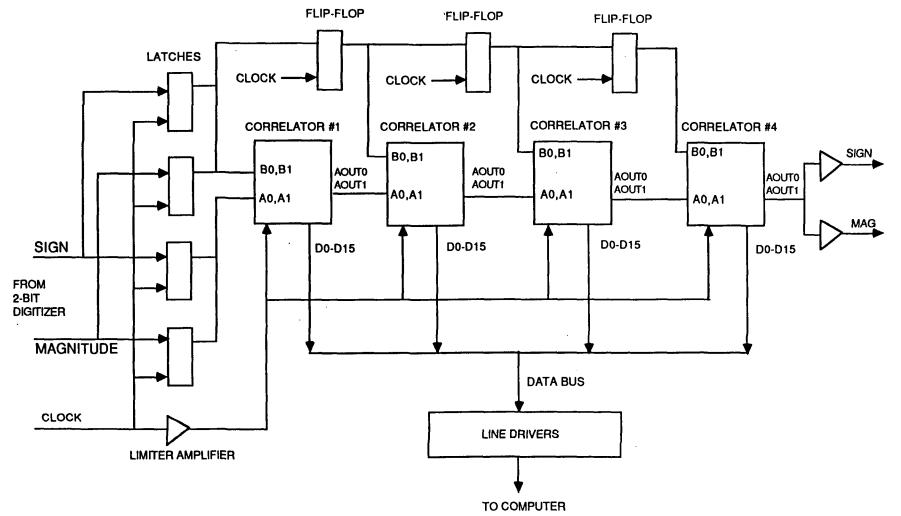

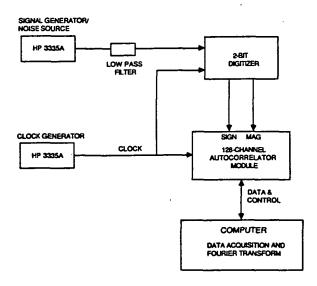

| Low Power, CMOS Digital Autocorrelator Spectrometer for Space-<br>bourne Applications<br>Kumar Chandra and William J. Wilson | 10.2 |

| A Real Time Correlator Using Distributed Arithmetic Principles A. Benjamin Premkumar and T. Srikanthan                       | 10.3 |

| Low Energy CMOS for Space Applications Ramesh Panwar and Leon Alkalaj                                                        | 10.4 |

# List of Authors

| All-4              | I · II           |

|--------------------|------------------|

|                    | Li, H            |

|                    | Li, Xueqin       |

| Alkalaj, L         | Lursinsap, C     |

| Arave, K           | 3.5              |

| Bagherzadeh, N 2.3 | Lye, C 3.2       |

| Bamberger, R       | Lynn, D8.2       |

| Barnett, J4.1      | Malaiya, Y       |

| 5.1                | 8.4              |

| Beagles, G8.1      | Maki, G5.4       |

| Bobin, V5.4        | McKerracher, P   |

| Cain, R 5.1        | McKnight, T 4.1  |

| Cameron, K         | Menon, S8.4      |

| Campbell, L        | Miles, L         |

| Canaris, J         | Mohamed, G       |

|                    | Ngee, T 3.2      |

| Chandra, K         | Offord, B4.3     |

| Cheng, H           | Panwar, R        |

| Cheung, D          | Park, J          |

| Eldin, A           | Pitchumani, V    |

|                    | Premkumar, A     |

| Erdogan, S         |                  |

| Eshraghi, A 2.2    | Probst, D 6.4    |

| Feeley, J          | Purviance, J     |

| Fiez, T            |                  |

| Fischer, T         | Rodriguez, D 4.1 |

|                    |                  |

| Frenzel, J         | Sarker, J        |

| 9.3                | Schubert, E 6.2  |

| Gambles, J         | Shamanna, M      |

| Green, W           | Srikanthan, T    |

| Gunawardena, J     | Tran, T          |

| Hagen, J           | Thelen, D        |

| Hebbalalu, K       | Timoc, C10.1     |

| Ingermann, E       | Unaltuna, M      |

| Jayasumana, J7.2   | Valverde, C4.1   |

| 8.4                | Volkening, L     |

| Jeon, B3.4         | Vincent, P       |

| 3.5                | Wahab, A         |

| Kamath, S 8.2      | Wang, K          |

| Kinnison, J        | G.               |

| •                  | •                |

|                    | •                |

| •                  |                  |

|                    | •                |

| Whitaker, S 8.3 |

|-----------------|

|                 |

| Wilson, W       |

| Windley, P      |

|                 |

| Winters, K      |

| 8.1             |

| Wiseman, D8.3   |

| Wongso, J10.1   |

| Zweigle, G      |

# Session 1 Featured Presentations I

Chairman: Gary Maki

# Applications of Correlator Chips in Radio Science

Jon B. Hagen Cornell University NAIC Lab 124 124 Maple Ave Ithaca NY 14850 607-255-5274

Abstract - Spectral line observations in radio astronomy require simultaneous power estimation in many (often hundreds to thousands) of frequency bins. Digital autocorrelation spectrometers, which appeared thirty years ago, are now being implemented in VLSI. The same architecture can be used to implement transversal digital filters. This was done at the Arecibo Observatory for pulse compression in radar observations of Venus.

#### 1 Introduction

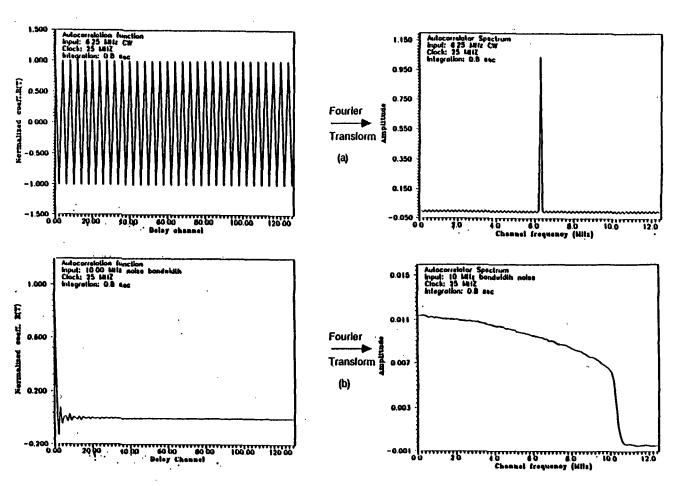

This paper reviews applications and implementations of the digital correlator, a signal processor long used for radio spectrometry and increasingly used for digital filtering. Most radio engineers intuitively define points on the power spectrum (power density v.s. frequency) of a signal to be the average voltages from a set of square-law detectors following a bank of bandpass filters. A formal definition is provided by the Wiener-Khinchin theorem: the power spectrum of a signal is the Fourier transform of the signal's autocorrelation function (ACF). In autocorrelation spectrometry the intensive on-line averaging is done in a correlator; the Fourier transform is a one-time operation done prior to further data analysis. (Occasionally experimental ACFs are compared to theoretical ACFs without ever transforming from the time domain to the frequency domain).

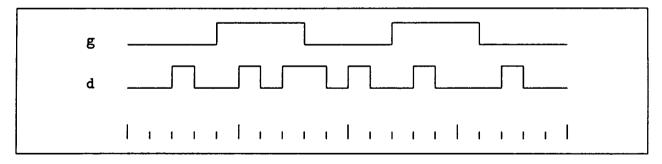

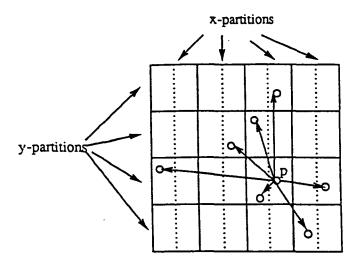

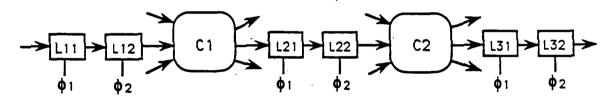

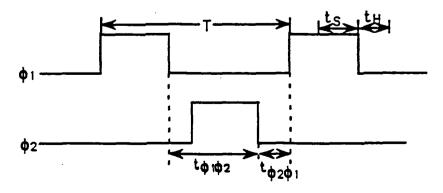

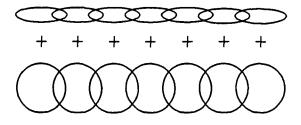

#### 2 Basic Correlator Architecture

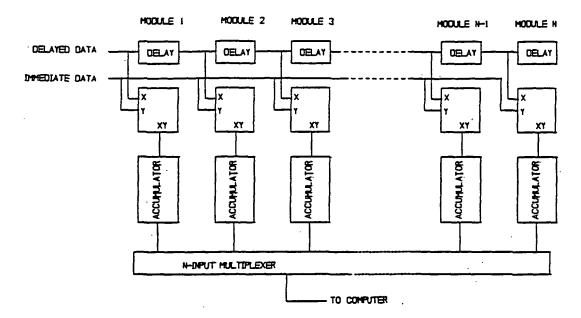

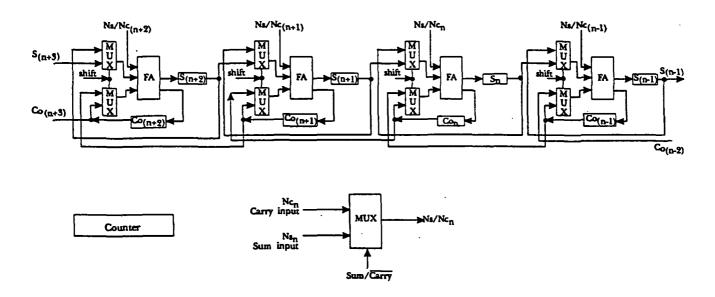

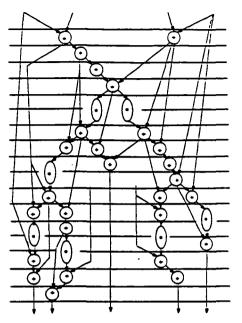

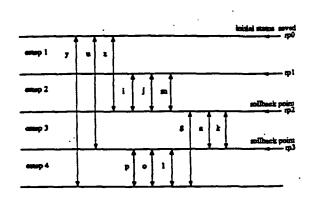

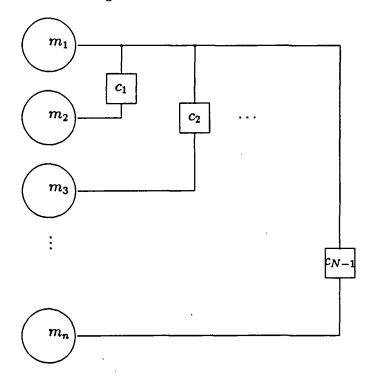

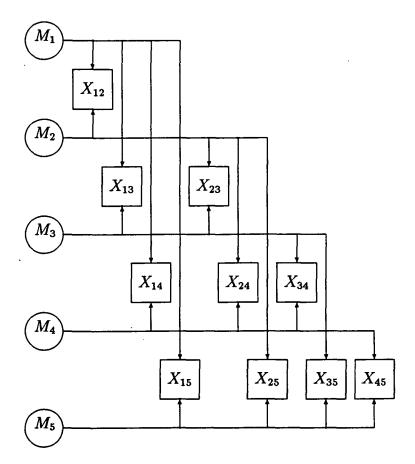

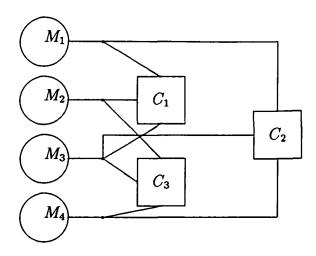

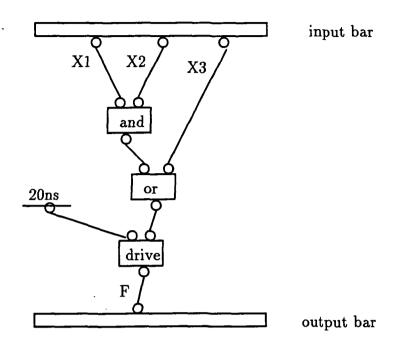

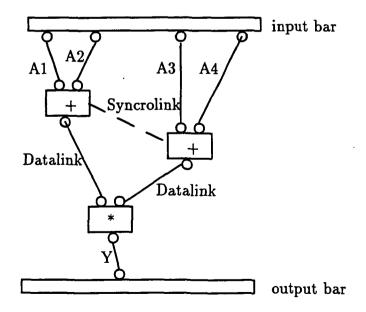

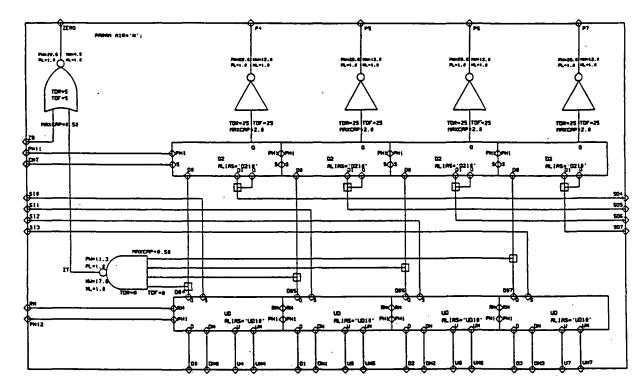

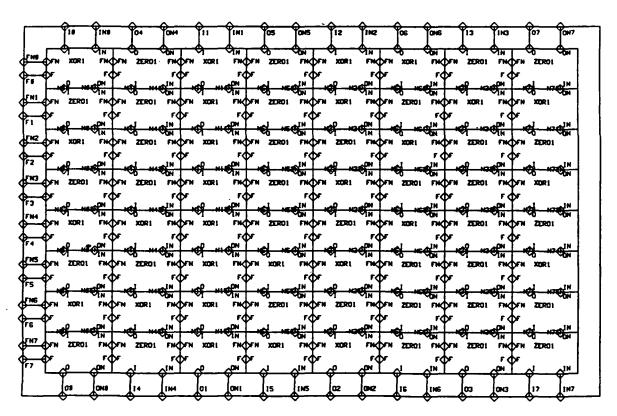

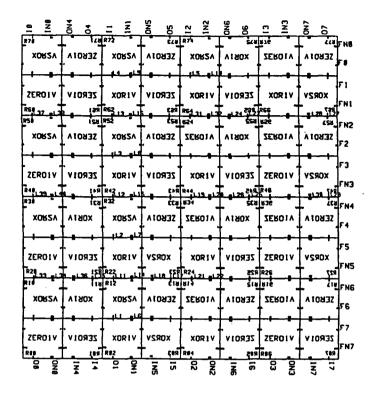

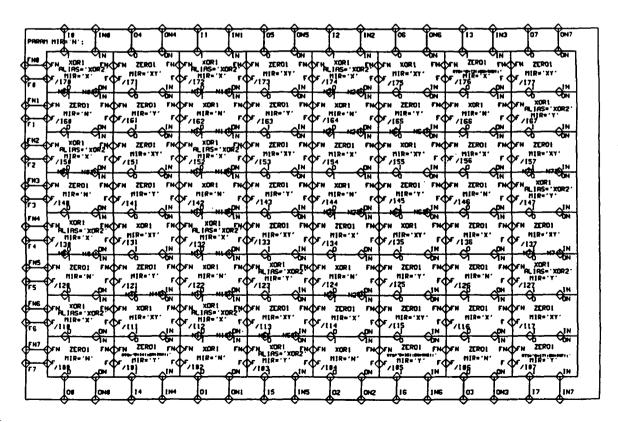

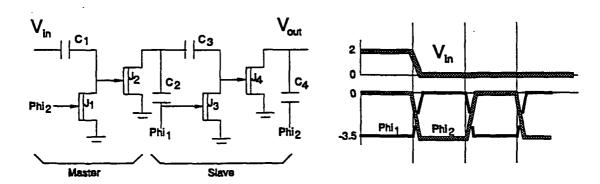

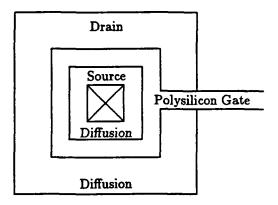

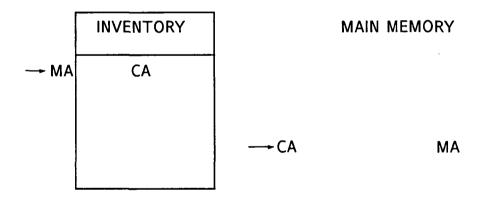

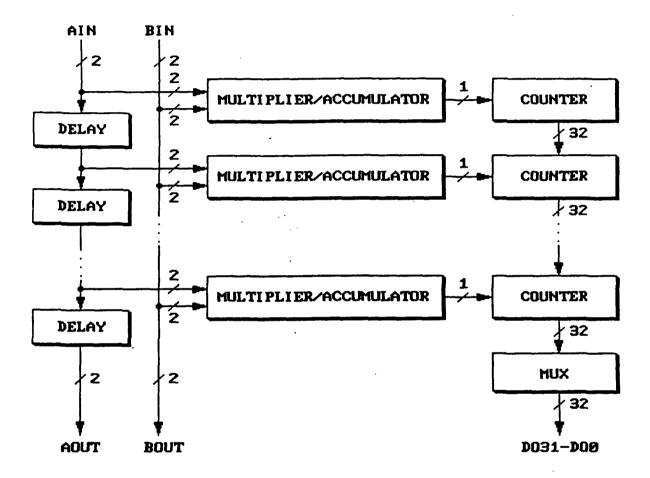

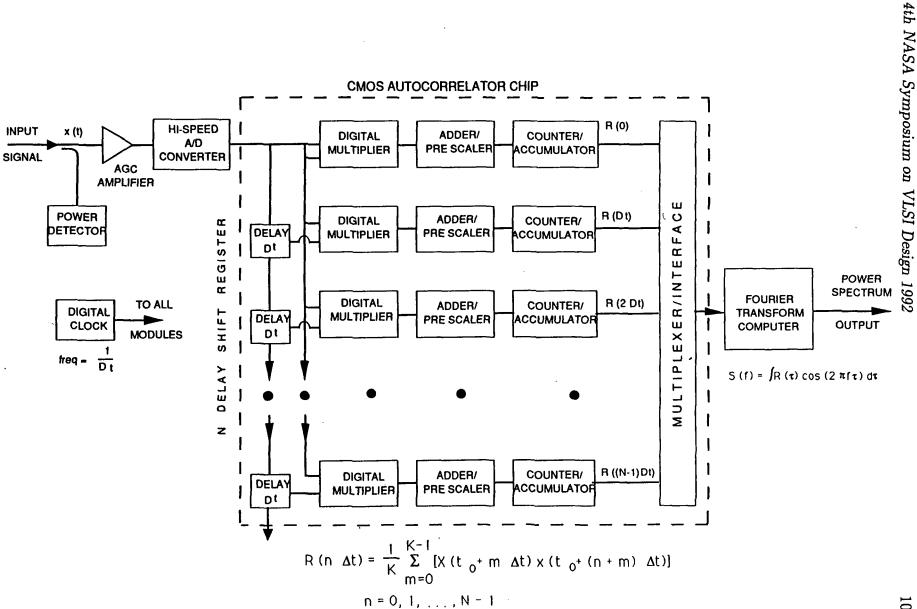

The architecture in question is extremely simple; the chip contains N identical arithmetic modules or "lags" which operate in parallel, independently forming products from two data streams and accumulating the sum of these products. One of the data streams, the "immediate" data is common to every lag. The other data stream, the "delayed" data, is supplied from successive taps of a shift register contained on the chip. Each clock pulse advances the shift register data and adds the new lagged products to the contents of each accumulator. Each module thus calculates a point on the autocorrelation function, i.e. the average product of the signal voltage at time T and the signal voltage at time (t-T). An output multiplexer provides access to the individual accumulators. The basic block diagram is shown in Figure 1.

To measure a power spectrum via the autocorrelation function, the immediate and the delayed inputs are both tied to the same signal (the undetected baseband output voltage of the radio astronomy receiver). This type of correlator was introduced in radio astronomy by

Figure 1: Basic Correlator Architecture

Sander Weinreb (1) in 1963 and has been the workhorse for spectral analysis. It is discussed further in Section 4 after a review of the basic principles of spectrometry.

# 3 Spectrometry in Radio Astronomy

Though a radio astronomer occasionally deals with objects that are sources of spectrally flat white noise, the more interesting and challenging sources have considerable spectral structure. Such sources include molecular clouds with emission or absorption lines, natural masers, and dispersed pulses from rapidly rotating neutron stars (pulsars). The spectrum can have enough structure to warrant hundreds to thousands of points of resolution. Each point requires its own radiometer, i.e. bandpass filter plus square-law detector or an equivalent such as one module of a correlator. This kind of multiplex spectrometer (meaning that all points are measured simultaneously) is always necessary in radio astronomy because the received signals are noiselike random processes and time averaging is needed at each filter/detector or correlator module. If the required accuracy is, say, 1% or one part in one hundred, it is necessary to average about 1002 or 10,000 samples of V<sup>2</sup>. Sampling theory shows that the time needed to gather the required number of independent samples will be inversely proportional to the bandwidth. These radiometry considerations show why an ordinary laboratory spectrum analyzer - a scanning receiver with a single bandpass filter - is not suitable for this work as it would increase the required observation time in proportion to the number of frequency channels. Such increases in observing time are simply not available; radio astronomers are usually trying to dig small spectral features out of background noise (the sum of cosmic noise, atmospheric noise, antenna noise, and amplifier noise) and, even with multiplex spectrometers, integration times run to dozens or even hundreds of hours since the signal-to-noise ratios (before averaging) are typically in the -30 to -60 dB range.

# 4 Digital Correlators

The basic correlator module can be implemented partly or wholly in analog circuitry but all-digital implementations have been favored from the start. Autocorrelation is not the only way to do digital spectrometry; the Fast Fourier Transform (FFT), familiar since the late sixties, is, in principle, a more appealing algorithm since it ultimately must be more efficient - arithmetic operations are done at a rate proportional to N log(N) rather than N<sup>2</sup> where N is the number of points on the spectrum. Surely, for N large enough, the FFT will be better. Yet for N smaller than, say, 10,000, and at sampling rates, i.e. bandwidths, high enough that the digital circuitry is running at full speed, it seems that the correlator architecture has two advantages.

The first advantage comes from the simplicity of the architecture. The modules run independently. Apart from the shift register that distributes the delayed data, there are no data interconnections between modules. The correlator is easily expandable. To get more points on the spectrum one cascades more of the same modules. Conversely, a machine with many modules can be subdivided into several smaller correlators which can independently analyze several different signals. The simplicity of the basic module thus provides flexibility at the system level.

The second advantage is that correlators can use very coarse quantization of the input signal. Instead of digitizing the signal with 8 to 16 bits, as is often required in digital signal processing, it has been common to digitize to only one bit; the amplitude is ignored and the signal's polarity determines whether the value of the bit is a 1 or a -1. As one would expect, such a distorted representation of the signal produces a distorted version of the desired correlation function, but, as long as the signal is a Gaussian random process, the distortion can be removed perfectly after the integration is finished. The correction procedure is very simple: divide all the points (lags) by the first point (zero lag), multiply them by  $\pi/2$  radians, and then replace them by their trigonometric sines. This relationship between the correlation function of the input signal and the correlation of the 1-bit representation was first described by J.H. VanVleck in a wartime study of overmodulation (clipping) for radar jammers.

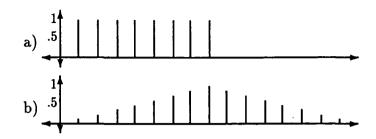

Obviously 1-bit arithmetic greatly simplifies the multipliers and accumulators that form the correlator modules. Each multiplier reduces to a single exclusive-or gate and each accumulator reduces to a counter. (The same simplification doesn't work for an FFT processor; while the data could be represented with one bit, the trigonometric coefficients still need to be multibit and, except for the first stage, the butterfly operations still use multibit  $\times$  multibit multiplication). Simple one-bit correlation, however, does have its price: more integration time, by a factor of  $\pi^2/4$  or 2.47, is required if the averaging is to be as effective as if the signal had been multibit. Going from a 1-bit digitizer to a 2-bit digitizer reduces the 2.47 integration time penalty to only 1.29 but obviously complicates the multiplier/accumulator circuitry. A three-level digitizer ("1.6 bits") is often used; it permits multiplier/accumulator circuitry almost as simple as the 1-bit case and yields an integration time penalty of 1.51. In all of these quantization schemes the distortion of the ACF can be corrected [2].

Some of the integration time penalty can be recovered. When the signal is oversampled by a factor of 2, i.e. sampling at a rate of 4 times the bandwidth, the factors of 2.47, 1.29, and 1.51 reduce to 1.82, 1.14, and 1.26, respectively. Very little is gained by going to still

faster sampling rates.

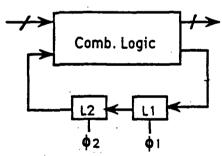

# 5 Digital Filtering

The canonical transversal digital filter uses a tapped delay line (shift register). Successively delayed samples of the signal are taken from these taps and multiplied by constant weighting coefficients. The weighted signals are combined in a single multi-input adder. Each new input sample pushes data down the shift register to produce a new output value from the adder. The correlator architecture described above provides another way to implement the transversal filter. The input signal provides the immediate data to an N-lag correlator. The filter coefficients are generated serially (e.g. from a ROM addressed by a counter) and form the delayed "data." After each input sample one correlator module will contain the desired convolution of the last N data values and the N coefficients. Its accumulator contents are latched into an output register and its accumulator is zeroed. After the next input sample, the output register is loaded from the adjacent correlator module. The process continues indefinitely, with the correlator modules being read out and rezeroed cyclicly.

At the Arecibo Observatory an 8-bit × 1-bit correlator was used this way as a transversal filter to produce radar maps of the surface of Venus. The c.w. transmitted signal is phasecoded with a long (4095, say) pseudo-noise sequence to get the bandwidth needed for range resolution. The received signal (radar echo) is decoded by the transversal filter. The filter coefficients are the plus ones and minus ones of the code so the code generator itself provides these coefficients in the required serial sequence. With the code properly phased, the first lag module of the correlator produces the signal reflected from the front cap of the planet. The next lag module produces the signal corresponding to the next range ring, etc [3]. The lags are read in order and the resulting data sequence is identical to what would have been obtained by transmitting a powerful short pulse (pulse length equal to the baud length) and using no decoder. Good range resolution, essentially equal to the baud length, is a consequence of the very sharp peak resulting when the pseudo-noise code is convolved with itself. The code sequence must be long enough to avoid aliasing other ranges in each decoder channel, i.e. the code length is deeper than the radius of the planet. In this application our correlator had fewer lag modules than the number of bauds in the code sequence - an economic constraint. The code was phased such that the ranges of interest were decoded by the implemented modules; other ranges landed in absent modules (which were, of course, just ignored). This trade-off of ranges for less hardware would not have been possible with the canonical delay line transversal filter.

# 6 VLSI Implementations

Correlators were implemented first with discrete transistor logic and then with all the standard families of integrated logic elements. A gate-array correlator chip designed by Albert Bos (4) has 16 lags running at 50 MHz. More recently, Brian Von Herzen (5) produced a VLSI chip with 320 lags that runs at 250 MHz. John Canaris (6), of the VLSI design group at the University of Idaho (now at the University of New Mexico), is designing a 1024-lag

correlator chip with 3-level quantization to run at 100 MHz. A commercial product, the Zoran ZR33891 Digital Filter Processor is an 8-lag correlator chip that does 9-bit × 9-bit multiplications at a 20 MHz rate and has 26-bit accumulators. As explained above, radio astronomy applications favor designs use much coarser quantization in order to have many more lags and higher speed.

# 7 Multi-chip Expansions

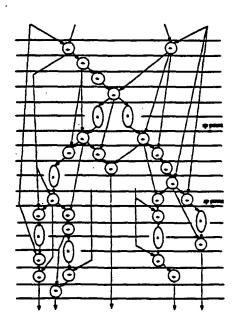

The basic correlator chip shown in Figure 1 can be used in a variety of ways to build expanded systems. Perhaps the most obvious is series expansion (simple cascading), which only requires that the chip have an output pin from its last delay element to provide the delayed data for the following chip. Time multiplexing is a parallel expansion technique that provides both higher speed and more lags. For example, suppose our N-lag correlator chip is able to accept data at only half the required rate. We can split the data stream into two half-speed streams, the even samples and the odd samples, and then use four chips to calculate the two possible autocorrelation functions (ACFs) and two possible cross-correlation functions (CCFs). When the integrated results are dumped to the computer, the sum of the ACFs gives us N even lags and the sum of the CCFs gives us N odd lags. By going from one to four chips we've doubled the speed and doubled the number of lags. Generalizing, we can divide data into N streams and use N<sup>2</sup> correlators to form all the possible lagged products. Another interesting form of parallelism, distributed arithmetic (from the distributive law of multiplication), was described by Zohar (7) as a way by which signals with many bits can by correlated using simple 1-bit, 2-bit, etc, correlator chips. Since signed numbers complicate matters, consider first a digitizer that encodes positive integers into, say, standard 8- bit binary representation. Group the eight bits into four 2-bit digits. We could multiply two such 4-digit numbers by separately multiplying each digit of one by each of the digits of the other. This could be done in parallel by 4<sup>2</sup> or sixteen 2-bit multipliers. Sixteen 2-bit correlators could independently form sub-products and accumulate them during an integration cycle. The results would be read out, appropriately weighted, and added to accomplish 8-bit × 8-bit correlation. This technique will work with signed numbers if we have either

- 1. a number system where the place weights carry signs, or

- 2. a number system where the digit values possible for each place are signed.

An example of the first case is the negabinary system (radix -2) where the digit values are just 0 and 1 but the place weights are 1, -2, 4, -8, etc. An example of the second case is the balanced ternary system where the values are -1, 0 and 1 and the place weights are 1,3,9,27, etc. For the negabinary system we would need 1-bit correlators with AND gates as multipliers rather than the EX-OR gates of the standard 1-bit correlator. For the balanced ternary system the popular 3-level correlator is just the right correlator element. Four 3-level (1.6-bit) correlators can run in parallel to correlate 9-level (3.2-bit) numbers. Correlators using many bits provide wide instantaneous dynamic range, especially if the quantization levels are exponentially spaced rather than uniformly spaced.

### 8 Summary

Digital VLSI correlator chips using coarse quantization and having many lag units are simple building blocks for spectrometers, convolvers, and digital filters. Chips can be paralleled to increase the number of channels, speed, and dynamic range.

#### References

- [1] Weinreb, Sander, "A Digital Spectral Analysis Technique and its Application to Radio Astronomy," Technical Report 412, MIT Research Laboratory of Electronics, August, 1963.

- [2] Hagen, J.B. and D.T. Farley, "Digital-correlation techniques in radio science," Radio Science, Vol. 8, Numbers 9.9, pp 775-784, August-September 1973.

- [3] Hagen, Jon B. "Communication Techniques in Radio Physics and Astronomy," IEEE Communications Magazine, October 1986 Vol. 24, No. 10, pp 16-20.

- [4] Bos, Albert, "A High Speed 2-Bit Correlator Chip for Radio Astronomy," IEEE Transactions on Instrumentation and Measurement, Vol. 40, No. 3, June 1991.

- [5] Von Herzen, Brian, "VLSI Partitioning of a 2-Gs/s Digital Spectrometer," IEEE Journal of Solid-State Circuits, Vol. 26, No. 5, May 1991.

- [6] Canaris, John, "NASA SERC Digital Correlator Projects" Fourth NASA Symposium on VLSI Design, October 1992.

- [7] Zohar, Shalhav, "The Role of the 1 Number System in Multibit Hardware Correlators," IEEE Transactions on Acoustics, Speech and Signal Processing, Vol. 37, No. 10, October 1989.

# Single Event Phenomena: Testing and Prediction

James D. Kinnison

The Johns Hopkins University

Applied Physics Laboratory

Laurel, Maryland 20723

jdk@aplcomm.jhuapl.edu

Abstract - Highly integrated microelectronic devices are often used to increase the performance of satellite systems while reducing the system power dissipation, size, and weight. However, these devices are usually more susceptible to radiation than less integrated devices. In particular, the problem of sensitivity to single event upset and latchup is greatly increased as the integration level is increased. Therefore, a method for accurately evaluating the susceptibility of new devices to single event phenomena is critical to qualifying new components for use in space systems. This evaluation includes testing devices for upset or latchup and extrapolating the results of these tests to the orbital environment. Current methods for testing devices for single event effects are reviewed, and methods for upset rate prediction, including a new technique based on Monte Carlo simulation, are presented.

#### 1 Introduction

Satellite system designers are constantly seeking new technology to increase the performance of their systems. Many new VLSI devices are well suited to space applications. For example, telescopes flown on spacecraft have greatly benefited from the use of on-board digital signal processors. However, space contains many hazards for which most VLSI devices have no inherent immunity. To be used in a satellite application, the response of these integrated circuits to the various space hazards must be measured, and some estimate of the survivability of these devices must be made.

One of the most difficult problems facing integrated circuits is that of exposure to charged particles. As these particles pass through a material, they lose energy by ionizing the material, inducing electron-hole pairs along the path of the particle. The interaction of electrons, protons, and heavy ions with integrated circuits leads to two different kinds of problems. The first is total dose degradation, in which the cumulative effect of many particles passing through an integrated circuit causes parameter degradation and functional failure, and will not be considered here. In addition to this problem, single particles passing through a device may cause a variety of effects, collectively known as single event phenomena (SEP).

In digital devices, the most common phenomenon is single event upset, in which the state of a bit or an active node is reversed. This erroneous state remains until that bit or node is reset. CMOS devices are susceptible to ion-induced latchup, similar to input latchup commonly observed on the workbench. In this case, a charged particle traverses a p-n-p-n region, and the induced current pulse injects enough minority carriers into the parasitic transistors present in the structure to cause a low impedance path from supply to ground.

Latchup is usually destructive. Analog or mixed analog-digital devices are susceptible to current pulses injected by charged particles. These pulses are short-term transients which can propagate to other devices and cause a bewildering array of system-level effects. Finally, power MOSFETs are susceptible to burnout and gate rupture due to charged particles, described first in [1].

#### 2 General Considerations

The effects discussed above are nominally different, but have a core of similarity. In each case, the effect is initiated by a single charged particle traversing a sensitive region of a device. In the simplest case, a monoenergetic beam of particles irradiating a device, some particles deposit enough charge in a sensitive region to cause an event (i.e., an upset, latchup, or transient). The number of events occurring, N, is given by

$$N = \rho * n \tag{1}$$

where  $\rho$  is the probability that a particle causes an event, and n is the number of particles passing through the device. Normally, the number of interactions is given in terms of the particle fluence, the number of particles per unit area, instead of the number of particles. If we multiply  $\rho$  and divide n by the area of the device, the previous equation becomes

$$N = \sigma * \Psi \tag{2}$$

where  $\sigma$  is the event cross-section, with units of area, and  $\Psi$  is the particle fluence.

In principle, the cross-section contains all the information about an integrated circuit necessary to estimate the event rate in any environment. For each type of event, the cross-section depends on many factors, including angle of incidence, the type and energy of the incoming particle, the temperature, and the electric fields present near the sensitive regions. In some cases, it is possible to assign a physical meaning to the cross-section. For example, in a static RAM, each cell is nearly identical, and contains a nearly identical sensitive volume. If a particle induces enough charge in one of these volumes, an upset occurs in that cell. The cross-section is just the area of the sensitive volume normal to the particle path.

In the case of heavy ions, it is convenient to describe the event cross-section as a function of the incident particle linear energy transfer (LET), rather than particle type and energy. The linear energy transfer is the amount of energy transferred to the target material along the particle path, and is the derivative of the energy with respect to distance along the track. LET is usually given in units of MeV\*cm²/mg, and is determined by the incident particle type, charge, and energy, and by the target material density. The cross-section for a device is zero below some LET normally referred to as the threshold LET, and rapidly increases to a value called the asymptotic cross-section. For SEP due to protons, the cross-section is determined as a function of incident proton energy rather than LET, but the form of the cross-section remains the same.

For many devices, the angular dependence of the cross-section is easily expressed. A particle which travels through a device at some oblique angle has a longer path through the device than a particle which travels normal to the device; therefore, more energy is

transferred to the target material. The result is a particle which appears to have a larger LET than the same particle at normal incidence. Therefore, the LET of the particle is expressed as an effective LET given by

$$L_{eff} = \frac{L}{\cos\theta} \tag{3}$$

Note that this does not account for azimuthal asymmetry of the device, and so does not give the azimuthal dependence of the cross-section. This dependence is measured by irradiating the device at several azimuthal angles.

The cross-section of a device can sometimes be estimated using a computer model. This obviously requires in-depth knowledge of the device layout which is not usually available to the user. In most cases, the cross-section must be measured. These tests are usually performed at a particle accelerator laboratory; one of the most commonly used sites is the Tandem Van de Graaff accelerator at Brookhaven National Laboratory. No matter where the test is performed, the layout is much the same. The accelerator provides a beam to a target area with the same LET (or in the case of protons, energy) as particles found in space. Since the path length of heavy ions in air is very short, the target area is usually a vacuum chamber connected to an evacuated beam line. The device under test (DUT) is mounted in the target area, irradiated with particles, and tested for events. Since the beam is monoenergetic, and the particle fluence over the exposure is measured, equation (2) can be used to calculate the cross-section. This procedure is repeated for a variety of test conditions, until the cross-section is completely characterized.

#### 3 Test Methods

Nearly all SEP cross-section measurements are performed in the manner outlined above. The main differences occur in the ways that logistical problems for a target area are solved. For example, nearly all SEP tests are computer controlled, but the tests must be performed in a vacuum chamber. Therefore, the problem of communicating with a DUT or test hardware through vacuum feedthroughs must be solved. Similarly, DUTs dissipate heat when operated; in a vacuum chamber, good thermal control is essential.

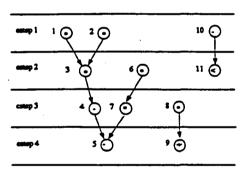

The integrated circuits under consideration are usually quite complex, and the problem of exercising the device while looking for errors is challenging, to say the least. While there are many ways to implement a test for SEP events, they all fall into four categories, the squirt, golden-chip, pseudo-golden-chip, and loosely coupled methods. There are benefits to each method, but none is appropriate for all device types. Therefore, an understanding of all four is essential to planning a good SEP test [2].

#### 3.1 Squirt Method

The squirt method is the simplest way to test for SEP. In this type of test, a device is prepared for exposure, irradiated, and then interrogated for the presence of events. In general, the DUT is under static bias, and only SEP which are not time dependent are considered.

As an example, consider upsets in a static RAM. The test hardware consists of a circuit which loads a fixed pattern into the memory, then reads back the contents of the memory and compares this to the original. The cross-section is calculated by counting the total number of upset bits and dividing by the particle fluence over that exposure. This sequence is repeated for a variety of particles with different LET and incident angle, and for a number of other device conditions such as bit pattern and temperature.

Latchup or burnout tests are often performed using this method. In this case a device is irradiated under static bias; after exposure, the device is examined for latchup or burnout. Since the latchup could have occurred during any part of the irradiation, the results of this test can not be used to calculate the latchup cross-section, but the susceptibility of a device to a particle of a particular LET is determined.

Obviously, this type of test is easy to implement, and for many devices, is quite adequate as a screen for destructive phenomena. However, this type of test is usually incomplete in the sense that only static errors are counted. In the case of the static RAM, for instance, those portions of the device which provide control and address decoding are never tested. Since one error in control logic may upset many bits at once, this oversight may gloss over grossly undesirable behavior. Other significant behavior, such as the device operating frequency dependence of the event cross-section, may also be missed. Finally, sensitive bits may flip more than once during an exposure. If this occurs, an error may never be counted, or may only be counted once, and so the cross-section may be too low by a factor of two or three. Despite these drawbacks, there may be times when this type of test is appropriate. The upset cross-section of many memories is still measured this way, since cell upsets dominate the cross-section.

#### 3.2 Golden-Chip Method

Since static tests can miss some types of events, dynamic testing is preferred for SEP measurements. The golden chip method is a way to implement these dynamic tests without building a large VLSI integrated circuit tester that fits in a vacuum chamber. The test hardware is built around two identical devices which are mounted so that one is irradiated while the other is not. If the devices are given the same inputs, they should have the same outputs, unless an event occurs. Therefore, the error detection consists of a set of level comparators, one for each output, and a counter which keeps track of the number of events observed. In addition, the control hardware must be able to simultaneously reset the test device and the golden device when an error occurs.

Golden-chip tests offer one important advantage over the previous type; the test is dynamic, not static. Therefore, all portions of a circuit can be exercised. In addition, events are counted dynamically, so missed multiple events are much less likely. The golden-chip method can be used to test many different kinds of logic devices which operate at relatively low frequency and with a small number of inputs. For example, latchup tests can be performed by comparing the supply current and outputs of an irradiated device to those of a golden device. When a large difference in the supply current is observed, a latchup has occurred.

However, there are limitations to the usefulness of this method. First, the test hardware

must provide inputs to the devices simultaneously. Second, the number of input states in a test cycle determines the amount of data storage needed in the test control hardware; for some devices, the number of inputs needed to effectively exercise all portions of the DUT can be quite large. Third, the devices should not be overly sensitive to noise, which on an output could be mistaken for an event. Finally, the device outputs, including timing parameters, must be identical to within the resolution of the tester comparators. In most cases, this restriction imposes an upper limit to the DUT operating frequency during the test.

#### 3.3 Pseudo-Golden-Chip Method

The pseudo-golden-chip method seeks to avoid the limitations of the golden-chip method by comparing the output sequence of the DUT to some standard sequence. In essence, we replace the golden device with a computer. As the DUT is irradiated, each output is compared to an expected value. Any discrepancy is counted as an event.

A good example of a device suited to this test method is a FIFO memory. A known bit pattern is repeatedly applied to the FIFO, and after each write, a word is read. If the correct pattern does not appear, then a single event upset has occurred in either the control logic or the circular buffer in the FIFO.

This type of test is frequently used in SEP testing. Most groups who regularly test devices for SEP susceptibility have developed some type of computer-based test hardware which can rapidly be tailored for this kind of test. As with the golden-chip method, the number of different states in the input sequence limits the usefulness of this tests. The operating frequency of the DUT is also limited by the time taken to compare all the DUT outputs to the expected values.

# 3.4 Loosely Coupled Systems Method

All three methods discussed above are based on some set of test hardware closely controlling and examining a device. This is, in principle, the best way to test for SEP. In practice, however, an event in a DUT can cause the test hardware to malfunction. This is disastrous in an SEP test; any dead time, in which the beam is on but events cannot be counted, artificially reduces the accuracy of the cross-section measurement. Therefore, it is essential that the test system is able to quickly detect and correct any events observed in the DUT.

The loosely coupled systems method is built around the interaction of two systems. The first system, which I will call the DUT test system is used to exercise the DUT. The second system, called the test controller, is used to monitor for events reported by the DUT test system, and to reset the DUT test system when an event is observed. The two systems communicate asynchronously.

This method is the most effective way to test microprocessors and related devices. In this case, the DUT test system would be a single board computer which executes some fixed test routine on bootup. This routine is written so that a known status word, which indicates whether the DUT test routine was completed successfully or an event occurred, is sent to the test controller computer at regular intervals via a serial link or some similar communication protocol. The test controller receives the status word, examines it, and forces a reset in the

DUT test computer if an event is detected. In addition, the test controller operates as a watchdog so that if an event in the DUT stops the operation of the DUT test system, a reset is forced.

In spite of the benefits discussed above, there are problems with this method. First, some information about the distribution and effect of event in the DUT is lost. We can determine that an event occurred, but not where or exactly what the consequences of that event are in the DUT. Second, the cross-section measured is really the cross-section of the DUT test system, not the DUT; if only the DUT is irradiated and all events which occur in the DUT are observed, then the system event cross-section is a close approximation to the DUT cross-section. Third, because the devices tested in this manner are complex, the cross-section may vary significantly with test program. Because of these problems, the DUT test system should be as close to the target application as possible.

#### 4 Rate Prediction

The cross-section for some event is a parameter used to characterize the susceptibility of a device to that event. It contains all the information needed to estimate the event rate in an arbitrary charged particle environment. The methods by which these estimates are calculated, however, are not simple, and much research into event rate prediction methods has been centered around simplifying the calculation of event rate estimates.

Unfortunately, some methods developed for one type of event may not be applicable to other types of events. Most of the effort has been directed toward developing single event upset prediction methods. Only recently have researchers started examining other effects and the relationship between the cross-sections for different effects. The most important event rate prediction methods are discussed below.

#### 4.1 The Path-Length Distribution Model

The path-length distribution model assumes that every upsetable cell in a device is identical, and that each contains one thin rectangular parallelepiped region, called the sensitive volume, such that a particle which deposits charge in this region may cause an upset. If this is true, the upset rate, N, is given by

$$N = 22.5\pi AQ_C \int_0^\infty \frac{D[p(L)]}{L^2} \psi(L) dL \tag{4}$$

where A is the area of the sensitive volume,  $Q_C$  is the smallest deposited charge that will cause an upset (called the critical charge), L is LET, D[p(L)] is the differential distribution of path lengths over which a particle of LET, L, will produce a charge greater than the critical charge, and  $\psi$  is the integral flux spectrum given as a function of LET. Pickel and Blanford [3], in 1980, originally proposed an integral of this form for the error rate.

All of the parameters in (4) are given by the cross-section except the particle flux. The critical charge is just the threshold LET in units of pC/ $\mu$ m(which is equivalent to MeV\*cm²/mg) times the minimum thickness of the sensitive volume (in  $\mu$ m). A is the asymptotic cross-section. The differential path length distribution depends on the shape of

the sensitive volume, and is not simply expressed. In most cases, the sensitive volume is assumed to be a rectangular parallelepiped, and the appropriate path-length distribution is used to evaluate (4)

The path-length distribution model was developed to predict single event upset rates in memories. The assumptions used to write (4) approximate most static RAMs to first order. However, many devices are not so simply described. For instance, a microprocessor may contain many different upsetable nodes, each with a unique sensitive volume. The result is that each node may have a different threshold and asymptotic value. The cross-section, as measured in SEP tests, is the sum of the responses of each individual sensitive volume. The integral in (4) does not model these situations well, but it is possible to increase the accuracy of the calculation for some devices which do not have identical sensitive volumes. If the individual sensitive volumes can be separated into a small number of groups with nearly identical volumes in each group, error rates can be calculated for each group. The total device error rate is just the sum of the group error rates.

Only single event upsets are considered in the path-length distribution model; the assumptions concerning the shape and uniformity of the sensitive volume only apply to single event upset. In other cases, particularly latchup, the concept of a sensitive volume is not meaningful, and so an equation like (4) cannot be written.

Several computer programs have been written to estimate the single event upset rate of a device using the path-length distribution model. The first of these was Cosmic Ray Induced Error Rate Analysis (CRIER) by Pickel and Blandford [4]. In 1981, Adams, Silverberg, and Tsao published the first part of a new model of the galactic cosmic ray environment. Over the next three years, they added the effects of the Earth's magnetic field to the model, and included a program to calculate the single event upset rate of a device in an arbitrary environment by evaluating (4). This model is called Cosmic Ray Effects in Microelectronics, also known as CREME [5]. CREME is commonly used today for single event upset rate estimations.

#### 4.2 The Bendel Proton Upset Models

It is commonly known that galactic cosmic rays cause single event upsets. Less commonly known is that high energy protons found in the Van Allen radiation belts can also cause single event upsets. These protons do not produce enough ionization to upset a device directly, but secondary particles created in nuclear reactions with the target material can produce sufficiently high ionization to cause upset. The Bendel models provide an estimate of the upset rate due to proton nuclear reactions in a variety of low Earth orbits as a function of semi-empirical fit parameters.

The first model is called the one-parameter Bendel model [6]. The proton upset cross-section is measured at a few proton energies, and then fitted to the following equations to solve for A:

$$\sigma = (24/A)^{14} [1 - exp(-0.18Y^{1/2})]^4$$

(5)

$$Y = (18/A)^{1/2}(E - A) \tag{6}$$

where E is the proton energy and  $\sigma$  is in units of  $10^{-12}$  upsets per proton/cm<sup>2</sup> per bit. An estimate of the proton upset rate as a function of orbit altitude and inclination, and as a

function of the parameter A is given in [6]. This semi-empirical model works reasonably well for older devices, but needs improvement for newer, more complex technology.

To increase the accuracy of the method, Stapor, et al. [7]

have recast (5) as a two parameter model. The equation becomes

$$\sigma = (B/A)^{14} [1 - exp(-0.18Y^{1/2})]^4 \tag{7}$$

where Y and  $\sigma$  are defined as in (5)-(6). As before, an estimate of the proton upset rate as a function of altitude and inclination, and as a function of both parameters, A and B, is given in [7].

Estimates made with the two parameter Bendel model have been compared to flight data taken on the CRRES satellite. These estimates are in reasonably good agreement with the flight data [8]. However, the estimates provided by the Bendel models are averages over a very dynamic environment, and the short term error rate may be much higher than the estimate. Therefore, systems with devices susceptible to proton upset must be able to withstand short periods of greatly increased error rate.

#### 4.3 Probabilistic Model

The definition of a cross-section given in (1)-(2) is based on a probabilistic interpretation of the interaction which causes SEP. Consider a monoenergetic beam of particles with direction normal to the face of a device. If the beam is uniform, the probability that a particle intersects the device at a particular point is constant across the face of the device. Assume that some regions of the device are sensitive to an event; any particle passing through those regions will cause an upset. The probability that a particle passes through these regions is just the total area of the sensitive regions divided by the area of the device. The total area of the sensitive regions is given by the cross-section.

In space, the particles interacting with the device are not monoenergetic, and so not all have the same LET. In addition, the particle flux is omnidirectional; the particles arrive from every direction at the same rate. So, for a particle of a given LET and direction, the probability that an event occurs is just the cross-section for that LET and direction divided by the projected area of the device normal to the particle direction.

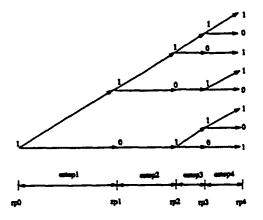

The probabilistic nature of the cross-section can be exploited to calculate an event rate for a device in a particular environment using a Monte Carlo simulation [9]. For a calculation of this nature, only the event cross-section as a function of LET and incident direction and the fluence as a function of LET are needed. The flux spectrum is divided into narrow LET bins. For a particle in one of the bins, the basic algorithm is as follows:

- 1. Pick a random LET within the bin.

- 2. Pick a direction.

- 3. Calculate the cross-section based on the LET and direction.

- 4. Generate a random number.

- 5. If the random number is less than the cross-section, increment the event count.

The event rate estimate is given by the event count which results after repeating the algorithm for the total number of particles in each LET bin of the flux spectrum.

The algorithm given above is applicable to any SEP for which a cross-section can be measured. Event rates generated by this type of computer simulation compare well with CREME and Bendel model estimates and with flight data. The advantage of this method is that no information about the geometry or architecture of the device is necessary to generate a good estimate of the event rate.

#### 5 Current Research

Several areas of current research in SEP may lead to new test and estimation techniques which will simplify the problem of qualifying new devices for use in space. These new techniques include new ways to stimulate devices to produce SEP, methods of estimating the cross-section for on type of event from the cross-section of another type, and new models for estimating event rates from cross-section data.

Accelerator beams are not cheap, and it can be difficult to schedule an experiment in a timely fashion. In addition, few researchers are located near an accelerator; experiments must be transported to the accelerator facility. Because of these difficulties, some researchers are using radioactive isotopes to provide high LET, low energy particles in a small vacuum chamber as an alternative stimulus for SEP. The most commonly used isotope for SEP testing is  $^{252}$ Cf, which produces fission fragments with a mean LET of 43 MeV\*cm²/mg. Unfortunately, these fragments have a limited range in silicon; they lose a significant fraction of their total energy in about 25  $\mu$ m. Therefore, this type of testing works reasonably well for single event upset testing, but is not useful for latchup, which requires deeper penetration into the device. In addition, as the particle travels deeper into the device, the LET changes as energy is lost. This effect must be taken into account when assigning an LET to the fission fragments. In spite of the disadvantages,  $^{252}$ Cf is commonly used to compare the relative sensitivity of devices, and to supplement accelerator tests.

Several groups are examining the use of pulsed lasers to simulate the effects produced by charged particles in devices [10]. A narrowly focussed laser beam produces localized electron-hole pairs in the target material like an ion. The effective LET of the laser beam can be varied by changing the intensity of the laser, so a wide LET range can be simulated. The primary advantage of using a laser beam to stimulate SEP is that the spot size is of the same order as the feature size. Therefore, sensitive regions of the device can be mapped accurately, and geometrical assumptions about the sensitive volume are not necessary. Unfortunately, metal layers reflect the laser light, and so regions under metal can not be tested; the cross-section given by laser exposures is not complete, and can not be used in event rate calculations. However, the information gathered using a laser can be used to identify SEP sensitive regions so that device designers can correct the problem.

Solid-state detectors have been used in nuclear and radiation physics experiments for some time. In many ways, an integrated circuit may be viewed as a collection of solid state detectors. McNulty, et al, [11] have characterized the charge collection properties of many integrated circuits, and have shown that these measurements can be used to calculate the single event upset cross-section of a device. In a test of this type, the DUT is biased such

that the inputs and output are floating, supply pins are grounded, and the ground pins are connected to pulse height analysis system. When the device is exposed to a particle beam, charge is collected; the passage of a single particle is seen as a current pulse. These pulses are collected and sorted by the pulse height analyzer into a pulse spectrum. Peaks in this spectrum represent sensitive regions in the device, and the area under a peak divided by the total fluence over the exposure is the cross-section of the sensitive region which generated that peak. This technique may be used to map sensitive volumes, so geometrical assumptions are not necessary to calculate an event rate. To date, this technique has only been used to measure single event upset cross-sections in regular structures, like static RAMs. A complex device such as a microprocessor may not be tested well with charge collection techniques. In addition, this is a static test, which can not be used while dynamically exercising a device. It is not clear that this test will accurately measure a cross-section that depends on frequency, program, or other dynamic variables.

A group led by Newberry has recently begun examining the relationship between device upset rates and system-level upset rates [12]. She has shown that, for some systems, single event upsets which occur in a device in that system are not propagated to the system output, and that, for other systems, device upsets are multiplied and spread throughout the system. This indicates that the upset rate of a system may not be the sum of the upset rates for each component of the system. If this is true, methods for simulating the effect of upsets on system behavior must be developed. In addition, this behavior may force experimenters to test for events at the system level, instead of the device level; entirely new test methods will have to be developed.

### 6 Summary

Satellite systems will continue to grow more complex, and the problem of SEP susceptibility will not go away. Therefore, it is critical that space systems designers understand the behavior of new integrated circuits in the space environment. I have discussed the methods which are commonly used to assess SEP vulnerability and to estimate the rate at which SEP occur in an orbital environment. SEP tests can be grouped in four classes of test types. Each of these test types have benefits and drawbacks, and an understanding of each test type is necessary to effectively gather the data necessary to predict the rate at which SEP occur in space.

In addition to the test types, I have discussed the most commonly used methods used to calculate estimates of the SEP rate in any environment. The assumptions upon which each of the methods are based are given, and the range of applicability is discussed.

Finally, some of the newest areas of SEP research are discussed. These research areas give some indication of the direction future SEP tests will take. Of critical importance will be the way system-level SEP tests are performed, and how these tests will be used to estimate the performance of a complex system in space.

#### References

- [1] A. E. Waskiewicz, J. W. Groninger, V. H. Strahan, and D. M. Long, "Burnout of Power MOS Transistors with Heavy Ions of Californium-252," *IEEE Trans. Nucl. Sci.* NS-33, 1710-1713 (1986).

- [2] R. Koga, W. A. Kolasinski, M. T. Marra, and W. A. Hanna, "Techniques of Microprocessor Testing and SEU Rate Prediction, UU IEEE Trans. Nucl. Sci. NS-32, 4219-4224 (1985).

- [3] J. C. Pickel and J. T. Blanford, "Cosmic Ray Induced Errors in MOS Devices," *IEEE Trans. Nucl. Sci.* NS-27, 1006-1015 (1980).

- [4] J. C. Pickel and J. T. Blanford, "CMOS RAM Cosmic Ray Induced Error Rate Analysis," *IEEE Trans. Nucl. Sci.* NS-28, 3962-3967 (1981).

- [5] J. H. Adams, Jr., Cosmic Ray Effects on Microelectronics, MR 5901, Naval Research Laboratory, Washington DC (Dec 1986).

- [6] W. L. Bendel and E. L. Petersen, "Proton Upsets in Orbit," IEEE Trans. Nucl. Sci. NS-30, 4481-4485 (1983).

- [7] W. J. Stapor, J. P. Meyers, J. B. Langworthy, and E. L. Petersen, "Two Parameter Bendel Model Calculations for Predicting Proton Induced Upset," *IEEE Trans. Nucl.* Sci. NS-37, 1966-1973 (1990).

- [8] P. J. McNulty, W. J. Beauvais, W. G. Abdel-Kader, S. S. El-Teleaty, E. G. Mullen, and K. P. Ray, "Test of SEU Algorithms Against Preliminary CRRES Data," *IEEE Trans. Nucl. Sci.* NS-38, 1642-1646 (1991).

- [9] J. D. Kinnison, R. H. Maurer, and T. M. Jordan, "Estimation of the Charged Particle Environment for Earth Orbits," *Johns Hopkins APL Technical Digest* 11, 300-310 (1990).

- [10] S. Buchner, K. Kang, W. J. Stapor, A. B. Campbell, A. R. Knudson, P. McDonald, and S. Rivet, "Pulsed Laser Induced SEU in Integrated Circuits: A Practical Method for Hardness Assurance Testing," *IEEE Trans. Nucl. Sci.* NS-37, 1825-1831 (1990).

- [11] P. J. McNulty, "Predicting Single Event Phenomena in Space," 27th IEEE Nuclear and Space Radiation Effects Conference Short Course, Reno, Nevada (July 16, 1990).

- [12] D. M. Newberry, D. H. Kaye, and G. A. Soli, "Single Event Induced Transients in I/O Devices: A Characterization," *IEEE Trans. Nucl. Sci.* NS-37, 1974-1980 (1990).

# Heterojunction Bipolar Transistor Technology for Data Acquisition and Communication

C. Wang, M. Chang, S. Beccue, R. Nubling, P. Zampardi, N. Sheng and R. Pierson Rockwell International Science Center Camino Dos Rios Thousand Oaks, CA 91360 kcw@jupiter.risc.rockwell.com, 805-373-4143

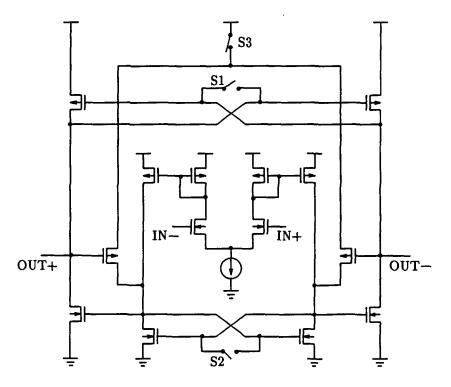

Abstract - Heterojunction Bipolar Transistor (HBT) technology has emerged as one of the most promising technologies for ultrahigh-speed integrated circuits. HBT circuits for digital and analog applications, data conversion, and power amplification have been realized, with speed performance well above 20 GHz. At Rockwell, a baseline AlGaAs/GaAs HBT technology has been established in a manufacturing facility. This paper describes the HBT technology, transistor characteristics, and HBT circuits for data acquisition and communication.

#### 1 Introduction

Heterojunction Bipolar Transistor (HBT) technology has shown great capabilities for the realization of high performance analog, digital, and microwave circuits [1-2]. To date, most of the HBT circuits demonstrated are based on AlGaAs/GaAs material system with widebandgap AlGaAs emitters and heavily doped GaAs bases. The AlGaAs/GaAs HBT technology offers a number of intrinsic advantages. High  $f_t$  and  $f_{max}$  (above 55 GHz), as well as high transconductance (above 10000 mS/mm), can be realized. The threshold voltages (Vth) are highly uniform; matching of Vth's of HBTs in differential pairs of about 1 mV has been measured. The intrinsic junctions of HBTs are well shielded from substrate and surface. Trap induced hysteresis effects are absent and 1/f noise is low. AlGaAs/GaAs HBTs also offer high breakdown voltages. The HBTs are fabricated on semi-insulating GaAs substrate, which reduces parasitic capacitances of transistors and interconnect lines and allows integration of multifunctional circuits. Rockwell pioneered the research of AlGaAs/GaAs HBT technology and developed a baseline technology with high current gain for analog, digital, and A/D conversion applications. The technology is now established in a manufacturing facility (Rockwell's Microelectronics Technology Center-MTC). High performance HBT circuits can be realized with high yields. As a result, recently Rockwell announced its initial HBT products. This paper presents Rockwell's baseline HBT technology and its applications in data acquisition and communication. Development of HBT-based technologies will also be described.

# 2 Rockwell's Baseline HBT Technology

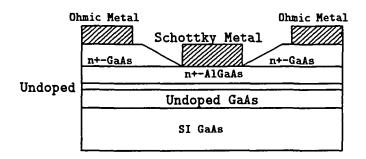

The HBT technology features emitter-up/single-heterojunction bipolar transistors, monolithically integrated Schottky diodes, NiCr thin film resistors, MIM capacitors, and up to

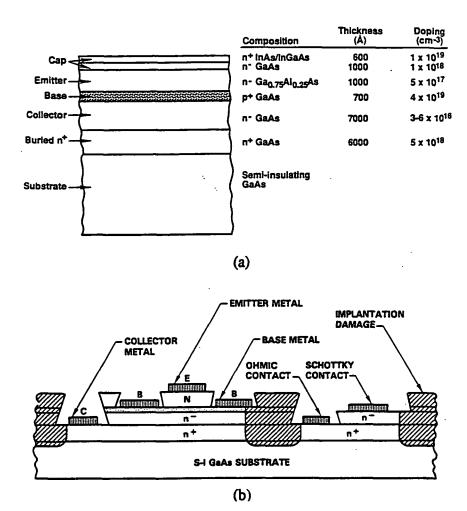

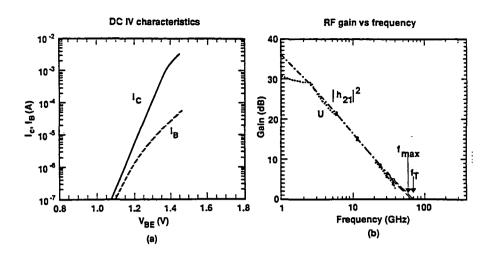

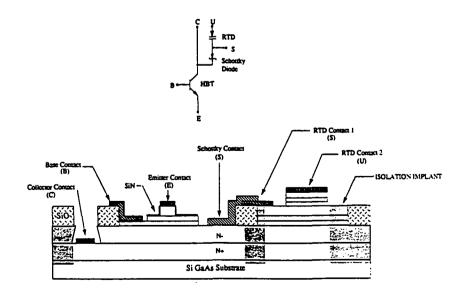

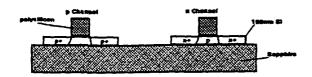

three levels of metal interconnect. AlGaAs/GaAs HBTs are fabricated on MBE or MOCVD grown epitaxial wafers. The epitaxial layer structure and a schematic cross section of an integrated HBT and a Schottky diode are shown in Fig. 1. The minimum geometry device used for the circuits has an emitter area of  $1.4\mu m \times 3\mu m$ , defined by projection optical lithography. The measured Gummel Plot of this device as shown in Fig. 2(a) illustrates current gain of about 100 at Ic = 1mA. The measured RF characteristics of the transistor at  $Vce = 2 \ V$  and  $Jc = 8 \times 10^4 A/cm^2$  are shown in Fig. 3(b).  $F_t$  and  $f_{max}$  above 55 GHz are obtained.

Figure 1: (a) HBT epitaxtal layer structure (b) Simplified cross section of an HBT and a Schottky diode

The diodes are realized using same layer structure and process as the HBTs. Typical series resistance and parasitic capacitance are  $40\Omega$  and 12fF for a  $2\mu m \times 4\mu m$  diode.

Many high-performance digital and analog circuits have been realized with the Rockwell baseline HBT technology. Frequency dividers have been demonstrated to work above 25 GHz [3]. 8-GHz 1000-gate gate arrays and 15-GHz 500-gate gate arrays were also realized

Figure 2: (a) Gummel Plot and (b) RF characteristics of an HBT that has an emitter area of  $1.4\mu m \times 3\mu m$

Figure 3: (a) Microphotograph of a fabricated HBT 2:1 mux. (b) Eye pattern of the mux output at 30 Gb/s operation.

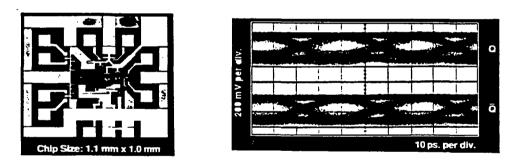

(jointly developed with IBM) [4-5]. We have demonstrated a number of ultra-high speed HBT circuits for lightwave communication, jointly with Bellcore. These include a 30 Gb/s 2:1 mux, a 27 Gb/s 1:2 demux, a 27 Gb/s 4-bit mux/demux, and a 7 Gb/s 8-bit mux/demux [6-7]. The microphotograph and operation of the 30 Gb/s 2:1 mux are shown in Fig. 3.

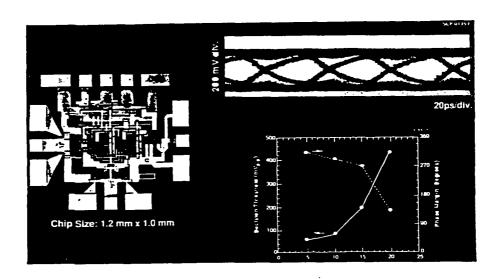

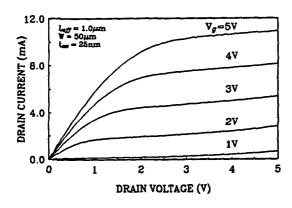

In the A/D conversion area, we have realized HBT voltage comparators that operate up to 20 GSps [8], as shown in Fig. 4. We have demonstrated 2 GSps sample-and-hold (S/H) circuits with less than -40 dB distortion (jointly with HP Labs.), and Multi-GSps 4-bit and 6-bit quantizers [9-10]. We are developing high performance ADCs and DACs with the HBT technology. These include: a 6-GSps 6-bit ADC (also with HP Labs.), a 1.5-GSps 8-bit ADC, a 100-MSps 12-14 bit sigma-delta ADC, and a 1.2-GSps 12-bit DAC.

Figure 4: (a) Microphotograph of a fabricated HBT voltage comparator. (b) Output eye pattern of the comparator at 20 GSps operation. (c) Measured sensitivity and phase margin.

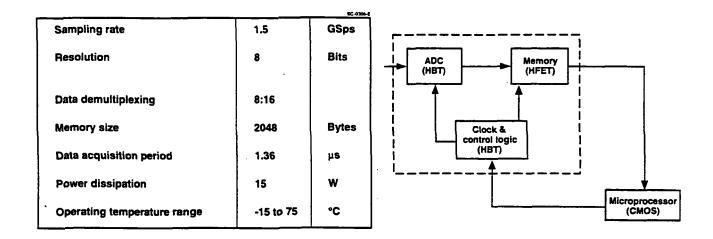

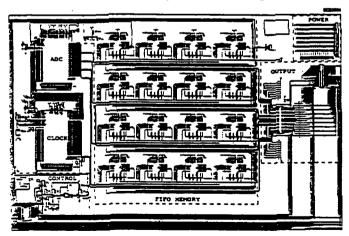

# 3 An HBT Based Data Acquisition System

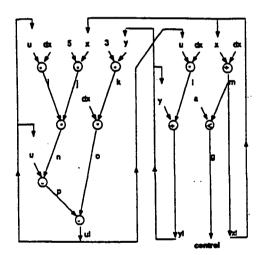

We are developing a 1.5-GHz 8-bit data acquisition system (DAS), under a NASA/ONR contract. The primary goal is for laser altimeter applications, although the system can be used for general purpose ultra-high speed data acquisition. The system specifications are shown in Fig. 5. The system includes an HBT ADC, an HBT clock driver, 16 HFET (heterojunction FET) 1K memory circuits, and Si CMOS interface circuits. A schematic block diagram is also shown in Fig. 5.

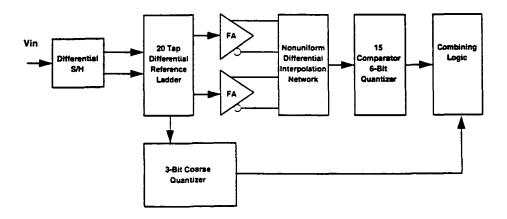

The key component of the system is an HBT 8-bit 1.5-GSps ADC. The ADC employs a folding and interpolating scheme [11] that features flash ADC speed at significant savings in device counts and power. The block diagram of the ADC design is shown in Fig. 6.

Figure 5: System specifications and Block diagram of an HBT based DAS.

Figure 6: Block diagram of the 8-bit 1.5-GHz ADC design.

It contains an on-chip S/H circuit, a 3-bit coarse quantizer, a 6-bit fine quantizer, and a combining logic. We chose an all-differential architecture to reduce common-mode errors. An on-chip 1:2 demultiplexer for each output bit reduces the output data rate. The circuit contains about 1700 HBTs (950 in the A/D and 750 in the demux). The estimated power consumption is 3 W. Figure 7 shows a fabricated 8-bit 1.5 GSps HBT ADC.

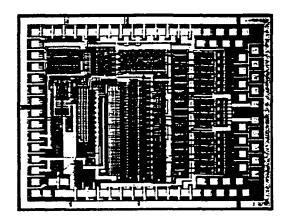

Figure 7: Microphotograph of a fabricated 8-bit 1.5 GSps HBT ADC.

To evaluate the expected dynamic accuracy of the HBT 8-bit ADC design, we have simulated the performance of the whole ADC circuit (except the data demuxing) with HSPICE, and analyzed the results. The digitized input waveform for a 1.6 MHz input at 1.5 GSps operation was reconstructed as shown in Fig. 8. The vertical scale of the signal waveform (shown on the right side of the figure) is in units of LSBs (least-significant bits). The distortions and noises were calculated, with much finer vertical scale (on left side). The calculated signal to noise + distortion ratio (S/N) is about 47 dB, which corresponds to 7.5 effective bits. Operations of the ADC at other sampling rates and input frequencies were similarly simulated and analyzed. Good S/N ratios were obtained. Initial fabricated ADCs are being evaluated.

Figure 8: Simulated output waveform and noise + distortion of the 8-bit HBT ADC operation at 1.5 GSps and with a 1.6 MHz input.

The HBT clock driver circuit provides control logic and synchronized complimentary clocks to the 16 memory chips. It also contains a high speed frequency divider as a part of a phase locked loop for a clock generator. Other important components of the DAS are the 16 1K-bit FIFOs (first-in first-out memory). They are implemented with Rockwell's HMESFET which has a large noise margin.

The access time is 1.3 ns, with an estimated power consumption of 0.8 W per chip. Design of the FIFO allows convenient cascading of a series of chips for memory extension. The HBT clock driver and HMESFET circuits are also in fabrication now. We used an off-the-shelf CMOS transceiver chip to interface the GaAs chips with a personal computer.

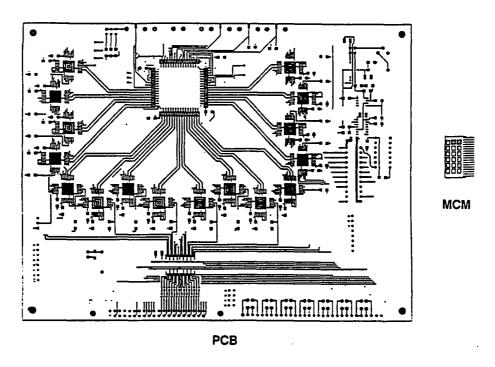

# 4 Packaging Considerations

The HBT ADC and clock driver will be packaged with commercially available multi-layer ceramic packages, such as the TriQuint MLC132/64. They can be tested by direct capture of output data using logic analyzers (e.g. HP 16500) up to 1.5 GSps operation (with the help of on-chip demux). The memory chips will be packaged in MSI 3H32CM chip carriers. The data acquisition system will be assembled on a printed-circuit board (PCB). Figure 9 shows the design of the eight-layer PCB. The outer two layers will be implemented with polymide for high performance microstrips. The inner six power and ground layers will be realized with FR4 material for strength and low cost. The layout of one outer layer is shown in Fig. 10(a). The PCB measures  $20cm \times 15cm$ . The ADC and clock driver will be mounted back-to-back, so that the ADC output and clock signals can be routed to each FIFO identically. The PCB provides a clock synthesizer, a DMA (direct memory access) interface to computer, and SMA connectors for analog and clock inputs.

Figure 9: PCB design of the data acquisition system.

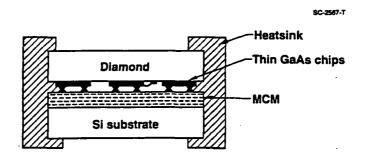

At Rockwell Science Center, advanced packaging technologies are being developed. One idea is to use Total Substrate Removal (also known as epitaxial layer lift-off or peeled film process) of the GaAs circuits, and attach them on a substrate of high thermal conductivity (e.g. diamond or AlN) in high density. The thin (about  $5\mu m$ ) circuits and high thermal

conductivity of the substrate allow extra-dense chip packaging. This shortens the metal interconnect, thus increasing the allowed signal rates. A conventional Multi-Chip Module (MCM), using polyimide and Au/Cu wires, can be used for signal interconnect and power supply. The circuits on diamond or AlN substrate will be flip-chip bonded to the MCM. We estimated that  $15cm \times 10cm$  of PC board area can be reduced to  $2cm \times 1.1cm$  of the new MCM are a, as shown in Fig. 10(b). The packaging concept is illustrated in Fig.11. In addition to the size and speed benefits, the new packaging allows for increased ADC accuracy due to lower temperature variation over the chip, and improved lifetime/reliability due to improved thermal management. Furthermore, the HBT clock driver circuit may not be needed since the clocks to the memory chips may be distributed with a common bus in the new packaging. This will result in about 20% reduction in power consumption.

Figure 10: (a) Layout of one outer layer of the PCB. (b) Schematic layout of an advanced MCM, that contains the two HBT circuits and sixteen HFET memory chips.

Figure 11: Advanced MCM packaging concept.

Figure 12: A simplified lightwave communication system.

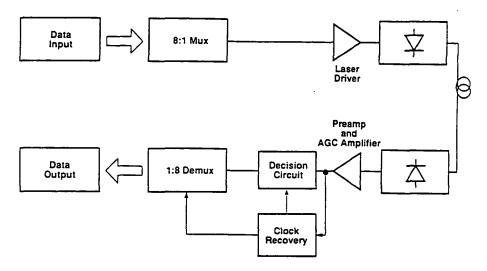

#### 5 HBT Circuits for Communications

HBT technology offers great capabilities to meet speed, accuracy, and power requirements of many communication systems. High-performance HBT circuits for lightwave and wireless communications have been demonstrated and many more are being developed.

Figure 12 shows a simplified lightwave communication system. Parallel digital data are serialized by a mux into a bit string of high data rate. A laser driver receives the bit string and generates current pulses to modulate a laser diode. The light signal is transmitted to a photo-detector through an optical fiber. The detector converts the light energy back to current pulses that are then translated into voltage pulses by a transimpedance amplifier. The signal is amplified, and a clock recovery circuit is used to regenerate synchronized clocks for the decision circuit and demux. Finally, the demux de-serializes the data into parallel outputs. As mentioned in Section 2, we have demonstrated ultra-high speed mux and demux circuits for this application. The 20 GSps voltage comparator can serve as the decision circuit to distinguish data 1's from 0's. In addition, we have realized an 11 Gb/s HBT laser driver that can modulate more than 50 mA of AC current into a 50 ohm load [6]. For the receiver side, a D C coupled, differential transimpedance amplifier has been demonstrated [12]. We have also realized DC coupled amplifiers of 10-dB gain and 14 GHz bandwidth. An HBT phase detector for clock recovery operated at 5 GHz. We are now developing complete clock recovery circuits for 2.5 and 10 Gb/s operation. These building blocks will be integrated monolithically into transmitter and receiver circuits, and in 4- to 8-channel arrays, for various fiber optic applications.

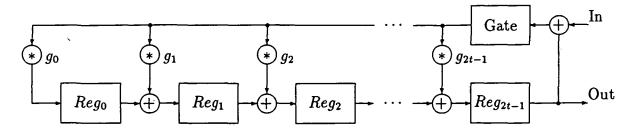

Pseudo-random bit generators (PRBS) are used for scrambling and descrambling data and for testing communication modules (as part of a bit-error-rate detector). They can also be used in pseudo-random code modulated laser altimeters for NASA [13]. We have realized an HBT PRBS (with a 15-stage shift register) and tested it up to 5.3 GHz, as shown in Fig. 13.

For wireless communication, power HBTs implemented with thebaseline technology have

5.3 GHZ (h)

Figure 13: (a) Microphotograph of a fabricated HBT PRBS. (b) Output eye patterns at 1 and 5.3 GHz.

shown > 60% of power added efficiency at 825-850 MHz. High performance HBT mixers were realized. We are developing an HBT based DDS (direct digital synthesizer) for I and Q demodulation. The DDS includes a DAC (digital to analog converter), an accumulator, and a ROM for sine/cosine look-up table. In addition, we are designing high-resolution sigmadelta ADCs with high speed HBT modulators. These ADCs are aimed at 12- to 14-bit 100 MSps for digital radios.

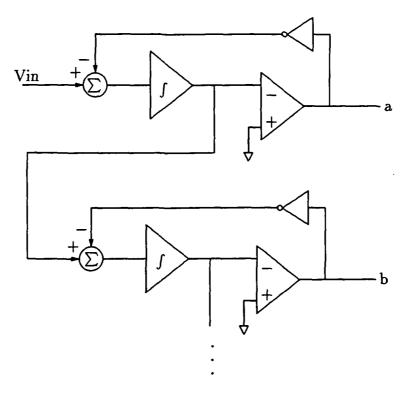

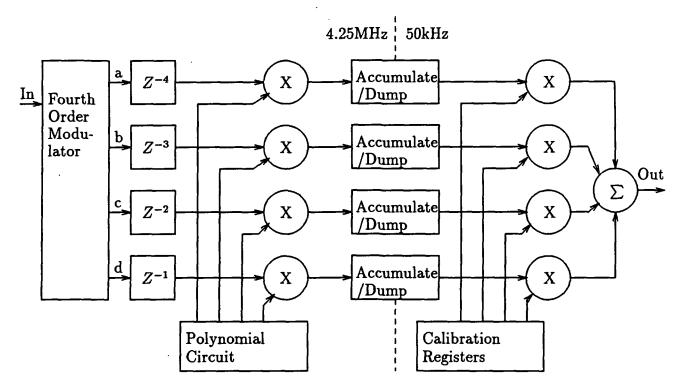

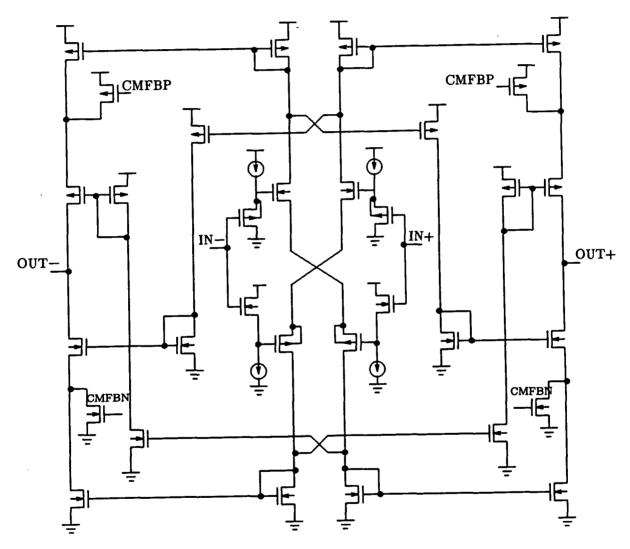

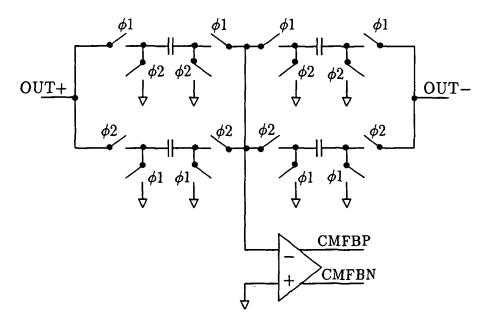

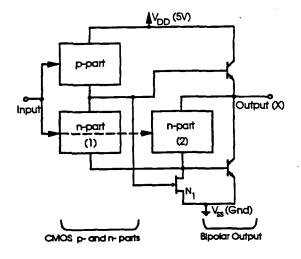

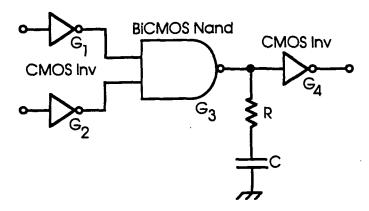

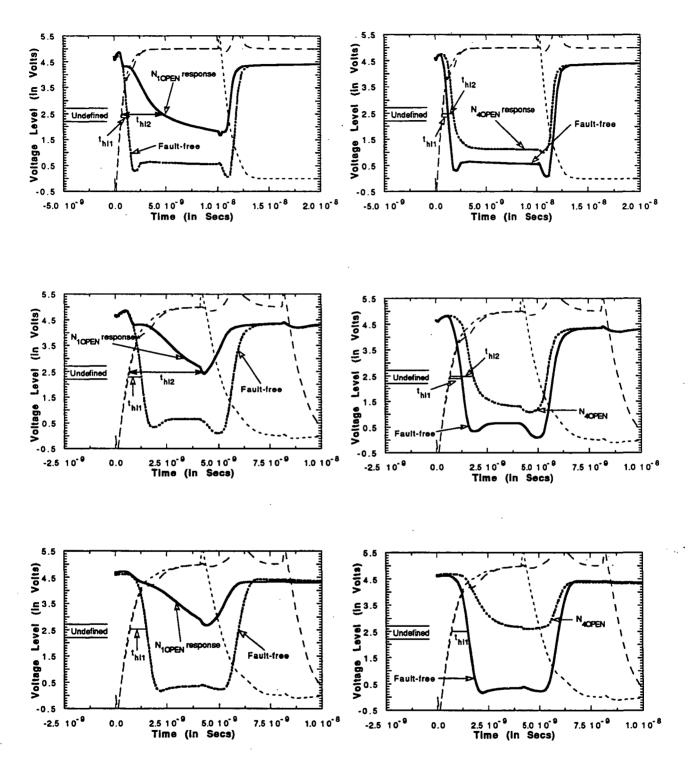

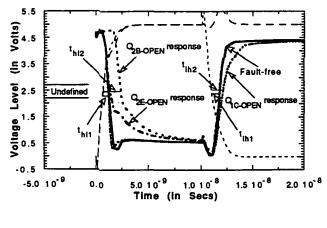

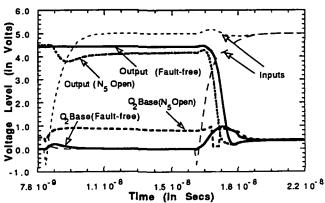

# 6 Development of Advanced Technologies Involving HBTs