https://ntrs.nasa.gov/search.jsp?R=19940023160 2020-06-16T13:49:29+00:00Z

/N-6/

NASA Contractor Report 187588

- 76-3 1601

# Hardware and Software Reliability Estimation Using Simulations

Frederic L. Swern Stevens Institute of Technology, Hoboken, New Jersey

| (NASA-CR-187588) HARDWARE AND    | N94-27663 |

|----------------------------------|-----------|

| SOFTWARE RELIABILITY ESTIMATION  |           |

| USING SIMULATIONS (Stevens Inst. |           |

| of Tech.) 160 p                  | Unclas    |

G3/61 0208963

Grant NAG1-587

February 1994

National Aeronautics and Space Administration Langley Research Center Hampton, Virginia 23681-0001

## CONTENTS

.

-

-

| 1. | INT | INTRODUCTION                                                            |  |  |  |  |

|----|-----|-------------------------------------------------------------------------|--|--|--|--|

|    | 1.1 | Flight Control Scenario6                                                |  |  |  |  |

|    | 1.2 | Latency as a Factor in the Failure of Highly Reliable<br>Systems8       |  |  |  |  |

|    | 1.3 | Software Errors Modeled as Latent Faults                                |  |  |  |  |

|    | 1.4 | Objectives of the Studies9                                              |  |  |  |  |

|    | 1.5 | Simulation as a Tool in the Reliability Estimation for                  |  |  |  |  |

|    |     | both Hardware and Software in a Highly Reliable System9                 |  |  |  |  |

| 2. | THE | GGLOSS SIMULATION PROGRAM                                               |  |  |  |  |

|    | 2.1 | The GGLOSS Simulation Methodology                                       |  |  |  |  |

|    | 2.2 | Some New Features Added to GGLOSS                                       |  |  |  |  |

|    | 2.3 | Processing Systems Described Across Multiple SDL Files20                |  |  |  |  |

|    | 2.4 | Simulation of Functional Blocks26                                       |  |  |  |  |

|    | 2.5 | Simulation of Memory Blocks                                             |  |  |  |  |

|    | 2.6 | Improving the GGLOSS Architecture for Other Simulation<br>Methodologies |  |  |  |  |

|    | 2.7 | Event Driven Simulation within the GGLOSS Architecture42                |  |  |  |  |

|    | 2.8 | Deductive Simulation using GGLOSS45                                     |  |  |  |  |

|    | 2.9 | Postprocessor Requirements47                                            |  |  |  |  |

| 3. | USE | OF GGLOSS TO STUDY LATENT FAULTS                                        |  |  |  |  |

|    | 3.1 | Causes of Failure in Highly Reliable Systems48                          |  |  |  |  |

|    | 3.2 | Latent Fault Scenario                                                   |  |  |  |  |

|    | 3.3 | Latency Effects as a Function of Architecture54                         |  |  |  |  |

|    | 3.4 | Description of Latent Fault Simulation Studies58                        |  |  |  |  |

|    | 3.5 | Probability of System Failure Due to Latent Faults59                    |  |  |  |  |

|    | 3.6 | Latency Characteristics of a Processor/Program                          |  |  |  |  |

|    |     | Combination                                                             |  |  |  |  |

|    | 3.7  | Measurements of a TMR System80                            |

|----|------|-----------------------------------------------------------|

|    | 3.8  | Latency Characteristics as a Function of System Mode91    |

|    | 3.9  | Effects of Modal Change on the Reliability of Systems     |

|    |      | with Latent Faults102                                     |

| 4. | SOFT | WARE RELIABILITY EVALUATION USING SIMULATION              |

|    | 4.1  | Introduction                                              |

|    | 4.2  | Flight Critical Software Requirements                     |

|    | 4.3  | Typical Programming Errors113                             |

|    | 4.4  | Methodology Development115                                |

|    | 4.5  | Mathematical Development117                               |

|    | 4.6  | Reliability Model for an Operational Flight Program121    |

|    | 4.7  | Validation by Simulation versus Flight Testing122         |

|    | 4.8  | Implementation procedure for the Methodology123           |

| 5. | VALI | DATION OF AN OPERATIONAL FLIGHT PROGRAM                   |

|    | 5.1  | Description of the Operational Flight Program             |

|    | 5.2  | Results of the Study127                                   |

| 6. | VALI | DATION OF THE LAUNCH INTERCEPTOR CONDITION PROGRAM        |

|    | 6.1  | Description of the Program under Test                     |

|    | 6.2  | Results of the Study 135                                  |

| 7. | A SI | MULATION METHODOLOGY FOR EVALUATING THE EFFECTS OF SINGLE |

|    | EVEN | T UPSETS (SEU)                                            |

|    | 7.1  | Description of Single Event Upsets                        |

|    | 7.2  | Associating a probability of recovery with an SEU 140     |

| 8. | CONC | LUSIONS AND SUGGESTIONS FOR FUTURE WORK 145               |

|    |      | I. GGLOSS USERS MANUAL                                    |

|    |      | II. GGLOSS DATASETS                                       |

|    |      |                                                           |

## LIST OF ILLUSTRATIONS

•

.

.

| Figure | 2.3.1 | A Modularly Constructed Simulation                             | 24  |

|--------|-------|----------------------------------------------------------------|-----|

| Figure | 2.3.2 | An Example of a Connectivity Matrix T                          | .25 |

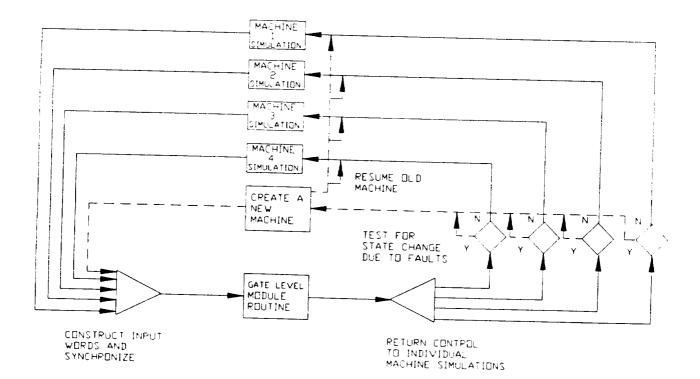

| Figure | 2.4.1 | Modeling of Multiple "Machines" Using Functional/              |     |

|        |       | Gate Level Simulation                                          | .29 |

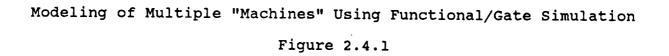

| Figure | 2.4.2 | Interfacing Functional Models with Gate Level                  |     |

|        |       | Simulation                                                     | .30 |

| Figure | 2.4.3 | Example of a Functional Level Module                           | .31 |

| Figure | 2.4.4 | Example of a Functional Level Interface Routine                | .33 |

| Figure | 2.4.5 | Performance Results for a Single Functional Level Interface    |     |

|        |       | Routine                                                        | .35 |

| Figure | 2.6.1 | Example of GGLOSS Macro Output                                 | .40 |

| Figure | 2.6.2 | Example of GGLOSS Macro Definition                             | .41 |

| Figure | 2.7.1 | Example of GGLOSS Event Driven Simulation                      | 44  |

| Figure | 2.8.1 | Example of Deductive Logic Algorithm                           | .46 |

| Figure | 3.1.1 | Block Diagram of an N Module Redundant                         | 51  |

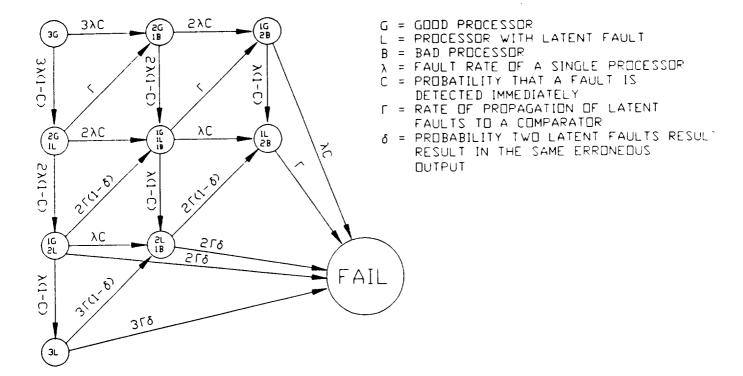

| Figure | 3.3.1 | Markov Model of a Triplex System Including Latency But Without | t   |

|        |       | Repair                                                         | 55  |

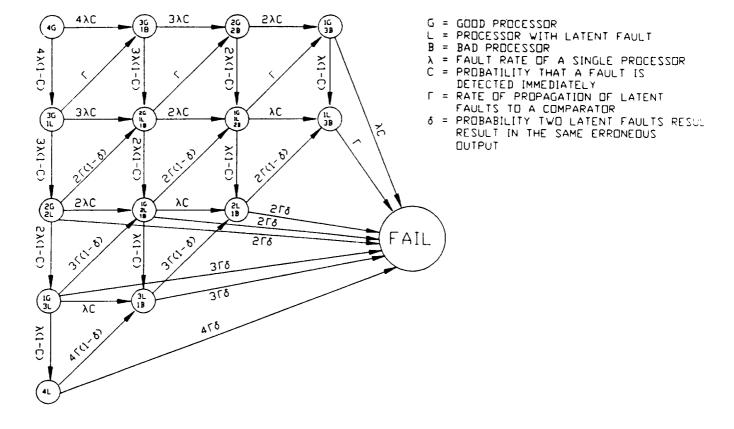

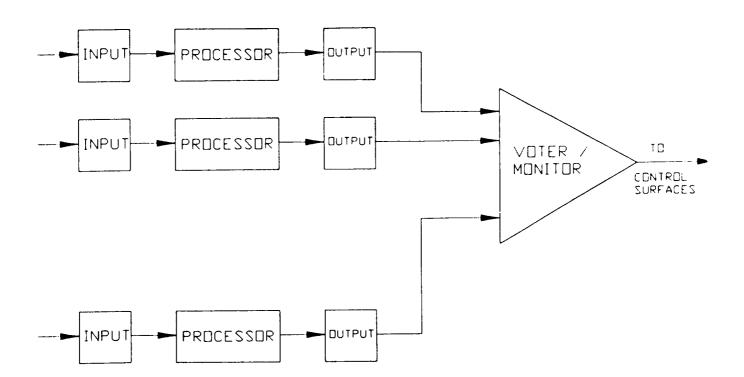

| Figure | 3.3.2 | Markov Model of a Quad System Including Latency But Without    |     |

|        |       | Repair                                                         | 56  |

| Figure | 3.3.3 | Probability of Failure as a Function of Latency for d = .1     | 57  |

| Figure | 3.5.1 | Simple Flight Control Program                                  | 66  |

| Figure | 3.5.2 | NMR Architecture                                               | 67  |

| Figure | 3.6.1 | Urn Model Markov Diagram                                       | 75  |

| Figure | 3.6.2 | Five State Program Model Markov Diagram                        | 76  |

| Figure | 3.6.3 | Generalized Program Markov Diagram                             | 77  |

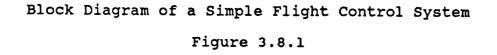

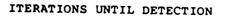

| Figure 3.6.4 | Graphical Form of Processor/Program Results78        |

|--------------|------------------------------------------------------|

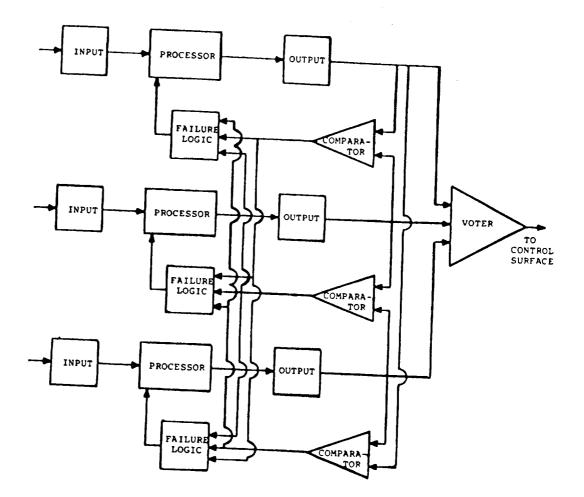

| Figure 3.7.1 | TMR Architecture                                     |

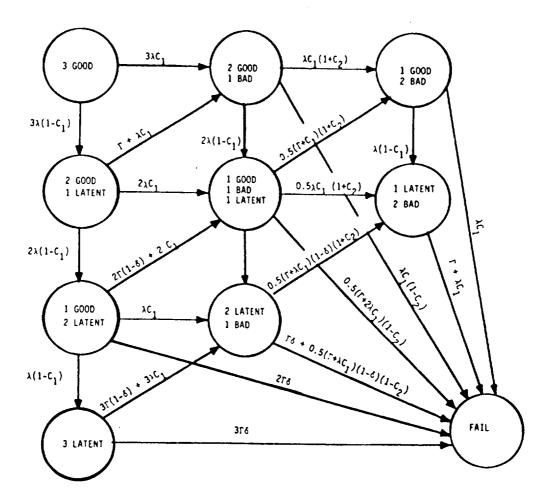

| Figure 3.7.2 | TMR Markov Diagram85                                 |

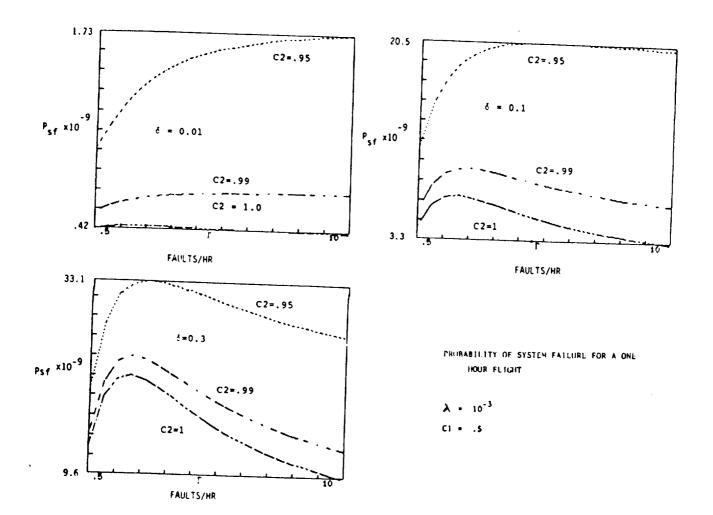

| Figure 3.7.3 | TMR Study Results86                                  |

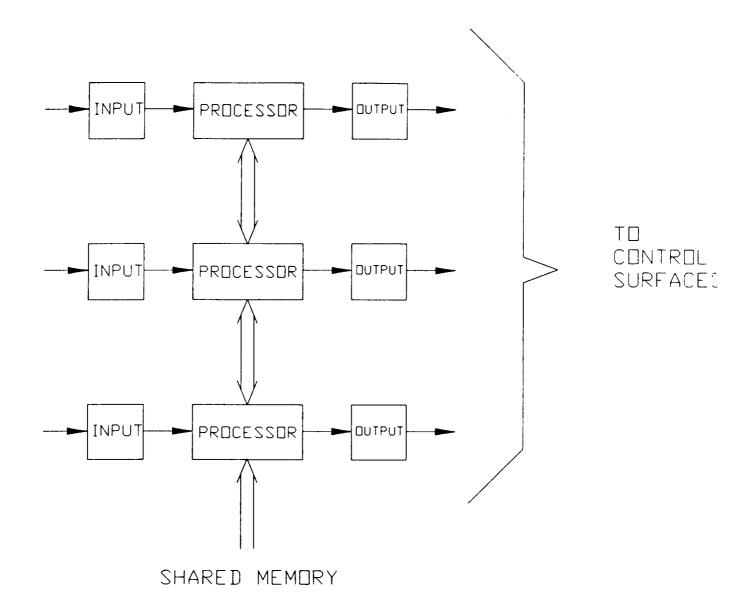

| Figure 3.7.4 | Software Monitoring System Architecture              |

| Figure 3.7.5 | Flight Control Program for Triplex Study             |

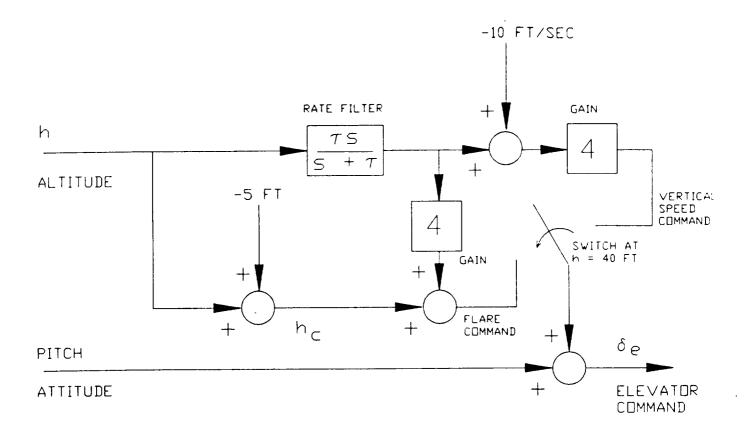

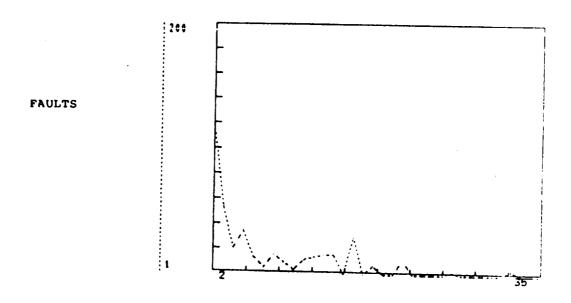

| Figure 3.8.1 | Block Diagram of a Simple Flight Control System93    |

| Figure 3.8.2 | Flight Control Program Listing94                     |

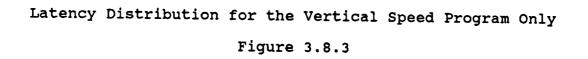

| Figure 3.8.3 | Latency Distribution for the Vertical Speed Program  |

|              | Only                                                 |

| Figure 3.8.4 | Latency Distribution for the Flare Program Only99    |

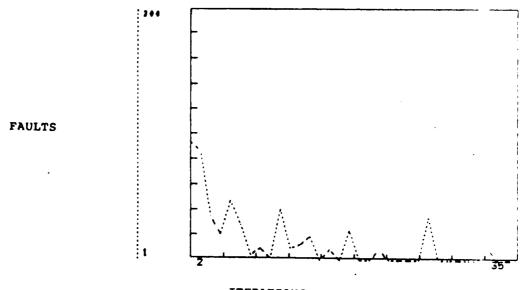

| Figure 3.8.5 | Latency Distribution for the Modal Logic Only100     |

| Figure 3.8.6 | Comparison of Results for Different Programs Running |

|              | on the Simulator101                                  |

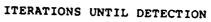

| Figure 3.9.1 | Markov Model of a Triplex System with Two Latency    |

|              | Classes                                              |

| Figure 3.9.2 | Vertical Speed Mode Latency Parameters               |

| Figure 3.9.3 | Flare Mode Latency Parameters107                     |

| Figure 3.9.4 | Latency Class Switching Matrix S from Vertical Speed |

|              | toFlare                                              |

| Figure 5.1.1 | Sample of an Instrumented Program                    |

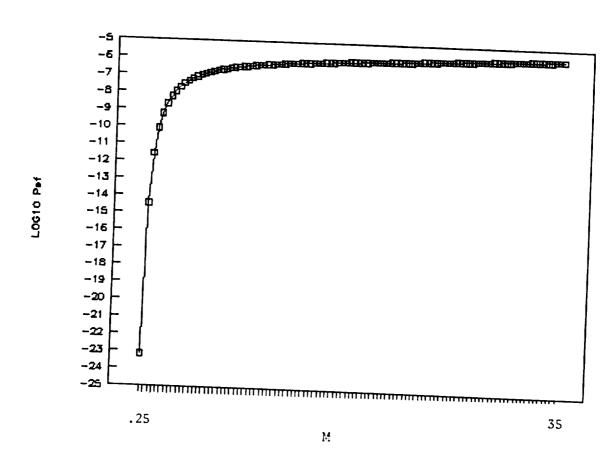

| Figure 5.1.2 | Probability of Failure as a Function of M in the M   |

|              | ErrorModel                                           |

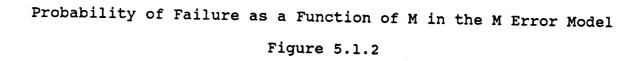

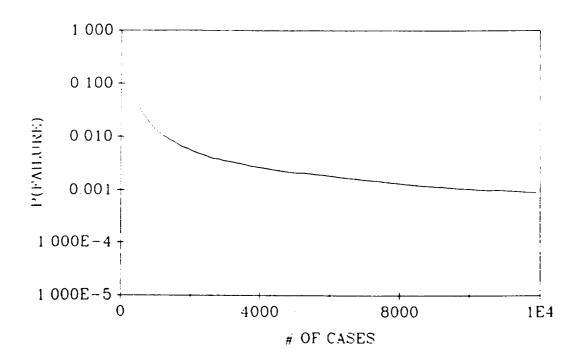

| Figure 6.2.1 | Typical Probabilities of Regional Occupancy for      |

|              | a Single Output                                      |

| Figure 6.2.2 | Probability of Failure of Gold Module                |

## LIST OF TABLES

| Table 3.5.1 | Tabular Postprocessor Output for Flight Control     |

|-------------|-----------------------------------------------------|

|             | Program                                             |

| Table 3.5.2 | Latency Distribution of the Faults                  |

| Table 3.5.3 | Resolution of Undetected Faults70                   |

| Table 3.6.1 | Model Parameters for Processor/Program Results79    |

| Table 3.7.1 | Results of Triplex Study90                          |

| Table 5.1.1 | Probability of Regional Occupancy for a Single      |

|             | Variable129                                         |

| Table 5.1.2 | Probability of Execution of Regions of Variables130 |

.

.

-

#### 1. INTRODUCTION

#### 1.1 The Flight Control Scenario

New developments in aviation technology will significantly improve an aircraft's performance while reducing its operating cost. Many of the new techniques deteriorate aircraft stability; to make it flyable by the average pilot, computer based flight control systems are used to modify its handling characteristics. A flight control system mates well with the fly by wire concept, the latter clearing the aircraft of a kluge of cables and pulleys that previously activated the control surfaces. Some examples of the new technology are the X29 forward swept wing fighter, an unstable but highly maneuverable aircraft, and the Boeing 7J7 aircraft, to fly in commercial service in the next decade.

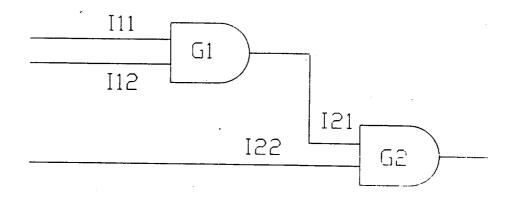

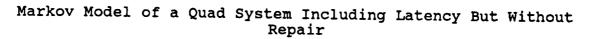

It is typical for a flight control system to have embedded processors performing the real-time control applications. A typical configuration contains an input processing subsystem that captures sensory data, a processor to implement the control laws, and an output processing subsystem to communicate the computed commands to the control surfaces. The computers that implement these control systems have become "flight critical"; that is, if the flight control system becomes inoperative, the pilot may be unable to control the aircraft. This differs radically from the autopilot on previous aircraft - if the autopilot failed, it was only necessary to revert control to the pilot in an orderly manner. The FAA requires that the probability of failure for a commercial aircraft be on the order of  $10^{-9}$  per hour of flight. In order to meet this overall figure, the probability of failure of the flight control system must be an order of magnitude lower.

It is beyond the state of the art at the present time to manufacture a single processor with a failure rate this low, even if one considers only random hardware failures. A state-of-the-art system composed of a single input subsystem, processor, and output subsystem would exhibit a mean time to failure of 2000 hours. The accepted method of constructing a highly reliable system is to use multiple redundant processors and employ failure logic in such a manner that, when one processor fails, it is removed from the system. The remaining processors continue to safely control the aircraft. It is reasonable to assume that such hardware failures are independent events, and, if the failure logic and redundancy management are perfect, then the probability of system failure is simply the probability of all the processors failing at the same time. With currently available hardware, between three and four processors are required to achieve a probability of system failure of 10<sup>-9</sup>. When the failure rate of the actuating system is considered, it is necessary to increase flight controller reliability to a probability of failure on the order of 10<sup>-10</sup>.

For a redundant system to operate successfully, the system must start each flight with all channels operative and fault free. The channels must be interconnected in such a way that it is possible to detect and isolate a failure in any channel and reconfigure the system without that channel. Usually, the outputs of all the channels are compared, and voting is used to detect and isolate a However, when the system is operating with only two failure. channels, a secondary detection means, such as self-test, is used to detect and isolate failures. Because the system operates in a dynamic environment, there is a limit to the time that this reconfiguration process can take. That is, during the reconfiguration time the aircraft is operating without control; there is a time after which the aircraft may no longer operate safely in this state. In the worst case scenario this time is equal to the length of time the aircraft can survive a hardover on the control surface.

It is not necessary for each channel to be an autonomous flight controller. Rather, monitoring may be done at a subsystem level and the voted output of a subsystem fed forward to the next redundant level. This adds move voting planes to the system, which relaxes the requirements of fault detection at each comparator-monitor. There is no limit to the number of voting planes that may be added to the system provided that it is demonstrated that each voting plane detects all the failures of the subsystems it votes on, and the overall probability of system failure (including failure of the additional monitoring hardware) is within acceptable limits.

Many system designs already exist for modularly decomposing a large avionics system into smaller subsystems that may be configured in a manner similar to the one just described. In the past, the processor itself could be partitioned into smaller modules, with each module containing its own independent redundant architecture, i.e., multiple replication with a comparator and voter. The probability of system failure could then be calculated from hardware considerations only (see, for instance, FTMP [1]). With the advent of microprocessors into the avionics world, the partitioning of the processor for monitoring is unfeasible. Therefore, a system architecture using the processor as a building block is used. Such an architecture is desirable from an economic standpoint, and has been studied extensively in the past [2,3].

There is an intuitive appeal to the system designer in placing the comparator at the processor output because it protects the control surfaces of the aircraft from receiving erroneous signals. Because of the complexity of the processor and its complement of memory devices, it becomes increasingly difficult to show when or if a single fault within the processor will reach the comparator and be detected. Under these conditions, it is possible for faults to accumulate within the processors in such a manner that, when a particular fault is propagated to the comparators, faults have occurred in more than one redundant channels. The latency period of the fault may have allowed a similar fault to occur in another channel resulting in premature system failure.

Recapping, in order to demonstrate the required survivability of an avionics system it is necessary to show that:

- the reliability of each of the redundant hardware modules is sufficient,

- the pre-flight test insures that all channels are fault-free,

- the voter/monitor detects and isolates all faults,

- secondary detection means detect and isolate faults as required,

- fault isolation time is within required time limits, and

- all faults propagate to a comparator quickly enough so that latent buildup does not reduce system reliability.

#### 1.2 Latency as a Factor in Highly Reliable Systems

It has been shown by many investigators [4,11,14] that the predominant cause of failure in highly reliable computing systems is not through exhaustion of spares. If faults in any portion of the system are not correctly detected by the failure logic, recovery will fail. For instance, faults in nonreplicated hardware may cause incorrect computations and this will not be detectable; these faults cause single point failures. The probability of system failure cannot be decreased below that due to single point failures by adding more spares (unless, of course, the spares make these single point failures redundant). The inability to detect all faults within a system is referred to as imperfect coverage, and the coverage of a system is defined as the probability that a fault in the system is detected so that proper recovery can occur.

The computation of coverage is complicated by a group of faults that may or may not be detected depending on the operational state of the system. Since the state of the system is a complicated function of its operating environment, one cannot say for sure when and if these faults will be detected. The time from occurrence to detection of these faults is called the latency time. When the latency time of a fault is significant, other mechanisms exist for system failure to occur:

- a latent fault in one module of a redundant system could combine with a new fault in a second module of the system to defeat the comparator, and

- two latent faults can exist in two separate modules of the system, and a particular state of the environment could activate them.

In order to properly estimate the probability of system

failure, it is necessary to associate probabilities with each mechanism that could cause it to occur. While the above latency mechanisms are well understood, a practical methodology for measuring the parameters necessary to compute the probabilities does not exist.

#### 1.3 Software Errors Modeled as Latent Faults

Designers have gained experience with generic hardware design problems in existing equipment, and the use of good engineering techniques has reduced them to an acceptable level. However, the experience of computer system designers is that software posses a significantly larger problem in validating error free operation than its complementary hardware. Reliability analysis is often based on the premise that the probability of component failure is random when exposed to the stresses and strains of normal operation. Moreover, two identical components subject to the same environment fail independently. However, software failures are not failures per se. Software never deteriorates with age; rather all failures result from design errors. In use, these errors are subject to "random excitation" and result in unpredicted system response.

To perform a system level reliability analysis, a "probability of failure" be associated with each software module. It would be more correct to say that the probability of excitation of existing latent design errors is required. In this sense, latent design errors are like latent hardware faults, and it seems reasonable to explore whether the same techniques can be used to measure software probability of failure as are being used to measure fault latency herein.

#### 1.4 Objectives of the Studies

The overall objectives of this work are to provide estimates of the system characteristics that are necessary to calculate the probability of system failure due to latency. It would be desirable to supply both a methodology for measuring latency, and an estimate of its effects in a typical avionics application.

It is also desirable to measure the probability of failure of the software embedded in a flight critical piece of hardware using similar techniques to those used for measuring hardware latency.

### 1.5 <u>Simulation as a Tool in the Reliability Estimation for Both</u> <u>Hardware and Software in a Highly Reliable System</u>

To achieve the above objectives, simulations were constructed

that were appropriate for the type of system being tested (i.e., hardware or software). The actual reliability estimation process consisted of three tasks:

- <u>Markov models must be constructed to relate the probability of</u> <u>system failure to measurable system characteristics</u>. Markov models of latent faults were developed, and have been expanded herein. Markov models of the software modules were also constructed.

- <u>A simulation of the system must be constructed and its</u> <u>characteristics measured</u>. A fault simulation language called GGLOSS was developed under NASA funding [15]. GGLOSS is a special purpose logic simulation program which is gate level and very high speed. GGLOSS is capable of simulating multiple processors with different software programs running concurrently. It is envisioned that GGLOSS will be used to demonstrate the reliability of a flight control system. While many high quality gate level logic simulator are available in the marketplace, they cannot be used for this purpose because:

- they cannot accommodate the number of gates required, and

- their speed of execution is too slow.

The circuit description is presented to GGLOSS in a standard Partslist format. It is important to emphasize that GGLOSS was never intended as a circuit design tool. Consequently, it lacks many of the features normally contained in a commercially available simulator. It is assumed that the circuit will operate properly in the unfaulted state.

GGLOSS performs statistical fault analysis of the system. That is, GGLOSS inserts a number of random faults into the processor while it executes its software. The results are recorded, and a postprocessor reports the failure statistics to the user in a format meaningful for conducting reliability studies.

A separate simulation of the process environment (aircraft landing, etc.) was constructed for software validation.

- <u>The Markov model must be solved</u>. Models of a simple processor with simple flight control programs were used to measure system characteristics that were then used to numerically solve the Markov models for probability of system failure. Results from simulations for software validation were used to evaluate software reliability.

### 2. THE GGLOSS SIMULATION

#### 2.1 The GGLOSS Simulation Methodology

Examining the faulted behavior of a processing system requires a simulation methodology that emulates logic network operation. In addition, statistical techniques are needed to inject faults into the system in such a manner that the simulation results can be used to accurately predict failure characteristics of the hardware. The required methodology was designed by considering:

#### - a mathematical model of the faults to be considered

The mathematical model for the faults in GGLOSS is a stuck-at-zero or stuck-at-one fault at each node of a gate level equivalent circuit of the processing system. The use of pin level faults was considered in earlier work [6], but the results were too optimistic to be reliable. That is, the advent of VLSI hides many of the intermediate nodes of the system within a chip, and these faults are not tested under pin level assumptions. It also appears that a fault on an intermediate node is more likely to remain latent than a fault on a pin.

To model LSI and VLSI circuits, each device is represented by its manufacturers supplied gate level equivalent circuit.

## - <u>a simulation technique that incorporates the faults and accurately predicts the response of the processing system</u>

The simulation technique used in GGLOSS is parallel fault simulation. Parallel simulation takes advantage of the fact that logical operations incorporated in the instruction set of a digital computer operate independently on each bit of the computer word. If the simulation is written in such a manner that only boolean operations are used, then each bit position in the host computer word can be used to simulate a different version of the same logic network. Each version finds the response to a different fault. On a VAX computer, thirty two different faults can be simulated on the processor at the same time.

To increase the speed of GGLOSS, it is assumed that all sequential logic being simulated is synchronous and no pulse generation is allowed. This lack of pulse, or transient, signals allows GGLOSS to compute only the steady state output of each combinational network. Modern logic design precludes the use of asynchronous circuitry.

#### - <u>a statistical technique for controlling fault injection and</u> <u>interpreting the results of the simulation</u>

To obtain failure statistics for the system, a probability of

occurrence is assigned to each fault in its fault set. The following rules were utilized for assigning probabilities to gate level faults:

- The failure rate for each device is obtained from the applicable military handbook,

- The failure rate of the device is equally distributed over the gates of the equivalent circuit.

- The failure rate of a gate is equally distributed over the nodes of that gate.

- o Stuck-at-one and stuck-at-zero faults are equally likely.

The probability of occurrence for all the faults in the fault set is summed to obtain the probability of a fault occurring within the system.

If every fault is simulated for every possible input, the conditional detection probabilities of each fault is known. These detection probabilities can be combined with the probability of each input to obtain overall occurrence of detection characteristics for the system, such as fault coverage, latency time, etc. Often, the number of possible faults is too large to allow simulation of every one. In this case, Monte Carlo techniques can be used to obtain approximate results by proceeding in the following manner:

- Faults are placed in a numerical ordering for selection purposes

- A cumulative distribution function for the ordering is generated based on the probability of occurrence of each fault

- A random number is selected within the range of the cumulative distribution function

- o This number is mapped back through the CDF to a specific fault

The last two steps in the above process are repeated until a list of faults is generated. These faults are simulated, and the results are used to calculate the overall detection characteristics of the system. The error in a detection characteristic obtained in this manner depends on the value of the detection characteristic, the number of faults simulated, and the desired confidence level. However, calculation of error is straight forward as illustrated in [6]. When this error is considered unacceptably high, the Monte Carlo process is repeated for a larger fault sample.

### Choice of Simulation Technique

The behavior of a particular digital network can be checked under the fault model either analytically, or by one of three fault modeling techniques.

Analytical techniques require examining the topology of a network to determine what faults can and cannot be detected at the If the boolean equations describing the network were output. available for the unfaulted case and for a faulted case, then they could be solved in such a way as to predict under what input conditions the fault could be detected at the network outputs. One way of doing this is to examine the faulted gate and determine what values on the input nodes induce a boolean value at the gate output that is different from the faulted case. The input nodes are then traced backwards to the network inputs to determine if an input set exists that induces this gate output. This process is known as failure excitation. The output of the faulty gate is then traced to the network output to see if its effects are measurable. This process is known as path sensitization. If both failure excitation and path sensitization are present for each failure, then it is detectable under the proper input vector. An analytic technique that performs the above calculations on boolean equations is called the D algorithm.

The general simulation of an electrical circuit involves the solution of differential equations representing lumped circuit parameters. Such a simulation will correctly predict both the steady state and transient behavior of the system. Simulation of logic circuits is usually simplified by requiring that only the steady state behavior be simulated. The steady state solution can be updated after the network has reacted to an input stimulus. Let the output of every gate represent a state variable of the system. Then the circuit be represented by a set of simultaneous boolean difference equations of the form:

$O_{x}(k+1) = B(I_{1}(k), I_{2}(k), \dots, I_{n}(k))$

where  $O_{1}$  is the output of gate x at the k+1 interval

B is a boolean expression of its arguments

I is the nth input to gate x

The exact form of these equations depends on what additional assumptions have been made about the circuit.

In the <u>unit delay</u> simulation, it is assumed that each gate exercises a boolean equation of its inputs, but with a small time delay (usually on the order of 5-10 nanoseconds, depending on the logic family). The boolean equations can be iterated on a time base that represents this unit delay. For a given set of circuit inputs, the boolean equations are solved on a digital computer repeatedly until the network reaches an equilibrium or steady state value, which is the response of the network to these circuit inputs. As in any iterative solution technique, it is not guaranteed that convergence will occur. However, convergence will occur if the network is feedforward only. It is noted that:

- unit delay simulation correctly predicts that portion of the transient response that can be represented as a boolean change, and

- if the network is poorly designed, there is no guarantee that a steady state solution will be reached.

One disadvantage of unit delay simulation is the amount of iterations required to reach steady state. Even in a network of N gates that is feed forward, this can amount to N evaluations of the entire network, or  $N^2$  equations. However, by proper ordering of the equations, this can be reduced to one evaluation of the network equations. This ordering will be referred to as a p-ordering.

In many applications, only small portions of the circuit change boolean value for a given interval of time. The propagation of such a change is often "blocked" somewhere along the network by a single gate which feeds forward its previous value even after its inputs have changed. To take advantage of this phenomenon, one could retain the previous state outputs of the gates and evaluate only those gates whose inputs have changed at the beginning of each This process is repeated until no inputs to any gates iteration. have changed from the previous iteration, at which time the network has reached a steady state. The changing of input values for a gate is referred to as an "event", and this type of simulation is called event driven simulation. Statistically, most network simulations result in fewer gate evaluations using this technique. One disadvantage of the technique is the amount of simulation code required to do the bookkeeping.

The logical operations indicated by the boolean equations are performed by computer instructions that operate independently on each bit of the computer word. If the simulation program is written in such a manner that boolean operations only are used, then each bit position in the host computer word can be used to simulate a different version of the same logic network. However, each logic network can have a different boolean value on its inputs. In this manner, the same amount of host computer time can be used to simulate up to 32 different networks on a VAX host, each reacting to a different possible set of inputs. Let the presence of a stuck-at-one, stuck-at-zero fault be modeled as an input to the system for each gate. Then a large number of faults can be simulated in a small amount of host time using this method, which is commonly called <u>parallel fault simulation</u>.

One disadvantage of parallel fault simulation is that it must be implemented on top of a unit delay simulation, which is often time inefficient. However, by p-ordering the gates in the simulation, the parallel simulation can be made very efficient.

GGLOSS was initially designed to be a parallel logic

simulator. (However, later improvements allow other simulation techniques to be incorporated into the simulators GGLOSS produces). To increase the speed of GGLOSS, it was also assumed that all the sequential logic being simulated was synchronous, i.e. no asynchronous pulse generation is allowed. The lack of asynchronous circuitry allows GGLOSS to compute only the steady state output of each combinational network ignoring transient response. Modern logic design precludes the use of asynchronous circuitry.

Most microsequencer controlled logic is designed so that all flip-flops change state at the same instant of the system clock cycle. This is usually either the leading or trailing edge of the clock, and the remainder of the clock cycle time is used for the logic network to stabilize. GGLOSS works most efficiently with this type of logic network by evaluating the boolean logic equations only once for each clock cycle. This requires some special treatment of clocking in flip-flops, which occurs within the flip-flop macros.

Some logic networks which operate synchronously use both the leading edge of the clock pulse for certain flip-flops to trigger and the trailing edge of the clock pulse for triggering others. In the "toy" microprocessor, there were two timing signals that used the opposite edge of the clock from the rest. This created a problem for GGLOSS, and two solutions were developed to overcome it:

- modify the simulation to evaluate all the gates once every leading clock edge and once every trailing clock edge. This has the advantage that the user need not concern himself with which edge a particular flip-flop is triggered. However, it has the disadvantage that it requires twice as much host CPU time to execute each simulated clock cycle. The modification to the simulator requires changing the model of the flip-flop as given in the BLISS library of logic functions.

- force those flip-flops that are clocked from timing signals on the opposite edge to be evaluated last. This can be done by using the "fictitious clock" concept which was mentioned previously. In this case, the fictitious clock represents a half clock cycle delay.

#### 2.2 Some New Features Added to GGLOSS

The original version of GGLOSS was constructed by J. McGough and F. Swern at Bendix, and called IGGLOSS. One objective of this work was to improve IGGLOSS to make it useable for validation studies. Some improvements that were initially made to IGGLOSS were:

#### Automatic Fault Injection

The fault insertion mechanism was modified so that a large number of randomly chosen faults can be injected, and the simulator will return fault detection statistics. To accomplish this, the following changes were made to GGLOSS.

The GGLOSS compiler inserts provisions in the simulation for faulting every node of every gate in the model. Each prospective fault is assigned a number, and an index dataset is created that associates each number with the name of the gate and node it faults.

The user supplies an input dataset that contains a probability of failure for each gate type used in the simulation. GGLOSS uses this data to compute a cumulative probability of failure distribution for the logic being tested. When GGLOSS is run, it asks the user how many faults to inject. Faults are then chosen at random using the cumulative distribution and the random number generator on the VAX. The list of gates to be faulted is written out to a dataset. While the BLISS simulation is running, it reads the list of gates to be faulted, and simulates up to 31 faults. If more than 31 faults were to be injected, the simulation is repeated until the fault list is exhausted.

At the end of each simulation run, the name of the fault simulated is looked up in the 'fault index' dataset and placed in the detect dataset. A list of faults not detected is also produced.

## Accommodate 32 different ROMS

The simulation was modified to optionally run a single copy of 32 different machines executing in parallel, each running from a different copy of ROM. Because of the parallel simulation technique, the machines would be running bit synchronous. In order for the machines to communicate with one another, a common memory area can be set up that can be accessed by each machine. A single fault is injected into one of the machines, and the recovery mechanism of the system can be tested.

## Accommodate multiple faults in a single machine

The simulation was modified so that multiple fault situations might be studied. In this case, a total of 31 faulted machines is simulated, but two or more faults will be injected per machine. A prompt from GGLOSS during compilation of the simulation sets the number of faults injected per machine.

### Specification of Initial Conditions

The user may wish to specify initial conditions for each simulation. To simplify the process of initialization, GGLOSS assumes that all initial conditions are zero. The user may then specify an initial condition of one for the output of any gate(s) in the simulation.

This is accomplished by prompting while the simulation is being compiled. The user specifies the name of the output signal of the gate as given in the partslist. The prompt is repeated over and over again until the user indicates he is satisfied with the set of initial conditions.

#### Extended Test Pin Coverage

One output of the GGLOSS simulation is a table of faults followed by the test points that detect these faults. An entry is made into this table every clock cycle that the signal at the test point differs from the nominal case. At the end of the simulation, a complete fault dictionary has been constructed.

#### Memory Mapped I/O

One can now simulate inputs and outputs to the outside world, using memory mapped I/O. The actual values of input signals are contained in a dataset, one dataset record for each clock cycle that an IO signal is referenced. It is assumed that the user knows the proper sequence of input values required for each particular experiment a priori. An output signal is considered to be a monitoring point, and any deviation in output between different machines is recorded as detection of the failure.

#### Shared Memory

When GGLOSS is used to simulate a redundant processor complex, each group of processors can communicate with one another through shared memory. The shared memory is available to all the processors in the complex so that processor interaction and software monitoring and recovery can be simulated.

#### Intermittent Faults

An intermittent fault model was be developed and programmed into the simulation. This particular fault model allows two types of intermittent faults: single incident and cyclic. In the cyclic fault model, the user specifies the frequency and duration of intermittency. In the single incident model, the user specifies the starting and ending clock cycle of the fault.

#### Expand Library of Bliss Coded Primitives

This task involved using a catalog of MSI and LSI logic to expand the GGLOSS primitive library to include most of the commonly available blocks used in logic design.

#### Faults in RAM

This task involves modifying the RAM model so that stuck at faults can be simulated. One may currently inject faults in RAM by specifying the word address, bit number, and stuck-at-one or stuck at zero. A dataset is supplied to GGLOSS which describes the memory locations to be faulted.

## Tasks to be Modified or not to be Undertaken

The initial plans for modifying IGGLOSS contained items which were later modified as new directions in the development of GGLOSS as a simulator were planned:

### Network Partitioning

A parallel fault simulation of a processor contains a large number of prospective gates to be faulted. However, the procedure only allows 31 different gates to be faulted each time the simulator is run. In the Bendix BDX930 simulator, simulation time was reduced significantly by dividing the processor into four partitions. Four different simulators were constructed, each allowing only one quarter of the processors gates to be faulted. After a large number of faults were selected, they were sorted into groups corresponding to the partitions. By running each group on its corresponding simulator, the correct results were obtained at a significant savings in execution time.

Discussions with RTI at Langley indicate that future development of the simulator would change the fault simulation mechanism used in the simulator. In the new technique, every gate would contain a unconditional branch statement that would bypass fault simulation. Memory modification techniques would be used to change the unconditional branch statements for those gates that are faulted. The advantage of this technique is lower overhead in the fault injection process.

Because of the lower overhead in the new technique, there is little to be gained by partitioning the network as described above. Therefore, this task is being held in abeyance pending future decisions on the fault simulation mechanism to be used.

#### Multiple Fictitious Clocks

The original role of the fictitious clock was to force the

evaluation order of the logic. Multiple fictitious clocks was supposed to allow different clock periods to be used within the simulation.

Many of the problems in getting the simulator to operate correctly with the model of a processor centered around the use of fictitious clocks. It was easier building a circuit model without them. However, they were useful in simulating a half clock cycle delay.

It is unclear at this point what fictitious clocks will be used for in the simulation. However, some thought will be given to the problem of how circuit timing (i.e., half cycle delays, etc.) can be properly simulated.

#### Fault Collapsing

This task requires comparing faults in a large fault list and deciding which faults have exactly the same effect on the network. This would be done from the topology of the network. Once a list of equivalent faults has been found, each equivalency group need be simulated only once. In a large combinatory network, this can represent a considerable savings in execution time. However, more work is needed to synthesize the algorithm to do this, and work on this task is continuing.

#### 2.3 Processing Systems Described Across Multiple 8DL Files

One problem with the IGGLOSS version of GGLOSS was that an entire processing system had to be described as a single module using a single SDL file. In systems containing a large number of logic gates, this was cumbersome and severely stressed the storage capacity of the GGLOSS program. A better approach is a modular one, breaking the simulation down into different SDL files and allowing GGLOSS to translate each SDL file separately. In the current version of GGLOSS, large processing systems may be represented in this manner.

Decomposition into modules is very natural to digital design, as digital systems are built hierarchically from chips into boards, and boards into systems. It is possible for a VLSI chip to be modeled by a software module and used multiple times within the simulation. The chip's pinout gives the signals that cross the module boundaries. In other cases, partitioning occurs solely due to module size, and choosing signals to cross module boundaries is not as natural as using a chip's pinout.

Each module is represented by a separate SDL file, and is compiled by GGLOSS into a separate BLISS program. To construct a modular simulator, it is the responsibility of the user to supply the appropriate SDL files to GGLOSS, including:

- at the top of the hierarchy, <u>a single SDL file that describes</u> <u>the system</u> using partitions, chips, and gates to be described in lower levels,

- additional SDL files to describe partitions of the system using both gates and lower level modules as required,

- any additional SDL files describing modules at lower levels,

- a library of primitives representing gates (same as the old GGLOSS library file), and

- sufficient gate failure statistics for GGLOSS to compute the failure rate of a module, and all modules in the hierarchy.

An example of a modularly constructed simulation is given in Figure 2.3.1.

#### CONNECTIVITY OF MODULES

There is a caveat in this partitioning process when working with parallel simulations. In the parallel method of simulation, the ordering of statement execution is extremely important. When GGLOSS works with a single SDL file describing a large system, its "P - ordering" algorithm almost always assemble a simulation module that will work properly when there are no feedback loops in the system. However, partitioning implies that GGLOSS cannot easily "shuffle the statements from different modules" to find this correct ordering, and a poor partitioning may result in an unusable simulator. When this occurs, there will be no correct "P ordering" of the higher level modules. GGLOSS can help the user by giving diagnostic information to help pinpoint which submodules or gates it is having trouble ordering.

Consider first how the user would handle this partitioning problem. One solution would be to break every module down into a number of submodules such that the interconnection characteristics of the submodules guarantees the existence of an overall ordering for the system. A possible technique would be to translate each module into BLISS using GGLOSS and note what problems GGLOSS has in "P - ordering" the module. Modules which GGLOSS has trouble ordering can then be broken down into smaller submodules, and the process repeated until a good simulator is built.

It seems desirable to solve the problem within GGLOSS, rather than hand it to the user. GGLOSS must examine the topology of each module, and determine the number of submodules that are required. In this case, all the submodules will be contained in a single BLISS module, existing as subsections of that module. The BLISS code would contain a variable indicating which submodule the caller wishes to execute. For "P - ordering" purposes, higher level GGLOSS routines treat the single BLISS module as separate submodules, and generate calls indicating which submodule to execute.

To develop the topological algorithms, let the inputs to a module be represented by a binary vector I and the outputs be represented by a binary vector  $\underline{O}$ . Then there exists a binary transfer matrix T that relates the circuit outputs to the circuit inputs, i.e.,

$\underline{O} = T \underline{I}.$

Each element of T represents a boolean transfer function between a particular input and a particular output. The exact values of the elements of matrix T are not of interest, only whether or not the element is a logical zero. A matrix T' is constructed by substituting logical ones in matrix T for nonzero transfer elements, and T' represents the connectivity of the module. An example of the T' matrix is given in Figure 2.3.2. If all the elements of T' are nonzero, then there is nothing further that can be done to break this module into submodules, since each output requires the knowledge of all the inputs for its computation.

When some of the elements of a specific row are zero, its corresponding output can be computed without knowing the values of those inputs whose columns contain the zeroes. Hence, each row in T' which contains a different pattern is a candidate for a separate submodule. The construction of the submodules and the order of their call must be such that the proper evaluation of the module occurs; however, this can be ascertained using the "P - ordering" algorithm as it already exists.

#### MODULE DATA FILES

When GGLOSS compiles a module from SDL into BLISS, it generates a file containing data about the module. This file contains:

- the name of the module,

- the number and values of any initial conditions on the module,

- the number of memory elements in the module,

- the failure rate of the module and a cumulative fault distribution among all the gates of the module,

- detection points within the module,

whether the input pins are in common or passed as parameters, and

- the template of the calling statement including the order of the arguments.

This file is created in the GDAT: area of disk and has the file extension of .FTB.

The file has three uses:

#### - Computing the gate level equivalent of higher level modules

In order to properly compile a multi-module simulation, modules must be compiled working up the hierarchy chain. Each succeeding level of the hierarchy requires information about lower levels; specifically, the calling template of all lower level modules and their gate level equivalents. The gate level equivalent and its cumulative failure rate for each module is read directly from the FTB file.

## - Generating complex simulations without recompiling each module

In order to avoid recompiling all modules each time the simulator is rebuilt, the INCLUDE command can be used to read the required data from the FTB file. This is convenient and time saving if a library of VLSI chips is built to be used in constructing complicated network simulations.

## - <u>Generating new fault simulation lists without recompiling the</u> <u>simulation</u>

In the Monte Carlo environment, it may be desired to run the simulator again with a different random selection of faults. This

can easily be done by INCLUDEing the highest level module and generating a new faults set with the FLTGEN command.

\$ R GLOSS GLOSS> COMPILE GDAT: JEANX1.SDL, FAULT TOTAL NUMBER OF FAULTS IS 906 14 COMPONENTS IN THE FAILURE RATE TABLE, FAILURE RATE FOR THE MODULE IS 1.3111077E-08 NUMBER OF STATEMENTS = 132 GLOSS> COMPILE GDAT: JEANX2.SDL, FAULT TOTAL NUMBER OF FAULTS IS 376 14 COMPONENTS IN THE FAILURE RATE TABLE, FAILURE RATE FOR THE MODULE IS 5.1111111E-08 NUMBER OF STATEMENTS = 61 GLOSS> COMPILE GDAT: JEANX3.SDL, FAULT TOTAL NUMBER OF FAULTS IS 410 14 COMPONENTS IN THE FAILURE RATE TABLE, FAILURE RATE FOR THE MODULE IS 6.5111112E-09 NUMBER OF STATEMENTS = 67 GLOSS> COMPILE GDAT: JEANXT.SDL, FAULT, TABLE=GDAT: TOYFAIL.DAT TOTAL NUMBER OF FAULTS IS 1692 14 COMPONENTS IN THE FAILURE RATE TABLE, FAILURE RATE FOR THE MODULE IS 2.4733000E-08 NUMBER OF STATEMENTS = 4 GLOSS> MEMORY RAM, TYPE=RAM, ADDBITS=8, -GLOSS> DATABITS=8, INIT=GDAT: TOY.MEM, FAULT, LENGTH=32 GLOSS> BIND TOY, CYCLES=300, PRINT

A Modularly Constructed Simulation

Figure 2.3.1

|   |       | INPUTS           |                  |                  |                  |             |                       |

|---|-------|------------------|------------------|------------------|------------------|-------------|-----------------------|

|   |       | B<br>I<br>N<br>1 | B<br>I<br>N<br>2 | B<br>I<br>N<br>3 | 8<br>I<br>N<br>4 | C<br>I<br>N | A<br>L<br>U<br>E<br>N |

| 0 | ALU01 |                  |                  |                  |                  |             | 1                     |

| U | ALU02 |                  |                  |                  |                  |             | 1                     |

| T | ALU03 |                  |                  |                  |                  |             | 1                     |

| P | ALUO4 |                  |                  |                  |                  |             | 1                     |

| U | CARRY | 1                | 1                | 1                | 1                | 1           |                       |

| T | C7NM1 | 1                | 1                | 1                | 1                | 1           |                       |

C7NM2 1 1 1 1

S

An Example of a Connectivity Matrix T' Figure 2.3.2

25

## 2.4 <u>Simulation of Functional Blocks</u>

GGLOSS is capable of simulating up to 32 different faults within the same parallel run. In practice, one of the parallel executing simulations is always the good system, acting as a reference to determine when fault detection occurs. This means that 31 different faults are being evaluated during each simulation run on a VAX machine. The fault set of even a small processor contains more than ten thousand faults - most of which are not active during a given simulation run. Thus, a large portion of the logic is running "true-value"; that is, it is not simulating faults, but rather propagating the results of faults occurring in other logic gates.

Unfortunately, gate level logic simulation does not efficiently simulate this propagation phenomena. In most cases it is faster to functionally characterize portions of the logic that are unfaulted. For instance, it may take a hundred statements to simulate an ALU chip at the gate level while it takes only a few statements to functionally describe the chip. When a functional simulation of a module executes significantly faster than the equivalent gate level simulation, there may be a decrease in GGLOSS execution time by including that functional module. The objective of this portion of the study was to develop a methodology that would allow simulations to be constructed consisting of a combination of modules described functionally and at the gate level. In addition to decreased simulation time, there are other advantages of the functional simulation technique:

- ability to use a simplified description of peripheral hardware,

- ability to debug large simulations using simplified functional descriptions of hardware not yet simulated at the gate level, and

- ability to include environmental and analog simulations.

#### CONSTRUCTION OF FUNCTIONAL LEVEL MODULES

Functional level modules are constructed using the following groundrules:

## - <u>functional level modules simulate input/output relationships</u> <u>only</u>

Functional level modules use the same pinout signals as gate level modules, but they need only simulate the functional relationship between the pins. This means that the internals of the module can be simplified in such a way as to reduce the amount of necessary computation, as long as it produces the correct answer at the output pins. However, to construct such simplification requires an individual to examine the circuit in each module and synthesize a "custom" subroutine representing that module.

## - functional level modules simulate one version of the network only

Functional level modules do not utilize parallel simulation, and therefore simulate one version of the network only. Thus, a functional level module must be called once for each active version in the parallel simulation. To correctly keep track of the different versions, the functional level module is passed a state storage array to store all the results of computation for this version. The same functional module can be called repeatedly in a loop to simulate all the active versions of the system as long as the calling module changes the state storage array it passes with each call.

#### - functional level modules may contain analog simulations

Functional level modules may contain continuous differential equations simulated in the standard manner, i.e. using any of the well known integration techniques such as Eulerian integration, Runge-Kutta, etc. These modules share in common with the control routines a time base which is used to synchronize any analog simulation with logic simulation.

#### SIMULATION ARCHITECTURE WITH FUNCTIONAL MODULES

To make the maximum use of functional computation, all modules but one are modeled at the functional level while the remaining module is modeled at the gate level using parallel simulation. Faults are injected at the gate level in the latter module only. An interface routine is provided that translates from the functional level output to gate level input, and back again.

Often it is not necessary for functional modules to be executed thirty two times to represent the thirty two versions being simulated. If a fault does not manifest itself by propagating to the output of the parallel module, then its functional state is the same as that of the unfaulted version. Even when a fault propagates to the output of the parallel module, its functional state may be the same as another fault being simulated which presents the same outputs from the parallel module. Faults which have shared the same functional state from the start of the simulation until a particular time will be termed equivalent, for they manifest themselves in exactly the same manner outside the faulted circuitry within that time frame.

Equivalent faults are modeled by a single execution of the functional modules. At the start of a simulation run, there is exactly one equivalence class for all faults including the unfaulted network since faults have not yet manifest themselves. As the simulation continues, the outputs of the parallel module are tested for a pattern that indicates a new equivalence class. When a new equivalence class is found, a new functional "machine" is set up, copying the state storage array from the "machine" that spawned it. This process continues, spawning new machines as required. However, when a fault is successfully detected, the machine representing its equivalence class is terminated. At any instant, the simulation must execute its functional modules as many times as there are active equivalence classes. The process is shown diagrammatically in Figure 2.4.1.

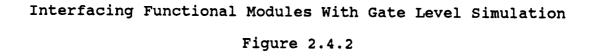

The logistics of simulating faulted machines is simplified by storing a fault mask for each equivalence class. A one in a particular bit position indicates that the parallel fault represented by this bit position is part of this equivalence class. Initially, the simulation starts out with one equivalence class and a fault mask of all ones. The fault mask is used to pack the input words to the parallel module from the outputs of the functional functional machine for a particular modules, i.e., when the equivalence class has an output of one to be input to the parallel module, its fault mask is ored into the appropriate parallel module On return from the parallel module, each output is input word. checked against the fault mask for each equivalence class - if all the bits that are one in the fault mask are the same (all either one or zero) in the output, then execution proceeds. If some of the bits that are one in the fault mask are mixed in the output, then a new machine is spawned. The procedure is shown in Figure 2.4.2.

#### TESTING OF FUNCTIONAL LEVEL SIMULATION

Functional level simulation was tested by implementing the ALU portion of the toy processor as a functional module. A partial listing of the module is shown in Figure 2.4.3. An interface module was constructed in BLISS that performed the checking and spawning operations described above, and is shown in Figure 2.4.4. Another FORTRAN module was programmed to keep track of both the average number of equivalence classes that existed in the simulation and the high water mark. The results of running this simulation is shown in Figure 2.4.5.

The functions performed by the ALU in the toy processor were simple to program. However, constructing and debugging the interface code in both BLISS and FORTRAN occupied much of the development time for this task. It was concluded that most of this code could have been generated by GGLOSS, and development of this capability should be part of the next contract period.

```

SUBROUTINE FTALU (CCLK, CCLR, MD0, MD1, MD2, MD3, MD4, MD5, MD6, MD7, ENBL,

1 ADDSUB, CNM1, ALUOY, ALU1Y, ALU2Y, ALU3Y, ALU4Y, ALU5Y, ALU6Y, ALU7Y,

2 ALU71, ALU72, ALU7Q, ALU7QB, CSTEP, STATE)

FUNCTIONAL SIMULATION OF TOY ALU

IMPLICIT INTEGER*4 (A-Z)

DIMENSION STATE(100)

IF (CSTEP.EQ.0) THEN

MD=0

IF(MDO.LT.0) MD=MD+1

IF(MD1.LT.0) MD=MD+2

IF(MD2.LT.0) MD=MD+4

IF(MD3.LT.0) MD=MD+8

IF(MD4.LT.0) MD=MD+16

IF(MD5.LT.0) MD=MD+32

IF(MD6.LT.0) MD=MD+64

IF(MD7.LT.0) MD=MD-128

STATE(5)=CCLK

STATE(6)=CCLR

IF (ADDSUB.EQ.0) THEN

STATE(2)=MD

ELSE

STATE(2) = -MD - 1

ENDIF

IF (CNM1.LT.O) THEN

STATE(3) = STATE(1) + STATE(2) + 1

ELSE

STATE(3) = STATE(1) + STATE(2)

ENDIF

IF (ENBL.LT.O) THEN

STATE(4)=STATE(1)

ELSE

STATE(4) = -1

ENDIF

ELSE

IF (STATE(5).LT.0) STATE(1)=STATE(3)

IF (STATE(6).EQ.0) STATE(1)=0

ENDIF

```

c c

С

С

· C

Example of a Functional Level Module

#### Figure 2.4.3

31

```

IF(BTEST(STATE(4),0)) THEN

ALUOY=-1

ELSE

ALUOY=0

ENDIF

IF(BTEST(STATE(4),1)) THEN

ALU1Y=-1

ELSE

ALU1Y=0

ENDIF

IF(BTEST(STATE(4),2)) THEN

ALU2Y=-1

ELSE

ALU2Y=0

ENDIF

IF(BTEST(STATE(4),3)) THEN

ALU3Y=-1

ELSE

ALU3Y=0

ENDIF

IF(BTEST(STATE(4),4)) THEN

ALU4Y=-1

ELSE

ALU4Y=0

ENDIF

IF(BTEST(STATE(4),5)) THEN

ALU5Y=-1

ELSE

ALU5Y=0

ENDIF

IF(BTEST(STATE(4),6)) THEN

ALU6Y=-1

ELSE

ALU6Y=0

ENDIF

IF(BTEST(STATE(4),7)) THEN

ALU7Y = -1

ELSE

ALU7Y=0

ENDIF

IF(BTEST(STATE(3),7)) THEN

ALU71=-1

ELSE

ALU71=0

ENDIF

IF(BTEST(STATE(2),7)) THEN

ALU72=-1

ELSE

ALU72=0

ENDIF

```

-

Example of a Functional Level Module ( Continued ) Figure 2.4.3

```

MODULE FUNCTION (ADDRESSING MODE (EXTERNAL = LONG RELATIVE,

NONEXTERNAL = LONG RELATIVE)) =

BEGIN

1

GLOBAL ROUTINE TOYALU(11, 12, 13, 14, 15, 16, 17, 18, 19, 110, 111,

I12, I13, 01, 02, 03, 04, 05, 06, 07, 08, 09, 010, 011, 012, J, K) : NOVALUE =

1

NAME: FUNCTIONAL INTERFACE ROUTINE

1

!

PURPOSE: INTERFACES BETWEEN GGLOSS PARALLEL GATE LEVEL SIMULATOR

1

AND BLOCKS WRITTEN AT FUNCTIONAL, NONPARALLEL LEVEL

1

!

!

INPUTS:

1

OUTPUTS:

I

ł

1

DESCRIPTION:

1

1

BEGIN

MACRO CHECKIN(INPUT) =

X = .INPUT AND .MASK[.I];

IF (.X NEQ 0) AND (.X NEQ .MASK[.I]) THEN

(NMASK = .NMASK + 1;

MASK[.NMASK] = .X;

MASK[.I] = .MASK[.I] AND NOT .X;

INCR L FROM 0 TO 99 DO FSTATE[100*.NMASK+.L]=.FSTATE[100*.I+.L];

EXITLOOP); %;

OWN I, REG, JMASK, 001,002,111,112,113,114,115,116,117,118,119,1110,

II11, II12, II13, 003, 004, 005, 006, 007, 008, 009, 0010, 0011, 0012, X, L,

MONE ;

OWN

FSTATE: VECTOR[3200],

MASK: VECTOR[32],

NMASK;

EXTERNAL ROUTINE FTALU : FORTRAN;

EXTERNAL ROUTINE PRI : FORTRAN;

EXTERNAL ROUTINE CNTF : FORTRAN;

1

REQUIRE 'GDAT: BLISCOM.R32';

1

IF . IGOP EQL 1 THEN

(NMASK=0; MASK[0] = -1; STOPMASK = -1; INCR I FROM 0 TO 3199 DO

FSTATE[.I]=0;IGOP=0; MONE = -1; CNTF(MONE, MONE););

```

Example of a Functional Level Interface Routine

Figure 2.4.4

1

```

JMASK = 0;

INCR I FROM 0 TO .NMASK DO

(MASK[.I]=.MASK[.I] AND .STOPMASK;

IF .MASK[.I] NEQ O THEN JMASK = .JMASK + 1;);

CNTF(JMASK, NMASK);

DO BEGIN

JMASK = .NMASK ;

INCR I FROM 0 TO .NMASK DO

BEGIN

CHECKIN(.I1);

CHECKIN(.12);

CHECKIN(.I3);

CHECKIN(.14);

CHECKIN(.15);

CHECKIN(.16);

CHECKIN(.17);

CHECKIN(.IB);

CHECKIN(.19);

CHECKIN(.110);

CHECKIN(.111);

CHECKIN(.112);

CHECKIN(.I13);

END;

END

UNTIL .JMASK EQL .NMASK ;

.01 = 0; .02 = 0; .03 = 0; .04 = 0; .05 = 0; .06 = 0; .07 = 0; .08 = 0; .09 = 0; .010 = 0; .011 = 0; .012 = 0;

INCR I FROM O TO .NMASK DO

IF .MASK[.I] NEQ 0 THEN

BEGIN

II1 = (IF (.MASK[.I] AND ..I1) NEQ 0 THEN -1 ELSE 0);

II2 = (IF (.MASK[.I] AND ..I2) NEQ 0 THEN -1 ELSE 0);

112 = (IF (.MASK[.I] AND ..I2) NEQ 0 THEN -1 ELSE 0);

II3 = (IF (.MASK[.I] AND ..I3) NEQ 0 THEN -1 ELSE 0);

II4 = (IF (.MASK[.I] AND ..I4) NEQ 0 THEN -1 ELSE 0);

II5 = (IF (.MASK[.I] AND ..I5) NEQ 0 THEN -1 ELSE 0);

II6 = (IF (.MASK[.I] AND ..I6) NEQ 0 THEN -1 ELSE 0);

II7 = (IF (.MASK[.I] AND ..I7) NEQ 0 THEN -1 ELSE 0);

II8 = (IF (.MASK[.I] AND ..I7) NEQ 0 THEN -1 ELSE 0);

II9 = (IF (.MASK[.I] AND ..I9) NEQ 0 THEN -1 ELSE 0);

II0 = (IF (.MASK[.I] AND ..I9) NEQ 0 THEN -1 ELSE 0);

II0 = (IF (.MASK[.I] AND ..I9) NEQ 0 THEN -1 ELSE 0);

III0 = (IF (.MASK[.I] AND ..II0) NEQ 0 THEN -1 ELSE 0);

III1 = (IF (.MASK[.I] AND ..II1) NEQ 0 THEN -1 ELSE 0);

II12 = (IF (.MASK[.I] AND ..I12) NEQ O THEN -1 ELSE 0);

II13 = (IF (.MASK[.I] AND ..I13) NEQ O THEN -1 ELSE 0);

FTALU(111,112,113,114,115,116,117,118,119,1110,1111,1112,1113,

001,002,003,004,005,006,007,008,009,0010,0011,0012,

CSTEP, FSTATE[100*.1]);

.01 = ..01 OR (.001 AND .MASK[.I]);

.02 = ..02 OR (.002 AND .MASK[.I]);

.03 = ..03 OR (.003 AND .MASK[.I]);

.04 = ..04 OR (.004 AND .MASK[.I]);

.05 = ..05 OR (.005 AND .MASK[.I]);

.MASK[.I]);

.06 = ..06 \text{ OR} (.006 AND

.07 = ..07 OR (.007 AND .MASK[.I]);

.08 = ..08 OR (.008 AND .MASK[.I]);

.09 = ..09 OR (.009 AND .MASK[.I]);

```

Example of a Functional Level Interface Routine

( Continued )

Figure 2.4.4

\$ RUN GSIM: EXEC 0 00:00:41.00 CPU: 0:00:16.94 BUFIO: 304 DIRIO: 12 ELAPSED: FAULTS 468 TOTAL CYCLES WAS 600 HIGH WATER MARK MACHINES WAS 1 AVERAGE NUMBER OF MACHINES WAS 1.000000 ELAPSED: 0 00:00:42.94 CPU: 0:00:17.17 BUFIO: 304 DIRIO: 14 FAULTS 125 TOTAL CYCLES WAS 600 HIGH WATER MARK MACHINES WAS 2 AVERAGE NUMBER OF MACHINES WAS 1.998333 ELAPSED: 0 00:00:42.91 CPU: 0:00:16.94 BUFIO: 303 DIRIO: 10 FAULTS 0 TOTAL CYCLES WAS 600 HIGH WATER MARK MACHINES WAS 2 AVERAGE NUMBER OF MACHINES WAS 1.9988333 ELAPSED: 0 00:00:39.77 CPU: 0:00:16.08 BUFIO: 304 DIRIO: 14 FAULTS 0 TOTAL CYCLES WAS 600 HIGH WATER MARK MACHINES WAS 2 AVERAGE NUMBER OF MACHINES WAS 1.9988333 ELAPSED: 0 00:00:44.34 CPU: 0:00:16.54 BUFIO: 305 DIRIO: 15 FAULTS 0 TOTAL CYCLES WAS 600 HIGH WATER MARK MACHINES WAS 5 2.275000 AVERAGE NUMBER OF MACHINES WAS 0 00:00:44.46 CPU: 0:00:17.39 BUFIO: 304 DIRIO: 15 ELAPSED: FAULTS 0 TOTAL CYCLES WAS 600 HIGH WATER MARK MACHINES WAS 8 AVERAGE NUMBER OF MACHINES WAS 2.335002 ELAPSED: 0 00:00:43.49 CPU: 0:00:17.49 BUFIO: 303 DIRIO: 10 FAULTS 0 TOTAL CYCLES WAS 600 HIGH WATER MARK MACHINES WAS 8 AVERAGE NUMBER OF MACHINES WAS 2.348333

Performance Results for a Single Functional Level Subroutine

Figure 2.4.5

# 2.5 <u>Simulation of Memory Blocks</u>

Processors and sequencers to be simulated with GGLOSS contain a number of memory elements such as PROM used to contain microcode, PROM used to contain program code, RAM used as scratchpad, and memory mapped I/O. The previous GGLOSS memory simulation was inadequate in simulating all these different memories, and this situation was addressed by an improved memory block simulation technique. The GGLOSS memory simulation now allows the construction of twenty (an arbitrary number which can be increased) different memory chips with a variety of characteristics that allows enough flexibility to simulate practical processors.

Memories are handled on a functional basis, allocating VAX storage for either read only or read/write memory. The former is allocated only once; the same copy is read by each of the thirty two different machines. The latter is allocated thirty-two times so that each machine can have its own copy of RAM to modify as necessary. It is noted that there is no attempt to model memory at any lower level, such as static vs. dynamic, and/or including memory cycle timing. It was concluded that this type of simulation would be desirable in many cases; however, it is best modeled by using gate level logic to simulate the timing and then interface the processing system to the functional simulation included in GGLOSS.

Other features that have been retained in the memory simulation:

- Multiple processors may be simulated by neighboring bit positions on the VAX communicating through common memory.

- Only a portion of ROM and/or RAM need be simulated to conserve space in large memory simulations. Failures which result in access to unsimulated portions of the memory will return a word of all ones.

- Both ROM and RAM can be initialized.

- Memory mapped inputs are simulated by subroutine, and may either be linked to functional blocks or read a dataset containing input values.

- Memory mapped outputs are now detection addresses which may be used in the same manner as detect pins to initiate postprocessing.

- A single memory chip may contain ROM, RAM and memory mapped I/O. This feature allows simplified simulation of processor operation without simulating the memory mapping logic.

- Both ROM and RAM memory may be selectively faulted by chip. ROM

faults randomly invert bits in memory while RAM faults are of the stuck-at-one, stuck-at-zero variety.

Memories are simulated in SDL using the MEMR primitive. However, the partsname for the memory is an eight character name that is used to reference that memory at simulation time. The GGLOSS MEMORY directive, described in the appendix, is used to associate memory attributes with memory chips using the partsname association. MEMORY also creates an initialization program to handle ROM loading.

# 2.6 Improving The GGLOSS Architecture for Other Simulation

# <u>Methodologies</u>

One design objective of GGLOSS was to produce a package that would simulate gate level hardware level with faults at speeds high enough so that phenomena such as fault latency could be studied. Parallel simulation methodology was chosen for maximum speed with faulted logic. Further, GLOSS reads a description of the logic under test and compiles a computer program that simulates that logic. However, after implementing GGLOSS, it soon became apparent that GGLOSS should be expanded to support more complex simulations including simulation modes other than parallel.

To accomplish this, building a simulation with GGLOSS was reorganized into a two stage process: -

o Build a P-ordered sequence of macro calls that represent the logic to be simulated. The translation process consists of three steps:

- Generate data declarations for every logic signal in the circuit being simulated.

- P-order the SDL description of the logic into an ordered list of simulation "blocks".

- Translate each simulation block into a macro sequence that describes its operation in a "neutral format".

o Translate the macro sequence into a target language for the simulation engine. This process also consists of three steps:

- Read in a macro definition file that expands each macro sequence generated above into a target language for simulation.

- Expand the macro sequences for each simulation block.

- Compile the tables required for table driven algorithms.

The above process was implemented, and shows many advantages over previous GGLOSS implementations. It allows GGLOSS to run on a variety of different computers, using a variety of different simulation languages, using a variety of different simulation techniques. More specifically, the languages GGLOSS can produce simulators for might include:

- o BLISS

- o FORTRAN

- o C

- o PASCAL

o Assembly Language

while the types of simulators that might be produced are:

o Parallel

o Event Driven

o Deductive

o Concurrent

The flexibility of GGLOSS should be apparent: GGLOSS can produce an optimum simulator for each situation with a minimum of effort on the part of the GGLOSS user.

To illustrate how the GGLOSS works, Figure 2.6.1 shows the output of the first stage of building a simulation while Figure 2.6.2 shows the macro definitions for the second stage that produces a FORTRAN parallel simulator. The next two sections describe how GGLOSS constructs Event Driven and Deductive simulators.

| \$MODULE I O REGS                         |                               |                 |

|-------------------------------------------|-------------------------------|-----------------|

| SMEXTNM MPSNEW                            |                               |                 |

| SMEXING AFONEW                            |                               |                 |

| SMEXINM ALULATCH                          |                               |                 |

| SMEXTNM ADDIATCH                          |                               |                 |

| SMEATING CNIRSTOR<br>SMEATING CS REG      |                               |                 |

| SMEXINM CS_REG<br>SMEXTNM IC AD RG        |                               |                 |

| SMEXINM IC AD RO<br>SMEXINM MAINSTOR      |                               |                 |

| SMEXINM MAINSTOR<br>SMEXINM MAPSTORE      |                               |                 |

| SMEXINM MAPSIORE<br>SMEXINM GP REGS       |                               |                 |

| SMEATNM GF_REGS<br>SMEXTNM TEMPREGS       |                               |                 |

| SMEXINM TEMPRESS<br>SMEXINM T1750A        |                               |                 |

| \$ROUTINE I O REGS                        |                               |                 |

| SREND                                     |                               |                 |

| \$EXTERN2 IINJECTOX                       | <b>IINJECT1X</b>              | I O REGS        |

| \$EXTERN2 OEDBIRX                         | ICLRDBIRX                     | I O REGS        |

| \$EXTERN2 GCDBIRX                         | SERIALX                       | I O REGS        |

| \$EXTERN2 GCSIGREGX                       | TESTMODEX                     | I O REGS        |

| \$EXTERN2 OEDBORX                         |                               | I O REGS        |

|                                           | ICLRDBORX<br>CLK1X            | I O REGS        |

| \$EXTERN2 GODBORX<br>\$EXTERN2 GOOD_MACHX | IDB N15X                      | I O REGS        |

| \$EXTERN2 IDB N14X                        | IDB N13X                      | IOREGS          |

| \$EXTERN2 IDB N12X                        | IDB N11X                      | I O REGS        |

| CEVEEDNO TOPNION                          | IDB N9X                       | IOREGS          |

| \$EXTERN2 IDB_N8X                         | IDB N7X                       | IOREGS          |

| \$EXTERN2 IDB N6X                         | IDB N5X                       | IOREGS          |

| SEXTERN2 IDB N4X                          | IDB_N3X                       | IOREGS          |

| \$EXTERN2 IDB_N4X<br>\$EXTERN2 IDB_N2X    |                               | I O REGS        |

| \$EXTERN2 IDB NOX                         | IDB_N1X<br>IB_N15X<br>IB_N12Y | I O REGS        |

| \$EXTERN2 IB NI4X                         | IB N13X                       | I O REGS        |

| \$EXTERN2 IB N12X                         | IBNIIX                        | <b>I</b> OREGS  |

| \$EXTERN2 IB N10X                         | IB N9X                        | <b>I</b> O REGS |

| SEXTERN2 IB N8X                           | IB N7X                        | IOREGS          |

| \$EXTERN2 IB N6X                          | IB N5X                        | <b>I</b> O REGS |

| \$EXTERN2 IB N4X                          | IBN3X                         | IOREGS          |

| \$EXTERN2 IB N2X                          | IBNIX                         | IOREGS          |

| \$EXTERN4 IB NOX                          | $I \overline{O} REGS$         |                 |

| \$LOCAL NNN259064_2_1                     |                               |                 |

| \$LOCAL NNN31606421                       |                               |                 |

| \$LOCAL NNN373064221                      |                               |                 |

| \$LOCAL NNN430064221                      |                               |                 |

|                                           |                               |                 |

----

\_\_\_\_\_

Example of GGLOSS Macro Output

Figure 2.6.1

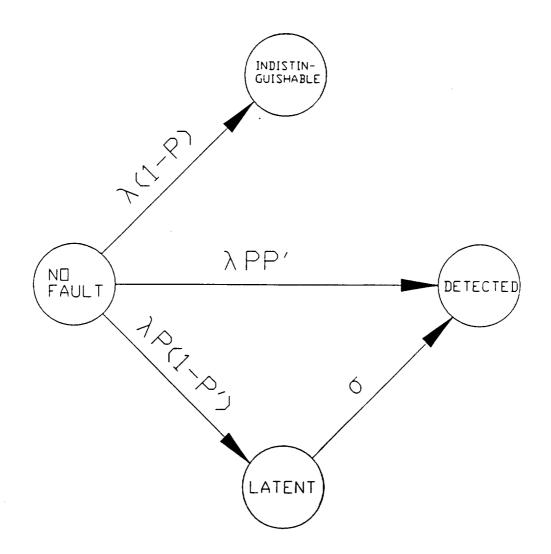

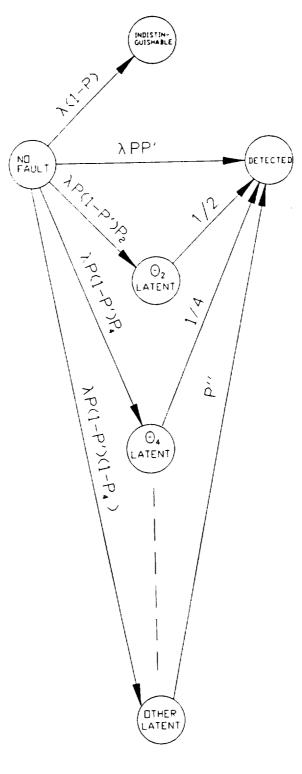

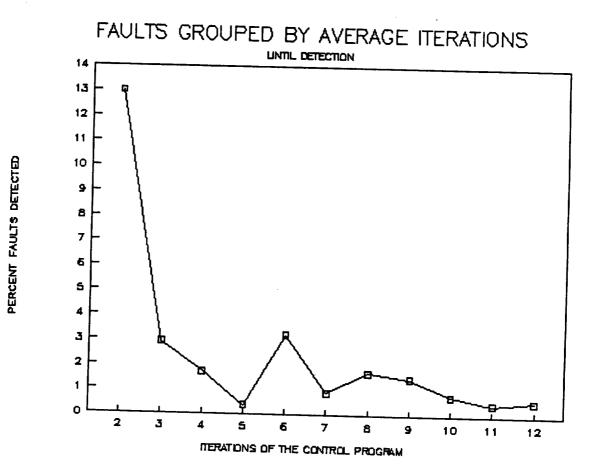

```