IN 33 - K 50 1 8 S 68 P

NASA Cooperative Agreement NCC 2-303

-.

•

# INVESTIGATION OF ADVANCED FAULT INSERTION AND SIMULATOR METHODS

FINAL TECHNICAL REPORT

covering the period June 1984 - August 1986

(NASA-CR-195241) INVESTIGATION OF N94-28511 ADVANCED FAULT INSERTION AND SIMULATOR METHODS Final Technical Report, Jun. 1984 - Aug. 1986 Unclas (Southern Colorado State Coll.) 68 p G3/33 0209828

Principal Investigator: Dr. W.R. Dunn Co-investigator: Dr. D. Cottrell Research Assistants: Joel Flanders Alan Javornik Michael Rusovick Institution: University of Southern Colorado Electronics Engineering Department 2200 Bonforte Blvd. Pueblo, Colorado 81001

## TABLE OF CONTENTS

| Report Summary1                                    |   |

|----------------------------------------------------|---|

| Notation                                           |   |

| 1.0 Introduction                                   |   |

| 2.0 Pin-Level Fault Modelling in Failure Modes and |   |

| Effects Analysis and Testing                       |   |

| 2.1 Pin Level Fault Model                          |   |

| 2.2 Gate-Level Fault Models5                       |   |

| 2.3 Limitations of Gate-Level Fault Models9        |   |

| 3.0 Semiconductor Failure Mechanisms and Modes9    |   |

| 3.1 Definitions                                    |   |

| 3.2 Survey of Available Failure Mode and Failure   |   |

| Mechanism Data Bases                               | ) |

| 3.3 Analysis of Failure Mechanism Data             | ) |

| 3.4 Analysis of Failure Mode Data                  | 3 |

| 4.0 Developing Pin-Level Device Models             | 3 |

| 4.1 Overview                                       | 3 |

| 4.2 Model Elements Based on Failure Mechanisms1    | 3 |

| 4.2.1 Interconnects                                | 3 |

| 4.2.2 Die Defects/Package Failures                 | 3 |

| 4.3 Model Elements Based on Failure Mode Data      | ) |

| 4.3.1 Open Circuits                                | ) |

| 4.3.2 Short Circuits1                              | ) |

| 4.3.3 Excess Leakage and Out-of-Tolerance          |   |

| Parameters1                                        | 9 |

| 4.3.4 Functional Anomalies                         | 9 |

| 4.4 Semiconductor Device Stress Testing1           | 9 |

| 4.4.1 Rationale Behind Semiconductor Stress        |   |

| Testing                                            | Э |

| 4.4.2 Experimental Setup2                          | ) |

| 4.4.3 Stress Testing Results2                      | ) |

| 4.5 Functional Fault Modelling2                    | 3 |

| 4.6 Summary                                        | 3 |

| 5.0 Conclusions and Indicated Research Directions2 | З |

| References                                         | 3 |

| Acknowledgements                                   | 9 |

| Acknowledgements                                   |   |

.

NASA Cooperative Agreement NCC 2-303

### INVESTIGATION OF ADVANCED FAULT INSERTION AND SIMULATOR METHODS

FINAL TECHNICAL REPORT

#### Report Summary

The cooperative agreement partly supported research leading to the open-literature publication cited below.

Additional efforts under the agreement included research into fault modelling of semiconductor devices. Results of this research are presented in this report which is summarized in the following paragraphs.

As a result of the cited research, it appears that semiconductor failure mechanism data is abundant but of little use in developing pin-level device models. Failure mode data on the other hand does exist but is too sparse to be of any (statistical) use in developing fault models. What is significant in the failure mode data is that, unlike classical logic, MSI and LSI devices do exhibit more than "stuck-at" and open/short failure modes. Specifically they are dominated by parametric failures and functional anomalies that can include intermittent faults and multiple-pin failures.

The report discusses methods of developing composite pinlevel models based on extrapolation of semiconductor device failure mechanisms, failure modes, results of (temperature) stress testing and functional modelling. Limitations of this model particularly with regard to determination of fault detection coverage and latency time measurement are discussed.

Indicated research directions are presented.

### Reference

Dunn, W.R., "Software Reliability: Measures and Effects in Flight Critical Digital Avionics Systems", 7th Digital Avionics Systems Conference, Fort Worth, Texas, October 13-16, 1986. Notation

- DTL = Diode-Transistor Logic

- FMEA = Failure Modes & Effects Analysis

- FMET = Failure Modes & Effects Tests

- LSTTL = Low Power Schottky Transistor-Transistor Logic

- RAC = Reliability Analysis Center

- SSI = Small Scale Integration

- VLSI = Very Large Scale Integration

INVESTIGATION OF ADVANCED FAULT INSERTION AND SIMULATOR METHODS

### 1.0 Introduction

In the design and development of a flight-critical digital system, it is necessary to prove that the system can tolerate single- and multiple-component faults. Two widelyused methods supporting such proof are Failure Modes and Effects Analysis (FMEA) and Failure Modes and Effects Testing (FMET). FMEA is usually performed very early in the design process either by hand or, in more complex systems, through fault simulation. FMET is performed toward the end of development and prior to initial flight test. In Failure Modes and Effects Testing, actual or simulated faults are inserted in the actual digital system (generally configured in ground-based, "iron bird" environment) in order to validate system fault tolerance. Both FMEA and FMET activities require knowledge of probable component failure modes.

This report addresses the subject of digital integrated circuit semiconductor failure modes. The study leading to the report was motivated by the suspicion that the permanent, "stuck- at" type failure modes characteristic of relay, transistor and small-scale integrated circuit logic might not fully embrace possible failure modes in many of the Medium Scale Integration (MSI) and Very Large Scale Integration (VLSI) components employed in modern, flight-critical digital system designs. The study was therefore undertaken with the (admittedly ambitious) objective of developing an approach for deriving practical fault models for MSI digital integrated circuits. The work was subject to two important, practical constraints:

Owing to limited resources, detailed study would be confined to a limited number of Low Power Schottky Transistor-Transistor Logic (LSTTL) devices. (These devices are extensively employed in modern flight systems.)

2) The study would employ only that semiconductor reliability data available to the general public. (Superior data lies within the semiconductor houses but is, in general, not available to the avionics designer.)

As the informed reader might suspect, it was quickly determined that the latter reliability data was of very limited usefulness in terms of fault model development.\*

<sup>\*</sup>At the time, workers at Hughes aircraft independently reached the same conclusion. See Reference 1.

For this reason, the originally-planned research activities were supplemented with laboratory stress testing of select LSTTL devices.

The remainder of this report is organized as discussed in the following.

Section 2.0 explains in detail what is meant by "fault model" and discusses past approaches to realizing fault models. Limitations of these models are discussed.

Section 3.0 presents definitions of semiconductor failure mechanisms and failure modes. Results of a USC survey and analysis of available failure mechanism and mode data bases are presented.

Section 4.0 describes several approaches to fault model development including use of semiconductor failure mode data and extrapolation of failure mechanism data. The section also contains a description of the test methodology and results of USC semiconductor stress testing.

Section 5.0 presents conclusions and indicated research directions.

2.0 Pin-Level Fault Modelling in Failure Modes and Effects Analysis and Testing

2.1 Pin Level Fault Model

Figure 2-1 shows the package outline of a general LSTTL device. In every device, two pins are dedicated to power supply source and return. The remaining pins are inputs and outputs. Under unfaulted conditions the device will output a predictable set of logic states (and/or state transitions) given a set of input states (and/or transitions) and (for sequential logic devices) a set of internal states. If there are failures internal to the device, output may be incorrect. To effect a pin-level fault model for the device, electrical characteristics at one or more pins are altered in such a manner that the resulting "new" device behaves exactly the same as the corresponding device with the internal failure.

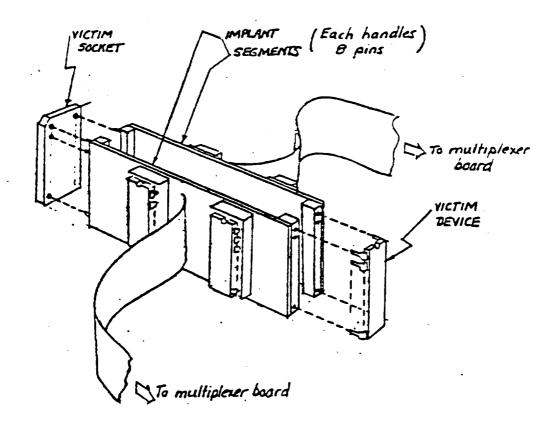

In a FMEA these characteristics are introduced analytically. In a FMET, special circuitry is interposed between the good device and the system circuitry as shown in Figure 2-2 and altered characteristics are electrically introduced at the device pins. (Reference 2 & 3.)

This report focuses on approaches (and limitations) for determining these pin-level characteristics for failures that can occur within the device. (The term "fault modelling" is used in this report to describe this process.)

## 2.2 Gate-Level Fault Models

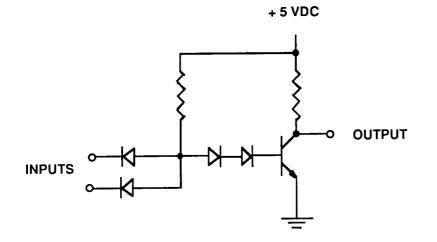

Prior to the introduction of integrated circuit logic (almost 30 years ago) it was relatively simple to correllate physical failures with the altered behavior of logic components. For example, the relay of Figure 2-3a could be associated with four fault characteristics: contact stuckopen, contact stuck-closed, coil short-circuited and coil open-circuited. Discrete component logic could be handled in a similar manner. For example, in the discrete component, diode-transistor-logic (DTL) gate of Figure 2-3b, one could directly associate known physical failures (open and shorted resistors, open diodes, collector-base opens, open solder joints, etc.) with behavior at the input/output terminals of the circuit.

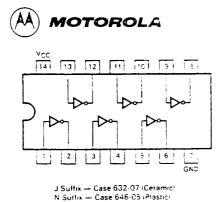

FIGURE 2-1 PACKAGE OUTLINE - LSTTL DEVICE

.

# FIGURE 2-2 FAULT INSERTION CIRCUITRY

(a) Relay

(b) Discrete Diode-Transistor LogicFIGURE 2-3 EARLY LOGIC DEVICES

The first digital integrated circuits consisted of single gates (such as the DTL gate of Figure 2-3b) implemented on a single chip. For reasons to be explained shortly (Section 3.3), on-chip physical failure mechanisms could not be translated to behavior at the output terminals. Instead, physical failures were considered in terms of altered behavior at the gate inputs and outputs which could be stuck-at-1, stuck-at-0, open-circuited or shortcircuited. Realistic FMEAs and FMETs could be performed for early systems employing these small scale, integrated gates by successively applying each of these failure characteristics to each pin in the logic circuit.

2.3 Limitations of Gate-Level Fault Models

This report is concerned with fault modelling of commercial, non-custom MSI, LSI and VLSI digital semiconductor devices. (As noted, USC detailed studies were confined to LSTTL SSI and MSI devices. Findings with these specific devices appear however to apply to higher levels of integration and to other semiconductor technologies.) In attempting to apply classical, gate-level fault modelling to this class of devices, one encounters several practical roadblocks:

1) With a few exceptions, semiconductor manufacturers do not provide gate-level circuit schematics of their integrated devices. Consequently, one cannot perform a gatelevel FMEA.

2) With early gate-level circuitry, it was possible to perform fault insertions (as a part of FMET) by opening and/or shorting gate inputs and outputs. In MSI and LSI, gates are integrated on the chip with the result that internal gate imputs and outputs cannot be physically accessed.

3) As will be seen in the next section, failure mechanisms within the device can lead to failure modes other than open-circuit, short-circuit and stuck-at behavior at the device pins.

### 3.0 Semiconductor Failure Mechanisms and Modes

### 3.1 Definitions

In what follows, the term <u>failure mechanism</u> refers to a physical anomaly within the device. <u>Failure mode</u> refers to altered electrical characteristics and/or behavior as a result of occurrence of the failure mechanism.

For example, a broken wire bond is a failure mechanism. It produces an open circuit failure mode at the pin to which it is connected.

3.2 Survey of Available Failure Mode and Failure Mechanism Data Bases

USC conducted a survey among some ten semiconductor manufacturers and three avionics firms in an effort to obtain failure mechanism and failure mode data to support pin-level fault modelling of select LSTTL devices. In the course of this survey, it was determined that these data are also collected by the DOD-sponsored Reliability Analysis Center (RAC) located at Griffiss AFB in New York.

Between the semiconductor manufacturers and the RAC, there is a copious amount of available data on digital semiconductor failure mechanisms. Failure mode data on the other hand is another matter. It is available only (with a few exceptions) from RAC which periodically publishes failure mechanism and failure mode data by semiconductor technology.

Tables 3-1 and 3-2 respectively summarize LSTTL failure mechanism and failure mode data taken from two RAC reports as referenced. Note that, in terms of the objectives of the study (to obtain pin level models of digital devices), these data represent the best\* information gathered in the study.

## 3.3 Analysis of Failure Mechanism Data

With the exception of wirebond failures, it is virtually impossible to directly correlate semiconductor failure mechanisms with behavior at the device terminals. (Again, it is assumed that details of the chip circuitry and layout are not known.) The reason for this is that die defects (or package defects that lead to die contamination) can be very local (e.g. bad metal contact on a single emitter) or regional (e.g. an oxide contamination effecting several transistors). With each defect, the digital circuit structure can be altered. Given the range of possible combinations of defects one is inclined to speculate that a device could exhibit every possible combination of outputs for any given input (and input history in the case of a sequential circuit).

\*We had originally hoped to find failure mode data for each chip type. Unfortunately, (RAC) published data on each device type is too fragmentary to attach any statistical significance to the distribution of failure modes of any given device.

## TABLE 3-1 - LSTTL Failure Mechanisms

## (SSI and MSI Devices)

1984 RAC Report (Ref. 4)

| Failure Mechanism | No. of  |

|-------------------|---------|

| (By Component)    | Devices |

## Percentage

| Die:             | 68 | 25.1 |

|------------------|----|------|

| Bulk Aspects     | 15 |      |

| Metallization    | 38 |      |

| Oxide/Dielectric | 10 |      |

| Surface          | 5  |      |

| Interconnects: | 24 | 8.8 |

|----------------|----|-----|

| Wire           | 9  |     |

| Wirebond       | 15 |     |

| Package:        | 179 | 66.1 |

|-----------------|-----|------|

| Seal            | 116 |      |

| Lid             | 54  |      |

| Die Attach Bond | 9   |      |

## TABLE 3-2 - LSTTL Device Failure Modes (Ref. 4) (SSI and MSI Devices)

| Failure Mode               | Percent<br><u>of Total</u> | <u>Adjusted**</u> |

|----------------------------|----------------------------|-------------------|

| OPEN                       | 3.4                        | 3.4               |

| SHORT                      | 4.1                        | 4.1               |

| DEGRADED                   | 22.4                       | 22.4              |

| Unknown*                   | 3.4                        | 0.0               |

| Leakage                    | 6.1                        | 7.2               |

| Parameter Out-of-Tolerance | 12.9                       | 15.2              |

| FUNCTIONAL ANOMALY         | 70.1                       | 70.1              |

| Unknown                    | 57.2                       | 0.0               |

| Non-Functional             | 2.7                        | 14.8              |

| Improper Output            | 9.5                        | 51.6              |

| Stuck-at-1                 | 0.0                        | 0.0               |

| Stuck-at-0                 | 0.7                        | 3.7               |

\*"Unknown" means failure mode was in major category (DE-GRADED or FUNCTIONAL ANOMALY) but sub-category (leakage, improper output, etc.) is not known.

\*\*Unknowns allocated to known categories in proportion to known percentages of total.

## 3.4 Analysis of Failure Mode Data

Unlike failure mechanism data, failure mode data (Table 3-2) describe faulted behavior at the device pins. What stands out most in the table is that the majority of failure modes in LSTTL are not the classical open, short and stuck- at modes but functional, parametric and leakage failures. (Table 3-3, prepared from the same RAC report, shows expectedly, that failure modes for the obsolescent DTL technology fall principally in the former category.)

Excess leakage and parameter out-of-tolerance failure modes could have three effects in an operational digital flight system:

1) If sufficiently severe, they could produce a hard or permanent device failure.

2) If borderline, they could produce a soft or intermittent device failure. (In working with LSTTL devices, one occasionally encounters what's called a "flaky chip": a device that works correctly most of the time but not always.)

3) If below fault-activating thresholds, the device could be expected to function properly but with reduced life.

It is observed that in both DTL and LSTTL implementations, leakage and parametic failures can constitute a significant portion of latent faults. Unlike the "stuck-bit" latent fault, leakage and parametric failure modes could conceivably be missed in preflight built-in-test yet become activated in the harsher environment of flight.

LSTTL failure mode data of Table 3-4 for both life test and field application would seem to indicate the presence of such latent faults in fielded equipment. It is important to qualify this latter statement as well as all of the RAC data related to LSTTL failure modes. Specifically the failure mode distributions of Table 3-2 correspond to a limited number of devices that does not span the full range of device types. Table 3-5 shows significantly different failure mode distributions for two separate LSTTL samples, one taken in 1984 (the data of Table 3-2) and another taken in 1980 (Reference 5). (As suggested by Table 3-6, this difference in distributions does not appear to apply to DTL.) 3.4 Analysis of Failure Mode Data

Unlike failure mechanism data, failure mode data (Table 3-2) describe faulted behavior at the device pins. What stands out most in the table is that the majority of failure modes in LSTTL are not the classical open, short and stuck- at modes but functional, parametric and leakage failures. (Table 3-3, prepared from the same RAC report, shows expectedly, that failure modes for the obsolescent DTL technology fall principally in the former category.)

Excess leakage and parameter out-of-tolerance failure modes could have three effects in an operational digital flight system:

1) If sufficiently severe, they could produce a hard or permanent device failure.

2) If borderline, they could produce a soft or intermittent device failure. (In working with LSTTL devices, one occasionally encounters what's called a "flaky chip": a device that works correctly most of the time but not always.)

3) If below fault-activating thresholds, the device could be expected to function properly but with reduced life.

It is observed that in both DTL and LSTTL implementations, leakage and parametic failures can constitute a significant portion of latent faults. Unlike the "stuck-bit" latent fault, leakage and parametric failure modes could conceivably be missed in preflight built-in-test yet become activated in the harsher environment of flight.

LSTTL failure mode data of Table 3-4 for both life test and field application would seem to indicate the presence of such latent faults in fielded equipment. It is important to qualify this latter statement as well as all of the RAC data related to LSTTL failure modes. Specifically the failure mode distributions of Table 3-2 correspond to a limited number of devices that does not span the full range of device types. Table 3-5 shows significantly different failure mode distributions for two separate LSTTL samples, one taken in 1984 (the data of Table 3-2) and another taken in 1980 (Reference 5). (As suggested by Table 3-6, this difference in distributions does not appear to apply to DTL.)

# TABLE 3-3 - DTL Failure Modes (Ref. 4)

| Failure Mode               | Percent<br>of Total | Percent<br>Adjusted** |

|----------------------------|---------------------|-----------------------|

| OPEN                       | 0.0                 | 0.0                   |

| SHORT                      | 6.2                 | 6.2                   |

| DEGRADED                   | 18.8                | 18.8                  |

| Unknown*                   | 15.6                | 0.0                   |

| Leakage                    | 1.6                 | 9.4                   |

| Parameter Out-of-Tolerance | 1.6                 | 9.4                   |

| FUNCTIONAL ANOMALY         | 75.0                | 75.0                  |

| Unknown                    | 46.9                | 0.0                   |

| Non-Functional             | 1.6                 | 4.2                   |

| Improper Output            | 1.6                 | 4.2                   |

| Stuck-at-1                 | 10.8                | 29.1                  |

| Stuck-at-0                 | 14.1                | 37.5                  |

\*"Unknown" means failure mode was in major category (DE-GRADED or FUNCTIONAL ANOMALY) but sub-category (leakage, improper output, etc.) is not known.

\*\*Unknowns allocated to known categories in proportion to known percentages of total.

# TABLE 3-4 - LSTTL Device Failure Modes Life Test vs. Field

|                    | Life Test           | Field               |

|--------------------|---------------------|---------------------|

| Failure Mode       | Percent<br>of Total | Percent<br>of Total |

| OPEN               | 3.5                 | 4.5                 |

| SHORT              | 2.8                 | 4.5                 |

| DEGRADED           | 22.4                | 10.7                |

| FUNCTIONAL ANOMALY | 71.3                | 80.3                |

## TABLE 3-5 - LSTTL Device Failure Modes (SSI and MSI Devices)

Comparison of 1984 and 1980 Data

| Failure Mode       | Percent<br>of Total<br>1984 Data<br>(147 Devices)( | Percent<br>of Total<br>1980 Data<br>450 Devices) |

|--------------------|----------------------------------------------------|--------------------------------------------------|

| OPEN               | 3.4                                                | 0.0                                              |

| SHORT              | 4.1                                                | 0.4                                              |

| DEGRADED           | 22.4                                               | 84.7                                             |

| FUNCTIONAL ANOMALY | 70.1                                               | 14.9                                             |

# TABLE 3-6 - DTL Device Failure Modes

Comparison of 1984 and 1980 Data

| Failure Mode       | Percent<br>of Total<br>1984 Data<br>(64 Devices) | Percent<br>of Total<br>1980 Data<br>(59 Devices) |

|--------------------|--------------------------------------------------|--------------------------------------------------|

| OPEN               | 0.0                                              | 0.0                                              |

| SHORT              | 6.2                                              | 0.0                                              |

| DEGRADED           | 18.8                                             | 20.3                                             |

| FUNCTIONAL ANOMALY | 75.0                                             | 77.7                                             |

4.0 Developing Pin-Level Device Models

### 4.1 Overview

Given the severe constraint that one does not "know" what's inside the semiconductor package, fault modelling becomes more art than science. This section, therefore, describes various approaches (employed by USC and others) which can be invoked collectively to develop a pin-level fault model. The approaches consist of device modelling based on,

- (1) failure mechanisms

- (2) failure mode data

- (3) device stress testing

- (4) functional modelling

- 4.2 Model Elements Based on Failure Mechanisms

4.2.1 Interconnects

Interconnect failure mechanisms consist of broken wire and detachment of die-pad and/or lead-frame wire bonds. These mechanisms can be modelled by:

1) introducing single (i.e. one-at-a-time) open-circuits at each pin.

2) introducing single short circuits across adjacent pins.

(These two failure modes are also discussed in Section 4.3)

4.2.2 Die Defects/Package Failures

As discussed in Section 3.3, die defects and package failures can lead to a virtually infinite combination of incorrect signal outputs.

With SSI devices and (to a limited extent) MSI devices, all combinations could be considered (in FMEA) and inserted (in FMET) provided that circuit complexity is low. In complex circuits employing both MSI and LSI devices, such exhaustive testing is impractical. As a result one must consider altering outputs by randomly selecting a subset of total combinations or employing a set of "worst case" combinations based upon the specific circuit design. 4.3 Model Elements Based on Failure Mode Data

#### 4.3.1 Open Circuits

Based on the 1984 RAC data, open circuits (pin- to-pad) constitute some 3% of total failure modes (Table 3-2). (Wire bond data in Table 3-1 tends to collaborate this fraction.) Note that open-circuit failure modes are single failures.

### 4.3.2 Short Circuits

Short circuits would include single shorts of adjacent pins.

4.3.3 Excess Leakage and Out-of-Tolerance Parameters

Note that failure mode data applies to leakages and parameters at the pins. We are of the belief that equivalent (for FMEA) or actual (for FMET) analog interface circuitry could be interposed between device pins and socket host to effect excess leakages and out- of-tolerance voltage levels, switching characteristics and delays. (This "parasitic circuit" model has, to date, not been pursued in the study.) Failure modes here would be single and multiple. With the same considerations discussed in Section 4.2.2, fault insertion testing involving all possible combinations of leakage currents and parameter values is not practical for complex circuitry. One would accordingly have to randomly select combinations or, where possible, select "worst case" combinations based on the design at hand.

## 4.3.4 Functional Anomalies

The non-functional chip, improper output and latchedoutput failure modes can be modelled using the classical "stuck-at" approaches. Again, one faces a virtually infinite number of fault combinations for MSI and LSI devices employed in complex circuitry.

4.4 Semiconductor Device Stress Testing

4.4.1 Rationale Behind Semiconductor Stress Testing

The failure modes termed "degraded" in Table 3-2 are the result of altered transistor gains, switching thresholds, changed (diffused) resistance values and excess leakage

current. (Responsible failure mechanisms would include marginal semiconductor doping concentrations and/or die bulk and surface contamination.) As seen in Table 4-1, these circuit parameters are all temperature dependent. Consequently by operating an LSTTL device outside of its specified operating temperature limits\* it is possible to induce failure of the device.

4.4.2 Experimental Setup

USC students set up a high-temperature burn-in rig with which digital integrated circuits could be operated and monitored from room temperature up to 200 degrees Celsius.

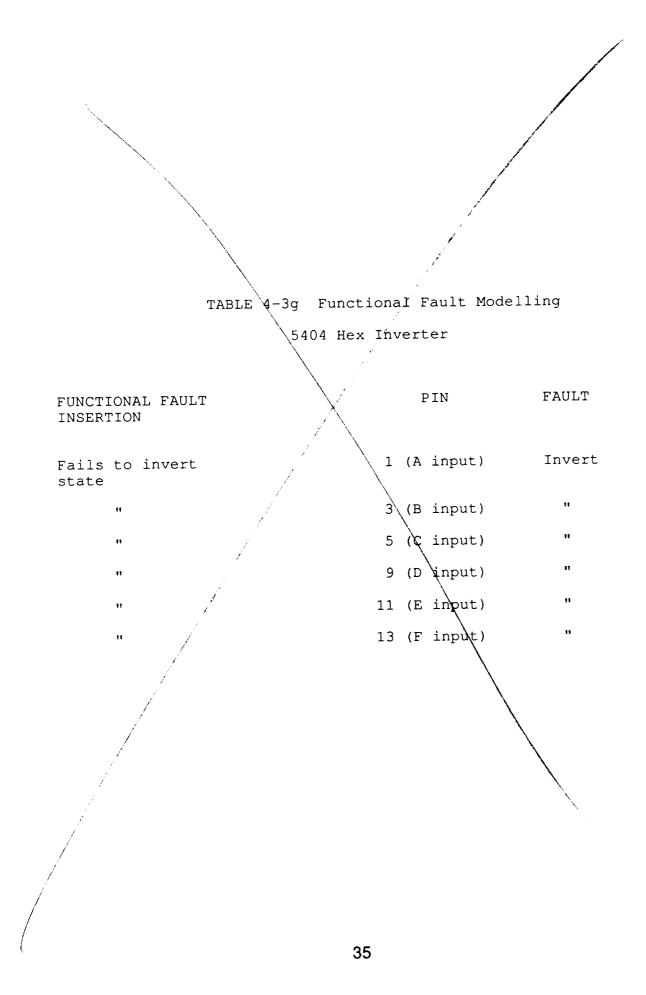

Three LSTTL device types and one TTL device type were selected\*\* for high temperature testing:

- 74LS138 1-of-8-DECODER/DEMULTIPLEXER

- 74174 HEX D-TYPE FLIP FLOPS

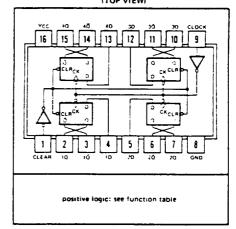

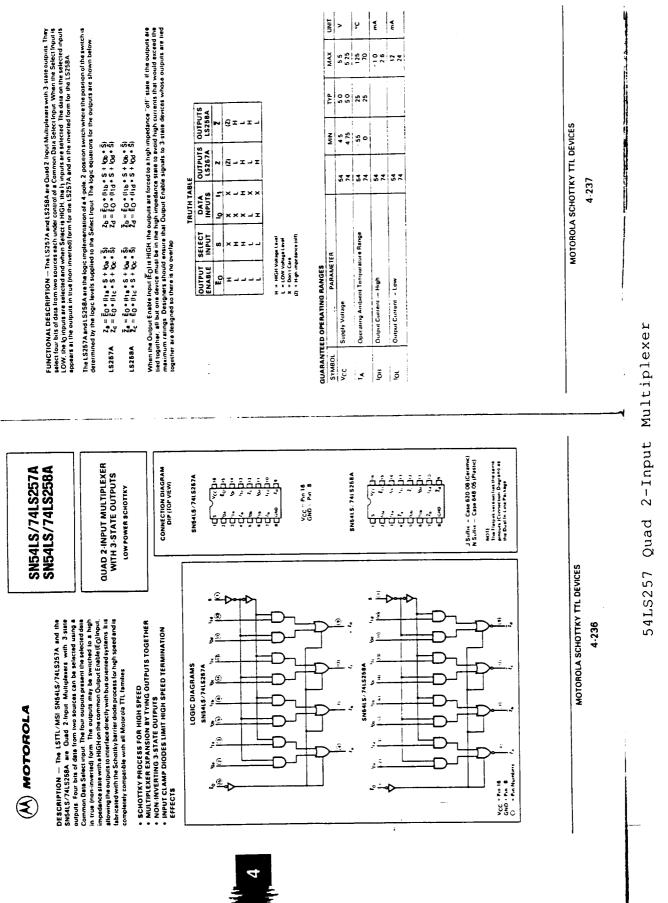

- 74LS257 QUAD 2-TO-1 MULTIPLEXER

- 74LS194 4-BIT SHIFT REGISTER

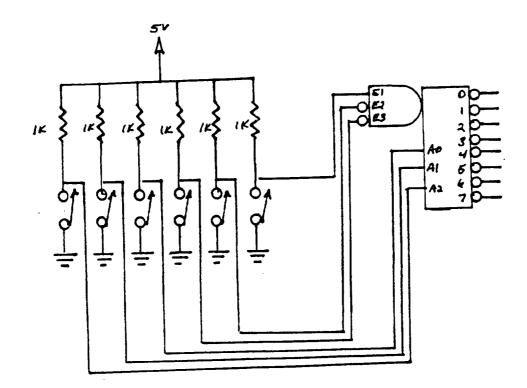

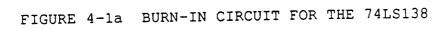

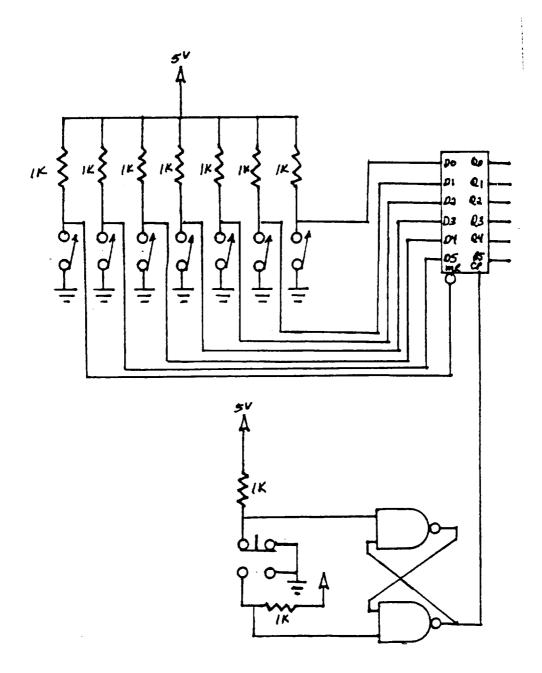

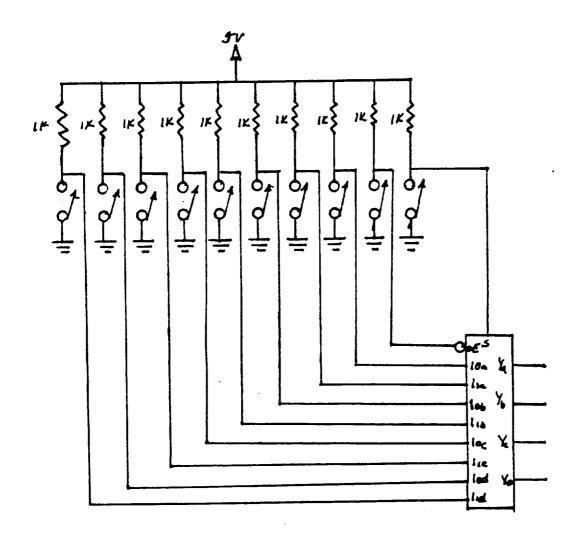

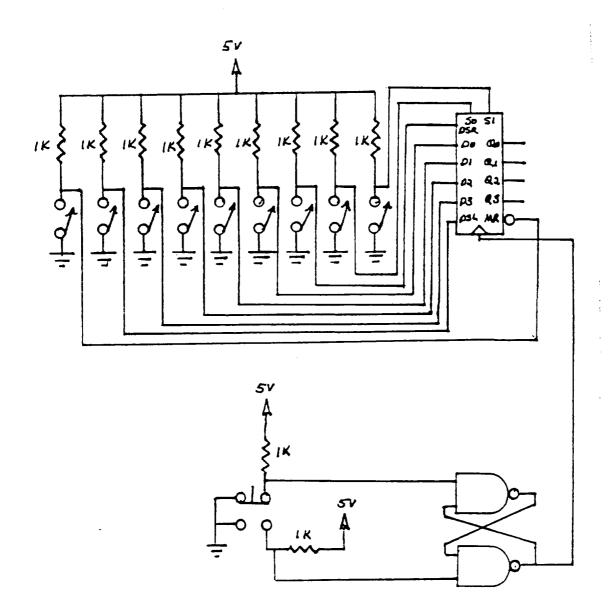

Burn-in circuits for these devices are shown in Figure 4-1.

### 4.4.3 Stress Testing Results

All devices tested were commercial components having a maximum operating temperature\*\*\* of 70 degrees Celsius.

The following describes results of operating the devices at elevated temperatures. (Device data sheets are presented in Appendix A.)

\*These limits define the temperature range over which the device manufacturer guarantees minimum and maximum parameter values.

\*\*\*As noted earlier, this is the temperature beyond which the manufacturer will not guarantee minimum and maximum parameter values.

<sup>\*\*</sup>These device types were concurrently being employed in fault insertion experiments at NASA Ames Research Center.

## TABLE 4-1

# Transistor Parameters vs. Temperature

|                                   |              | Typical      | Values      |             |

|-----------------------------------|--------------|--------------|-------------|-------------|

| Parameter                         | <u>Units</u> | <u>-55 C</u> | <u>25 C</u> | <u>70 C</u> |

| Resistance<br>(Diffused Resistor) | Ohms         | 320          | 360         | 450         |

| (DC) Current Gain                 | dim.         | 65           | 100         | 200         |

| LeakageCurrent                    | nA           | 10           | 70          | 300         |

| Input Voltage Threshold           | Volts        | 0.95         | 0.82        | 0.70        |

FIGURE 4-1b BURN-IN CIRCUIT FOR THE 74174

FIGURE 4-1C BURN-IN CIRCUIT FOR THE 74LS257

FIGURE 4-1d BURN-IN CIRCUIT FOR THE 74LS194

When testing the 74LS138, five different devices were tested under high temperature tests and the following results were obtained: In the first test, all of the outputs stuck high from 170 to 200 degrees Celsius. In the second test, all of the outputs stuck high from 170 to 200 degrees Celsius. For the other three tests, the circuits performed exactly as they were supposed to for temperatures from 20 to 200 degrees Celsius.

When testing the 74174, five different devices were tested and the following results were obtained: In the first test, output Q3 stuck low from 180 to 200 degrees Celsius. In the second test, the clock and output Q5 shorted together from 180 to 200 degrees Celsius. In the third test, output Q4 stuck high from 160 to 200 degrees Celsius. In the fourth test, all outputs stuck low from 100 to 200 degrees Celsius. In the fifth test, all outputs stuck low from 120 to 200 degrees Celsius.

When testing the 74LS257, five different devices were tested under high temperature tests and no change in the outputs was found from 20 to 200 degrees Celsius.

When testing the 74LS194, five different devices were tested under high temperature conditions and the following results were obtained: In the first test, outputs Q0, Q1, and Q2 were stuck high in the hold mode at 190 degrees Celsius. In the second test, all of the outputs stuck high at 200 degrees Celsius. In the third test, all of the outputs stuck high at 80 degrees Celsius. In the fourth test, all outputs were stuck high in the shift left mode at 200 degrees Celsius. In the fifth test, outputs Q1 and Q3 were stuck high in the parallel load mode from 80 to 200 degrees Celsius.

The foregoing test results are summarized in Table 4-2.

Appendix B shows the truth tables for each of the failed devices made at the time the device was failed. Note that all of the faults induced were permanent faults. (No attempt was made in the experiments to induce intermittent faults.)

## TABLE 4-2

Semiconductor Device Stress Testing Results

| DEVICE TYPE I | DEVICE NO.    | RESULTS                                         |

|---------------|---------------|-------------------------------------------------|

| 74LS138       | 1, 2          | ALL OUTPUTS STUCKHIGH                           |

|               | 3, 4, 5       | NO FAILURES                                     |

| 74174         | 1             | Q3 STUCK LOW                                    |

|               | 2             | CLOCK AND Q5 SHORTED                            |

|               | 3             | Q4 STUCK HIGH                                   |

|               | 4, 5          | ALL OUTPUTS STUCK LOW                           |

| 74LS257       | 1, 2, 3, 4, 5 | NO FAILURES                                     |

|               | 1             | Q0, Q1, Q2 STUCK HIGH                           |

|               | 2             | ALL OUTPUTS STUCK HIGH                          |

| 74LS194       | 3             | ALL OUTPUTS STUCK HIGH                          |

|               | 4             | ALL OUTPUTS STUCK HIGH<br>(IN LEFT SHIFT MODE)  |

|               | 5             | Q1 AND Q3 STUCK HIGH<br>(IN PARALLEL LOAD MODE) |

#### 4.5 Functional Fault Modelling

Given that gates in an LSI device are inaccessable (i.e. analytically in FMEA; physically in FMET), many workers have opted to employ functional models in performing fault free and fault insertion simulations (e.g. see References 6, 7 & Functional fault modelling, quite simply, consists of 8). altering pin states (in simulation during FMEA; or in real time during FMET) such that the function of the (individual or sets of) pins is defeated. Table 4-3 shows functional faults for a select number\* of LSTTL devices along with the corresponding alteration of pin states. Note that some of the fault insertions in the table require that pin states be changed instantaneously. (For example, the insertion "invert state" in Table 4-3a requires that the corresponding pin state must be monitored and changed.) While "instantaneous" changes are feasible in simulation, they may be impossible to achieve in physical fault insertion particularly where victim circuit speeds equal or exceed that of the insertion circuitry. Finally, it is noted that the fault insertions of Table 4-3 can occur as single or multiple faults and as well as being permanent or intermittent in duration.

4.6 Summary

As noted in the introduction to this section, a fault model for an LSTTL device would incorporate all of the approaches described above. These are summarized in Table 4-4 which also shows corresponding failure modes.

5.0 Conclusions and Indicated Research Directions

As a result of our investigations, we find that semiconductor failure mechanism data is abundant but of little use in developing pin level device models. Failure mode data on the other hand does exist but is too sparse to be of any (statistical) use in developing fault models.

What is significant in the failure mode data is that, unlike classical logic, MSI and LSI devices do exhibit more than "stuckat" and open/short failure modes. Specifically they are dominated by parametric failures and functional anomalies that can include intermittent faults and multiple pin failures.

<sup>\*</sup>These device types were concurrently being employed in fault insertion experiments at NASA Ames Research Center.

# TABLE 4-3a FUNCTIONAL FAULT MODELLING

## 2901 MICROPROCESSOR SLICE

| FUNCTIONAL FAULT<br>INSERTION    | PIN     | FAULT        |

|----------------------------------|---------|--------------|

| Register select failure (A port) | 4 (AO)  | invert state |

| 11                               | 3 (A1)  | 11           |

| 11                               | 2 (A2)  | 11           |

| 11                               | 1 (A3)  | "            |

| Register select failure (B port) | 17 (BO) | "            |

| n                                | 18 (B1) | n            |

| n                                | 19 (B2) | 11           |

| п                                | 20 (B3) | 11           |

| Microinstruction decode fail     | 12 (IO) | "            |

| n                                | 13 (I1) | "            |

| 11                               | 14 (I2) | "            |

| 11                               | 26 (13) |              |

| n                                | 28 (14) |              |

| 11                               | 27 (15) | TT TT        |

| 11                               | 5 (16)  | н п          |

| u                                | 7 (17)  | ) п          |

| T                                | 6 (18)  | ) "          |

| Correct data shift fail (Q req.) | 8       | open         |

| n                                | 9       | "            |

# TABLE 4-3a FUNCTIONAL FAULT MODELLING

## 2901 MICROPROCESSOR SLICE

## (CONTINUED)

| FUNCTIONAL FAULT<br>INSERTION     | PIN | FAULT  |

|-----------------------------------|-----|--------|

| Correct (Y) output fail<br>state  | 36  | invert |

| n                                 | 37  | **     |

| 11                                | 38  | 18     |

| u                                 | 39  | 11     |

| Output disable*                   | 40  | S-a-1  |

| Carry generate/prop fail<br>state | 32  | invert |

| "                                 | 35  | 11     |

| Overflow (false) fail             | 34  | S-a-1  |

| ALU zero (false) fail             | 11  | S-a-1  |

| ALU MSB out fail<br>state         | 31  | invert |

| Carry-in fail                     | 29  | S-a-1  |

| Clock fail                        | 15  | S-a-1  |

| н                                 | 15  | S-a-0  |

\*Tied low on all 2901 chips.

30

TABLE 4-3b Functional Fault Modelling

# 2911 Microprogram Sequencer

| FUNCTIONAL FAULT<br>INSERTION       | PIN      | FAULT        |

|-------------------------------------|----------|--------------|

| Address source select fail<br>state | 10       | invert       |

| 11                                  | 11       | "            |

| Push/pop stock oper. fail           | 19       |              |

| n                                   | 20       | T            |

| Internal reg. select fail           | 3        | S-a-1        |

| Zero enable fail                    | 9 (zero) | S-a-1        |

| Zero disable fail                   | 9        | S-a-O        |

| Y-enable fail                       | 16       | S-a-1        |

| Y-disable fail                      | 16       | S-a-0        |

| Incrementer carry-in fail           | 17       | S-a-0        |

| "                                   | 6        | invert state |

.

TABLE 4-3c Functional Fault Modelling

# 2918 Quad D Register

| FUNCTIONAL FAULT<br>INSERTION | PIN     | FAULT                            |

|-------------------------------|---------|----------------------------------|

| Y enable fail                 | 7 (OE)  | S-a-1                            |

| Y disable fail                | 7 (OE)  | S-a-0                            |

| Clock fail                    | 9 (CP)  | S-a-0                            |

| Correct Q output fail         | 2 (Q0)  | invert state                     |

| п                             | 5 (Q1)  | 11                               |

| п                             | 11 (Q2) |                                  |

| п                             | 14 (Q3) | "                                |

| CorrectY output fail          | 3 (YO)  | invert state (when pin $7 = 0$ ) |

| п                             | 6 (Y1)  | TT                               |

| 11                            | 10 (Y2) | 11                               |

| 11                            | 13 (Y3) | "                                |

TABLE 4-3d Functional Fault Modelling

54LS253 Dual 4-Input Multiplexer

| FUNCTIONAL FAULT<br>INSERTION | PIN               | FAULT                        |

|-------------------------------|-------------------|------------------------------|

| Chip enable fail              | 1 (Mux 1 enable)  | S-a-1                        |

| 11                            | 15 (Mux 2 enable) | "                            |

| Chip disable fail             | 1                 | S-a-0                        |

| 11                            | 15                | H                            |

| Channel select fail<br>state  | 14 (select 0)     | invert                       |

| 11                            | 2 (select 1)      | u                            |

| Correctoutput fail            | 7 (Mux 1 out)     | invert<br>when<br>pin 1 = 0  |

| T                             | 9 (Mux 2 out)     | invert<br>when<br>pin 15 = 0 |

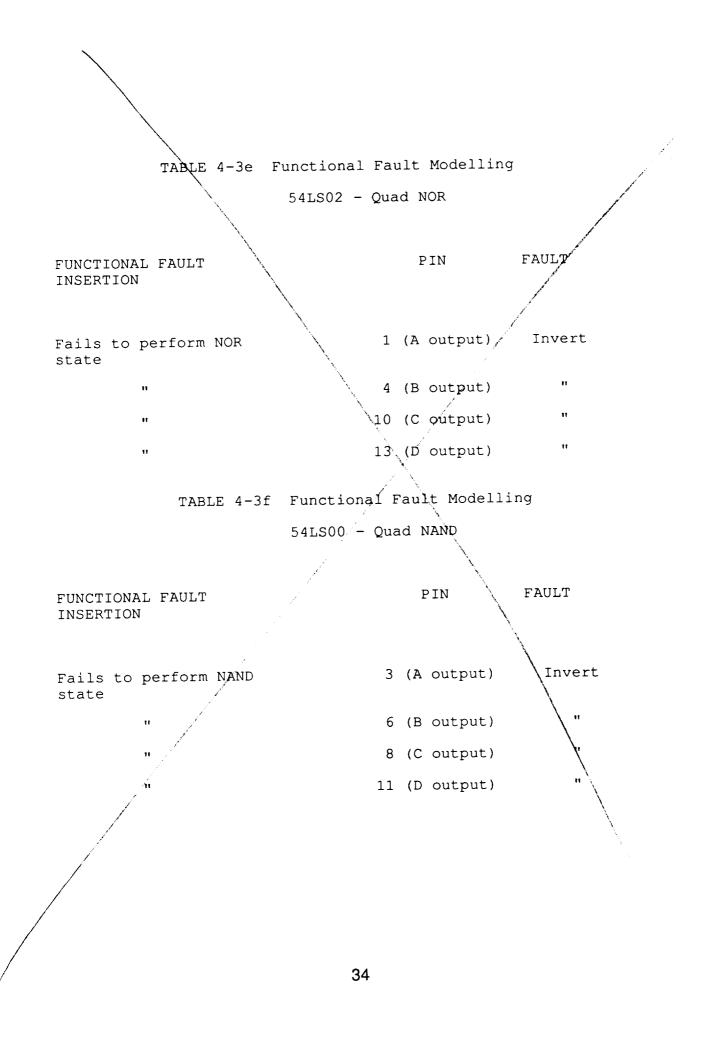

TABLE 4-3e Functional Fault Modelling

54LS02 - Quad NOR

| FUNCTIONAL FAULT<br>INSERTION  |                              | PIN        | FAULT  |

|--------------------------------|------------------------------|------------|--------|

| Fails to perform NOR<br>state  | 1                            | (A output) | Invert |

| 11                             | 4                            | (B output) | TT     |

| 11                             | 10                           | (C output) | 11     |

| 11                             | 13                           | (D output) | n      |

| TABLE 4-3f                     | Functional H<br>54LS00 - Qua |            | ing    |

| FUNCTIONAL FAULT<br>INSERTION  |                              | PIN        | FAULT  |

| Fails to perform NAND<br>state | 3                            | (A output) | Invert |

| 11                             | 6                            | (B output) | 11     |

| 11                             | 8                            | (C output) | 11     |

| 11                             | 11                           | (D output) | "      |

34

# TABLE 4-3g Functional Fault Modelling

## 5404 Hex Inverter

| FUNCTIONAL FAULT<br>INSERTION | PIN          | FAULT  |

|-------------------------------|--------------|--------|

| Fails to invert<br>state      | 1 (A input)  | Invert |

| Π                             | 3 (B input)  | 11     |

| n                             | 5 (C input)  | 11     |

| n                             | 9 (D input)  | "      |

| "                             | ll (E input) | **     |

| n                             | 13 (F input) | 11     |

TABLE 4-4 - LSTTL Failure Modes and Fault Models

| Failure Mode       | Fault Model                                                                |

|--------------------|----------------------------------------------------------------------------|

| Functional Anomaly | Functional Fault Model<br>(FMEA); Model Generated<br>Fault Patterns (FMET) |

| Degraded (At Pins) | Parasitic Circuit                                                          |

| Degraded (On Chip) | Device Stress Tests to<br>Corroborate Functional<br>Fault Model            |

| Opens              | Open-Circuit Pin                                                           |

| Shorts             | Short-Circuit Adjacent<br>Pins                                             |

It is certainly possible, and this report discusses the methods, to develop pin-level models based on extrapolation of semiconductor device failure mechanisms, failure modes, results of (temperature) stress testing and functional modelling. Such a composite model would include credible faults that could be experienced by the device. Unfortunately, the number of such faults would be insignificant when compared to the (virtually infinite) number of possible fault patterns. At issue here is the fact that one could insert all the faults in a composite model and yet gain no accurate measure of fault detection coverage and/or fault latency times. I.e. one could demonstrate fault tolerance yet come away with no measures of the degree of fault tolerance.

The foregoing prompt several research questions:

1) Although single-pin "stuck-at" or open/short permanent fault insertions do not characterize the modern MSI and LSI device, can they be legitimately\* employed to cover actual failure modes that might be experienced?

2) Is it possible to obtain a definition of coverage and coverage measures with a device which can exhibit permanent or intermittent failures at one or more device pins?

3) Is one better off considering failure patterns at electrical connection boundaries other than integrated circuit pins (e.g. data busses, I/O lines, etc.)?

<sup>\*</sup>The approach is extensively used today with FMEA.

### References

1. P. Goddard, R. Davis, "Automated FMEA Techniques", Rome Air Development Center Report RADC-TR-84-244, Grifiss AFB, New York. December 1984.

2. Lala, J. & T. Basil Smith III, "Development and Evaluation of a Fault - Tolerant Multiprocessor (FTMP) Computer", Volume III (FTMP Test and Evaluation), Charles Stark Draper Laboratory Report CSDL-R-1602, May 1983.

3. DeFeo, P., D. Doane, & J. Saito, "An Integrated User -Oriented Laboratory for Verification of Digital Flight Control Systems - Features and Capabilities", NASA Technical Memorandum 84276, August 1982.

4. "Digital SSI/MSI Data", Report MDR-19, Reliability Analysis Center, Rome Air Development Center, Griffiss AFB, New York, Spring 1984.

5. "Digital Evaluation and Failure Analysis Data", Report MDR-15, Reliability Analysis Center, Rome Air Development Center, Griffiss AFB, New York, Spring 1984.

6.J. Galidy, Y. Crouzet & M. Vergniault, "Physical Versus Logical Fault Models in MOS LSI Circuits, Impact on Their Testability", 9th Annual International Symposium on Fault Tolerant Computing Madison, Wisconsin, June 1979.

7.Wadsack, R., "Fault Modeling and Logic Simulation of CMOS Integrated Circuits", Bell System Technical Journal, Vol. 57, No. 5, May-June 1978.

8. J. Armstrong, "Chip Level Modelling of LSI Devices", IEEE Transactions on Computer-Aided Design. Vol. CAD-3, No. 4, pp. 288 thru 297, October 1984.

V9.McGough, J., "Feasibility Study for a Generalized Gate Logic Software Simulator", The Bendix Corporation, NASA Contractors Report 172159, July 1983.

## Acknowledgements

Cooperative Agreement NCC 2-303 was jointly funded by NASA Ames Research Center (Douglas Doane, Technical Monitor) and the FAA Technical Center (William Larsen, Technical Monitor).

## APPENDIX A

## DEVICE DATA SHEETS

SN54LS/74LS138

SN54LS138 SN74LS138

M MOTOROLA

decoder with just lour LS138s and one inverter. (See Figure J.)

Decoder 1 - of - 854LS138

MOTOROLA SCHOTTRY LEL DE VICT S

÷.

MUTOROLA SCHOTTKY TTL DEVICES

4-102

----

4 103

A-1

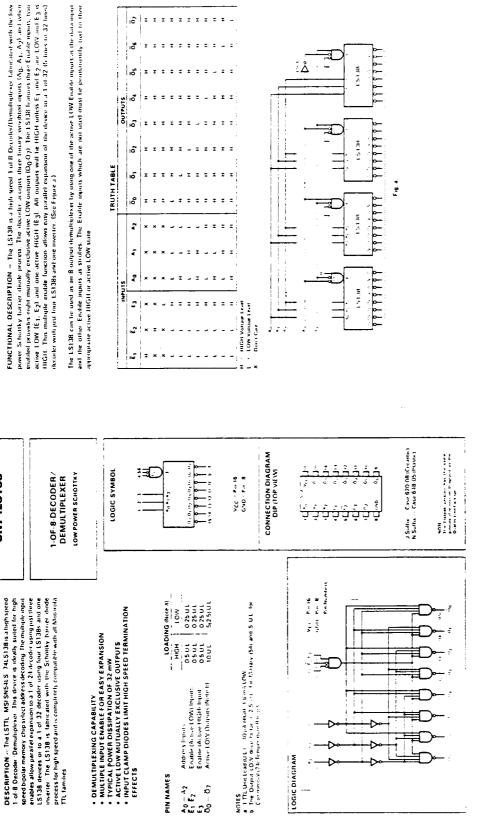

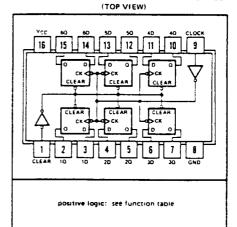

### TYPES SN54174, SN54175, SN54LS174, SN54LS175, SN54S174, SN54S175, SN74174, SN74175, SN74LS174, SN74LS175, SN74S174, SN74S175 HEX/QUADRUPLE D-TYPE FLIP-FLOPS WITH CLEAR LETIN NO. DL S 7511803 DECEMBER 1972-REVISED OCTOBER 1976

#### '174, 'LS174, 'S174 . . . HEX D-TYPE FLIP-FLOPS 175, LS175, S175... QUADRUPLE D-TYPE FLIP-FLOPS

- '174, 'LS174, 'S174 Contain Six Flip-Flops 3 with Single-Rail Outputs

- '175, 'LS175, 'S175 Contain Four Flip-Flops .... with Double-Rail Outputs

- Three Performance Ranges Offered: See 3 **Table Lower Right**

- **Buffered Clock and Direct Clear Inputs** .

- Individual Data Input to Each Flip-Flop ,

- Applications include: **Buffer/Storage Registers** Shift Registers Pattern Generators

#### cescription

These monolithic, positive-edge-triggered flip-flops utilize TTL circuitry to implement D-type flip-flop logic. All have a direct clear input, and the '175, 'LS175, and 'S175 feature complementary outputs from each flip-flops.

Information at the D inputs meeting the setup time requirements is transferred to the Q outputs on the positive-going edge of the clock pulse. Clock triggering occurs at a particular voltage level and is not directly related to the transition time of the positive-going pulse. When the clock input is at either the high or low level, the D input signal has no effect at the output.

These circuits are fully compatible for use with most TTL or DTL circuits.

| FUNCTION TABLE   |       |   |          |    |  |  |  |  |

|------------------|-------|---|----------|----|--|--|--|--|

| (EACH FLIP-FLOP) |       |   |          |    |  |  |  |  |

| INPUTS OUTPUTS   |       |   |          |    |  |  |  |  |

| CLEAR            | CLOCK | D | <u>a</u> | Ō٢ |  |  |  |  |

| L                | х     | x | L        | Ħ  |  |  |  |  |

| н                | :     | н | н        | L  |  |  |  |  |

| н                | •     | L | L        | н  |  |  |  |  |

| н                | L     | x | a        | ā, |  |  |  |  |

H = high level (steady state) L = low revel (steady state) X = irrelevant

1 - transition from low to high level

$\widehat{\boldsymbol{u}}_{0}$  – the level of Q before the indicated steady-state mout conditions were established.

\* 175\_1LS175, and S175 only

SN54174, SN54LS174, SN54S174 ... J OR W PACKAGE SN74174, SN74LS174, SN74S174 ... J OR N PACKAGE

SN54175, SN54LS175, SN54S175 ... J OR W PACKAGE SN74175, SN74LS175, SN74S175 . . . J OR N PACKAGE TOP VIEW

|                | TYPICAL   | TYPICAL       |  |  |

|----------------|-----------|---------------|--|--|

| TYPES          | MAXIMUM   | POWER         |  |  |

| ITPES          | CLOCK     | DISSIPATION   |  |  |

|                | FREQUENCY | PER FLIP-FLOP |  |  |

| 174, 175       | 35 MHz    | 38 mW         |  |  |

| 'LS174, 'LS175 | 40 MHz    | 14 mW         |  |  |

| 'S174, 'S175   | 110 MHz   | 75 mW         |  |  |

|                |           |               |  |  |

### TEXAS INSTRUMENTS OFFICE BOX SOL2 + DALLAS, TEXAS 75222

7.253

## 54LS174 Hex D-Type Flip Flops

SN64LS/74LS267A • SN64LS/74LS268A

A-3

SN54LS194A SN74LS194A

4-BIT BIDIRECTIONAL UNIVERSAL SHIFT REGISTER

LOW POWER SCHOTTKY

- INPUT CLAMP DIODES LIMIT HIGH SPEED TERMINATION

CONNECTION DIAGRAM DIP (TOP VIEW)

Į.

EFFECTS

J Suffix -- Case 620-08 (Ceramic) N Suffix -- Case 648 05 (Plastic)

¢

9

۲

۲

VCC = Pin 18 GND = Pin 8 () = Pin Numbers

4-192

FUNCTIONAL DESCRIPTION – The Logic Diagram and Truth Table indicate the functional characteristics of the LS194A 4 Bit Bidirectional Shift Register. The LS194A is similar in operation to the Motorola LS195A Universal Shift Register when used in serial or parallel data register transfers. Some of the common features of the two devices are described below:

- 1. All data and mode control input are edge tregered, responding only to the LOW to HIGH transition of the Clock (CP) The only immigrativitions, therefore, a that the mode control and setticted data input must be table one set up time provious behaviour and the clock burks.

- The register is fully synchronous, with all operations taking place in less than 15 ns (typical) making the device especially useful for implementing very high speed CPUs, or the memory buffler registers. ~

- 3. The four parallel data inputs (P<sub>0</sub>, P<sub>1</sub>, P<sub>2</sub>, P<sub>3</sub>) are O type inputs. When both S<sub>0</sub> and S<sub>1</sub> are HIGH, the data appending on P<sub>0</sub>, P<sub>1</sub>, P<sub>2</sub>, and P<sub>3</sub> and P<sub>3</sub> inputs in transferred to the Q<sub>0</sub> Q<sub>1</sub>, Q<sub>2</sub>, and Q<sub>3</sub> outputs respectively following the next LOW to HIGH introduced for the C<sub>0</sub> Q<sub>1</sub>, Q<sub>2</sub>, and Q<sub>3</sub> outputs respectively following the next LOW to HIGH.

- The asynchronous Master Reset (MR), when LOW, overrides all other input conditions and forces the Q outputs LOW

- Special logic leatures of the LS194A design which increase the range of application are described below

- Two mode control input 150, 5,1 determine the synchronous operation of the device. As shown in the Mode Selection Table, data can be entered and shitted from thit to input 10, -0, jet to so with to left (hint) tett,  $0^3 0_2$ etc.) or patallel data can be entered loading all four bits of the respirer munitareously. When poly 50, and 51, are LOW the sating data in standards and shifted mode embour restricting the HGH to LOW clock transition \_

- D type serial data inputs IDSR, DSL) are provided on both the first and last stages to allow multistage shuft right or shift Hit data stansfers without interfereng with parallel load operation:

4-193

MOTOROLA SCHOTTKY TTL DEVICES

Register

Shift

A-4

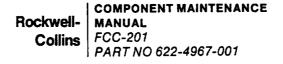

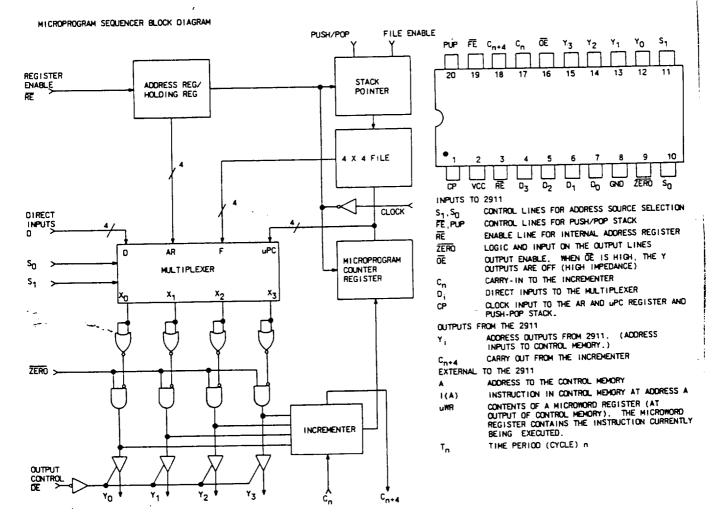

GENERAL DESCRIPTION

THE 2911 IS A FOUT-BIT WIDE ADDRESS CONTROLLER INTENDED FOR SEQUENCING THROUGH A SERIES OF MICROINSTRUCTIONS CONTAINED IN A ROM OR PROM. TWO 2911'S MAY BE INTERCONNECTED TO GENERATE AN EIGHT-BIT ADDRESS (256 WORDS), AND THREE MAY BE USED TO GENERATE A TWELVE-BIT ADDRESS (4K WORDS).

THE 2911 CAN SELECT AN ADDRESS FROM ANY OF THREE SOURCES. THEY ARE: 1) A SET OF EXTERNAL DIRECT INPUTS (D): 2) A FOUR-HORD DEEP PUSH/POP STACK: OR 3) A PROGRAM COUNTER REGISTER (MHICH USUALLY CONTAINS THE LAST ADDRESS PLUS ONE). THE PUSH/POP STACK INCLUDES CERTAIN CONTROL LINES SO THAT IT CAN EFFICIENTLY EXECUTE NESTED SUBROUTINE LINKAGES. A SEPARATE LINE FORCES THE OUTPUTS TO ALL ZERDES. THE OUTPUTS ARE THREE-STATE.

4-Bit Controller Type 2911

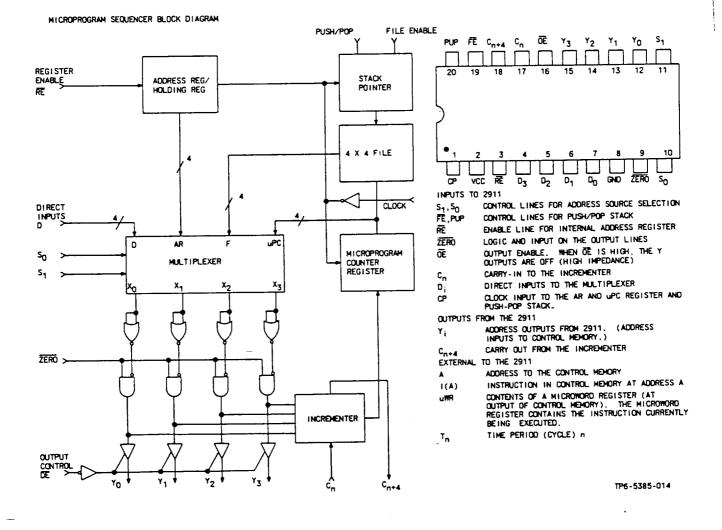

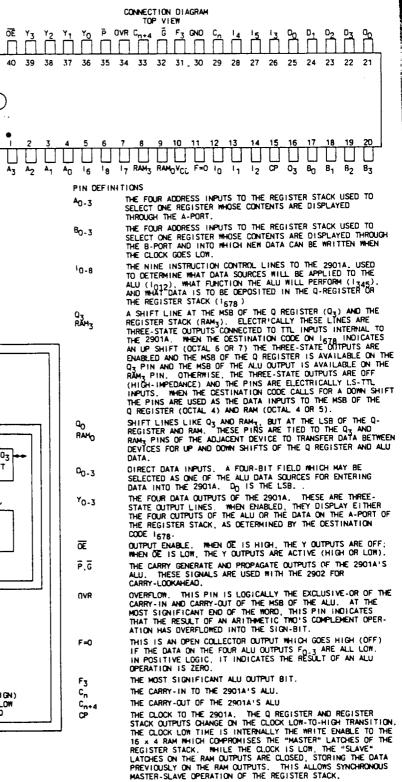

#### GENERAL DESCRIPTION THE FOUR-BIT BIPOLAR MICROPROCESSOR SLICE IS DESIGNED AS A HIGH SPEED CASCADARLE ELEMENT INTENDED FOR USE IN CPU'S, PERIPHERAL CONTROLLERS. PROGRAMMABLE MICROPROCESSORS AND NUMEROUS OTHER APPLICATIONS. THE MICROINSTRUCTION FLEXIBILITY OF THE 2901A WILL ALLOW EFFICIENT EMULATION OF ALMOST ANY DIGITAL COMPUTING MACHINE. THE DEVICE, AS SHOWN IN THE BLOCK DIAGRAM BELOM. CONSISTS OF ALGOD BY 4-BIT TMO-PORT RAM. A HIGH-SPEED ALU, AND THE ASSOCIATED SHIFTING, DECODING AND MULTI-PLEXING CIRCUITRY. THE NINE-BIT MICROINSTRUCTION FUNCTION, AND THE ALU DESTINATION REGISTER. THE MICROPROCESSOR IS CASCADARLE WITH FULL LOOK-AMEAD OR WITH RIPPLE CARRY, HAS THREE-STATE OUTPUTS, AND PROVIDES VARIOUS STATUS FLAG OUTPUTS FROM THE ALU

ì

2901 Microprocessor Slice

GENERAL DESCRIPTION

THE 2911 IS A FOUT-BIT WIDE ADDRESS CONTROLLER INTENDED FOR SEQUENCING THROUGH A SERIES OF MICROINSTRUCTIONS CONTAINED IN A ROM OR PROM. TWO 2911'S MAY BE INTERCONNECTED TO GENERATE AN EIGHT-BIT ADDRESS (256 WORDS), AND THREE MAY BE USED TO GENERATE A TWELVE-BIT ADDRESS (4K WORDS).

THE 2911 CAN SELECT AN ADDRESS FROM ANY OF THREE SOURCES. THEY ARE: 1) A SET OF EXTERNAL DIRECT INPUTS (D): 2) A FOUR-WORD DEEP PUSH/POP STACK; OR 3) A PROGRAM COUNTER REGISTER (WHICH USUALLY CONTAINS THE LAST ADDRESS PLUS ONE). THE PUSH/POP STACK INCLUDES CERTAIN CONTROL LINES SO THAT IT CAN EFFICIENTLY EXECUTE NESTED SUBROUTINE LINKAGES. A SEPARATE LINE FORCES THE OUTPUTS TO ALL ZEROES. THE OUTPUTS ARE THREE-STATE.

2911 Microprogram Sequencer

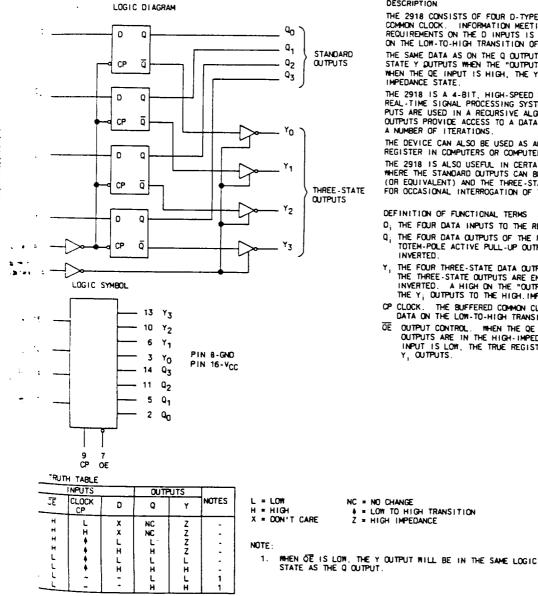

DESCRIPTION

THE 2918 CONSISTS OF FOUR D-TYPE FLIP-FLOPS WITH A BUFFERED COMMON CLOCK. INFORMATION MEETING THE SET-UP AND HOLD REQUIREMENTS ON THE D INPUTS IS TRANSFERRED TO THE Q OUTPUTS ON THE LOW-TO-HIGH TRANSITION OF THE CLOCK.

THE SAME DATA AS ON THE Q OUTPUTS IS ENABLED AT THE THREE-STATE Y DUTPUTS WHEN THE "OUTPUT CONTROL" (QE) INPUT IS LOW. WHEN THE QE INPUT IS HIGH, THE Y OUTPUTS ARE IN THE HIGH-IMPEDANCE STATE.

THE 2918 IS & 4-BIT, HIGH-SPEED REGISTER INTENDED FOR USE IN REAL-TIME SIGNAL PROCESSING SYSTEMS WHERE THE STANDARD OUT-PUTS ARE USED IN A RECURSIVE ALGORITHM AND THE THREE-STATE OUTPUTS PROVIDE ACCESS TO A DATA BUS TO DUMP THE RESULTS AFTER A NUMBER OF ITERATIONS.

THE DEVICE CAN ALSO BE USED AS AN ADORESS REGISTER OR STATUS REGISTER IN COMPUTERS OR COMPUTER PERIPHERALS.

THE 2918 IS ALSO USEFUL IN CERTAIN DISPLAY APPLICATIONS WHERE THE STANDARD OUTPUTS CAN BE DECODED TO DRIVE LED'S (OR EQUIVALENT) AND THE THREE-STATE OUTPUTS ARE BUS ORGANIZED FOR OCCASIONAL INTERROGATION OF THE DATA AS DISPLAYED.

DEFINITION OF FUNCTIONAL TERMS

O; THE FOUR DATA INPUTS TO THE REGISTER.

- Q THE FOUR DATA OUTPUTS OF THE REGISTER WITH STANDARD TOTEM-POLE ACTIVE PULL-UP OUTPUTS. DATA IS PASSED NON-INVERTED.

- Y; THE FOUR THREE-STATE DATA OUTPUTS OF THE REGISTER. WHEN THE THREE-STATE OUTPUTS ARE ENABLED. DATA IS PASSED NON-INVERTED. A HIGH ON THE "OUTPUT CONTROL" INPUT FORCES THE Y; OUTPUTS TO THE HIGH. IMPEDANCE STATE.

- CP CLOCK. THE BUFFERED COMMON CLOCK FOR THE REGISTER ENTERS DATA ON THE LOW-TO-HIGH TRANSITION.

- OE OUTPUT CONTROL. WHEN THE QE INPUT IS HIGH, THE YI OUTPUTS ARE IN THE HIGH-IMPEDANCE STATE. WHEN THE QE INPUT IS LOW, THE TRUE REGISTER DATA IS PRESENT AT THE Y, OUTPUTS.

2918 Quad-D Register

| М МОТОРОLA                                                                                                                                                                                                                                                                                                                   | SNEAL COED                                                                                                                | FUNCTIONAL DESCRIPTION - The (\$353 contains two identical 4 lineal Maturations and 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DESCRIPTION - The LSTL MSI SNS4LS /74LS253 is a Duel 4-<br>forul Multiplerer with 3 stative outputs In Can sufer Tiwobles of data from<br>four sources using common select inputs. The outputs may be                                                                                                                        | SN74LS253                                                                                                                 | two bits from flow sources seticited by common vieter moust 15/6, 5/1. The 4-moust mustures take individual function<br>Enable (Égy, Égy) moust which when HIGH forces the aurpust to a tradit manufacture (high: 2) state.<br>The USS3 is the topic implementation of a 2 pole, 4 position sourch, where the position of the switch is determined to a flogic device and use and used to a<br>logic ferelt supplied to the two setied individual. The flogic equation for the use undividual seties.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| individually sourched to a high impediance state which a Midel on ine<br>respective Output Enable (EQ) injunds allowing the outputs to minicle<br>directly with bus onemed systems it is fabricated with the Scionitty<br>burrier diote process for high speed and is completely comparitie with<br>all Motorola TL Lamilies | DUAL 4 INPUT MULTIPLEXER<br>WITH 3.STATE OUTPUTS                                                                          | $Z_{a} = \overline{E}_{a} \cdot \overline{E}_{a} \cdot \overline{E}_{a} \cdot \overline{E}_{a} + \overline{1}_{a} \cdot \overline{5}_{1} - \overline{5}_{0} + \overline{1}_{2} \cdot \overline{5}_{1} - \overline{5}_{0} + \overline{1}_{2} \cdot \overline{5}_{1} - \overline{5}_{0} - \overline{5}_{1} - \overline{5}_{0} - \overline{5}_{1} - \overline{5}_{0} - \overline{1}_{2} - \overline{5}_{0} - \overline{1}_{2} - \overline{5}_{1} - \overline{5}_{0} - \overline{1}_{2} - \overline{5}_{1} - \overline{5}_{0} - \overline$ |

| <ul> <li>SCHOTTAY PROCESS FOR HIGH SPEED</li> <li>MULTIFUNCTION CAPABILITY</li> </ul>                                                                                                                                                                                                                                        |                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |