NASA Contractor Report 4594

IN-61 ,. 9995 P.69

# Interpreter Composition Issues in the Formal Verification of a Processor-Memory Module

David A. Fura and Gerald C. Cohen

| (NASA-CR-4594) INTERPRETER         | N94-32775 |

|------------------------------------|-----------|

| COMPOSITION ISSUES IN THE FORMAL   |           |

| VERIFICATION OF A PROCESSOR-MEMORY |           |

| MODULE Final Report (Boeing Co.)   | Unclas    |

| 69 p                               |           |

|                                    |           |

H1/61 0009995

Contract NAS1-18586 Prepared for Langley Research Center

NASA Contractor Report 4594

## Interpreter Composition Issues in the Formal Verification of a Processor-Memory Module

David A. Fura and Gerald C. Cohen The Boeing Company • Seattle, Washington

National Aeronautics and Space Administration Langley Research Center • Hampton, Virginia 23681-0001 Prepared for Langley Research Center under Contract NAS1-18586

#### Preface

This document was generated in support of NASA contract NAS1-18586, Design and Validation of Digital Flight Control Systems Suitable for Fly-By-Wire Applications, Task Assignment 12. Task 12 is concerned with issues in the formal specification and verification of a processor-memory module.

This report describes interpreter composition techniques suitable for the formal specification and verification of a processor-memory module using the HOL theorem-proving system. The processor-memory module is a multi-chip subsystem within a fault-tolerant embedded system under development within the Boeing Defense & Space Group. It provides the opportunity to investigate the specification and verification of a real-world subsystem within a commercially-developed fault-tolerant computer.

The NASA technical monitor for this work is Sally Johnson of the NASA Langley Research Center, Hampton, Virginia.

The work was accomplished at the Boeing Company, Seattle, Washington. Personnel responsible for the work include:

Boeing Defense & Space Group: D. Gangsaas, Responsible Manager T. M. Richardson, Program Manager

Boeing Defense & Space Group: Gerald C. Cohen, Principal Investigator David A. Fura, Researcher

## \* \*\* \*\* \*

### Contents

| 1 | Introduction                                                   | 1    |

|---|----------------------------------------------------------------|------|

| 2 | Hierarchical Pre-Post Logic                                    |      |

|   | 2.1 Interpreter Behavioral Model                               |      |

|   | 2.1.1 Related Work                                             |      |

|   | 2.1.2 HPL Interpreter Behavior                                 | . 6  |

|   | 2.2 Interpreter Abstraction                                    | 8    |

|   | 2.2.1 Related Work                                             | . 8  |

|   | 2.2.2 HPL Abstraction                                          | . 9  |

|   | 2.3 Interpreter Liveness                                       | . 10 |

|   | 2.3.1 Related Work                                             | 10   |

|   | 2.3.2 HPL Interpreter Liveness                                 | . 11 |

|   | 2.4 Interpreter Correctness                                    |      |

|   | 2.4.1 Related Work                                             |      |

|   | 2.4.2 HPL Correctness                                          |      |

|   |                                                                |      |

| 3 | Issues in Secure Abstract-Level Composition                    | . 14 |

|   | 3.1 The Role of Abstraction                                    |      |

|   | 3.2 Temporal Abstraction for Globally-Clocked Systems          | 15   |

|   | 3.3 Temporal Abstraction for Interface-Clocked Systems         | . 16 |

|   |                                                                |      |

| 4 | Synchronizing Interface-Clocked Interpreters                   | 18   |

|   | 4.1 Bijective Monorate Interpreters                            | 20   |

|   | 4.2 Injective Multirate Interpreters                           | 22   |

|   | 4.3 Surjective Multirate Interpreters                          | 25   |

|   |                                                                |      |

| 5 | Processor-Memory Module Specification and Verification         |      |

|   | 5.1 PMM Overview                                               |      |

|   | 5.2 Local Processor Specification                              |      |

|   | 5.3 Local Memory Specification                                 |      |

|   | 5.4 PIU Specification Refinements                              | 31   |

|   |                                                                |      |

| 6 | Conclusions                                                    | . 33 |

| 7 | Deferences                                                     | 24   |

| 1 | References                                                     | . 54 |

| A | HOL Overview                                                   | 36   |

|   | A.1 The Language                                               |      |

|   | A.2 The Proof System                                           |      |

|   |                                                                | 20   |

| В | Interpreter Verification Test Case Studies                     | 39   |

| - | B.1 Standard Interpreter Justification-Proof Example           | 39   |

|   | B.2 Monorate Bijective Interpreter Justification-Proof Example | 40   |

|   | B.3 Multirate Injective Interpreters                           | 43   |

|   |                                                                |      |

PRISENDING PAGE BLANK NOT FILMED

| С | Proc | essor-Memory Module Specification Examples    | 50 |

|---|------|-----------------------------------------------|----|

|   | C.1  | Transaction Signal Data Structure Definitions | 50 |

|   | C.2  | Local Processor Transaction-Level Model       | 55 |

|   | C.3  | Local Memory Transaction-Level Model          | 56 |

|   | C.4  | M-Port Transaction-Level Model                | 58 |

ų.

## **List of Figures**

| 3.1 | The Problem of Composing Abstract Models                                        | 14 |

|-----|---------------------------------------------------------------------------------|----|

| 3.2 | Temporal Abstraction Linking the Timing and Clock Levels                        |    |

| 3.3 | Temporal Abstraction Linking the Clock and Transaction Levels                   | 16 |

| 4.1 | Description of an Interpreter's Transaction Events and Concrete-Level Variables | 18 |

| 4.2 | Transaction One-to-One and Onto Relationships                                   |    |

| 4.3 | Example Bijective Monorate Interpreter Model                                    |    |

| 4.4 | Example Dijective Multirate Interpreter Model                                   |    |

| 4.5 | Example System Exhibiting Injective Multirate Behavior                          | 23 |

| 4.6 | Desired Composite-System Behavior for System of Figure 4.5                      |    |

| 4.7 | Specification Hierarchy for System of Figure 4.5                                |    |

| 4.8 | Example Surjective Multirate Interpreter Model                                  | 25 |

| 4.9 | Example System Exhibiting Surjective Multirate Behavior                         | 26 |

|     | Desired Composite-System Behavior of System of Figure 4.9                       |    |

|     | Partial Specification Hierarchy for System of Figure 4.9                        |    |

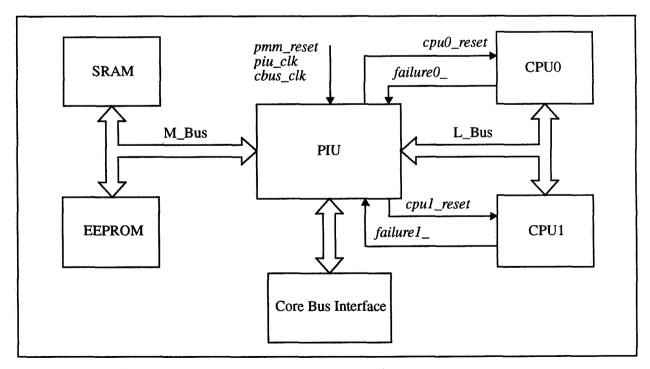

| 51  | Block Diagram of the Processor-Memory Module                                    | 28 |

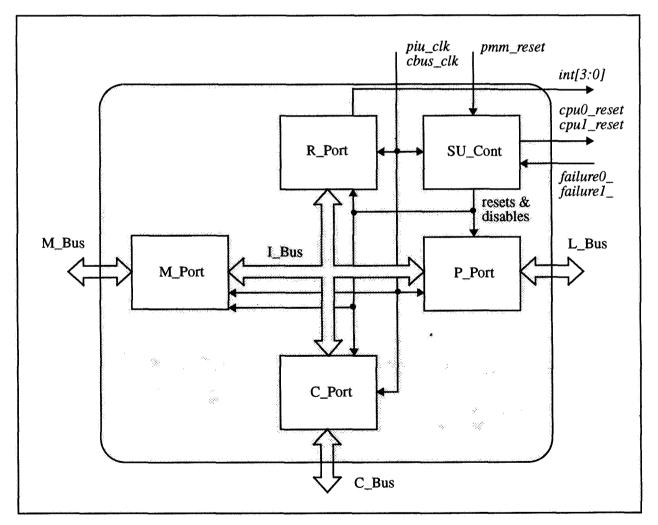

| 5.1 | Major Blocks of the Processor Interface Unit                                    | 20 |

| 5.2 | Major Blocks of the Processor interface Onit                                    | 2) |

## List of Tables

| A.1 | HOL Infix Operators | 37 |

|-----|---------------------|----|

| A.2 | HOL Binders         | 37 |

| A.3 | HOL Type Operators  | 38 |

#### **1** Introduction

To date, theorem-proving efforts targeting microprocessor-based system verification have treated these systems as self-enclosed state-transition systems without outputs (e.g., [Hun86], [Coh88], [Joy90], [Win90], [Gra92], [Lev93]). While these approaches have been effective on the small-scale systems addressed thus far, they are not ones that we expect to scale up to larger systems in any practical way. The fundamental problem with these approaches is their insistence on performing subsystem compositions at very low levels of abstraction.

We believe that the ability to compose hardware models at high levels of abstraction is fundamental to the practical specification and formal verification of nontrivial hardware systems. Without such a capability, large-scale system verifications would quickly become bogged down by the explosion in low-level state resulting from the independent actions of typical interacting subsystems. In this report we describe a new approach to interpreter composition that permits provably-secure compositions at high levels of abstraction.

Our work under this task is ultimately targeted to a commercially-developed processing subsystem, called the Processor-Memory Module (or PMM), of a fault-tolerant computer system. The Fault Tolerant Embedded Processor (FTEP) is targeted towards applications in avionics and space requiring extremely high levels of mission reliability, extended maintenance-free operation, or both. Since the need for high-quality design assurance in these systems is an undisputed fact, the continued development and application of formal methods is vital as these systems see increasing use in modern society.

The work described in this report represents the culmination of a multiyear effort to develop and apply theorem-proving technology to hardware verification. Previous work under Task 10 developed abstraction techniques and an interpreter modeling approach to specify a PMM interface chip (the Processor Interface Unit, or PIU) in terms of its higher-level transaction handling. In this context, a transaction refers to the bus transactions of typical commercial microprocessors, such as the Intel 80960 [Int89] or the MIPS R3000 [Kan87]. Techniques for formally verifying the transaction level with respect to its underlying clock level were also developed in Task 10. Two Task 10 final reports describe the results of the PIU specification and verification work ([Fur93a] and [Fur93b], respectively).

Prior to this, work under Task 3 developed interpreter modeling and verification techniques applicable to a wide range of hardware verification problems. A new approach to hierarchical decomposition and the development of a generic interpreter theory together greatly reduced the level of effort required by many verifications. The recent verification of an implementation of the Viper microprocessor certifies the strength of these methods. The methodology that was employed in this verification is described in [Win91] and [Win92], while the verification itself is described in [Lev93].

The research focus of the Task 12 work described here was on composition, specifically *transactionlevel composition*. We have developed modeling and verification methods that permit provably-secure composition at this high level of abstraction. To our knowledge, this work represents the first successful demonstration of an interpreter-based approach to this problem. All of our work was performed using the HOL theorem proving system from the University of Cambridge [Gor93].

Section 2 of this report describes an interpreter modeling approach first developed under Task 10. Called 'hierarchical pre-post logic' (or HPL), this model has seen further refinement during Task 12. The aspects of HPL covered here include the modeling of interpreter behavior, interpreter abstraction, interpreter liveness, and interpreter correctness.

Section 3 explains important issues in secure abstract-level composition. The primary focus is on the role that abstraction plays in secure abstract-level composition. Low-level hardware composition is reviewed and a new approach to abstract-level synchronization, based on interface-event clocking, is introduced. Section 4 describes how interface-event clocking impacts the modeling and verification of interpreterbased systems. It introduces 'multirate' interpreters, where the interpreter inputs and outputs clock at different rates. Largely through two significant examples, techniques to solve some important modeling and verification problems are demonstrated.

Section 5 contains a description of the new PMM specification models produced under this task and describes some modifications to the existing models required to support composition.

Section 6 presents our conclusions.

A brief description of the HOL theorem proving system is contained in Appendix A.

Appendix B contains the HOL listings of several interpreter verification test case studies.

Appendix C provides Processor-Memory Module specification examples.

#### 2 Hierarchical Pre-Post Logic

In this section we describe a formal modeling approach that addresses the specification and verification needs of the PMM. The interpreter behavioral model provides for the specification of both operation preconditions and postconditions, hence the 'pre-post' designation. The approach supports hierarchical decomposition of system specifications and the explicit relating of the different levels through the use of abstraction predicates, as explained in this section.

In describing this hierarchical pre-post logic (HPL), we make use of a specification approach introduced by Joyce [Joy90], by describing operators and data types *generically*. Many operators are defined only by their types, with nothing said about what operations they actually perform. In this way, theorems proven about them are applicable to all operators satisfying the appropriate type. We make extensive use of type variables so that our results are applicable, in some instances, to structures with arbitrary types.

In this section we make consistent use of the following variable names. The variables k, t, s, e, and p represent, in order, instructions, time, state signals, environment (input) signals, and output signals. When a variable is primed it denotes a *concrete*-level, or implementing, entity. Type variables prefixed by a \* are polymorphic and denote abstract types. Note that each of the types shown here is abstract except for that of the time variable. The type ":time" is an abbreviation for the HOL type for natural numbers ":num"

| Common Variables and Their Types |                                   |  |

|----------------------------------|-----------------------------------|--|

| Instructions:                    | k :*instr, k' :*instr'            |  |

| Time:                            | t :time, t' :time'                |  |

| State:                           | s :time→*state, s' :time'→*state' |  |

| Environment:                     | e :time→*env, e' :time'→*env'     |  |

| Output:                          | p :time→*out, p' :time'→*out'     |  |

The following generic operators are used throughout this section. We don't describe them in detail here, but merely point out that the first three (the execution predicate, precondition, and postcondition) are associated with the interpreter behavioral model (Section 2.1) and the last four (event predicate, state, input, and output abstraction) are used in the abstraction definition (Section 2.2).

The variable **rep** is an n-tuple whose elements are of the types specified for the generic operators. The operators are implemented as accessor functions that select elements of this n-tuple. For example, **EXEC** is a function that, when applied to **rep**, returns an arbitrary value of the appropriate type.

| Generic Operators        |           |                                       |

|--------------------------|-----------|---------------------------------------|

| Execution Predicate:     | EXEC rep  | :∗instr-→s_sig→e_sig-→p_sig→time→bool |

| Precondition:            | PREC rep  | :∗instr→s_sig→e_sig→p_sig→time→bool   |

| Postcondition:           | POSTC rep | :∗instr→s_sig→e_sig→p_sig→time→bool   |

| Event Predicate:         | G rep     | :time'→bool                           |

| State Abstraction:       | SAbs rep  | :s_sig'→e_sig'→p_sig'→time'→∗state    |

| Environment Abstraction: | EAbs rep  | :s_sig'→e_sig'→p_sig'→time'→*env      |

| Output Abstraction:      | PAbs rep  | :s_sig'→e_sig'→p_sig'→time'→*out      |

| where:                   |           |                                       |

| s_sig = (time→*state)    | s_sig' =  | (time'→*state')                       |

| e_sig = (time→*env)      | e_sig' =  | (time'→*env')                         |

| p_sig = (time→*out)      | p_sig' =  | (time'→*out')                         |

The rest of this section describes four major aspects of our modeling approach: (a) the interpreter behavior model, (b) abstraction between levels, (c) interpreter liveness, and (d) interpreter correctness. Each of these is covered in its own subsection.

#### 2.1 Interpreter Behavioral Specification

In this and the subsequent sections we begin first with a description of prior work, usually with the HOL system. After this we describe the HPL approach to the particular subject being addressed.

#### 2.1.1 Related Work

Interpreter modeling has a significant history now within the theorem proving community. In this section we discuss three different approaches that have been implemented within the HOL system, as well as others. Because the term 'interpreter' is such a broad one, covering essentially the entire class of finite-state machines, we have limited our focus to those approaches having been used to model hardware at higher levels of abstraction. By 'higher' we mean above the level of latches and flip-flops. The approaches cited here have all been used for modeling microprocessor instruction sets, for example. We have made minor modifications to the original definitions in some cases to achieve a common syntax for this section.

#### **'FSM' Approach**

The first approach was used by a number of researchers: Cohn for the Viper proof [Coh88][Coh89], Joyce for the Tamarack proof [Joy90], and Graham for the SECD proof [Gra92]. In each of these microprocessor modeling and verification efforts, the machine behavior was defined using a single function to represent the next state with respect to the current state and current environment. Interpreter outputs were not modeled.

FSM Specification Style [Coh88][Joy90][Gra92]  $\forall$  t . s (t+1) = NEXT\_STATE (s t) (e t)

This approach is a natural one to take and, indeed, worked as intended for all three of the cited efforts. However, one difficulty with it is its embedding of the instruction decoding operation within the next-state function. As explained in Section 2.4, this leads to some complexity in performing an implementation correctness proof.

#### **GIT Approach**

Windley developed the generic interpreter theory (GIT) to address some of the problems existing with the previous interpreter models [Win90]. The basic idea behind the theory is that by implementing (inside the theory) some of the difficult proofs common to many interpreter verifications, the user is spared the burden of carrying out these proofs. Furthermore, the theory presents to the user a well-defined interface, detailing exactly what kinds of specifications need to be made and precisely what lemmas need to be proved. This has the effect of greatly streamlining the specification and verification tasks associated with interpreter proofs that use the theory.

The GIT specification style, shown next, is different from the FSM style in its use of an instruction variable, k, which is defined by the function **SELECT**. **SELECT** takes the current state and environment and returns an instruction, or 'instruction key,' in the GIT parlance. **SELECT** can be thought of as an instruction *decoding* function.

The instruction key is used by the **INSTRUCTIONS** and **OUTPUT** functions to determine the particular next-state and output functions, respectively, to use for the current time. These functions are denoted **NEXT\_-**

**STATE\_K** and **OUTPUT\_K** here to indicate that they are associated with a single instruction, **k**, and do not define the behavior for the entire instruction set.

```

GIT Specification Style [Win90]

∀t. let k = SELECT (s t) (e t) in

let NEXT_STATE_K = INSTRUCTIONS k in

let OUTPUT_K = OUTPUT k in

(s (t+1) = NEXT_STATE_K (s t) (e t) ∧

p t = OUTPUT_K (s t) (e t))

```

From a specification standpoint, the GIT approach is very similar to the previous FSM models in its reliance on functions to define interpreter behavior. The incorporation of outputs into the GIT is a natural step forward however. Section 2.4 explains in more detail the advantages of the GIT approach over the previous models in its support for interpreter verification.

#### **RTS** Approach

In [Her92], Herbert describes a relational transition system (RTS), a modified GIT in which the behavior is expressed with relations rather than functions. One advantage of such a modification is that it admits *partial* descriptions of behavior. This was an important consideration in Herbert's work on incremental design verification, where proofs were sometimes being performed before the design was finished.

The RTS specification style is shown in the following HOL code. To begin, the approach makes use of a property list, **prop\_list**, where each property, **prop**, within this list is a 2-tuple. The first element of the 2tuple is an instruction key and the second element is a predicate. The main idea is that, for each execution step, exactly one key will be selected and the predicate it is paired with acts as a 'postcondition' for the exection step. The predicate IS\_SELECT (k, s t, e t) is a relational version of the GIT SELECT function. It returns true when the instruction key, k, is selected by the current state, s t, and environment, e t. The postcondition predicate specifies the correct relationship between the next state and the current state and environment.

Interpreter behavior is expressed as: for every property, prop, if prop is a member of the property list, and if the key within prop matches that selected by IS\_SELECT, then the postcondition within prop is satisfied.

```

RTS Specification Style [Her92]

∀ t. let k = ɛ k. IS_SELECT (k, s t, e t) in

(∀ prop. prop MEM prop_list ∧

(FST prop = k)

⊃

SND prop (s (t+1), s t, e t)))

where: prop_list is a list of (instruction tag, predicate) pairs with type:

":(*instr # (*state#*state#*env→bool)) list"

```

The use of the choice operator ( $\epsilon$ ) here is to guard against the possibility that multiple instruction keys are selected at a single time. Such a possibility would constitute a specification error and would be caught by this approach since the 'uniqueness' required to process the choice operator would not be established.

#### 2.1.2 HPL Interpreter Behavior

Our interpreter behavioral model has benefitted from the prior work done on the FSM and GIT approaches. Herbert's efforts proceeded in parallel with ours, however, and thus our modeling work was performed independently of it.

As was the case for Herbert, the motivation for developing a new interpreter model here was certain limitations within the existing approaches. In the case of HPL, the objective was to model fault-tolerant systems at very high levels of abstraction. The model required three elements: (1) a predicate to represent the state of a system prior to a mission, (2) a predicate to represent a set of fault-occurrence properties, and (3) a predicate to represent the system state at mission end. The existing models did not provide this.

This work on fault-tolerance modeling was performed outside of this contract, and is described in detail in [Fur94]. It produced the basic structure of the model, with the three elements mentioned above given the names *precondition*, *execution predicate*, and *postcondition*, respectively. However, most of the work described in this section, and virtually all of that described in the following sections, was performed under Tasks 10 and 12 of this contract.

#### **Interpreter Definition**

To specify hardware interpreters, HPL employs only two of the three predicates directly: the execution predicate (**EXEC rep**) and the postcondition (**POSTC rep**) as shown in the following definition. Interpreter correctness is stated informally as "whenever an instruction is executed its postcondition is satisfied." This represents the standard behavior used in the other models described above. Where HPL differs is the combination of: (a) the use of an explicit instruction variable, **k**, (b) the separation of instruction decoding and execution into their own predicates, and (c) the relational-style postcondition predicate.

As explained in Section 2.4, providing the instruction variable k as part of the interpreter definition permits straightforward instruction set case splitting, thus simplifying correctness proofs. This is achieved without having to perform nontrivial theorem proving within a generic theory.

As explained later in this section, and in the interpreter liveness discussion in Section 2.3, having access to the instruction decoding behavior (the execution predicate) provides certain modeling advantages that can be exploited.

Because the postcondition has very little predefined structure, HPL provides a great amount of flexibility in its interpreter modeling. It is equivalent to RTS in this regard. It can accommodate the functional style of the FSM and GIT approaches, as well as the relational style of the RTS approach.

```

Intepreter Definition:

⊢ INTRP repsep = ∀kt. EXEC repksept⊃ POSTC repsept

```

#### **Preconditioned Interpreter Definition**

The above definition faithfully models the interpreter behavior we are interested in, and for many verifications it is suitable for direct use. There are some verification problems, however, that are inconvenient to solve using this model directly. In these proofs, correct execution requires that certain state variables contain specified initial values at the beginning of an operation. The transaction-level proofs for the PMM are one example of this. A convenient way to handle these proofs is to first postulate the appropriate values using a precondition (**PREC rep**) and then prove the simpler theorem shown next.

```

Preconditioned Interpreter Definition:

⊢ INTRP_PREC rep se p =

∀kt. EXEC rep k se p t ∧ PREC rep k se p t ⊃ POSTC rep k se p t

```

The need for operation preconditioning results in an additional theory obligation. The precondition must be initially established at time **0**, and then it must be propagated at each successor time. The following definition of 'precondition satisfaction' describes this property.

```

Precondition Satisfaction:

⊢ PREC_SAT rep se p =

(∀ k. EXEC rep k se p 0 ⊃ PREC rep k se p 0) ∧

(∀ k k1 t. POSTC rep k se p t ∧ EXEC rep k1 se p (SUC t) ⊃ PREC rep k1 se p (SUC t))

```

**PREC\_SAT** is a property that clearly must be met if the precondition is to hold at every operation boundary. The reason for including the execution predicate here is that, in general, a state's value may be defined conditionally on an input occurrence that is encapsulated within the execution predicate.

While the need for the above condition is expected in a correctness proof, the following proof obligation did surprise us initially. It states that when an instruction is executed at some (nonzero) time then there must have been an instruction executed at the previous time.

```

Instruction Sequence Liveness:

\vdash SEQ_LIVE repsep = \forall kt. EXEC repksep (SUCt) \supset (\exists k1. EXEC repk1 sept)

```

'Instruction sequence liveness' is an issue for us because we are verifying an instruction set rather than a program. In a program we know that a prior instruction is executed by virtue of its position within the code. Instruction set verification does not permit this solution, instead we must explicitly prove it.

In the approach described here, interpreter correctness can be verified by satisfying the following three proof obligations. The justification theorem states that when they are satisfied, then the interpreter is correct The actual HOL definitions and the proof for this justification theorem are contained in Appendix B.

| Modified Proof Obligations:                                                        | Justification Theorem:                                                                    |

|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| ∀ repsep.INTRP_PREC repsep<br>∀ repsep.PREC_SAT repsep<br>∀ repsep.SEQ_LIVE repsep | - ∀ repsep.<br>INTRP_PREC repsep⊃<br>PREC_SAT repsep⊃<br>SEQ_LIVE repsep⊃<br>INTRP repsep |

In the tradition of Windley's generic interpreter theory, we believe that the breakdown of theorem proving tasks into two distinct classes, as shown here, has a great practical benefit in reducing the number of theorem proving tasks that must be repeated in every interpreter verification. The advantage to proving interpreter correctness this way is that the justification-theorem proof could be embedded within a generic theory and then simply reused whenever a new interpreter is being verified. The user would only be concerned with proving facts that were specific to the particular circuit being addressed. In this case, these are the proof obligations shown here.

#### 2.2 Interpreter Abstraction

Virtually all interpreter verifications performed in HOL have used the abstraction ideas described by Melham in [Mel90]. Of the different types of abstraction described in this previous work, two are of primary interest to interpreter modeling and verification: (a) temporal abstraction and (b) data abstraction. These thus represent the major topics of this section.

#### 2.2.1 Related Work

This section focuses on the temporal and data abstraction ideas described in [Mel90] used in most of the microprocessor verifications cited earlier in this report.

#### **Temporal Abstraction**

Temporal abstraction relates the coarse-grained time at an abstract level of description to a fine-grained concrete time. The objective of a temporal abstraction approach is, therefore, to define an appropriate mapping between the two levels. This is necessary so that the state, input, and output signals defined over these times can be related.

In typical interpreter applications, the temporal relationship is defined with respect to the concrete-level signals. An 'event predicate,' **G rep**, shown among the following HOL expressions, when true, marks an 'instruction boundary event.' These events define the concrete times marking the boundaries of the abstract operations.

| Event Predicate:<br>Instruction Boundary Event: | (G rep) :time'→bool<br>G rep t' = T | 4 |

|-------------------------------------------------|-------------------------------------|---|

|                                                 |                                     |   |

Numerous examples of event predicates exist. In the low-level modeling work of [Her88] and [Mel90], for example, clock-level operation boundaries are defined by the rising edge of the system clock. In the microprocessor verifications cited previously, the boundaries of the abstract-level assembly instructions are defined by the return of the microcode program counter to address zero.

Having an event predicate is not sufficient, however, to relate an abstract level to an underlying concrete level. For example, while the event predicate **G rep** defines the concrete times marking the abstract-operation boundaries, it cannot identify the *particular* abstract times that correspond to these boundaries. The usual approach to address this is to define the abstract time as the accumulated 'count' of the boundary events.

'Operation boundary predicates' implement this idea, as shown in the following HOL code. NTH\_TIME\_TRUE t (G rep) 0 t' relates the abstract and concrete times through the event predicate G rep. The predicate is read "G rep is true for the t'th time at concrete time t'." The 'temporal abstraction function,' t\_abs, maps abstract time to concrete time using the instruction boundary predicate. For each abstract time t, it returns a concrete time, t', such that G rep is true for the t'th time at t'.

| Instruction Boundary Predicate: | NTH_TIME_TRUE t (G rep) 0 t'                                                                    |

|---------------------------------|-------------------------------------------------------------------------------------------------|

|                                 |                                                                                                 |

| Temporal Abstraction Function:  | t_abs :time $\rightarrow$ time' = $\lambda$ t . $\varepsilon$ t' . NTH_TIME_TRUE t (G rep) 0 t' |

|                                 | Laba .une - une - xt.ct. http://www.une - xt.ct.                                                |

#### **Data Abstraction**

Data abstraction relates the abstract-level data values to the data of the implementation. It is typically implemented with functions that map concrete values to abstract values. The following expressions show the abstraction functions mapping the state, environment, and output. While these functions can theoretically handle arbitrary mappings, in practice the abstract data structures are usually simple subsets of the underlying concrete data structures. Note that the types for these functions are different from those of the

generic functions shown at the beginning of Section 2. The generic functions apply to the data abstraction described in the next section.

Data Abstraction Functions

State Abstraction:

s\_abs :\*state'→\*state

Environment Abstraction:

e\_abs :\*env'→\*env

Output Abstraction:

p\_abs :\*out'→\*out

#### **Putting the Two Together**

The following HOL expressions show how the temporal and data abstraction operators are normally combined to implement abstraction ( $\mathbf{o}$  is the function composition operator). The abstract state signal  $\mathbf{s}$ , for example, is defined as the expression within the parentheses on the right-hand side. The value defined by this expression applied to an abstract time  $\mathbf{t}$  is seen to be a concrete value ( $\mathbf{s}' \mathbf{t}'$ ) mapped through  $\mathbf{s}_a\mathbf{bs}$ . The concrete time  $\mathbf{t}'$  is the abstract time  $\mathbf{t}$  mapped through  $\mathbf{t}_a\mathbf{bs}$ .

```

Traditional Interpreter Abstraction Relationships:

st = (s_abs o s' o t_abs) t

et = (e_abs o e' o t_abs) t

pt = (p_abs o p' o t_abs) t

```

#### 2.2.2 HPL Abstraction

The HPL approach to interpreter abstraction uses the same temporal abstraction ideas as above but otherwise differs in two fundamental ways: (a) it uses more-powerful data abstraction functions to implement interval abstraction (described in the Task 10 Specification Report [Fur93a]) and (b) it implements the abstraction within 'abstraction predicates' rather than embedding it within the interpreter correctness statement.

The following definition describes a typical abstraction predicate. Again, the temporal mapping uses the function  $t_abs$  defined above. The difference from the traditional interpreter approach is that the state abstraction functions are strengthened to support interval abstraction. For example, the state abstraction is implemented using SAbs rep, which operates on the concrete state *signal*, s' (type :time' $\rightarrow$ \*state'), rather than the state *value*, s' t' (type :\*state'). This gives the user of the abstraction function freedom to map multiple (temporal) instances of a concrete signal to the abstract level, and allows mapping from concrete times other than t'.

The abstraction is defined within an abstraction predicate, in contrast to current practice where it is defined within the interpreter correctness statement. One of the benefits of this approach is that abstraction is now defined and reasoned about as a stand-alone entity. This more closely matches our intuitive understanding of abstraction, which we view as defining the relationships between abstract and concrete variables, period. We do not require the existence of a correctness statement to think about these relationships. We also find the explicit naming of both the concrete and abstract signals to increase the clarity of these relationships. The implicitly defined abstract signals in the traditional approach provide a more cryptic definition.

```

HPL Abstraction Predicate:

```

```

⊢ INTRP_ABS rep s e p s' e' p' =

∀t. let t' = t_abs t in

((st = SAbs rep s' e' p' t') ∧

(et = EAbs rep s' e' p' t') ∧

(pt = PAbs rep s' e' p' t'))

```

As explained in [Fur93a], the traditional approach to interpreter abstraction, implemented in the GIT, is not flexible enough to handle the required mapping between the clock level and the transaction level of the PIU. This was our original motivation for examining alternative approaches, leading to the selection and further development of HPL.

#### 2.3 Interpreter Liveness

Interpreter liveness is a subtle issue, and the reason for this is that it involves the Hilbert choice operator,  $\varepsilon$ . To help clarify things we consider again the HPL abstraction predicate, but we define it in a somewhat different way (and without  $\varepsilon$ ) as shown in the following HOL code. This definition is actually one that could be used for an implementation proof (it has certain disadvantages with respect to composition however). We show it because it demonstrates the clear need to establish that NTH\_TIME\_TRUE t (G rep) 0 t' is true for the temporal variables t and t'. This is the interpreter liveness proof obligation.

```

Modified Abstraction Predicate:

⊢ INTRP_ABS_X rep s e p s' e' p' =

∀ t t'. NTH_TIME_TRUE t (G rep) 0 t'

⊃ ((s t = SAbs rep s' e' p' t') ∧

(e t = EAbs rep s' e' p' t') ∧

(p t = PAbs rep s' e' p' t'))

```

In the actual abstraction predicate (of Section 2.2.2) the concrete time is mapped from the abstract time using the rewritten t\_abs function as:  $t' = \mathcal{E} t'$ . NTH\_TIME\_TRUE t (G rep) 0 t'. What can we say about this time t'? Nothing, actually, unless we can prove the following subgoal:  $\exists t'$ . NTH\_TIME\_TRUE t (G rep) 0 t' In other words, just as above, to achieve an interpreter correctness proof, the predicate NTH\_TIME\_TRUE t (G rep) 0 t' must be proven true for the abstract instruction executed at time t. Without this the concrete and abstract variables cannot be related through the data abstraction functions. This proof obligation is easily obscured by the way that the abstraction predicate is defined in Section 2.2.2.

#### 2.3.1 Related Work

In Melham's treatment of abstraction, the interpreter liveness proof obligation is to establish a 'universal liveness' property similar to the one shown next. Proving liveness therefore entails showing that an abstract-to-concrete temporal mapping exists for *all* abstract times (or **G rep** is true infinitely often).

```

Universal Liveness:

|- INTRP_LIVE rep =

∀t.∃t'. NTH_TIME_TRUE t (G rep) 0 t'

```

When the event predicate depends on the interpreter input (i.e., G rep = G'e' rep) then universal liveness cannot be proven. The source of the input may simply stop transmitting, for example. In their low-level hardware verification work, both Melham and Herbert simply assumed universal liveness for the clock input signals within their event predicates [Mel90] [Her88].

When the event predicate is a function of the state (i.e.,  $\mathbf{G} \mathbf{rep} = \mathbf{G' s' rep}$ ) then the situation is much improved, and universal liveness can be proven. In the microprocessor verifications of Graham and Joyce, for example, the liveness property proven was actually somewhat different from the above definition. The basic idea in their work was to instead prove the following two properties: (1) **G** rep is true in at least one state, and (2) whenever **G** rep is true in a state then it is true in some later state [Gra92] [Joy90]. The proofs

of these two facts are more easily accommodated in an interpreter correctness proof than a direct assault on the above definition. Windley's GIT incorporated many of these proof steps as part of the theory's infrastructure [Win90].

#### 2.3.2 HPL Interpreter Liveness

For the vast majority of the transaction-level implementation proofs within the PMM, the event predicate is a function of the input rather than the state. The option of assuming universal liveness is not very appealing here, particularly for the S process that is concerned with start-up behavior. Here we would expect the event predicate (an active reset) to occur exactly once.

Fortunately, it is not really necessary to establish universal liveness to achieve an implementation proof. The sufficient property to establish is that, given that an abstract operation is executed at time t, then there exists a t'th occurrence of the event predicate. This property is defined next.

```

Conditional Liveness:

⊢ COND_INTRP_LIVE rep sep =

∀ kt. EXEC rep k sep t

⊃∃t'. NTH_TIME_TRUE t (G rep) 0 t'

```

We have demonstrated in our on-going P-Port verification that this definition is strong enough to achieve implementation correctness proofs. It is also weak enough so that it can be proven itself, provided that the execution predicate and abstraction predicate are defined appropriately. We use an example from the PIU P-Port to illustrate what we mean here. More explanation of the following terms can be found in [Fur93a].

In the P-Port the event predicate is defined with respect to two L-Bus signals received from the local processor:  $G \operatorname{rep} = \lambda t'. \neg BSel(L_ads_E (e't')) \land BSel (L_den_E (e't'))$ . Now, turning to the transaction level, the execution predicate EXEC rep k s e p t is true if one of the six valid L-Bus transaction opcodes is received at time t; PBM\_WrLM, PBM\_WrPIU, PBM\_WrCB, PBM\_RdLM, PBM\_RdPIU, or PBM\_RdCB. In order to be able to prove conditional liveness, we place the following constraint on the abstraction: We require that the abstraction function define a transaction opcode equal to one of these values only if NTH\_TIME\_TRUE t (G rep) 0 t' is true, where t' is defined in the normal way as t\_abs t.

This constraint says that we don't consider the P-Port to have received a valid transaction opcode at time t unless the P-Port has received t (clock-level) transaction requests. This is really not much of a constraint since we would expect this fact to be true anyway.

To conclude this section, we point out only that it is the separation of the operation decoding function into its own execution predicate that permits this preferred solution to the interpreter liveness problem.

#### 2.4 Interpreter Correctness

With a few exceptions (e.g., [Hun86]), interpreter correctness statements have generally followed the same form. These statements define an implication in which the behavior defined by the implementation interpreter implies the behavior defined by the specification interpreter. If we ignore the issues of abstraction and liveness, these statements are represented by the following pseudo-code.

General (Stripped Down) Interpreter Correctness Definition: ⊢ imp\_intrp behavior ⊃ spec\_intrp behavior

Proving correctness statements such as this directly is usually avoided because of the complicated behaviors involved. One common approach used to break these proofs into smaller subgoals is to perform

a case split on the abstract-level instruction set. When this is done the proof obligations resemble the following pseudo-code. Each of these subgoals is read: "if we assume the concrete interpreter behavior, and if we assume that the condition for (abstract) operation J's execution is satisfied, then the specified behavior for operation J results."

General (Stripped Down) Operation Case Split: |- imp\_intrp behavior ⊃ spec\_op1 execution condition ⊃ spec\_op1 postcondition |- imp\_intrp behavior ⊃ spec\_opN execution condition ⊃ spec\_opN postcondition

#### 2.4.1 Related Work

The microprocessor verifications cited earlier employ a correctness statement similar to the one shown next. This statement says: "if we assume the given implementation and interpreter liveness, then the instance of the specification interpreter 'defined by the abstraction' is correct." This embedding of the abstraction within the correctness statement follows [Mel90], and is the approach used to formally link the abstract- and concrete-level variables.

```

Interpreter Correctness Definition (based on [Mel90],[Joy90], etc.):

∀ rep s' e' p'.

INTRP_imp rep s' e' p' ∧

INTRP_LIVE rep

⊃ INTRP_spec rep (s_abs o s' o t_abs)

(e_abs o e' o t_abs)

(p_abs o p' o t_abs)

```

Given this basic form, the correctness proof can be approached in a couple of ways. The Viper, Tamarack, and SECD proofs all employed variations of a common technique. Windley's GIT-based verification of AVM-1 was a significant departure from this however.

#### **'FSM' Approach**

As indicated in Section 2.1, the FSM-style interpreter specification approach presents some difficulties for correctness proofs. The problem is that the embedding of the instruction decoding within the **NEXT\_STATE** function makes it somewhat difficult to perform the desired case split on the instruction set. Although this is not a major problem, it does require extra work in performing the verification.

Joyce, in the proof of Tamarack [Joy90], handled the instruction case split by explicitly defining a proof obligation for each instruction in terms of its 3-bit opcode bit combination. In all, there were eight instructions verified this way. Some final processing was needed to show that the collection of cases proved actually covered all possible combinations of bit patterns.

In the SECD proof [Gra92], Graham introduced a disjunctive 'valid\_program\_constraint' as a precondition within the correctness statement. Each disjunct represented the conditions under which that particular instuction was selected for execution. The case split was performed directly as part of the proof, with each case using its disjunct as an assumption. A disadvantage of this approach was the extra work required to specify the constraint, which was lengthy and quite detailed.

#### **GIT Approach**

Windley's work on the GIT recognized that the steps needed (in [Joy90]) to process the individual instruction proofs into a finished verification were independent of the actual system being verified. Rather, they were functions of the structure of the interpreter model, which could be fixed. Where the GIT takes a significant departure from these previous efforts is in collecting up these sorts of proof requirements and proving them within a generic theory.

This has two beneficial aspects. First of all, the workload for the user of the theory is reduced since the theory proofs are reused. Secondly, the theory presents to the user a clear definition of the user's proof obligations. For example, the GIT presents the following two obligations to the user.

```

GIT User Proof Obligations [Win90]:

(∀ s' e' p' k. INST_CORRECT s' e' p' k) ∧

(∀ s' e' p' k. OUTPUT_CORRECT s' e' p' k)

```

We don't go into the details of INST\_CORRECT and OUTPUT\_CORRECT here since they are somewhat lengthy – these details can be found in [Win92]. The important point to be noted about these obligations is that they both contain the 'for all k' that makes clear the need for an instruction case split. Again, the proof infrastructure within the theory takes care of the details necessary to derive the interpreter correctness statement described previously.

#### 2.4.2 HPL Correctness

HPL interpreter correctness is proven using the same general approach described above. There are some differences however, primarily in (a) the handling of abstraction and (b) the support for instruction case splitting.

The HPL interpreter correctness definition is shown next. This statement says: "if we assume the given implementation and interpreter liveness, and if the abstraction is defined according to the abstraction predicate there, then the specification interpreter is correct."

```

HPL Interpreter Correctness Definition:

\forall rep s e p s' e' p'.

INTRP_imp rep s' e' p' \land

INTRP_ABS rep s e p s' e' p' \land

COND_INTRP_LIVE rep s e p

\supset INTRP_spec rep s e p

```

We view this correctness statement as preferable over the statement of the last section in two respects: (a) the theorem consequence contains the specification interpreter, rather than a particular instance of the interpreter, and (b) abstraction is clearly (and correctly) treated as an *asserted* entity by its very position within the correctness statement. The practical differences between the two definitions may be small however.

Instruction case-split support is not evident from this definition. To see where it exists we need to revisit the interpreter definition described in Section 2.1.2. Informally, this definition says: "for all k and t, if instruction k is executed at time t then the postcondition for k is true at t." Thus, the instruction case split requirement is clearly indicated in the interpreter definition itself. It is made visible during an interpreter proof as soon as the abstract interpreter is rewritten, as a normal part of the initial proof steps in any verification.

#### 3 Issues in Secure Abstract-Level Composition

An important capability of a theorem-proving approach to hardware verification is the ability to achieve provably correct compositions of subsystem models at high levels of abstraction. This is an area in which theorem proving holds a potential advantage over competing approaches such as model checking [McM93], as well as others.

There are good practical reasons for composing at high levels of abstraction. As pointed out in the Task 10 Specification Report [Fur93a], abstract-level compositions are easier to verify than those performed lower in the hierarchy. In addition, the difficult implementation proof performed within a subsystem to achieve a verified abstract level is reused every time the subsystem is designed into a new system configuration. In contrast, composition proofs must be repeated for new configurations.

For the specification and verification of large hardware systems there is probably no choice but to perform as much abstraction as possible within subsystems, before composition, just to get a handle on the complexity. As demonstrated in the work under Task 10, performing the clock- to transaction-level abstraction within the PIU ports greatly reduced the complexity of the PIU system model, and is expected to reduce the amount of required theorem proving as well.

In this section we overview some important issues in achieving provably correct compositions of abstract subsystem models. We first review the role of abstraction in this process. Following this, we describe the role of temporal abstraction for secure composition at low levels of abstraction. We then contrast this to the temporal abstraction necessary for composition at levels comparable to the transaction level. The interface-event clocking introduced here provides the subject for Section 4.

#### 3.1 The Role of Abstraction

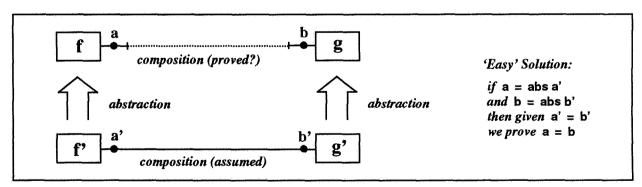

The problem of ensuring the soundness of abstract-level composition is illustrated by Figure 3.1 At the top of this figure are two components, f and g, with output a and input b, respectively. Each of these components is an abstract representation of the component beneath it, f' and g', respectively. In its intended operation, the abstract component g should receive the output of component f; in other words, we desire that the value on signal b be equal to the value on signal a, for all time t. The problem is to show that making this connection (composing f and g) is 'sound,' or that the composed abstract-level system remains an accurate abstraction of the composed concrete-level system.

Figure 3.1: The Problem of Composing Abstract Models.

At the lowest level of abstraction in a model hierarchy, it is necessary to make the assumption that components are interconnected in some specified way. This is akin to assuming that the individual components have a specified behavior, and, hence, is unavoidable. However, at high levels of abstraction it is not acceptable to make such assumptions for the interconnections, just as it is not acceptable to assume the required behavior of the individual components. Fortunately, we don't need to make these assumptions, since the necessary properties can, in principle, be proven from the underlying implementation.

Referring again to Figure 3.1, the abstract-level composition proof obligation is to show that the signals **a** and **b** are equal, given the specified models for components **f'** and **g'**, plus their indicated interconnection, plus the abstraction linking **f'** with **f** and **g'** with **g**. The easiest way that this can be accomplished is if **a** and **b** are defined using a common abstraction function, **abs** for example, from their concrete counterparts **a'** and **b'** Since it is already assumed that **a'** and **b'** are equal, the desired property that **a** (= **abs a'**) and **b** (= **abs b'**) are equal would result directly.

In fact, the condition in which the abstract component inputs and outputs are abstractions of only the concrete inputs and outputs (and not state) holds among the transaction- and clock-level models of the PMM. The PMM specification hierarchy was constructed in this way partly in response to the composition problems that were anticipated during Task 10.

#### 3.2 Temporal Abstraction for Globally-Clocked Systems

The work referred to in the last section (in [Her88] and [Mel90]) was concerned with compositions at the 'clock' level of abstraction, using concrete-level components defined at the 'timing' level. At the clock level, a time step corresponds to a single period of the system clock. The *timing level* [Her88] has as its time step a fixed increment of real time, such as a nanosecond or a fraction of a nanosecond. Even though we do not use a timing level in our own work, it is worthwhile to examine the temporal abstraction used in this prior work in preparation for the transaction-level discussion of the next section.

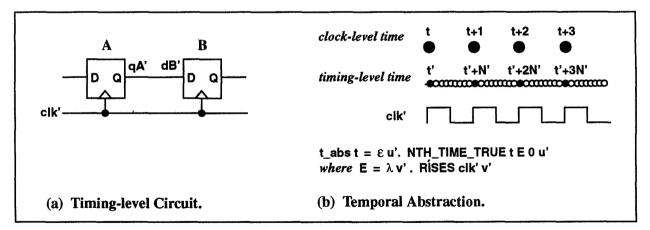

Figure 3.2(a) shows a very simple circuit that we use to illustrate some of these concepts. The flip-flops are both assumed to change their states on the rising edge of the clock signal **clk'**. The output of flip-flop A is assumed to be connected to the input of flip-flop B at the timing level of abstraction shown in the figure. The composition problem here is to prove that the same interconnection can be made at the clock level of abstraction.

#### Figure 3.2: Temporal Abstraction Linking the Timing and Clock Levels.

Almost intuitively, hardware designers know that two clock-level flip-flop models can be interconnected this way, provided that the applicable setup and hold times are all met. Ignoring these details, which we consider to be data abstraction issues, the underlying reason why this is so is that both flip-flops are clocked on the same edge of the same clock. In other words, they both employ the same temporal abstraction to link their timing and clock levels. As shown in Figure 3.2(b), the temporal abstraction function  $t_{abs}$ relates the clock level to the timing level at the rising edges of the timing-level clock. The event signal **E**, defined using the predicate RISES, is true precisely at these points of interest. RISES clk' v' is true precisely when clk' v' is true and clk' (v'-1) is false.

The synchronous timing control that is provided by a common clock is instrumental in making the design of even large digital systems tractable. Again, it is the use of a common temporal abstraction function implied by this that eases the composition-correctness burden on the digital designer. Likewise, this common clock simplifies the formal modeling and verification of composition at the clock level of abstraction. Unfortunately, from a modeling standpoint, digital designers do not include global clocks in their designs that step at the rate of all the levels in a specification hierarchy. The techniques described in this section need to be generalized to work at these higher levels.

#### 3.3 Temporal Abstraction for Interface-Clocked Systems

In contrast to the low-level work described above, we are aware of no work to compose interpreters at higher levels of abstraction. The bulk of the work done by the theorem-proving community targets microprocessors. In this work the top level is typically the *macroinstruction level*, where a time step corresponds to the execution of an assembly-language instruction. The level immediately below this is often at the *micro-instruction level*. When compositions are performed as part of these microprocessor verifications however (for example between the microprocessor and system memory), it is done at the clock level or lower (e.g., [Hun86],[Coh88],[Joy90],[Win90],[Gra92],[Lev93]). In [Fur93a] we explained why we reject this approach for the PMM.

One difficulty with higher-level composition is that, in direct contrast to the clock level, there is no notion of a global clock to synchronize the actions of the participating subsystems. For this reason, higher-level composition requires a certain amount of flexibility in defining what constitutes a 'clock,' as well as its corresponding 'time steps.'

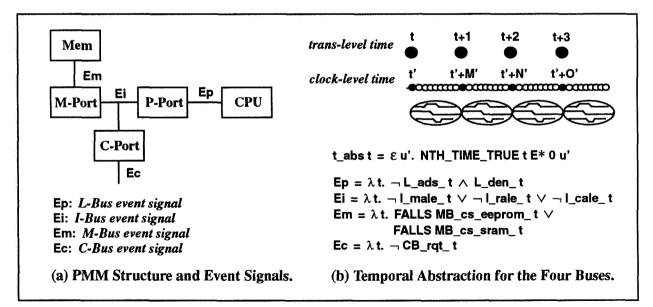

As before, one key to secure higher-level composition is the use of a consistent temporal abstraction for the subsystems being composed. For our transaction-level modeling, we have accomplished this by focusing on the bus protocols used by the subsystems of the PMM. At this level, a time step is defined by the occurrence of an event corresponding to the initiation of a new bus transaction. Figure 3.3 describes these events for the four buses of the PMM: the L-Bus (or P-Bus), I-Bus, M-Bus, and C-Bus.

Figure 3.3: Temporal Abstraction Linking the Clock and Transaction Levels.

The L-Bus event signal **Ep**, for example, when true for a clock-level time **tp'** indicates that a new L-Bus transaction has begun, and, hence, that the transaction-level time should be incremented.

In a system with multiple buses then, it is possible that multiple clocks will exist. Section 4 covers the issues involved in modeling and verifying interpreters with interface clocking. (In the rest of this report we generalize the notion of bus protocols to include any communication policy between two or more subsystems, we use the more generic term *interface protocol* to describe them.)

and the

#### **4** Synchronizing Interface-Clocked Interpreters

The last section has shown that interface-event clocking can present scenarios in which interpreters relate to different events over their input and output interfaces. Since these events dictate the temporal abstraction for the abstract level, this implies that the abstract-level temporal variables for an interpreter's input and output may themselves be different. In this section we examine how this possibility affects the modeling and verification of interpreter-based systems.

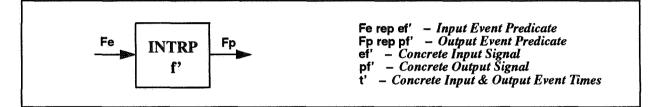

The discussions of this section will be largely example driven. Figure 4.1 introduces the modeling style that will be used throughout the section. The interpreter in this figure has an input event predicate **Fe rep ef** and output event predicate **Fp rep pf**. The 'representation' variable **rep** has the same interpretation as in the previous sections. For example, **Fe rep** is a generic operator that maps a signal, **ef** in this case, to the booleans. The actual definition of **Fe rep**'s behavior is undefined, only its type is known. Within the actual HOL segments shown in this section, the complete expression will be used. However, in the text we will usually employ the abbreviated form: **Fe, Fp**, etc.

#### Figure 4.1: Description of an Interpreter's Transaction Events and Concrete-Level Variables.

The input and output signal names follow a standard pattern of prefixing an e or a p, for the inputs and outputs respectively, to the name of the interpreter under consideration. The concrete-level signal names ef' and pf' are therefore used for the concrete-level interpreter f' All concrete signals used in the following examples are of the type ":time' $\rightarrow$ \*io"; the abstract signals map abstract time, t, to the same signal-value type \*io.

To permit this section to focus on issues of composition, the models in this section avoid unnecessary complexity wherever feasible. For example, the behavior of both concrete- and abstract-level interpreters is a simple flowthrough:  $\forall t'$ . pf' t' = ef' t' in the above example. We will describe other assumptions as they are needed.

Moving on to the interpreter modeling issues themselves, we begin by pointing out that, even though a given interpreter's event predicates may be different for the inputs and outputs, this does not mean that the temporal variables themselves must be different. A good illustration of this is the P-Port within the PIU. Here, the port's input events are defined over the L-Bus and its output events over the PIU I-Bus. These are clearly different events yet the transaction-level temporal variable is the same for the inputs and outputs. The reason for this is that the input-to-output event mapping is one-to-one and onto. In other words, each input event causes at least one output event, and, furthermore, it causes at most one output event.

Therefore, an important consideration for interface-clocked interpreters is the relationship between the occurrences of the input-transaction requests and the resulting output-transaction requests. These requests may or may not be one-to-one and they may or may not be onto.

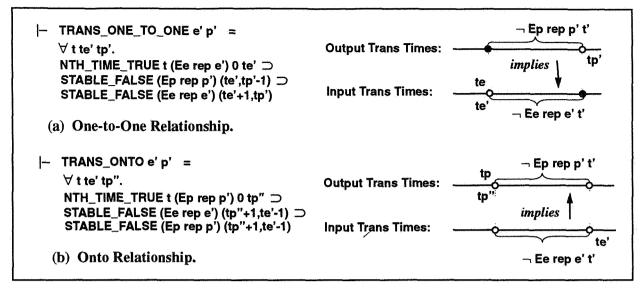

To gain a better picture of exactly what we mean here, Figure 4.2 shows these two relationships graphically. The one-to-one mapping, defined by the HOL definition **TRANS\_ONE\_TO\_ONE** in part (a), describes an interpreter where every input transaction event results in a unique output transaction event. In other words, if an input request arrives at concrete time **te**', then no further requests will arrive until after an output

Figure 4.2: Transaction One-to-One and Onto Relationships.

transaction is begun. The predicate STABLE\_FALSE f(t1,t2) is true precisely when ft is F for all t in the closed interval [t1, t2].

The onto mapping defined in part (b) describes an interpreter where every output request is in response to a unique input transaction event. Here, if an output request is transmitted by the interpreter at concrete time tp", then no more such requests will be transmitted until a new input transaction request is received.

The one-to-one and onto relationships just described provide for a four-element partitioning of the class of (single-input, single-output) interface-clocked interpreters:

- (1) Interpreter transactions are one-to-one and onto.

- (2) Interpreter transactions are *one-to-one* but not onto.

- (3) Interpreter transactions are not one-to-one but are *onto*.

- (4) Interpreter transactions are neither one-to-one nor onto.

Examples of all four interpreter types can be found in the PMM, depending on how one defines the transaction events for the various buses. As we have defined them, they lead to the existence of interpreter types (1), (2), and (3). In the following three subsections we examine each of the first three interpreter types, primarily through simplified examples.

#### 4.1 Bijective Monorate Interpreters

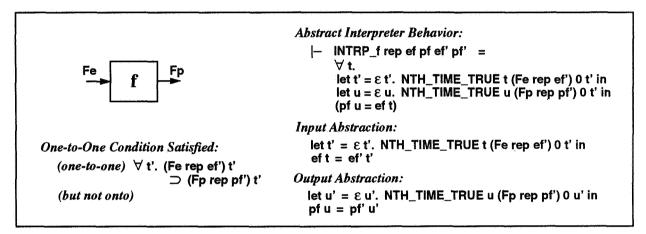

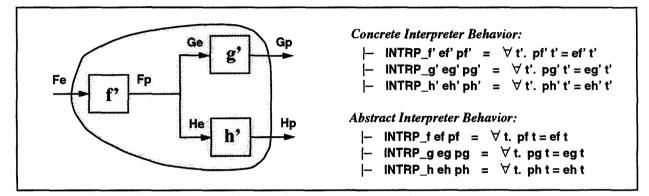

When the mapping between the interpreter input transactions and the output transactions is bijective (both one-to-one and onto) we have the familiar situation in which the abstract clock rates are the same for the interpreter inputs and outputs. In order to introduce some concreteness into the following discussion, we will refer often to the simple circuit example shown in Figure 4.3.

| Fe f' Fp                                                                                                         | Concrete Interpreter Behavior:<br>$ -$ INTRP_f' ef' pf' = $\forall$ t'. pf' t' = ef' t'     |

|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

|                                                                                                                  | Abstract Interpreter Behavior:<br>$ -$ INTRP_f ef pf = $\forall$ t. pf t = ef t             |

| One-to-one and Onto Conditions Satisfied:<br>(one-to-one)<br>$\forall$ t'. Fe rep ef' t' $\supset$ Fp rep pf' t' | Input Abstraction:<br>let t' = ε t'. NTH_TIMĘ_TRUE t (Fe rep ef') 0 t' in<br>ef t = ef' t'  |

| <i>(onto)</i><br>∀t'. Fp rep pf' t' ⊃ Fe rep ef' t'                                                              | Output Abstraction:<br>let t' = ɛ t'. NTH_TIME_TRUE t (Fp rep pf') 0 t' in<br>pf t = pf' t' |

Figure 4.3: Example Bijective Monorate Interpreter Model.

The synchronization problem for monorate interpreters is fundamentally different from the interpreter synchronization problems of the following two sections. Here, we are concerned with an aspect of the interpreter implementation verification. In a verification such as this it is clearly necessary to establish a proper input-output relationship for the concrete-level interpreter; in other words, in response to an input event request at time t' the interpreter must be shown to produce correct outputs. Now, having this, it is an additional step to prove that the t'th input request produces the correct behavior corresponding to the t'th output transaction, and not some other output transaction.

A fair amount of our Task 10 work dealt with this synchronization problem for the PIU P-Port, and it resulted in the solution described in [Fur93a]. In our work under Task 12 we have revisited the Task 10 solution and made a fairly significant improvement to it. We don't detail the Task 10 approach here except to say that it requires two additional theorems not required by the new approach that we describe next.

The Task 10 work taught us that synchronizing an interpreter's abstract-level inputs and outputs can be divided into two subproblems that can be handled separately. These are: (a) establishing interpreter 'output liveness', and then, from this, (b) establishing the correct 'transaction ordering.' The following two HOL definitions precisely capture these two concepts. In these definitions, to save space we have introduced the terms **Ee** and **Ep** to represent **Ee rep e'** and **Ep rep p'**, respectively.

| Interpreter Output Liveness: In                                                                                                 | terpreter Trans Ordering:                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ├─ OUT_TRANS_LIVE e' p' =<br>∀ t te'.<br>NTH_TIME_TRUE t <i>Ee</i> 0 te' ⊃<br>∃ tp'. STABLE_FALSE_THEN_TRUE <i>Ep</i> (te',tp') | <ul> <li>NEXT_OUT_TRANS_IS_NTH e' p' =</li> <li>∀ t te' tp'.</li> <li>NTH_TIME_TRUE t <i>Ee</i> 0 te' ⊃</li> <li>STABLE_FALSE_THEN_TRUE <i>Ep</i> (te',tp') ⊃</li> <li>NTH_TIME_TRUE t <i>Ep</i> 0 tp'</li> </ul> |

The predicate **OUT\_TRANS\_LIVE** is true precisely when an output transaction event exists following every input transaction event. This is a property that clearly must be proved, since otherwise there would be no hope of establishing a proper temporal mapping on the interpreter output side. It is also a property that should be provable directly from the concrete-level definition of the circuit under consideration. Nothing is said about the ordering of such an output request, only that one must exist sometime on or after the arrival of the input request. The on-going P-Port verification includes this proof.

The predicate NEXT\_OUT\_TRANS\_IS\_NTH is distinguished from OUT\_TRANS\_LIVE in that it is usually not possible to be proved directly from the concrete-level circuit. The reason for this is that it involves the abstract-level time t. Since circuits don't normally maintain a memory of the number of input and output transactions processed, there is no notion of t contained within the circuit description. These types of theorems are most naturally proven by induction; in this case, on the abstract time t.

The following HOL segment describes an approach to achieving a proof for NEXT\_OUT\_TRAN-S\_IS\_NTH. In addition to the definition OUT\_TRANS\_LIVE just discussed, proof obligations exist for the definitions TRANS\_ONE\_TO\_ONE, TRANS\_ONTO, and FIRST\_TRANS\_CAUSAL. The first two of these were defined at the beginning of Section 4; the third is shown here. FIRST\_TRANS\_CAUSAL says that no output transactions will be produced before the first input transaction is received. Having proofs for the four theorem obligations, the justification theorem provides the desired result. The HOL listings in Appendix B contain these definitions and the proof of the justification theorem.

| <pre>'Interpreter Trans Ordering' Proof Obligations:<br/> - ∀ e' p'. TRANS_ONE_TO_ONE e' p'<br/> - ∀ e' p'. TRANS_ONTO e' p'<br/> - ∀ e' p'. FIRST_TRANS_CAUSAL e' p'<br/>where:<br/> - FIRST_TRANS_CAUSAL e' p' =<br/>∀ te'.<br/>STABLE_FALSE (Ee rep e') (0,te'-1) ⊃<br/>STABLE_FALSE (Ep rep p') (0,te'-1)</pre> | Justification Theorem:<br> - ∀ e' p'.<br>TRANS_ONE_TO_ONE e' p' ∧<br>TRANS_ONTO e' p' ∧<br>FIRST_TRANS_CAUSAL e' p' ∧<br>OUT_TRANS_LIVE e' p'<br>⊃ NEXT_OUT_TRANS_IS_NTH e' p' |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

In the tradition of Windley's generic interpreter theory, we believe that the breakdown of theorem proving tasks into two distinct classes, as shown here, has a great practical benefit in reducing the number of theorem proving tasks that must be repeated in every interpreter verification. The advantage to proving transaction ordering this way is that the justification-theorem proof could be embedded within a generic theory and then simply reused whenever a new circuit is being verified. The user of the theory would therefore not need to be concerned with constructing the proof. In general, it would be desirable to include into such a theory all of the proof infrastructure that doesn't directly involve the circuit implementation or specification. In this way, the user would only be concerned with proving facts that were specific to the particular circuit being addressed.

We are not proposing to develop a generic theory for interface-clocked interpreters in the near term, since a significant amount of basic research remains to be done; however, we believe that it is a good practice to structure theorem-proving tasks so that they could be easily incorporated into a future theory.

#### 4.2 Injective Multirate Interpreters

The monorate interpreters addressed in the last section resemble very closely the interpreters employing global clocks, in the sense that the output times and the input times were the same for each state of the machine. Of course, there is no inherent reason that an interpreter's input and output transaction events must be one-to-one and onto. When they are not, then the input and output times can be different, even for those corresponding to a common clock cycle. This possibility can seem strange unless one keeps in mind the fact that the *interface events* dictate the associated clock rates, and that these events can occur at different rates. As we shall explain in this section, the benefit that is gained by handling interpreters this way is provably secure interpreter composition. And this composition is performed at a high level of abstraction, such as the PMM transaction level.

In this section we address interpreters where the mapping between input and output transaction events is one-to-one but not onto. In other words, for every input event there are one or more output events. Figure 4.4 depicts this scenario, using a version of the simplified example used in the last section. Again, the output behavior of this interpreter, at the abstract level, is the identity function, as are the data abstractions for the input and output variables.

Figure 4.4: Example Injective Multirate Interpreter Model.

The temporal abstraction functions in this figure clearly illustrate the multirate aspect of this example interpreter. Abstract time t at the interpreter input corresponds to the concrete time t', where event Fe is true for the t'th time. Likewise, abstract time u at the output marks the concrete time that Fp is true for the u'th time. For this interpreter the relationship  $t \le u$  holds.

The interpreter behavioral model has some unfortunate complexity. Our objective at the start of this task was to employ the simpler relationship  $\forall t. \exists u. pf u = ef t$  to express interpreter behavior. However, this was not satisfactory. While it was possible to successfully verify the behavior with respect to a concrete-level implementation, using it to verify behavior higher up in the hierarchy proved to be extremely difficult. We were not able to accomplish this, due to the existential quantifier's inability to 'keep track' of the necessary relationship with the concrete-level time. More discussion on this general topic proceeds below.

The other approach that we considered was the relationship  $\forall t u. pf u = ef t$ . This also failed to work, but for the opposite reason; that is, it was too strong a statement to verify with respect to the implementation. Specifying the abstract time u for the interpreter output has thus turned out to be a fine balancing act between constraining it too much and not constraining it enough. Although somewhat ugly, the interpreter definition in Figure 4.4 achieves the proper balance.

In this interpreter definition the output expression contains the abstract time u, defined as the 'event count' corresponding to the concrete time t'. The definition of t' here is critical – it is defined as the concrete time that the input event is true for the t'th time. Thus, the t'th input event and u'th output event are related through their common concrete-level time t'.

To provide further explanation of these types of interpreters and to answer the question: "yes, but do they really exist in practice?" we now present a fairly substantial example. This example is actually a simplified version of certain ports within the PIU. It can also be seen to represent an important class of computing structures, namely shared-memory systems. All of the definitions and proofs shown here have been implemented in HOL and are contained in Appendix B.

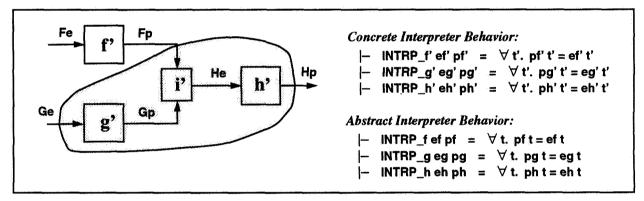

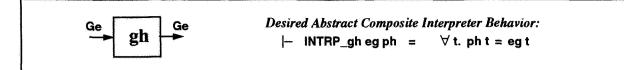

Figure 4.5 shows the example circuit. The components labeled f', g', and h' are intended to mimic certain aspects of the behavior of the PIU C-Port, P-Port, and M-Port, respectively, while i' represents the I-Bus. The individual concrete-interpreter behaviors are simply flowthrough. The i' component behavior is viewed in a highly simplified way to avoid complexity not relevant to the immediate discussion. We assume that a transaction request from either of the source components, f' or g', is passed on to the h' component. Thus, we are ignoring possible bus contention here.

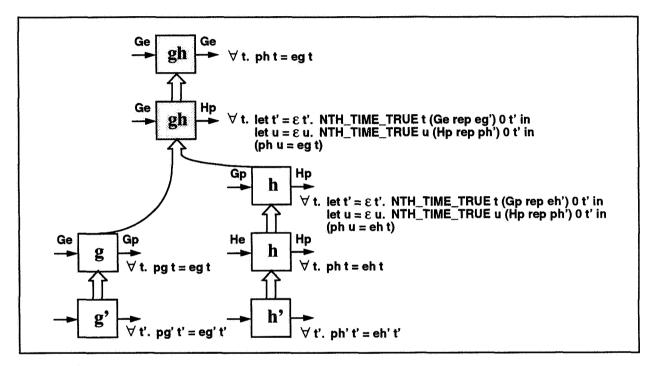

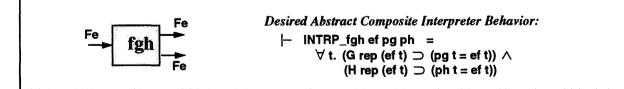

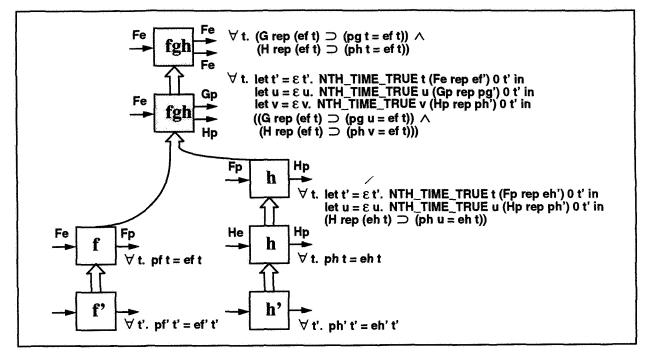

The abstract interpreter behavior is also a simple flowthrough for each of the three interpreters. In this figure, and in the following discussion, it is important to keep in mind that the abstract time variables (there) are defined over the interface events shown in the appropriate figure. For example, t within the INTRP\_f model counts the input events Fe and the output events Fp.