# Cleveland State University Department of Electrical Engineering

# A Small Terminal for Satellite Communication Systems

by

Fuqin Xiong

Dong Wu

Min Jin

Department of Electrical Engineering Cleveland State University Cleveland, Ohio 44115

submitted to

NASA Lewis Research Center

Grant NCC3-201 Final Report, May 8, 1994

# Contents

| Li | st of | Cigures Cigures                               | 3  |

|----|-------|-----------------------------------------------|----|

| Li | st of | Tables                                        | 5  |

| 1  | INT   | RODUCTION                                     | 6  |

| 2  | МО    | DEM/CODEC THEORY                              | 10 |

|    | 2.1   | MODEM Theory                                  | 10 |

|    |       | 2.1.1 BPSK (Binary Phase Shift Keying)        | 10 |

|    |       | 2.1.2 QPSK (Quadrature Phase Shift Keying)    | 12 |

|    |       | 2.1.3 OQPSK (Offset QPSK)                     | 15 |

|    |       | 2.1.4 MSK (Minimum Shift Keying)              | 16 |

|    | 2.2   | CODEC Theory                                  | 20 |

|    |       | 2.2.1 Convolutional Encoder                   | 20 |

|    |       | 2.2.2 Viterbi Decoder                         | 21 |

| 3  | SYS   | rem design                                    | 23 |

| _  | 3.1   | System Specifications                         | 23 |

|    | 3.2   | System Interfaces                             | 24 |

|    | 3.3   | IF Frequency                                  | 25 |

|    | 3.4   | System Structure                              | 26 |

| 4  | TR.   | NSMITTER DESIGN                               | 29 |

| -  | 4.1   | Modulator Design                              | 29 |

|    |       | 4.1.1 Q2334 Direct Digital Synthesizer        | 30 |

|    |       | 4.1.2 Modulator Design                        | 33 |

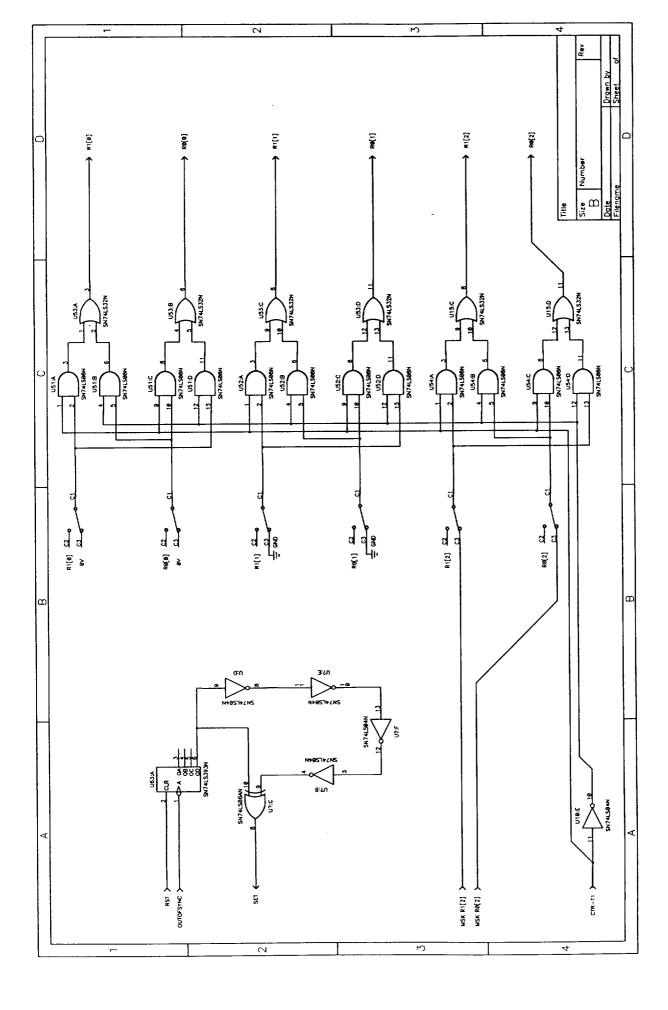

|    | 4.2   | Encoder/Decoder Design                        | 38 |

|    |       | 4.2.1 Parallel and Serial Data Modes          | 39 |

|    |       | 4.2.2 Synchronization Status Monitor Design   | 40 |

|    |       | 4.2.3 Monitoring Channel Bit Error Rate (BER) | 42 |

|    |       | 4.2.4 The Other Considerations                | 43 |

|    | 13    | D / A Converter                               | 43 |

|    | 4.4   | Lowpass Filter                                    | 45  |

|----|-------|---------------------------------------------------|-----|

| 5  | REG   | CEIVER DESIGN                                     | 48  |

|    | 5.1   | IF Amplifier and Bandpass Filter                  | 48  |

|    | 5.2   | Multiplier, LPF and Amplifier                     | 49  |

|    |       | 5.2.1 Multiplier                                  | 50  |

|    |       | 5.2.2 LPF and Amplifier                           | 52  |

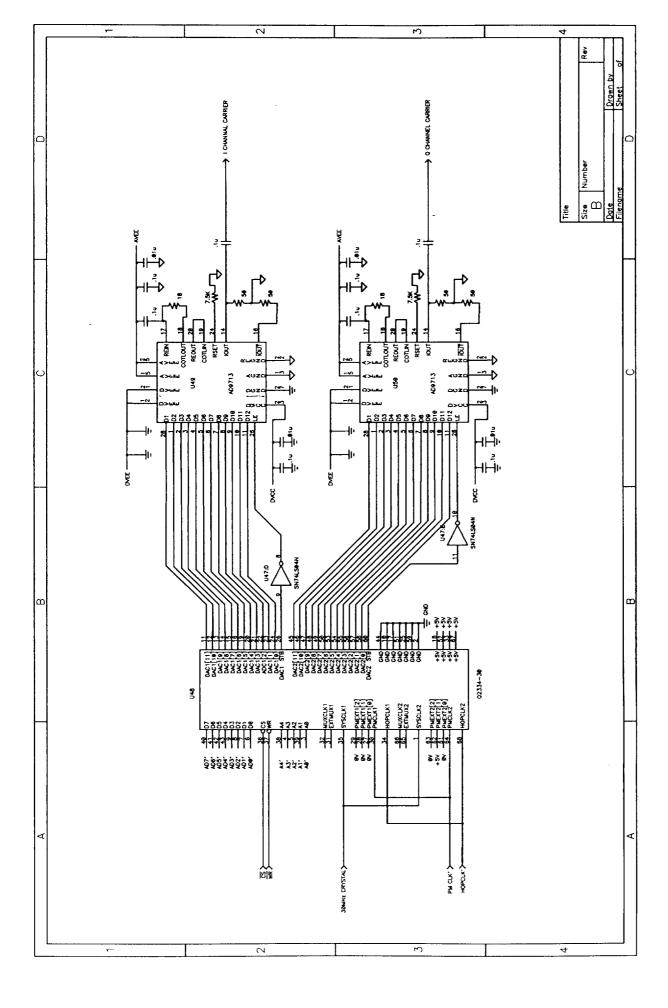

|    | 5.3   | Analog to Digital Converter                       | 52  |

|    | 5.4   | STEL-2110                                         | 54  |

|    |       | 5.4.1 STEL-2110 Bit Synchronizer/PSK Demodulator  | 54  |

|    |       | 5.4.2 Design with STEL-2110                       | 56  |

|    | 5.5   | Carrier Recovery Circuit for QPSK, OQPSK and BPSK | 62  |

|    |       | 5.5.1 Digital Phase Lock Loop                     | 62  |

|    | 5.6   | Msk Demodulator                                   | 64  |

| 6  | CO    | NTROL CIRCUITS DESIGN                             | 68  |

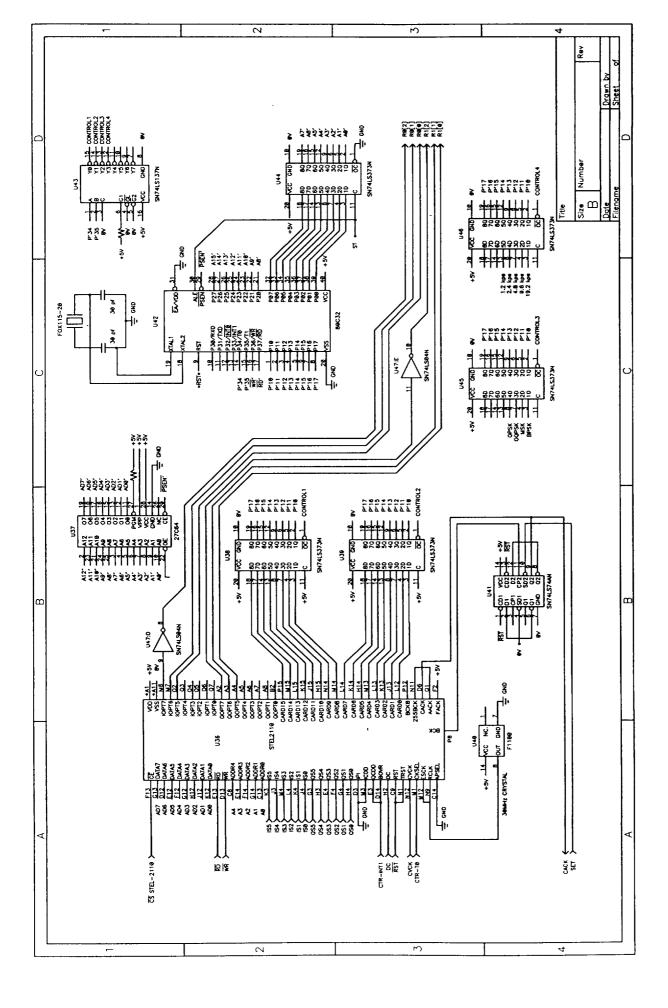

|    | 6.1   | Intel 80C32 Microcontroller                       | 68  |

|    | 6.2   | Variable Bit Rate Control                         | 70  |

|    | 6.3   | Configuration and Control                         | 71  |

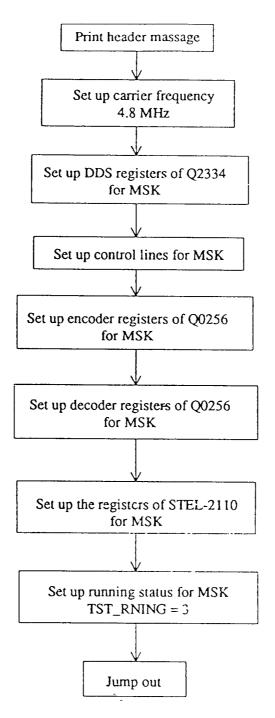

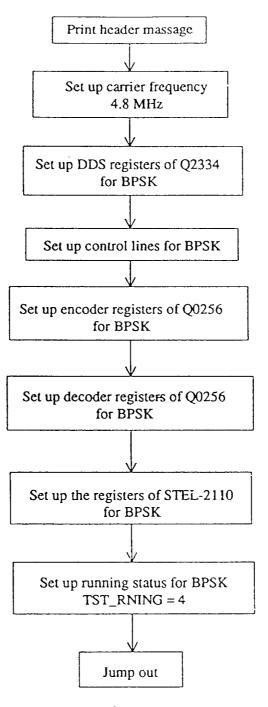

|    |       | 6.3.1 BPSK                                        | 71  |

|    |       | 6.3.2 QPSK and OQPSK                              | 73  |

|    |       | 6.3.3 MSK                                         | 74  |

|    | 6.4   | Control Software                                  | 74  |

| 7  | TES   | ST RESULTS                                        | 82  |

| Bi | bliog | graphy                                            | 93  |

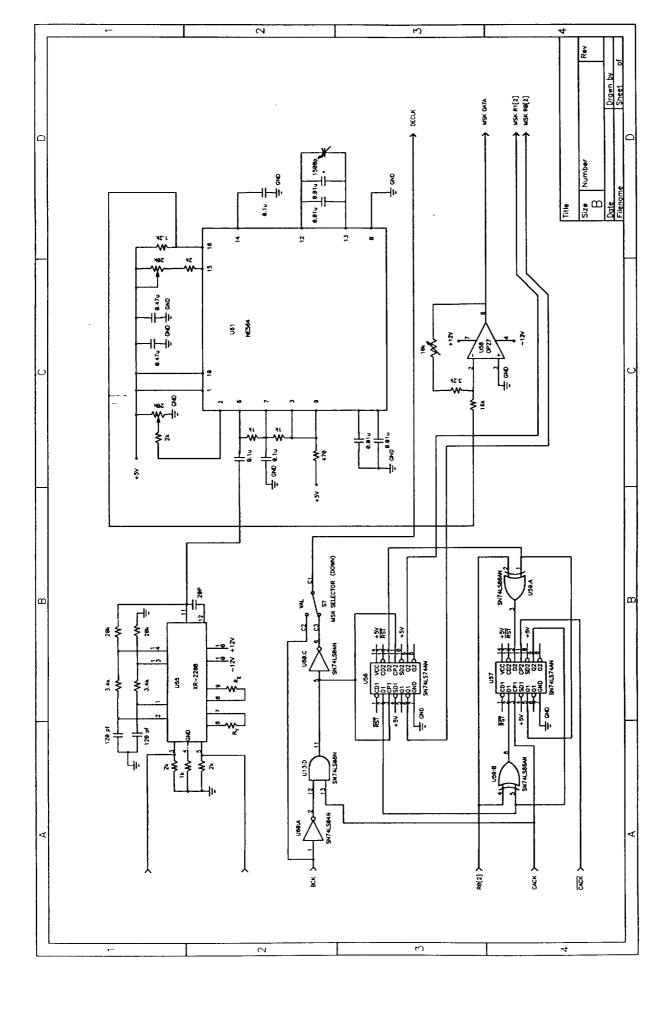

| A  | The   | e Design Circuits                                 | 96  |

| В  | The   | e Firmware (Software) Listing                     | 105 |

# List of Figures

| 2.1  | Generalized quadrature modulator                                   | 11        |

|------|--------------------------------------------------------------------|-----------|

| 2.2  | Generalized quadrature demodulator                                 | 12        |

| 2.3  | (a) input data stream, (b) QPSK data stream,                       | 14        |

| 2.4  | (a) QPSK and (b) OQPSK waveforms                                   | 15        |

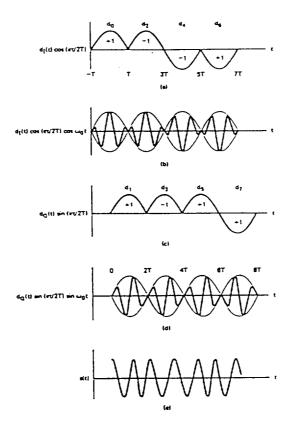

| 2.5  | MSK waveforms                                                      | 17        |

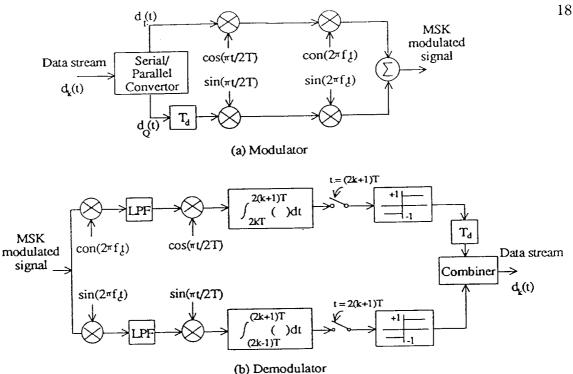

| 2.6  | Block diagrams of MSK (a) modulator, (b) demodulator               | 18        |

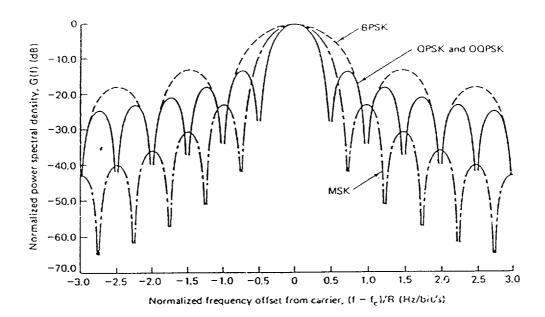

| 2.7  | Normalized power spectral densities for BPSK, QPSK, OQPSK and MSK. | 19        |

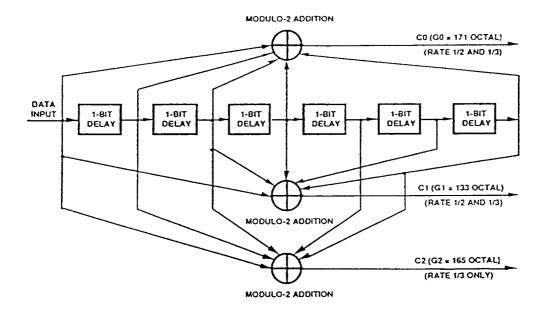

| 2.8  | Constraint length seven (k=7) convolutional encoder                | 21        |

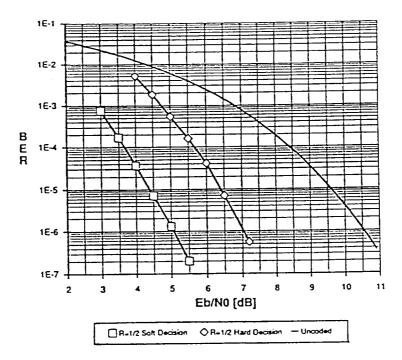

| 2.9  | Q0256 coding performance                                           | 22        |

| 3.1  | System interfaces                                                  | 25        |

| 3.2  | System structures                                                  | 28        |

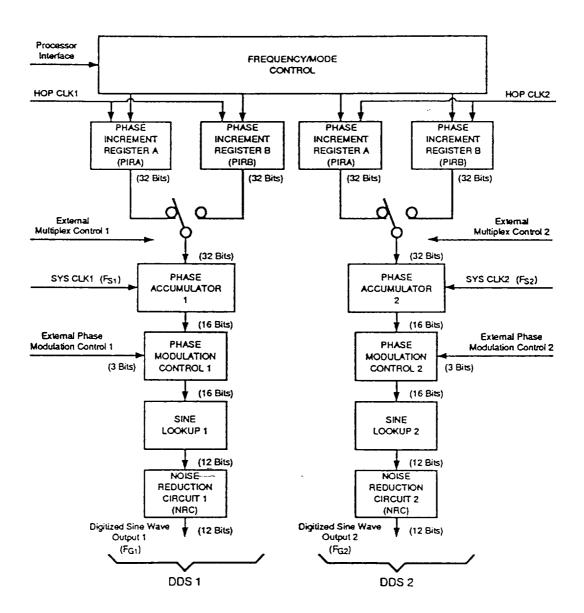

| 4.1  | Q2334 DDS blok diagram                                             | 31        |

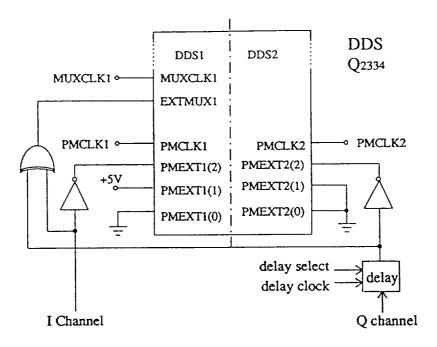

| 4.2  | The modulator circuit for BPSK, QPSK, OQPSK and MSK                | 34        |

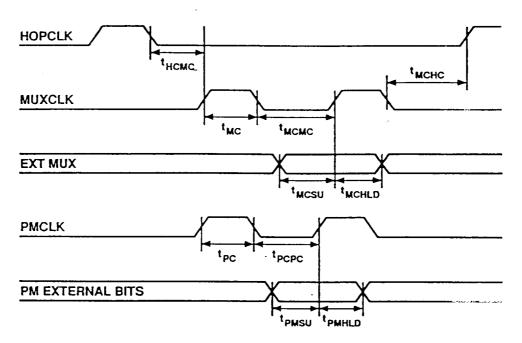

| 4.3  | External control timing                                            | <b>35</b> |

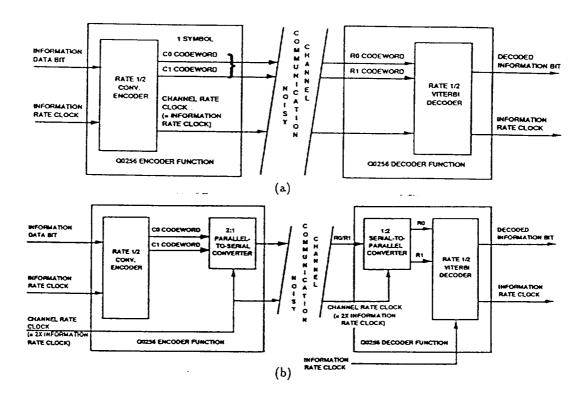

| 4.4  | (a). Parallel data mode, (b). Serial data mode                     | 39        |

| 4.5  | D / A converter circuit                                            | 44        |

| 4.6  | Power supply                                                       | 45        |

| 4.7  | (a) lowpass filter circuit, (b) frequency response                 | 47        |

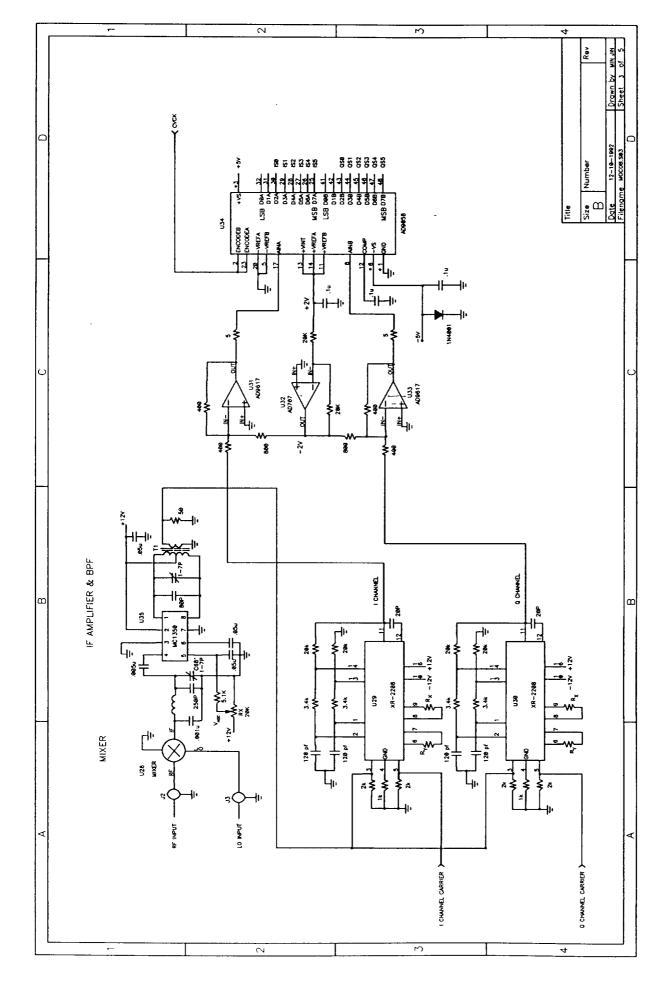

| 5.1  | IF amplifer and BPF                                                | 49        |

| 5.2  | The frequency response curve of the IF amplifier and BPF           | 50        |

| 5.3  | Multiplier, LPF and amplifier                                      | <b>50</b> |

| 5.4  | The equivalent circuit for LPF and amplifier                       | 52        |

| 5.5  | The analog to digital converter                                    | 53        |

| 5.6  | Block diagram of the STEL-2110                                     | 54        |

| 5.7  | Block diagram of the bit timing feedback loop system               | 58        |

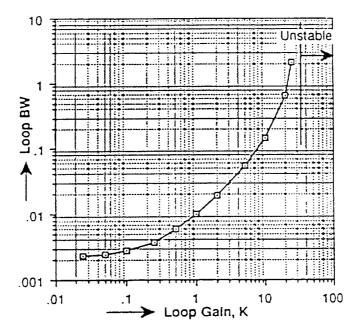

| 5.8  | The performance related with loop gain and bandwidth               | 59        |

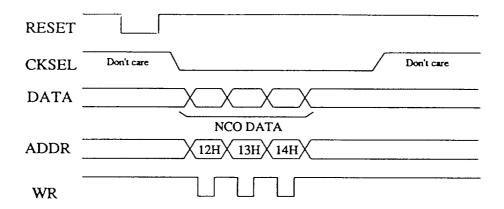

| 5.9  | Start up the chip STEL-2110                                        | 61        |

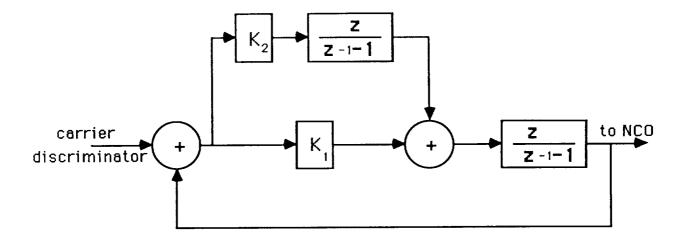

| 5.10 | Digital Phase Lock Loop                                            | 63        |

| 5.11 | MSK modulation scheme                                              | 64        |

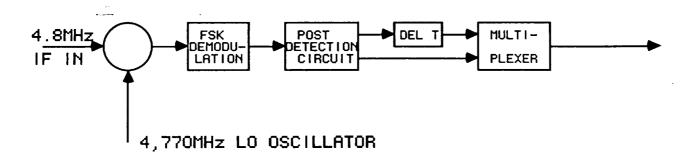

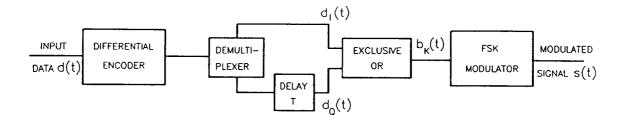

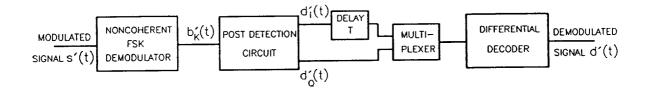

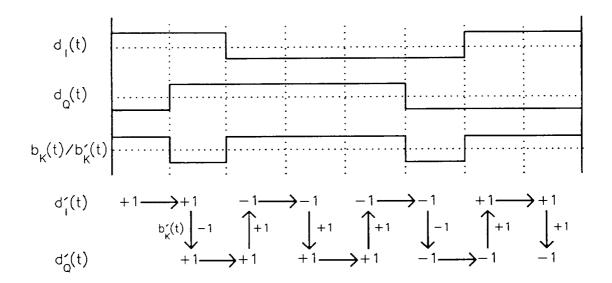

| 5.12 | MSK demodulation scheme                              |   |   |   |   |   |   | 65 |

|------|------------------------------------------------------|---|---|---|---|---|---|----|

| 5.13 | An example showing MSK baseband waveforms relations. |   |   |   |   |   |   | 65 |

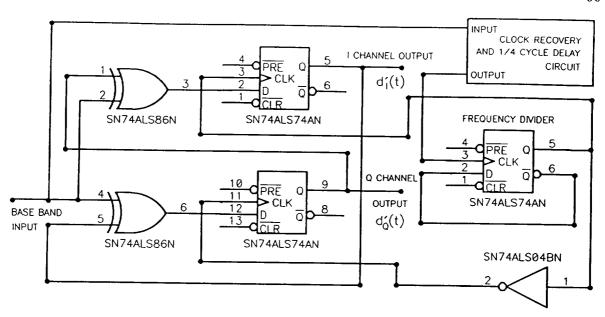

| 5.14 | MSK post-detection circuit                           | • | • | • | • | • | • | 66 |

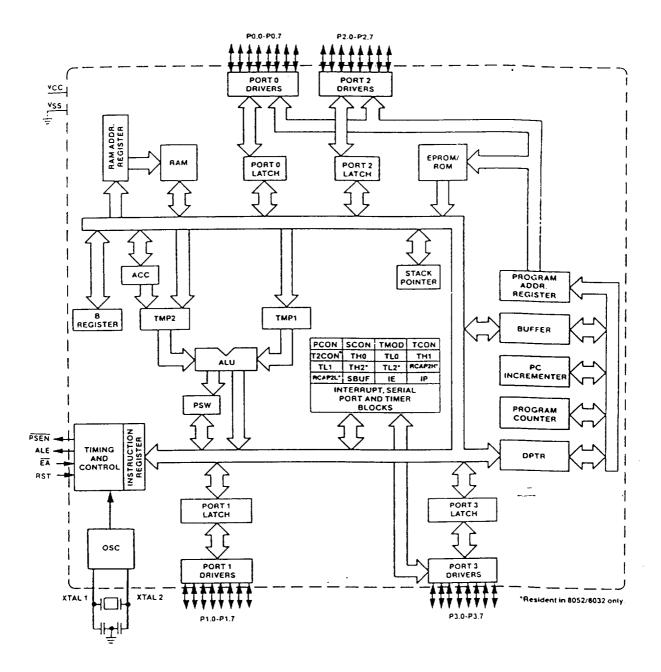

| 6.1  | Intel 80C32 architectural block diagram              |   |   |   |   |   |   | 69 |

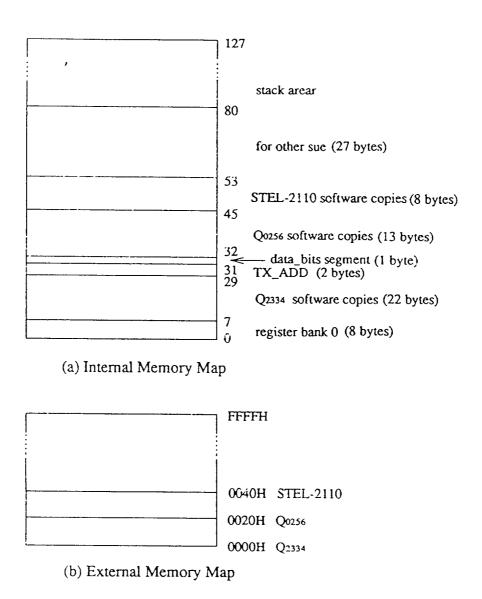

|      | (a) Internal memory map, (b) External memory map     |   |   |   |   |   |   |    |

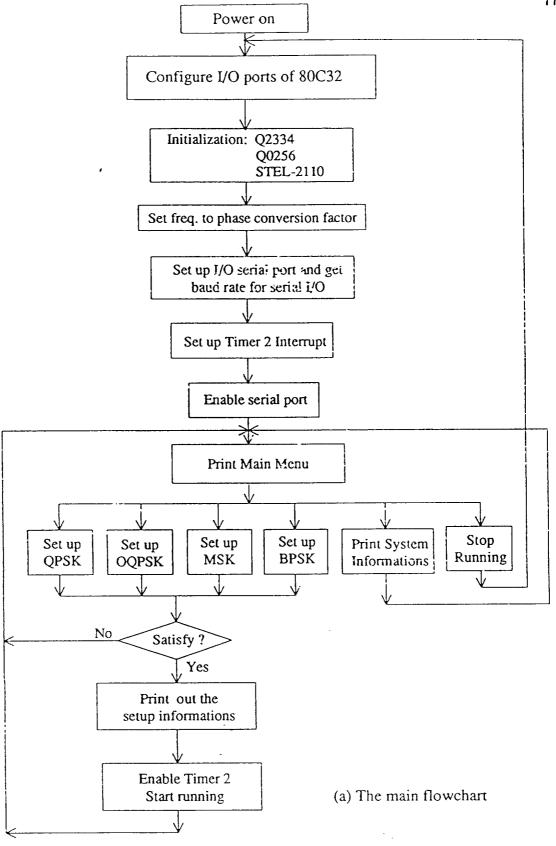

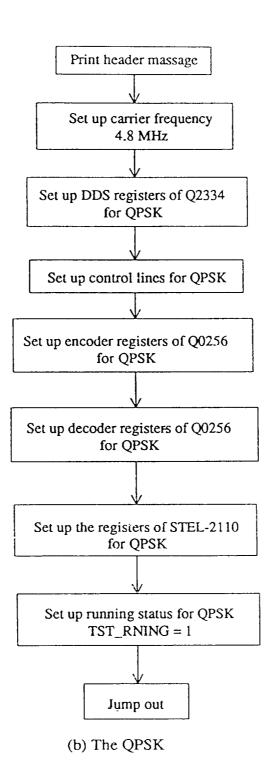

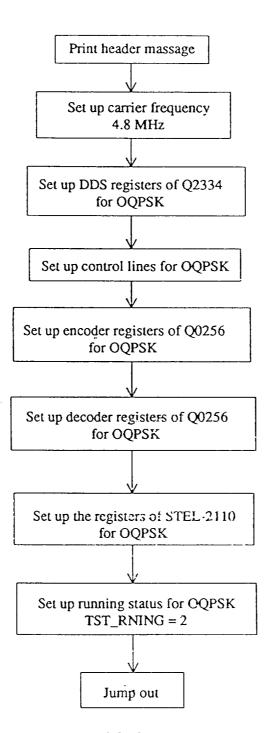

|      | Flowchart                                            |   |   |   |   |   |   |    |

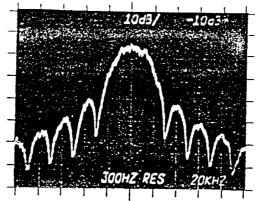

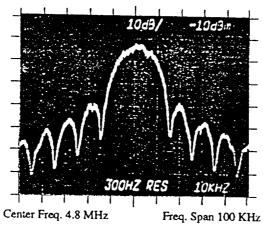

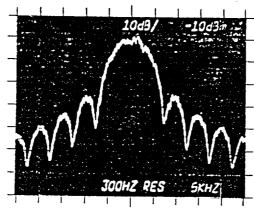

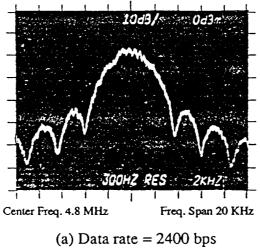

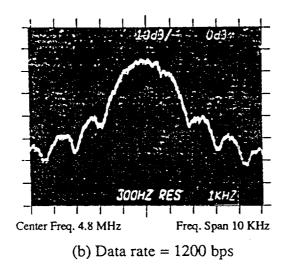

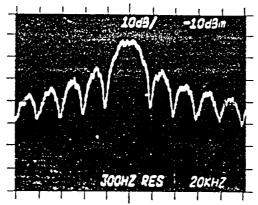

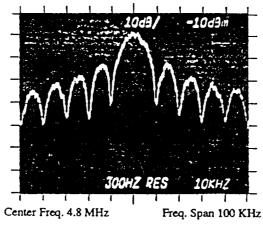

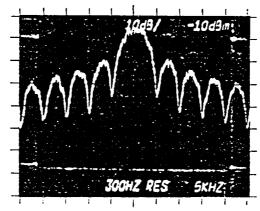

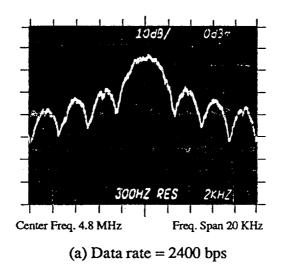

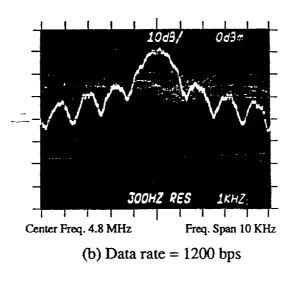

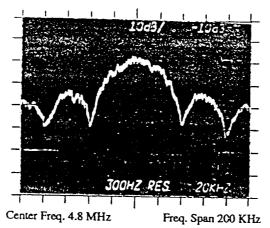

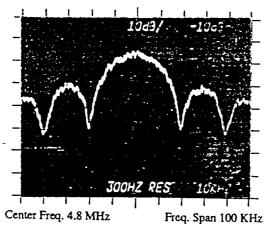

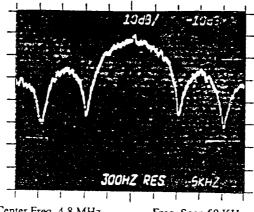

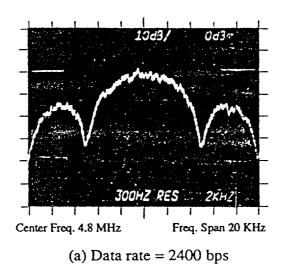

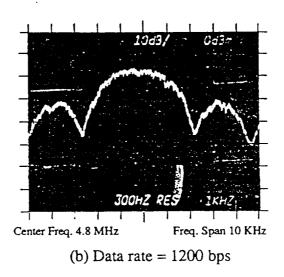

| 7.1  | Power spectral densities of MSK                      |   |   |   |   |   |   | 88 |

|      | Power spectral densities of QPSK and OQPSK           |   |   |   |   |   |   |    |

|      | Power spectral densities of BPSK                     |   |   |   |   |   |   |    |

|      |                                                      |   |   |   |   |   |   |    |

.

# List of Tables

|     | Q2334 interface register address map                 |    |

|-----|------------------------------------------------------|----|

| 5.1 | The loop bandwidth with K1 and K2                    | 59 |

| 5.2 | (a) The control factor K1, (b) The control factor K2 | 60 |

# Chapter 1

# INTRODUCTION

This is a final report for the design activities supported by the NASA grant NCC3-201. The goal of this project is to design and develop a small portable terminal system for satellite communications. A multi-scheme, multi-rate modulator/demodulator (MODEM) and a convolutional-Viterbi coder/decoder (CODEC) are the main parts of this system.

Recent technological improvements are leading towards low-cost satellite communication systems that can be applied to rural communications worldwide[1][2]. Advance in signal processing and error-correction techniques allow more efficient use of the space segment by locating the sophisticated processing equipment on board the satellite[3][14]. Combined with the trend of higher power and higher frequency satellites this results in simple and inexpensive ground terminal architecture, making VSAT technology more attractive. The Advanced Communications Technology Satellite (ACTS) is certainly no exception to this general trend.

ACTS operating at Ka band incorporates most of these technological advances, Namely, higher power, higher frequency, frequency and spatial reuse using spot beams and polarization. These capabilities and facts the ACST uses beam hopping makes the development of small portable terminals very attractive to service to low population density areas, remote locations, as well as the areas where traffic is

spread geographically. Further, the efficiency and flexibility of a beam-hopping satellite system serving small and economical earth stations would also benefit developing nations.

This project is a part of designing and realizing this kind of small and economical earth stations. The research activities involved in this project include:

- (1). Design of a programmable Modulator/Demodulator which can provide multiple bit rates, multiple modulation and demodulation schemes.

- (2). Design of a code rate 1/2, constaint length 7 Convolutional coder/Viterbi decoder which can provide a low cost, high performance solution for FEC (Forward Error Correction) system requirement.

- (3). Design of a control system for this small terminal system with one microcontroller. It can write the control code into the internal registers of the VLSI chips for proper system configuration and control. Also several required clocks are produced using this microcontroller. Another microcontroller is used to realize digital Phase Lock Loop (PLL) for carrier recovery for QPSK, OQPSK, and BPSK.

- (4). Translation of this design into a prototype which was built using wire wrapping method.

- (5). Debugging and trouble-shooting both hardware and software of this prototype system.

- (6). Testing the transmitter and the receiver.

The MODEM can provide four kinds of modulation schemes: BPSK, QPSK, OQPSK, and MSK. Direct Digital Synthesizer (DDS) is used to generate modulation signals. Bit synchronizer/PSK demodulator (STEL-2110A) and digital Phase Lock Loop (PLL) are used to provide clock and carrier synchronization for BPSK, QPSK and OQPSK. A new type of low cost, easily realized MSK demodulator is presented for MSK demodulation. Five kinds of low bit rates ranging frcm 1,200 bps to 19,200 bps are employed in each kind of modulation scheme. Four different modulation schemes and five different bit rates provides us twenty different communication mode combinations. That which combination is well suited for low bit rate satellite communications will be tested through field experiments using ACTS launched by NASA in October, 1993. This is also the final purpose of this project.

The QUALCOMM Q0256 convolutional coder/Viterbi decoder VLSI chip is selected to provide low bit rate, high volume communications. Rate 1/2 and constraint length 7 convolutional coding scheme is selected. 3-bit soft-decision encoder data greatly improve the BER performance of the whole system. Only about 5.2 dB  $E_b/N_0$  is required for 1E-6 BER performance.

Two 80C32 microcontrollers in the INTEL MCS-51 family are used in the control system and the digital PLL. Over 2,500 lines software are developed for the proper system operation, control and digital PLL calculation. An ICE-51FX emulator is used for the software developing. Selections of modulation schemes and bit rates can be done easily by switches. The control system also provides a master clock to the vocoder - the stage before the MODEM and CODEC.

Most of the system has been successfully built according to the system design requirements. The measured power spectral densities of modulated signals, BPSK, QPSK, OQPSK and MSK, under five different data rates agreed with the theoretical predictions very well. 0 BER performance was realized when signals passed through an idea channel. Realizing carrier synchronization for BPSK, QPSK and OQPSK in low bit rate situation and finding an MSK demodulation scheme suitable for low cost, small terminal are the key points in the system design and realization. Having successfully solved these problems with innovation offers several unique features to this system.

There are also some problems left. The system is not working at bit rate of 19.2 kbps for BPSK because the microcontroller which we employ doesn't have the function to generate 50% duty cycle clock. Thus, in our design, we generate a double frequency clock, then let it pass through a frequency divider to generate the required frequency 50% clock. For 19.2 kbps, we have to generate a 76.8 kbps clock for BPSK encoder use, but it is not possible for microcontroller 80C32. We can use a microcontroller which can directly generate 50% duty cycle clock or a microcontroller which can generate a 76.8 kbps clock to solve this problem. This is not a big problem.

Another problem is with MSK demodulation, only 2.4 kbps and 4.8 kbps bit rate can be successfully demodulated, but they are not robust enough. The key point here is to find or built a noncoherent robust FSK demodulator. NE564 which

we used in our system is what we can find to most suit for our system, but it still can not give us satisfactory results.

Overall, we have meet many problem in our system realization and we have solve most of them. For QPSK, OQPSK and BPSK, the MODEM/CODEC can successfully operate at bit rate 1.2 kbps, 2.4 kbps, 4.8 kbps and 9.6 kbps. For MSK, transmitter is well working. there is a problem with the demodulator under some bit rates.

# Chapter 2

# MODEM/CODEC THEORY

### 2.1 MODEM Theory

For satellite communication, due to the nonlinear amplification of the TWTA and limited bandwidth allocation, the most efficient MODEM technique is the PSK with coherent detection. It has the desirable characteristic that the transmitted signal has a constant envelope with the information in the carrier phase transitions. Thus it is the least susceptible to the nonlinear amplification. It also has a higher bandwidth efficiency than the FSK even though the FSK is a constant envelope modulation too.

BPSK (Binary Phase Shift Keying), QPSK (Quadrature Phase Shift Keying) and OQPSK (Offset QPSK) are most often used PSK variations for satellite modems. [4]-[8]. MSK (Minimum Shift Keying), which can be considered as an OQPSK with sinusoidal pulse shaping, was developed in recent years [9][11][12].

#### 2.1.1 BPSK (Binary Phase Shift Keying)

BPSK is a binary signaling scheme where the phase of the carrier changes between two values separated by 180° with each new binary digit. Hence, two signals  $s_1(t)$  and  $s_2(t)$  are employed to represent the binary digits 1 and 0, as follows

$$s_1(t) = A\cos(2\pi f_c t + \theta)$$

,  $(k-1)T < t < kT$  (2.1)

$$s_2(t) = A\cos(2\pi f_c t + \theta + \pi) = -A\cos(2\pi f_c t + \theta)$$

,  $(k-1)T < t < kT$  (2.2)

or simply as

$$s(t) = d_k(t)A\cos(2\pi f_c t + \theta) \tag{2.3}$$

where  $f_c$  is the carrier frequency,  $\theta$  is the initial phase of the carrier, A is the carrier amplitude, T is the bit duration, and  $d_k(t)$  is the binary data stream,  $d_k(t) = \{d_{0,}d_{1}, d_{2}, \dots \}$ , consisting of bipolar pulses; that is, the values of  $d_k$  are +1 or -1, representing binary one and zero, respectively. The power spectral density of BPSK is shown in Figure 2.7.

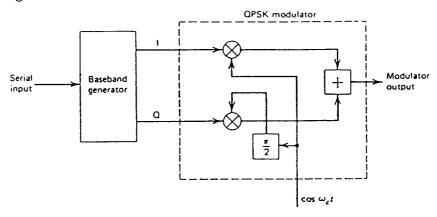

Figure 2.1: Generalized quadrature modulator.

Figure 2.1 shows the generalized quadrature modulator which is applicable for BPSK, QPSK and OQPSK. For BPSK the baseband generator is not needed, and only the upper half of the modulator is required.

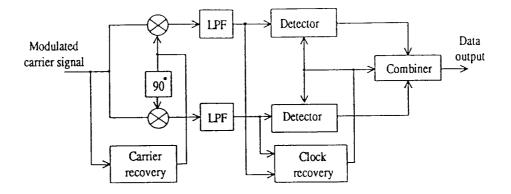

Figure 2.2 shows the generalized quadrature demodulator which is applicable for BPSK, QPSK and OQPSK. BPSK does not need the lower half of the circuit and combiner. The input signal is  $d_k(t)A\cos 2\pi f_c t$ . The carrier recovery circuit detects and regenerates a carrier signal that is both frequency and phase coherent with the original transmit carrier. The output of the mixer is the product of the two inputs (the BPSK signal and the recovered carrier). The low-pass filter (LPF) separates the recovered binary data from the complex demodulated spectrum. The demodulation process is as follows:

Figure 2.2: Generalized quadrature demodulator.

$$Multiplier output = [d_k(t)A\cos 2\pi f_c t](\cos 2\pi f_c t)$$

$$= \frac{A}{2}d_k(t) + \frac{A}{2}d_k(t)\cos 2(2\pi f_c)t$$

(2.4)

After low-pass filter, the second component is filtered out. So we obtain

$$Data\ output = \frac{A}{2}d_k(t)$$

which is proportional to the original data stream we have transmitted.

### 2.1.2 QPSK (Quadrature Phase Shift Keying)

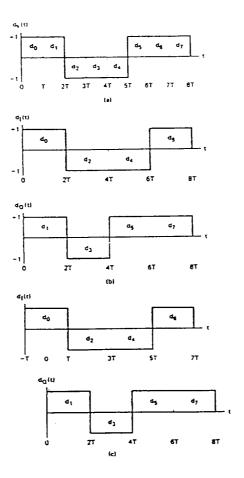

QPSK is an M-ary encoding technique where M=4. Figure 2.3 illustrates the partitioning of a typical data stream for QPSK. Figure 2.3(a) shows the original data stream  $d_k(t) = \{d_0, d_1, d_2, d_3, \dots \}$  consisting of bipolar pulses. This data stream is divided into two bit streams: (1) the in-phase stream  $d_I(t)$  for I channel, (2) the quadrature stream  $d_Q(t)$  for Q channel. This is illustrated in Figure 2.3(b).

$$d_I(t) = \{d_0, d_2, d_4, \dots \}$$

(even)

$$d_Q(t) = \{d_1, d_3, d_5, \dots \}$$

(odd)

Note that  $d_I(t)$  and  $d_Q(t)$  have half the bit rate of  $d_k(t)$ . A convenient orthogonal realization of a QPSK waveform, s(t), is achieved by modulating the in-phase and quadrature data streams onto a cosine and a sine carriers, as follows:

$$s(t) = \frac{A}{\sqrt{2}} d_I(t) \cos 2\pi f_c t + \frac{A}{\sqrt{2}} d_Q(t) \sin 2\pi f_c t$$

(2.6)

Using the trigonometric identities, Equation (2.6) can also be written as

$$s(t) = A\cos\left[2\pi f_c t + \theta(t)\right] \tag{2.7}$$

The value of  $\theta(t)$  will correspond to one of the four possible combinations of  $d_I(t)$  and  $d_Q(t)$  in Equation (2.6). These values are:  $\theta(t) = \pm 45^{\circ}$ , or  $\pm 135^{\circ}$ .

The power spectral density for QPSK is given by [4]

$$G(f) = 2PT \left(\frac{\sin 2\pi fT}{2\pi fT}\right)^2, \tag{2.8}$$

where P is the average power in the modulated waveform, as shown in Figure 2.7.

The block diagram of a QPSK modulator is shown in the Figure 2.1. The baseband generator is a serial to parallel converter that is used to split data stream  $d_k(t)$  into  $d_I(t)$  and  $d_Q(t)$ . The in-phase stream  $d_I(t)$  modulates the cosine function. This produces a BPSK waveform. Similarly, the quadrature stream  $d_Q(t)$  modulates the sine function, yielding a BPSK waveform orthogonal to the cosine function. The summation of these two orthogonal components of the carrier yields the QPSK waveform.

The block diagram of a QPSK receiver is shown in Figure 2.2. The input signal is directed to the I channel, Q channel and the carrier recovery circuit. The detector here is a integrate-dump circuit (or Matched filter). The QPSK signal is demodulated in the I and Q channels, which generate the original I and Q data streams.

The incoming QPSK signal can be seen from Equation (2.6) as

$$s(t) = Ad_I(t)\cos 2\pi f_c t + Ad_Q(t)\sin 2\pi f_c t \tag{2.9}$$

For I channel, recovered carrier is  $\cos 2\pi f_c t$ , so the output of I channel is

$$I_{out} = [Ad_I(t)\cos 2\pi f_c t + Ad_Q(t)\sin 2\pi f_c t]\cos 2\pi f_c t$$

=  $\frac{A}{2}d_I(t) + \frac{A}{2}d_I(t)\cos 2(2\pi f_c)t + \frac{A}{2}d_Q(t)\sin 2(2\pi f_c)t$  (2.10)

after LPF, second and third components are filtered out. So

$$I_{out} = \frac{A}{2}d_I(t).$$

Figure 2.3: (a) input data stream, (b) QPSK data stream, (c) OQPSK data stream.

For Q channel, recovered carrier is  $\sin 2\pi f_c t$ , so the output of Q channel is

$$Q_{out} = [Ad_I(t)\cos 2\pi f_c t + Ad_Q(t)\sin 2\pi f_c t]\sin 2\pi f_c t$$

$$= \frac{A}{2}d_I(t)\sin 2(2\pi f_c)t + \frac{A}{2}d_Q(t) - \frac{A}{2}d_Q(t)\cos 2(2\pi f_c)t$$

(2.11)

after LPF, first and third components are filtered out. So

$$Q_{out} = \frac{A}{2} d_Q(t).$$

The output of I and Q channels are fed to the bit combining circuit, where they are converted from parallel I and Q data channels to a single binary output data stream  $d_K(t)$ .

#### 2.1.3 OQPSK (Offset QPSK)

OQPSk signaling can also be represented by Equations (2.6) or (2.7); the difference between the two modulation schemes, QPSK and OQPSK, is only in the alignment of the two baseband waveforms. In QPSK, the odd and even pulse streams are both synchronously aligned. In OQPSK, there is the same data stream partitioning and orthogonal transmission; the difference is that the timing of the pulse stream  $d_I(t)$  and  $d_Q(t)$  is shifted such that the alignment of the two streams is offset by T. Figure 2.3(c) illustrates this offset.

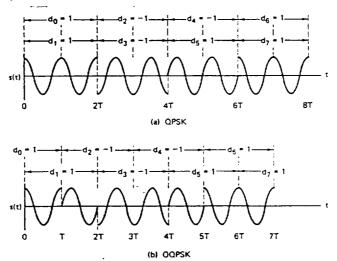

In QPSK, due to the alignment of  $d_I(t)$  and  $d_Q(t)$ , the phase change of the carrier during any 2T interval can be any one of the four phases 0°,  $\pm 90$ ° and 180°. Figure 2.4(a) shows a typical QPSK waveform for the sample sequence  $d_I(t)$  and  $d_Q(t)$  shown in Figure 2.3(b).

If a QPSK modulated signal undergoes filtering to reduce the spectral sidelobes, the resulting waveform will not longer have a constant envelope and in fact the occasional 180° phase shifts will cause the envelope to go to zero momentarily. When these signals are used in satellite channels employing highly nonlinear amplifiers, the constant envelope will tend to be restored. However, at the same time, all of the undesirable frequency side-lobes, which can interfere with nearby channels and other communication systems, are also restored.

Figure 2.4: (a) QPSK and (b) OQPSK waveforms.

In OQPSK, the pulse streams  $d_I(t)$  and  $d_Q(t)$  are staggered and thus do not change states simultaneously. The possibility of the carrier changing phase by 180° is eliminated, since only one component can make a transition at one time. Changes are limited to 0 and  $\pm 90^{\circ}$  every T seconds. Figure 2.4(b) shows a typical OQPSK waveform for the sample sequence in Figure 2.3(c). When an OQPSK signal undergoes bandlimiting, the resulting intersymbol interference causes the envelope to droop slightly in the region of  $\pm 90^{\circ}$  phase transition, but since the phase transitions of 180° have been avoided in OQPSK, the envelope will not go to zero as it does with QPSK.

OQPSK can be used the same block diagram of Figure 2.1 and Figure 2.2 to be accomplished. The baseband generator of Figure 2.1 consists of a serial to parallel converter followed by a Q channel delay of T, and a delay of T in Figure 2.2 is needed after the detector in the I channel. Furthermore, the power spectral density of OQPSK is identical to that of QPSK.

### 2.1.4 MSK (Minimum Shift Keying)

MSK can be though of as a special case of OQPSK with sinusoidal pulse weighting [9][11][12]. Consider the OQPSK signal, with the bit streams offset as shown in Figure 2.3(c). If sinusoidal pulses are employed instead of rectangular shapes, the modified signal can be defined as MSK and equals

$$s(t) = d_I(t)\cos(\frac{\pi t}{2T})\cos 2\pi f_c t + d_Q(t)\sin(\frac{\pi t}{2T})\sin 2\pi f_c t \qquad (2.12)$$

Figure 2.5 shows the various components of the MSK signal defined by Equation (2.12). The waveform in Figure 2.5(e) can be better understood if we use a trigonometric identity to rewrite Equation (2.12) as

$$s(t) = \cos(2\pi f_c t + b_k(t) \frac{\pi t}{2T} + \phi_k)$$

(2.13)

where

$$b_k(t) = -d_I(t)d_Q(t)$$

(2.14)

and  $\phi_k$  is the initial phase.

Figure 2.5: MSK waveforms.

From Figure 2.5 and Equation (2.13), we deduce the following properties of MSK:

- (1) the waveform s(t) has constant envelope;

- (2) there is phase continuity in the RF carrier at the bit transitions;

- (3) the waveform s(t) can be regarded as an FSK waveform with signaling frequencies:

$$f_{c+} = f_c + \frac{1}{4T}$$

;  $f_{c-} = f_c - \frac{1}{4T}$

Therefore, the minimum tone separation requires for MSK modulation is

$$\Delta f = f_{c+} - f_{c-} = \frac{1}{2T} \tag{2.15}$$

which is equal to half the bit rate. Notice that the required tone spacing for MSK is one-half the spacing,  $\frac{1}{T}$ , required for the noncoherent detection of FSK signals.

The modulation and demodulation block diagrams are shown in Figure 2.6. In modulation, the serial data stream  $d_k(t)$  is converted into its even and odd bit

Figure 2.6: Block diagrams of MSK (a) modulator, (b) demodulator.

streams,  $d_I(t)$  and  $d_Q(t)$ , which are staggered  $\frac{1}{2}$  symbol. Each symbol of  $d_I(t)$  and  $d_{Q}(t)$  is then weighted by a sinusoid signal. If the symbol weighting function  $\cos(\frac{\pi t}{2T})$ and  $\sin(\frac{\pi t}{2T})$  are replaced by rectangular shaping functions, MSK becomes Offset QPSK. Without staggered by ½ symbol and sinusoidal weighting, QPSK results.

Because MSK is a quadrature-multiplexed modulation scheme, it can be optimally detected by coherently demodulating its in-phase and quadrature components separately, as shown in Figure 2.6(b).

The power spectral density G(f) for MSK is given by [4]

$$G(f) = \frac{16PT}{\pi^2} \left( \frac{\cos 2\pi fT}{1 - 16f^2 T^2} \right)^2 \tag{2.16}$$

and shown in Figure 2.7.

The normalized power spectral density (P=1W) for BPSK, QPSK, OQPSK and MSK are sketched in Figure 2.7[10]. The one which has wider main-lobe has less bandwidth efficiency. The one which has higher side-lobes is more susceptible to nonlinearity. Even though QPSK and OQPSK have same power spectral density, OQPSK

Figure 2.7: Normalized power spectral densities for BPSK, QPSK, OQPSK and MSK.

has better immunity to nonlinearity since it does not have 180° phase transitions like QPSK does.

It is seen from Figure 2.7 that the main-lobe bandwidth (null-to-null bandwidth) of these modulations are different (T is the bit duration):

For BPSK,  $BW_{BPSK} = 2.0/T$ For MSK,  $BW_{MSK} = 1.5/T$ For QPSK and OQPSK,  $BW_{QPSK,OQPSK} = \overline{1.0/T}$

As we can see, the BPSK has poorest bandwidth efficiency and immunity. The MSK has lower side-lobes than QPSK or OQPSK. This is a consequence of multiplying the data stream with a sinusoid, yielding more gradual phase transitions. The more gradual the transition, the faster the spectral tails drop to zero. MSK has the best immunity, moderate bandwidth efficiency.

All of them have almost the same bit error rate ( $P_b$  or BER) at same signal to noise ratio. That is, for coherent detection[4],

$$P_b = Q\left[\sqrt{\frac{2E_b}{N_0}}\right] \tag{2.17}$$

where  $Q(x) = \frac{1}{\sqrt{2\pi}} \int_x^{\infty} e^{-y^2/2} dy$ ,  $E_b$  is the bit energy, and  $\frac{N_0}{2}$  is the double-sided noise

power spectral density at the receiver input.

### 2.2 CODEC Theory

#### 2.2.1 Convolutional Encoder

Convolutional codes have been studied and used for forward error correction (FEC) in digital communication systems since the 1950's. A convolutional code maps a number (n) of information bits into a number (m) of single-bit codewords to be transmitted over the channel, where m>n. The ratio of n/m is referred to the code rate.

The transformation from information bits to codewords for transmission is accomplished by a time convolution of the information data with a finite-memory windowing function commonly referred to as a generating function. In the case of the rate 1/2 code, two generating functions G0 and G1 are convolved with the information data stream such that each time a new information data bit is considered, the G0 and G1 generating functions create one output bit or codeword, respectively.

The length of the finite memory of the convolutional generating function is the constraint length of the code. Figure 2.8 shows the generating functions of the rate 1/2 and 1/3 codes implemented by the Q0256 convolutional encoder. As the diagram shows, the memory length of the encoder is that six previous bits plus the current input bit; thus, this is a constraint length seven code, commonly denoted as k=7. The generating functions of the convolutional code are identified by denoting the "taps" of each convoluting function. For the rate 1/2, k=7 code shown in Figure 2.8, the generating functions are denoted as

$$G0 = 1111001$$

(binary) or  $G0 = 171$  (octal)

and

$$G1 = 1011011$$

(binary) or  $G1 = 133$  (octal)

This code provides the best error correcting performance of all rate 1/2, k=7 codes[13][17].

Figure 2.8: Constraint length seven (k=7) convolutional encoder.

#### 2.2.2 Viterbi Decoder

While the implementation of a convolutional encoder is quite straightforward as shown in the previous section, the decoding of such a coded data stream at the receiving node is quite complex. In the late 1960's, Dr. A. J. Viterbi described a maximum likelihood decoding technique which greatly reduced the circuit sophistication of previous approaches.

Viterbi decoding consists fundamentally of three processes [17]. The first step in the decoder process is to generate of a set of correlation measurements, known as branch metrics, for each m grouping of codewords input from the communication channel (where m is 2 for rate 1/2 codes). These branch metric values indicate the correlation between the received codewords and the  $2^m$  possible codeword combinations.

The Viterbi decoder determines the state of the 7-bit memory at the encoder using a maximum likelihood technique. Once the value of the encoder memory is determined, the original information is known, since the encoder memory is simply the information that has been stored in the memory. To determine the encoder state, the second step in the Viterbi algorithm generates a set of  $2^{k-1}$  (where k is

Figure 2.9: Q0256 coding performance.

the constraint length, i.e., k=7 for the Q0256 algorithms) state metrics which are measurements of the occurrence probability for each of the  $2^{k-1}$  possible states as to the probable path taken to arrive at that particular state. These binary decision are stored in a path memory.

Step three computes the decoded output data. To do this, the path from the current state to some point in the finite past is traced back by chaining the binary decisions stored in the path memory during step 2 from state to state. The effects caused by noise to the one and only correct results are mitigated as the paths within the chainback memory converge after some history. The greater the depth of the chainback process the more likely that the final decoded result is error free. As a result, higher code rates and constraint lengths require longer chainback depth for best performance. The chainback memory in the Viterbi decoder traces the history of the previous states to arrive at the most probable state of the encoder in the past, and thus determine the transmitted data.

The Q0256 provides coding gain of 5.2 dB for rate 1/2 at  $10^{-5}$  BER shown in Figure 2.9[17].

# Chapter 3

# SYSTEM DESIGN

The goal of this design and development is to produce a programmable digital coder/decoder and modulator/demodulator to provide flexible data rates and multiple modulation/demodulation modes. The approach adopted is to use current VLSI chips from ASIC manufacturers such as Qualcomm and Stanford Telecomm to simplify needed circuits and get good performance. These VLSI chips can handle wide range of data rates and are programmable via a microcontroller through assembly language code.

In this chapter we will discuss some assumptions and constraints, such as system specifications, system interfaces, selection of IF frequency and system structure.

#### 3.1 **System Specifications**

#### (1). Coder/Decoder (CODEC)

Code Rate: 1/2

Constraint Length: K= 7

CODEC Scheme: convolutional encoder and Viterbi decoder;

differential encoder and differential decoder.

#### (2). Modulation/Demodulation (MODEM)

Data Rate: 1,200 bps, 2,400 bps, 4,800 bps, 9,600 bps, 19,200 bps.

MODEM Schemes: BPSK, QPSK, OQPSK, MSK.

#### (3). Control

One microcontroller (Intel 80C32) controls whole system. It can write or read control registers of the VLSI chips, communicate with the console display and provide other control signals. Another microcontroller is used in a digital Phase Lock Loop (PLL) for proper control and calculation.

#### (4). Flexibility

The MODEM/CODEC must be easily switched from one modulation mode to another and from one data rate to another.

#### (5). Full-Duplex Operation Capability

The terminal can be used as transmitter and receiver simultaneously.

### 3.2 System Interfaces

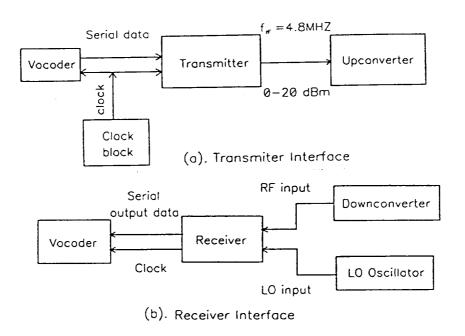

#### (1). Transmitter Interfaces

The input of the transmitter interfaces with a Vocoder which can provide several speech compression modes. The coming data is in serial format and is fed to the input of the encoder. After encoder the data rate is double, and becomes 2,400 bps, 4,800 bps 9,600 bps 19,200 bps and 38,400 bps. A master clock is created by the transmitter to synchronize the input data from the vocoder.

The output of the transmitter interfaces with a upconverter. Figure 3.1(a) shows the transmitter interfaces. The intermediate frequency (IF) signal has following specifications:

- (a). IF signal frequency:  $f_{IF} = 4.8 MHz$ .

- (b). IF signal power:  $P_{IF} = 0 \sim 20 dBm$ .

- (c). Maximum IF bandwidth = 100KHz.

#### (2). Reveiver Interfaces

The input of the receiver interfaces with two input resources: one is the downconverter signal (RF input), another is the local oscillator signal (LO input).

Figure 3.1: System interfaces.

The LO frequency signal mixed with RF frequency signal gives the IF frequency signal. These signals have following specifications:

- (a). IF signal frequency:  $f_{IF} = f_{RF} f_{LO} = 4.8 \text{MHz}$ .

- (b). Maximum IF bandwidth = 100KHz.

- (c). LO signal frequency:  $f_{LO}=900{\sim}1600 \rm MHz$  with a 1.25MHz step. LO signal power:  $P_{LO}=0{\sim}+5 \rm dBm$ .

- (d). RF signal power:  $P_{RF} = -30 dBm \pm 10 dBm$ .

RF signal frequency: Depending on the downconverter.

The outputs of the receiver are the serial output data and its clock. Figure 3.1(b) shows the receiver interfaces.

### 3.3 IF Frequency

The selection of IF frequency  $f_{IF}$  must satisfy the following two conditions.

(1). In order to make the phase continuous at bit transitions in MSK, the IF frequency  $f_{IF}$  (or carrier frequency  $f_c$ ) should be chosen such that  $f_{IF}$  is integral

multiple of 1/4T, one-fourth the bit rate[9].

(2). The demodulator's analog signal processing section is running at IF frequency  $f_{IF}$ . If it is much higher than necessary, as a result, board layout becomes more critical, circuitry becomes very sensitive to component variations and stray reactances, and the performance parameters of many devices are pushed to the limit.

In our design we chose that the IF frequency  $f_{IF}$  equals to 4.8MHz. Obviously, it is the integral multiple of 1/4T and not too high so that we can handle easily.

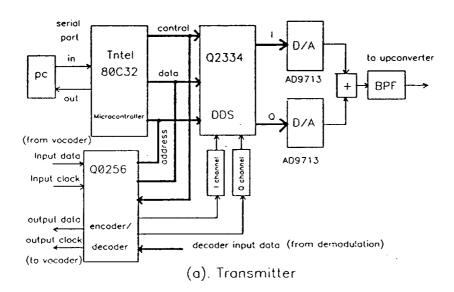

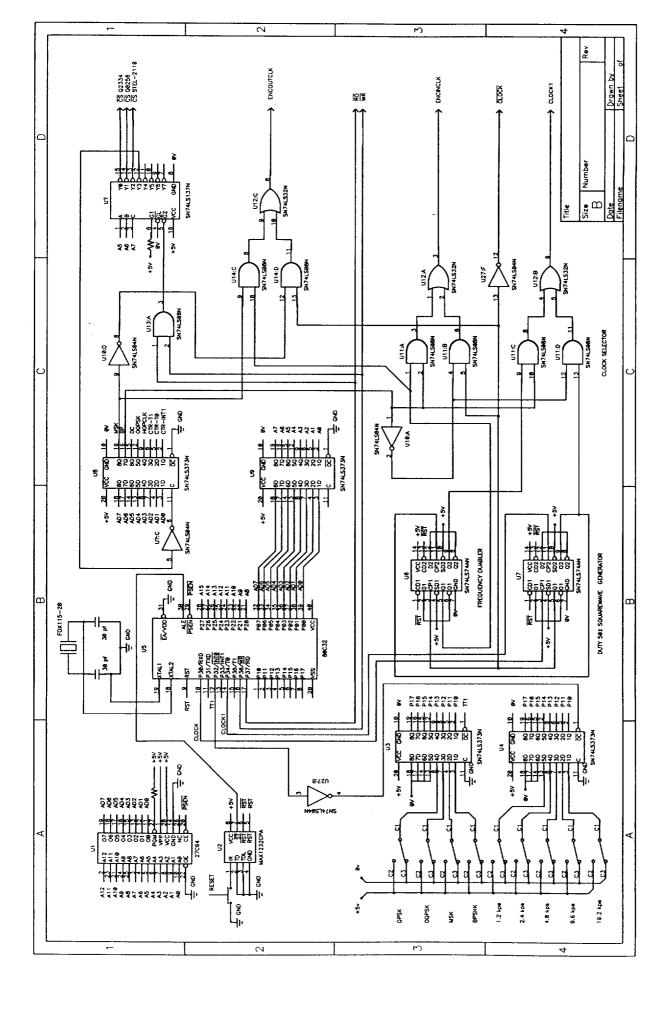

### 3.4 System Structure

#### (1). Transmitter Section

Figure 3.2(a) shows the block diagram of the transmitter section. The input signal of transmitter comes from previous stage Vocoder. After convolutional encoding in the chip Q0256 (Qualcomm Inc.), encoded signals are sent to the DDS chip Q2334 (Qualcomm Inc.) through I channel and Q channel control blocks. Our design uses the DDS to generate four different modulated signals instead of using traditional analog-generated method. DDS-generated quadrature signals have significant advantages over analog-generated quadrature signals. These include accurate 90 degrees phase shift and amplitude balance over a wide bandwidth, as well as minimal temperature and aging effect. The digital modulated signals output from chip Q2334 and go through two D/A converters. Then I and Q channel signals are combined together and go to a bandpass filter and are finally sent to the upconverter.

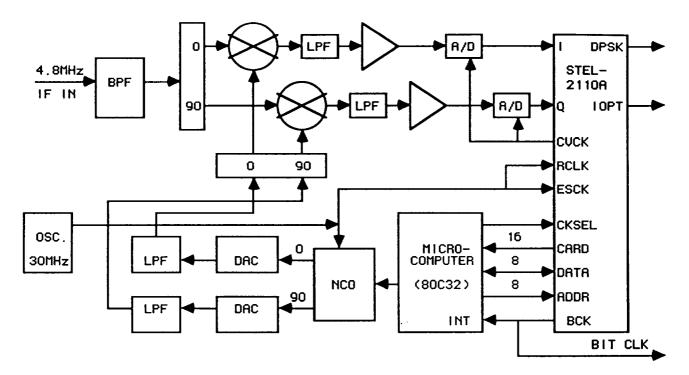

#### (2). Receiver Section

Figure 3.2(b) and (c) show the block diagrams of the receiver section. Figure 3.2(b) is for BPSK, QPSK and OQPSK. After mixer the IF signal goes through an IF amplifier and gains 30~50 dB. This signal is directly fed to I and Q channels and demodulated. Output signals of the multipliers are filtered out high frequency components and further amplified. Then an A/D converter converts analog signals to 6-bit digital signals which are sent to chip STEL-2110 (Stanford Telecom). The chip STEL-2110 has three fundamental functions: (1) The bit synchronizer produces the

clock signals to drive the entire circuit as well as the sampling of the incoming signals. (2) The optimally integrated I and Q signals are used to derive a feedback signal to control a digital Phase Lock Loop (PLL) circuit for carrier tracking. This signal is connected to a microcontroller which is used for calculations and control needed by the digital PLL. (3) Integrated I and Q channel signals are also provided in soft-decision output format which is used to facilitate the inclusion of Forward Error Correction (FEC) using convolutional coding and Viterbi decoding in the system.

Figure 3.2(c) shows the block diagram of MSK. An easier realized, low cost MSK demodulator is used.

#### (3). Control Section

The control circuit section can offer three main features in our design. (1). It can communicate with two input switchs which is used for the selections of modulation/demodulation modes and bit rates. (2). It produces all kinds of clocks for properly system operation and coding/decoding. (3) It can be used to write into or read from the control registers of the VLSI chips used in this system for proper configuration. Besides these, the control circuit also provides a lot of control signals to whole system.

An important task in this project is to develop the control code to write into or read from the internal registers of the VLSI chips for proper configuration and system control.

The control software is required to store in an EPROM at the final step.

(b). Demodulator-BPSK, QPSK, OQPSK

### (c). Receiver-MSK

Figure 3.2: System structures.

# Chapter 4

# TRANSMITTER DESIGN

In this chapter we will discuss the design activities which include the modulator design, encoder/decoder, D/A converter and other related designs. We put the decoder design in this chapter just for easy description.

## 4.1 Modulator Design

The Qualcomm Q2334 Direct Digital Synthesizer (DDS) is used for the modulator to support a wide range of modulation types including BPSK, QPSK, QPSK and MSK[15][16]. This technique provides fine frequency resolution and phase control, a broad bandwidth of operation, fast frequency switching, good spurious and phase noise performance, and the small size and power consumption.

DDS quadrature signals have significant advantages over analog quadrature signals, including excellent 90 degrees phase shift and amplitude balance over a wide bandwidth, as well as minimal temperature and aging effects. When DDS interfaces with a microprocessor, the intent is to make the modulator sufficiently versatile to allow easy modifications and upgrades.

#### 4.1.1 Q2334 Direct Digital Synthesizer

The Qualcomm Q2334 contains two independent DPS functions controlled from a single microprocessor interface. This interface provides the control for the phase and frequency of the generated sine waves as well as controlling the operating mode of the device. Figure 4.1 shows the internal structure of the Q2334. The value stored in phase increment register A or B is added to the value in the phase accumulator once during each clock period of the reference frequency. The resulting phase value (from 0 to  $2\pi$ ) is converted to a digitized sine wave value by the sine lookup function and this digital value is output from the DDS device.

The DDS is able to generate frequencies from 0 Hz to 1/2 the reference frequency. However, the practical upper limit of the output frequency is about 40% of the reference frequency. To output a particular frequency, the associated phase increment value  $\Delta\Phi$  must be loaded into the phase increment registers A or B. The generated frequency  $F_G$  and reference frequency (system clock)  $F_S$  are related to the phase increment value  $\Delta\Phi$  by the following equation:

$$F_G = \frac{F_S \times \Delta \Phi}{2^{32}} \tag{4.1}$$

The frequency resolution is determined by

Frequency Resolution =

$$\frac{F_S}{2^{32}}$$

(4.2)

when  $F_s=30$  MHz, we have the Frequency Resolution = 0.007 Hz.

Table 4.1 gives the register address map for the Q2334.

The Q2334 DDS provides the following modulation features:

### (1). External Phase Modulation

External phase modulation operates as an absolute phase adjustment technique. When using this mode the phase increment value for the unmodulated input is written into PIRA. The External Phase Modulation Enable (EPME) bit in the SMC register is set to logic 1 to enable this mode. The phase offset determined by the PM EXT BITs is latched into the DDS function each time the signal PM CLK is asserted. This PM EXT BIT setting causes a phase offset in 45 degrees increments

Figure 4.1: Q2334 DDS blok diagram.

| DDS1 REGISTER<br>ADDRESS | DDS2 REGISTER<br>ADDRESS | FUNCTION                                  |

|--------------------------|--------------------------|-------------------------------------------|

| 00H                      | 10H                      | Phase Increment A (PIRA) bits 0-7 (LSB)   |

| 01H                      | 11H                      | Phase Increment A (PIRA) bits 8-15        |

| 02H                      | 12H                      | Phase Increment A (PIRA) bits 16-23       |

| 03H                      | 13H                      | Phase Increment A (PIRA) bits 24-31 (MSB) |

| 04H                      | 14H                      | Phase Increment B (PIRB) bits 0-7 (LSB)   |

| 05H                      | 15H                      | Phase Increment B (PIRB) bits 8-15        |

| 06H                      | 16H                      | Phase Increment B (PIRB) bits 6-23        |

| 07H                      | 17H                      | Phase Increment B (PIRB) bits 24-31 (MSB) |

| 08Н                      | 18H                      | Synchronous Mode Control (SMC)            |

| 09H                      | 19H                      | Reserved                                  |

| OAH                      | 1AH                      | Asynchronous Mode Control (AMC)           |

| 08H                      | 18H                      | Reserved                                  |

| 0CH                      | 1CH                      | Accumulator Reset Register (ARR)          |

| ODH                      | 1DH                      | Reserved                                  |

| 0EH                      | 1EH                      | Asynchronous Hop Clock (AHC)              |

| 0FH                      | 1FH                      | Reserved                                  |

Table 4.1: Q2334 interface register address map.

as indicated in Table 4.2 without affecting the operation of the phase accumulator. Using this method we designed the BPSK, QPSK and OQPSK.

#### (2). Frequency Modulation

Frequency modulation is achieved by using the frequency multiplexer function that selects which PIR register (A or B) is used for accumulation in the phase accumulator function. External Multiplexer Enable (EME) bit in the SMC register is set to logic 1 to enable this mode. The signal EXT MUX controls the selection

| PM EXT<br>BIT2 | PM EXT<br>BIT1 | PM EXT<br>BIT0 | ABSOLUTE PHASE<br>OFFSET (degrees) |

|----------------|----------------|----------------|------------------------------------|

| 0              | 0              | 0              | 0                                  |

| 0              | 0              | 1              | 45                                 |

| 0              | 1              | 0              | 90                                 |

| 0              | 1              | 1              | 135                                |

| 1              | 0              | 0              | 180                                |

| 1              | 0              | 1              | 225                                |

| 1              | 1              | 0              | 270                                |

| 1              | 1              | 1              | 315                                |

Table 4.2: External phase modulation offset setting.

of the value stored in either PIRA or PIRB and the signal MUX CLK enables the selection made by the EXT MUX signal. The selection made by the EXT MUX signal is synchronously activated on the rising edge of the MUX CLK signal. Using this method we designed the MSK.

#### (3). Internal Modulation

Internal modulation requires use of the processor interface. By storing the synthesizer frequency (basic frequency without phase modulation) in the PIRA and modifying only the most 8 significant bits of the PIRB register, we can obtain a modulator up to 256 states phase modulation.

#### 4.1.2 Modulator Design

#### (1). BPSK Modulator design

In this design, the external phase modulation mode and only one half of the DDS (DDS1) are used. The design steps are as following:

- (a). The EPME bit in the SMC1 register (08H) is set to logic 1 to enable the external phase modulation mode. At same time, we need to disable the second part of the DDS (DDS2).

- (b). The phase increment value  $\Delta\Phi$  is loaded into the PIRA1 of the DDS1 to generate a unmodulated sine wave whose frequency is 4.8 MHz. According to Equation (4.1), and  $F_S = 30$  MHz and  $F_G = 4.8$  MHZ;

$$\Delta\Phi = \frac{4.8 \times 10^6}{30 \times 10^6} \times 2^{32} = 28F5C28F \quad (Hex)$$

We wrote this value  $\Delta\Phi$  to the register PIRA1 of the DDS1.

(c). From Equation (2.3) the BPSK modulated signal s(t) can be represented by

$$s(t) = d_I(t)\cos(2\pi f_c t)$$

where  $d_I(t)$  is the input data stream. When:

$$d_I(t) = 1$$

(high):  $s(t) = \cos(2\pi f_c t) = \sin(2\pi f_c t + 90^\circ)$

Figure 4.2: The modulator circuit for BPSK, QPSK, OQPSK and MSK.

$$d_I(t) = 0$$

(low):  $s(t) = \cos(2\pi f_c t + 180^\circ) = \sin(2\pi f_c t + 270^\circ)$

According to the Table 4.2 we can see that when setting PM1 EXT BIT 0 = 0 and PM1 EXT BIT 1 = 1 the phase offset of the unmodulated sine wave will only depend on the value of PM1 EXT BIT 2, so that

PM1 EXT BIT 2 = 0: phase offset =  $90^{\circ}$ PM1 EXT BIT 2 = 1: phase offset =  $270^{\circ}$

Figure 4.2 shows the BPSK modulator circuit. There needs an inverter at pin PM EXT BIT 2 to make I channel coming signal satisfy the phase transition of the BPSK signal.

Figure 4.3 shows the external control timing. The signal PM CLK comes from the microcontroller and is used to control the data rate.

#### (2). QPSK and OQPSK Modulators Design

In QPSK design the external phase modulation mode and two parts of the DDS are used. The design steps are as following:

- (a). The EPME bits in SMC1 (08H) and SMC2 (18H) registers are set to logic 1 to enable the external phase modulation mode.

- (b). The phase increment value  $\Delta \Phi$  is loaded into phase increment registers

| SIGNAL             | DESCRIPTION                       |

|--------------------|-----------------------------------|

| tHCMC              | HOP CLK falling to MUX CLK rising |

| tMC                | MUX CLK high period               |

| <sup>†</sup> MCMC  | MUX CLK low period                |

| tMCHC              | MUX CLK falling to HOP CLK rising |

| <sup>t</sup> MCHLD | EXT MUX setup to MUX CLK          |

| tMCSU              | EXT MUX hold after MUX CLK        |

| tpc                | PM CLK high period                |

| tPCPC              | PM CLK low period                 |

| 1PMSU              | PM data setup to PM CLK           |

| tPMHLD             | PM data hold after PM CLK         |

Figure 4.3: External control timing.

PIRA1 and PIRA2 of the DDS to generate unmodulated sine waves whose frequencies are equal to 4.8 MHz. According to equation (4.1)

$$\Delta \Phi = \frac{F_G}{F_S} \times 2^{32} = 28F5C28F \qquad (Hex)$$

where  $F_G = 30MHz$ , and  $F_S = 4.8MHz$ .

(c). From Equation (2.6) the QPSK modulated signal s(t) can be written by:

$$s(t) = d_I(t)\cos(2\pi f_c t) + d_Q(t)\sin(2\pi f_c t)$$

Because the QPSK signal can be represented as the summation of the orthogonal BPSK signals, we can design I channel and Q channel separately.

I channel: It is identical with the BPSK design. we can use the same configuration and circuit to accomplish the I channel function of QPSK.

Q channel: when

$$d_Q(t) = 1$$

(high):  $\sin(2\pi f_c t)$

$d_Q(t) = 0$  (low):  $\sin(2\pi f_c t + 180^\circ)$

According to the Table 4.2 we can see that when setting PM2 EXT BIT 0 = 0 and PM2 EXT BIT 1 = 0, the phase offset of the unmodulated sine wave of Q channel will only rely on the value of PM2 EXT BIT 2. So we have

PM2 EXT BIT

$$2 = 0$$

(low): phase offset  $= 0$

PM2 EXT BIT  $2 = 1$  (high): phase offset  $= 180^{\circ}$

Figure 4.2 shows the QPSK modulator circuit. QPSK has the same external control timing as BPSK shown in Figure 4.3.

OQPSK modulator is identical with QPSK modulator except there is a delay of T, the one half symbol during, at Q channel input signal. A dual D Flip-Flop (74LS74A) is used to design this delay function.

#### (3). MSK Modulator Design

In MSK design the frequency multiplexer function and only one half of the DDS (DDS1) are used. The following is the design steps:

(a). The EME bit in SMC1 register (08H) is set to logic 1 to enable the external multiplex control. Meanwhile, we need to disable the second part of the DDS.

(b). There are two phase increment values  $\Delta \Phi_+$  and  $\Delta \Phi_-$  which must be loaded into phase increment registers PIRA1 and PIRB1 of the DDS1 in MSK.

$$\Delta \Phi_{+} = \frac{f_{+}}{F_{S}} \times 2^{32}$$

$$\Delta \Phi_{-} = \frac{f_{-}}{F_{S}} \times 2^{32}$$

(4.3)

where  $f_{+} = f_{c} + \frac{1}{4T}$ ;  $f_{-} = f_{c} - \frac{1}{4T}$  and  $\frac{1}{T}$  is the channel data rate which is double input data rate because there is an encoder with 1/2 code rate in the system.

With different data rate the  $\Delta\Phi_+$  and  $\Delta\Phi_-$  are different. For example, If  $\frac{1}{T}=19200$  bps (input data rate = 9600 bps)

$$f_{+} = f_{c} + \frac{1}{4T} = 4804800 \ Hz$$

$f_{-} = f_{c} - \frac{1}{4T} = 4795200 \ Hz$

and

$$\triangle \Phi_{+} = \frac{4804800}{30000000} \times 2^{32} = 29003EEA \quad (Hex)$$

$\triangle \Phi_{-} = \frac{4795200}{30000000} \times 2^{32} = 28EB4635 \quad (Hex)$

If  $\frac{1}{T} = 9600$  bps (input data rate = 4800 bps)

$$f_{+} = f_{c} + \frac{1}{4T} = 4802400 \ Hz$$

$f_{-} = f_{c} - \frac{1}{4T} = 4797600 \ Hz$

and

by

$$\triangle \Phi_{+} = \frac{4802400}{30000000} \times 2^{32} = 28FB00BD \quad (Hex)$$

$$\triangle \Phi_{-} = \frac{4797600}{30000000} \times 2^{32} = 28F08463 \quad (Hex)$$

(c). From Equation (2.13) the MSK modulated signal s(t) can be written

$$s(t) = \cos\left(2\pi f_c t + b_k(t)\frac{\pi t}{2T} + \Phi_k\right)$$

where  $b_k(t) = -d_I(t)d_Q(t)$ , and  $\Phi_k$  is an initial phase. From this Equation, we have:

If  $d_I(t)$  and  $d_Q(t)$  are opposite,  $b_k(t) = 1$  (high)

If

$$d_I(t)$$

and  $d_Q(t)$  are same,  $b_k(t) = -1$  (low)

The relationship between  $d_I(t)$  and  $d_Q(t)$  is the exclusive-OR function. Practically, we use an exclusive-OR gate to realize this function.

When the external multiplex control is enable we have the following features in Q2334 DDS. If the EXT MUX signal is high when the MUT CLK is asserted the

phase accumulator accumulates phase increments from the PIRB register. If the EXT MUX signal is low when the MUX CLK is asserted the phase accumulator accumulates phase increments from the PIRA register. Changing the value of the EXT MUX input therefore causes the alternation between the frequency controlled by the PIRA and the frequency controlled by the PIRB. In this way, we have to write the value of  $\Delta\Phi_+$  into register PIRB1 to generate the first frequency and the value of  $\Delta\Phi_-$  into register PIRA1 to generate the second frequency, respectively. The output of the exclusive-OR gate is connected to the pin EXTMUX1. Following above rules, we have:

$d_I(t)$  and  $d_Q(t)$  are opposite  $\Rightarrow b_k(t) = 1 \Rightarrow EXTMUX1 = high \Rightarrow PIRB1$  $d_I(t)$  and  $d_Q(t)$  are same  $\Rightarrow b_k(t) = 0 \Rightarrow EXTMUX1 = low \Rightarrow PIRA1$

Figure 4.2 shows this design and Figure 4.3 provides the external control timing. The signal MUX CLK comes from the microcontroller and is used to control the data rate.

## 4.2 Encoder/Decoder Design

The Qualcomm Q0256 is used as encoder and decoder in our design[17]. The Q0256 provides:

- (a). On-chip convolutional encoder/Viterbi decoder, differential encoder/decoder, and V.35 data scrambler/descrambler.

- (b). Processing data at one of four selectable code rates (1/2, 1/3, 3/4 and 7/8).

- (c). Built-in synchronization capability for BPSK, QPSK and OQPSK modems and operating with either 1 bit hard-decision or 3-bit soft-decision.

- (d). Two powerful techniques for monitoring synchronization status as well as performing channel bit error rate measurement.

- (e). 5.2 dB coding gain (rate 1/2) at  $10^{-5}$  BER.

Figure 4.4: (a). Parallel data mode, (b). Serial data mode.

#### 4.2.1 Parallel and Serial Data Modes

The Q0256 provides two kinds of data modes: "parallel" and "serial", as shown in Figure 4.4.

The Q0256 encoder produces two encoded bits with code rate 1/2 for each information input bit. When operating in the parallel data mode these two output bits are presented at C0 and C1 output pins during each period of the channel rate clock (ENCOUTCLK). In this case, the ENCOUTCLK frequency should be the same as the frequency of information rate clock (ENCINCLK). When operating with serial data mode all encoded bits are provided on the single output pin C0 at the period of the ENOUTCLK signal. In this mode, the ENOUTCLK frequency should be twice the ENCINCLK frequency.

The Q0256 decoder inputs data in either serial or parallel mode. When operating in the parallel data mode with code rate 1/2, two input codewords are provided in the R0 and R1 input pins during each period of the DECINCLK. When

operating in the serial mode, the decoder inputs all encoded data using only the R0 input pin. The relationship of the DECINCLK to DECOUTCLK frequencies is the reciprocal of the relationship of the encoder ENCINCLK to ENCOUTCLK frequencies.

Design rules (code rate 1/2):

(1). Parallel mode (QPSK, OQPSK and MSK)

ENCINCLK = ENCOUTCLK

DECINCLK = DECOUTCLK

(2). Serial mode (BPSK)

$2 \times ENCINCLK = ENCOUTCLK$

$\frac{1}{2} \times DECINCLK = DECOUTCLK$

## 4.2.2 Synchronization Status Monitor Design

The Q0256 can automatically synchronize incoming data streams to the Viterbi decoder circuit. The synchronization technique is a two-step process.

- (1). Detect: The decoder quality state is constantly monitored by using the "state metric normalization rate" circuit. The designer programs an "in-sync/out-of-sync" threshold for this internal circuit. The success or failure of this test for each test period is indicated on output pins 53 (INSYNC) and 52 (OUTOFSYNC).

- (2). Correct: The OUTOFSYNC output pin can be directly connected to the SYNCCHNG input pin. This provides a feedback path between the synchronization monitor and the synchronization correction circuit. The effects of the out-of-sync condition can be compensated for either by a timing re-alignment or by permutation of the decoder input data.

The normalization circuit consists of two counters:

- T counter measures the number of decoded bits.

- N counter measures the number of state metric normalizations.

#### (1). Design Rules:

(a). The actual number of decoded bits in the normalization teat period

is

$$T \times 256 \tag{4.4}$$

(b). The actual number of normalizations allowed is

$$(N-1)\times 8+4\tag{4.5}$$

(c). The normalization rate threshold is

$$\frac{(N-1)\times 8+4}{T\times 256}\tag{4.6}$$

where T and N are the two's complement values of the 8-bit numbers loaded into the T and N counters.

- (2). Conditions:

- (a). When operating with rate 1/2 coding, a normalization rate threshold of about 10% will reliably detect a loss of synchronization.

- (b). The normalization measurement should detect at least 20-30 normalizations before declaring a loss of synchronization.

- (3). Design:

- (a). Select the number of normalizations to be detected to be approximately 50. So we set:

$$N = 7$$

Because

$$(N-1) \times 8 + 4 = (7-1) \times 8 + 4 = 52$$

the binary value which is loaded into N counter is F9 (Hex).

(b). Because the value for the T counter must be approximately ten times the value in the N counter, we set:

$$T = 2$$

Because

$$T \times 256 = 2 \times 256 = 512$$

the binary value which is loaded into T counter is FE (Hex).

(c). The normalization rate threshold is

$$\frac{52}{512} \times 100\% = 10.2\%$$

It is satisfied the condition (a).

#### (4). Experiment results:

Through many times of experiments, We found that for different modulation modes and different bit rates, the values in N counter and T counter vary from the theoretical values for best system performance. These values are given in the software-MDCOB. Also, the procedure of loading values into the internal registers of Q0256 is fixed for proper system operation. The software MDCOB is in consistance with this fixed procedure.

## 4.2.3 Monitoring Channel Bit Error Rate (BER)

The on-chip BER monitor circuit consists of two accumulators acting as counters. One accumulator counts decoder input codewords. Another accumulator counts codeword errors detected by the on-chip re-encode and compare circuit. The design steps are as following:

- (1). Set BER measurement period register. The loaded value is the two's complement 24-bit binary value and is multiplied by 1000 to give the actual number of codewords to be monitored. For example, if the actual number is 10<sup>7</sup>, the two's complement binary value FFD8F0 (Hex) of 10<sup>4</sup> is loaded into addresses 0CH, 0BH and 0AH.

- (2). When the BER measurement period is completed, the signal BERDONE (pin 50) goes to high for two periods of DECOUTCLK. It can be used as an interrupt status bit to microprocessor. The actual measured bit error count is found from the following formula:

$$Actual\ Error\ count = (register\ value - 1) \times 8 \tag{4.7}$$

(3). The actual symbol BER is

$$BER = \frac{the \ measured \ error \ quantity}{the \ number \ of \ codewords \ in \ the \ test} \tag{4.8}$$

#### 4.2.4 The Other Considerations

- (1). The 3-bit soft-decision values can be fed to the Q0256 decoder inputs in either sign-magnitude or offset-binary notation. The selection of the input format is made via the microprocessor interface. We used offset binary format in our design.

- (2). Enable the on-chip differential encoder/decoder, and data scrambling/descrambling circuits. This is also made via the microprocessor interface.

- (3). The Q0256 processor interface has 4 read registers and 21 write registers. Carefully setting these registers we can configure the different operating modes for encoder and decoder.

- (4). In our design, there is a mechanism that can interchange the demodulated I-channel data and Q-channel data before these data go into the decoder. This is because we found that these data need be interchanged for some modulation modes for proper operation.

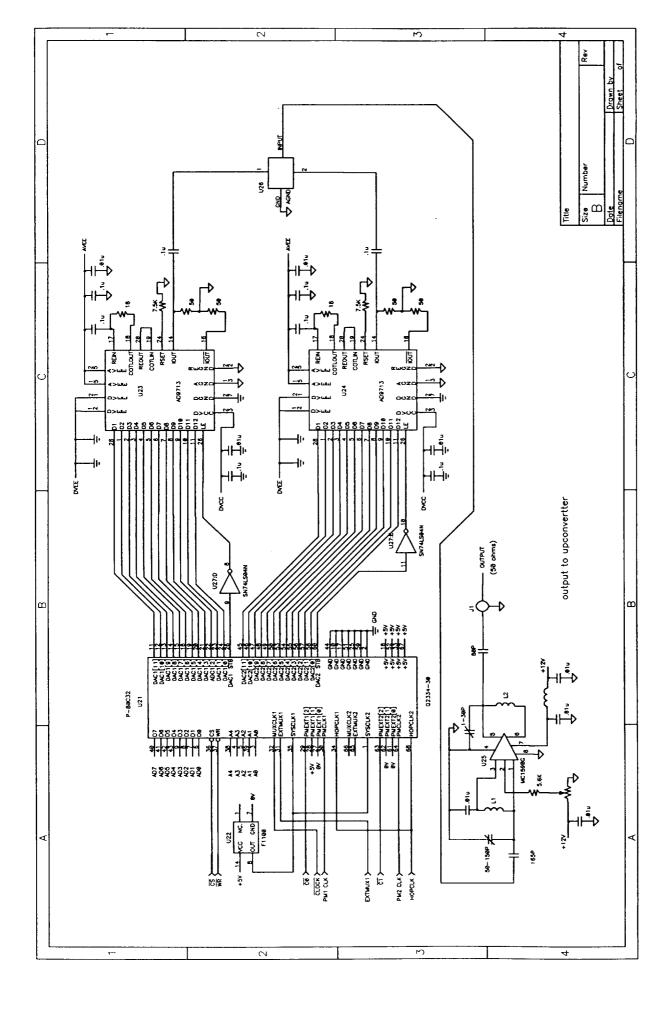

## 4.3 D / A Converter

We selected AD9713 (Analog Devices) as the digital to analog converter[19]. The AD9713 has the following features:

- 1). 12-bit resolutions

- 2). TTL-compatible

- 3). Fast setting

- 4). 80 MSPS update rate

- 5). Low power consumption

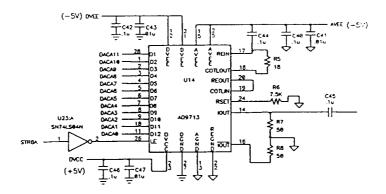

Figure 4.5 shows the actual circuit that we used in our design for D/A converter.

#### (1). Setting the Reference

Figure 4.5: D / A converter circuit.

We used the internal reference that allows operation with a minimum of external components in our design. When using the internal reference:

- a). PEOUT (pin 20) should be connected to COTLIN (pin 19);

- b). COTLOUT (pin 18) should be connected to REIN (pin 17) through as 18  $\Omega$  resistor;

- c). A 0.1 uF capacitor from pin 17 to -Vs (pin 15) improves setting by decoupling switching noise from the current sink base line;

- d).  $R_{SET}$  (pin 24) should be connected to ground through a 7.8 K $\Omega$  resister. This determines the Full-scale current out.

#### (2). Outputs

The switch network controls complementary current outputs  $I_{out}$  and  $\overline{I_{out}}$ . The current output can be converted to a voltage output by resistive loading as shows in Figure 4.5. Both  $I_{out}$  and  $\overline{I_{out}}$  should be loaded equally for best overall performance.

Full-scale output current  $I_{out(FS)}$  is determined by

$$I_{out(FS)} = \frac{Reference\ Voltage}{R_{SET}} \times 128 \tag{4.9}$$

The internal reference is nominally -1.26 V with a tolerance of  $\pm$  10%, and  $R_{SET} =$  7.5 K $\Omega$ , so

$$I_{out(FS)} = -20.48 \ mA$$

The voltage which is developed is the product of the output current and the value of

the load resistor.

$$V_{out(FS)} = -20.48 \times 10^{-3} \times 50 = -1.024 \ V$$

The voltage swing will be from 0 to -1.024 V across 50  $\Omega$  resistor.

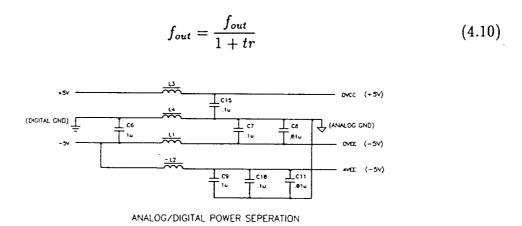

#### (3). Power and Grounding

Maintaining low noise on power supplied and ground is critical for obtaining optimum results with the AD9713. We separate the analog ground plane with digital ground plane, and also isolate digital power supply with analog power supply. Figure 4.6 shows this effort.

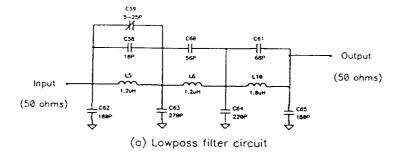

## 4.4 Lowpass Filter

Since this is a sampled data system, spectral components will be generated at all the frequencies  $n f_{clk} \pm f_c$ , where n is an integer. n = 0 gives the carrier frequency, and the frequencies given by all other values of n are above the Nyquist frequency (half the sampling frequency). The design is made on the board for an anti-aliasing (low pass) filter at the output of the combiner to attenuate these spurious signals. This filter has up to 3 sections (7th. order), and is a pole and zero type (cauer). Cauer (elliptic) filters are recommended because of their superior characteristics[20].

The maximum cutoff frequency is given by the equation:

Figure 4.6: Power supply.

where tr is the transition ratio of the filter. Assuming that about 1 dB of ripple is allowable in the passband and 55-60 dB of attenuation is required in the stop-band, a 7 pole (3 sections) filter have a tr of about 1.17, and the maximum value of  $f_{out}$  is

$$f_{out} = \frac{f_{clk}}{1 + 1.17} = \frac{30 \times 10^6}{2.17} = 13.9 \ MHz$$

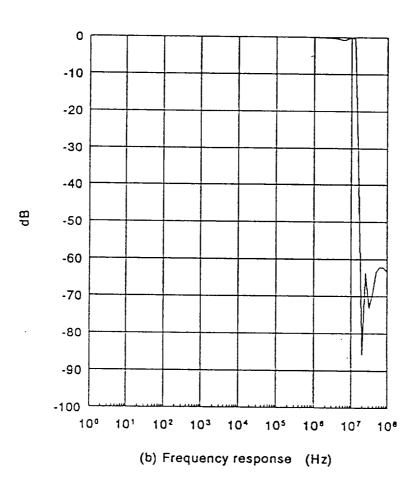

where  $f_{clk} = 30 \ MHz$ . Figure 4.7 (a) shows the lowpass filter circuit (50  $\Omega$  impedance) and (b) is the frequency response of this lowpass filter.

Figure 4.7: (a) lowpass filter circuit, (b) frequency response.

--

# Chapter 5

# RECEIVER DESIGN

In this chapter, we will discuss two kinds of demodulator design, one for BPSK, QPSK and OQPSK, and another for MSK. Figure 3.2(b) and (c) show these two demodulator block diagrams.

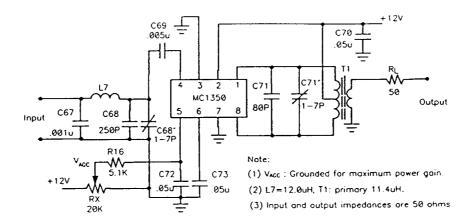

## 5.1 IF Amplifier and Bandpass Filter

Mainly using the MOTOROLA MC1350 chip, this circuit combines IF amplifier and bandpass filter (BPF) together. MC1350 is a monolithic IF amplifier chip featuring wide range AGC, nearly constant input and output admittances over the entire AGC range and low reverse transfer admittance[27]. Operating at required center frequency 4.8 MHz and 3-dB bandwidth 100 KHz, this circuit can realize power gain about 45 dB (with input = 0.01 v) and has low noise and linear amplifying features. Figure 5.1 shows this circuit.

There are several points which should be noted:

(1). There are two self-resonant loops in this circuit ( $C_{67}$ ,  $C_{68}$ ,  $L_7$  and  $C_{71}$ ,  $T_1$  with  $C_{68}$ ' and  $C_{71}$ ' micro-adjustment). Theoretically, it should be better to make both of these two loops resonant at center frequency. In practice, it may be discovered  $C_{71}$  and the choke  $T_1$  are more sensitive to the center frequency while  $C_{67}$ ,  $C_{68}$  and

Figure 5.1: IF amplifer and BPF.

$L_7$  are more related with the range of 3-dB bandwidth. When this circuit is running properly, only the loop of  $C_{71}$  and  $T_1$  resonates at center frequency (4.8 MHz). And increasing the value of  $C_{67}$  or  $C_{68}$ , we will have narrower bandwidth.

- (2). T<sub>1</sub> is wound with #36 AWG. It's primary winding is about 10-12 turns and secondary winding about 2-3 turns. The number of primary winding turns determines the center frequency while the number of secondary winding turns is related with power gain.

- (3). All the system parameters are measured with  $V_{AGC}$  grounded for maximum power gain. The value of  $V_{AGC}$  has little influence on the center frequency and 3-dB bandwidth.

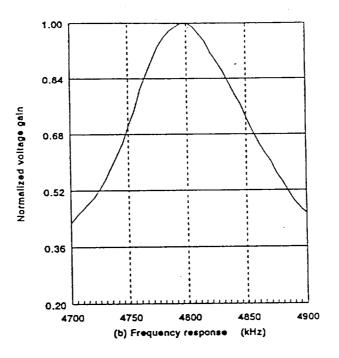

The frequency response curve of this circuit is shown in Figure 5.2 (V<sub>AGC</sub> grounded).

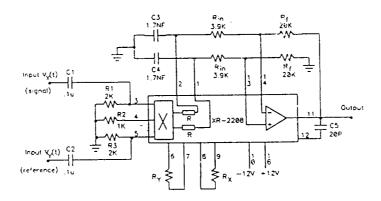

## 5.2 Multiplier, LPF and Amplifier

The chip XR-2208 (EXAR) is used for the purposes of multiplier, LPF and amplifier as shown in Figure 5.3. The XR-2208 contains a four quadrant multiplier and an independent Op Amp[30]. The main features are maximum versatility, excellent linearity and wide bandwidth.

Figure 5.2: The frequency response curve of the IF amplifier and BPF.

## 5.2.1 Multiplier

The multiplier section of the XR-2208 can be used as a synchronous detector. There are two input signals:

- (1) IF input signal  $V_X$ : IF frequency = 4.8 MHz, input power level = 0 dB (approximately).

- (2) Reference signal  $V_Y$ : a square wave coming from the carrier recovery

Figure 5.3: Multiplier, LPF and amplifier.

circuit.

The differential output voltage  $V_d$ , across the pins 1 and 2, is proportional to the product of voltages  $V_X$  and  $V_Y$  applied to the inputs. The  $V_d$  can be expressed as

$$V_d \approx \left(\frac{25}{R_X R_Y}\right) (V_X V_Y) \tag{5.1}$$

where all voltages are in volts and resistors are in  $K\Omega$ .  $R_X$  and  $R_Y$  are the gain control resistors for X and Y sections of the multiplier. From above, the gain constant of the multiplier section  $K_m$  can be expressed as

$$K_m = \frac{25}{R_X R_Y} \tag{5.2}$$

If  $R_X = 0.4 \text{ K}\Omega$  and  $R_Y = 3.6 \text{ K}\Omega$ , we have  $k_m = 6.25$ . The resistors  $R_X$  and  $R_Y$  are selected so that the circuit can never become saturated.

Now, consider an IF input signal as

$$V_X(t) = V_X \sin(\omega_i t + \theta_i) \tag{5.3}$$

and the square wave reference signal from the carrier recovery circuit is

$$V_Y(t) = V_Y \sum_{n=0}^{\infty} \frac{4}{\pi(2n+1)} \sin[(2n+1)\omega_r t]$$

(5.4)

where  $\omega_i$  is the IF frequency,  $\omega_r$  is the reference signal frequency and  $\theta_i$  is the phase in relation to the reference signal.

Multiplying these two terms, using the appropriate trigonometric relationships, gives:

$$V_d(t) = \frac{2K_m}{\pi} \left[ \sum_{n=0}^{\infty} \frac{V_X V_Y}{(2n+1)} \cos[(2n+1)\omega_r t - \omega_i t - \theta_i] - \sum_{n=0}^{\infty} \frac{V_X V_Y}{(2n+1)} \cos[(2n+1)\omega_r t + \omega_i t + \theta_i] \right]$$

(5.5)

If  $\omega_r$  is close to  $\omega_i$ , the first term (n=0) has a low difference frequency component. As  $\omega_r$  is driven closer to  $\omega_i$  this difference becomes smaller until  $\omega_r = \omega_i$  and lock is achieved. The first term then becomes:

$$V_d(t) = \frac{2K_m V_X V_Y}{\pi} \cos \theta_i$$

Other terms are of high frequencies and are rejected by the loowpass filter.

## 5.2.2 LPF and Amplifier

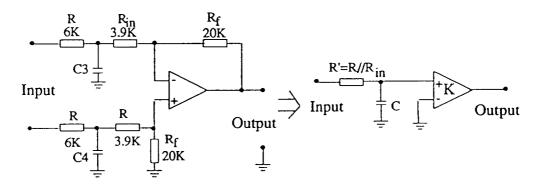

The equivalent circuit for LPF and amplifier is shown in Figure 5.4.

Figure 5.4: The equivalent circuit for LPF and amplifier.

where R is the internal resistor of the XR-2208, gain K for the amplifier

$$K = -\frac{R_f}{R + R_{in}} \approx -2$$

and

$$R' = \frac{R \times R_{in}}{R + R_{in}} = 2.36 \ K\Omega$$

Let @-3dB cutoff frequency  $f_{cut}$  of the lowpass filter be 40 KHz (>38.4KHz), so

$$C = \frac{1}{2\pi f_{cut}R'} = 1700 \ PF$$

We chose 1500 PF~1800 PF for  $C_3$  and  $C_4$ . If needed, the amplifier gain can be increased by changing the resistors  $R_{in}$  and  $R_f$ .

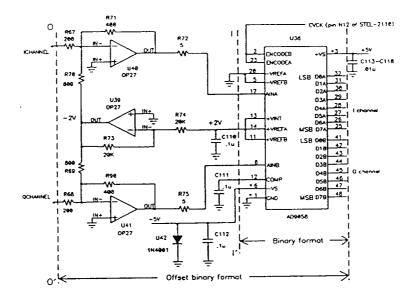

## 5.3 Analog to Digital Converter

After synchronous detection stage, the analog signals from I and Q channels should be converted to digital signals, which are then fed to the STEL-2110 chip for further processing. We have known that the maximum inputs from I and Q channels are  $\pm$  0.5  $V_{p-p}$  bipolar analog signals, and outputs of STEL-2110 should be digital signals with offset binary format. The AD9058 (Analog Devices) is selected for the

Figure 5.5: The analog to digital converter.

purpose of converting the analog signal to the digital signal[19]. It combines two independent high performance 8-bit analog-to-digital converters (ADCs) on a single monolithic IC. Analog input range is established by the voltages applied at the voltage reference inputs ( $+V_{ref}$  and  $-V_{ref}$ ). The AD9058 can operate from 0V to 2V using the internal voltage reference, or anywhere between -1V to +2V using external reference.

Figure 5.5 shows the analog-to-digital converter circuit. In our design, the internal voltage reference was used for reducing the number of external components. The input range of the ADCs are positive unipolar in this configuration, ranging from 0V to +2V. The bipolar input signals are buffered, amplified and offset into the proper input range of the ADC using three low distortion amplifiers such as OP27.

We have:  $amplifier\ gain = 2$  and  $offset\ voltage = 1V$ .

In this case, the bipolar  $\pm 0.5$ V input signals are changed into the unipolar positive 0V to +2V input signals. The output signal format is binary format (unipolar) with respect to the input signals I—I' and is offset binary format (bipolar) with respect to the input signals O—O'.

The sampling clock comes from the pin N12 (CVCK) of the STEL-2110chip. The diode between ground and  $-V_S$  is normally reverse biased and is used to prevent latch-up.

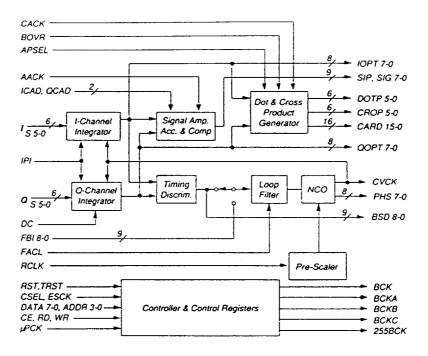

Figure 5.6: Block diagram of the STEL-2110.

## 5.4 STEL-2110

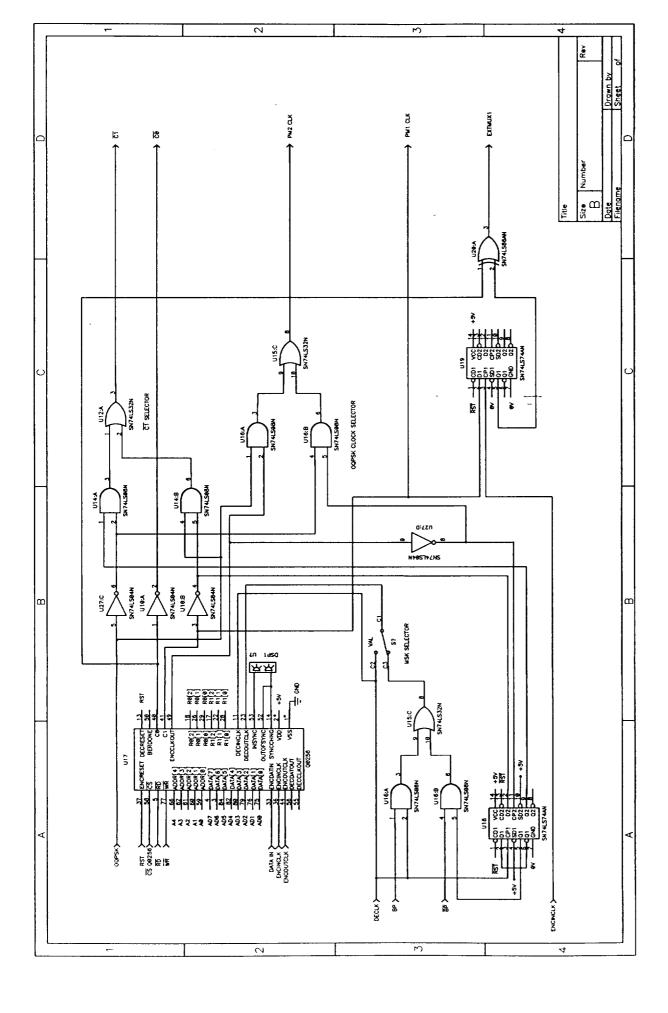

## 5.4.1 STEL-2110 Bit Synchronizer/PSK Demodulator

Figure 5.6 shows the block diagram of the STEL-2110. The STEL-2110 has three fundamental functions: (a) Bit timing recovery circuit, (b) Carrier tracking feedback, (c) Integrated I and Q channel output signals[21][22].

## (1) Bit timing recovery circuit

The bit synchronizer portion of the STEL-2110 is a digital phase locked loop which operates by integrating the input signals in both the I and Q channels over one symbol period. This is done 3 times: in addition to the nominally "on time" integration, "quarter period early" and "quarter period late" integrations are also carried out. The difference between the early and late integrations gives an indication of the timing error, since the averaged difference will be zero when the timing is correct. This signal is passed into the loop filter which is effectively a second order filter and then used to drive a numerically controlled oscillator (NCO)

which produces the clock signals to drive the entire circuit as well as sampling the incoming signals.

The NCO has 28-bit frequency resolution and is preset to the nominal symbol frequency at the start-up. The preset data is a 24-bit word and is loaded into the 24 MSBs of the 28-bit accumulator. The data from the loop filter is added to this word so that the data from the loop filter modifies the 23 LSBs of the 28-bit phase accumulator.

In our design, this circuit provides the bit timing for all four demodulations.

#### (2) Carrie tracking feedback circuit

The punctual I and Q signals from the I and Q channel integrator circuits are processed in the carrier discriminator circuit. The dot and cross produce of the I and Q signals are first formed, where:

$$Dot \ product = I_n \times I_{n-1} + Q_n \times Q_{n-1} \tag{5.6}$$

and

$$Cross\ product = I_n \times Q_{n-1} - Q_n \times I_{n-1} \tag{5.7}$$

both signals are used to form the carrier discriminator functions.

In the automatic frequency control (AFC) mode, this is

for BPSK data:

-Sign (Dot)

$$\times$$

Cross

for QPSK data:

In the phase locked loop (PLL) mode, this is

for BPSK data:

-Sign

$$(I) \times Q$$

for QPSK data:

-Sign

$$(I_{rot}) \times Q_{rot}$$

, if  $|I_{rot}| > |Q_{rot}|$

Sign  $(Q_{rot}) \times I_{rot}$ , else

where I<sub>rot</sub> and Q<sub>rot</sub> are the I and Q vectors rotated by 45°.

In our design, the PLL mode is selected since it is intended for coherent demodulation in continuous carrier systems. This function is integrated under the control of the carrier accumulate clock (CACK) to form the discriminator output, which is available on the 16-bit bus. The 12-bit of them is connected to a digital to analog converter to drive a loop filter which in turn drives the frequency control of the local oscillator. This is the method we used to design the carrier recovery circuit for BPSK, QPSK and OQPSK. For MSK, we used the self-synchronization feature of MSK to generate the reference carrier signals.

#### (3) The I and Q channel output signals

The punctually integrated I and Q channel signals are provided as the outputs in 8-bit soft-decision format which is used to facilitate the inclusion of forward error correction using Viterbi deciding in the system. The 8-bit integrated outputs are represented in offset two's complement format.

## 5.4.2 Design with STEL-2110

#### (1) Bit rate control

Addresses  $12_H$ ,  $13_H$  and  $14_H$  are the bit rate control register. The 28-bit NCO is programmed with these 3 bytes, which are loaded into the 24 MSBs of the 28-bit phase increment register. Bit 7 of address  $12_H$  is the MSB, and bit 0 of address  $14_H$  is the LSB. The formula for  $N_r$ , the number programmed in the NCO, is as follows:

$$A_{\tau} = R_s \times S_s \times A_i \tag{5.8}$$

and

$$N_r = \frac{A_r}{f_c} \times 2^{24} \tag{5.9}$$

where:

N<sub>r</sub>: 24 bit number which establishes the nominal A/D sample rate.

$f_c$ : NCO input clock frequency  $f_c = \frac{reference\ clock}{C_s}$  (after scaling the input clock by  $C_s = 16$ ).

$A_r$ : A/D converter clock rate.

R<sub>s</sub>: symbol rate of PSK information to be demodulated.

S<sub>s</sub>: number of accumulated samples per symbol.

A<sub>i</sub>: number of front end accumulator.

We set:

$$f_c = \frac{30 MHz}{16} = 1875000 Hz$$

$S_s = 4$

$$A_i = 1$$

For QPSK, OQPSK and MSK (parallel mode)

$R_s = 1200, 2400, 4800, 9600, 19200 \text{ bps}$

For BPSK (serial mode)

$R_s = 2400, 4800, 9600, 19200, 38400 \text{ bps}$

The  $N_r$  has the different value with the different symbol rates. In our design, for example, if  $R_s = 9600$  bps

$$A_r = 9600 \times 4 \times 1 = 38400$$

and

$$N_r = \frac{38400}{1875000} \times 2^{24} = 053E2D \quad (Hex)$$

The NCO is not double buffered and will immediately switch to the newly programmed frequency after any of the bytes are changed. Do not set the 24-bit data to be  $000000_H$  at any time as this will set the NCO output frequency to zero, causing the entire chip to freeze up, requiring to restart the chip.

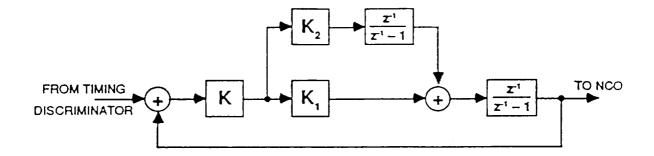

## (2) Loop gain control