63227

NASA Contractor Report 4682

12-106

## Formal Verification of an Avionics Microprocessor

Mandayam K. Srivas and Steven P. Miller

(NASA-CR-4682) FORMAL VERIFICATION OF AN AVIONICS MICROPROCESSOR Final Report (SRI International Corp.) 106 p

N95-33396

**Unclas**

H1/61 0063227

Contract NAS1-18969 Prepared for Langley Research Center

## Formal Verification of an Avionics Microprocessor

Mandayam K. Srivas SRI International • Menlo Park, California

Steven P. Miller Rockwell International • Cedar Rapids, Iowa

Printed copies available from the following:

NASA Center for AeroSpace Information 800 Elkridge Landing Road Linthicum Heights, MD 21090-2934 (301) 621-0390

National Technical Information Service (NTIS)

5285 Port Royal Road

Springfield, VA 22161-2171

(703) 487-4650

#### Abstract

Formal specification combined with mechanical verification is a promising approach for achieving the extremely high levels of assurance required of safety-critical digital systems. However, many questions remain regarding their use in practice: Can these techniques scale up to industrial systems, where are they likely to be useful, and how should industry go about incorporating them into practice? This report discusses a project undertaken to answer some of these questions, the formal verification of the AAMP5 microprocessor. This project consisted of formally specifying in the PVS language a Rockwell proprietary microprocessor at both the instructionset and register-transfer levels and using the PVS theorem prover to show that the microcode correctly implemented the instruction-level specification for a representative subset of instructions. Notable aspects of this project include the use of a formal specification language by practicing hardware and software engineers, the integration of traditional inspections with formal specifications, and the use of a mechanical theorem prover to verify a portion of a commercial, pipelined microprocessor that was not explicitly designed for formal verification.

|   |   | • • |  |  |

|---|---|-----|--|--|

|   |   |     |  |  |

|   |   |     |  |  |

|   |   |     |  |  |

|   |   |     |  |  |

|   |   |     |  |  |

|   |   |     |  |  |

|   |   |     |  |  |

|   |   |     |  |  |

|   |   |     |  |  |

|   |   |     |  |  |

|   |   |     |  |  |

|   |   |     |  |  |

|   |   |     |  |  |

|   |   |     |  |  |

|   |   |     |  |  |

|   | - |     |  |  |

| 4 |   |     |  |  |

## Contents

| 1 | Introduction 1 |        |                                                  | 1  |

|---|----------------|--------|--------------------------------------------------|----|

| 2 | Bac            | kgroui | nd                                               | 5  |

|   | 2.1            | NASA   | Langley, SRI International, and Rockwell Collins | 5  |

|   | 2.2            | AAMI   | P Family of Microprocessors                      | 6  |

|   | 2.3            | PVS    |                                                  | 6  |

|   | 2.4            | Histor | ical Perspective and the Scale of the Challenge  | 8  |

| 3 | Pro            | ject G | oals and Organization                            | 9  |

| 4 | The            | Macr   | oarchitecture                                    | 13 |

|   | 4.1            | Overv  | iew of the AAMP Macroarchitecture                | 13 |

|   |                | 4.1.1  | Organization of Memory                           | 13 |

|   |                | 4.1.2  | Process Stack                                    | 14 |

|   |                | 4.1.3  | Internal Registers                               | 14 |

|   |                | 4.1.4  | Instruction Set and Memory Data Types            | 15 |

|   |                | 4.1.5  | Multi-Tasking and Error Handling                 | 17 |

|   | 4.2            | The M  | Tacroarchitecture Specification                  | 18 |

|   |                | 4.2.1  | Attributes of AAMP Instructions                  | 20 |

|   |                | 4.2.2  | Data and Code Memory                             | 21 |

|   |                | 4.2.3  | Macroarchitecture State                          | 23 |

|   |                | 4.2.4  | The Next State Function                          | 24 |

|   |                | 4.2.5  | Constructive vs. Descriptive Specifications      | 28 |

|   |     | 4.2.6   | The Stack Cache Abstraction                               | ξ.  |

|---|-----|---------|-----------------------------------------------------------|-----|

|   | 4.3 | Interr  | upts and Unrecoverable User Errors                        |     |

|   | 4.4 |         | opment of the Macroarchitecture Specification 3           |     |

|   |     | 4.4.1   | Initial Development                                       |     |

|   |     | 4.4.2   | Revision and Extension                                    |     |

|   |     | 4.4.3   |                                                           |     |

| 5 | The | e Micr  | oarchitecture 4                                           | .1  |

|   | 5.1 | The I   | Oata Processing Unit                                      | 2   |

|   |     | 5.1.1   | The Datapath 4                                            | 2   |

|   |     | 5.1.2   | The Microcontroller 4                                     | .4  |

|   |     | 5.1.3   | The Stack Cache and Stack Adjustment 4                    | . 4 |

|   | 5.2 | Forma   | d Specification of the Microarchitecture 4                | (   |

|   |     | 5.2.1   | DPU Specification                                         | 7   |

|   |     | 5.2.2   | DPU-LFU Interface 4                                       | ç   |

|   |     | 5.2.3   | DPU-BIU Interface                                         | 4   |

|   | 5.3 | Devel   | opment of the Microarchitecture Specification 5           | 5   |

|   |     | 5.3.1   | Initial Development                                       | 5   |

|   |     | 5.3.2   | Revision                                                  | 6   |

|   |     | 5.3.3   | Inspection                                                | 7   |

| 6 | For | mal Ve  | erification of AAMP5                                      | 9   |

|   | 6.1 | Gener   | al Microprocessor Correctness 5                           | 9   |

|   | 6.2 | Impac   | t of Pipelining and Asynchronous Memory Interface 6       | 2   |

|   | 6.3 | The A   | AMP5 Pipeline 6                                           | 4   |

|   |     | 6.3.1   | Normal Pipeline Operation 6                               | 5   |

|   |     | 6.3.2   | Pipeline Stalling and Delayed Jumps 6                     | 6   |

|   | 6.4 | Our A   | pproach to Verification                                   | 3   |

|   |     | 6.4.1   | The Verification Conditions                               | 1   |

|   |     |         | 6.4.1.1 Instruction-Specific Verification Conditions . 73 | 3   |

|   |     |         | 6.4.1.2 General Verification Conditions 76                | 3   |

|   |     | 6.4.2   | Bridging the Micro-Macro Gap                              | 3   |

|   | 6.5 | Mecha   | nization of Proofs of Verification Conditions 79          | 9   |

|   | 6.6 | Verific | ation of Interrupt Handling                               | 2   |

|   | 6.7 | Scope   | of the Verification Performed                             | 1   |

|   | 6.8 | Errors  | Discovered by the Verification Effort                     | 3   |

| 7  | Cor   | clusions and Lessons Learned            | 91 |

|----|-------|-----------------------------------------|----|

|    | 7.1   | Feasibility of Formal Verification      | 91 |

|    | 7.2   | Benefits of Formal Verification         | 92 |

|    | 7.3   | Cost of Formal Verification             | 92 |

|    | 7.4   | Transferring Formal Methods to Industry | 93 |

| Bi | bliog | raphy                                   | 96 |

## List of Figures

| 4.1 | The Process Stack                                          | . 5 |

|-----|------------------------------------------------------------|-----|

| 4.2 | Macroarchitecture Specification Hierarchy 1                | 9   |

| 4.3 | PVS Specification of Reference Instructions Attributes 2   |     |

| 4.4 | PVS Specification of AAMP Data Memory 2                    | 2   |

| 4.5 | The AAMP5 Macrostate (continues) 2                         | 3   |

| 4.5 | The AAMP5 Macrostate                                       | 4   |

| 4.6 | PVS Specification of Reference Instructions 2              | 5   |

| 4.7 | PVS Specification of Arithmetic Instructions (continues) 2 | 6   |

| 4.7 | PVS Specification of Arithmetic Instructions 2             | 7   |

| 4.8 | Effects of Stack Cache Abstraction                         | 2   |

| 5.1 | AAMP5 Block Diagram 4                                      | 1   |

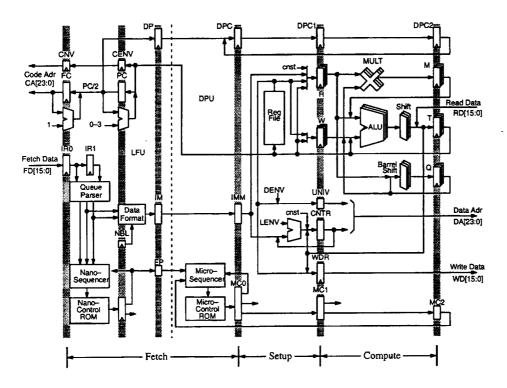

| 5.2 | The LFU and DPU Datapath 4                                 | 3   |

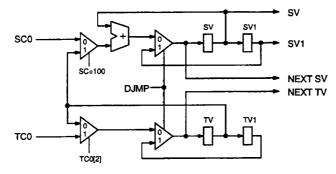

| 5.3 | SV and TV Logic                                            | 5   |

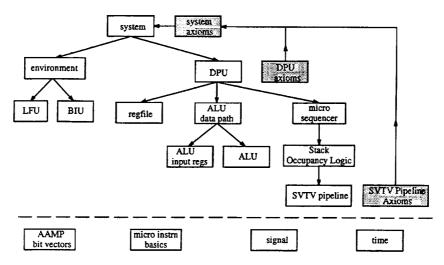

| 5.4 | Microarchitecture Specification Hierarchy 4                | 6   |

| 5.5 | Signals for the SV-TV Pipeline                             | 8   |

| 5.6 | Specification of the SV-TV Pipeline 56                     | 0   |

| 5.7 | DPU-LFU Interface Specification                            | 2   |

| 5.8 | DPU-BIU Interface Specification                            | 4   |

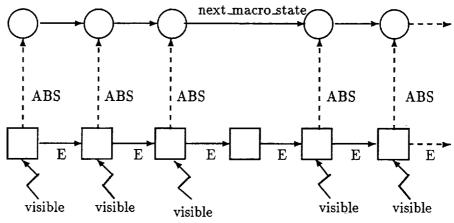

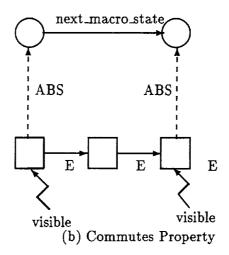

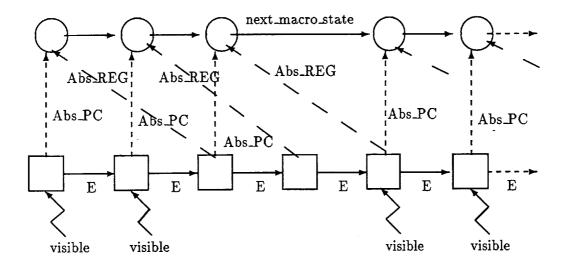

| 6.1 | General Microprocessor Correctness 60                      | D   |

| 6.2 | Impact of Pipelining on Abstraction 63                     | 3   |

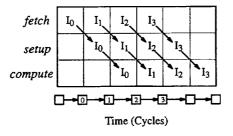

| 6.3 | Normal Pipeline Operation 68                               | 5   |

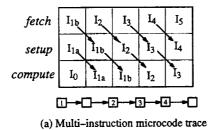

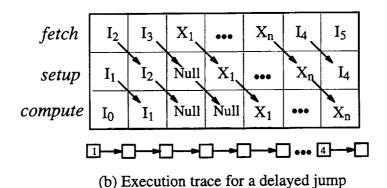

| 6.4 | Execution Traces for Pipeline Extension 67                 | 7   |

| 6.5 | Execution Traces for Pipeline Stalling 69                  | 9   |

| 6.6 | Verification Conditions for ADD                            | 4   |

| 6.7 | General Verification Conditions                            | 7   |

## Chapter 1

## Introduction

Software and digital hardware are increasingly being used in situations where failure could be life threatening, such as aircraft, nuclear power plants, weapon systems, and medical instrumentation. Several authors have demonstrated the infeasibility of showing that such systems meet ultra-high reliability requirements through testing alone [BF93,LS93]. Formal methods are a promising approach for increasing our confidence in digital systems, but many questions remain as to how it can be used effectively in an industrial setting.

This report describes a project, formal verification of the microcode in the AAMP5 microprocessor, conducted to explore how formal techniques for specification and verification could be introduced into an industrial process. Sponsored by the Systems Validation Branch of NASA Langley and Collins Commercial Avionics, a division of Rockwell International, it was conducted by Collins and the Computer Science Laboratory at SRI International. The project consisted of specifying in the PVS language developed by SRI [OSR93] a portion of a Rockwell proprietary microprocessor, the AAMP5, at both the instruction set and register-transfer levels and using the PVS theorem prover [ORS92, SOR93] to show that the microcode correctly implemented the specified behavior for a representative subset of instructions.

The central result of this project was to demonstrate the feasibility of formally specifying a commercial microprocessor and the use of mechanical proofs of correctness to verify microcode. This result is particularly significant since the AAMP5 was not designed for formal verification, but to

provide a more than threefold performance improvement while remaining object-code-compatible with the earlier AAMP2. As a consequence, the AAMP5 is one of the most complex microprocessors to which formal methods have been applied.

Besides demonstrating the verification of a subset of AAMP5 microcode, an equally important accomplishment of the project was the development of a methodology that can be used by practicing engineers to apply formal verification technology to a complex microprocessor design. This includes techniques for decomposing the microprocessor verification problem into a set of verification conditions that the engineers can formulate and strategies to automate the proof of the verification conditions.

This methodology was used to formally verify a core set of eleven AAMP5 instructions representative of several instruction classes. Although the number of instructions verified is small, the methodology and the formal machinery developed are adequate to cover most of the remaining AAMP5 microcode. The success of this project has lead to a sequel in which the same methodology is being reused to verify another member of the AAMP family.

Another key result was the discovery of both actual and seeded errors. Two actual microcode errors were discovered during development of the formal specification, illustrating the value of simply creating a precise specification. Two additional errors seeded by Collins in the microcode were systematically uncovered by SRI while doing correctness proofs. One of these was an actual error that had been discovered by Collins after first fabrication but left in the microcode provided to SRI. The other error was designed to be unlikely to be detected by walk-throughs, testing, or simulation.

Several other results emerged during the project, including the ease with which practicing engineers became comfortable with PVS, the need for libraries of general-purpose theories, the usefulness of formal specification in revealing errors, the natural fit between formal specification and inspections, the difficulty of selecting the best style of specification for a new problem domain, the high level of assurance provided by proofs of correctness, and the need to engineer proof strategies for reuse.

### Organization of the Report

This report is organized as follows. Chapter 2 provides general background, describing the participants in the project, the history of the AAMP family of microprocessors, the PVS specification language, and a brief survey of related work. Chapter 3 discusses the goals, organization, and history of the project. Chapter 4 describes the AAMP5 instruction set (macro) architecture, the PVS specification of the macroarchitecture, and how the specification was produced and validated. Chapter 5 provides a similar discussion of the AAMP5 register transfer (micro) architecture and its formal specification. Chapter 6 describes the formal verification effort, including an overview of the general approach to microprocessor verification and the impact of the AAMP5's pipelining and asynchronous memory interface on this model, a detailed discussion of our approach, and a summary of the errors found and the scope of the verification performed. Chapter 7 presents conclusions and lessons learned.

| Ĩ |  |   |    |

|---|--|---|----|

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  | - |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  | • |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   | ţ. |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

|   |  |   |    |

## Chapter 2

## Background

### 2.1 NASA Langley, SRI International, and Rockwell Collins

NASA Langley's research program in formal methods [But91] was established to bring formal methods technology to a sufficiently mature level for use by the United States aerospace industry. Besides the inhouse development of a formally verified reliable computing platform RCP [DBC90], NASA has sponsored a variety of demonstration projects to apply formal methods to critical subsystems of real aerospace computer systems.

The Computer Science Laboratory of SRI International has been involved in the development and application of formal methods for more than twenty years. The formal verification systems EHDM and the more advanced PVS were both developed at SRI. Both EHDM and PVS have been used to perform several verifications of significant difficulty, most notably in the field of fault-tolerant architectures and hardware designs. Recently, SRI has been actively involved in investigating ways to transfer formal verification technology to industry.

Collins Commercial Avionics is a division of Rockwell International and one of the largest suppliers of communications and avionics systems for commercial transport and general aviation aircraft. Collins' interest in formal methods dates from 1991 when it participated in the MCC Formal Methods Transition Study [GBG+91]. As a result of this study, Collins initiated

several small pilot projects to explore the use of formal methods, with verification of the AAMP5 microcode being the latest and most ambitious in the series.

### 2.2 AAMP Family of Microprocessors

The Advanced Architecture Microprocessor (AAMP) consists of a Rockwell proprietary family of microprocessors based on the Collins Adaptive Processor System (CAPS) originally developed in 1972 [Roc90, BKM+82]. The AAMP architecture is specifically designed for use with block-structured, high-level languages such as Ada in real-time embedded applications. It is based on a stack architecture and provides hardware support for many features normally provided by the compiler run-time environment, such as procedure state saving, parameter passage, return linkage, and reentrancy. The AAMP also simplifies the real-time executive by implementing in hardware such functions as interrupt handling, task state saving, and context switching. Use of internal registers holding the top few elements of the stack provides the AAMP family with performance that rivals or exceeds that of most commercially available 16-bit microprocessors.

The original CAPS architecture, a multiboard minicomputer, was developed in 1972 and was quickly followed by the CAPS-2 through CAPS-10. In 1981, the original AAMP consolidated all CAPS functions except memory on a single integrated circuit. It was followed by the AAMP2, AAMP3, and AAMP5. Members of the CAPS/AAMP family have been used in an impressive variety of products as shown in Table 2.1.

The AAMP5 was designed as an object-code-compatible replacement for the earlier AAMP2 [Roc90], with advanced implementation techniques such as pipelining providing a more than threefold performance improvement. The AAMP5 is designed for use in critical applications such as avionics displays, but is not intended for use in ultra-critical systems such as autoland or fly-by-wire.

### 2.3 PVS

PVS (Prototype Verification System) [SOR93] is an environment for specification and verification that has been developed at SRI International's

Table 2.1: Applications of the CAPS/AAMP Family

| CAPS-4 1974 Global Positioning System, General Development Model (GPS GDM)  CAPS-6 1977 Boeing 757, 767 Autopilot Flight Director System (AFDS) Lockheed L-1011 Active Control System (ACS) Lockheed L-1011 Digital Flight Control System (DFCS) NASA Fault Tolerant Multiprocessor (FTMP)  CAPS-8 1979 Boeing 757, 767 Electronic Flight Instrumentation System (EFIS) Boeing 757, 767 Engine Instrumentation/Crew Alerting System (EICAS)  CAPS-7 1979 Navstar Global Positioning System (GPS) Boeing 747-400 Integrated Display System (IDS)  CAPS-10 1979 Boeing 747-400 Central Maintenance Computer (CMC) Boeing 737-300 Electronic Flight Instrumentation System (EFIS)  AAMP1 1981 Boeing 737-300 Engine Instrumentation/Crew Alerting System (EICAS) Air Transport Traffic Collision Avoidance System (TCAS) Air Transport TCAS Vertical Speed Indicator (TVI) Boeing 777 Flight Control Backdrive Commercial GPS: Navcore I, Navcore V  AAMP3 1992 Boeing 777 Standby Instruments AAMP5 1993 Global Positioning Systems, Upgrade for AAMP2 |         |      | 2 12 11                                                  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|----------------------------------------------------------|--|

| CAPS-6 1977 Boeing 757, 767 Autopilot Flight Director System (AFDS) Lockheed L-1011 Active Control System (ACS) Lockheed L-1011 Digital Flight Control System (DFCS) NASA Fault Tolerant Multiprocessor (FTMP)  CAPS-8 1979 Boeing 757, 767 Electronic Flight Instrumentation System (EFIS) Boeing 757, 767 Engine Instrumentation/Crew Alerting System (EICAS)  CAPS-7 1979 Navstar Global Positioning System (GPS) Boeing 747-400 Integrated Display System (IDS)  CAPS-10 1979 Boeing 747-400 Central Maintenance Computer (CMC) Boeing 737-300 Electronic Flight Instrumentation System (EFIS)  AAMP1 1981 Boeing 737-300 Engine Instrumentation/Crew Alerting System (EICAS) Air Transport Traffic Collision Avoidance System (TCAS) Air Transport TCAS Vertical Speed Indicator (TVI) Boeing 777 Flight Control Backdrive Commercial GPS: Navcore I, Navcore II, Navcore V  AAMP3 1992 Boeing 777 Standby Instruments                                                                                                                          | CAPS-4  | 1974 | Global Positioning System, General Development Model     |  |

| (AFDS) Lockheed L-1011 Active Control System (ACS) Lockheed L-1011 Digital Flight Control System (DFCS) NASA Fault Tolerant Multiprocessor (FTMP)  CAPS-8 1979 Boeing 757, 767 Electronic Flight Instrumentation System (EFIS) Boeing 757, 767 Engine Instrumentation/Crew Alerting System (EICAS)  CAPS-7 1979 Navstar Global Positioning System (GPS) Boeing 747-400 Integrated Display System (IDS) Boeing 747-400 Central Maintenance Computer (CMC) Boeing 737-300 Electronic Flight Instrumentation System (EFIS)  AAMP1 1981 Boeing 737-300 Engine Instrumentation/Crew Alerting System (EICAS) Air Transport Traffic Collision Avoidance System (TCAS) Air Transport TCAS Vertical Speed Indicator (TVI) Boeing 777 Flight Control Backdrive Commercial GPS: Navcore I, Navcore V  AAMP3 1992 Boeing 777 Standby Instruments                                                                                                                                                                                                                 |         |      |                                                          |  |

| Lockheed L-1011 Active Control System (ACS) Lockheed L-1011 Digital Flight Control System (DFCS) NASA Fault Tolerant Multiprocessor (FTMP)  CAPS-8 1979 Boeing 757, 767 Electronic Flight Instrumentation System (EFIS) Boeing 757, 767 Engine Instrumentation/Crew Alerting System (EICAS)  CAPS-7 1979 Navstar Global Positioning System (GPS) Boeing 747-400 Integrated Display System (IDS)  CAPS-10 1979 Boeing 747-400 Central Maintenance Computer (CMC) Boeing 737-300 Electronic Flight Instrumentation System (EFIS)  AAMP1 1981 Boeing 737-300 Engine Instrumentation/Crew Alerting System (EICAS) Air Transport Traffic Collision Avoidance System (TCAS)  AAMP2 1987 Air Transport TCAS Vertical Speed Indicator (TVI) Boeing 777 Flight Control Backdrive Commercial GPS: Navcore I, Navcore V  AAMP3 1992 Boeing 777 Standby Instruments                                                                                                                                                                                              | CAPS-6  | 1977 | Boeing 757, 767 Autopilot Flight Director System         |  |

| Lockheed L-1011 Digital Flight Control System (DFCS) NASA Fault Tolerant Multiprocessor (FTMP)  CAPS-8 1979 Boeing 757, 767 Electronic Flight Instrumentation System (EFIS) Boeing 757, 767 Engine Instrumentation/Crew Alerting System (EICAS)  CAPS-7 1979 Navstar Global Positioning System (GPS) Boeing 747-400 Integrated Display System (IDS)  CAPS-10 1979 Boeing 747-400 Central Maintenance Computer (CMC) Boeing 737-300 Electronic Flight Instrumentation System (EFIS)  AAMP1 1981 Boeing 737-300 Engine Instrumentation/Crew Alerting System (EICAS) Air Transport Traffic Collision Avoidance System (TCAS) AAMP2 1987 Air Transport TCAS Vertical Speed Indicator (TVI) Boeing 777 Flight Control Backdrive Commercial GPS: Navcore I, Navcore V  AAMP3 1992 Boeing 777 Standby Instruments                                                                                                                                                                                                                                           |         |      |                                                          |  |

| NASA Fault Tolerant Multiprocessor (FTMP)  CAPS-8 1979 Boeing 757, 767 Electronic Flight Instrumentation System (EFIS) Boeing 757, 767 Engine Instrumentation/Crew Alerting System (EICAS)  CAPS-7 1979 Navstar Global Positioning System (GPS) Boeing 747-400 Integrated Display System (IDS) Boeing 747-400 Central Maintenance Computer (CMC) Boeing 737-300 Electronic Flight Instrumentation System (EFIS)  AAMP1 1981 Boeing 737-300 Engine Instrumentation/Crew Alerting System (EICAS) Air Transport Traffic Collision Avoidance System (TCAS) Air Transport TCAS Vertical Speed Indicator (TVI) Boeing 777 Flight Control Backdrive Commercial GPS: Navcore I, Navcore V  AAMP3 1992 Boeing 777 Standby Instruments                                                                                                                                                                                                                                                                                                                         |         |      |                                                          |  |

| CAPS-8 1979 Boeing 757, 767 Electronic Flight Instrumentation System (EFIS) Boeing 757, 767 Engine Instrumentation/Crew Alerting System (EICAS)  CAPS-7 1979 Navstar Global Positioning System (GPS) Boeing 747-400 Integrated Display System (IDS) Boeing 747-400 Central Maintenance Computer (CMC) Boeing 737-300 Electronic Flight Instrumentation System (EFIS)  AAMP1 1981 Boeing 737-300 Engine Instrumentation/Crew Alerting System (EICAS) Air Transport Traffic Collision Avoidance System (TCAS) Air Transport TCAS Vertical Speed Indicator (TVI) Boeing 777 Flight Control Backdrive Commercial GPS: Navcore I, Navcore V  AAMP3 1992 Boeing 777 Standby Instruments                                                                                                                                                                                                                                                                                                                                                                    |         |      | Lockheed L-1011 Digital Flight Control System (DFCS)     |  |

| (EFIS) Boeing 757, 767 Engine Instrumentation/Crew Alerting System (EICAS)  CAPS-7 1979 Navstar Global Positioning System (GPS) Boeing 747-400 Integrated Display System (IDS) Boeing 747-400 Central Maintenance Computer (CMC) Boeing 737-300 Electronic Flight Instrumentation System (EFIS)  AAMP1 1981 Boeing 737-300 Engine Instrumentation/Crew Alerting System (EICAS) Air Transport Traffic Collision Avoidance System (TCAS) Air Transport TCAS Vertical Speed Indicator (TVI) Boeing 777 Flight Control Backdrive Commercial GPS: Navcore I, Navcore V  AAMP3 1992 Boeing 777 Standby Instruments                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |      |                                                          |  |

| Boeing 757, 767 Engine Instrumentation/Crew Alerting System (EICAS)  CAPS-7 1979 Navstar Global Positioning System (GPS) Boeing 747-400 Integrated Display System (IDS)  Boeing 747-400 Central Maintenance Computer (CMC) Boeing 737-300 Electronic Flight Instrumentation System (EFIS)  AAMP1 1981 Boeing 737-300 Engine Instrumentation/Crew Alerting System (EICAS) Air Transport Traffic Collision Avoidance System (TCAS)  AAMP2 1987 Air Transport TCAS Vertical Speed Indicator (TVI) Boeing 777 Flight Control Backdrive Commercial GPS: Navcore I, Navcore V  AAMP3 1992 Boeing 777 Standby Instruments                                                                                                                                                                                                                                                                                                                                                                                                                                   | CAPS-8  | 1979 | Boeing 757, 767 Electronic Flight Instrumentation System |  |

| System (EICAS)  CAPS-7 1979 Navstar Global Positioning System (GPS) Boeing 747-400 Integrated Display System (IDS)  CAPS-10 1979 Boeing 747-400 Central Maintenance Computer (CMC) Boeing 737-300 Electronic Flight Instrumentation System (EFIS)  AAMP1 1981 Boeing 737-300 Engine Instrumentation/Crew Alerting System (EICAS) Air Transport Traffic Collision Avoidance System (TCAS) Air Transport TCAS Vertical Speed Indicator (TVI) Boeing 777 Flight Control Backdrive Commercial GPS: Navcore I, Navcore V  AAMP3 1992 Boeing 777 Standby Instruments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |      |                                                          |  |

| CAPS-7 1979 Navstar Global Positioning System (GPS) Boeing 747-400 Integrated Display System (IDS) Boeing 747-400 Central Maintenance Computer (CMC) Boeing 737-300 Electronic Flight Instrumentation System (EFIS)  AAMP1 1981 Boeing 737-300 Engine Instrumentation/Crew Alerting System (EICAS) Air Transport Traffic Collision Avoidance System (TCAS) Air Transport TCAS Vertical Speed Indicator (TVI) Boeing 777 Flight Control Backdrive Commercial GPS: Navcore I, Navcore V  AAMP3 1992 Boeing 777 Standby Instruments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |      | Boeing 757, 767 Engine Instrumentation/Crew Alerting     |  |

| Boeing 747-400 Integrated Display System (IDS) Boeing 747-400 Central Maintenance Computer (CMC) Boeing 737-300 Electronic Flight Instrumentation System (EFIS)  AAMP1 1981 Boeing 737-300 Engine Instrumentation/Crew Alerting System (EICAS) Air Transport Traffic Collision Avoidance System (TCAS) Air Transport TCAS Vertical Speed Indicator (TVI) Boeing 777 Flight Control Backdrive Commercial GPS: Navcore I, Navcore V  AAMP3 1992 Boeing 777 Standby Instruments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |      |                                                          |  |

| CAPS-10 1979 Boeing 747-400 Central Maintenance Computer (CMC) Boeing 737-300 Electronic Flight Instrumentation System (EFIS)  AAMP1 1981 Boeing 737-300 Engine Instrumentation/Crew Alerting System (EICAS) Air Transport Traffic Collision Avoidance System (TCAS) Air Transport TCAS Vertical Speed Indicator (TVI) Boeing 777 Flight Control Backdrive Commercial GPS: Navcore I, Navcore V  AAMP3 1992 Boeing 777 Standby Instruments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CAPS-7  | 1979 |                                                          |  |

| Boeing 737-300 Electronic Flight Instrumentation System (EFIS)  Boeing 737-300 Engine Instrumentation/Crew Alerting System (EICAS) Air Transport Traffic Collision Avoidance System (TCAS)  AAMP2 1987 Air Transport TCAS Vertical Speed Indicator (TVI) Boeing 777 Flight Control Backdrive Commercial GPS: Navcore I, Navcore V  AAMP3 1992 Boeing 777 Standby Instruments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |      |                                                          |  |

| AAMP1 1981 Boeing 737-300 Engine Instrumentation/Crew Alerting System (EICAS) Air Transport Traffic Collision Avoidance System (TCAS) Air Transport TCAS Vertical Speed Indicator (TVI) Boeing 777 Flight Control Backdrive Commercial GPS: Navcore I, Navcore V  AAMP3 1992 Boeing 777 Standby Instruments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CAPS-10 | 1979 |                                                          |  |

| AAMP1 1981 Boeing 737-300 Engine Instrumentation/Crew Alerting System (EICAS) Air Transport Traffic Collision Avoidance System (TCAS) Air Transport TCAS Vertical Speed Indicator (TVI) Boeing 777 Flight Control Backdrive Commercial GPS: Navcore I, Navcore V  AAMP3 1992 Boeing 777 Standby Instruments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |      | •                                                        |  |

| System (EICAS) Air Transport Traffic Collision Avoidance System (TCAS)  Air Transport TCAS Vertical Speed Indicator (TVI) Boeing 777 Flight Control Backdrive Commercial GPS: Navcore I, Navcore V  AAMP3 1992 Boeing 777 Standby Instruments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | AAMP1   | 1981 |                                                          |  |

| Air Transport Traffic Collision Avoidance System (TCAS)  Air Transport TCAS Vertical Speed Indicator (TVI)  Boeing 777 Flight Control Backdrive  Commercial GPS: Navcore I, Navcore V  AAMP3 1992 Boeing 777 Standby Instruments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | AAMI    | 1301 |                                                          |  |

| AAMP2 1987 Air Transport TCAS Vertical Speed Indicator (TVI) Boeing 777 Flight Control Backdrive Commercial GPS: Navcore I, Navcore V  AAMP3 1992 Boeing 777 Standby Instruments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1       |      |                                                          |  |

| Commercial GPS: Navcore I, Navcore II, Navcore V  AAMP3 1992 Boeing 777 Standby Instruments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | AAMP2   | 1987 |                                                          |  |

| Commercial GPS: Navcore I, Navcore II, Navcore V  AAMP3 1992 Boeing 777 Standby Instruments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |      |                                                          |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |      |                                                          |  |

| AAMP5 1993 Global Positioning Systems, Upgrade for AAMP2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | AAMP3   | 1992 | Boeing 777 Standby Instruments                           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | AAMP5   | 1993 | Global Positioning Systems, Upgrade for AAMP2            |  |

Computer Science Laboratory. In comparison to other widely used verification systems, such as HOL [GM93] and the Boyer-Moore prover [BM79], the distinguishing characteristic of PVS is that it supports both a highly expressive specification language and a very effective interactive theorem prover in which most of the low-level proof steps are automated. The system consists of a specification language, a parser, a typechecker, and an interactive proof checker. The PVS specification language is based on higher-order logic with a richly expressive type system so that a number of semantic errors in specification can be caught by the typechecker. The PVS prover consists of a powerful collection of inference steps that can be used to reduce a proof goal to simpler subgoals that can be discharged automatically by the primitive proof steps of the prover. The primitive proof steps involve, among other

things, the use of arithmetic and equality decision procedures, automatic rewriting, and BDD-based boolean simplification.

## 2.4 Historical Perspective and the Scale of the Challenge

Microprogram verification has much in common with processor verification, in that both relate the programmer's view of a processor to its hardware implementation. A number of microprocessor designs have been formally verified [BB94, Hun94, CJB78, Coo86, SGGH94, SB90, Win90]. However, the AAMP5 is significantly more complex, at both the macro and microarchitecture levels, than any other processor for which formal verification has been attempted; it has a large, complex instruction set, multiple data types and addressing modes, and a microcoded, pipelined implementation. Of these, the pipeline and autonomous instruction and data fetching present special challenges. One measure of the complexity of a processor is the size of its implementation. In the case of the AAMP5, this is some 500,000 transistors, compared with some tens of thousands in previous formally verified designs and 3.1 million in an Intel Pentium [Int93].

Microcode verification is not new: it was pioneered by Bill Carter [LCB74] at IBM in the 1970's and applied to elements of NASA's Standard Spaceborne Computer [LCB74]; in the 1980's a group at the Aerospace Corporation verified microcode for an implementation of the C/30 switching computer using a verification system called SDVS [Coo86]; and a group at Inmos in the UK established correctness across two levels of description (in Occam) of the microcode for the T800 floating-point unit using mechanized transformations. Similarly, several groups have performed automated verification of non-microcoded processors, of which Warren Hunt's FM8501 [Hun94] and subsequent FM9000 [HB92] are among the most substantial. The problems of pipeline correctness were also studied previously by Srivas and Bickford [SB90], by Saxe and Garland [SGGH94], Burch and Dill [BD94], and Windley and Coe [WC94]. A very simple microcoded processor design developed by Mike Gordon called "Tamarack" serves as something of a benchmark for microprogram verification and was considered quite a challenge not so long ago [Joy88]. PVS is able to verify the microcode of Tamarack and Saxe's pipelined processor completely automatically in about five minutes [CRSS94].

## Chapter 3

## Project Goals and Organization

Formal verification of the AAMP5 microcode was selected for this project for a number of reasons. Both Collins and SRI wanted to explore the usefulness of formal verification on an example that was large enough to provide realistic insight, yet small enough to be completed at reasonable cost. Verification of the AAMP5 microcode fit these criteria well. While the AAMP5 was one of the most complex microprocessors Collins had built, its requirements were well understood since it was to be object-code-compatible with the earlier AAMP2. This allowed the formal methods team to concentrate on formal specification and verification rather than on designing a new product. Also, much of the complexity of an AAMP microprocessor resides in the microcode, and past experience has shown that this is one of the most difficult parts of the microprocessor to get right. Success with formal verification in other significant projects suggested that this technology might be ready for application to an industrial microprocessor.

Because of the importance of the AAMP5 to Collins' product line, the formal specification and verification of the AAMP5 were performed as a shadow project and did not replace any of the normal design and verification activities performed on a new microprocessor. This parallel approach also allowed us to relax some of the steps that would be required on a production project and focus instead on the application of formal methods. To fit the scope of the project to the time available, a core set of 13 instructions, each representative of a class of AAMP instructions, was identified to be specified

and verified by SRI. An additional set of 11 instructions was identified to be specified and verified by Collins as time permitted. Even so, it was necessary to specify the entire AAMP5 architecture and develop the infrastructure needed to verify the entire instruction set since the core set contained at least one member from each of the major instruction classes.

Staffing for the project was provided by SRI and Collins, with funding provided by NASA and Collins. SRI provided one formal methods expert full time for the project's duration while Collins provided approximately one full-time equivalent split among several engineers. A project plan was developed at the start of the project identifying goals, strategies, tasks, and schedules. This plan was updated periodically and level of effort was recorded by both SRI and Collins personnel on each task. A summary of the level of effort is presented in Table 3.1 (page 12).

As shown in Table 3.1, relatively little time was spent on training the Collins' engineers in PVS. The small amount of structured training needed was one of the surprises of the project. Early on, SRI conducted a one-week course on the use of PVS and formal specifications at the Collins Cedar Rapids facility for the five engineers who would be involved with the project. The course consisted of five half-day lectures with related lab exercises in the afternoon. No additional formal training seemed necessary. When new team members joined the project, they were provided access to the PVS documentation and trained by inclusion in review of the PVS specifications. The most effective form of education seemed to be hands-on development with frequent peer review.

Aside from overall management and education, the project split naturally into three phases: specification of the macroarchitecture (Chapter 4), specification of the microarchitecture (Chapter 5), and proofs of correctness of the microcode (Chapter 6). The basic process followed in the first two phases was that Collins would provide design specifications to SRI, SRI would provide first drafts of PVS specifications to Collins, and Collins would informally review these specifications and return comments to SRI for revision. At some point, the Collins team would take the specifications, prepare them for formal inspections [Fag86], conduct the inspections, correct the defects found, and send the revised specifications back to SRI. This approach was chosen both to validate the correctness of the specifications and to ensure that Collins personnel became actively involved in developing the PVS specifications. A similar process was followed for performing proofs

of correctness of the microcode, with SRI providing the first examples and strategies that Collins would use on similar instructions.

To reduce the potential for missing errors in the microcode due to errors in the PVS specifications, independent teams were assigned to different portions of the project. While all early drafts of the specifications were produced by SRI, different individuals at Collins were assigned to review and revise the macroarchitecture and microarchitecture specifications. Different teams were also used to inspect the macroarchitecture and the microarchitecture. The microcode itself was produced by a member of the original AAMP5 team without any knowledge of the formal specifications and translated into PVS by yet another individual. As a result, the process of proving the microcode correct often revealed errors in the specifications, but once a proof was completed, confidence in the correctness of the associated microcode was high.

Table 3.1: Level of Effort

| Task                                | Performed     | Start     | Stop         | Hours                                   |  |

|-------------------------------------|---------------|-----------|--------------|-----------------------------------------|--|

| Project Management                  |               |           |              |                                         |  |

| Planning & Monitoring               | Collins       | Jan 93    | Aug 94       | 123                                     |  |

| Education                           |               | ·         | <del>1</del> | <u> </u>                                |  |

| PVS Course                          | Collins       | Feb 93    | Feb 93       | 125                                     |  |

|                                     | SRI           | Feb 93    | Feb 93       | 68                                      |  |

| Specification of the Macroarchitect | ure (2,550 L  | ines of P | VS)          | * · · · · · · · · · · · · · · · · · · · |  |

| Initial Development                 | Collins       | Mar 93    | May 93       | 172                                     |  |

|                                     | SRI           | Mar 93    | May 93       | 360                                     |  |

| Revision & Extension                | Collins       | May 93    | Sept 93      | 289                                     |  |

|                                     | SRI           | May 93    | Sept 93      | 120                                     |  |

| Inspection                          | Collins       | Sept 93   | Feb 94       | 96                                      |  |

| Resolve Inspection Issues           | Collins       | Feb 94    | May 94       | 64                                      |  |

| Revision to Support Proofs          | Collins       | Mar 94    | Aug 94       | 54                                      |  |

| Specification of the Microarchitect | ure (2,679 Li | nes of P  | VS)          |                                         |  |

| Initial Development                 | Collins       | May 93    | Feb 94       | 137                                     |  |

|                                     | SRI           | May 93    | Feb 94       | 520                                     |  |

| Revision                            | Collins       | Feb 94    | Aug 94       | 160                                     |  |

|                                     | SRI           | Feb 94    | Aug 94       | 120                                     |  |

| Inspection                          | Collins       | Mar 94    | Aug 94       | 83                                      |  |

| Resolve Inspection Issues           | Collins       | Mar 94    | Aug 94       | 66                                      |  |

| Translate Microcode to PVS          | Collins       | Jun 94    | Aug 94       | 21                                      |  |

| Revision to Support Proofs          | Collins       | Jun 94    | Aug 94       | 12                                      |  |

| Proofs of Correctness               |               |           |              |                                         |  |

| Development of Correctness Criteria | SRI           | Mar 94    | Jun 94       | 320                                     |  |

| Developing Proof Infrastructure     | SRI           | May 94    | Aug 94       | 240                                     |  |

| Verification of Core Instructions   | SRI           | Jun 94    | Aug 94       | 240                                     |  |

## Chapter 4

# The Macroarchitecture: The Programmer's View of the AAMP5

### 4.1 Overview of the AAMP Macroarchitecture

Important features of the AAMP macroarchitecture include its organization of memory, process stack, internal registers that affect its observable behavior, instruction set, and support for multi-tasking and error handling. These are discussed in the following sections. A more detailed discussion can be found in [BKM<sup>+</sup>82].

### 4.1.1 Organization of Memory

The AAMP provides separate address spaces for code memory and data memory. While not required by the AAMP architecture, code memory is typically implemented in ROM. Both code and data memory are segmented, with code memory organized into 512 code environments, each containing 64K 8-bit bytes of code. Data memory is organized into 256 data environments, each containing 64K 16-bit words of data. Actual memory addresses are formed by concatenating a 9-bit code environment pointer (CENV) with a 16-bit program counter for instruction addresses, or an 8-bit data environment pointer (DENV) with a 16-bit offset for data addresses. The processor also provides data-transfer status lines which can be used by an

external memory management unit for protection against improper accesses to memory, allowing code fetches to be distinguished from data accesses and executive task accesses to be distinguished from user task accesses.

### 4.1.2 Process Stack

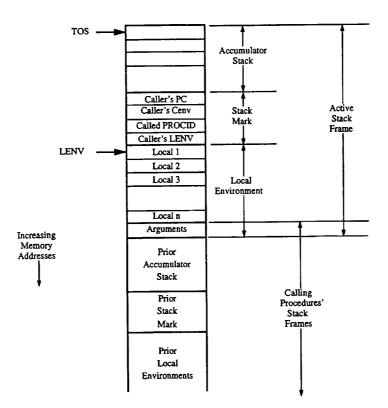

The process stack is central to the AAMP macroarchitecture, implementing in hardware many of the features needed to support high-level block structured languages and multi-tasking. Each task maintains a single process stack in the task's data environment, illustrated in Figure 4.1. At the top of the process stack is the accumulator stack used for manipulation of instruction operands and pointers. Directly below the accumulator stack is the stack mark of the current procedure. The stack mark contains the information needed to restore the calling procedure upon return from the current procedure, to access local variables within the calling procedure, and to locate the current procedure's header and executable code.

Below the stack mark is the current procedure's local environment consisting of its local variables and any parameters passed from the calling procedure. A procedure's local environment, stack mark, and accumulator stack form a stack frame. Beneath the current procedure's stack frame is the frame of its calling procedure, and so on. Note that the stack grows downward towards decreasing memory addresses.

### 4.1.3 Internal Registers

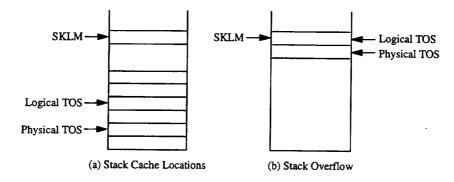

Many of the internal registers maintained by the AAMP are used to define the process stack. The DENV (data environment) register contains the pointer to the data environment of the current active task. The TOS (top of stack) register points to the topmost word in the process stack and the SKLM (stack limit) register points to the lower limit beyond which the stack is not allowed to grow. The LENV (local environment) register points to the local environment of the current procedure and is used in addressing local variables. The CENV (code environment) and PC (program counter) registers point to the code environment and address of the next instruction to be executed. Finally, the AAMP maintains two boolean flags, a USER flag to indicate whether the processor is in user or executive mode, and the INTE flag indicating whether or not the maskable interrupt is enabled (see Section 4.1.5).

Figure 4.1: The Process Stack

### 4.1.4 Instruction Set and Memory Data Types

The AAMP instruction set is large and CISC-like. It closely resembles the intermediate-level output of many compilers, directly supporting high-level language constructs such as procedure calls and returns. The instructions vary in length from 8 to 56 bits, although most are only 8 bits long, yielding improved throughput and code density.

The instruction set supports a variety of data types, including 16- and 32-bit integer, 16- and 32-bit fractional, 32- and 48-bit floating-point, and 16-bit logical variables. The floating-point formats have an 8-bit, excess-128 exponent and, respectively, 24 and 40 bits of fractional mantissa. Addition, subtraction, multiplication, division, and type conversions are provided for all of the arithmetic types. Computational exceptions, such as arithmetic overflow and divide-by-zero, are detected and handled automatically.

The original AAMP had 153 instructions. The AAMP5 has 209, which can be divided into several classes, as shown in Table 4.1. Of these, 72 are Reference or Assign instructions that move data between the top of the process stack and data memory. The Logical, Arithmetic, Relational, Type Conversion, Shift, Rotate, and Field classes account for another 81 instructions, each of which performs a prescribed operation on the top few elements of the process stack and pushes the result back onto the stack. An additional 20 instructions deal with program control, such as branch, loop, call, and return instructions. The remaining 31 instructions are used for block data memory transfers, pushing literals on the stack, locating operands in the stack, and miscellaneous functions.

Table 4.1: Instruction Classes

| Instruction Class        |                                       | Number of<br>Instructions |

|--------------------------|---------------------------------------|---------------------------|

| Stack Managemen          | t                                     | 8                         |

| Literal Data             | · · · · · · · · · · · · · · · · · · · | 8                         |

| Reference Data           |                                       | 36                        |

| Assign Data              |                                       | 36                        |

| Mutual Exclusion         | Synchronization                       | 1                         |

| Operand Location         |                                       | 5                         |

| Logical                  |                                       | 8                         |

| Arithmetic               |                                       | 43                        |

| Relational               |                                       | 11                        |

| Type Conversion          |                                       | 9                         |

| Shift, Rotate, and Field |                                       | 10                        |

| Program Control          | Branch                                | 7                         |

|                          | Call                                  | 5                         |

|                          | Case                                  | 1                         |

|                          | Exception                             | 1                         |

|                          | Halt                                  | 1                         |

|                          | Loop                                  | 2                         |

|                          | Return                                | 2                         |

| Trap                     |                                       | 1                         |

| Block Data               |                                       | 12                        |

| Miscellaneous            |                                       | 2                         |

### 4.1.5 Multi-Tasking and Error Handling

The AAMP stack architecture is designed for real-time multi-tasking applications, wherein the processor is time-shared among two or more concurrent tasks. Each task maintains its own process stack in its assigned data environment. Most multitasking operations, including context switching, are performed automatically by the AAMP. Since many errors generate a context switch to executive mode, the multi-tasking and error-handling features of the AAMP are closely intertwined.

Scheduling of user tasks is performed by an executive task assigned to code environment 0 and data environment 0. During execution, the executive selects one of several user tasks to be activated or resumed, then executes a RETURN instruction from its outer procedure. This causes the AAMP to transfer control to the selected user task. Normal execution of a user task can be suspended by an exception, an external interrupt, a trap, or an outer procedure return.

Exceptions are erroneous events, such as arithmetic overflow, that are primarily relevant to the currently executing user task. These are handled by the AAMP within the context of the user task, i.e., a context switch to the executive is not initiated. When an exception is detected, the exception error code is placed on the task's process stack and the AAMP calls the appropriate exception handler.

External hardware interrupts and traps differ from exceptions in that they are handled in executive mode and initiate a transfer of control to the executive, which schedules the appropriate interrupt or trap handler. External interrupts may arrive at any time during an instruction execution, and are recognized on master clock boundaries. Four interrupts are supported. Reset (RST) and memory transfer errors (XER) are processed immediately. The maskable interrupt (IRQ) and the nonmaskable interrupt (NMI) are held pending completion of the current instruction.

Traps are handled in a manner very similar to interrupts, initiating a context switch to the executive, which schedules the appropriate trap handler. Traps come in two varieties. A "hardware" trap is generated when the AAMP detects an error that must be processed in executive mode, such as stack overflow. "Software" traps are generated when the user process executes a TRAP instruction to request an executive service such as masking interrupts or transfering control to another user task. A user task may also

suspend its execution by executing an outer procedure return. An outer procedure return from a user task is handled in the same way as a trap.

Finally, normal execution of the executive can be suspended by detection of an unrecoverable error, such as overflow of the executive stack, while in executive mode. Such errors initiate a context switch to the executive error handler. If the executive error handler is undefined or an unrecoverable error is detected while in the executive error handler, the AAMP is forced into an idle loop pending a reset.

### 4.2 The Macroarchitecture Specification

The macroarchitecture specification formalizes an assembly-level programmer's view of the AAMP and its instruction set, hiding most of the internal state and pipelining of the processor. The PVS specification of the AAMP models the processor as a state machine: the state of the macromachine includes external memory and the internal state that affects its observable behavior, such as the internal registers defining the process stack; the next state function specifies the effect of executing the "current" instruction pointed to by the program counter.

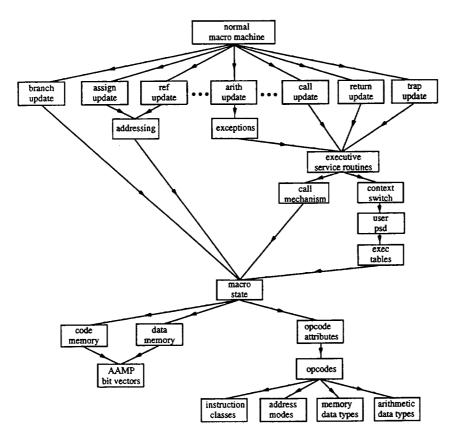

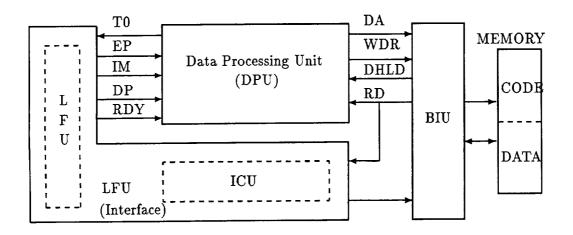

An overview of the *import chain* for the macroarchitecture specification is shown in Figure 4.2. In PVS, a theory gains access to another theory's definitions and axioms by *importing* that theory. Each box in the figure represents a theory in the specification. Importation of a theory is depicted by an arrow from the importing theory to the imported theory.

At the topmost level is the normal\_macro\_machine theory that defines the behavior of the AAMP in the absence of interrupts and unrecoverable errors such as stack overflow (handling of these is discussed in Section 4.3). The next\_macro\_state function for each instruction class is specified in an update theory for that class. Some instructions, such as the branch instructions, are simple enough that they can be defined directly in terms of changes to the macromachine state defined in the macro\_state theory. More complex instructions require additional definitions provided in supporting theories. For example, the assign (assignment) and ref (reference) instructions import the addressing theory that determines the source or target data memory address based on the addressing mode of the current instruction. Instructions that can raise exceptions require the definitions found in the exceptions theory. CALL, RETURN, and instructions that

Figure 4.2: Macroarchitecture Specification Hierarchy

require executive services cause the most complex changes to the macrostate and import a family of theories defining the executive services provided by the AAMP.

The macro\_state theory defines the state of the macromachine and functions useful in manipulating that state. This includes the internal registers that affect the observable behavior of the AAMP and instantiations of memory defined in the code\_memory and data\_memory theories. The AAMP\_bit\_vectors theory imports the bit\_vectors library, adding to it the specific bit vectors found in the AAMP such as words and bytes. To simplify the import chain, the macro\_state theory also imports the enumeration of the instructions, or opcodes, of the AAMP and their attributes. Representative samples of this hierarchy are discussed in the following sections, beginning with the theories lowest in the hierarchy. It should be noted that

the PVS theories shown in this report have been edited to remove material not relevant to the text.

### 4.2.1 Attributes of AAMP Instructions

The opcodes\_attributes theory is actually partitioned into a family of theories, one for each instruction class. The attributes of each instruction are specified as functions over the uninterpreted type opcodes. Specific values for each instruction are given in a theory similar to that shown in Figure 4.3. This theory defines two of the reference instructions, REFS and REFDL, as constants of type opcodes and defines the attributes of instruction class, memory data type, address mode, length of the instruction and immediate data in code memory, and the number of words of address information expected on the top of the stack prior to execution.

Care must be taken when using this form of specification to ensure that inconsistent axioms are not introduced. For example, it would be relatively easy to insert the wrong opcode in an axiom and inadvertently declare that opcode to have two different values for the same attribute. Originally, the opcodes category was declared as a PVS enumerated type and the attributes were specified as case analysis over the constants of the type. This form of specification ensured that PVS would detect such inconsistencies. However, early versions of PVS did not provide efficient support for large enumerated types. As the size of the macro and microarchitecture specifications grew, the definition of opcodes as enumerated types became cumbersome enough to justify switching to the declarative style shown in Figure 4.3. More recent versions of PVS have resolved this issue and provide efficient support for large enumerated types.

It is also worth noting that the preferred form of specification for the instruction attributes would be one or more "tables", with PVS internally generating the axioms describing the tables and checking to ensure their consistency. Such a construct has been added to the latest version of PVS.

```

% Defines the attributes of the reference instructions.

opcodes_attributes_reference: THEORY

BEGIN

IMPORTING opcodes

% REFS - Reference Absolute - Single Word

REFS: opcodes

= reference

: AXIOM instruction_class_of(REFS)

REFS_class

: AXIOM memory_data_type_of(REFS)

= single

REFS_mdt

: AXIOM address_mode_of(REFS)

= absolute

REFS_amode

: AXIOM length_of_instruction(REFS)

= 1

REFS_length

: AXIOM number_of_stack_words(REFS)

= 1

REFS_nstkwds

% REFDL - Reference Local Environment - Double Word

REFDL: opcodes

= reference

: AXIOM instruction_class_of(REFDL)

REFDL_class

= double

: AXIOM memory_data_type_of(REFDL)

REFDL_mdt

= local

: AXIOM address_mode_of(REFDL)

REFDL_amode

REFDL_length : AXIOM length_of_instruction(REFDL)

= 1

: AXIOM number_of_stack_words(REFDL)

= 0

REFDL_nstkwds

end opcodes_attributes_reference

```

Figure 4.3: PVS Specification of Reference Instructions Attributes

### 4.2.2 Data and Code Memory

The PVS specification of data memory is shown in Figure 4.4. AAMP data memory is organized into 256 possible data environments, each containing 64K 16-bit words of data. Data memory itself is defined as a function from 8-bit data environment pointers to data environments, where each data environment is another function from 16-bit data environment addresses to 16-bit words of memory. Standard bit vectors used in the AAMP, such as 16-bit words, are defined in the imported AAMP\_bit\_vectors theory, which also defines operations over bit vectors such as concatenation and extraction of bits. The specification of data memory also introduces unspecified constants

```

% The data_memory theory defines the AAMP's view of data memory.

% Data memory is organized into 256 possible data environments,

% each addressed by an 8-bit data environment pointer.

% Each data environment contains 64K words of data,

% each addressed by a 16-bit data environment relative address.

data_memory: THEORY

BEGIN

IMPORTING AAMP_bit_vectors

% A data environment address is a 16-bit word.

data_env_addr: TYPE = word

% An unspecified constant data environment address

unspecified_data_env_addr: data_env_addr

% A data environment is a function from data environment addresses

% to words of memory.

data_env: TYPE = [data_env_addr -> word]

% A data environment pointer is a bit vector of size 8.

data_env_ptr: TYPE = bvec[8]

% An unspecified constant data environment pointer.

unspecified_data_env_ptr: data_env_ptr

% Data memory is defined as a function from data environment pointers

% to data environments.

data_memory: TYPE = [data_env_ptr -> data_env]

% Converts a word to a data environment pointer.

word2denv(wd: word): data_env_ptr = wd^(7,0)

% Converts a data environment pointer to a word.

denv2word(denv: data_env_ptr): word = zero_extend[8](16)(denv)

END data_memory

```

Figure 4.4: PVS Specification of AAMP Data Memory

of type data environment pointer and data environment address used in later theories.

The specification of code memory is similar except that code memory is organized into 512 possible code environments, each containing 64K 8-bit bytes.

### 4.2.3 Macroarchitecture State