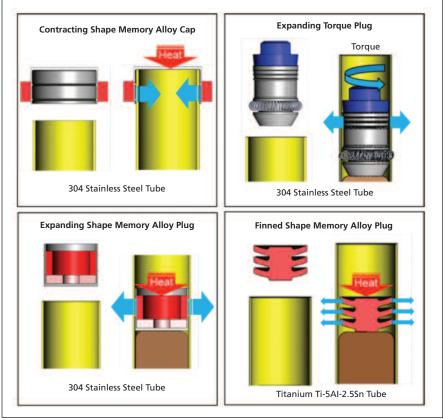

The finned shape memory alloy (SMA) plug currently shows hermetic sealing capability based on preliminary tests. The finned SMA plug sealing technique requires a heater to actuate the plug. Materials have been selected to comply with current sample compatibility, contamination control, and planetary protection concerns. Various Nitinol SMA chemistries are currently being investigated that allow the seal to start activating at temperatures as low as 45 °C (if low-temperature sealing is required for sample integrity), and as high as 135 °C (if planetary protection dry heat microbial reduction is required).

The contracting shape memory alloy cap requires a heater to actuate an SMA ring that swages the toothed cap onto the outside of the tube. The expanding SMA plug also requires a heater to actuate a ring that swages the toothed cap into the inside of the tube.

The benefit to the expanding torque plug is that no heat is required to create a seal. All that is needed is a rotating actuator to actuate the plug.

This work was done by Paulo J. Younse of Caltech for NASA's Jet Propulsion Laboratory. Further information is contained in a TSP (see page 1). NPO-48927

Potential hermetic Sample Sealing Techniques include a contracting shape memory alloy cap, expanding torque plug, expanding shape memory alloy plug, and a finned shape memory alloy plug.

## Silicon Alignment Pins: An Easy Way To Realize a Wafer-to-Wafer Alignment

## Etched pockets and silicon pins are used to align two wafers together.

NASA's Jet Propulsion Laboratory, Pasadena, California

Submillimeter heterodyne instruments play a critical role in addressing fundamental questions regarding the evolution of galaxies as well as being a crucial tool in planetary science. To make these instruments compatible with small platforms, especially for the study of the outer planets, or to enable the development of multi-pixel arrays, it is essential to reduce the mass, power, and volume of the existing single-pixel heterodyne receivers.

Silicon micromachining technology is naturally suited for making these submillimeter and terahertz components, where precision and accuracy are essential. Waveguide and channel cavities are etched in a silicon bulk material using deep reactive ion etching (DRIE) techniques. Power amplifiers, multiplier and mixer chips are then in-

tegrated and the silicon pieces are stacked together to form a supercompact receiver front end. By using silicon micromachined packages for these components, instrument mass can be reduced and higher levels of integration can be achieved.

A method is needed to assemble accurately these silicon pieces together, and a technique was developed here using etched pockets and silicon pins to align two wafers together. Each silicon piece is patterned with the pockets on both sides of the wafer, front and back, which are then etched down to  $\approx 130~\mu m$ .

Meanwhile, the silicon pins are etched in a 200-µm thick wafer. By etching a C-shaped pin, the pin can be compressed to fit into the alignment pocket by an appropriate choice of the pin wall thickness. When released, the pin ex-

pands to fill the pocket. A tight fit is ensured by choosing the relaxed pin diameter to be greater than the pocket diameter. This approach reduces the misalignment tolerance to the positional variation between the photolithographically defined pockets, which is typically under 3  $\mu$ m.

During assembly, the silicon compression pins are placed on the etched pockets of the first wafer, and the wafer to be aligned will find the right location using its own "back" etched pockets. The two wafers are therefore quickly and easily aligned. If more wafers need to be stacked, one can place additional layers, each time using the pins and the etched pockets as alignment features.

Using this method, one can align several wafers, if needed, by only handling and aligning two wafers at a time. Also, for accurate and tight alignments, the tolerances can be chosen down to only 1  $\mu m$  by using more accurate lithography.

This work was done by Cecile Jung-Kubiak, Theodore J. Reck, Robert H. Lin, Alejandro Peralta, John J. Gill, Choonsup Lee, Jose Siles, Risaku Toda, Goutam Chattopadhyay, Ken B. Cooper, and Imran Mehdi of Caltech; and Bertrand Thomas of RPG Radiometer Physics GmbH for NASA's Jet Propulsion Laboratory. For more information, contact iaoffice@jpl.nasa.gov.

In accordance with Public Law 96-517, the contractor has elected to retain title to this invention. Inquiries concerning rights for its commercial use should be addressed to: Innovative Technology Assets Management JPL Mail Stop 321-123 4800 Oak Grove Drive Pasadena, CA 91109-8099 E-mail: iaoffice@jpl.nasa.gov

Refer to NPO-48079/608, volume and number of this NASA Tech Briefs issue, and the page number.

NASA Tech Briefs, December 2013