# Real-Time On-Board Airborne Demonstration of High-Speed On-Board Data Processing for Science Instruments (HOPS)

## Jeffrey Y. Beyon<sup>1</sup>, Tak-Kwong Ng<sup>2</sup>, Mitchell J. Davis<sup>3</sup>, James K. Adams<sup>4</sup>, Stephen C. Bowen<sup>5</sup>, James J. Fay<sup>6</sup>, and Mark A. Hutchinson<sup>7</sup>

<sup>1</sup>NASA Langley Research Center, MS 488, Hampton, VA 23681, USA, Jeffrey.Y.Beyon@nasa.gov

<sup>2</sup>NASA Langley Research Center, MS 488, Hampton, VA 23681, USA, T.Ng@nasa.gov

<sup>3</sup>NASA Langley Research Center, MS 488, Hampton, VA 23681, USA, Mitchell.J.Davis@nasa.gov

<sup>4</sup>NASA Langley Research Center, MS 488, Hampton, VA 23681, USA, James.K.Adams@nasa.gov

<sup>5</sup>NASA Langley Research Center, MS 488, Hampton, VA 23681, USA, Stephen.C.Bowen@nasa.gov

<sup>6</sup>NASA Langley Research Center, MS 488, Hampton, VA 23681, USA, James.J.Fay@nasa.gov

<sup>7</sup>NASA Langley Research Center, MS 488, Hampton, VA 23681, USA, James.J.Fay@nasa.gov

#### ABSTRACT

The project called High-Speed On-Board Data Processing for Science Instruments (HOPS) has been funded by NASA Earth Science Technology Office (ESTO) Advanced Information Systems Technology (AIST) program since April, 2012. The HOPS team recently completed two flight campaigns during the summer of 2014 on two different aircrafts with two different science instruments. The first flight campaign was in July, 2014 based at NASA Langley Research Center (LaRC) in Hampton, VA on the NASA's HU-25 aircraft. The science instrument that flew with HOPS was Active Sensing of CO2 Emissions over Nights, Days, and Seasons (ASCENDS) CarbonHawk Experiment Simulator (ACES) funded by NASA's Instrument Incubator Program (IIP). The second campaign was in August, 2014 based at NASA Armstrong Flight Research Center (AFRC) in Palmdale, CA on the NASA's DC-8 aircraft. HOPS flew with the Multifunctional Fiber Laser Lidar (MFLL) instrument developed by Excelis Inc. The goal of the campaigns was to perform an end-to-end demonstration of the capabilities of the HOPS prototype system (HOPS COTS) while running the most computationally intensive part of the ASCENDS algorithm real-time on-board. The comparison of the two flight campaigns and the results of the functionality tests of the HOPS COTS are presented in this paper.

Keywords: onboard, high speed, HOPS, FPGA, ACES, ASCENDS

#### **1. INTRODUCTION**

HOPS is funded by NASA's ESTO AIST program for three years starting April in 2012. The goals of the project are to develop a high-speed on-board reconfigurable and scalable data processing platform for the select National Research Council's decadal survey science missions [1] such as ASCENDS [2-9] and 3-D Winds [10-12]. The HOPS maturation is scheduled for April, 2015, and this paper presents the results of two flight campaigns conducted in 2014. The entry and the exit Technology Readiness Level (TRL) of HOPS are two and five, respectively. All the components of HOPS are space-borne flight-ready equivalent (path-to-flight) and the board layout likewise seeks to minimize the risk associated with transitioning to a space-borne platform. HOPS is an enabler for science missions to perform real-time data processing by offering extremely high data processing rate [13-15]. The FPGA and memory bandwidth of HOPS is approaching 16 GB/sec and the inter-board communication bandwidth is approaching 4 GB/sec. The plug-N-play VHDL IP cores of HOPS provide the easy and efficient implementation of data processing algorithms with a quick turnaround time. The basic requirements to support high-speed on-board data processing are: (1) high speed computation element(s), (2) sufficient memory to hold intermediate computed values, and (3) sufficient bandwidth between the computation element and memory. Current space grade general purpose processors (GPPs) [16] and digital signal processors (DSPs) [17] do not meet all three requirements. There are multi-core general purpose and DSP processors [18] in the works which could meet requirement (1), but requirements (2) and (3) have not been met. With the

<sup>1</sup> Jeffrey.Y.Beyon@nasa.gov; phone 1 757 864–4249; fax 1 757 864–7944; www.nasa.gov

availability of rad-hardened reprogrammable FPGAs, however, it is now feasible to develop a high-speed on-board data processing system for science instruments that meets all three requirements, and high speed computation element(s) can be implemented in reconfigurable FPGAs [19-21]. FPGAs can be augmented with a high-speed on-board memory to address requirement (2) [22-24]. Furthermore, requirement (3) can be addressed with high-rate memories and a wide data bus architecture between the FPGA and the on-board memories. Lastly, FPGAs support high-speed serialized input/output allowing scalability. Section 2 discusses the design of HOPS from concept to flight, and Section 3 reports the outcome of the two flight campaigns. The current status of HOPS is presented in Section 4, followed by the conclusion.

## 2. CONCEPT TO FLIGHT

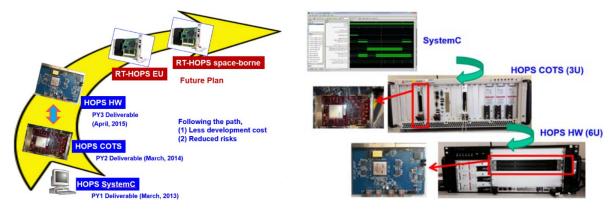

HOPS employs space-borne flight-equivalent parts in its design, allowing risk reduction in advancement to TRL 6. Several iterations of computing architecture supporting ASCENDS data processing were prototyped in SystemC during the first year of development. Preliminary HOPS hardware requirements were defined and the performance of ASCENDS data processing on HOPS was estimated during that period. Based on the analysis results in SystemC, a prototype (HOPS COTS) was built using commercial-off-the-shelf (COTS) components during the second project year. The system flew twice during the summer of 2014 to test its end-to-end capabilities. All the lessons learned from the campaigns are applied to the design and the demonstration of the final custom board called HOPS hardware (HOPS HW). HOPS is a three-year project and the future work post HOPS is called radiation-tolerant (RT) HOPS for space flights. HOPS seeks to minimize the risk associated with transitioning to RT-HOPS and therefore HOPS HW mimics the functional capabilities and layout of the anticipated RT-HOPS board through informed component selection and floor-planning. Since all the components of HOPS HW are path-to-flight, the construction of RT-HOPS will be at minimal risk and cost effective. Figure 1 illustrates the evolution of HOPS and its concept to flight path to RT-HOPS.

Figure 1 Concept-to-flight of HOPS and RT-HOPS.

## 3. FLIGHT CAMPAIGN WITH ACES AND ASCENDS

Figure 2 HOPS team during the Integration and Testing (IT) at AFRC

Figure 2 shows the photos of HOPS engineers at AFRC during the flight campaign in Palmdale, CA. The HOPS system that flew in 2014 is 3U-based, and consists of HOPS COTS and a COTS 14-bit digitizer. In order to demonstrate the end-to-end capabilities of HOPS, a sample C/C++ code was written to perform real-time data acquisition and processing running the ASCENDS algorithm. The system is quasi-autonomous and the majority of the data was acquired without an operator aboard.

| HOPS Flight<br>Campaigns | Campaign 1                                                      | Campaign 2                    |

|--------------------------|-----------------------------------------------------------------|-------------------------------|

| Location                 | LaRC in Hampton, VA                                             | AFRC in Palmdale, CA          |

| Aircraft                 | HU-25                                                           | DC-8                          |

| Period                   | July 1st - 16th, 2014                                           | July 27th – August 22nd, 2014 |

| Real-Time                | 4 million samples per second.<br>14-bit fixed point per sample. |                               |

| On-Board                 |                                                                 |                               |

| Data Rate                |                                                                 |                               |

| Algorithm                | ASCENDS                                                         |                               |

| Flight Hours             | 11.7 hours                                                      | 11 hours                      |

| Data Hours               | 20:43:34                                                        | 14:58:34                      |

| Science Team             | ACES (ESTO IIP)                                                 | Exelis Inc. (ESTO ACT)        |

Table 1 Logistics of HOPS flight campaigns in 2014.

Table 1 compares the logistics of the two flight campaigns. The first campaign was held during the first half of July based at LaRC and the HOPS system flew with the LIDAR instruments for ACES. The second campaign was based at AFRC in Palmdale, CA on the larger aircraft DC-8. The HOPS system tapped off of the LIDAR's raw data stream and preformed real-time data processing independently of the science instruments during the flight. The two campaigns serve as an end-to-end demonstration of the final deliverable HOPS HW since the operations and the functionalities of HOPS COTS are a subset of HOPS HW. The performance of HOPS HW will be far better than the HOPS COTS prototype, which will be demonstrated as part of the final deliverables.

| Campaign 1 Goals                           | Campaign 2 Goals                             |

|--------------------------------------------|----------------------------------------------|

| 1. Learn from a small aircraft campaign to |                                              |

| prepare for the DC-8 campaign.             |                                              |

| 2. Check the integration of HOPS COTS in a | Goals in campaign 1 plus                     |

| 3U cPCI system with a COTS digitizer.      |                                              |

| 3. Check HOPS COTS functionality.          | 1. Apply lessons from Campaign 1 to the      |

| 4. Check the integration of HOPS into a    | larger platform DC-8.                        |

| project and identify any issues such as    | 2. Check the heat dissipation of FPGA on the |

| cabling, boot-up sequence, power           | DC-8 during the campaign.                    |

| management, data archive, and HOPS         | 3. Check integration issues with a larger    |

| system monitoring.                         | platform in general.                         |

| 5. Test the sample code that utilizes HOPS | 4. End-to-end demonstration.                 |

| COTS with a digitizer.                     |                                              |

| 6. End-to-end demonstration.               |                                              |

Table 2 Goals of the two 2014 HOPS flight campaigns

Table 2 shows the list of goals in each campaign. The end-to-end airborne demonstration allows the HOPS team to be able to prepare HOPS HW for its seamless integration into the target science missions. Based on the lessons learned from the two campaigns, an integration plan has been devised so that the HOPS HW can be incorporated into the science mission data acquisition and processing system easily. Also, by-products from the campaigns such as a sample C/C++ program for real-time data distribution and archive and the know-hows in cabling and interface design will be valuable resources for science missions to adopt the HOPS HW into their system. At the end of each flight campaign, the accuracy of the algorithm was analyzed and the validation of the functionalities of the IP Core was performed. All the science data products met the required accuracy tolerance in those analyses, and the goals of each campaign were

#### accomplished.

### 4. STATUS QUO

The first bare-board of HOPS HW was built and tested for its basic electrical functionalities in August, 2014. It was populated upon the completion of basic electrical testing, and the major electrical and functional testing was performed on the resulting assembly board. A few issues were identified such as the difficulty of rewiring cabling used with the board and opportunities to further increase memory operating speed, and proper modifications were made to address these on the revised design and more bare-boards were ordered in December, 2014. After the basic electrical testing on the second bare-board, the second assembly board was made in January, 2015. A bit error problem was identified with a single data line on the DDR2 memory. The source of the problem was discovered to be damage to the DDR2 memory incurred during assembly due to solder lodged in a vertical trace which runs outside the component package. Testing revealed that a short circuit was not present between vertical traces and therefore it is currently believed that the solder transferred thermal energy inside the package damaging this single data line's connection with the vertical trace. Mitigations were discussed with both the component manufacturer and the assembly vendor and it was decided that a protective cap would be used to cover the vertical traces on the component during future assemblies. No electrical modification was necessary with the revised design. The third bare-board was ordered and received in February, 2015. After conducting a basic electrical testing on it, the third assembly board will be ordered in March, 2015. Upon its delivery in early March, 2015, the main electrical and functional testing will be performed to verify the correct operation of the board and the HOPS team will confirm the successful mitigation of the assembly problem previously encountered. Once this is confirmed, three additional assembly boards will be ordered and a total of four final HOPS custom boards will be delivered as final deliverables. Figure 3 shows an HOPS custom board (HOPS HW) during the electrical and functional testing.

Figure 3 HOPS custom board (HOPS HW) in testing.

#### 5. CONCLUSION

The three design phases of HOPS have been successful and the final HOPS HW is evolving to its maturity without any significant schedule delays. The seamless and user-friendly integration of HOPS HW into ASCENDS is the top priority of the project at the end of the project year, and an integration plan has been devised accordingly. The design principle of HOPS is to enable science missions that require extremely high data rate in general, and the final deliverable packages will contain documentations and resources that meet such a goal. The proof of re-configurability and scalability of HOPS HW is also part of the final deliverables, which are one of the unique features of HOPS HW. The two flight campaigns during the summer of 2014 were completed successfully in every aspect. The science data products met the required accuracy tolerance and the functionalities of the FPGA IP Core were verified and validated. The integration of the HOPS system using HOPS COTS into the science instruments for ACES and ASCENDS was successful, and all the integration and testing plans were executed without any issue. The HOPS system was quasi-autonomous and it operated without an operator once the system had started on the ground. All the lessons learned from the two flight campaigns will be incorporated into the completion of HOPS HW and the future planning of a space-borne version RT-HOPS. The

HOPS project is scheduled to complete in early 2015.

## ACKNOWLEDGMENT

The authors are grateful for the support from NASA Science Mission Directorate (SMD), the NASA SMD Earth Science Technology Office (ESTO), the ESTO Advanced Information System Technology (AIST) program, and the LaRC Engineering Directorate.

## BIBLIOGRAPHY

- [1] NRC, *Earth Science and Applications from Space: National Imperatives for the Next Decade and Beyond*, The National Academies Press, Washington, D.C., 2007.

- [2] ASCENDS, NASA Science Definition and Planning Workshop Report, NASA ASCENDS Workshop, University of Michigan, Ann Arbor, MI, 23-25 July 2008, Available at http://cce.nasa.gov/ascends/docs.htm

- [3] Browell, E. V., et al., "First Airborne Laser Remote Measurements of Atmospheric CO2 for Future Active Sensing of CO2 from Space," *Proceedings of the 8th International Carbon Dioxide Conference*, Jena, Germany, September 13-18, 2009

- [4] Browell, E. V., M. E. Dobbs, J. Dobler, S. Kooi, Y. Choi, F. W. Harrison, B. Moore III, and T. S. Zaccheo (2009b), "First airborne laser remote measurements of atmospheric CO2 for future active sensing of CO2 from space," *Proceedings of the 8th International Carbon Dioxide Conference*, Jena, Germany, 13-18 September. (Extended abstract and slides from presentation provided on request.)

- [5] Browell, E. V., M. E. Dobbs, J. Dobler, S. Kooi, Y. Choi, F. W. Harrison, B. Moore III, and T. S. Zaccheo (2009a), "First airborne Laser Remote Measurements of Atmospheric Carbon Dioxide," Presented at Fourth Symposium on Lidar Atmospheric Applications, 2009 AMS Annual Meeting, Phoenix, Arizona, 10-15 January. (Abstract and Video Presentation available via: http://ams.confex.com/ams/89annual/techprogram/paper\_146526.htm)

- [6] Pruitt et al., (2003), "High-speed CW lidar retrieval using spectral lock-in algorithm," *Proceeding of the SPIE*, vol. 5154, p 138

- [7] Dobbs, M., Pruitt, J., Gregory, D., & Sharp, W. 2006, "Matched Filter Enhanced Fiber-based Lidar for Earth, Weather and Exploration," AGU Fall Meeting, A1194

- [8] Active Remote Sensing using a Spectral Lock-in Technique, US Patent 6.949.734 B2

- [9] Active Remote Sensing Using a Simultaneous Spectral Sampling Technique, US Patent 7,009, 170 B2

- [10] J. Y. Beyon, G. J. Koch, and M. J. Kavaya, "Offshore Wind Measurements using Doppler Aerosol Wind Lidar (DAWN) at NASA Langley Research Center," in Proc. of the Defense and Security Symposium 2014 (9080-37), Baltimore, MD, May, 2014.

- [11] J. Y. Beyon, G. J. Koch, M. J. Kavaya, and T. J. Ray, "Airborne Wind Profiling Algorithms for the Pulsed 2-Micron Coherent Doppler Lidar at NASA Langley Research Center," in Proc. of the Defense and Security Symposium 2013 (8731-20), Baltimore, MD, May, 2013.

- [12] J. Y. Beyon, G. J. Koch, and M. J. Kavaya, "Airborne Wind Profiling with the Data Acquisition and Processing System for a Pulsed 2-Micron Coherent Doppler Lidar System," in Proc. of the Defense and Security Symposium 2012 (8379-22), Baltimore, MD, April, 2012.

- [13] J. Y. Beyon, "High-Speed On-Board Data Processing for Science Instruments," American Geophysical Union Fall Meeting, San Francisco, CA, December, 2014.

- [14] J. Y. Beyon and T. Ng, "High-Speed On-Board Data processing for Science Instruments," Earth Science Technology Forum 2014, Leesburg, VA, October, 2014.

- [15] J. Y. Beyon, T. Ng, B. Lin, Y. Hu, and W. Harrison, "High-Speed On-Board Data Processing for Science Instruments," in Proc. of the Defense and Security Symposium 2014 (9080-21), Baltimore, MD, May, 2014.

- [16] "Aitech S950 Single Board Computer," In <u>http://www.rugged.com/s950.htm#</u>

- [17] "Rad-Tolerant Class-V Floating-Point Digital Signal Processor" in http://www.ti.com/lit/ds/symlink/smj320c6701-sp.pdf

- [18] "Opera RHBD Multi-core," in https://nepp.nasa.gov/mapld\_2009/talks/083109\_Monday/03\_Malone\_Michael\_mapld09\_pres\_1.pdf

- [19] P. Sundararajan, "High Performance Computing Using FPGAs." Xilinx WP375, Sept., 2010

- [20] R. Hodson, K. Somervill, J. Williams, N. Bergman, R. Jones III, "An Architecture for Reconfigurable Computing." In MAPLD Conference, 2005

- [21] "Radiation-Hardened, Space-Grade Virtex-5QV Family Overview," in http://www.xilinx.com/support/documentation/data\_sheets/ds192\_V5QV\_Device\_Overview.pdf

- [22] T. Ng, C. Mills, "A. Bulyshev, and R. Hodson, Lidar Image Processing Acceleration Via FPGA Implementation" (abstract, presentation). In ReSpace/MAPLD Conference, 2010

- [23] "Radiation Tolerant Memory, DDR2 SDRAM Module," in http://www.3d-plus.com/doc/prod/3dfp\_0652\_1.pdf

- [24] "72-Mbit QDR II+ SRAM Two-Word Burst Architechture with RadStop Technology," http://www.cypress.com/?docID=48207