## UNIVERSITÀ DEGLI STUDI DI PARMA

Dottorato di Ricerca in Tecnologie dell'Informazione

XXIV Ciclo

## Thermal and electro-thermal modeling

of electronic devices and systems

## for high-power and high-frequency applications

Coordinatore: Chiar.mo Prof. Marco Locatelli

Tutor: Chiar.mo Prof. Roberto Menozzi

Dottorando: Mirko Bernardoni

Gennaio 2012

to my Mother

and to all the real Friends

of mine

# **Table of Contents**

| Introduction |  |

|--------------|--|

|              |  |

| 1        | The  | ermal a | and thermo-fluid dynamics FEM modeling of power mo-           |    |

|----------|------|---------|---------------------------------------------------------------|----|

|          | dule | es      |                                                               | 3  |

|          | 1.1  | Introd  | uction                                                        | 3  |

|          | 1.2  | The th  | nermo-fluid dynamics simulation process                       | 6  |

|          |      | 1.2.1   | Heat equations                                                | 7  |

|          |      | 1.2.2   | The Navier-Stokes equations                                   | 9  |

|          |      | 1.2.3   | Modeling the liquid-cooling heat-sink                         | 10 |

|          |      | 1.2.4   | FEM thermal modeling of power assemblies                      | 12 |

|          |      | 1.2.5   | Determination of the die temperature and thermal model tuning | 16 |

|          |      | 1.2.6   | Comparison between different solutions                        | 19 |

|          |      | 1.2.7   | Planar transformer and surface modeling                       | 27 |

|          |      | 1.2.8   | Simulation results                                            | 31 |

|          | 1.3  | Conclu  | usions                                                        | 36 |

| <b>2</b> | Elec | ctro-th | ermal modeling and characterization of electron devices       | 39 |

|          | 2.1  | A revi  | ew of some basic concepts                                     | 39 |

|          | 2.2  | The H   | EMT device                                                    | 43 |

|          |      | 2.2.1   | Large signal models of HEMTs                                  | 46 |

|          | 2.3  | Lumpe   | ed elements modeling techniques                               | 48 |

|          |      | 2.3.1   | Where the LEM idea comes from                                 | 50 |

|          | 2.4  | Self-co | onsistent coupling of electrical and thermal models           | 56 |

|          | 2.5  | Applic  | cation cases                                                  | 57 |

|          |      | 2.5.1   | Power MOSFET on a heat sink                                   | 57 |

|          |      | 2.5.2   | Thermal modeling of HEMTs                                     | 72 |

|          |      | 2.5.3   | FinFET modeling                                               | 89 |

1

|   | 2.6                                           | 2.5.4 Modeling of complex structures                                                                                                                                                                                                                                                                                                                                                                                     | 91<br>96                                                                                                                                     |

|---|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 3 | Hig<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6 | h spatial resolution thermal measurements         Contact and contact-less methods for temperature measurement         3.1.1       Introduction and useful concepts         The optical bench                                                                                                                                                                                                                            | <b>97</b><br>98<br>99<br>101<br>108<br>112<br>117                                                                                            |

| 4 |                                               | deration of high-voltage, nanosecond-duration electrical pulses for         nedical applications         Electroporation and nanoseconds pulse cell treatments         The design of the electrical bench         4.2.1         The architecture of the bench         Conclusions                                                                                                                                        | <b>119</b><br>119<br>120<br>120                                                                                                              |

|   |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                              |

| A |                                               | A modeling of thermomechanical stress in electronic assemblies         fatigue-oriented analysis         Introduction                                                                                                                                                                                                                                                                                                    | <b>135</b><br>135<br>135<br>138<br>140<br>141<br>142<br>143<br>144<br>150                                                                    |

|   | for 1<br>A.1<br>A.2<br>A.3                    | fatigue-oriented analysis         Introduction         Some concepts of mechanics of materials         A.2.1 Fatigue         The LCF applied to solder joints reliability         A.3.1 The modeled system         A.3.2 Material Properties and Boundary Conditions         A.3.3 Cases of study         A.3.4 How to analyze FEM simulation results                                                                    | <ol> <li>135</li> <li>135</li> <li>138</li> <li>140</li> <li>141</li> <li>142</li> <li>143</li> <li>144</li> </ol>                           |

| в | for 1<br>A.1<br>A.2<br>A.3                    | fatigue-oriented analysis         Introduction         Some concepts of mechanics of materials         A.2.1 Fatigue         A.2.1 Fatigue         The LCF applied to solder joints reliability         A.3.1 The modeled system         A.3.2 Material Properties and Boundary Conditions         A.3.3 Cases of study         A.3.4 How to analyze FEM simulation results         A.3.5 Considerations about the model | <ol> <li>135</li> <li>135</li> <li>138</li> <li>140</li> <li>141</li> <li>142</li> <li>143</li> <li>144</li> <li>150</li> </ol>              |

| в | for 1<br>A.1<br>A.2<br>A.3<br>FFT<br>List     | fatigue-oriented analysis         Introduction         Some concepts of mechanics of materials         A.2.1 Fatigue         A.2.1 Fatigue         The LCF applied to solder joints reliability         A.3.1 The modeled system         A.3.2 Material Properties and Boundary Conditions         A.3.3 Cases of study         A.3.4 How to analyze FEM simulation results         A.3.5 Considerations about the model | <ul> <li>135</li> <li>135</li> <li>138</li> <li>140</li> <li>141</li> <li>142</li> <li>143</li> <li>144</li> <li>150</li> <li>153</li> </ul> |

<u>ii</u>\_\_\_\_\_

# List of Figures

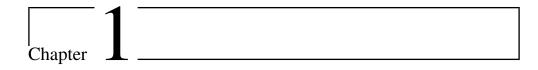

| 1.1   | Schematic of the SMPS (reprinted from [1])                                                                                                                     | 4          |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 1.2   | The metal case with the three power supply modules and heat-sinks                                                                                              | 6          |

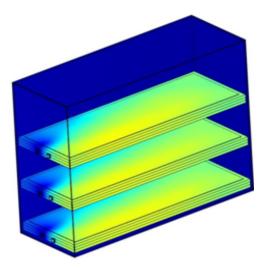

| 1.3   | A surface with its normal vector (left). Convective motions arise when the surface temperature $T$ is different from the fluid reference temperature $T_{ref}$ |            |

|       | (center). A cooling process is is described by a positive flux (blue arrow, right),                                                                            |            |

|       | while a heating process is described by a negative flux (red arrow, right).                                                                                    | 9          |

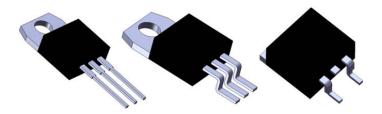

| 1.4   | Types of packages studied: from left, a TO-220, a modified TO-220 to be SMD $$                                                                                 |            |

|       | mounted, and a $D^2PAK$                                                                                                                                        | 13         |

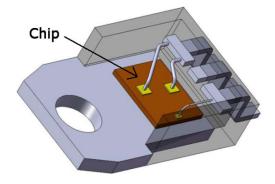

| 1.5   | Inner structure of the modeled device.                                                                                                                         | 13         |

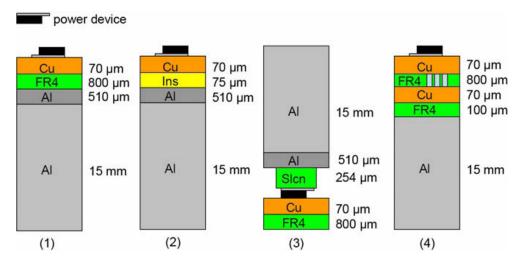

| 1.6   | Vertical cross-section of the four board topologies here studied: from the left:                                                                               |            |

|       | (1) standard FR4, (2) IMS board, (3) hybrid configuration with silicone layer                                                                                  |            |

|       | insulation, (4) standard FR4 with thermal vias                                                                                                                 | 14         |

| 1.7   | Test board developed for FE thermal model tuning, with indication of the                                                                                       |            |

|       | temperature measurement points                                                                                                                                 | 16         |

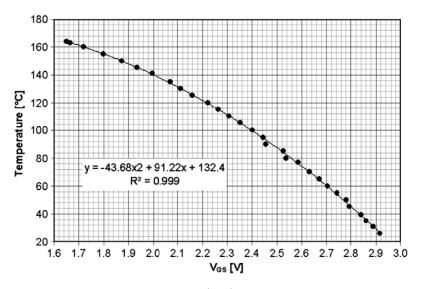

| 1.8   | Calibration curve $T = f(V_{GS})$ obtained for the device under test                                                                                           | 16         |

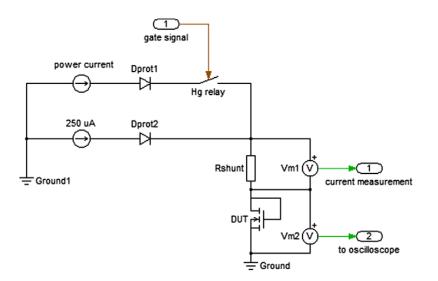

| 1.9   | Electrical setup for measuring the junction temperature of the device under                                                                                    |            |

|       | test                                                                                                                                                           | 17         |

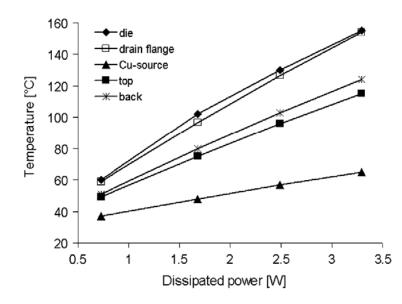

| 1.10  | Measured temperatures versus MOSFET dissipated power. The ambient tem-                                                                                         |            |

|       | perature is 26 °C.                                                                                                                                             | 18         |

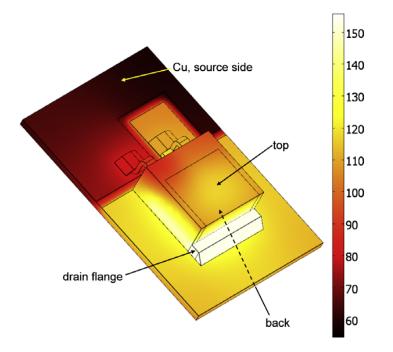

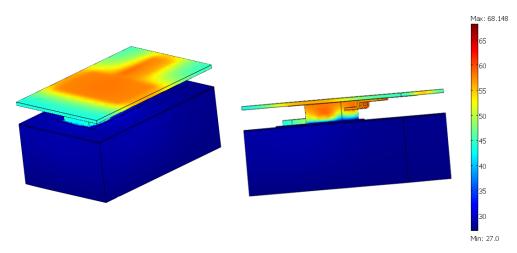

| 1.11  | Simulated thermal distribution of the test board (temperatures in °C), ob-                                                                                     |            |

|       | tained by 3D FEM model. The dissipated power is 3.3 W, and the measure-                                                                                        | 10         |

| 1 10  | ment points are pointed out by the arrows.                                                                                                                     | 19         |

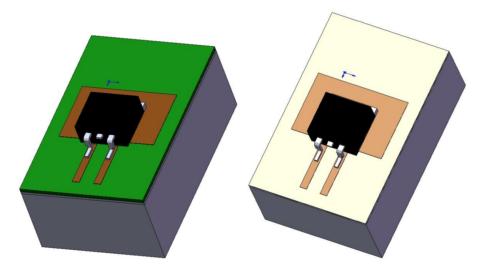

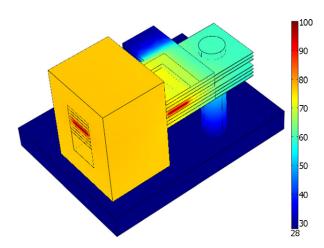

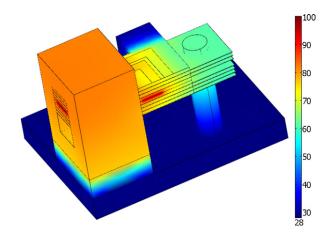

|       | The standard FR4 technology solution (left) and the IMS solution (right)                                                                                       | 21         |

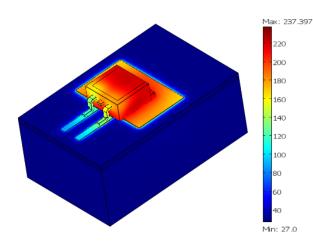

| 1.13  | Simulation results of the FR4 structure. The die dissipates 20 W. Temper-                                                                                      |            |

|       | atures in °C. The simulation features 206000 degrees of freedom. The die turns mature is $240$ °C                                                              | 00         |

| 1 1 / | temperature is 240 °C.                                                                                                                                         | 22         |

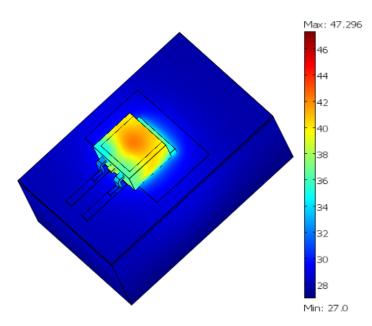

| 1.14  | Simulation of the IMS structure. The die dissipates 20 W. Temperatures in $^{\circ}C$ . The simulation features 267000 degrees of freedom. The die temperature |            |

|       | °C. The simulation features 267000 degrees of freedom. The die temperature is $47$ °C                                                                          | 23         |

|       | is $47 ^{\circ}$ C                                                                                                                                             | 2 <b>0</b> |

| 1.15  | The hybrid solution.                                                                                                                                                                                                              | 24 |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.16  | Simulation of the hybrid solution. The die dissipates 20 W. Temperatures in                                                                                                                                                       |    |

|       | $^{\circ}$ C. The simulation features 218000 degrees of freedom. The die temperature                                                                                                                                              | ~~ |

| 1 1 1 | is $68 ^{\circ}\mathrm{C}$ .                                                                                                                                                                                                      | 25 |

|       | Thermal vias structure.                                                                                                                                                                                                           | 26 |

| 1.18  | Simulation of the structure with thermal vias. The die is dissipating $20 \text{ W}$ .<br>Temperatures in °C. The structure has $430000$ degrees of freedom. The die                                                              |    |

|       | temperature is $100 ^{\circ}$ C                                                                                                                                                                                                   | 26 |

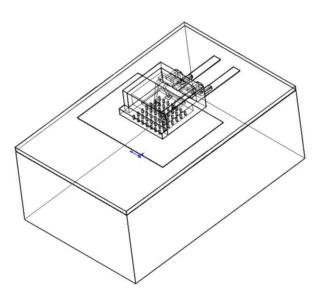

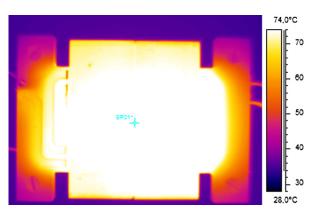

|       | Photograph of the planar transformer built at the University of Parma                                                                                                                                                             | 28 |

| 1.20  | Thermal map of the planar transformer operated at $V_{1\text{rms}} = 120 \text{ V}$ , $I_{1\text{rms}} = 2.1 \text{ A}$ . The ambient temperature is $28 ^{\circ}\text{C}$ and the maximum temperature is $74 ^{\circ}\text{C}$ . | 30 |

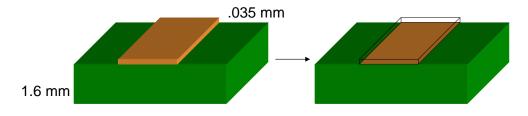

| 1 91  | Replacing a three-dimensional domain – a copper track in this particular case                                                                                                                                                     | 30 |

| 1.21  | - with an equivalent two-dimensional layer, which is basically the footprint of                                                                                                                                                   |    |

|       | the track on the underlying domain.                                                                                                                                                                                               | 30 |

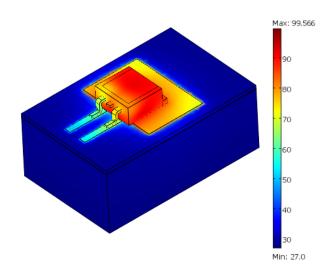

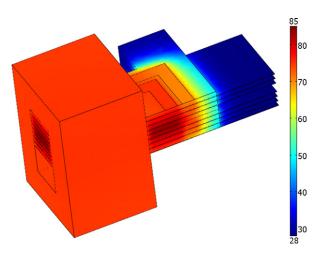

| 1 99  | Simulated transformer thermal map (temperature in $^{\circ}$ C); $P_{Cu1} = 7.3$ W,                                                                                                                                               | 30 |

| 1.22  | $P_{\text{Cu2}} = 3.9 \text{ W}, P_{\text{Core}} = 6.1 \text{ W}.$ The ambient temperature is 28 °C. The peak                                                                                                                     |    |

|       | surface temperature is $75 ^{\circ}\text{C}$ .                                                                                                                                                                                    | 32 |

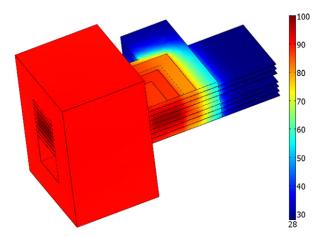

| 1 23  | Simulated transformer thermal map (temperature in $^{\circ}C$ ); $P_{Cu1} = 7.3 \text{ W}$ ,                                                                                                                                      | 02 |

| 1.20  | $P_{\text{Cu}2} = 3.9 \text{ W}, P_{\text{Core}} = 11.3 \text{ W}.$ The ambient temperature is 28 °C. The peak                                                                                                                    |    |

|       | temperature is $100$ °C and it is reached in the secondary windings                                                                                                                                                               | 32 |

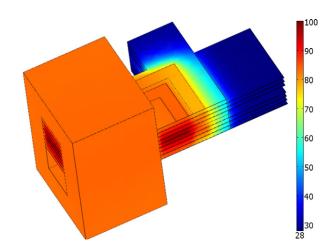

| 1.24  | Simulated transformer thermal map with output current $I_{\text{out}} = 8 \text{ A}$ (temperature                                                                                                                                 | -  |

|       | in °C); $P_{Cu1} = 7.3 \text{ W}$ , $P_{Cu2} = 7 \text{ W}$ , $P_{Core} = 11.3 \text{ W}$ . The ambient temperature                                                                                                               |    |

|       | is 28 °C. The peak temperature is $100$ °C and it is reached in the secondary                                                                                                                                                     |    |

|       | windings.                                                                                                                                                                                                                         | 33 |

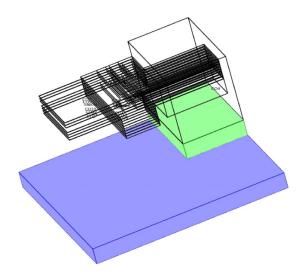

| 1.25  | 3D geometry of $1/4$ of the planar transformer with aluminum baseplate (blue)                                                                                                                                                     |    |

|       | and silicone gap-filler (green).                                                                                                                                                                                                  | 34 |

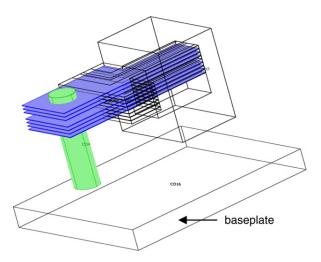

| 1.26  | 3D geometry of $1/4$ of the planar transformer with aluminum baseplate, ther-                                                                                                                                                     |    |

|       | mal bridge (green) and copper thermal layers (blue)                                                                                                                                                                               | 34 |

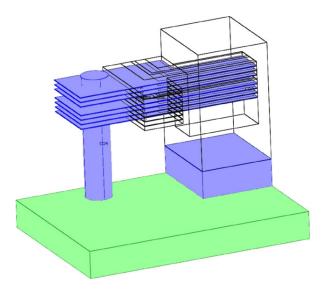

| 1.27  | 3D geometry of $1/4$ of the planar transformer with aluminum baseplate, cop-                                                                                                                                                      |    |

|       | per thermal layers, and silicone gap-filler.                                                                                                                                                                                      | 35 |

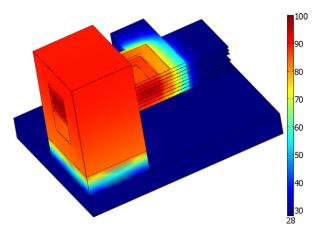

| 1.28  | Simulation results of the structure of Figure 1.25. $P_{\rm Cu1}$ = 7.3 W, $P_{\rm Cu2}$ =                                                                                                                                        |    |

|       | $3.9{\rm W},P_{\rm Core}=65.3{\rm W}.$ Temperature in °C. Ambient temperature is 28 °C                                                                                                                                            | 35 |

| 1.29  | Simulation results of the structure of Figure 1.26. $P_{\rm Cu1}$ = 7.3 W, $P_{\rm Cu2}$ =                                                                                                                                        |    |

|       | 32.9 W, $P_{\rm Core}=6.1{\rm W}.$ Temperature in °C. Ambient temperature is 28 °C                                                                                                                                                | 36 |

| 1.30  | Simulation results of the structure of Figure 1.27. $P_{\rm Cu1} = 7.3 \rm W, \ P_{\rm Cu2} =$                                                                                                                                    |    |

|       | 26.4 W, $P_{\rm Core} = 65.3$ W. Temperature in °C. Ambient temperature is 28 °C                                                                                                                                                  | 37 |

| 0.1   | Colometic description of a local structure for a service destar. These local the                                                                                                                                                  |    |

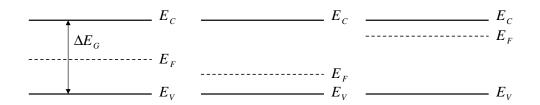

| 2.1   | Schematic drawing of a band structure for a semiconductor. From left: the                                                                                                                                                         |    |

|       | case of an intrinsic semiconductor, a $p$ -doped semiconductor, and an $n$ -doped semiconductor $E_{res}$ is the ten of the melane hand $E_{res}$ is the Fermi level and                                                          |    |

|       | semiconductor. $E_V$ is the top of the valence band, $E_F$ is the Fermi level, and $E_T$ is the bottom of the conduction band. $\Delta E_T$ denotes the bandgep                                                                   | 40 |

| იი    | $E_C$ is the bottom of the conduction band. $\Delta E_G$ denotes the bandgap Band diagram of a Schottky junction under no-bias condition – reprinted                                                                              | 40 |

| 2.2   |                                                                                                                                                                                                                                   | 41 |

|       | from [8]                                                                                                                                                                                                                          | 41 |

iv

## List of Figures

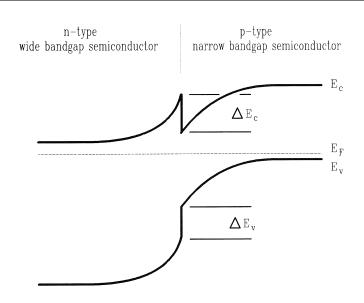

| $2.3 \\ 2.4$ | Band diagram of an heterojunction – reprinted from [8]                                                                                                                                                                                         | 42         |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

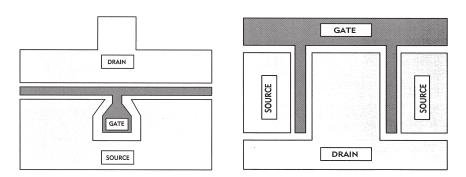

|              | dard cell (right) – reprinted from [8]                                                                                                                                                                                                         | 43         |

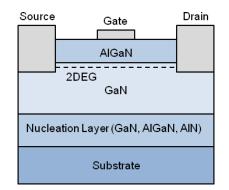

| $2.5 \\ 2.6$ | Cross section of a basic AlGaN/GaN HEMT structure                                                                                                                                                                                              | 43         |

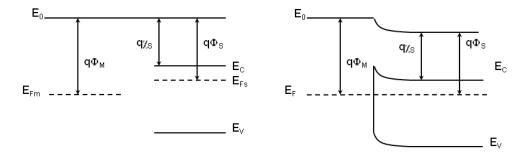

|              | Schottky barrier (right) at the thermal equilibrium. $E_0$ is the vacuum energy                                                                                                                                                                | 4.4        |

| 2.7          | level                                                                                                                                                                                                                                          | 44         |

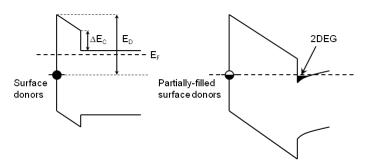

|              | thickness necessary for the creation of the 2DEG [11].                                                                                                                                                                                         | 45         |

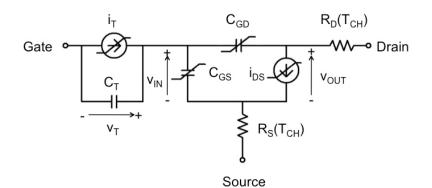

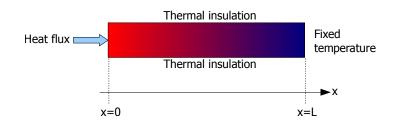

| $2.8 \\ 2.9$ | HEMT large signal model schematic. $I_T$ and $C_T$ describe the trap behavior<br>A case of a bar with a heated end and the opposite end kept at a constant                                                                                     | 47         |

|              | temperature. All other surfaces are insulated.                                                                                                                                                                                                 | 49         |

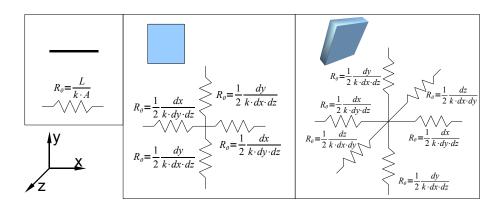

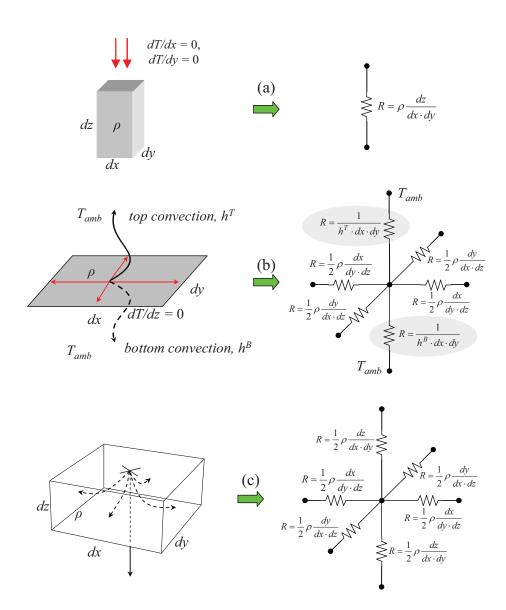

| 2.10         | Types of elements suitable for LEM thermal modeling. One-dimensional ele-<br>ment (left), two-dimensional element (center), three-dimensional element (right).                                                                                 | 51         |

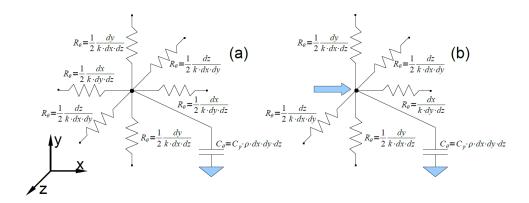

| 2.11         | Three-dimensional blocks used to model temperature transients; inner block (left) and border block (right) with indication of heat direction (arrow)                                                                                           | 52         |

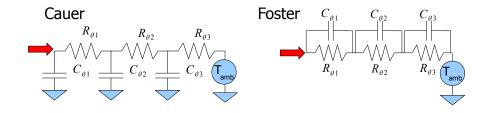

| 9 19         | Cauer and Foster thermal networks.                                                                                                                                                                                                             | 52<br>52   |

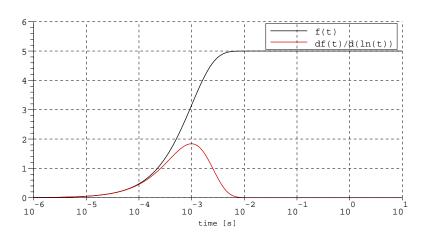

|              | The term $5(1 - e^{-t/10^{-3}})$ and its derivative.                                                                                                                                                                                           | 54         |

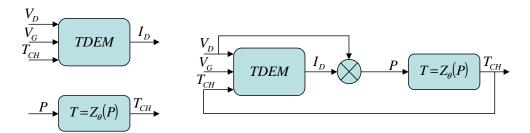

|              | Block diagram of a self-consistent electro-thermal device model. Starting from                                                                                                                                                                 | 94         |

| 2.11         | two independent systems, the first being the Temperature-Dependent Electri-<br>cal Model (TDEM) and the second the lumped element thermal network $Z_{\theta}$ ,<br>their feedback connection describes the device behavior in the presence of |            |

|              | self-heating.                                                                                                                                                                                                                                  | 56         |

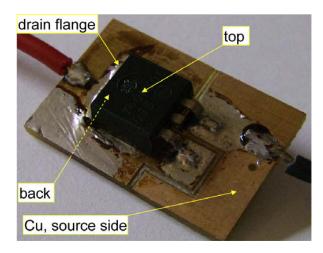

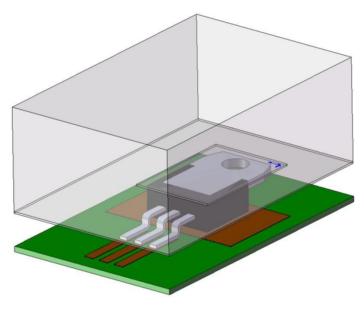

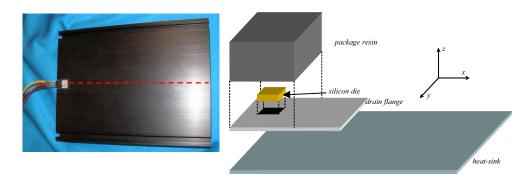

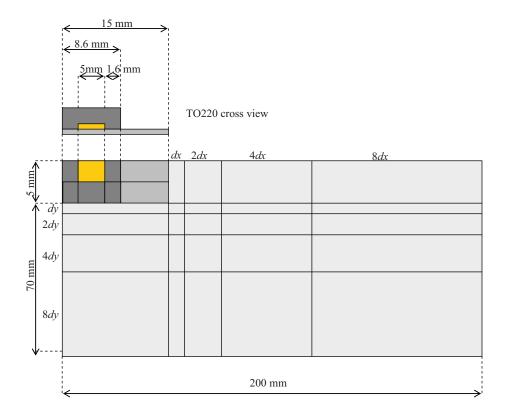

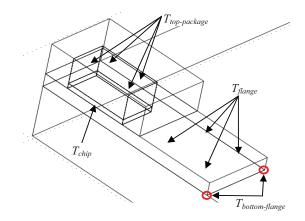

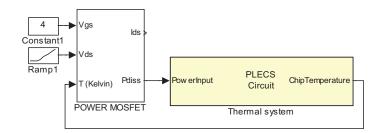

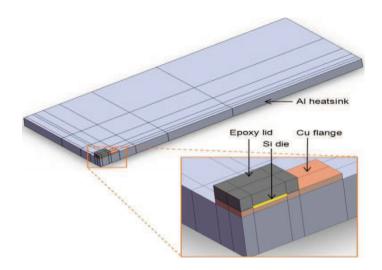

| 2.15         | Photograph (left) and exploded view (right) of the MOSFET assembly. The red line indicates the symmetry axis.                                                                                                                                  | 57         |

| 2.16         | Schematic 2-D view of how the assembly has been discretized. Thanks to                                                                                                                                                                         |            |

|              | symmetry, only one half of the structure needs to be modeled                                                                                                                                                                                   | 59         |

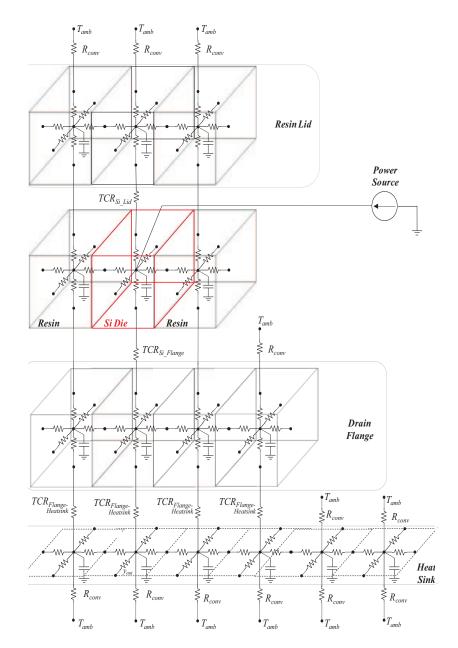

| 2.17         | An overview of the elements used to model the assembly, with the corre-<br>sponding thermal networks. From top: one-dimensional element (a), two-                                                                                              |            |

|              | dimensional element with convective boundary conditions (b), three-dimensional element (c)                                                                                                                                                     | <i>c</i> o |

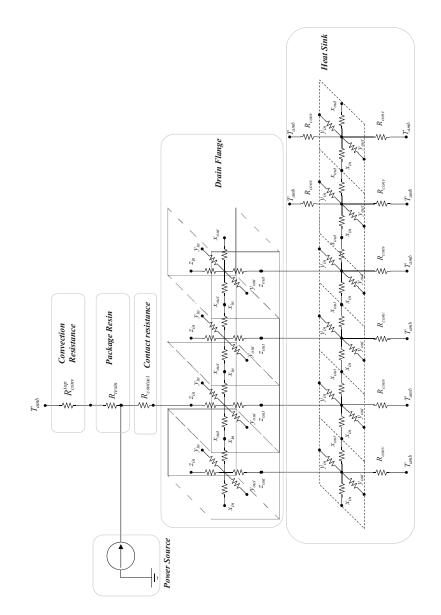

| 0 10         | A three-dimensional view of part of the lumped element thermal network. For                                                                                                                                                                    | 62         |

| 2.10         | the sake of clarity, only the part of the heat sink underlying the device is shown.                                                                                                                                                            | 63         |

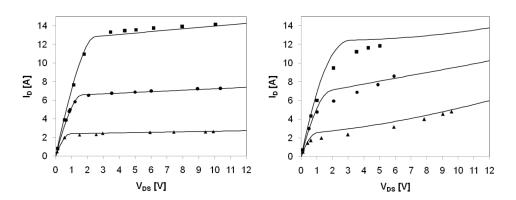

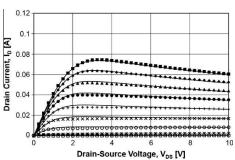

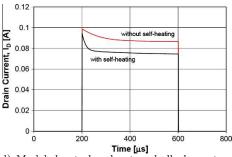

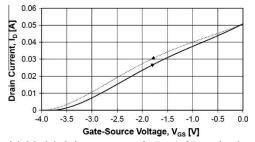

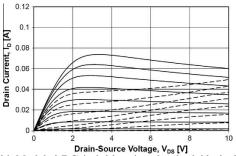

| 2.19         | Comparison between simulation results (lines) and measurements (points) in                                                                                                                                                                     | 00         |

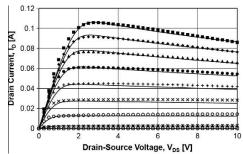

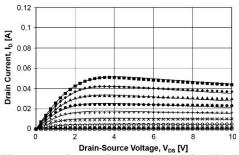

| 2.10         | the case of pulsed (isothermal) measurements (left) and in the DC case (i.e.,<br>with self-heating) (right).                                                                                                                                   | 64         |

| 2.20         | A blow-up on the device with the points/surfaces/volumes used to evaluate                                                                                                                                                                      |            |

| 2.21         | temperatures from the FEM model                                                                                                                                                                                                                | 65         |

| 2.22         | mal network, respectively                                                                                                                                                                                                                      | 66         |

|              | two sensing points $S_{p1}, S_{p2}, \ldots, \ldots, \ldots, \ldots, \ldots$                                                                                                                                                                    | 66         |

## v

| 2.23 | The modeled test structure, with a blow-up of the device. The grid used to mesh the assembly is shown. Different colors correspond to different domains.                                                                                                                                                                                                 | 67 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.24 | A vertical slice of the <i>RC</i> lumped-element thermal network modeling the assembly shown in Figure 2.15. Each capacitance is connected between the block central node and thermal ground.                                                                                                                                                            | 69 |

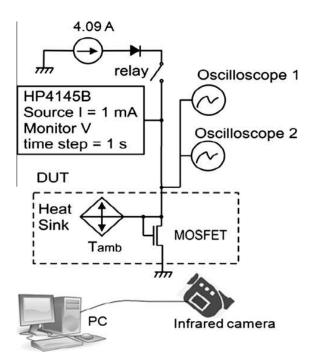

| 2.25 | Transient thermal measurement setup                                                                                                                                                                                                                                                                                                                      | 70 |

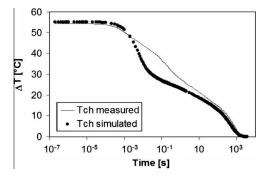

|      | Comparison between measured and simulated $T_{\rm CH}$ temperature increase tran-                                                                                                                                                                                                                                                                        |    |

|      | sients.                                                                                                                                                                                                                                                                                                                                                  | 70 |

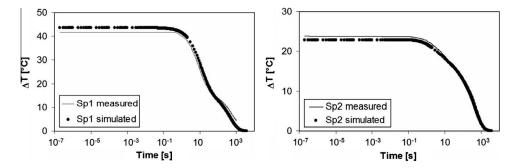

| 2.27 | Comparison between measured and simulated temperatures increase tran-<br>sients. $S_{p1}$ temperature (left), $S_{p2}$ temperature (right)                                                                                                                                                                                                               | 71 |

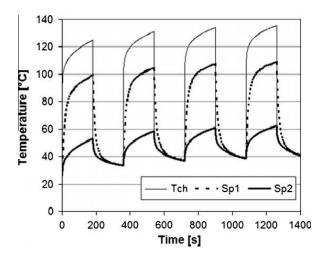

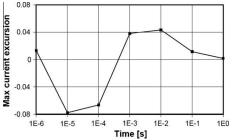

| 2.28 | Simulated temperatures of $S_{p1}$ , $S_{p2}$ and silicon die during a train of pulses with $P_D = 45 \text{ W}$ , $T = 360 \text{ s}$ , $d = 50\%$ . Ambient temperature is $26 \degree \text{C}$                                                                                                                                                       | 71 |

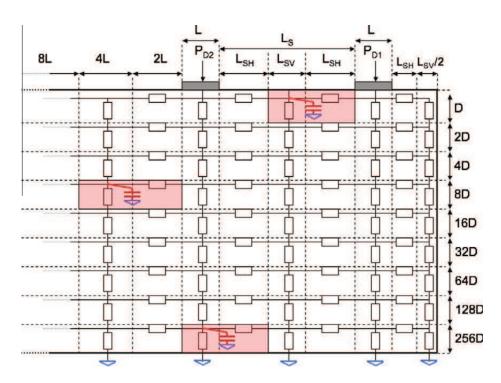

| 2.29 | Two-dimensional dynamic thermal network for an AlGaN/GaN HEMT [17].<br>Each node features a capacitance connected to ground, only three are shown<br>for the sake of clarity.                                                                                                                                                                            | 73 |

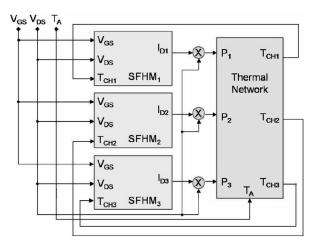

| 2.30 | The electro-thermal feedback loop. Each SFHM block is a single-finger HEMT model like the one in Figure 2.8.                                                                                                                                                                                                                                             | 74 |

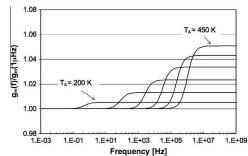

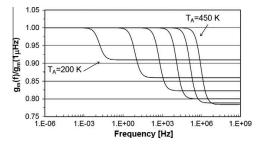

| 2.31 | Modeling results for a single-finger 150 µm-wide AlGaN/GaN HEMT on sap-<br>phire – part 1. Where not specified, ambient temperature is 300 K                                                                                                                                                                                                             | 77 |

| 2.32 | Modeling results for a single-finger 150 µm-wide AlGaN/GaN HEMT on sap-<br>phire – part 2                                                                                                                                                                                                                                                                | 78 |

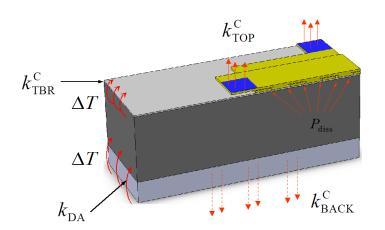

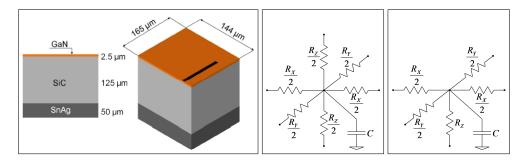

| 2.33 | View of the analyzed structure. Different materials are indicated by different colors. From the top: GaN, substrate (silicon or silicon carbide depending on different cases), and die-attach. Gold metallizations with blue pads for application of boundary conditions are also shown. The parameters used to model the boundary conditions are shown. | 79 |

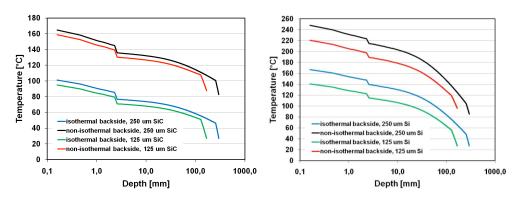

| 2.34 | Temperature profiles under the hottest (innermost) finger, for different SiC (left) and Si (right) substrates thicknesses and for ideal isothermal (300 K), and non isothermal ( $k_{BACK}^C = 3.6 \times 10^5 \text{ W/(m^2 K)}$ ) back-side boundary conditions. $P_D = 3 \text{ W/mm}$ .                                                              | 81 |

| 2.35 |                                                                                                                                                                                                                                                                                                                                                          | 81 |

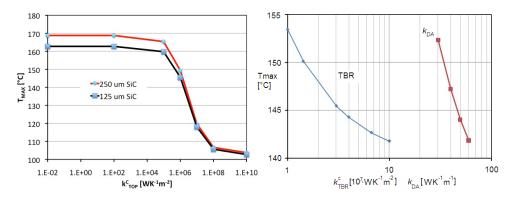

| 2.36 | Temperature profiles under the hottest (innermost) finger, for 125 µm-thick SiC substrate, at various times after the application of a power step ( $P_D = 3 \text{ W/mm}$ ). $k_{BACK}^C = 3.6 \times 10^5 \text{ W/(m^2K)}$ , $k_{TOP}^C = 0$ , $k_{TBR}^C = 3 \times 10^7 \text{ W/(m^2K)}$ , $k_{DA} = 45 \text{ W/(m \cdot K)}$ .                   | 82 |

vi

## List of Figures

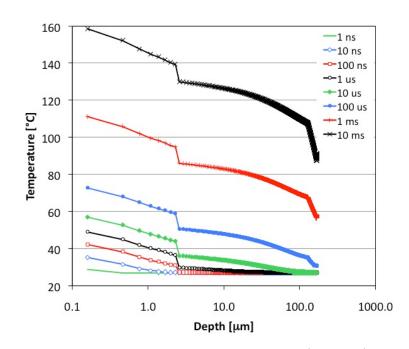

| 2.37 | How to use an SSD in order to implement a temperature-dependent resistance.<br>(a) example of a two-port SSD. (b) port 1 implements Ohm's law (expressed<br>in its thermal counterpart), while port 2 is used to sample the voltage in<br>the thermal network corresponding to the control temperature $T_{\text{control}}$ : this<br>temperature modulates the thermal resistance $R_{\theta}$ . (c) an example of how to<br>use four SDDs in order to describe a two-dimensional block, the schematic of<br>which is shown in (d): the temperature of the central node modulates the four<br>resistances in the building block. | 86 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.38 | The modeled 3D HEMT structure, not to scale (left). The structure represents a quarter of the real HEMT, because the two visible sidewalls are symmetry planes, modeled by adiabatic boundaries. The black line on the top surface represents the 75 µm-wide heating gate finger. (center, right) Building blocks of the 3D LE thermal network. The central block represents the generic element of volume, while the right block is used to model surface elements                                                                                                                                                               | 87 |

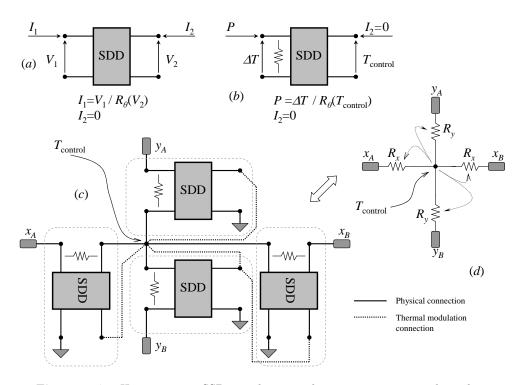

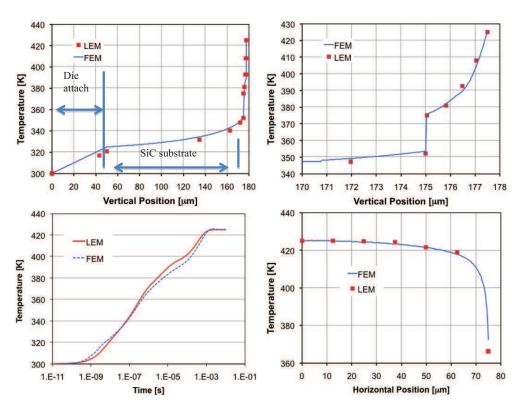

| 2.39 | (top left) Comparison between vertical temperature profiles obtained by FEM and LEM simulations. (top right) A close-up of the top part of the vertical profile showing the effect of the TBR. (bottom left) Comparison between LEM and FEM transient response after the application of a power step. (bottom right) Temperature profile along the finger width. In all cases, the steady-state dissipated power is 6.67 W/mm                                                                                                                                                                                                     | 88 |

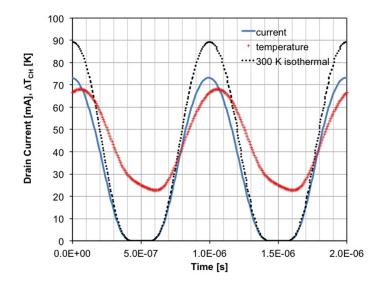

| 2.40 | Simulation results of the AB amplifier with and without self-heating. The channel temperature increase over ambient temperature is plotted as well, clearly showing the heating and cooling phases of the amplifier                                                                                                                                                                                                                                                                                                                                                                                                               | 89 |

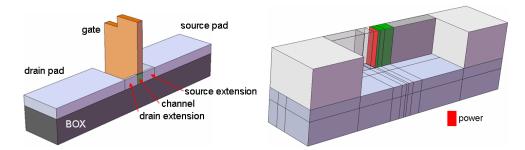

| 2.41 | (left) The FinFET structure. Only half of the device was modeled, since the vertical symmetry plane bisecting the FinFET along the channel length can be replaced by an adiabatic boundary. (right) The heating power is injected in the red area (channel end section); the channel is the green volume (gate omitted for clarity); the drawing shows the partitions for LE modeling                                                                                                                                                                                                                                             | 90 |

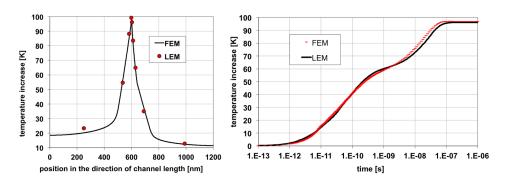

| 2.42 | Left: Comparison between FE model and LE model in the steady-state case.<br>Right: temperature response following a power step, as given by the FE and<br>LE models. In both cases, the match between the two models is excellent. No<br>fitting parameters are used.                                                                                                                                                                                                                                                                                                                                                             | 91 |

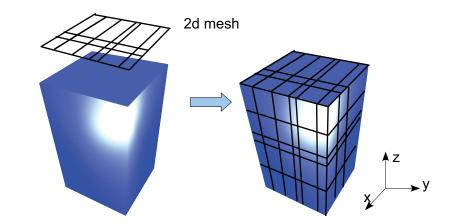

| 2.43 | Starting from a 3D domain and a surface 2D mesh, the discretization on the whole domain is simply achieved by extruding the 2D mesh throughout the $z$ direction. The meshing can get coarser and coarser as depth increases in order to limit the number of nodes.                                                                                                                                                                                                                                                                                                                                                               | 92 |

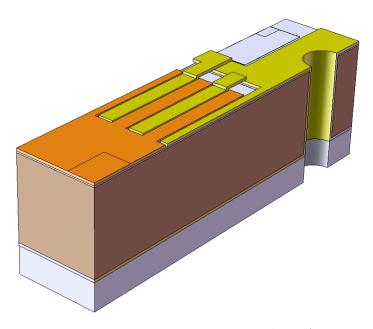

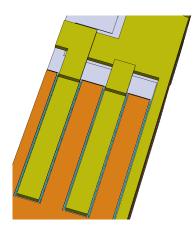

| 2.44 | The elementary cell of a large-periphery AlGaN/GaN power device, featuring drain, gate and source metallizations, and a source ground via.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 93 |

| 2.45 | A blow up of the HEMT surface cell. The light blue lines are the gate metal-<br>lization, below which are the heating areas.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 93 |

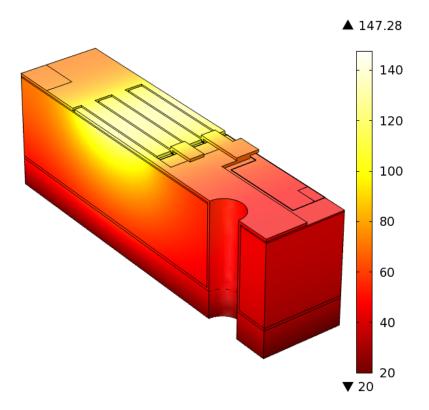

| 2.46 | FEM simulation results of the structure shown in Figure 2.44. The dissipated power for each finger is $0.5$ W. Temperatures in °C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 94 |

vii

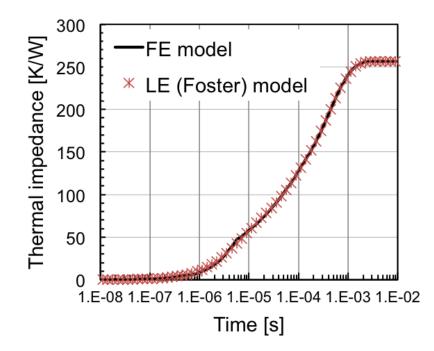

| 2.47 | Comparison between the thermal impedance calculated by the FEM model (continuous line) and that given by a 3-stage LE empirical Foster's network (stars). The profile corresponds to a power step of $0.5 \text{ W/finger}$ and the temperature is taken at the hottest point of the finger.                                          | 95  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

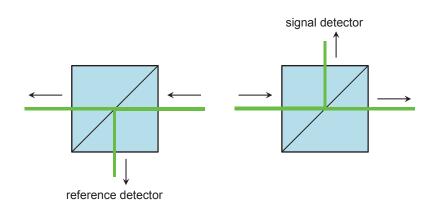

| 3.1  | Working principle of a beamsplitter. The primary incoming beam (left) is split<br>into two components; the reflected beam (right) is split as well; the position<br>of suitable detectors are shown                                                                                                                                   | 100 |

| 3.2  | The beamsplitter cased in an aluminum box and mounted on a support to<br>be fixed on the laser path (left). The detector is not shown here. The final<br>arrangement used for thermoreflectance measurements (right): from left, the<br>confocal microscope, the beamsplitter section, and the laser source                           | 101 |

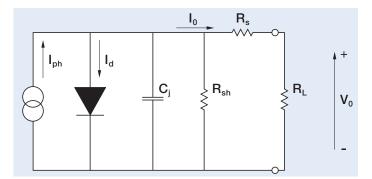

| 3.3  | Equivalent circuit of a photodiode.                                                                                                                                                                                                                                                                                                   | 102 |

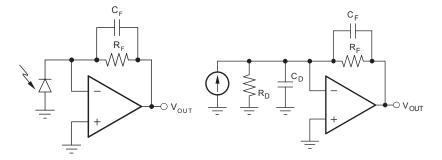

| 3.4  | Basic transimpedance amplifier (left). Transimpedance amplifier with a de-<br>tailed model of the photodiode (from [35]) (right).                                                                                                                                                                                                     | 102 |

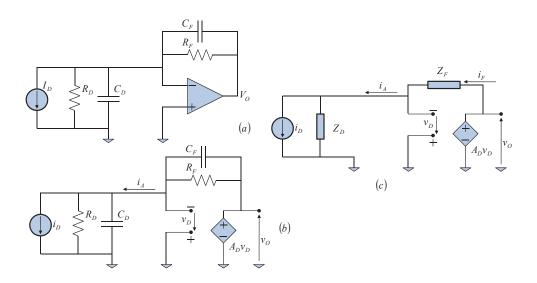

| 3.5  | Schematic for deriving the transfer function of the IV converter: $(a)$ large signal circuit, $(b, c)$ linearized circuit.                                                                                                                                                                                                            | 103 |

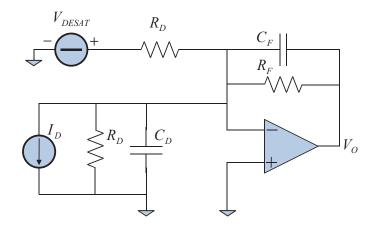

| 3.6  | Modified I/V converter with the addition of a second input $V_{\text{DESAT}}$ to desat-                                                                                                                                                                                                                                               |     |

|      | urate the opamp output                                                                                                                                                                                                                                                                                                                | 105 |

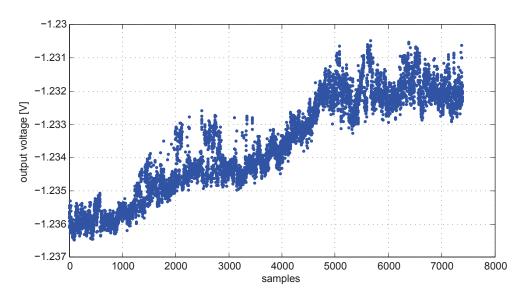

| 3.7  | Output voltage of the modified IV converter in function of time. Each point is sampled every 0.25 s. An effect of drift stabilizing can be noted after the first 5000 samples.                                                                                                                                                        | 107 |

| 3.8  | Time behaviour of the laser power over some hours of operation. Samples are                                                                                                                                                                                                                                                           |     |

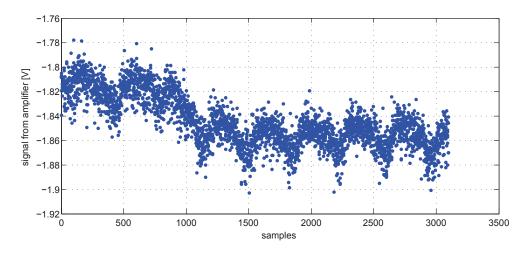

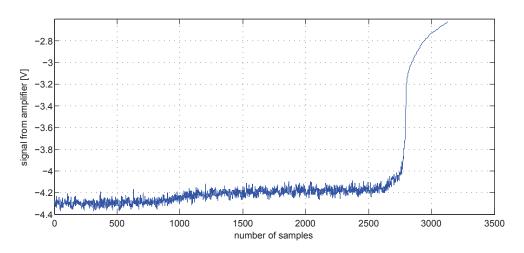

| 0.0  | taken every $3 	ext{ s. } \dots $                                                                                                                                                                                               | 108 |

| 3.9  | Time behaviour of the battery-powered amplifier until complete depletion of battery. The overall observation window is roughly 10 hours.                                                                                                                                                                                              | 109 |

| 3 10 | The thermoreflectance measurement bench.                                                                                                                                                                                                                                                                                              | 110 |

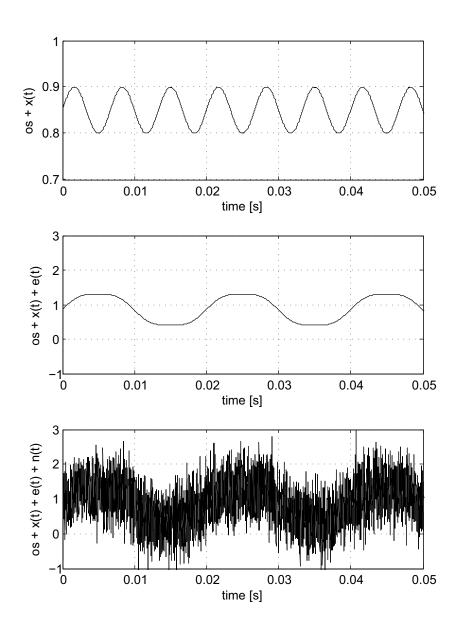

|      | (top) The signal $x(t)$ with offset os. (center) the sum of $x(t)$ and the line noise $e(t)$ . (bottom) The sum $x(t) + os + e(t)$ plus random noise source                                                                                                                                                                           | 110 |

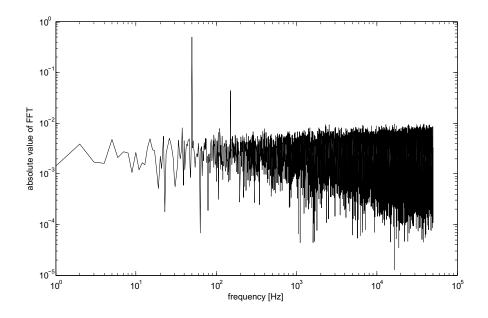

| 3.12 | FFT of the signal shown in Figure 3.11 (bottom). The two peaks corresponding to the line noise $e(t)$ , centered at 50 Hz, and to the signal $x(t)$ , centered at 150 Hz, are clearly visible.                                                                                                                                        | 115 |

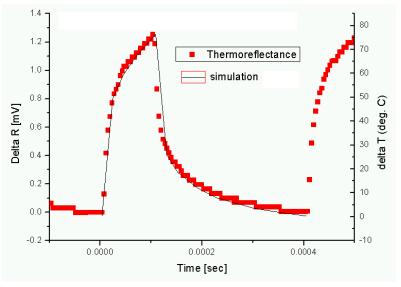

| 3.13 | Comparison between simulation results and termoreflectance measurement.<br>The match between the two curves is excellent, but the reflectance signal still                                                                                                                                                                            | 110 |

|      | does not translate into a temperature scale.                                                                                                                                                                                                                                                                                          | 116 |

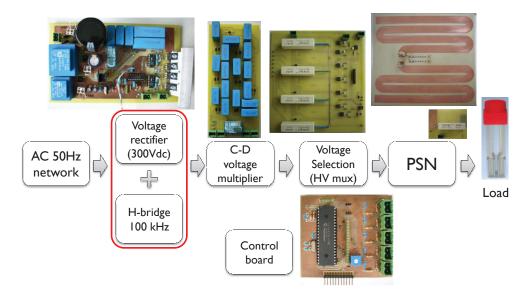

| 4.1  | Overview of the pulse generator bench                                                                                                                                                                                                                                                                                                 | 121 |

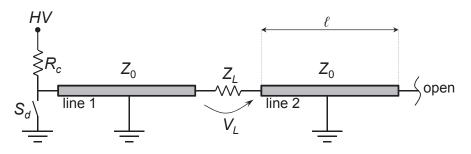

| 4.2  | A pulse generator made with a Blumlein line. The Blumlein arrangement is<br>made of a couple of equal transmission lines, line 1 and line 2, with the same<br>length $\ell$ and the same characteristic impedance $Z_0$ . The lines are charged to<br>the voltage $HV$ by a charging resistance $R_c$ , and discharged by closing the |     |

|      | switch $S_d$                                                                                                                                                                                                                                                                                                                          | 123 |

## List of Figures

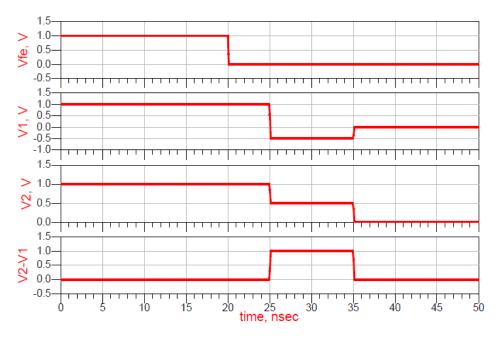

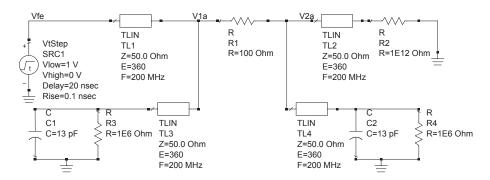

| 4.3  | Time-domain simulation results of a Blumlein line. From top: the pulse applied to the left end of line 1, the voltage at the left terminal of the load resistance, the voltage at the right terminal of the load resistance, and the voltage across the load (according to the notation in Figure 4.2). $\ell = 1 \text{ m}$ , $Z_0 = 50 \Omega$ , $Z_L = 100 \Omega$ . | 123 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

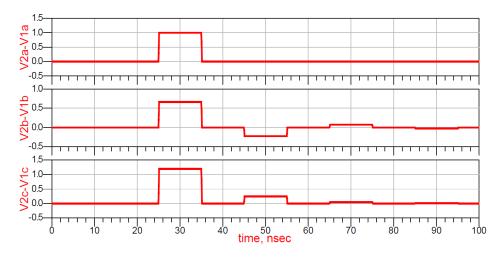

| 4.4  | The shape of the pulse across the load in a Blumlein line made of $50 \Omega$ lines,<br>for three different loads: (top) load perfectly matched $(Z_L = 100 \Omega)$ , (center)<br>$Z_L = 50 \Omega$ , (bottom) $Z_L = 150 \Omega$ .                                                                                                                                    | 124 |

| 4.5  | Schematic used to simulate the effect of the connection of two coaxial cables (TL3 and TL4), to measure the pulse shape by an oscilloscope. The oscilloscope channel input impedance has been taken into account. $R_2 = 1 \text{ T}\Omega$ is used to simulate the open circuit at the right end of transmission line 2 (Figure 4.2).                                  | 124 |

| 4.6  | Simulated effect of two additional coaxial cables used to measure the pulse in the circuit of Figure 4.5.                                                                                                                                                                                                                                                               | 125 |

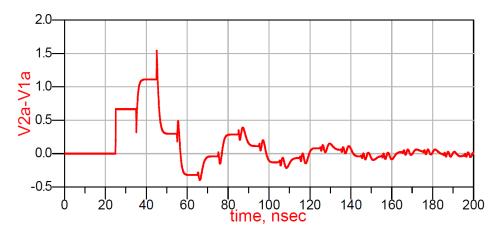

| 4.7  | (left) Single-stage voltage multiplier powered by a square wave voltage generator; (right) transient simulation results of input voltage (square wave with amplitude of $300 \text{ V}$ and frequency $50 \text{ Hz}$ ) and output voltage                                                                                                                              | 127 |

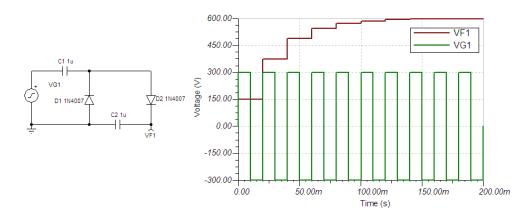

| 4.8  | (left) Schematic of a three-stage voltage multiplier; (right) simulated transient waveforms of the first, second and third output voltage, and voltage supply                                                                                                                                                                                                           | 107 |

| 1.0  |                                                                                                                                                                                                                                                                                                                                                                         | 127 |

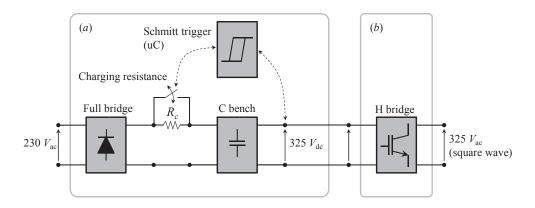

| 4.9  | A system view of the power section: (a) the rectifier; (b) the inverter                                                                                                                                                                                                                                                                                                 | 131 |

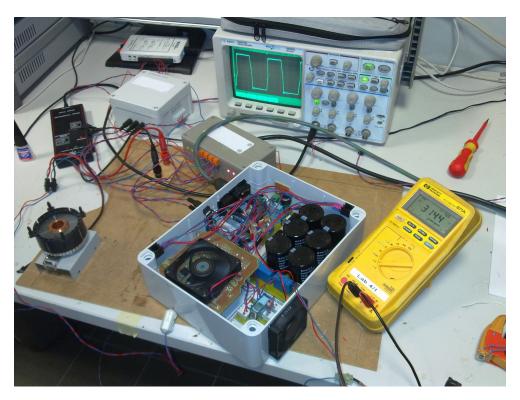

| 4.10 | 1 I                                                                                                                                                                                                                                                                                                                                                                     | 133 |

| 4.11 | The power load used to test the power supply: (left) top view of the fan used to cool down the resistors; (right) a bottom view in which the two TO247-                                                                                                                                                                                                                 | 100 |

|      | packaged $1 k\Omega$ power resistors are visible                                                                                                                                                                                                                                                                                                                        | 133 |

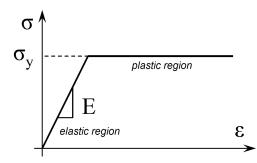

| A.1  | Perfect elasto-plastic stress-strain model for a given material.                                                                                                                                                                                                                                                                                                        | 137 |

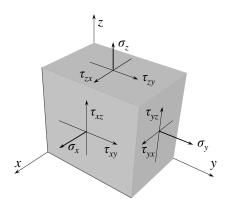

| A.2  | A small element on which a three-dimensional stress is acting                                                                                                                                                                                                                                                                                                           | 138 |

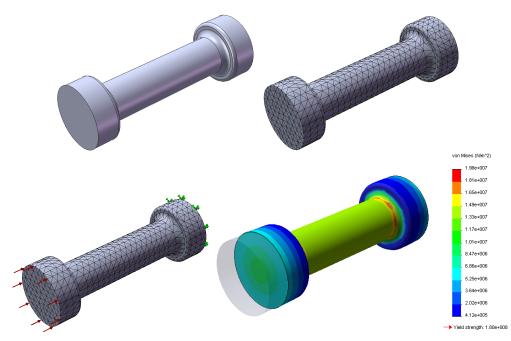

| A.3  | An example of mechanical analysis performed on a specimen: (top left) the specimen drawing; (top right) the discretization of the specimen for the FE analysis; (bottom left) the application of loads and constraints on the specimen; (bottom right) an example of Von Mises stress distribution over the structure after the solution of the FE model.               | 140 |

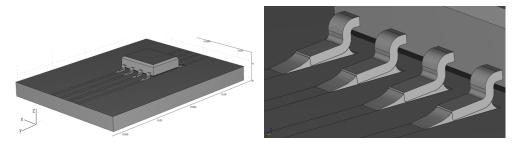

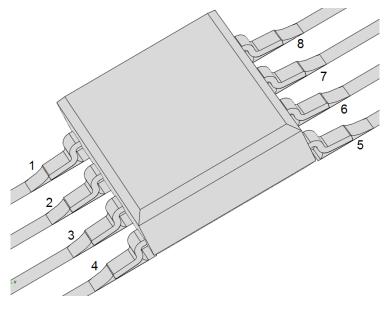

| A.4  | (left) View of the modeled structure. An SO-8 packaged device sits on a small FR4 board. (right) A blow-up of the structure highlighting the shape of the                                                                                                                                                                                                               |     |

|      | solder joints.                                                                                                                                                                                                                                                                                                                                                          | 141 |

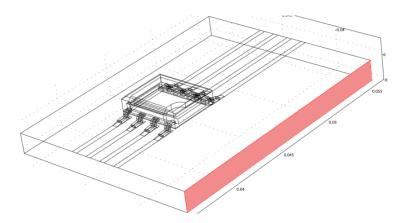

| A.5  | The mechanical constraint applied to the assembly: the board is fixed on the highlighted surface.                                                                                                                                                                                                                                                                       | 143 |

| A.6  | The solder joints numbered from 1 to 8, respectively                                                                                                                                                                                                                                                                                                                    | 145 |

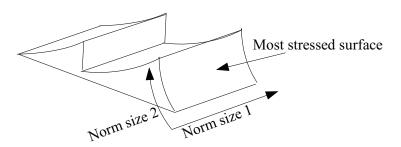

| A.7  | The most stressed surface of the most stressed solder joint in the case of an                                                                                                                                                                                                                                                                                           |     |

|      | applied power cycle, pointed out by the arrow.                                                                                                                                                                                                                                                                                                                          | 146 |

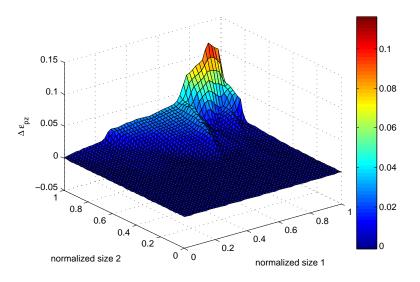

| A.8  | Three-dimensional plot of $\Delta \varepsilon_{pz}$ versus normalized dimension 1 and dimension |     |

|------|-------------------------------------------------------------------------------------------------|-----|

|      | 2 of the most stressed surface of the most stressed solder joint, when the device               |     |

|      | is dissipating 0.75 W                                                                           | 147 |

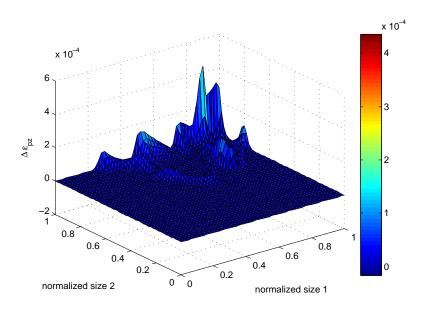

| A.9  | Three-dimensional plot of $\Delta \varepsilon_{pz}$ versus normalized dimension 1 and dimension |     |

|      | 2 of the most stressed surface of the most stressed solder joint, when the device               |     |

|      | is dissipating $0.15 \mathrm{W}$                                                                | 148 |

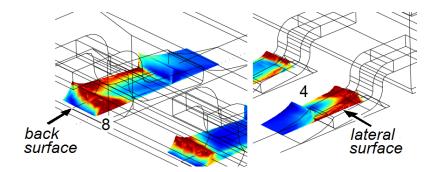

| A.10 | The most stressed surfaces in the structure, in the case of a thermal cycle.                    |     |

|      | These are the lateral surface of the solder joint 4, and the back-surface of the                |     |

|      | solder joint 8. The red areas are that where the joints plasticize.                             | 149 |

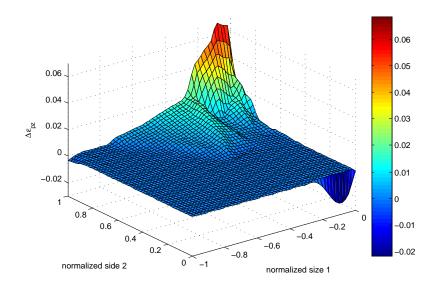

| A.11 | Three-dimensional plot of $\Delta \varepsilon_{pz}$ versus normalized dimension 1 and dimension |     |

|      | 2 of the most stressed surface of the most stressed solder joint, after a thermal               |     |

|      | cycle                                                                                           | 149 |

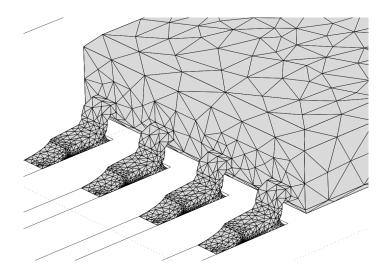

| A.12 | In inset of the structure showing the mesh related to the device only. The main                 |     |

|      | attention has been focused on solder joints, thus the mesh of other domains                     |     |

|      | has been kept at a coarser level                                                                | 151 |

<u>X</u>\_\_\_\_\_

# List of Tables

| 1.1 | Values of thermal conductivities $\lambda$ used in the simulation                                                                                                        | 15  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.2 | Fitting parameters used for tuning the test-board FEM model                                                                                                              | 18  |

| 1.3 | Comparison between measured and simulated temperatures at various points of the test board. The ambient temperature is 26 °C and the DUT dissipates 3.3 W.               | 20  |

| 2.1 | Comparison between measured and modeled temperatures obtained<br>from FEM and LEM models (in °C). The MOSFET dissipates 21.2 W,<br>and the ambient temperature is 26 °C. | 64  |

| 4.1 | Summary of the the various components in the bench                                                                                                                       | 131 |

| A.1 | Thermal and mechanical properties of the materials present in the as-<br>sembly.                                                                                         | 142 |

## Introduction

The work covered in this thesis is focused mainly on four topics.

**Chapter 1** focuses on the use of the Finite Element Method (FEM) to study the thermal dynamics in power devices, power electronics boards, and assemblies. The work is focused on thermal and fluid-thermal aspects of the components of a Switching Mode Power Supply used to supply detectors for High-Energy Physics Experiment performed at CERN, where the power supply has to be designed in order to meet stringent thermal constraints.

**Chapter 2**, which is the central chapter of this thesis, is focused on the selfconsistent, electro-thermal modeling of power devices. A primary concern in device modeling is the correct evaluation of the device channel temperature. In particular, while plenty of accurate electro-thermal, large-signal device models are available nowadays, the *thermal* aspect is often overlooked or poorly accounted for in the simulation process. Although it is possible to develop accurate thermal models by means of FEM, for instance, these do not lend themselves to be inserted into circuit simulators. A solution has been found in the Lumped-Element (LE) thermal modeling, in which thermal resistances and thermal capacitances are used to model the thermal dynamics of a given device. The approach shown here is based on the physical dimensions and material characteristics of the device, and it accounts for three-dimensional effects, non-linearities in thermal conductivities, complex boundary conditions, modeling both thermal steady-state and transients, without using fitting parameters. This approach has been applied to several device structures, and compared with FEM simulations, with excellent results. When this approach becomes impractical due to the complexity of the structure, empirical compact Foster thermal networks have been used, and a simple automated way to optimize the fitting process will be shown.

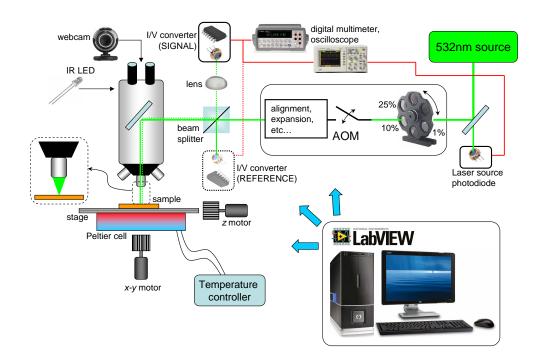

Chapter 3, which focuses on *thermo-reflectance* thermal measurement, describes the work performed at Centre for Device Thermography and Reliability (CDTR), H. H. Wills Department of Physics, University of Bristol (UK). The development of a bench to perform high-spatial resolution thermal measurement by the *thermo-reflectance* contact-less method is described here. This technique is based on the surface reflectance change with temperature.

**Chapter 4** is focused on a secondary activity aimed at the development of an electronic bench to generate high-voltage pulses (kV amplitude), with nano-seconds time duration, for biomedical applications; in particular the final goal is to perform studies on the possibility of reactivating *apoptosis* in cancer cells. This is still work-in-progress and this chapter describes the activity carried out so far, and the future developments.

Three appendixes complete the thesis: the first appendix is a complement to Chapter 1, in which the FE method is used to create a preliminary model describing the accumulated damage of soldering joints in electronic components (the so called *fatigue*); the second appendix is the Matlab code to implement the FFT routine used to post-process the data obtained from *thermo-reflectance* measurements, described in Chapter 3; the third appendix is the list of publications.

# Thermal and thermo-fluid dynamics FEM modeling of power modules

This Chapter deals with a numerical thermo-fluid-dynamic study of power assemblies; in particular the study will be focused on the thermal behavior of a *Switching Mode Power Supply* (SMPS) which has been the main topic of a project carried out by the Universities of Parma, Cassino, Milano and Padova in the context of the PRIN 2007 project. In particular, the task was the complete re-design of the SMPS used to supply detectors in the ATLAS experiment at CERN (Genéve). This chapter will show the simulation procedure which has been followed to obtain a quantitative description of the thermal behavior of the entire assembly.

## 1.1 Introduction

PRIN 2007 was a project in which the task was, basically, the re-design of a SMPS with stringent thermal constraints. In this section, some technical details about the SMPS will be given, for the sake of completeness (even if this part has been mainly developed by the University of Milano) and to frame the problem. The particular features of this SPMS can be summarized as follows:

- $\diamondsuit$  the ability of working in the presence of high magnetic fields (typical of high-energy experiments);

- $\diamond$  the ability of working with high power density, giving rise to very low temperature increase, with liquid cooling capability (not to heat the detectors, which are very close to the SMPS itself);

Figure 1.1 – Schematic of the SMPS (reprinted from [1]).

$\diamond$  the extremely high reliability, achieved by the introduction of redundancy (due to the location and to the impossibility of stopping the experiments for servicing defective parts).

The electrical schematic of the SMPS used in this project is shown in Figure 1.1: this SMPS is basically a phase-shift converter, in which one couple of transistors  $(S_1, S_3)$  is turned on in opposite phase with the other couple  $(S_2, S_4)$ , and viceversa. Further details about the operation of this SMPS can be found in [1]. The conversion ratio of this converter is 280:14. The details that will be given below are just to introduce the project, since the chapter will discuss mainly the tasks of the University of Parma. The fluid-mechanical specifications of the assembly are the following, as set by the partners of the project:

- $\diamond~$  the power supply case is made of 1510 steel, 2 mm thick, with external dimensions of 150 mm  $\times~285$  mm  $\times~402$  mm;

- $\diamondsuit$  the number of modules in a case is three;

$\diamond$  the overall power dissipated by the modules is 800 W with a 2+1 redundancy; it means that, during normal operation conditions, all 3 modules are working and each one dissipates a power of 267 W; in case of failure of one modules, the other two have to supply the overall power, thus dissipating 800/2 = 400W each. This is the worst case situation.

A mandatory step in the design is the liquid-cooling system, in this case a watercooled aluminum heat-sink for each module in the case. The cooling specifications are the following:

- $\diamond$  the water flow is 1.91/min, the maximum pressure drop is 0.35 bar, the inlet water temperature is 18 °C and the maximum temperature for the outgoing water is 25 °C;

- $\diamondsuit$  the heat-sink is an aluminum one, with a thickness of 15 mm and a channel diameter of 5 mm.

The theoretical power that can be extracted from such a heat-sink is given by:

$$Q = C_p \times \Delta T \times F = 4186 \cdot (25 - 18) \cdot \frac{1.9}{60} \simeq 928 \,\mathrm{W}$$

(1.1)

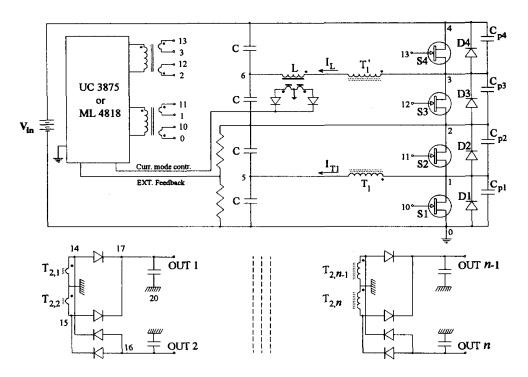

where  $C_p$  is the specific heat of water in  $[J/(kg \cdot K)]$  at constant pressure,  $\Delta T$  is the temperature difference between outgoing and incoming water in [K], and F is the water mass flow (mass per unit time) in [kg/s]. Since the maximum dissipated power is 800 W, i.e., below the theoretical limit, the problem is now how to design the board to achieve as uniform as possible a temperature distribution over the board itself (avoiding areas in which the dissipated power gives rise to high temperature increases, or hot spots, that can be dangerous for the sensitive instrumentation close to the SMPS). In Figure 1.2, the structure of a single case containing three SMPSs with their heat-sinks is shown. Once the problem is fully defined, the next step is to develop a numerical model of the object under study. The tool used to develop the numerical model is the Finite Element Method (FEM). The object under study changes at every design step, because at the beginning the attention has been focused just on the case with the three boards (as in Figure 1.2, in which no details are given at the board contents), while in further design steps many additional details have been made available, and the attention has been focused on different components. The next sections will illustrate this approach, which follows the temporal evolution of the design (some parts will be intentionally neglected, since they were found not to be relevant to the design process).

Figure 1.2 – The metal case with the three power supply modules and heat-sinks.

## 1.2 The thermo-fluid dynamics simulation process

In this part, the approach followed to describe the thermo-fluid dynamics inside the case will be shown. The device studied is a structure like the one shown in Figure 1.2, in which the power density is *not* representative of the effective power distribution, since the layout of the board (and thus the power sources that heat the board itself) is not known at this stage of the design. The aim of this stage is, basically:

- $\diamond$  to learn and improve the capability of *how* to build a numerical model in which the thermal dynamics and the fluid motion dynamics are simulated at the same time;

- $\diamondsuit$  to test the performance of the simulator, especially in solving fluid-dynamic problems;

- $\diamondsuit$  to reduce the computational complexity as much as possible, for reasons that will be explained shortly.

First of all, a brief review of the physical equations related to the analyzed problems is following.

#### **1.2.1** Heat equations

The thermal dynamics is described by means of the Fourier's law of heat propagation in solids, which can be written as follows for the most general case:

$$\varrho \cdot C_p \cdot \frac{\partial T}{\partial t} = \nabla (\lambda \cdot \nabla T) + q_g \tag{1.2}$$

where the meaning of different symbols is:  $\rho$  is the density of the material in [kg/m<sup>3</sup>],  $C_p$  is the specific heat of the material in [J/(kg · K)], T is the temperature in [K],  $\lambda$  is the thermal conductivity of the material in [W/(m · K)], and  $q_g$  is the heat generated per unit volume, expressed in [W/m<sup>3</sup>]. The operator  $\nabla$  is a compact way for defining divergences and rotors, and can be written as a vector<sup>1</sup> as follows:

$$\nabla = \mathbf{i}\frac{\partial}{\partial x} + \mathbf{j}\frac{\partial}{\partial y} + \mathbf{k}\frac{\partial}{\partial z}$$

(1.3)

where it is supposed to use a cartesian reference system, in which  $\mathbf{i}, \mathbf{j}, \mathbf{k}$  are the versors of the x, y, z axes, respectively.

In some cases, Eqn. (1.2) can be simplified. In particular, in the case of study, the term  $q_g$  is null, transients are not of interest (thus, time derivatives goes to zero), and the thermal conductivities of materials are considered isotropic (it means that, for each single domain,  $\lambda$  does not depend on the direction of heat propagation). Eqn. (1.2) can thus be reduced to the following:

$$0 = \nabla^2 T. \tag{1.4}$$

Eqn. (1.4) is the equation that will be used to define the thermal problems in the rest of the study.

Once the equation has been defined for the domain, one must fix some boundary conditions, basically to define the "inputs" of the system. There are several types of boundary conditions, which describe how the body exchanges heat with the surrounding environment. There are three types of boundary conditions (T is the temperature over the surface):

- fixed temperature in which we are going to fix the temperature over a surface of a body:  $T = T_0$ ;

- **fixed heat flux** in which the thermal flux is fixed through a surface. Matematically:  $q = q_0 + h(T - T_{ref})$ , where q is heat flux per surface unit in [W/m<sup>2</sup>],  $q_0$  is the imposed flux,  $T_{ref}$  is a reference temperature, and h is a heat exchange coefficient, or *convective* coefficient, that accounts for the fluid motions near the surface of interest; the physical concepts behind this simple condition are important, and then they will be explained shortly;

$<sup>^1\</sup>mathrm{It}$  can be applied both to vectors and scalars, with both the scalar or vectorial product.

radiative convection in which the surface and the environment exchange heat by means of radiation, basically emitting/receiving electromagnetic waves. It is expressed by:

$$Q = \varepsilon \cdot \sigma \cdot A \cdot (T_S^4 - T_C^4) \tag{1.5}$$

where Q is the power supplied by the body in [W],  $\varepsilon$  is a coefficient – the emissivity of the body (1 for black bodies, 0 for white bodies),  $\sigma$  is the Stefan-Boltzmann constant equal to  $5.67 \times 10^{-8} [W/(m^2 K^4)]$ , and A is the area in  $[m^2]$  of the surface which is irradiating towards the ambient.  $T_S$  and  $T_C$  are the surface and the surrounding environment temperatures, respectively.

The sign for the heat flux is conventional, since the heat exchange can be bi-directional.

The convective boundary condition deserves to be explained in full detail. Consider, for example, an horizontal hot surface in contact with air. The air close to the surface tends to be hot, and to flow away from the surface (thus removing heat from the surface), and when the air cools down it flows again on the surface, and so on. The meaning of the parameters  $T_{ref}$  and h can be easily understood after some simple observations. It is obvious that the convective motions are related to a restricted volume of fluid, in particular that close to the surface: it can be assumed that, far enough from the surface, the fluid is in quiet, and also the temperature of the fluid itself is constant. This is the meaning of  $T_{\rm ref}$ . Then, if the fluid is changed (for example water instead of air), or the temperature difference is increased, or a fan is used to force the fluid motion, the efficiency of heat exchange is modified. This is the meaning of h, which can itself be temperature dependent, which accounts for the *efficiency* of the thermal exchange. In general, then, h = h(T); some values<sup>2</sup> can be found in [2, 3]. The coefficient h can vary over a wide range, from  $2-25 \, [W/(m^2 K)]$  for natural convection up to  $10^5 \,[W/(m^2 K)]$ , for the case of liquid cooling with condensation (far improving the efficiency).

Another brief observation about the sign of the heat flux in the boundary conditions. Let us consider for example the convective boundary condition, here rewritten (in a slightly different form, assuming the flux  $q_0$  null and considering the area  $A [m^2]$ of the surface: thus, the power is in [W] instead of being per unit area):

$$Q = h \cdot A \cdot (T - T_{\rm ref}) \tag{1.6}$$

and let us consider Figure 1.3; if we consider a positive flux with the same direction of the vector normal to the surface, then a heating process is described by a negative flux (since  $T_{\rm ref} > T$  and then the direction of the flux is *opposite* to the direction of the surface versor), while a cooling process is described by a positive flux (since  $T_{\rm ref} < T$ ). This can be against common sense, since in practice a positive flux is considered to

<sup>&</sup>lt;sup>2</sup>The determination of the coefficient h is a very important step, as will be shown later on when the discussion will be focused on how to study the behavior of the heat-sink.