# Mains Power Quality Improvement using Active Filters

#### Robert V. Watson

A submission presented in partial fulfilment of the requirements of the University of Glamorgan/Prifysgol Morgannwg for the degree of Doctor of Philosophy

June 2009

R11

#### **Certificate of Research**

This is to certify that, except where specific reference is made, the work described in this thesis is the result of the candidate's research. Neither this thesis, nor any part of it, has been presented, or is currently submitted, in candidature for any degree at any other University.

| Signed | Candidate           |

|--------|---------------------|

| Date   |                     |

|        |                     |

| Signed | Director of Studies |

| Date   |                     |

#### **Preface**

The work contained in this thesis was carried out on a part time basis while employed as a Senior Lecturer at the School of Electronics of the University of Glamorgan and from 2006 onwards within the CCI Faculty of the University of Glamorgan.

Supervision was carried out by Dr Marcel Jayne (Director of Studies) and Dr David Rees.

### **Acknowledgments**

I would like to thank Dr Jayne for his advice and help throughout the time spent on this work and additionally Dr Rees for his advice in the preparation of this thesis. I would also like to thank Prof Jon Clare for his feedback following the viva.

I would like to thank my wife Jackie, for her continued support.

Finally I would like to acknowledge the help of my colleague Andrew Pennington during conversations on aspects of this work.

#### **Synopsis**

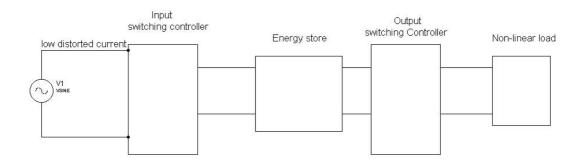

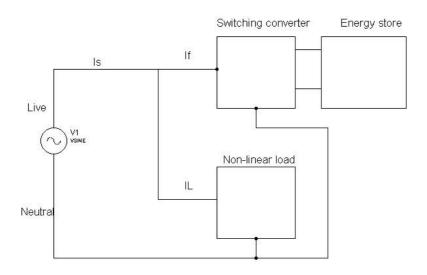

Improvements in the control of mains connected apparatus brought about by energy switching converters has resulted in disturbances to the supply current due to their non-linear characteristics. These disturbances result in a supply current that no longer retains the same shape and phase of the source Voltage which is the ideal requirement for a purely resistive load. The resulting current waveforms of these non-linear loads contain unwanted harmonics and non-unity power factors. EMC problems also arise as a consequence of the fast switching devices in the electronic control of power apparatus.

This thesis reports the results of an investigation into methods of actively filtering the unwanted harmonics from the supply current for single phase domestic applications. Designs were considered for loads up to a maximum of 15kW and simulations of such systems were carried out. Practical work was carried out at reduced Voltages and power levels to prove the viability of the developed theory. The focus of the work was initially to investigate the suitability of "Sliding Mode Control" for the control of the Active Power Filter (APF). Recent research investigations (see references [5.2], [5.3], [5.4], [5.5], [5.6], [5.7], [6.1]) indicated that this method achieved some success, however, after detailed investigation it was found that the sliding mode control methods of referenced papers did not provide the required steady state or dynamic response. A specific version of Sliding Mode based on a switching algorithm accounting for the practical limitations of physical devices called Discrete Sliding Mode (DSM) was developed. The conventional H-bridge was further developed by adding an additional inductor, two diodes and two switching devices allowing the system itself to change dynamically in response to load characteristics. Simulation models were derived based on the DSM technique and applied to the problem of harmonic reduction for a number of complex non-linear loads. Simulation results showed that the Sliding Mode technique was unnecessarily complex and unsuitable for the application of Active Filtering. Using averaging principles based on the flow of real power, detailed analysis of the dynamic response of several APF configurations was made possible. This work led to the development of a new control method called "Energy Compensation". Energy compensation in conjunction with the development of a new technique referred to as "Proportional Hysterisis Control"

allowed optimum placement of system poles in the Z-plane. A test system was built to demonstrate the proportional hysterisis control method using energy compensation. This test system provided a comprehensive user interface allowing all relevant control parameters to be varied and monitored. Good correlation was obtained between theoretical and practical results for steady state and transient responses (i.e. for loads that are assumed periodic but change after a few mains cycles) for a range of nonlinear loads.

# Several new ideas and techniques emerge in this thesis, a summary of which is as follows:

An algorithm is presented for applying Sliding Mode Control to a physical APF system taking physical switching devices into account including methods of deriving the reference signals. The theoretical developments are applied to the design of an enhanced APF bridge. A new discrete method is presented for analysing the APF system which is used to demonstrate the unsuitability of the sliding mode technique for APF control. The analysis method is further used to show how a control method can be obtained using "Energy Compensation" and "Proportional Hysterisis Control" that optimises the transient response and is shown to work well in a practical system.

### **Table of Contents**

| List | of Figures  | S                                                                     | .xiv |

|------|-------------|-----------------------------------------------------------------------|------|

| List | of Tables   | Σ                                                                     | xvi  |

| Glo  | ssary of To | erms x                                                                | vii  |

| Glo  | ssary of To | ermsx                                                                 | vii  |

| Cha  | apter 1     | An Introduction to the Thesis                                         | 1    |

|      | •           |                                                                       |      |

| 1.1  |             | Power Quality Problem                                                 |      |

| 1.2  |             | urvey of Active Power Filters                                         |      |

| 1.3  |             | of the reported research work and contribution to existing knowledge. |      |

|      | 1.3.1       | The Sliding Mode Method and the "Energy Compensation" method          |      |

|      | 1.3.2       | The APF Model                                                         |      |

|      | 1.3.3       | Practical Demonstration System                                        |      |

|      | 1.3.4       | Summary of the Contribution to Knowledge                              |      |

| 1.4  |             | as and Objectives                                                     |      |

| 1.5  | A G         | ruide to the Thesis                                                   | 12   |

| Cha  | apter 2     | Initial Investigations and Preparatory Theory                         | 14   |

| 2.1  | Lite        | rature Review                                                         | 1.5  |

| 2.2  |             | its of Harmonic Disturbance.                                          |      |

|      | 2.2.1       | Long and Short Term Harmonic Specification                            |      |

|      | 2.2.2       | Interpreting a Voltage THD specification                              |      |

|      | 2.2.3       | Voltage and current THD specification for higher current levels       |      |

|      | 2.2.4       | THD as a performance indicator                                        |      |

| 2.3  |             | ive and Reactive Power Calculations                                   |      |

|      | 2.3.1       | Active and reactive power calculations in a single phase sinusoidal   |      |

|      |             | system                                                                | 25   |

|      | 2.3.2       | Active, Reactive and Harmonic Power in a Single phase system with     | h    |

|      |             | periodic non-sinusoidal load current and APF control of the supply    |      |

|      |             | current                                                               | 28   |

|      | 2.3.3       | Defining Harmonic and Reactive Currents in the presence of a          |      |

|      |             | distorted Source Voltage                                              | 30   |

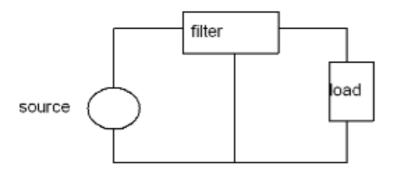

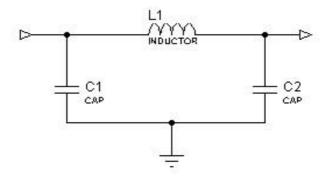

| 2.4  | Mai         | ns Harmonic Current removal: Passive and Active Filtering Methods     | .31  |

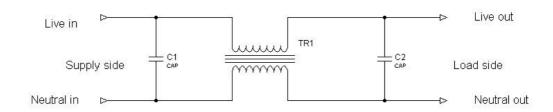

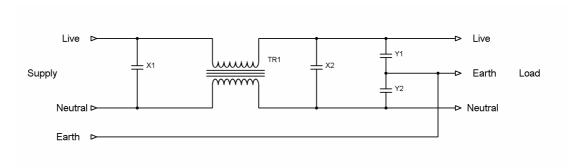

|      | 2.4.1       | Passive filtering                                                     | 31   |

|      | 2.4.2       | Active Filtering                                                      | 34   |

|      | 2.4.2.1     | Active Series Connected Filters                                       | 34   |

|      | 2.4.2.2     | Active shunt connected filters                                        | 35   |

|      | 2.4.2.3     | Active shunt filters synthesising a resistive load                    | 36   |

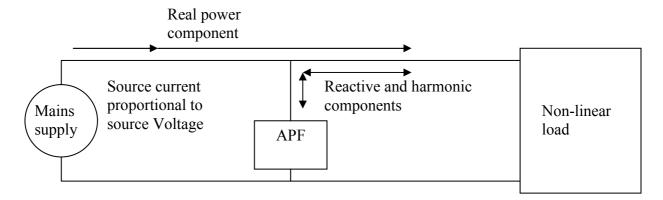

|      | 2.4.3       | Power Flow paths in a Shunt APF synthesising a resistive load         | 36   |

|      | 2.4.3.1     | C                                                                     |      |

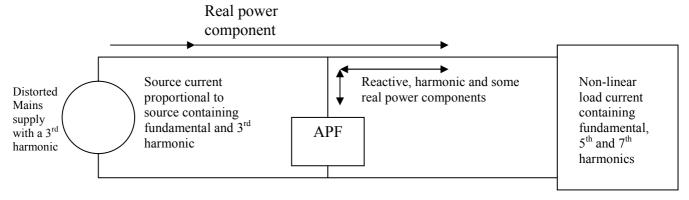

|      | 2.4.3.2     | When the source Voltage is distorted                                  | 37   |

| 2.5  | Con         | trol Strategies for Shunt Active Power Filters                        | 38   |

|      | 251         | Variable Structured Control                                           | 30   |

| Cha | pter 3  | The Application of Sliding Mode Control to the Shunt APF:                   | 44   |

|-----|---------|-----------------------------------------------------------------------------|------|

| 2 1 | C1: 4:  | Design Methods and Simulation                                               |      |

| 3.1 |         | ing Mode Control                                                            |      |

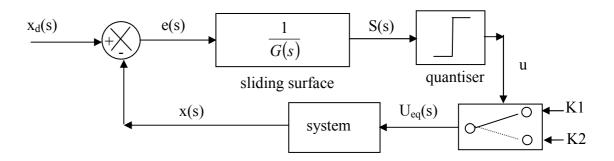

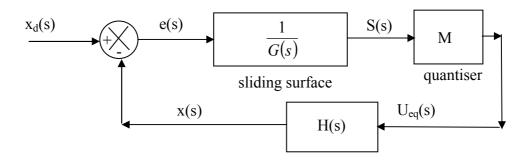

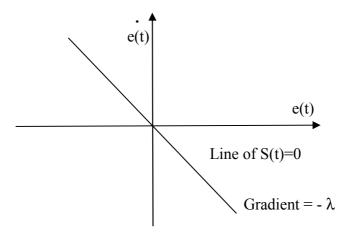

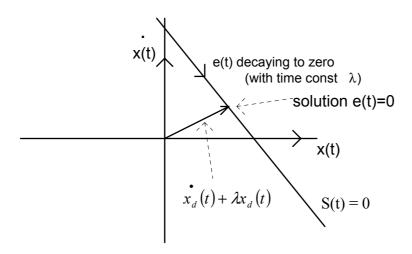

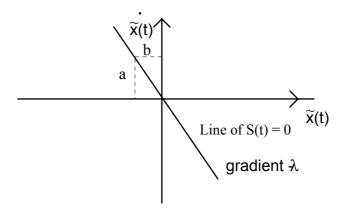

|     | 3.1.1   | Introduction to Sliding Mode Control                                        |      |

|     | 3.1.2   | An alternative viewpoint for the sliding control loop                       |      |

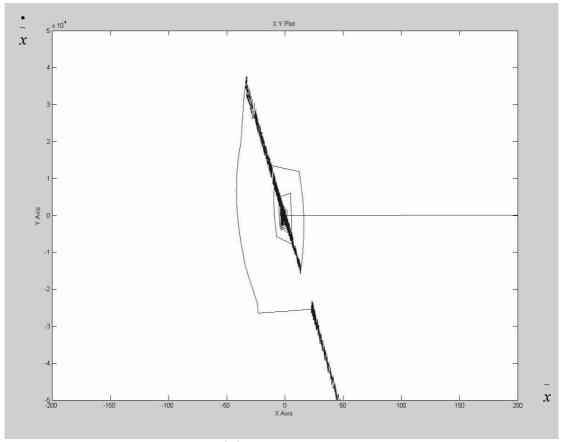

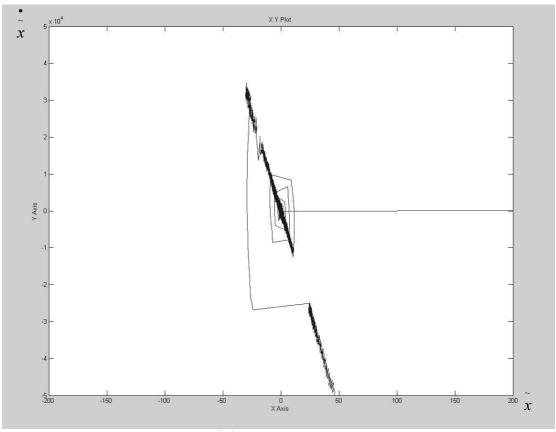

|     | 3.1.3   | Interpreting Pure Sliding Mode on a State Space diagram                     |      |

|     | 3.1.4   | The effect of extreme $\lambda$ values and a zero order surface             |      |

|     | 3.1.5   | Ensuring convergence to the switching surface                               |      |

|     | 3.1.6   | The Equivalent Dynamics while on the sliding surface                        |      |

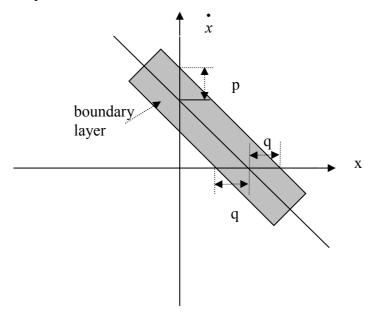

|     | 3.1.7   | The effect of "Chattering" in the design of a Sliding Mode Controlle System |      |

| 3.2 | Intro   | oducing the concept of Discrete Sliding Mode (DSM)                          |      |

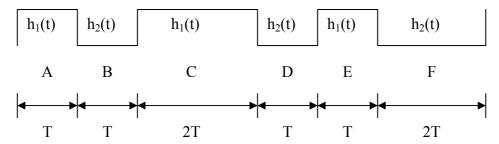

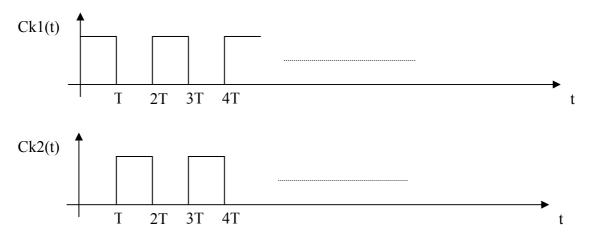

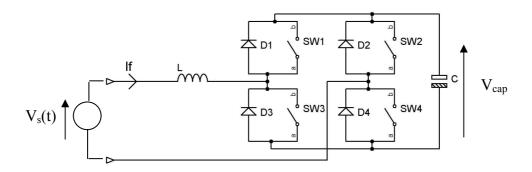

|     | 3.2.1   | Examining the spectrum of a System controlled using DSM                     |      |

| 3.3 |         | etailed discussion of the H Bridge and the Switching "Modes"                |      |

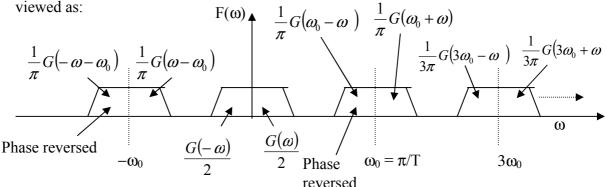

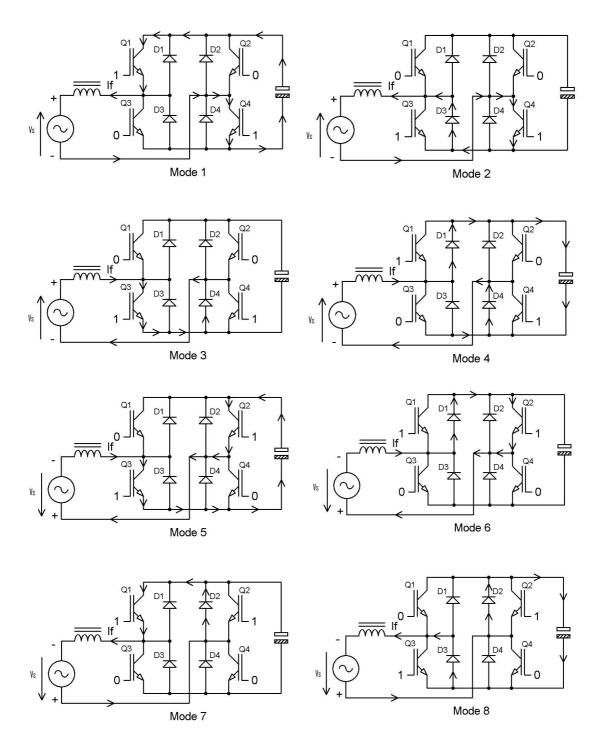

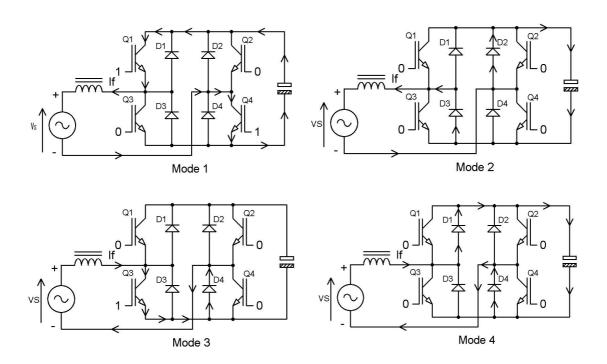

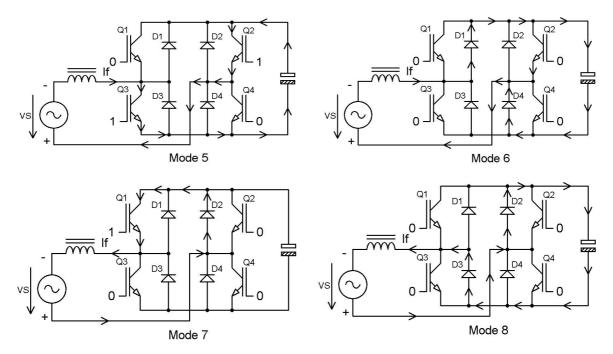

|     | 3.3.1   | Power, Energy and Current flow.                                             |      |

|     | 3.3.2   | Active and passive modes of the H-Bridge and Current flow paths             |      |

|     | 3.3.2.1 | •                                                                           |      |

|     | 3.3.2.2 | H-Bridge switching method 3: "Active" and "Passive"                         | 63   |

|     | 3.3.2.3 | Unipolar and Active/Passive modes                                           | 64   |

|     | 3.3.3   | The application of DSM to the Switching Mode considerations of the          |      |

|     |         | H-bridge                                                                    | 65   |

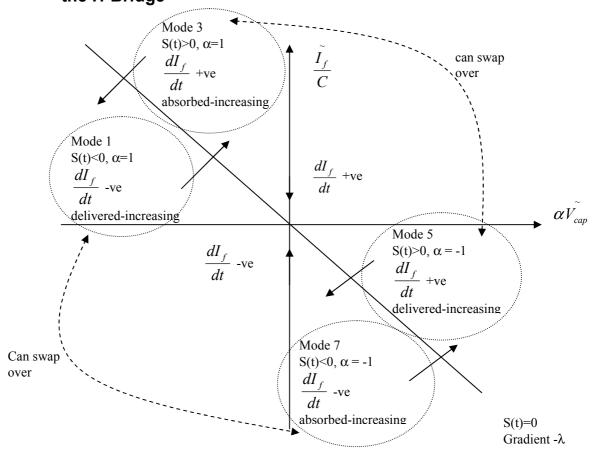

|     | 3.3.4   | State Space interpretation of the active switching phases of the H-         |      |

|     |         | Bridge                                                                      |      |

| 3.4 | Syst    | em Equation and the choice of Switching Variables                           |      |

|     | 3.4.1   | System Equations                                                            |      |

| 3.5 | Solv    | ring the System Equations in the Active Phases                              |      |

|     | 3.5.1   | When $\beta=0$                                                              | 70   |

|     | 3.5.2   | When $\beta = 1$                                                            |      |

|     | 3.5.3   | Plotting the equations for I <sub>f</sub> (t) and dI <sub>f</sub> (t)/dt    | 73   |

| 3.6 | Assi    | gning State variables for DSM and deriving the associated reference         | s 78 |

|     | 3.6.1   | Maximum order of the Sliding Space                                          | 78   |

|     | 3.6.2   | Assigning the physical state variables to define the DSM sliding            |      |

|     |         | surface                                                                     |      |

|     | 3.6.3   | Deriving the Reference for I <sub>f</sub>                                   |      |

|     | 3.6.4   | Obtaining the ideal input conductance                                       |      |

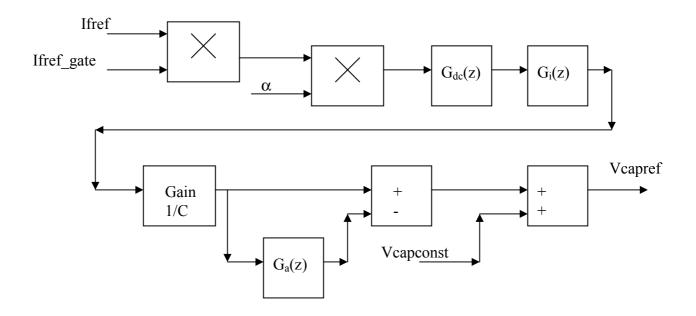

|     | 3.6.5   | The Sliding Equation and derivation of the reference for the capacit        | or   |

|     |         | Voltage (V <sub>capref</sub> )                                              | 84   |

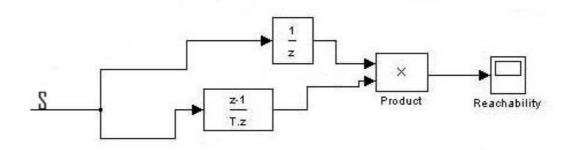

| 3.7 |         | g Lyapunov stability about the sliding surface to find the reaching         |      |

|     |         | ition                                                                       |      |

|     | 3.7.1   | Reachability Conditions                                                     |      |

|     | 3.7.1.1 | <b>5</b>                                                                    |      |

|     | 3.7.1.2 | 5                                                                           |      |

|     | 3.7.1.3 | J                                                                           |      |

|     | 3.7.1.4 | J                                                                           |      |

|     | 3.7.2   | Combined reachability conditions.                                           |      |

|     | 3.7.3   | Practical Implications of DSM on the Reachability Condition                 |      |

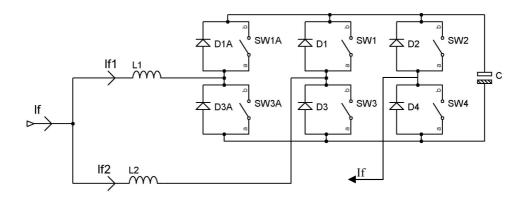

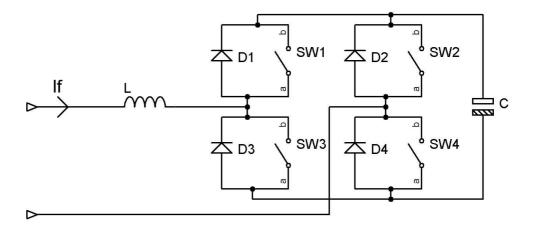

| 3.8 |         | Single Phase 3/2 H-Bridge                                                   |      |

| 3.9 |         | lication of Equivalent Dynamics to the H –Bridge                            |      |

|     | 3.9.1   | Applying Active Conditions to $\beta_{eq}$                                  |      |

|     | 3.9.2   | Switching control when β=0                                                  | 96   |

| 3.10  | De     | monstrating the advantages of a class $C^0$ current reference function | 96    |

|-------|--------|------------------------------------------------------------------------|-------|

| 3.11  |        | sign of the H-Bridge and the Derivation of Associated Component        |       |

|       |        | lues                                                                   | 99    |

|       | 3.11.1 | Considerations of Power Transistor specifications                      | 99    |

|       | 3.11.2 | Choosing T                                                             |       |

|       |        | •                                                                      |       |

|       | 3.11.3 | Selecting a minimum value for $I_f(t)$                                 |       |

|       | 3.11.4 | Criteria for Selecting $V_{capconst}$ , C, L and $\lambda$             | 104   |

|       | 3.11.5 | Design Values for a Prototype APF                                      | 108   |

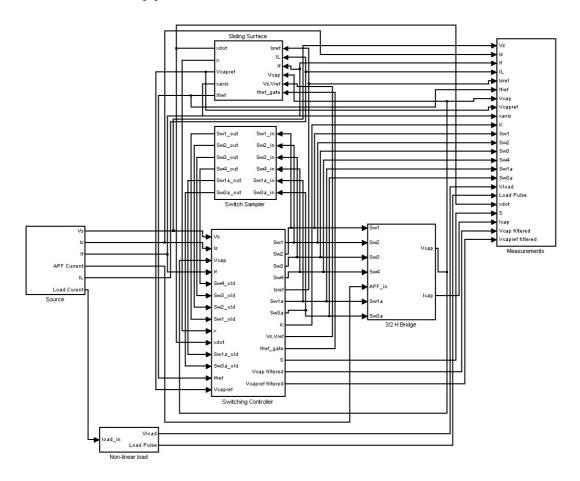

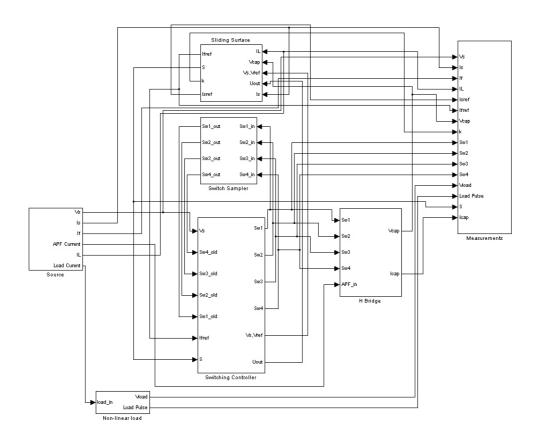

| 3.12  | De     | scription of the Model used for Simulation                             | 110   |

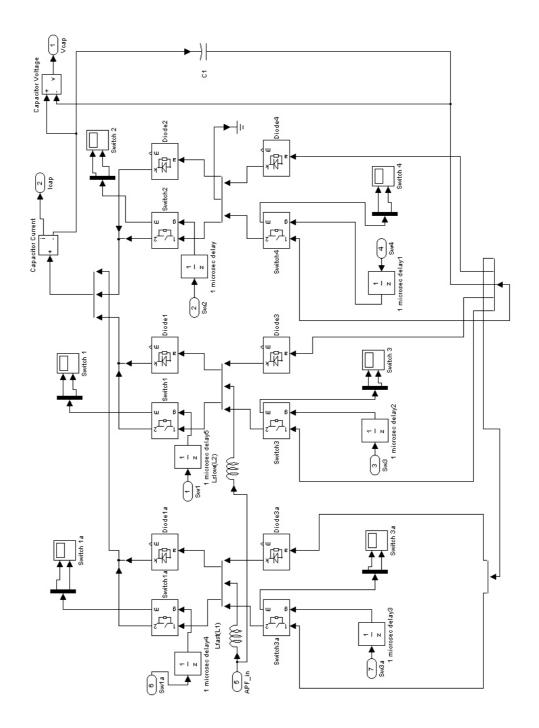

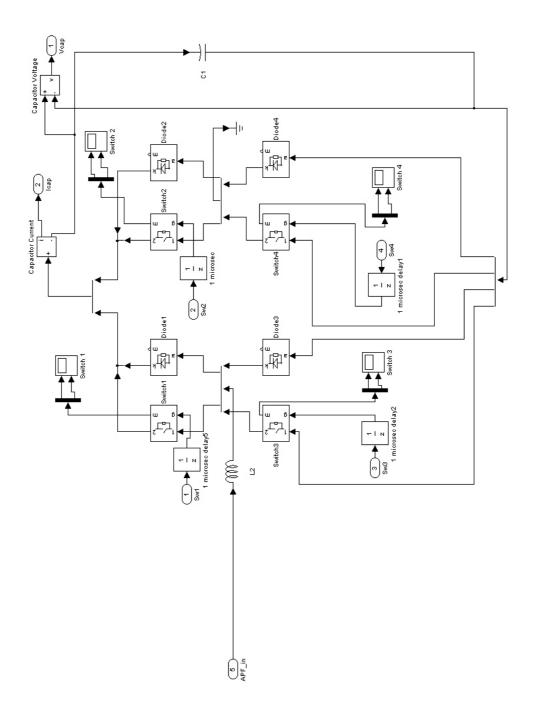

|       | 3.12.1 | Simulation block "3/2 H Bridge"                                        |       |

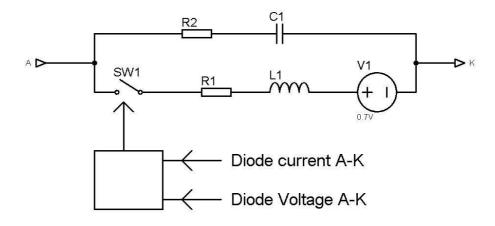

|       | 3.12.1 | 1.1 Overcoming Diode problems during Simulation                        | 112   |

|       | 3.12.1 | 1.2 Overcoming ideal switch simulation problems                        | 113   |

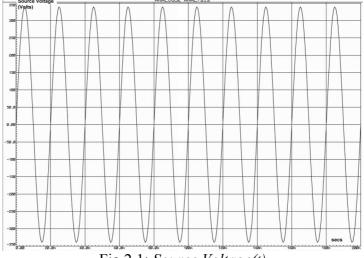

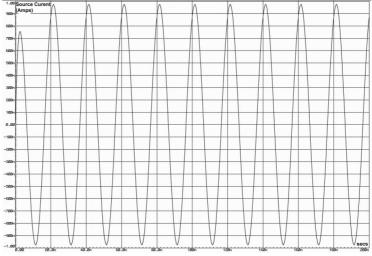

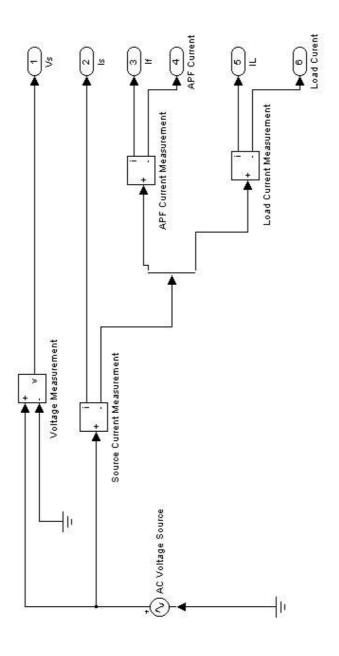

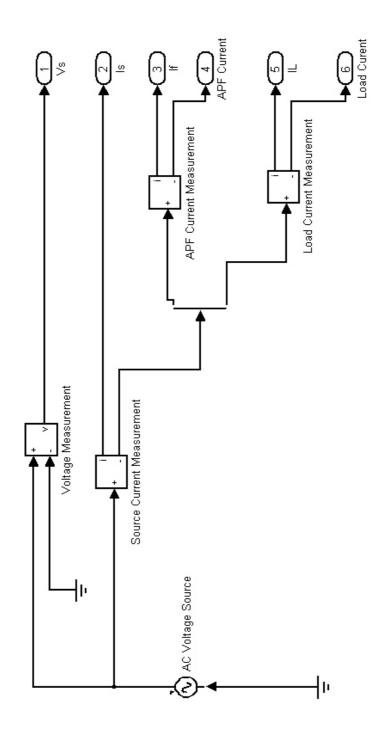

|       | 3.12.2 | Simulation block "Source"                                              |       |

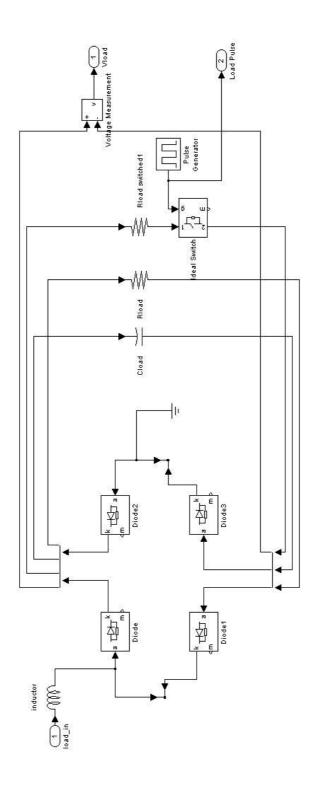

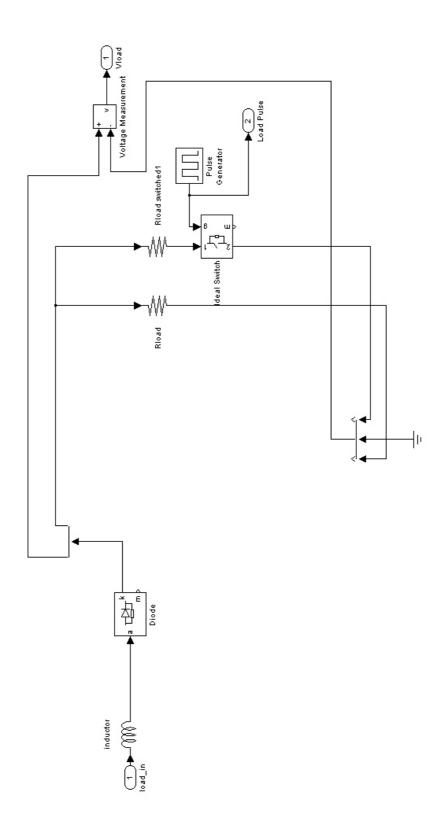

|       | 3.12.3 | Simulation block "Non-Linear Load"                                     | 114   |

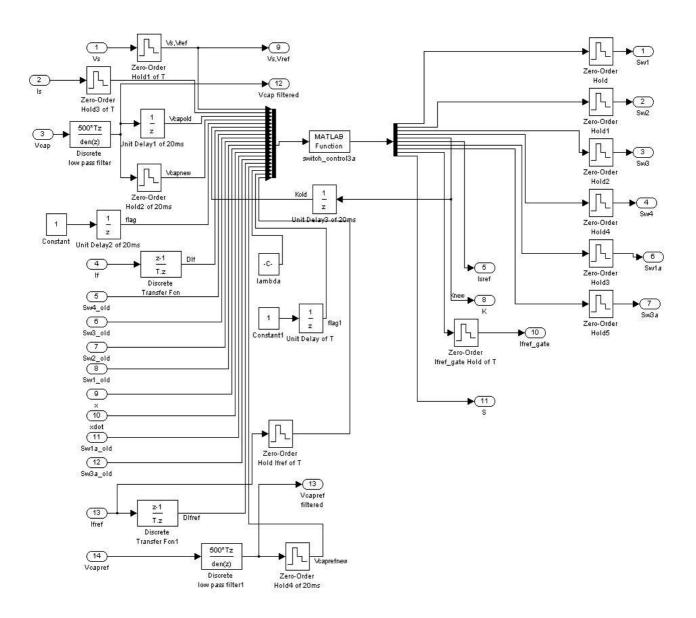

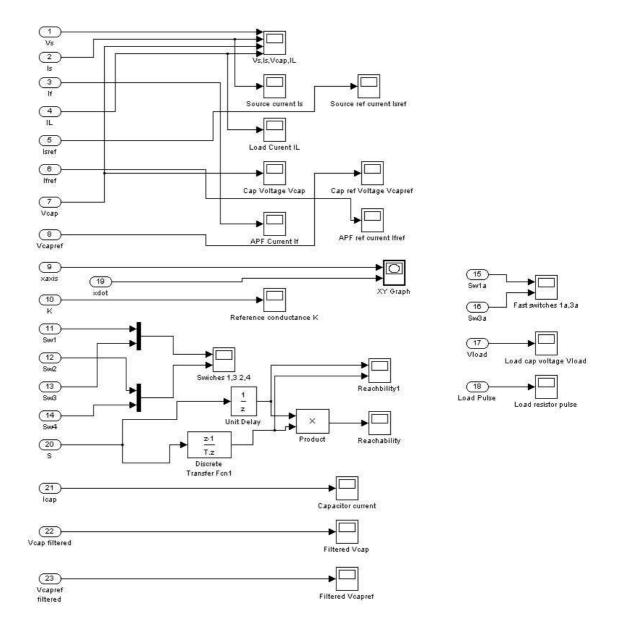

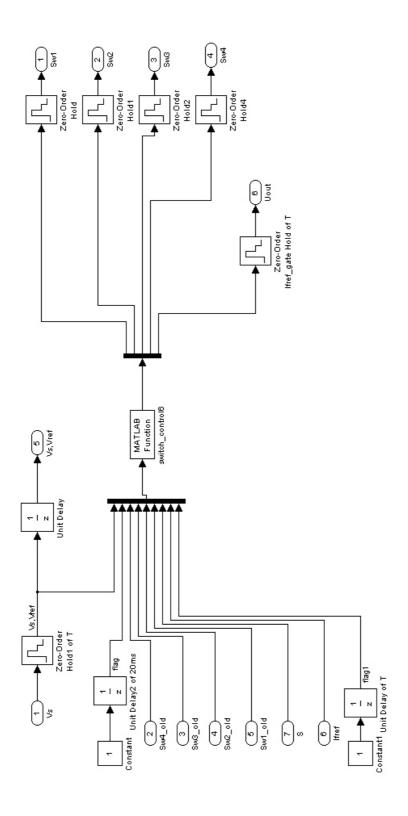

|       | 3.12.4 | Simulation block "Switching Controller"                                | 115   |

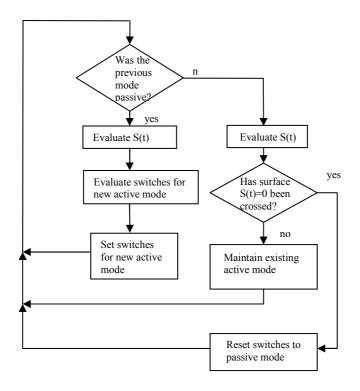

|       | 3.12.4 | 4.1 Details of "switch_control3a.m"                                    | 116   |

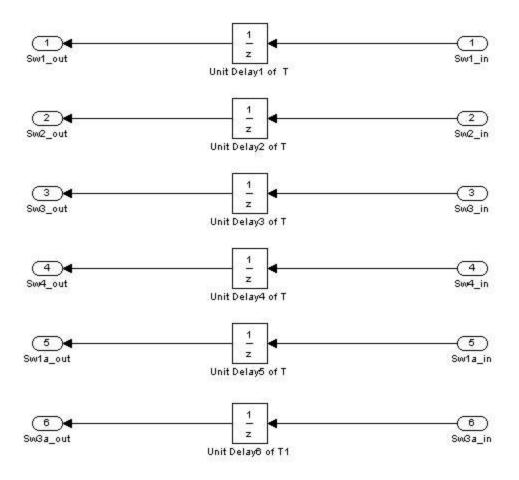

|       | 3.12.5 | Simulation block "Switch Sampler"                                      | 118   |

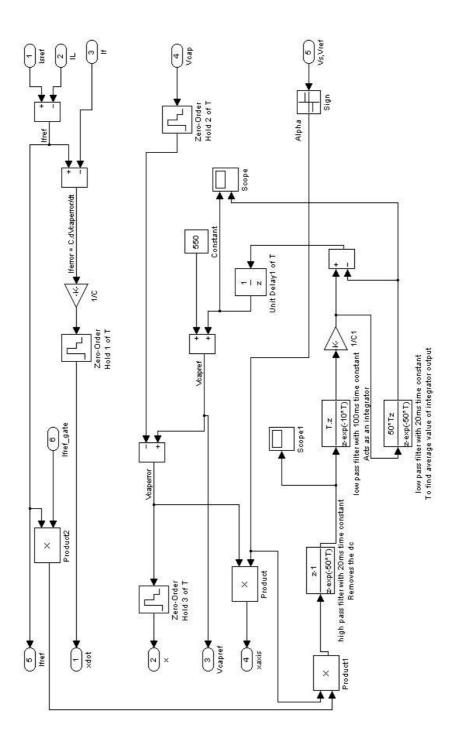

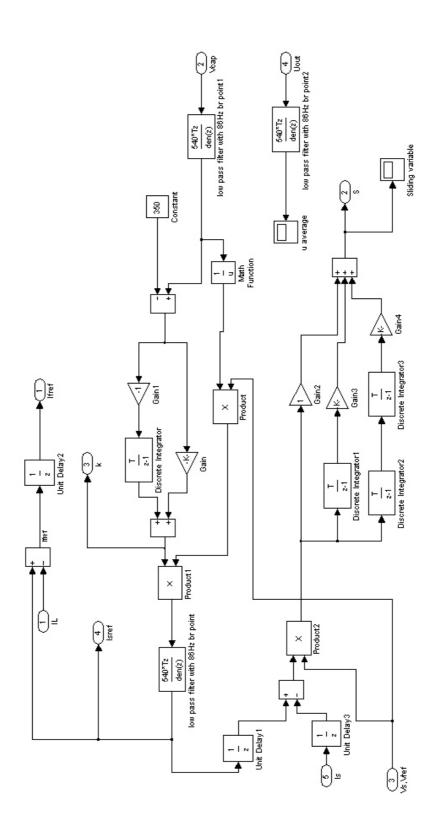

|       | 3.12.6 | Simulation block "Sliding Surface"                                     | 118   |

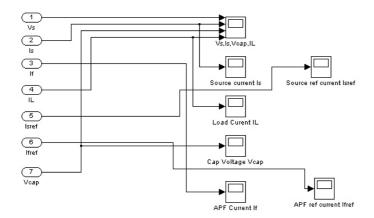

|       | 3.12.7 | Simulation block "Measurements"                                        | 119   |

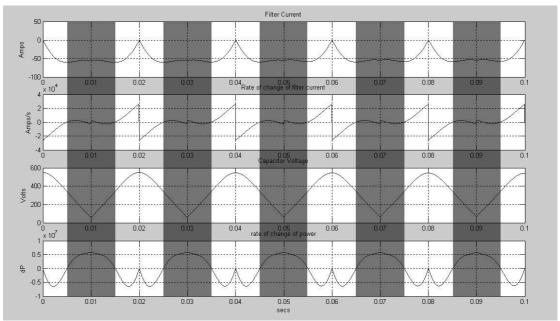

| 3.13  | Sin    | nulations and Results for a Zero and First Order control system using  | g     |

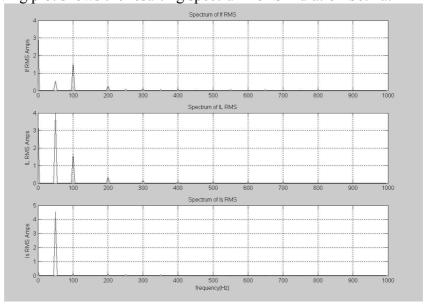

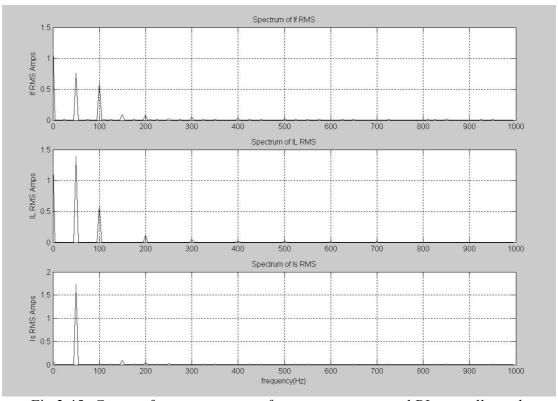

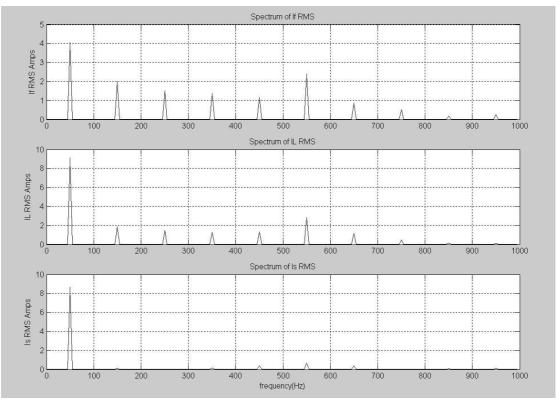

|       | MA     | ATLAB function switch_control3a.m                                      | 120   |

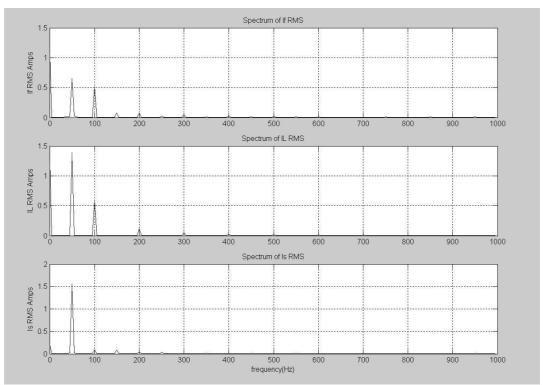

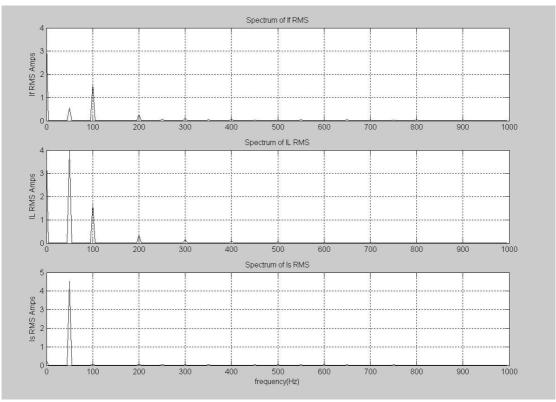

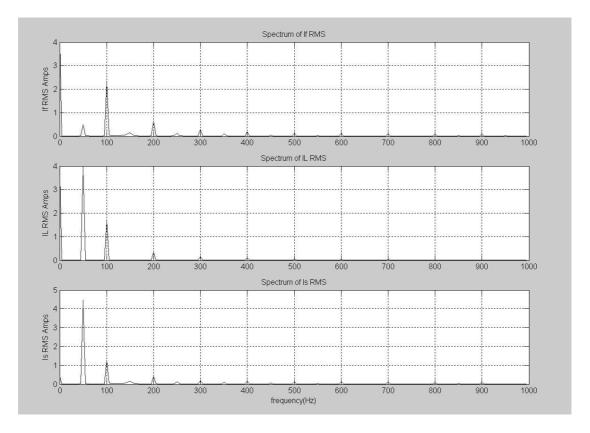

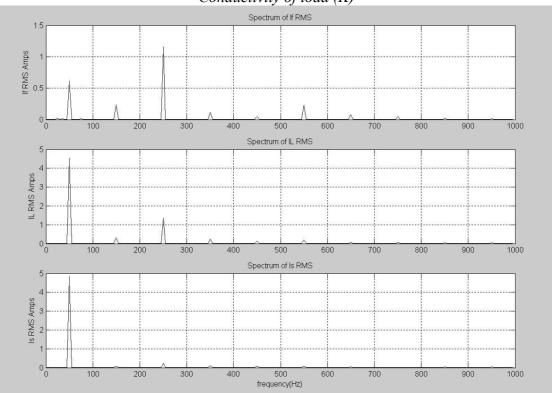

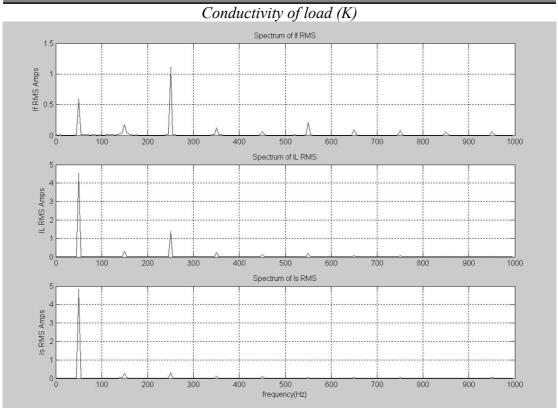

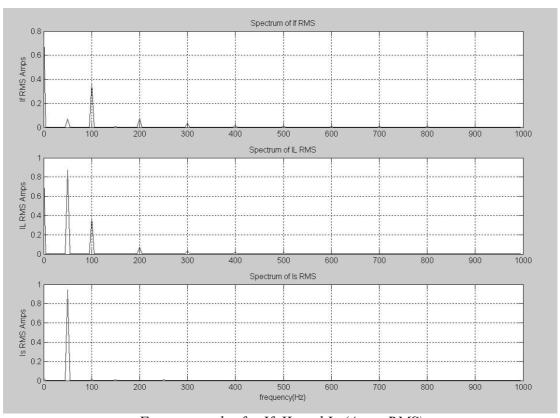

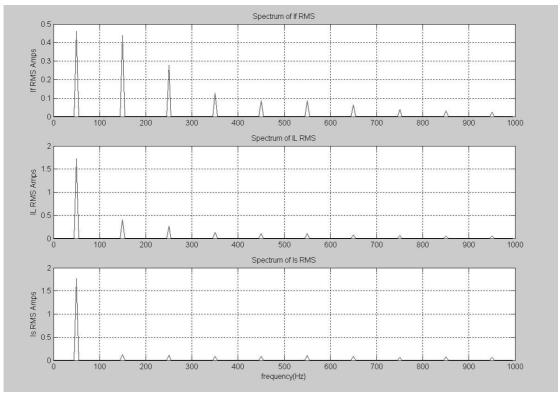

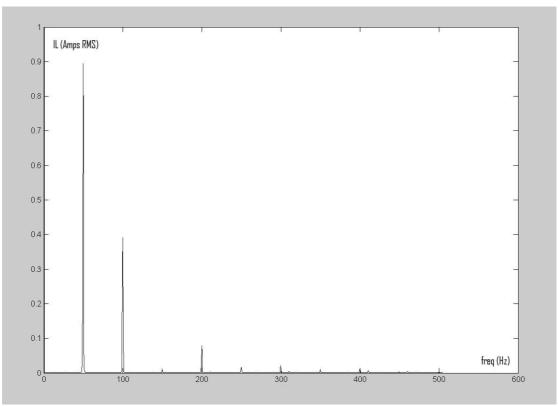

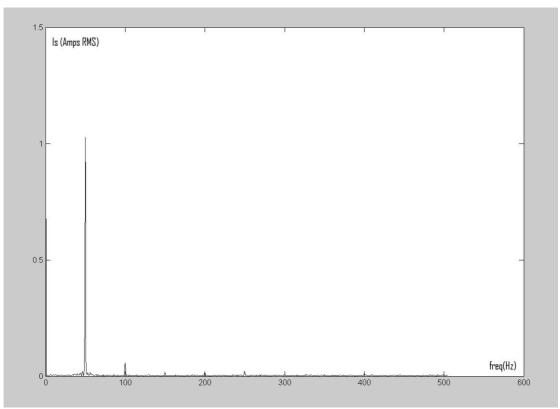

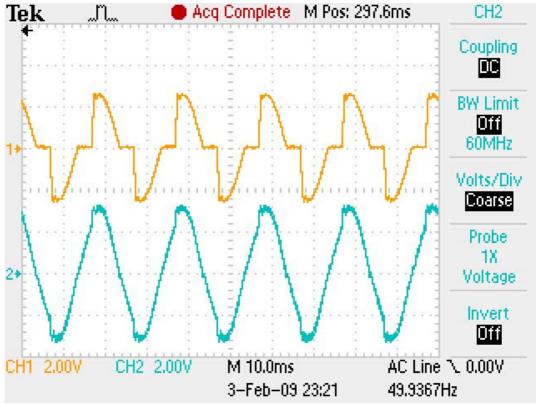

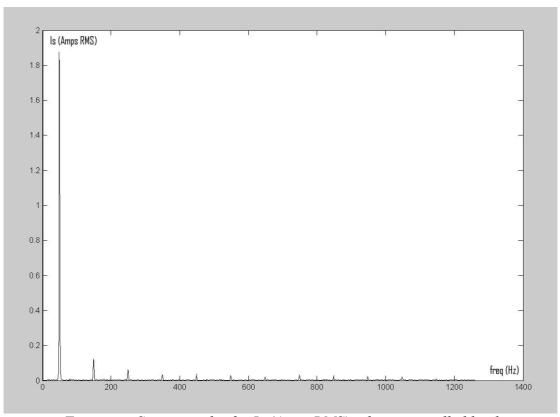

|       | 3.13.1 | Producing the frequency spectrum                                       | 121   |

|       | 3.13.2 | M Function "freqplot3.m"                                               | 121   |

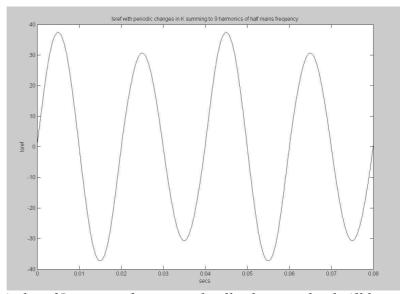

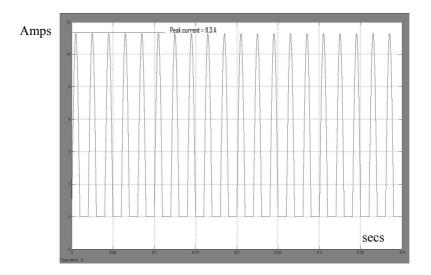

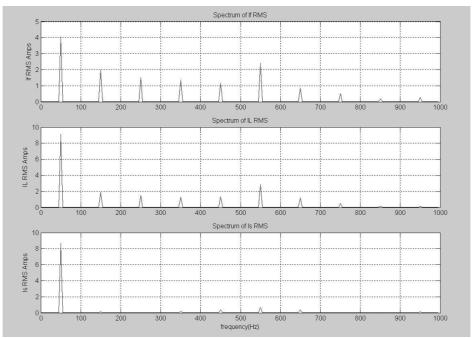

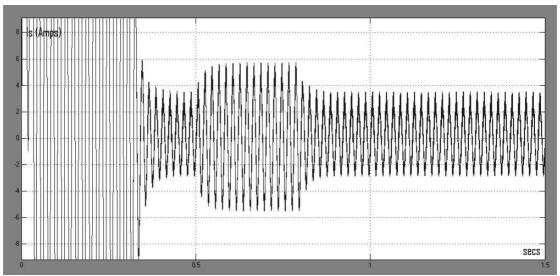

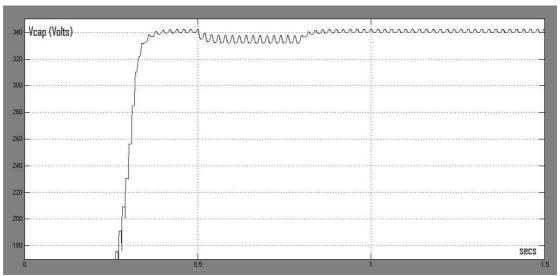

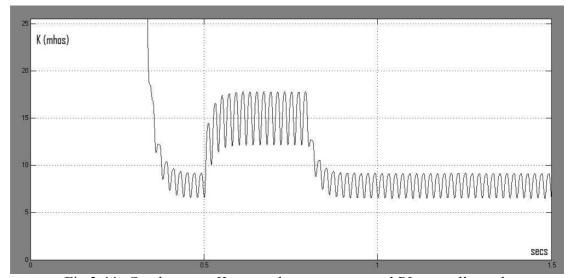

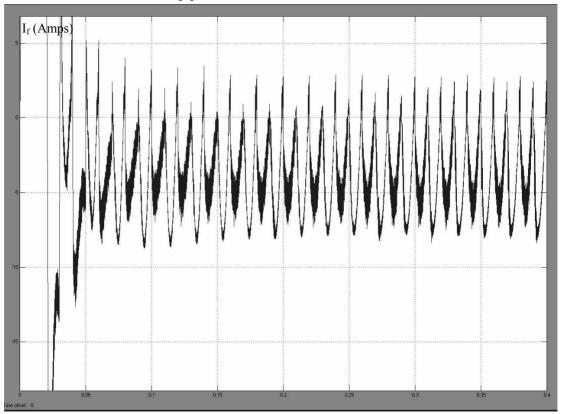

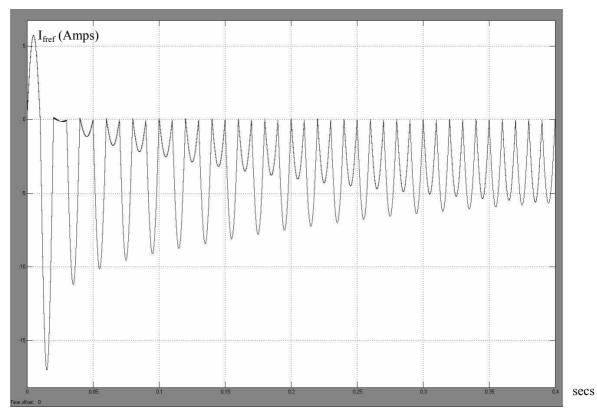

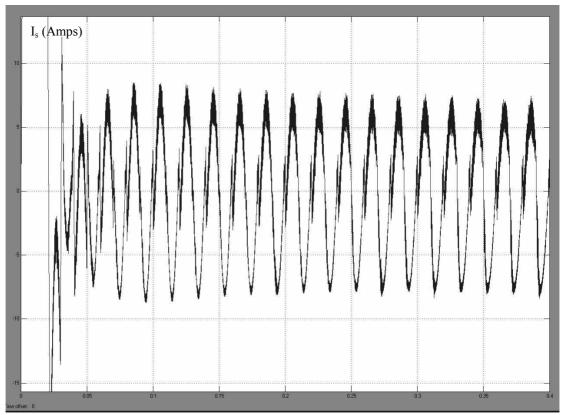

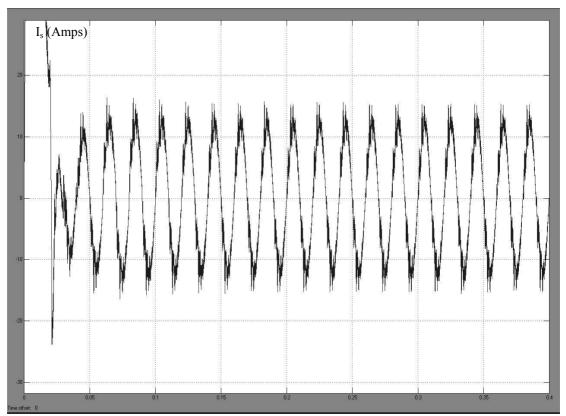

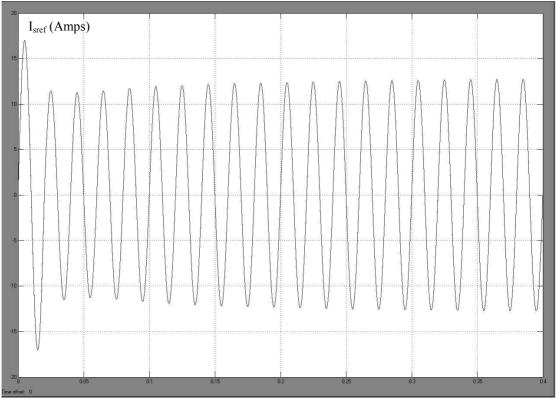

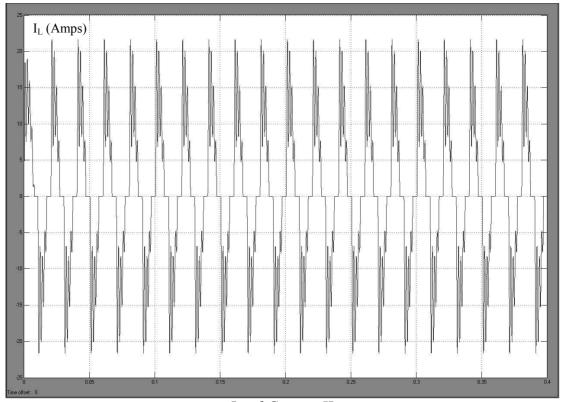

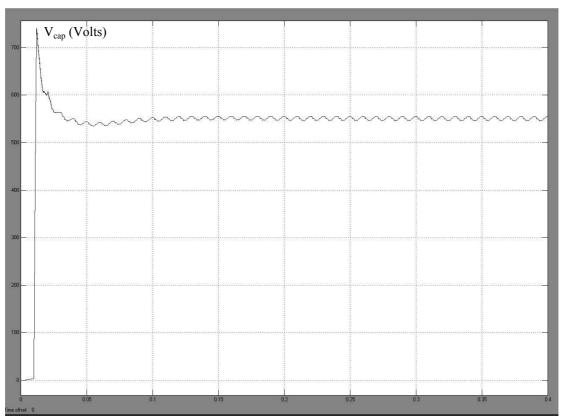

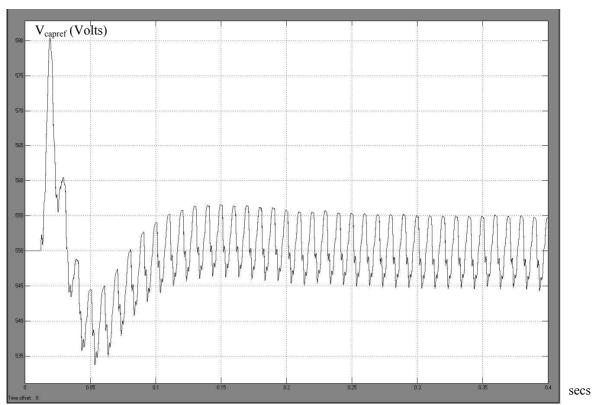

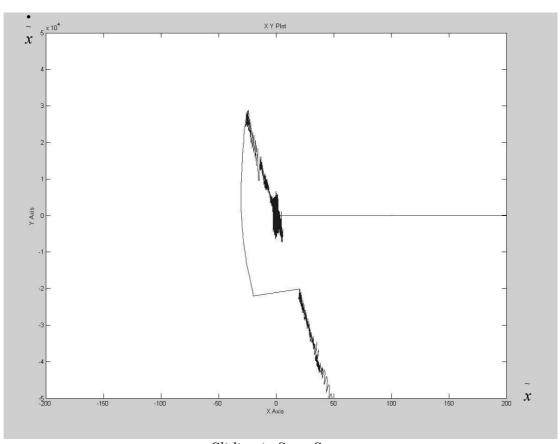

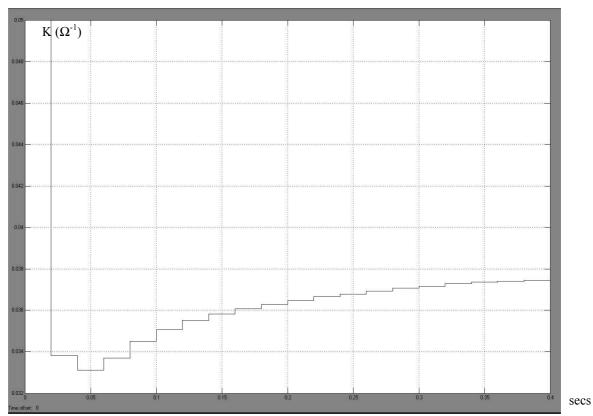

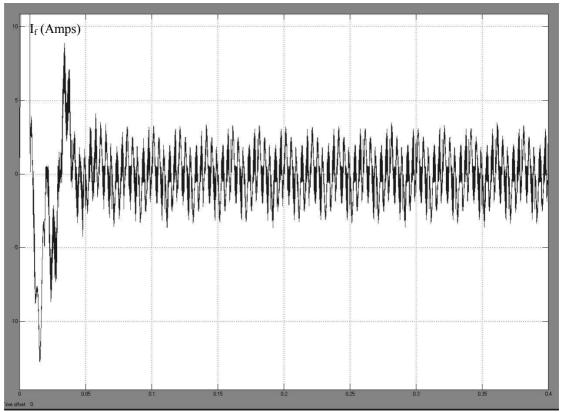

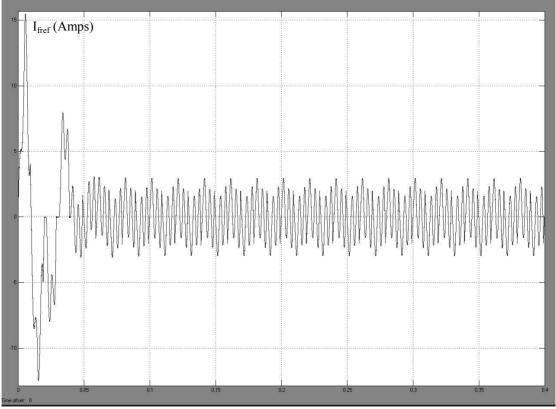

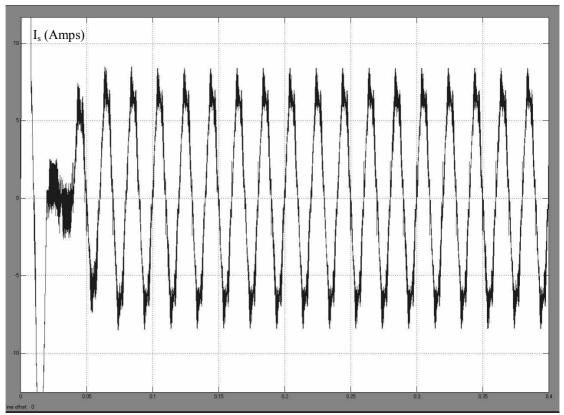

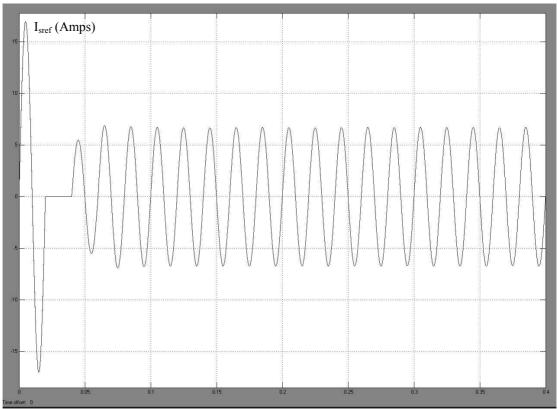

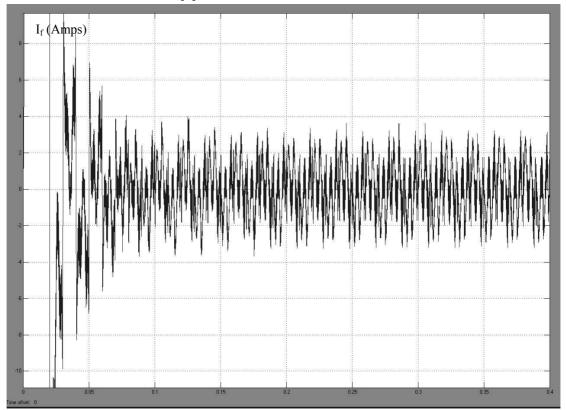

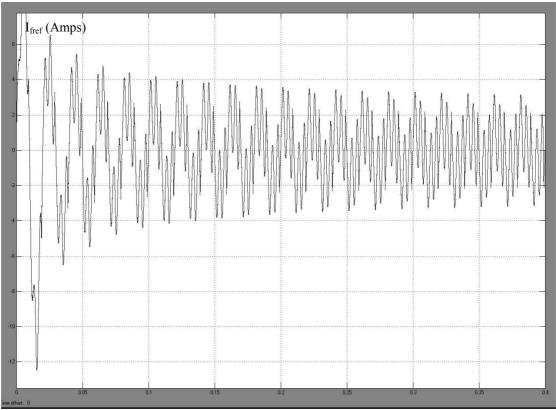

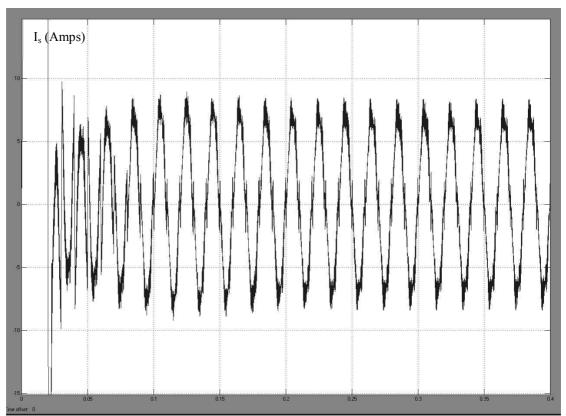

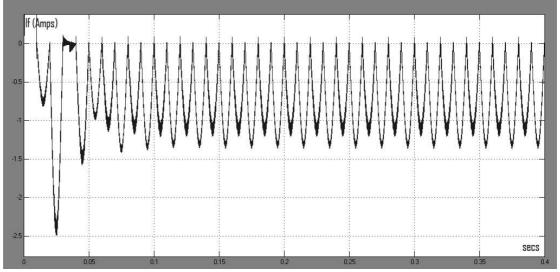

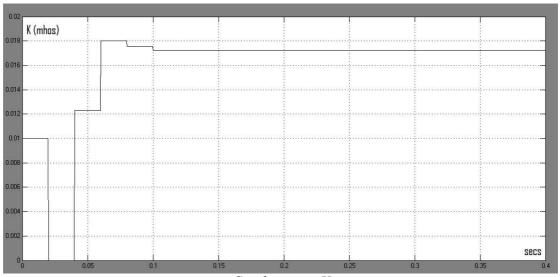

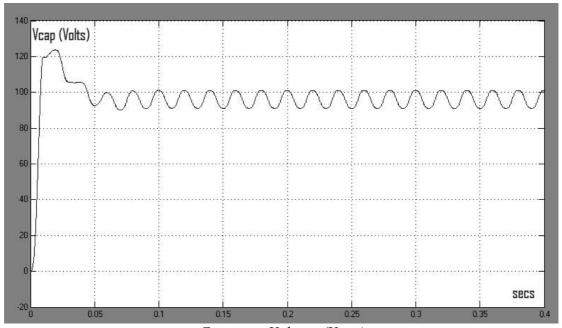

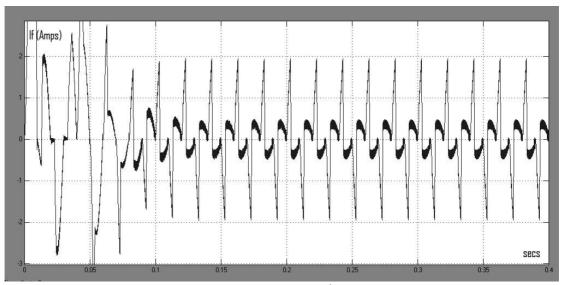

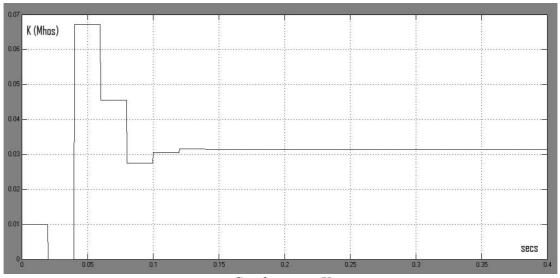

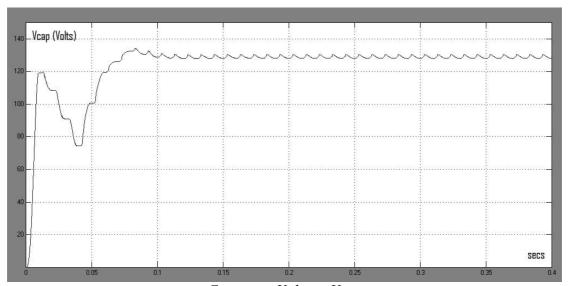

|       | 3.13.3 | Results Simulation Set 1a and 1b                                       | 124   |

|       | 3.13.3 | Non-Linear load used for Simulation Set 1a and 1b                      | 124   |

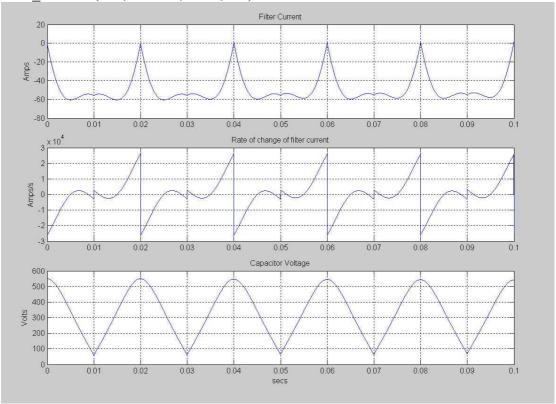

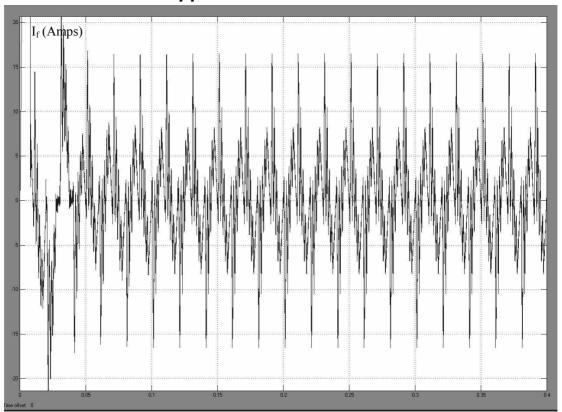

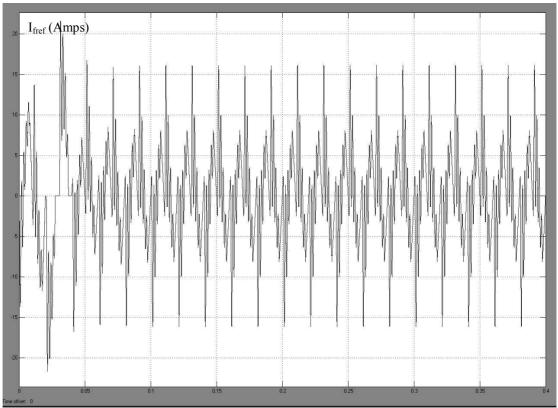

|       | 3.13.3 | 3.2 Simulation Set 1a                                                  | 125   |

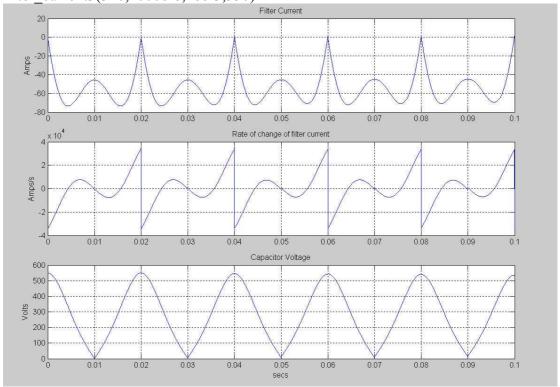

|       | 3.13.3 | 3.3 Simulation Set 1b                                                  | 126   |

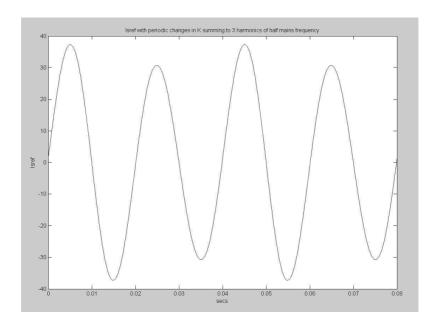

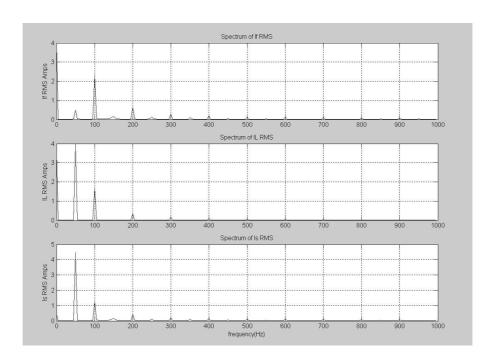

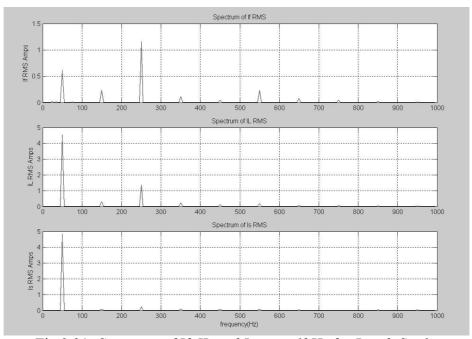

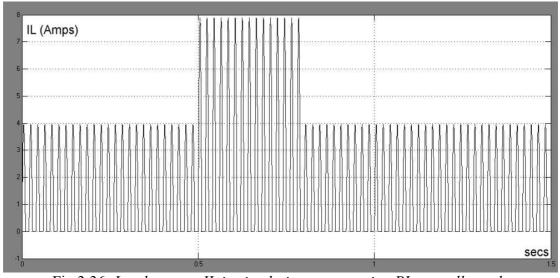

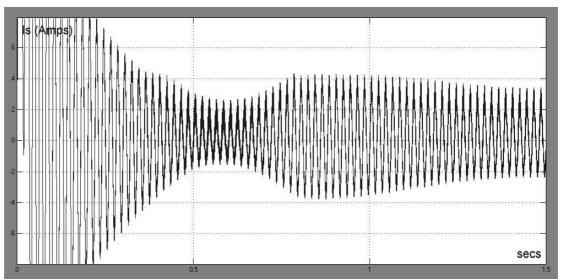

|       | 3.13.4 | Results Simulation set 2a and 2b                                       | 128   |

|       | 3.13.4 | Non-Linear load used for Simulation Set 2a and 2b                      | 128   |

|       | 3.13.4 | 4.2 Simulation Set 2a                                                  | 128   |

|       | 3.13.4 | 4.3 Simulation set 2b                                                  | 129   |

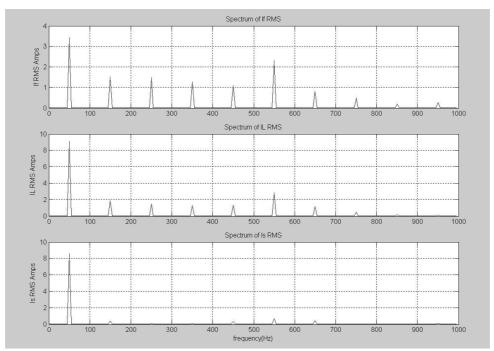

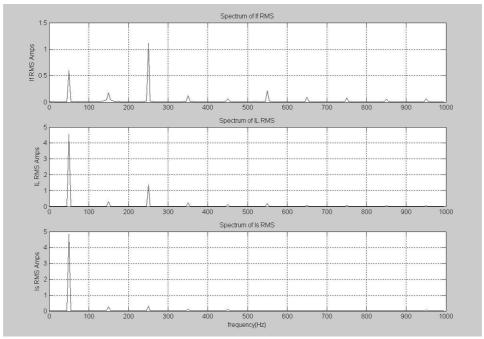

|       | 3.13.5 | Simulation set 3a and 3b                                               | 130   |

|       | 3.13.5 | Non-Linear load used for Simulation Set 3a and 3b                      | 131   |

|       | 3.13.5 | 5.2 Simulation 3a                                                      | 131   |

|       | 3.13.5 |                                                                        |       |

|       | 3.13.6 | Conclusion of results of section 3.13.3 to 3.13.5                      | 133   |

| 3.14  | Stu    | dy and comparison of results with existing methods                     | 134   |

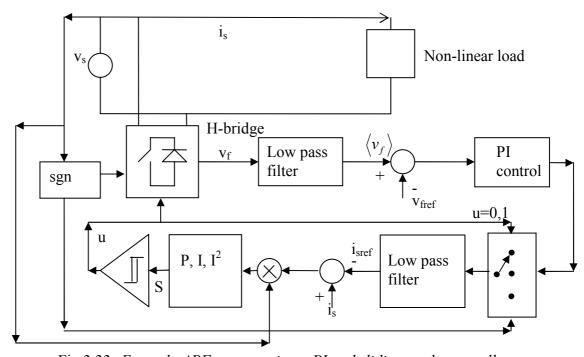

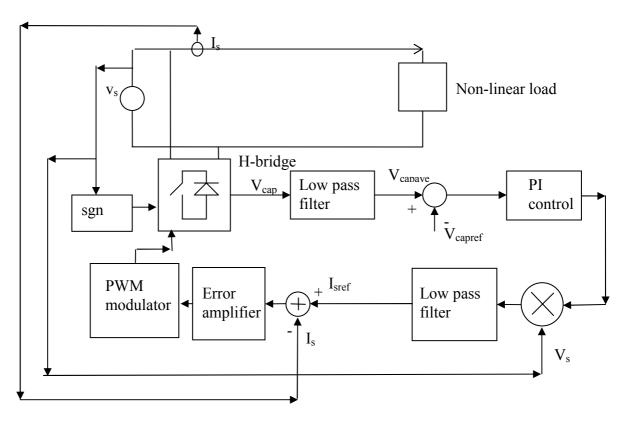

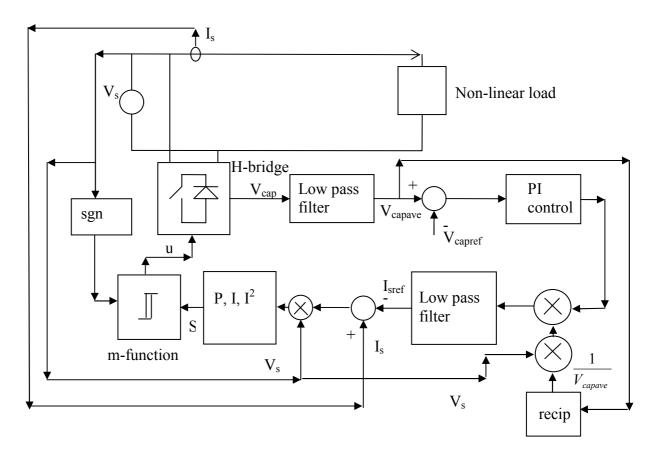

|       | 3.14.1 | The PI controller                                                      | 135   |

|       | 3.14.2 | A study of existing sliding control methods and linear control met     | hods. |

|       |        |                                                                        | 137   |

|       | 3.14.3 | Simulation of APF methods incorporating a PI controller                | 140   |

|       | 3.14.3 | 3.1 Matlab simulation of fig 3.36                                      | 141   |

|       | 3.14.3 | 3.2 Simulation parameters                                              | 142   |

|       | 3.14.3 | $\mathcal{E}$                                                          |       |

|       | 3.14.3 | 3.4 Load and simulation parameters                                     | 142   |

|       | 3.14.3 | Results of simulation for system block diagram 3.35                    | 143   |

|       | 3.14.3 | $\mathcal{C}$                                                          |       |

|       | 3.14.4 | Comparison of results                                                  |       |

| 2 1 5 | Ch     | anter 3: Conclusions                                                   | 150   |

| Chapter 4 |         | Real Power Flow Analysis, Proportional Hysterisis switching and           |       |  |

|-----------|---------|---------------------------------------------------------------------------|-------|--|

|           |         | the Energy Compensation Method                                            | 152   |  |

| 4.1       | An      | Introduction to Real Power Flow Analysis                                  | 153   |  |

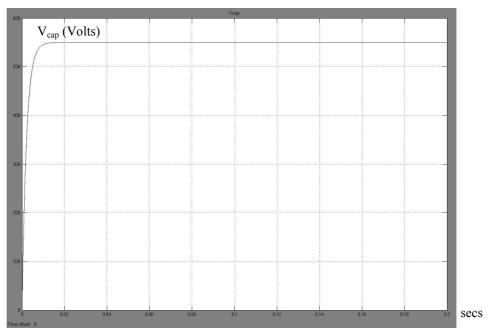

| 4.2       |         | o-order system analysis ( $\lambda = 0$ )                                 |       |  |

|           | 4.2.1   |                                                                           |       |  |

|           |         | 1 Step change of load in the MATLAB model of Appendix C with              |       |  |

|           |         | $\lambda = 0$                                                             | 162   |  |

|           | 4213    | 2 Step Change of Load using Real Power Flow model of fig 4.1              |       |  |

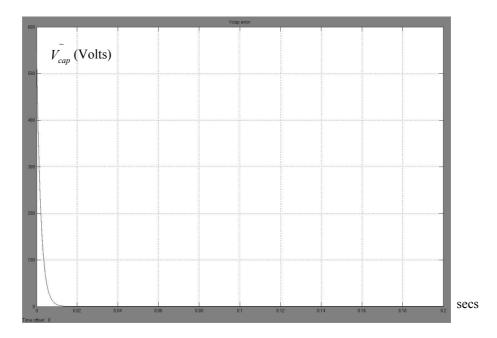

| 4.3       |         | al Power Flow Analysis of a DSM First Order System ( $\lambda > 0$ )      |       |  |

| 1.5       | 4.3.1   |                                                                           |       |  |

|           |         | 1 MATLAB simulation of the Inner Loop with linearising                    | 107   |  |

|           | 1.5.1.  | approximation                                                             | 170   |  |

|           | 4313    | 2 Analytical derivation of the inner loop response with linearising       |       |  |

|           | 1.5.1.2 | approximation                                                             | 172   |  |

|           | 4.3.2   | Inner Loop dynamics ( $\lambda > 0$ ) without linearising approximations. |       |  |

|           | 4.3.3   | Combining the inner and outer loops ( $\lambda > 0$ )                     |       |  |

|           | 4.3.4   | Combined the inner and outer loops ( $k > 0$ )                            | 170   |  |

|           | т.Э.т   | energy-difference signal in the outer loop                                | 187   |  |

|           | 4.3.5   | Combined Inner and Outer loops: Outer Loop Instability                    | 107   |  |

|           | 1.5.5   | Investigation using the Modified Energy-Difference Feedback Sig           | onal  |  |

|           |         | investigation using the Mounted Energy Difference recover sign            | _     |  |

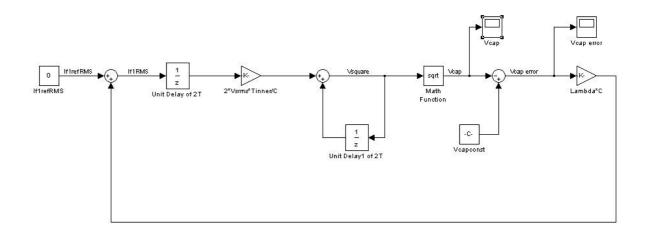

| 4.4       | Cor     | ntrol of both $I_f$ and $V_{cap}$ using the outer loop and                | 1)2   |  |

|           |         | nergy Compensation"                                                       | 194   |  |

|           | 4.4.1   | Developing the Real Power Flow Control Loop incorporating                 |       |  |

|           |         | Energy Compensation                                                       | 195   |  |

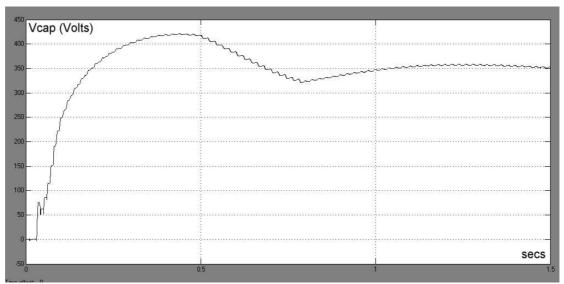

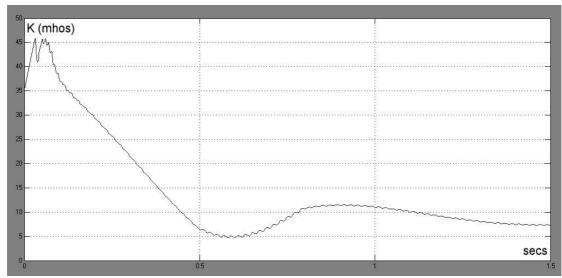

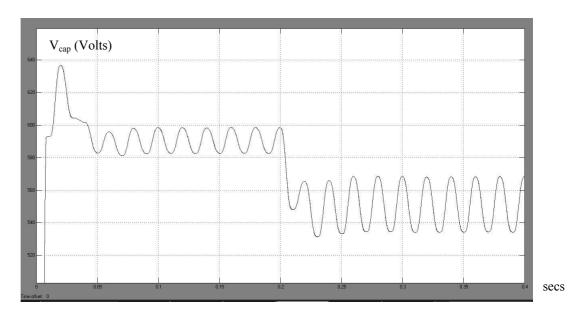

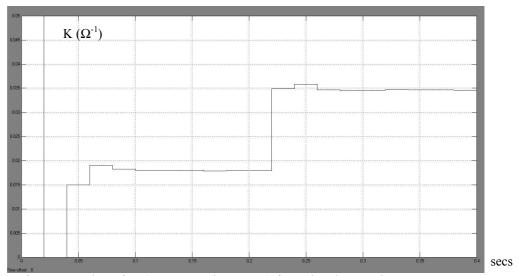

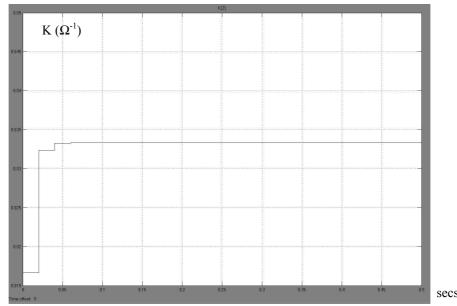

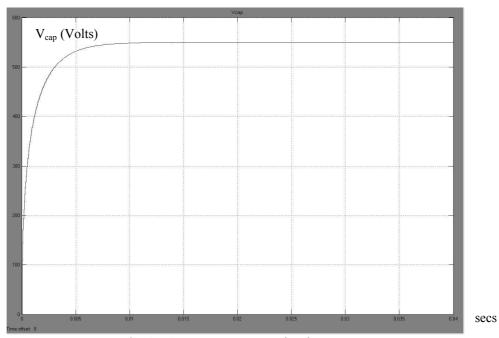

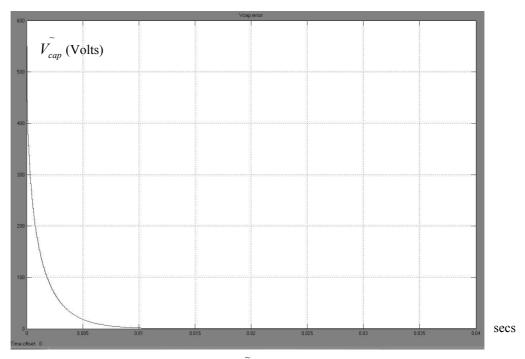

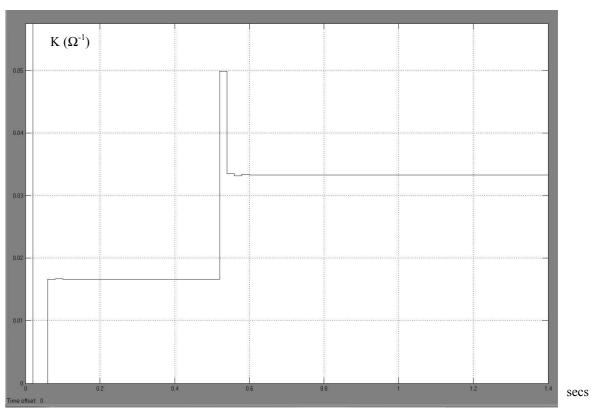

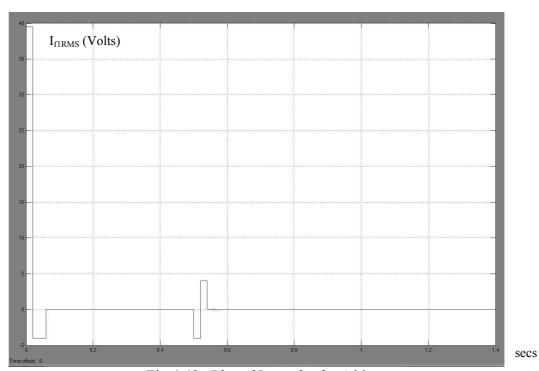

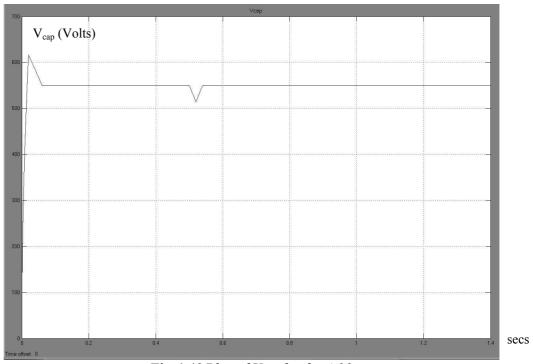

|           | 4.4.2   | Real Power Flow Simulation of the APF using Energy                        |       |  |

|           |         | Compensation with $\varepsilon = 1$                                       | 197   |  |

|           | 4.4.3   | Real Power Flow Analysis of the APF dynamics using Energy                 |       |  |

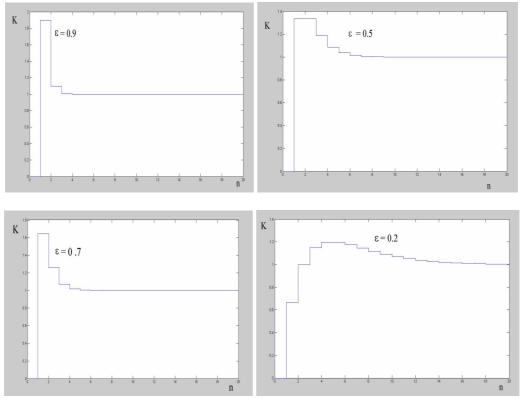

|           |         | Compensation with $0 \le \varepsilon \le 1$                               | 200   |  |

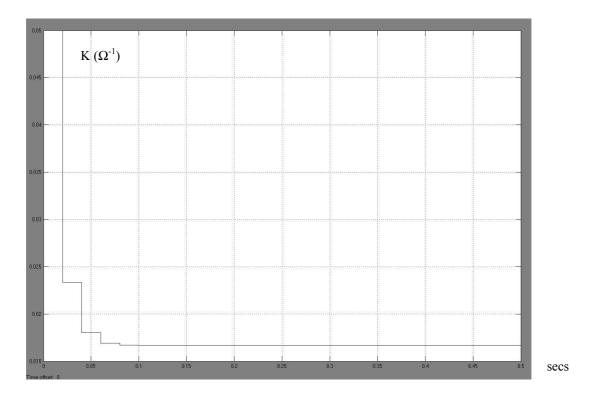

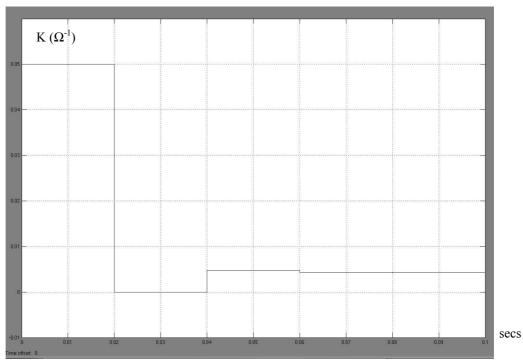

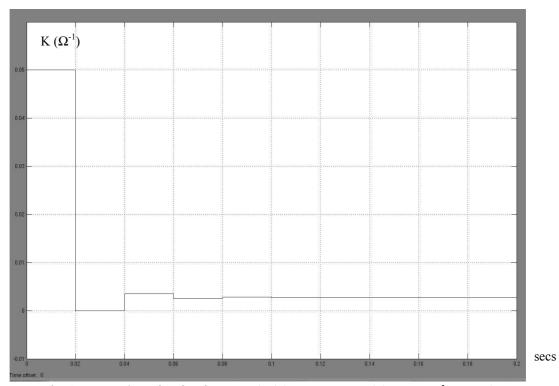

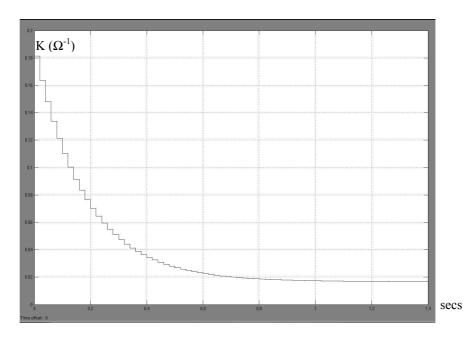

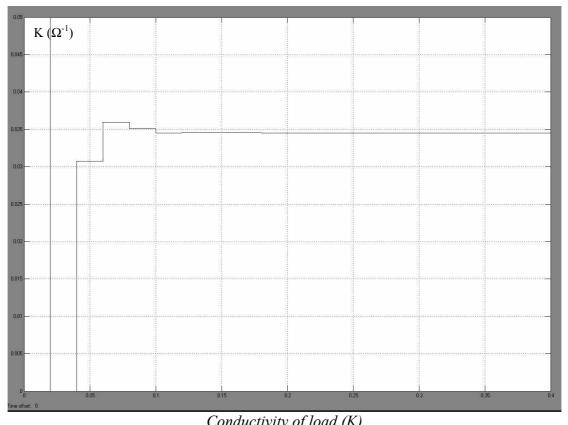

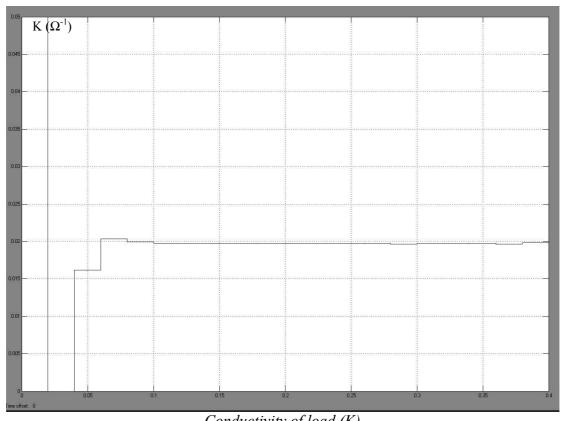

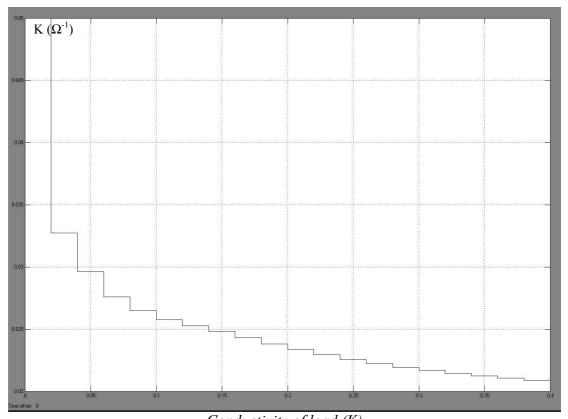

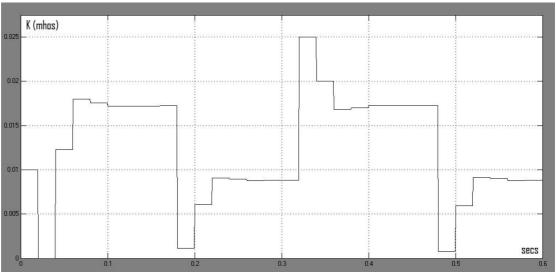

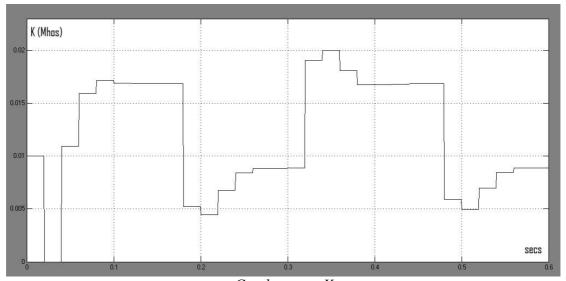

|           | 4.4.4   | Ideal analytical response for K for g = 1                                 |       |  |

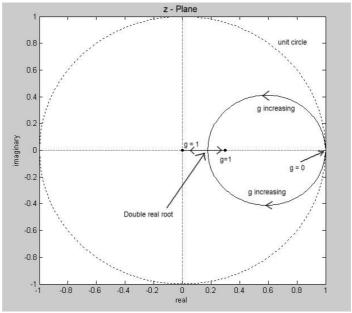

| 4.5       | Pro     | portional Hysterisis Control with Energy Compensation                     |       |  |

|           |         |                                                                           |       |  |

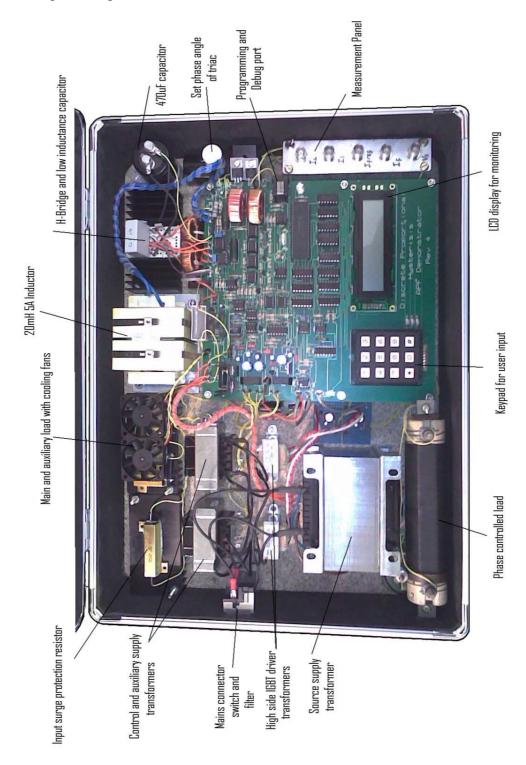

| Cha       | pter 5  | Design and Construction of an APF using Proportional Hyste                | risis |  |

|           |         | switching with Sampled Energy Compensation Control                        | 212   |  |

| 5.1       | Inte    | advetion                                                                  | 212   |  |

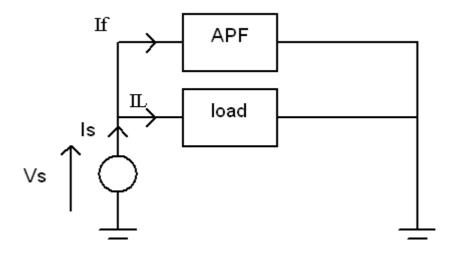

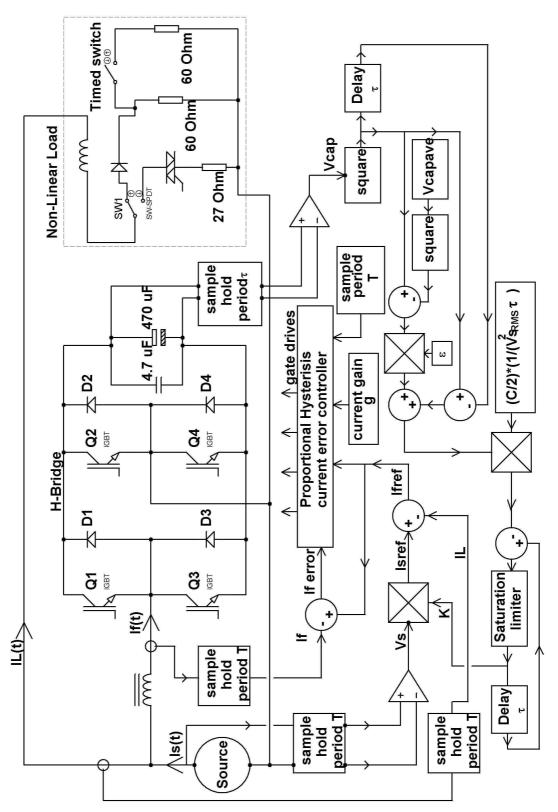

| 5.1       |         | oductionposed system overview                                             |       |  |

| 5.3       |         | ctical approach to System implementation                                  |       |  |

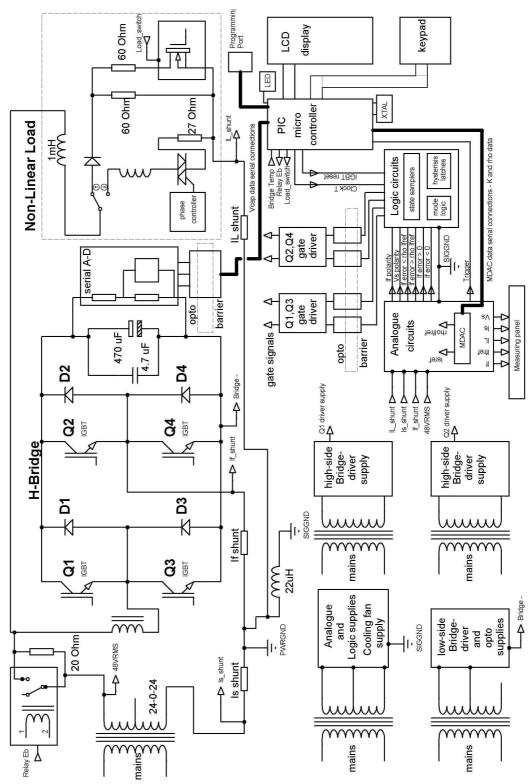

| 5.4       |         | dware Description                                                         |       |  |

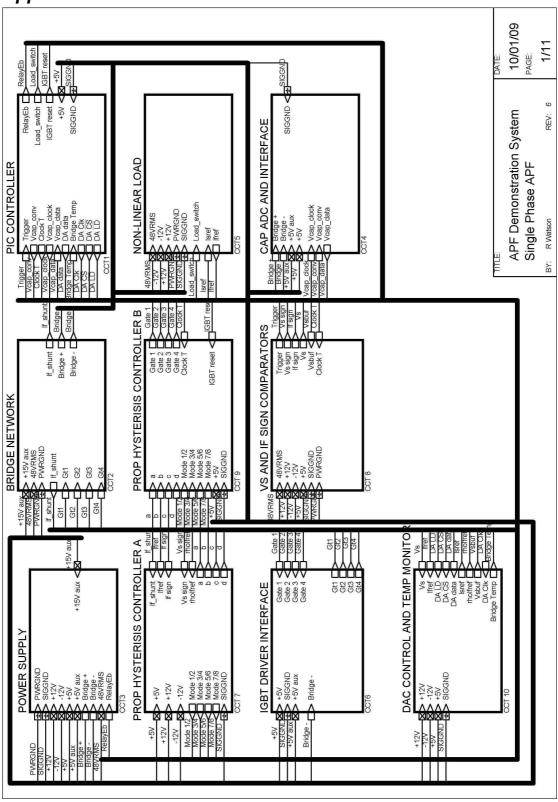

| 3.4       | 5.4.1   | Overview                                                                  |       |  |

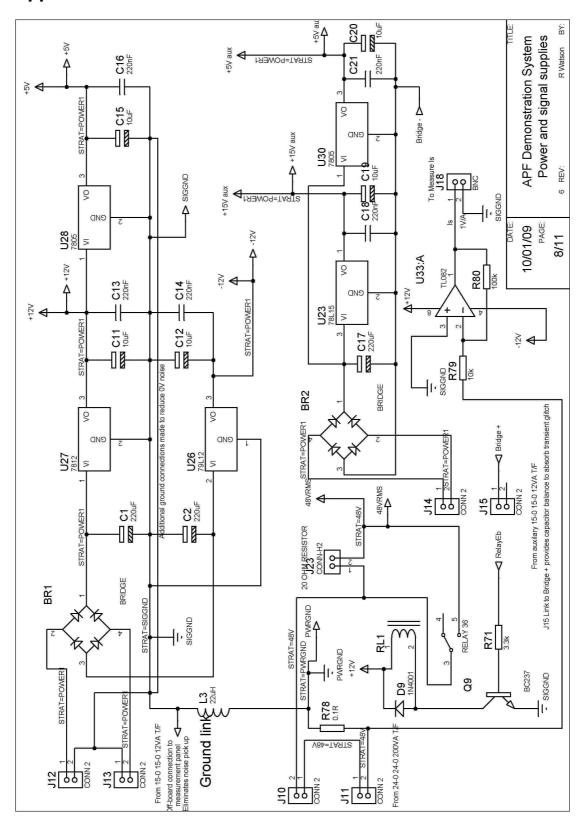

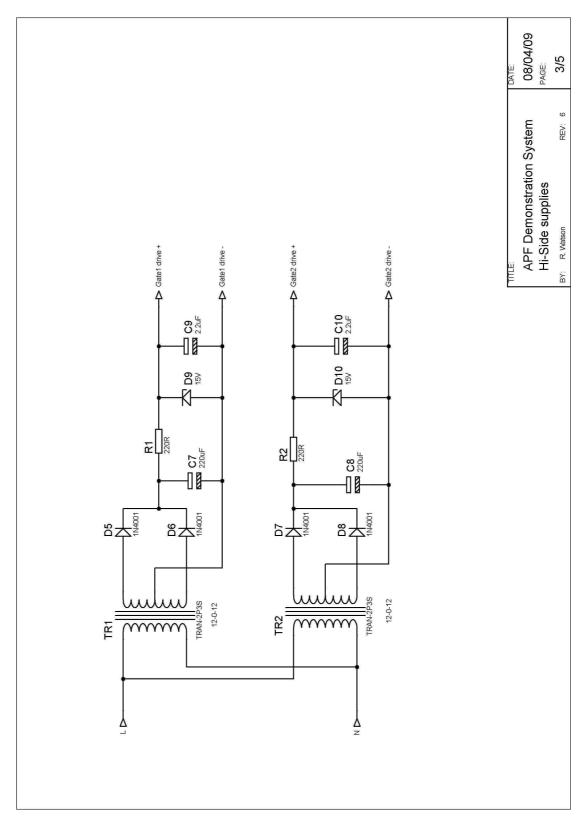

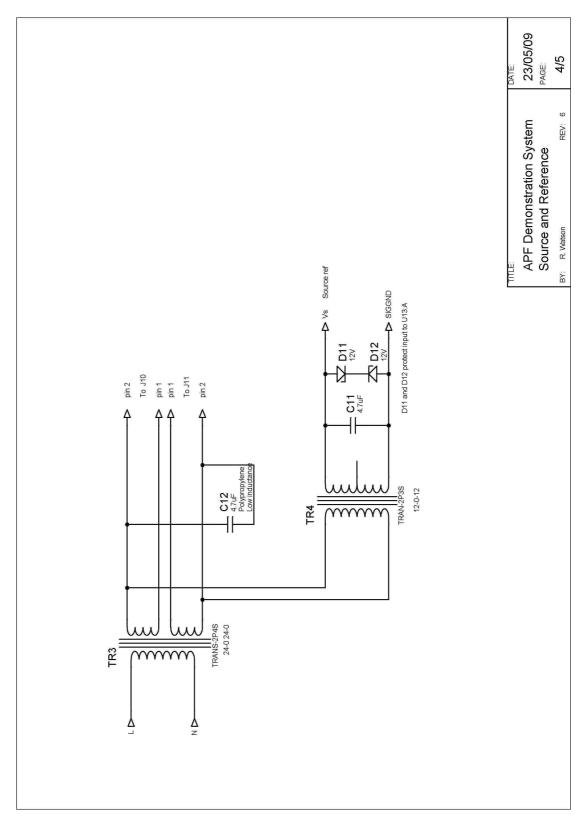

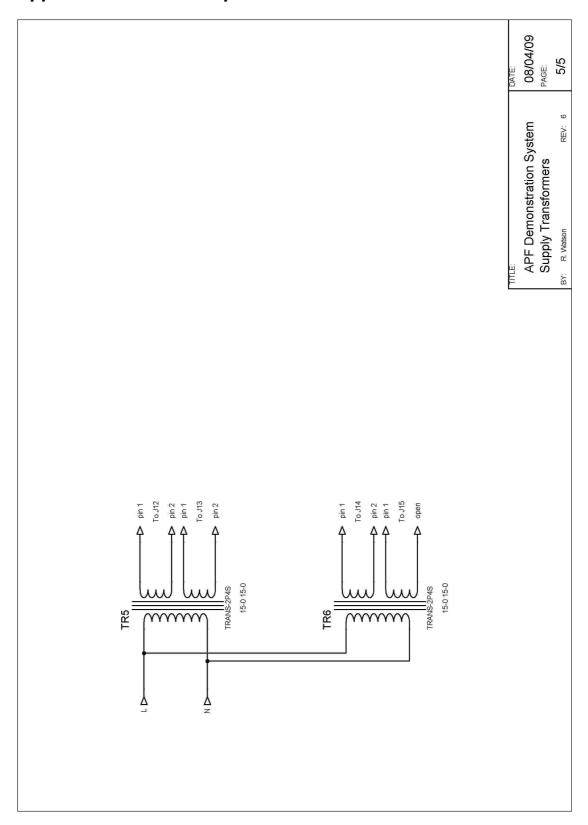

|           | 5.4.1   | Power and Signal Supplies and power-up considerations                     |       |  |

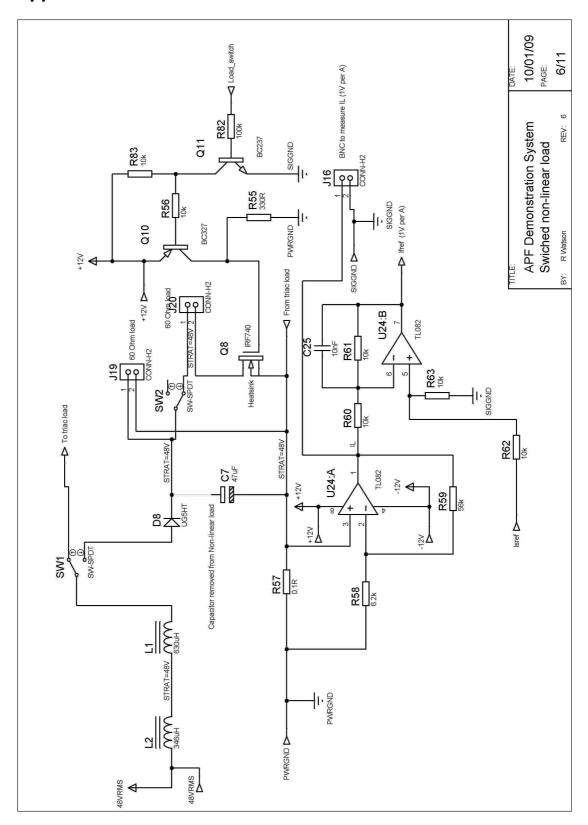

|           | 5.4.2   | Switched Non-Linear load                                                  |       |  |

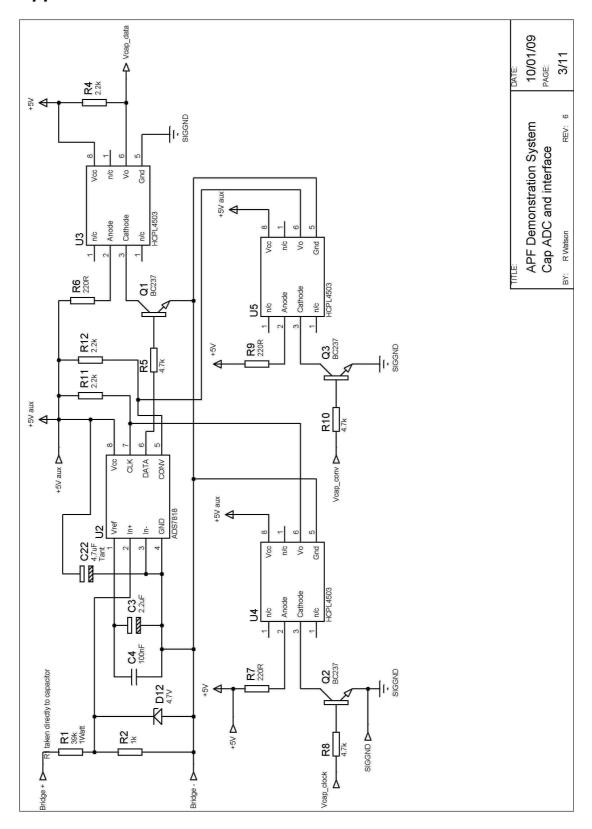

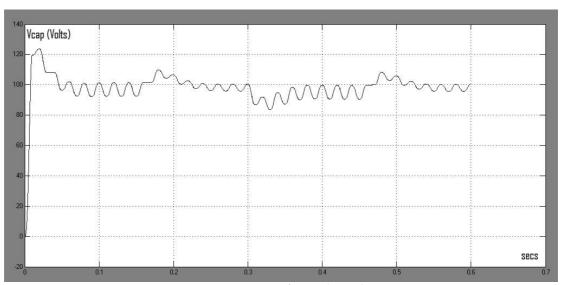

|           | 5.4.4   | Cap ADC and Interface                                                     |       |  |

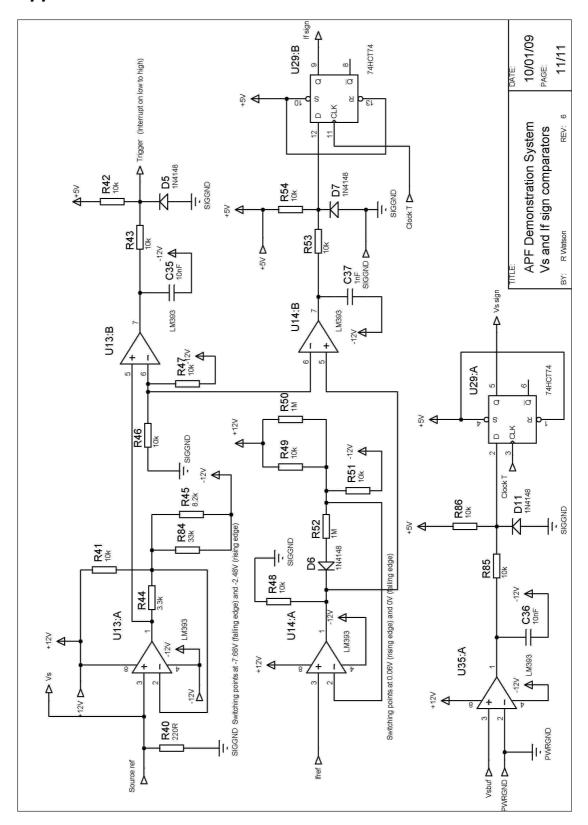

|           | 5.4.4   | Vs and If sign comparators                                                |       |  |

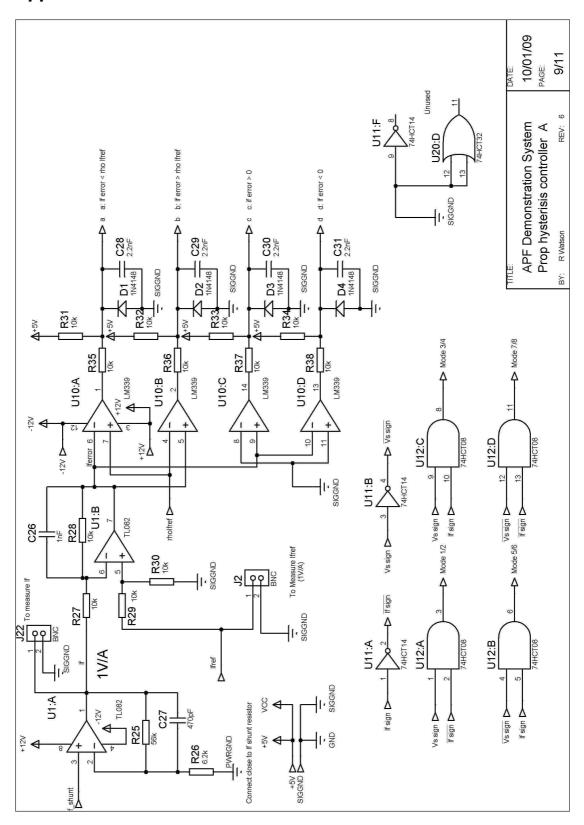

|           | 5.4.6   | Proportional Hysterisis Controller A                                      |       |  |

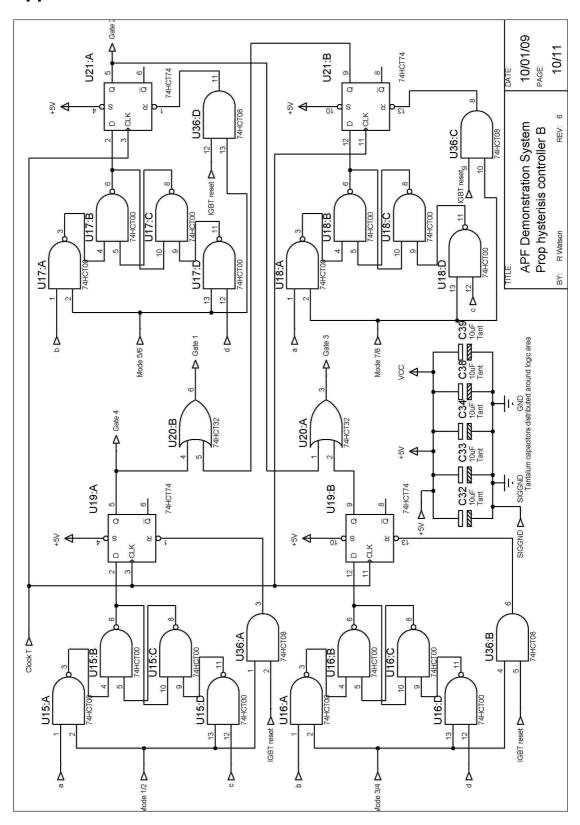

|           | 5.4.0   | Proportional Hysterisis Controller B                                      |       |  |

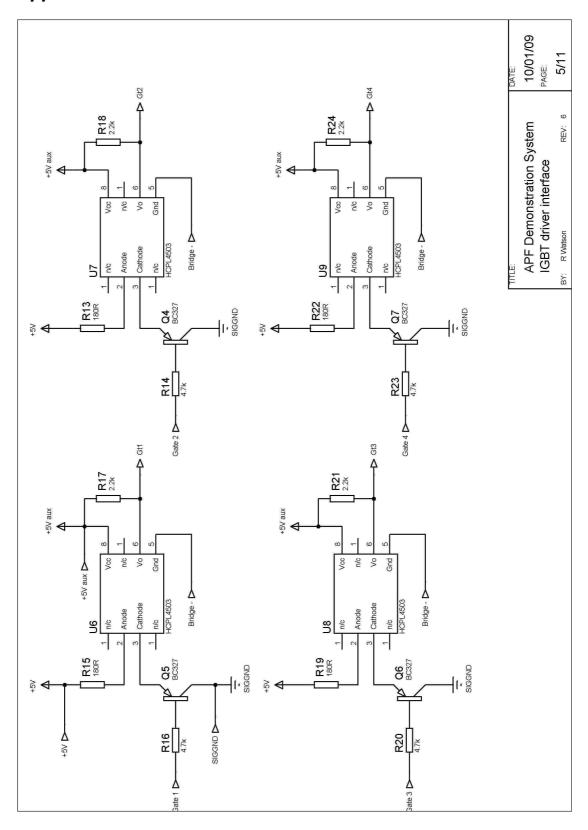

|           | 5.4.7   | IGBT driver interface                                                     |       |  |

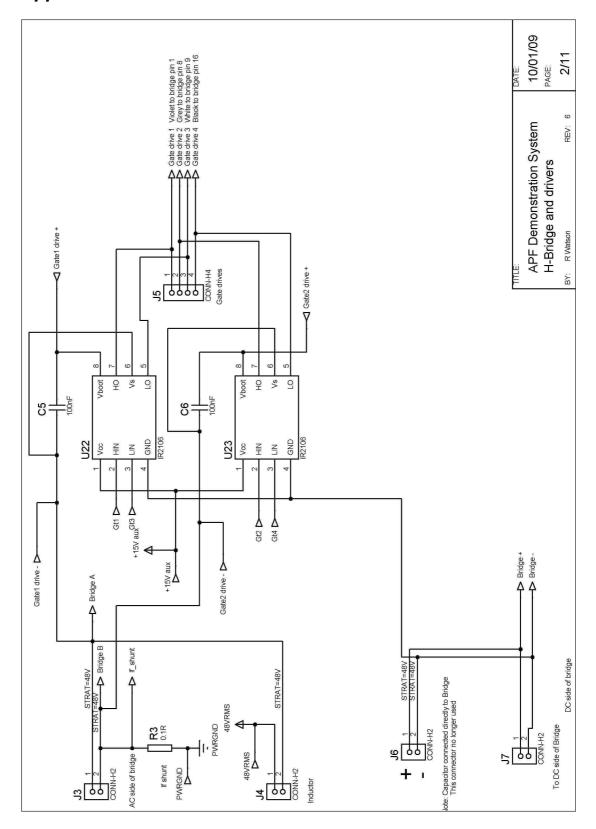

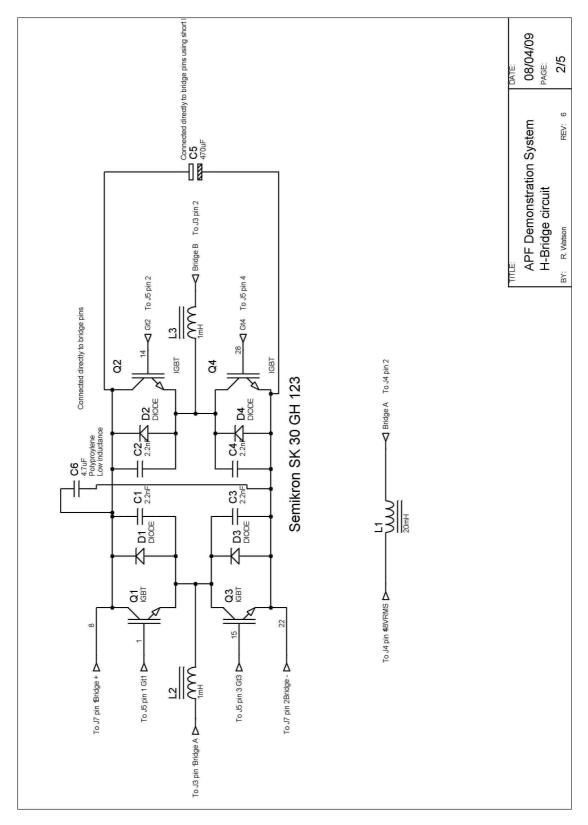

|           | 5.4.9   | H-Bridge and drivers                                                      |       |  |

|           | J.T.J   | 11 1011450 4114 4111 415                                                  | 441   |  |

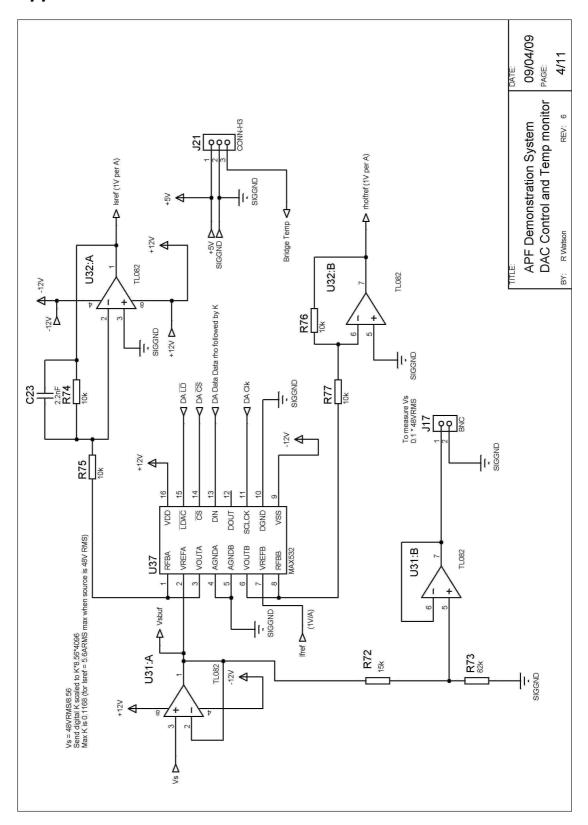

|            | 5.4.10  | DAC control and temperature monitor                              | 222           |

|------------|---------|------------------------------------------------------------------|---------------|

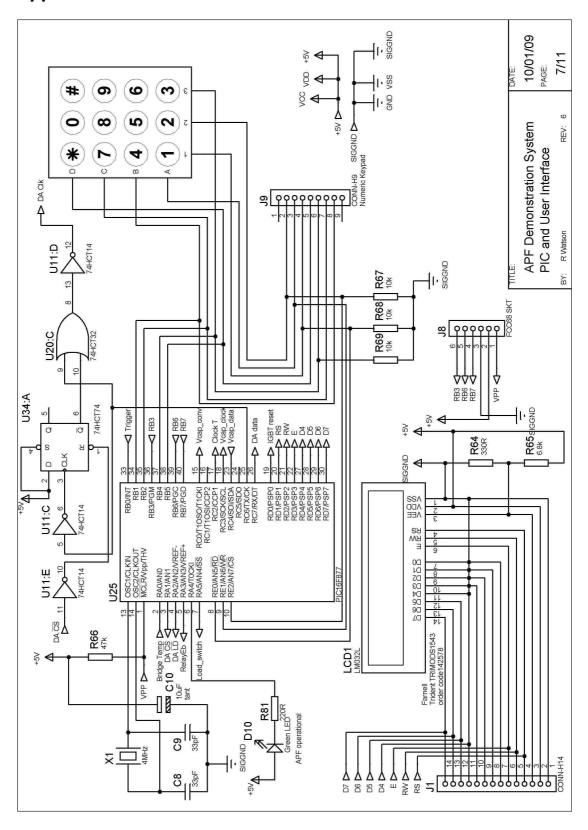

|            | 5.4.11  | PIC and User Interface                                           | 222           |

|            | 5.4.12  | IGBT H-Bridge and inductor                                       | 223           |

|            | 5.4.13  | Additional System Details                                        |               |

|            | 5.4.13  | $\boldsymbol{\mathcal{O}}$                                       |               |

|            | 5.4.13  |                                                                  |               |

|            | 5.4.13  |                                                                  |               |

|            | 5.4.13  |                                                                  |               |

| 5.5        |         | ails of control implementation and software details              |               |

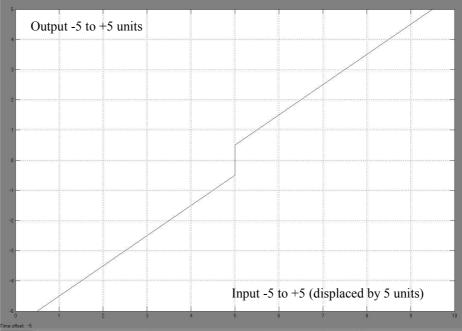

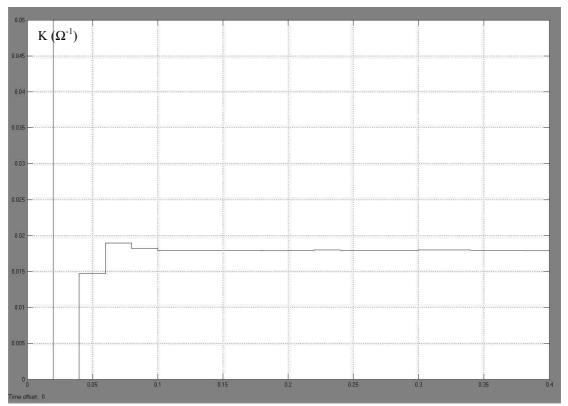

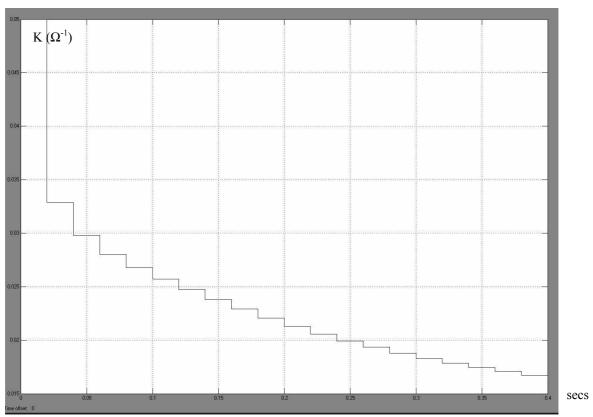

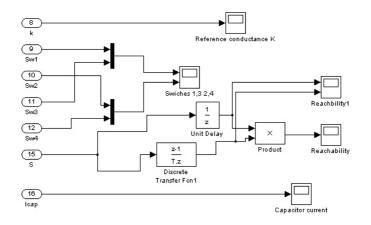

|            | 5.5.1   | Calculating K                                                    |               |

|            | 5.5.2   | Signal Scaling and Calculations                                  |               |

|            | 5.5.2.1 | E                                                                |               |

|            | 5.5.2.2 |                                                                  |               |

|            | 5.5.2.3 | 63                                                               |               |

|            | 5.5.2.4 | $\mathcal{C}$ 1                                                  |               |

|            | 5.5.3   | Software Details                                                 |               |

|            | 5.5.3.1 | 5 · F · · ( FF · · · )                                           |               |

| <b>-</b> . | 5.5.3.2 | 0 1 11 /                                                         |               |

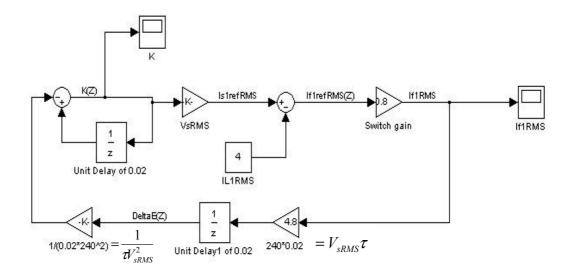

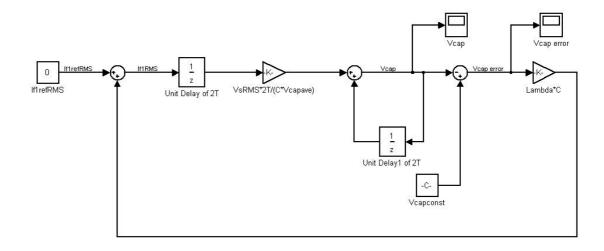

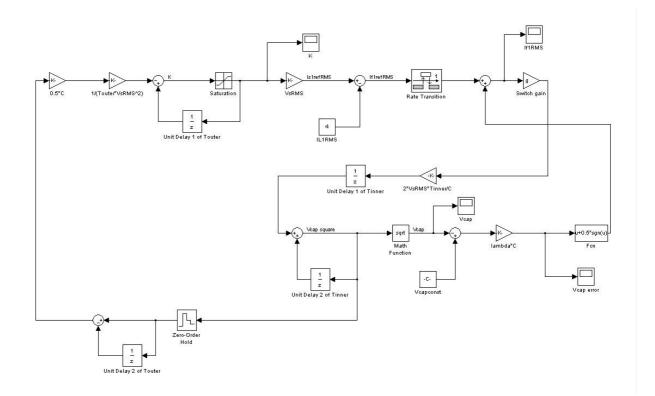

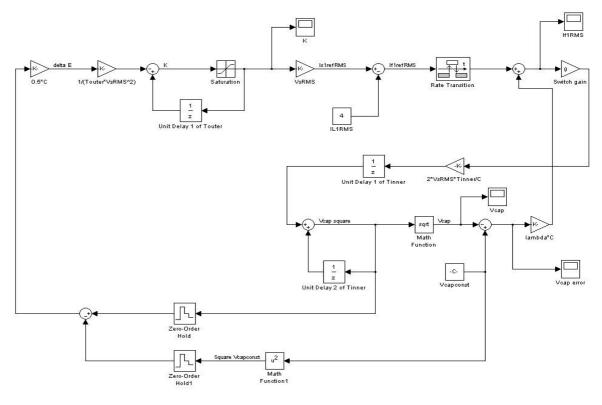

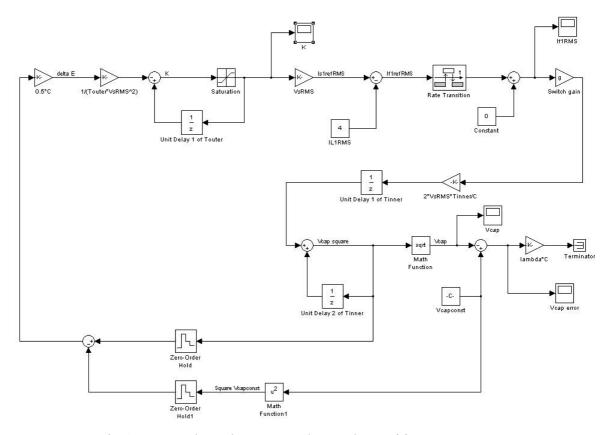

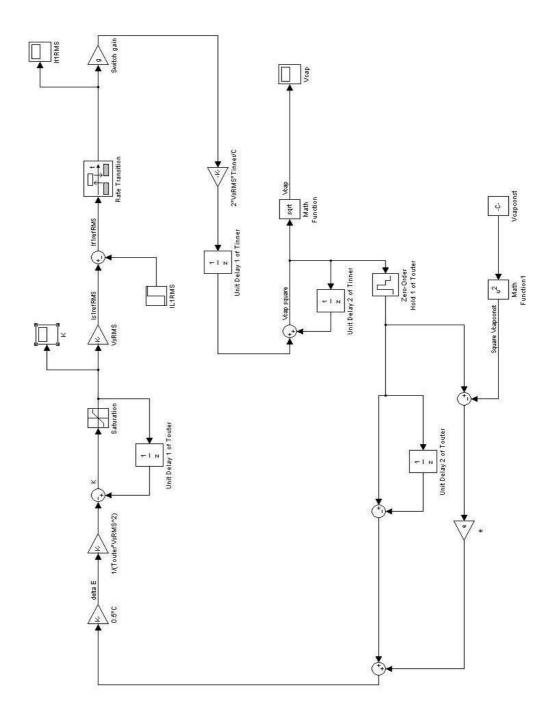

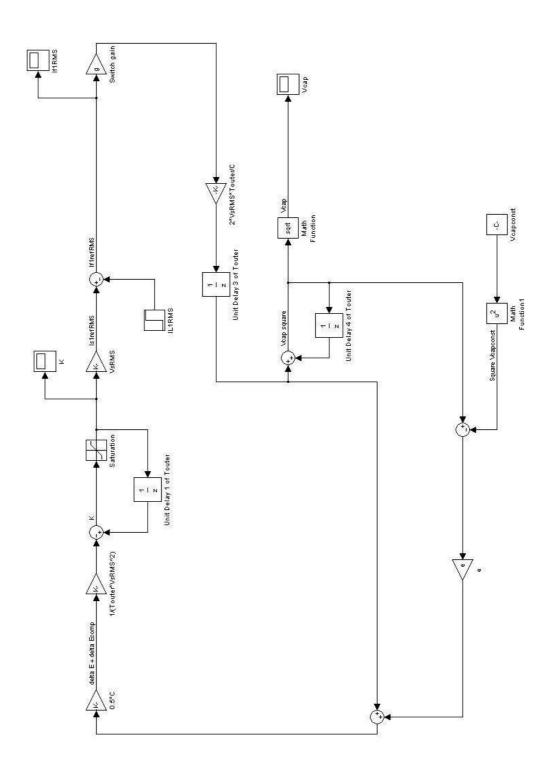

| 5.6        |         | relopment of a simulation model                                  |               |

|            | 5.6.1   | The Simulation System                                            |               |

|            | 5.6.2   | The switching control m-file                                     |               |

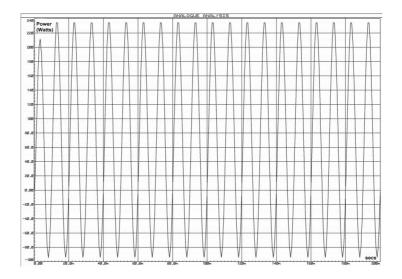

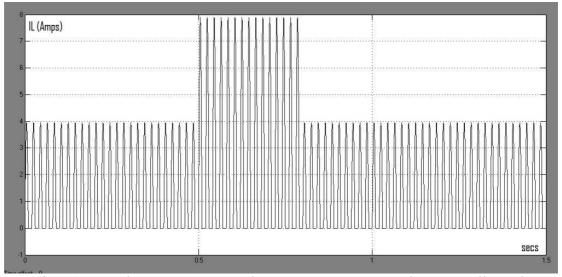

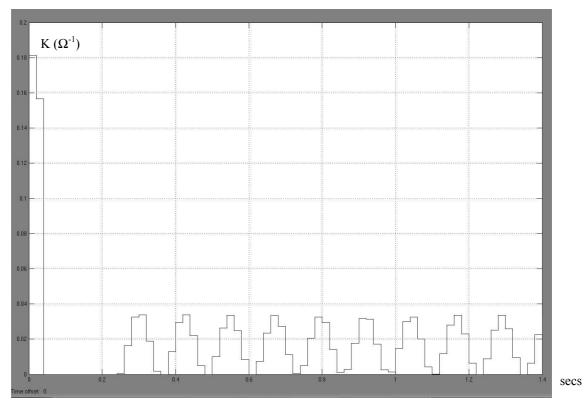

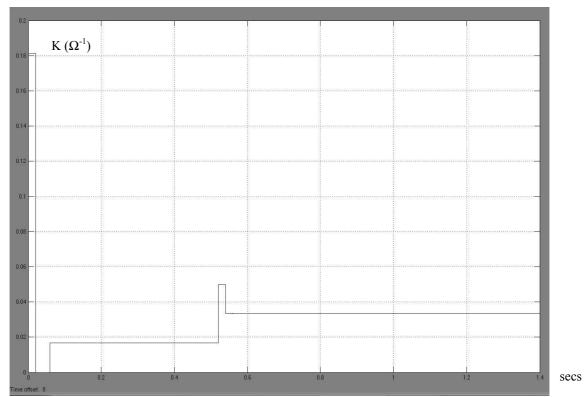

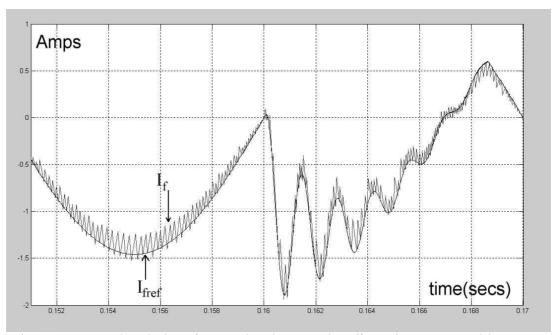

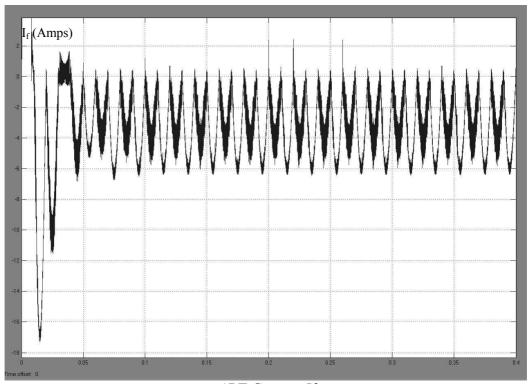

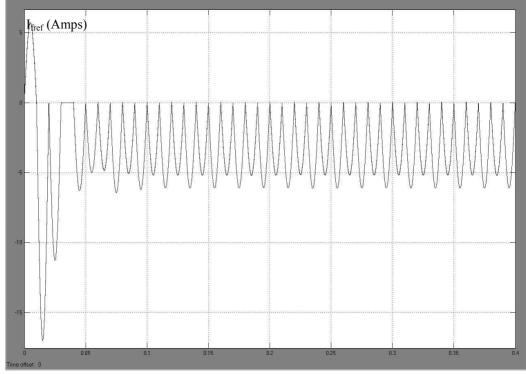

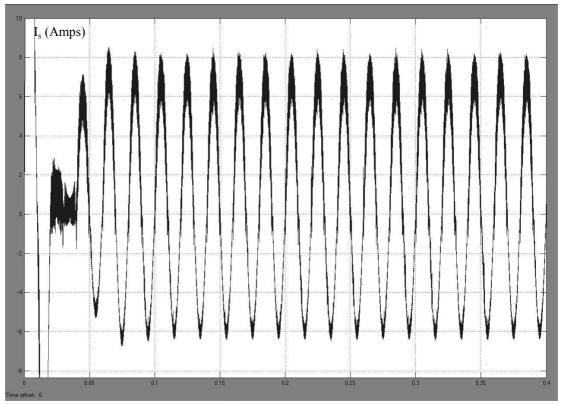

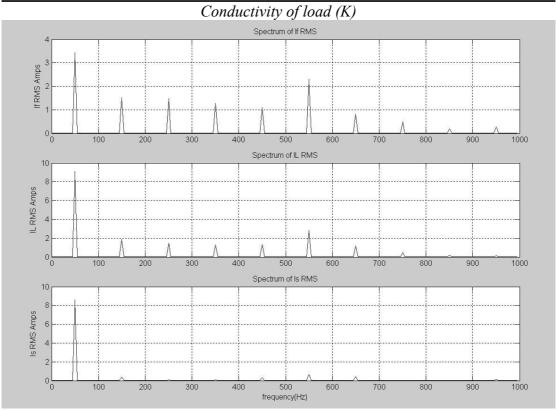

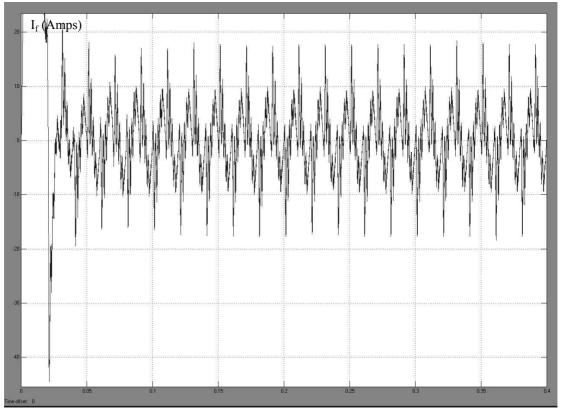

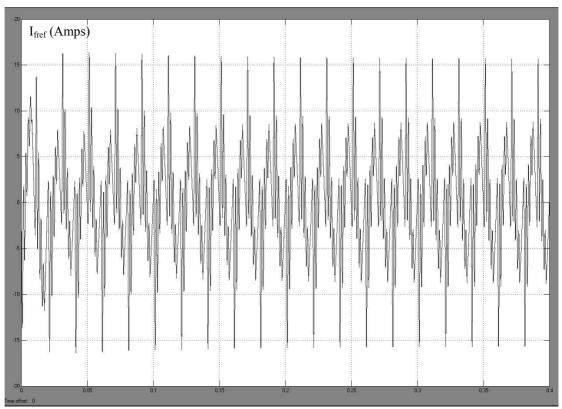

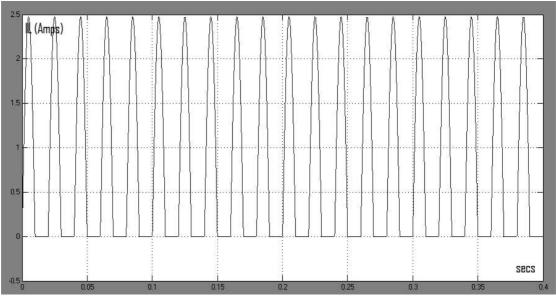

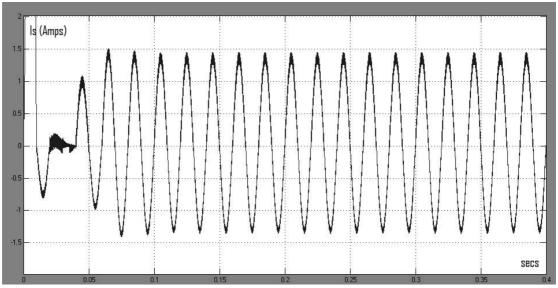

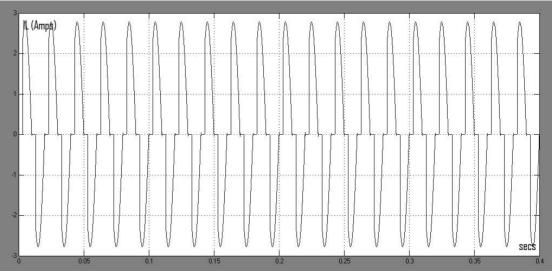

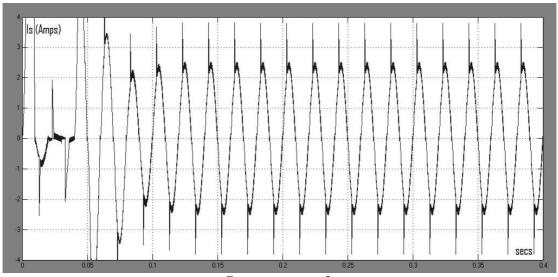

| 5.7        |         | ulation results                                                  |               |

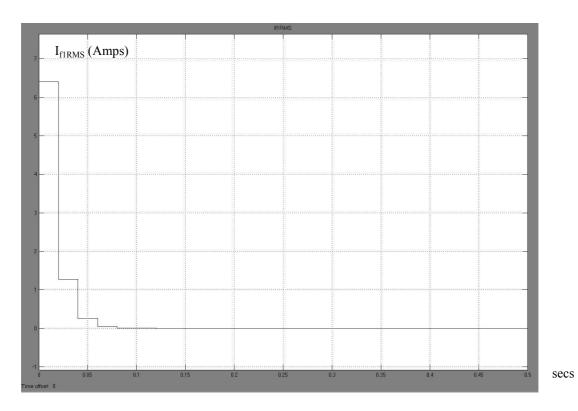

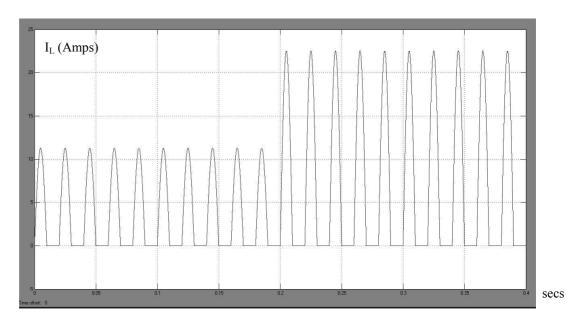

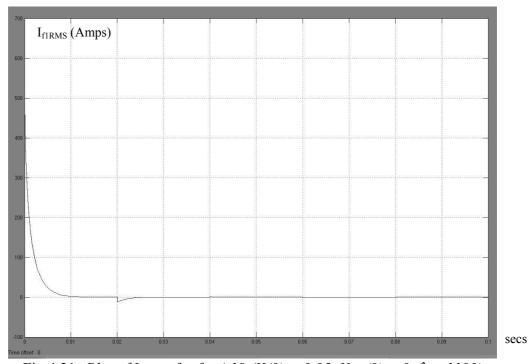

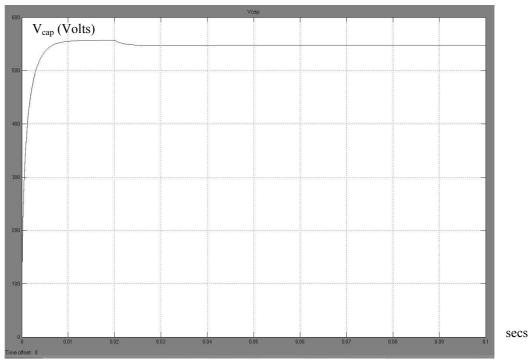

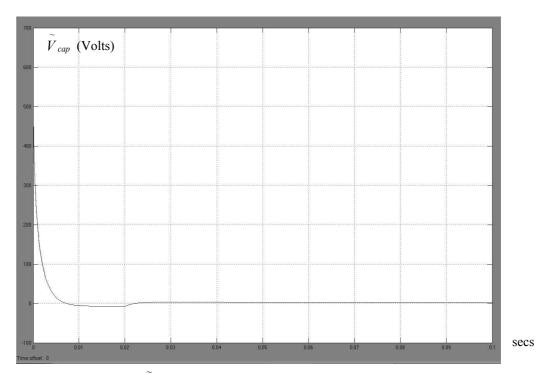

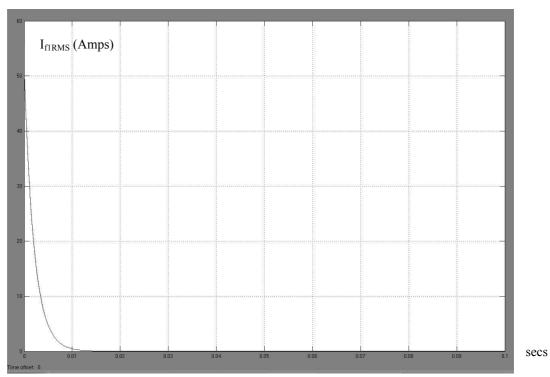

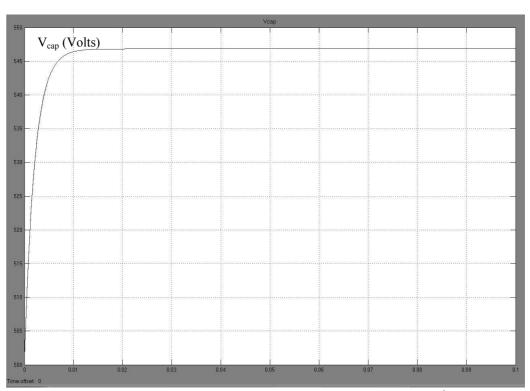

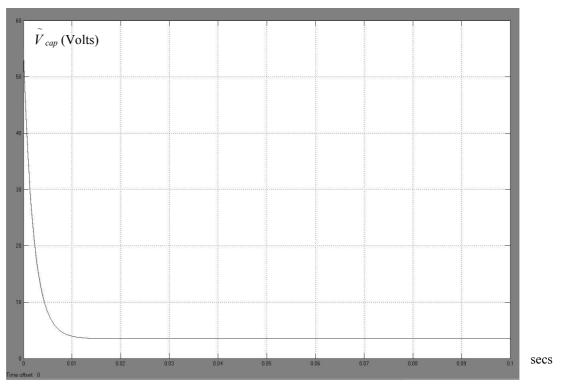

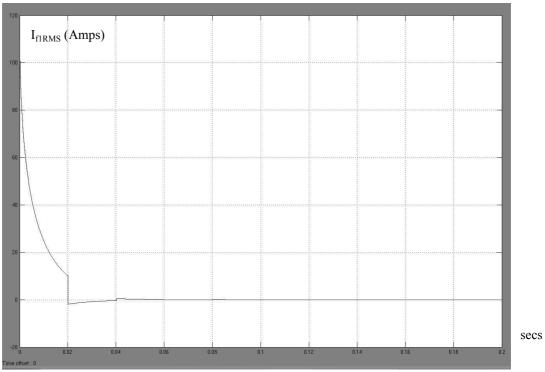

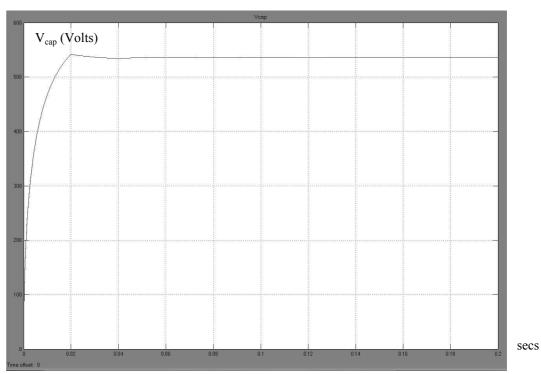

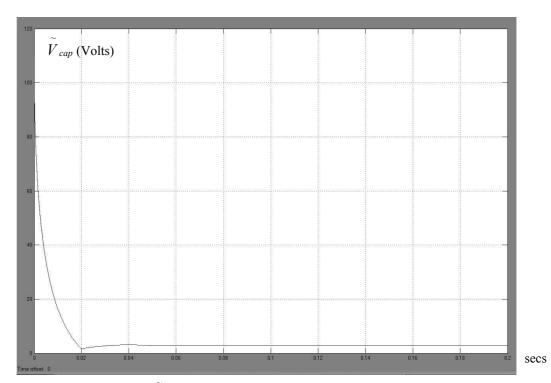

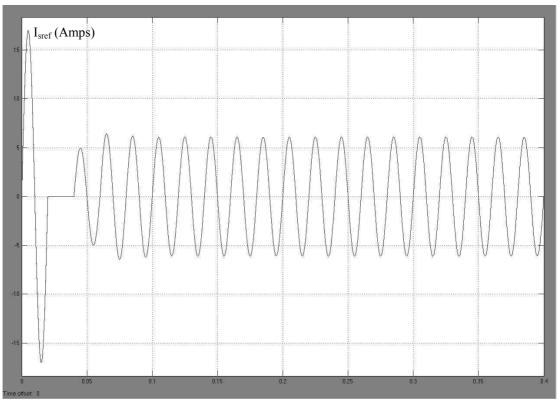

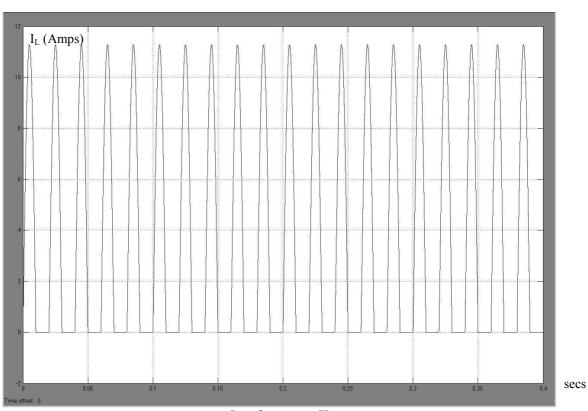

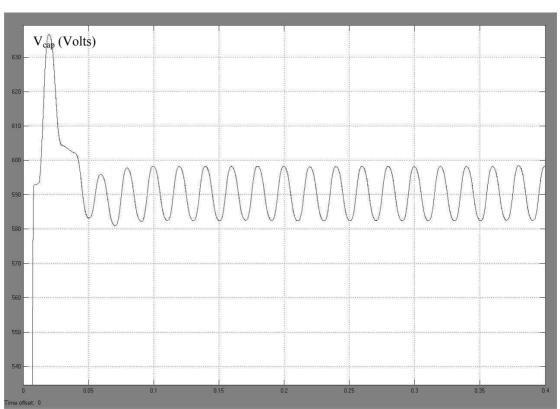

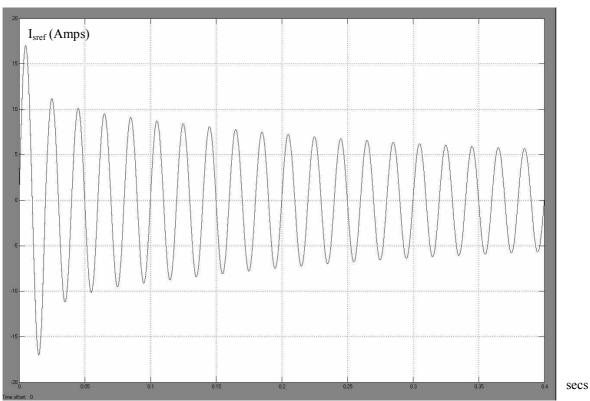

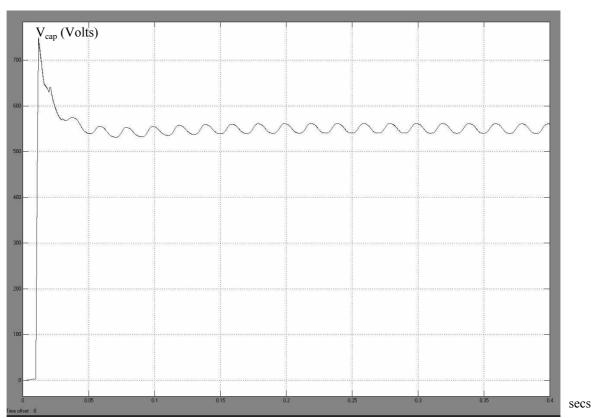

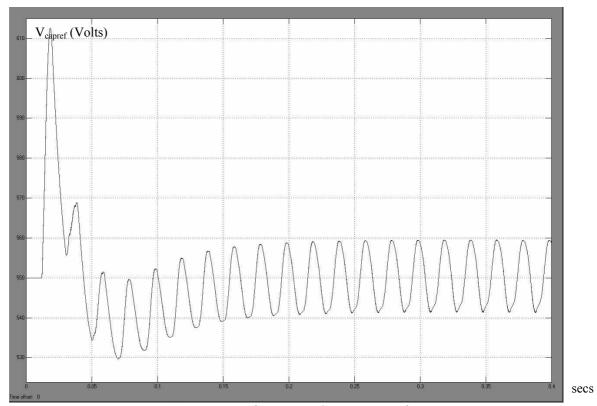

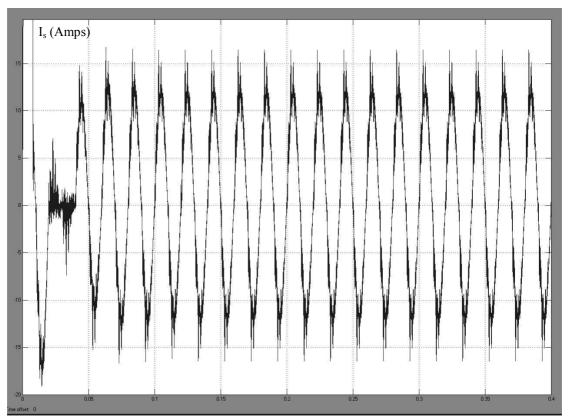

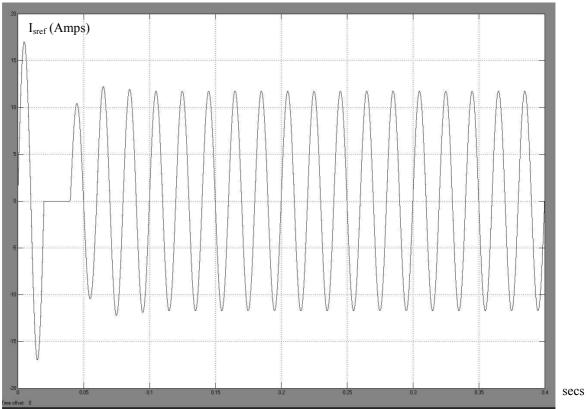

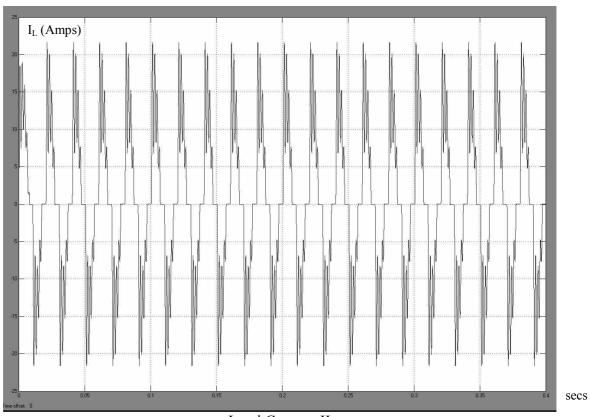

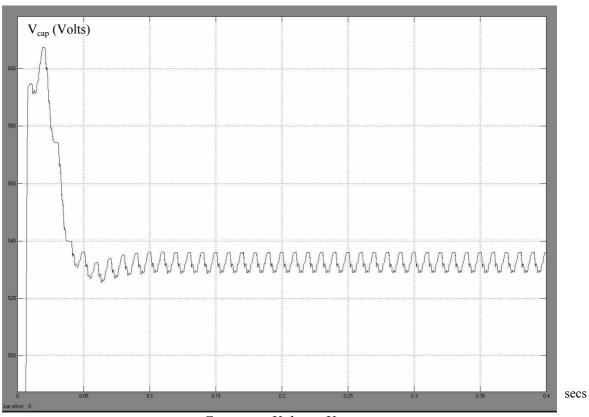

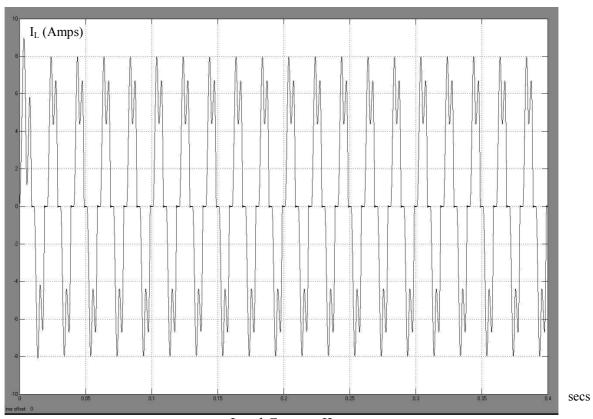

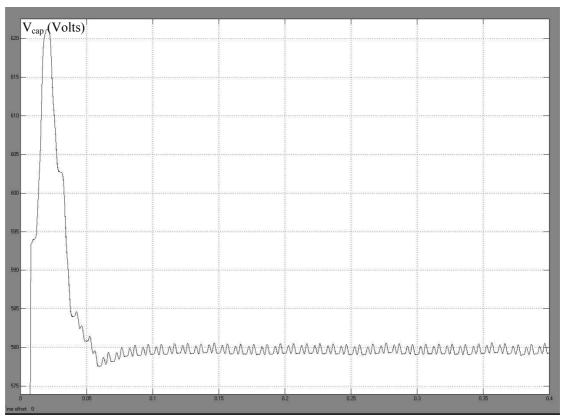

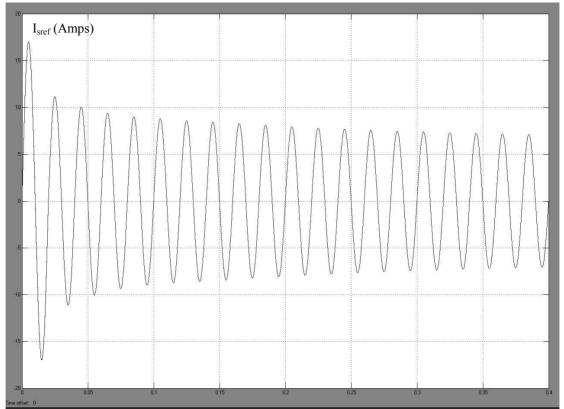

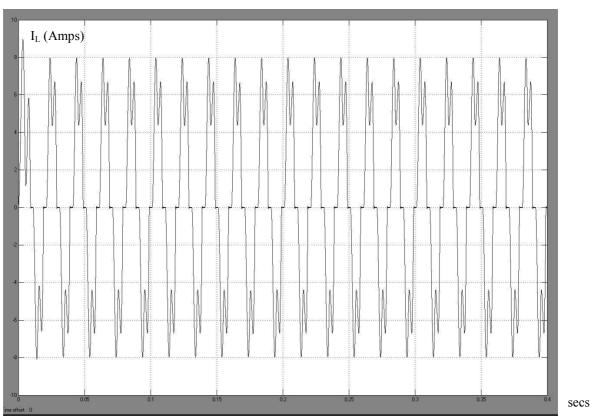

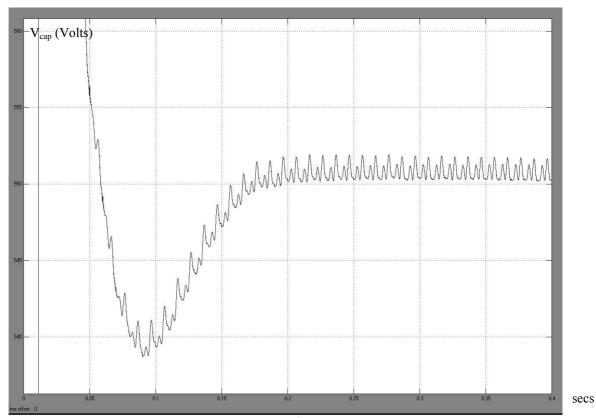

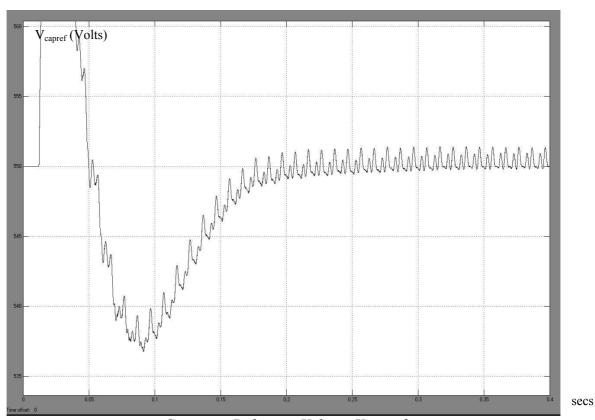

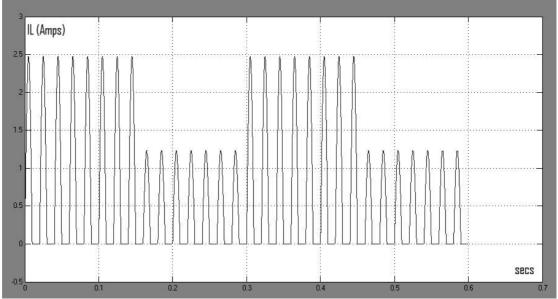

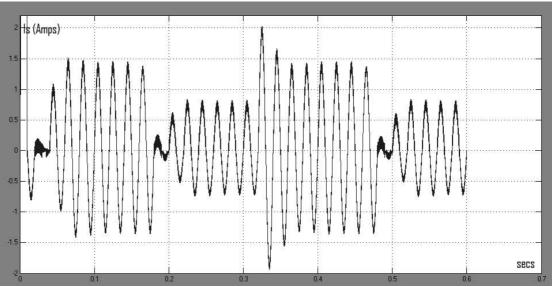

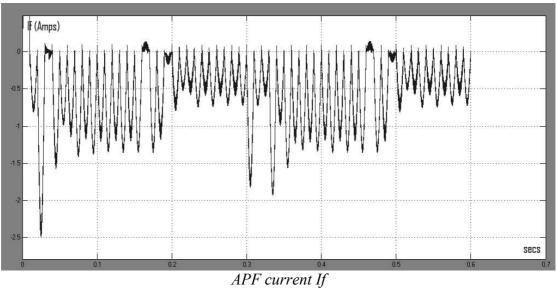

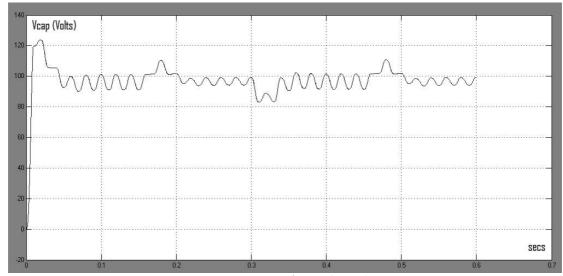

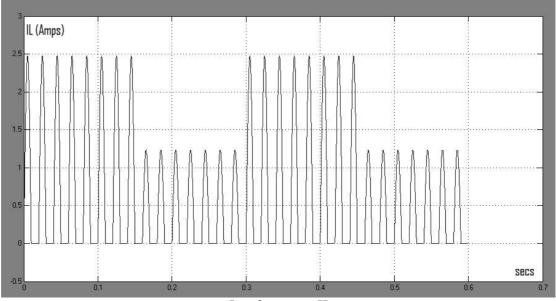

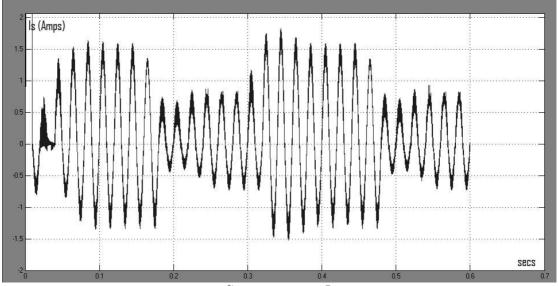

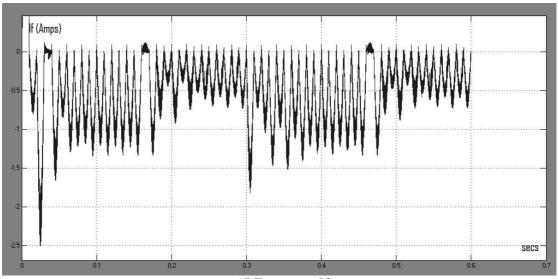

|            | 5.7.1   | Constant 30 Ohm half wave rectified load $\varepsilon = 0.9$     |               |

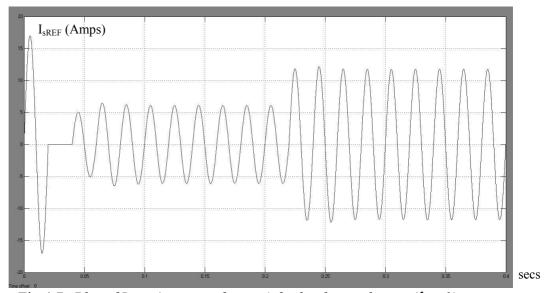

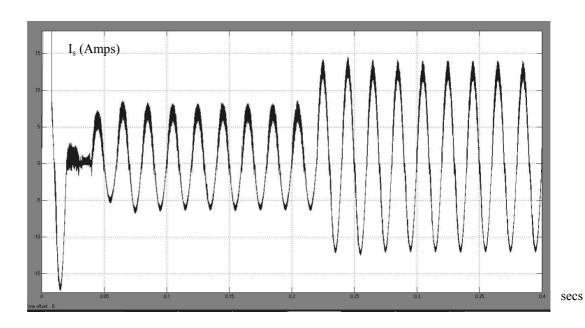

|            | 5.7.2   | Switched half-wave resistive load $\varepsilon = 0.9$            |               |

|            | 5.7.3   | Switched half-wave resistive load $\varepsilon = 0.5$            |               |

|            | 5.7.4   | Phase Controlled load $\varepsilon = 0.9$                        |               |

| 5.8        |         | etical Results                                                   |               |

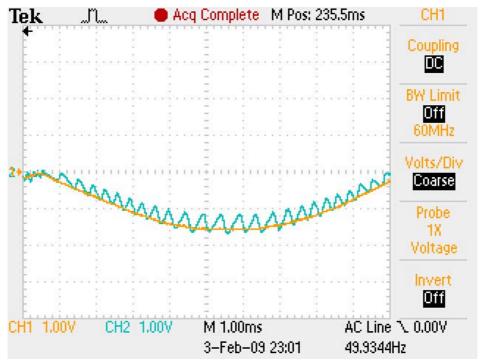

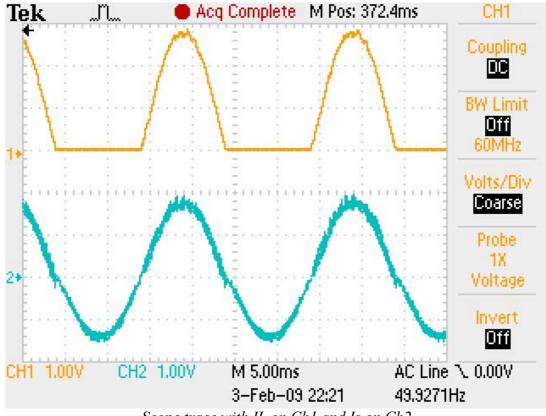

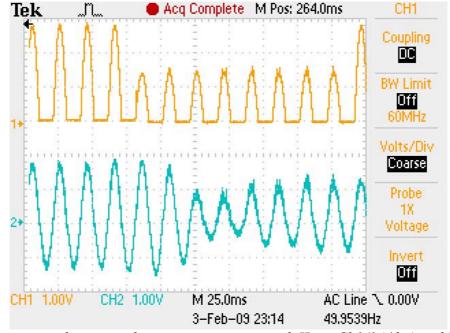

|            | 5.8.1   | Constant 30 Ohm half wave rectified load $\varepsilon = 0.9$     |               |

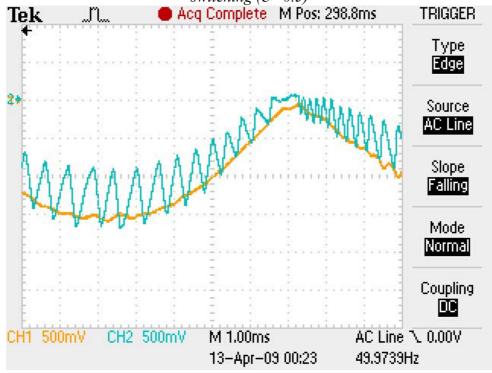

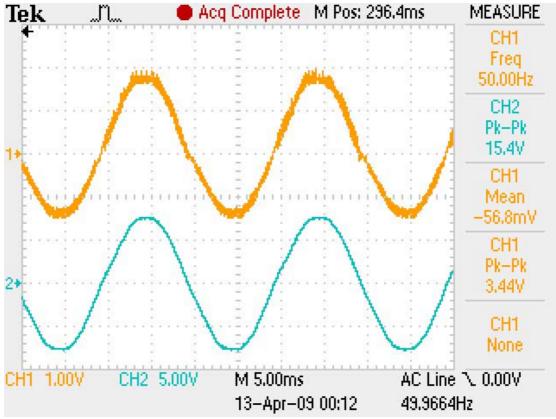

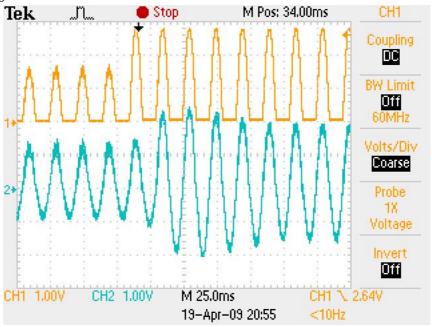

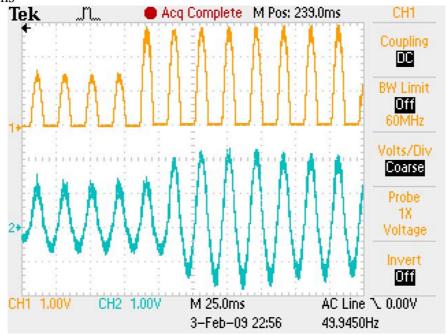

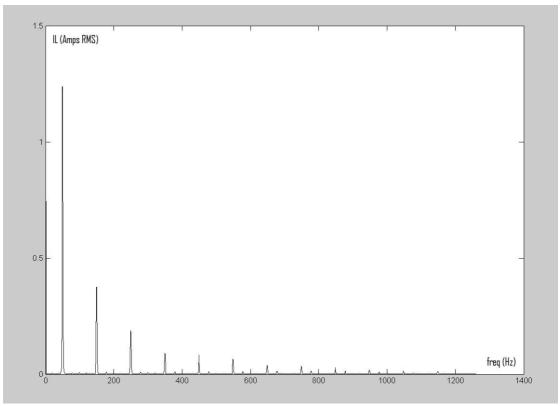

|            | 5.8.2   | Switched half-wave resistive load $\varepsilon = 0.9$            |               |

|            | 5.8.3   | Switched half-wave resistive load $\varepsilon = 0.5$            | 236           |

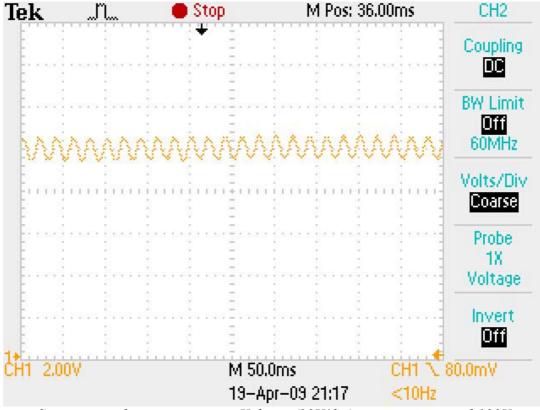

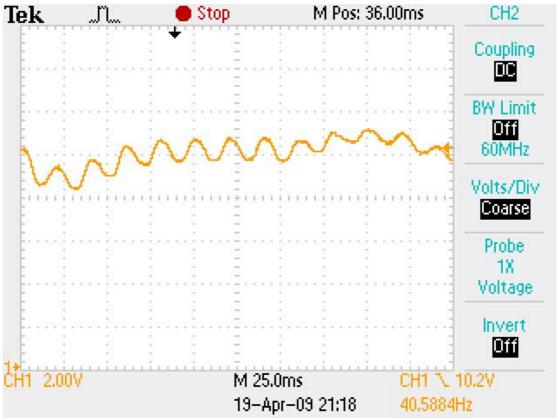

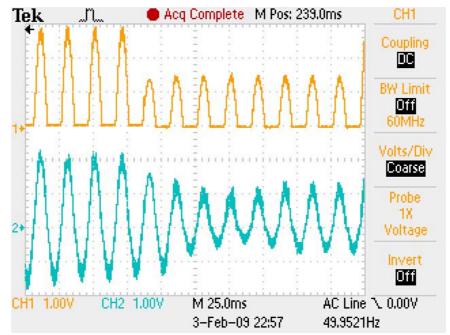

|            | 5.8.4   | Phase Controlled load $\varepsilon = 0.9$                        | 236           |

| 5.9        | Proj    | portional hysterisis switching with Energy Compensation Control: |               |

|            | Con     | clusions                                                         | 237           |

|            |         |                                                                  |               |

| Cha        | apter 6 | Conclusions and Further work                                     | 238           |

|            | ~       |                                                                  |               |

| 6.1        |         | clusions                                                         |               |

| 6.2        | Furt    | her Work                                                         | 241           |

| ъ с        |         |                                                                  | 2.42          |

| Kei        | erences |                                                                  | 242           |

| 1.         | Tox     | t books and general references                                   | 242           |

| 2.         |         | cifications                                                      |               |

| 2.<br>3.   |         | ase Active Power Filter papers using the PWM Bridge driving      | 243           |

| ۶.         | method  |                                                                  | 244           |

|            |         | oportional plus Integral Control as part of feedback strategy    |               |

|            |         | phase techniques using PWM                                       |               |

| 4.         |         | hase Active Power Filter papers using the PWM Bridge driving     | 4             |

| ٠.         |         | ase Active rower riter papers using the r wivi Bridge driving    | 244           |

|            |         | ues using Proportional plus Integral as part of control strategy |               |

|            |         | op or more press more as part or control bilates, f              | <u></u> .   . |

| 5.   | Single Phase Active Power Filter papers using methods other than PWM        |     |

|------|-----------------------------------------------------------------------------|-----|

|      | for driving the Bridge                                                      | 245 |

|      | Hysterisis method.                                                          | 245 |

|      | Sliding Mode / VSCS                                                         |     |

|      | Other single phase techniques not employing PWM to drive the bridge         | 246 |

| 6.   | University Reference Theses                                                 | 246 |

| 7.   | VAR Compensation Techniques                                                 | 246 |

| 8.   | Methods based on energy calculations for conductance control using Hysteris | is  |

|      | switching                                                                   | 247 |

| 9.   | General Survey and Overview Documents on Active Power Filters               | 247 |

| 10.  | Transistor specifications and related documents                             |     |

| Bibl | liography                                                                   | 249 |

| 1.   | Text Books                                                                  | 249 |

| 2.   | Specifications                                                              | 249 |

| 3.   | Three Phase Active Power Filter papers using the PWM Bridge driving meth    |     |

|      |                                                                             |     |

|      | Predictive/Deadbeat                                                         |     |

|      | Fuzzy Control                                                               |     |

|      | Using Proportional plus Integral Control as part of feedback strategy       |     |

|      | Adaptive/Neural based control strategy                                      |     |

|      | Other 3-phase techniques using PWM                                          | 252 |

| 4.   | Three Phase Active Power Filter papers using methods other than PWM for     |     |

|      | driving the Bridge                                                          | 254 |

| 5.   | Single Phase Active Power Filter papers using the PWM Bridge driving        |     |

|      | method                                                                      |     |

|      | Other Single Phase Techniques using PWM                                     | 256 |

| 6.   | Single Phase Active Power Filter papers using methods other than PWM for    |     |

|      | driving the Bridge                                                          |     |

| 7.   | University Reference Theses.                                                |     |

| 8.   | VAR Compensation Techniques                                                 | 259 |

| 9.   | General Survey and Overview Documents on Active Power Filters               | 259 |

| App  | oendix A: The Single Phase H-Bridge                                         | 260 |

| ••   |                                                                             |     |

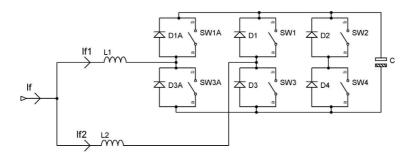

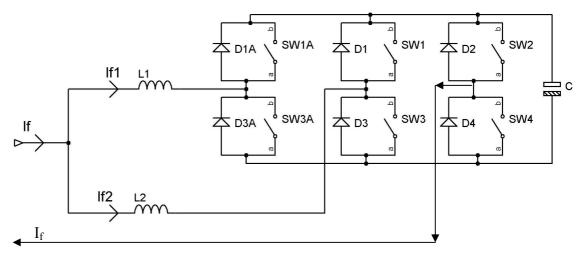

| App  | pendix B: The Single Phase 3/2 H-Bridge                                     | 261 |

| App  | pendix C: MATLAB Model (APF3.mdl) used to investigate zero and 1st          |     |

|      | 8                                                                           | 262 |

|      | endix C: APF Block Connections                                              |     |

|      | endix C: 3/2 H-Bridge                                                       |     |

|      | endix C: Non-Linear Load                                                    |     |

|      | endix C: Source                                                             |     |

|      | endix C: Switching Controller                                               |     |

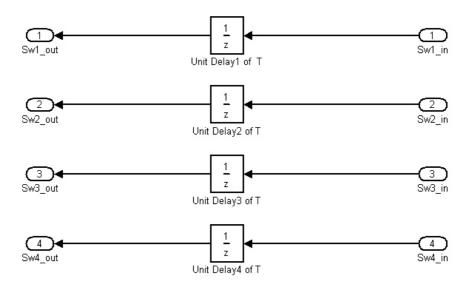

|      | endix C: Switch Sampler                                                     |     |

|      | endix C: Sliding Surface                                                    |     |

| App  | endix C: Measurements                                                       | 269 |

| Appendix D: M File switch_control3a.m (algorithm used in conjunction wit                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Matlab model of Appendix C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <i>2</i> / (                                                              |

| Appendix E: M File freqplot3.m (used to analyse the output of the Matlab                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                           |

| model of Appendix C and Appendix G)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 275                                                                       |

| Appendix F: Result sets for sections 3.13.3, 3.13.4 and 3.13.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 277                                                                       |

| Appendix F: Result Set 1a.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                           |

| Appendix F: Result Set 1b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 282                                                                       |

| Appendix F: Result Set 2a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 288                                                                       |

| Appendix F: Result Set 2b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 293                                                                       |

| Appendix F: Result Set 3a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 299                                                                       |

| Appendix F: Result Set 3b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                           |

| Appendix G: Matlab model for APF (APF6.mdl) incorporating a PI control                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ller                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 310                                                                       |

| Appendix G: block Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                           |

| Appendix G: H-Bridge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                           |

| Appendix G: non-linear load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                           |

| Appendix G: source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                           |

| Appendix G: Switching Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                           |

| Appendix G: Switch Sampler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                           |

| Appendix G: Sliding Surface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                           |

| Appendix G: Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 317                                                                       |

| Appendix H: Matlab control algorithm switch_control6.m (for use with                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                           |

| APF6.mdl given in Appendix G)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 318                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                           |

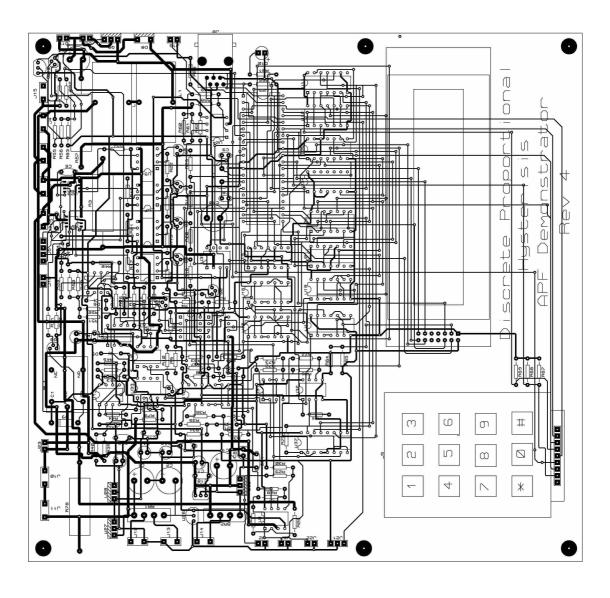

| Appendix I: Circuit diagrams for Practical demonstration system using                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                           |

| Appendix I: Circuit diagrams for Practical demonstration system using Proportional hysterisis and energy compensation                                                                                                                                                                                                                                                                                                                                                                                                                | 321                                                                       |

| Appendix I: Circuit diagrams for Practical demonstration system using Proportional hysterisis and energy compensation                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                           |

| Proportional hysterisis and energy compensation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 321                                                                       |

| Appendix I: sheet 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 321                                                                       |

| Proportional hysterisis and energy compensation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 321<br>322<br>323                                                         |

| Appendix I: sheet 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 321<br>322<br>323                                                         |

| Appendix I: sheet 1 Appendix I: sheet 2 Appendix I: sheet 3 Appendix I: sheet 4 Appendix I: sheet 5                                                                                                                                                                                                                                                                                                                                                                                                                                  | 321<br>322<br>323<br>324                                                  |

| Proportional hysterisis and energy compensation  Appendix I: sheet 1  Appendix I: sheet 2  Appendix I: sheet 3  Appendix I: sheet 4  Appendix I: sheet 5  Appendix I: sheet 6                                                                                                                                                                                                                                                                                                                                                        | 321<br>322<br>323<br>324<br>325                                           |

| Proportional hysterisis and energy compensation  Appendix I: sheet 1  Appendix I: sheet 2  Appendix I: sheet 3  Appendix I: sheet 4  Appendix I: sheet 5  Appendix I: sheet 6  Appendix I: sheet 7                                                                                                                                                                                                                                                                                                                                   | 321<br>322<br>324<br>325<br>326                                           |

| Appendix I: sheet 1 Appendix I: sheet 2 Appendix I: sheet 3 Appendix I: sheet 4 Appendix I: sheet 5 Appendix I: sheet 6 Appendix I: sheet 7 Appendix I: sheet 8                                                                                                                                                                                                                                                                                                                                                                      | 321<br>323<br>324<br>326<br>326                                           |

| Proportional hysterisis and energy compensation  Appendix I: sheet 1  Appendix I: sheet 2  Appendix I: sheet 3  Appendix I: sheet 4  Appendix I: sheet 5  Appendix I: sheet 6  Appendix I: sheet 7  Appendix I: sheet 8  Appendix I: sheet 9                                                                                                                                                                                                                                                                                         | 321<br>322<br>323<br>324<br>326<br>326<br>328                             |

| Proportional hysterisis and energy compensation  Appendix I: sheet 1  Appendix I: sheet 2  Appendix I: sheet 3  Appendix I: sheet 4  Appendix I: sheet 5  Appendix I: sheet 6  Appendix I: sheet 7  Appendix I: sheet 8  Appendix I: sheet 9  Appendix I: sheet 10                                                                                                                                                                                                                                                                   | 321<br>322<br>323<br>326<br>326<br>327<br>328                             |

| Proportional hysterisis and energy compensation  Appendix I: sheet 1  Appendix I: sheet 2  Appendix I: sheet 3  Appendix I: sheet 4  Appendix I: sheet 5  Appendix I: sheet 6  Appendix I: sheet 7  Appendix I: sheet 8  Appendix I: sheet 9  Appendix I: sheet 10  Appendix I: sheet 11                                                                                                                                                                                                                                             | 321<br>322<br>323<br>324<br>325<br>326<br>327<br>328                      |

| Proportional hysterisis and energy compensation  Appendix I: sheet 1  Appendix I: sheet 2  Appendix I: sheet 3  Appendix I: sheet 4  Appendix I: sheet 5  Appendix I: sheet 6  Appendix I: sheet 7  Appendix I: sheet 8  Appendix I: sheet 9  Appendix I: sheet 10  Appendix I: sheet 11  Appendix I: circuit components mounted off the PCB sheet 1                                                                                                                                                                                 | 321<br>322<br>323<br>325<br>326<br>328<br>3328<br>331                     |

| Proportional hysterisis and energy compensation  Appendix I: sheet 1  Appendix I: sheet 2  Appendix I: sheet 3  Appendix I: sheet 4  Appendix I: sheet 5  Appendix I: sheet 6  Appendix I: sheet 7  Appendix I: sheet 8  Appendix I: sheet 9  Appendix I: sheet 10  Appendix I: sheet 11  Appendix I: circuit components mounted off the PCB sheet 1  Appendix I: circuit components mounted off the PCB sheet 2                                                                                                                     | 321<br>322<br>323<br>326<br>327<br>328<br>330<br>331<br>332               |

| Appendix I: sheet 1 Appendix I: sheet 2 Appendix I: sheet 3 Appendix I: sheet 4 Appendix I: sheet 5 Appendix I: sheet 6 Appendix I: sheet 7 Appendix I: sheet 8 Appendix I: sheet 9 Appendix I: sheet 10 Appendix I: sheet 11 Appendix I: circuit components mounted off the PCB sheet 2 Appendix I: circuit components mounted off the PCB sheet 3                                                                                                                                                                                  | 321<br>323<br>324<br>325<br>326<br>327<br>338<br>331<br>332<br>333        |

| Proportional hysterisis and energy compensation  Appendix I: sheet 1  Appendix I: sheet 2  Appendix I: sheet 3  Appendix I: sheet 4  Appendix I: sheet 5  Appendix I: sheet 6  Appendix I: sheet 7  Appendix I: sheet 8  Appendix I: sheet 9  Appendix I: sheet 10  Appendix I: sheet 11  Appendix I: circuit components mounted off the PCB sheet 1  Appendix I: circuit components mounted off the PCB sheet 2                                                                                                                     | 321<br>322<br>323<br>325<br>326<br>328<br>331<br>331<br>332<br>334        |

| Appendix I: sheet 1 Appendix I: sheet 2 Appendix I: sheet 3 Appendix I: sheet 4 Appendix I: sheet 5 Appendix I: sheet 6 Appendix I: sheet 7 Appendix I: sheet 8 Appendix I: sheet 9 Appendix I: sheet 10 Appendix I: sheet 11 Appendix I: circuit components mounted off the PCB sheet 1 Appendix I: circuit components mounted off the PCB sheet 3 Appendix I: circuit components mounted off the PCB sheet 4 Appendix I: circuit components mounted off the PCB sheet 4 Appendix I: circuit components mounted off the PCB sheet 5 | 321<br>322<br>323<br>324<br>325<br>326<br>336<br>331<br>332<br>333<br>334 |

| Appendix I: sheet 1 Appendix I: sheet 2 Appendix I: sheet 3 Appendix I: sheet 4 Appendix I: sheet 5 Appendix I: sheet 6 Appendix I: sheet 7 Appendix I: sheet 8 Appendix I: sheet 9 Appendix I: sheet 10 Appendix I: sheet 11 Appendix I: circuit components mounted off the PCB sheet 1 Appendix I: circuit components mounted off the PCB sheet 3 Appendix I: circuit components mounted off the PCB sheet 4                                                                                                                       | 321322323325326326328331332334335                                         |

| Appendix K: C listing for APF demonstration system                       | 339   |

|--------------------------------------------------------------------------|-------|

| Appendix K: apf.c                                                        |       |

| Appendix K: utility.c                                                    |       |

| Appendix L: Matlab control algorithm switch_control5_53.m                | 362   |

| Appendix M: simulation results using discrete proportional hysterisis    | 9     |

| and energy compensation                                                  |       |

| Appendix M: Constant 30 Ohm half wave rectified load $\varepsilon = 0.9$ | 366   |

| Appendix M: Switched half-wave resistive load $\varepsilon = 0.9$        | 369   |

| Appendix M: Switched half-wave resistive load $\varepsilon = 0.5$        | 371   |

| Appendix M: Phase controlled load $\varepsilon = 0.9$                    | 373   |

| Appendix N: practical results from demonstration test system using di    |       |

| proportional hysterisis switching and energy compensation                | on376 |

| Appendix N: Constant 30 Ohm half wave rectified load $\varepsilon = 0.9$ | 376   |

| Appendix N: Switched half-wave resistive load $\varepsilon = 0.9$        | 379   |

| Appendix N: Switched half-wave resistive load $\varepsilon = 0.5$        | 381   |

| Appendix N: Phase controlled load $\varepsilon = 0.9$                    | 382   |

## List of Figures

| T 44 T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

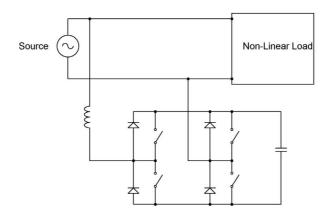

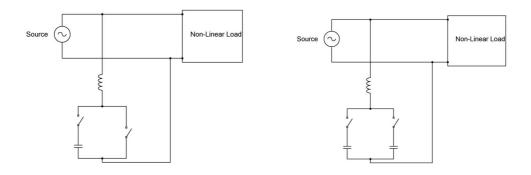

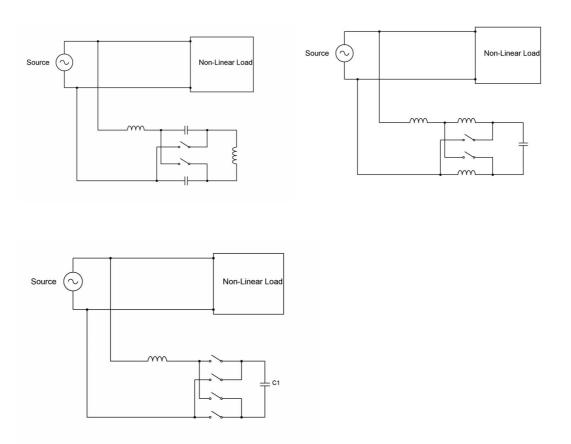

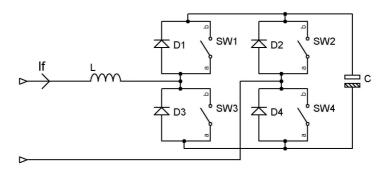

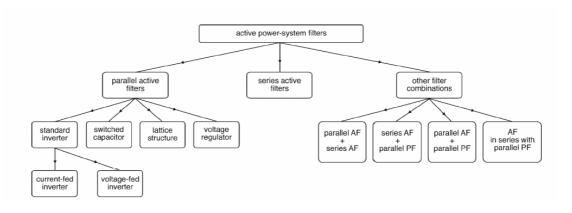

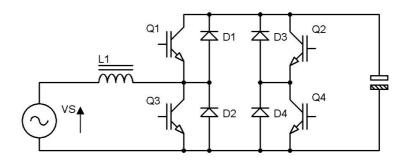

| FIG 1.1: VOLTAGE FED INVERTER BRIDGE APF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| FIG 1.2: CURRENT FED INVERTER BRIDGE APF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

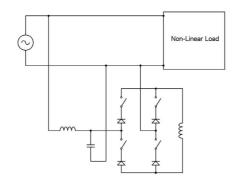

| FIG 1.3: SWITCHED CAPACITOR APF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| FIG 1.4: LATTICE STRUCTURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| FIG 1.5: BLOCK DIAGRAM OF A UNIFIED POWER FLOW CONTROLLER (UPFC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |