### Coset Coding to Extend the Lifetime of Non-Volatile Memory

by

### Adam Jacobvitz

# Department of Electrical and Computer Engineering Duke University

| Date:                    |

|--------------------------|

| Approved:                |

| Daniel Sorin, Supervisor |

| Robert Calderbank        |

| Jeff Chase               |

| Andrew Hilton            |

|                          |

Dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical and Computer Engineering in the Graduate School of Duke University

Benjamin Lee

#### **ABSTRACT**

Coset Coding to Extend the Lifetime of Non-Volatile Memory

by

Adam Jacobvitz

Department of Electrical and Computer Engineering

Duke University

| Date:                    |

|--------------------------|

| Approved:                |

| Daniel Sorin, Supervisor |

| Robert Calderbank        |

| Jeff Chase               |

| Andrew Hilton            |

|                          |

An abstract of a dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical and Computer Engineering in the Graduate School of Duke University

Benjamin Lee

### **Abstract**

Modern computing systems are increasingly integrating both Phase Change Memory (PCM) and Flash memory technologies into computer systems being developed today, yet the lifetime of these technologies is limited by the number of times cells are written. Due to their limited lifetime, PCM and Flash may wear-out before other parts of the system. The objective of this dissertation is to increase the lifetime of memory locations composed of either PCM or Flash cells using coset coding.

For PCM, we extend memory lifetime by using coset coding to reduce the number of bit-flips per write compared to un-coded writes. Flash program/erase operation cycle degrades page lifetime; we extend the lifetime of Flash memory cells by using coset coding to re-program a page multiple times without erasing. We then show how coset coding can be integrated into Flash solid state drives.

We ran simulations to evaluate the effectiveness of using coset coding to extend PCM and Flash lifetime. We simulated writes to PCM and found that in our simulations coset coding can be used to increase PCM lifetime by up to 3x over writing un-coded data directly to the memory location. We extended the lifetime of Flash using coset coding to re-write pages without an intervening erase and were able to re-write a single Flash page using coset coding more times than when writing un-coded data or using prior coding work for the same area overhead. We also found in our simulations that using coset coding in a Flash SSD results in higher lifetime for a given area overhead compared to un-coded writes.

# **Dedication**

To my family, mentors, and friends.

# **Table of Contents**

| 1. | In  | ntroduction                                                                                 | 1  |

|----|-----|---------------------------------------------------------------------------------------------|----|

| 1  | .1  | Memory Technologies                                                                         | 1  |

| 1  | .2  | Goals and Contributions                                                                     | 2  |

| 1  | .3  | Outline                                                                                     | 3  |

| 2. | Co  | oset Coding                                                                                 | 4  |

| 2  | .1  | Coset Code Terminology                                                                      | 4  |

| 2  | .2  | Coset Coding Encoding and Decoding Steps                                                    | 5  |

|    | 2.: | 2.1 Encoding Steps                                                                          | 5  |

|    | 2.: | 2.2 Decoding Steps                                                                          | 6  |

| 2  | .3  | Mapping Between Dataword and Coset                                                          | 7  |

|    | 2.: | 3.1 Coset Code Matrix Construction                                                          | 7  |

|    |     | 2.3.1.1 The Zero Coset Generator Matrix (Z)                                                 | 8  |

|    |     | 2.3.1.2 The Decoder Matrix (H) and Coset Label Generator Matrix (H*)                        | 9  |

|    | 2.: | 3.2 Error Correcting Coset Code (ECCC) Matrix Construction                                  | 9  |

|    |     | 2.3.2.1 ECC Matrices                                                                        | 11 |

|    |     | 2.3.2.2 Z (Zero Coset Generator Matrix), H <sup>#</sup> (Coset Generator Label Matrix), and | Н  |

|    |     | (Decoder Matrix) for Error Correction                                                       | 12 |

| 2  | .4  | Selecting a Coset Representative to Write from a Coset                                      | 14 |

|    | 2.4 | 4.1 Translate Coset                                                                         | 15 |

| 2.4.2 The Metric Function                        | 16 |

|--------------------------------------------------|----|

| 2.4.3 Exhaustive Search                          | 17 |

| 2.4.4 The Viterbi Algorithm                      | 19 |

| 3. Extending the Lifetime of Phase Change Memory | 21 |

| 3.1 Background                                   | 22 |

| 3.2 Failure Modes                                | 23 |

| 3.3 Related Work                                 | 23 |

| 3.3.1 Postponing Wear-out: BFR                   | 24 |

| 3.3.2 Tolerating Wear-out: Error Correction      | 25 |

| 3.3.3 Adding Memory Cells                        | 25 |

| 3.3.4 Wear-leveling                              | 26 |

| 3.4 FlipMin                                      | 26 |

| 3.4.1 System Model Assumptions                   | 27 |

| 3.4.2 FlipMin Coset Representative Selection     | 27 |

| 3.4.2.1 Steps                                    | 27 |

| 3.4.2.2 Example                                  | 29 |

| 3.4.3 Coset Erasure Matching (CEM)               | 30 |

| 3.5 FlipMin BFR Evaluation                       | 31 |

| 3.5.1 Methodology                                | 32 |

| 3.5.2 Results                                    | 32 |

| 3.6 Implementation                             | 33 |

|------------------------------------------------|----|

| 3.6.1 System Model                             | 33 |

| 3.6.2 Encoder                                  | 34 |

| 3.6.3 Decoder                                  | 37 |

| 3.7 Hardware Costs                             | 38 |

| 3.7.1 Coset Codes Evaluated                    | 38 |

| 3.7.2 Process Used to Evaluate Hardware Costs  | 39 |

| 3.7.3 Encoder Costs                            | 40 |

| 3.7.4 Decoder Costs                            | 40 |

| 3.8 Experimental Methodology                   | 41 |

| 3.8.1 Techniques Compared Against              | 41 |

| 3.8.2 Modeling Wear-Out                        | 42 |

| 3.9 Results                                    | 43 |

| 3.9.1 Random Input Results                     | 43 |

| 3.9.2 Benchmark Results                        | 54 |

| 3.9.2.1 Methodology                            | 54 |

| 3.9.2.2 Results                                | 55 |

| 3.10 Conclusion                                | 57 |

| 4. Extending the Lifetime of NAND Flash Memory | 58 |

| 4.1 Flash Background                           | 59 |

| 4.2 | 1.1 Flash Organization                                                | 59 |

|-----|-----------------------------------------------------------------------|----|

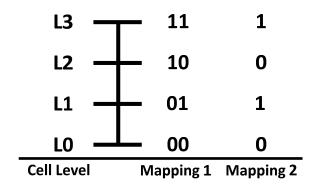

| 4.3 | 1.2 Storing Data in Flash Cells                                       | 60 |

| 4.2 | 1.3 Flash SSDs and ECC                                                | 62 |

| 4.2 | 1.4 Wear-out Mechanism                                                | 63 |

| 4.2 | Related Work                                                          | 64 |

| 4.2 | 2.1 Flash Location Lifetime Extension Prior Work                      | 65 |

| 4.2 | 2.2 Flash SSD Lifetime Extension Prior Work                           | 66 |

| 4.3 | Coset Code Design                                                     | 67 |

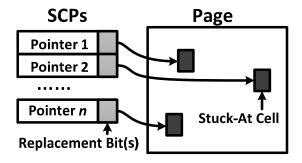

| 4.3 | 3.1 Metric Functions                                                  | 67 |

|     | 4.3.1.1 Flash Write and Cell Information Used in Our Metric Functions | 68 |

|     | 4.3.1.2 Metric Function BFR                                           | 69 |

|     | 4.3.1.3 Metric Function BFR+SCI+WL                                    | 69 |

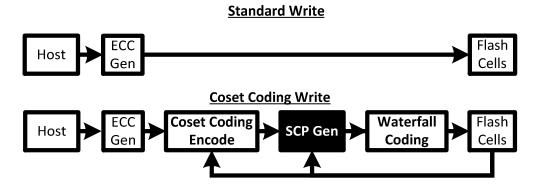

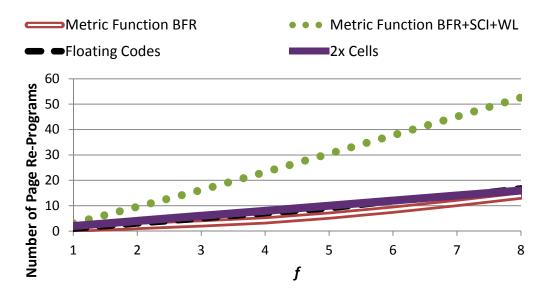

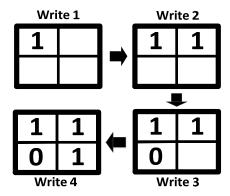

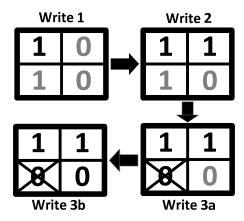

| 4.3 | 3.2 Write and Read Processes                                          | 71 |

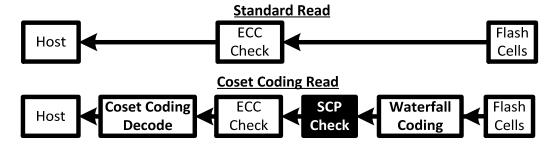

| 4.4 | Stuck-At Cell Pointers (SCPs)                                         | 74 |

| 4.5 | Flash Memory Location Lifetime Extension Evaluation                   | 74 |

| 4.5 | 5.1 Evaluation Methodology                                            | 75 |

| 4.5 | 5.2 Techniques Compared                                               | 75 |

| 4.5 | 5.3 Results                                                           | 77 |

| 4.6 | Flash SSD Implementation Design                                       | 81 |

| 4.6 | 6.1 Map Table                                                         | 82 |

| 4.6.2    | Garbage Collector                 | 84  |

|----------|-----------------------------------|-----|

| 4.6.3    | Write Controller                  | 88  |

| 4.7 Fla  | ash SSD Implementation Evaluation | 89  |

| 4.7.1    | Methodology                       | 90  |

| 4.7.2    | Over-Provisioning                 | 93  |

| 4.7.3    | Results                           | 93  |

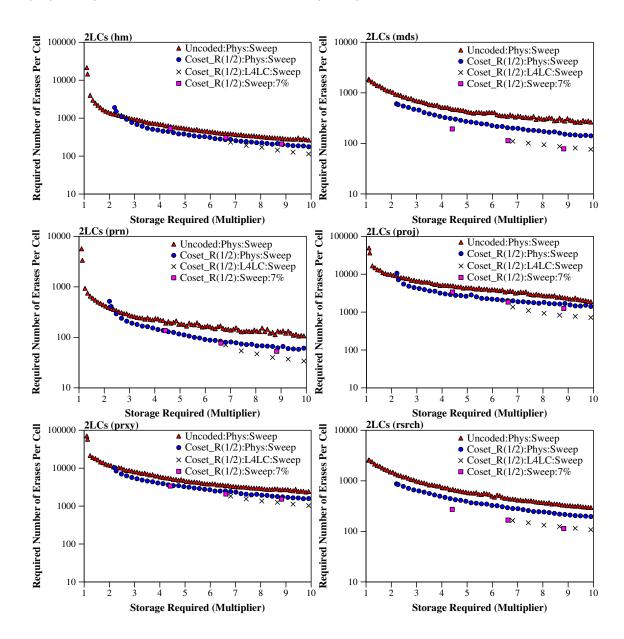

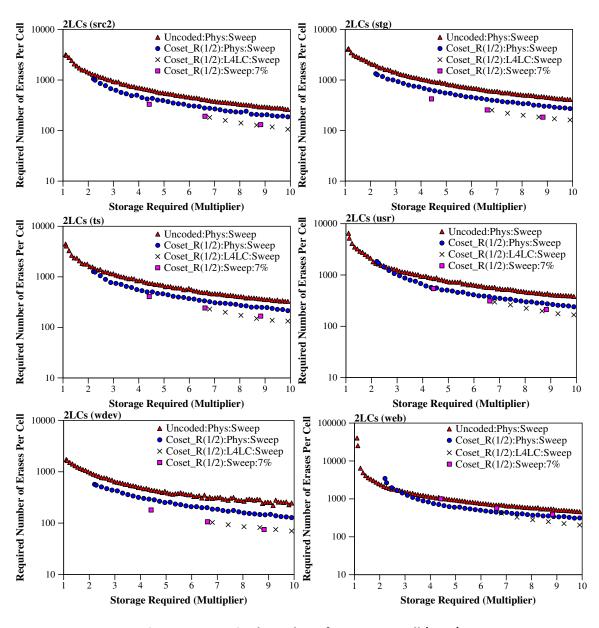

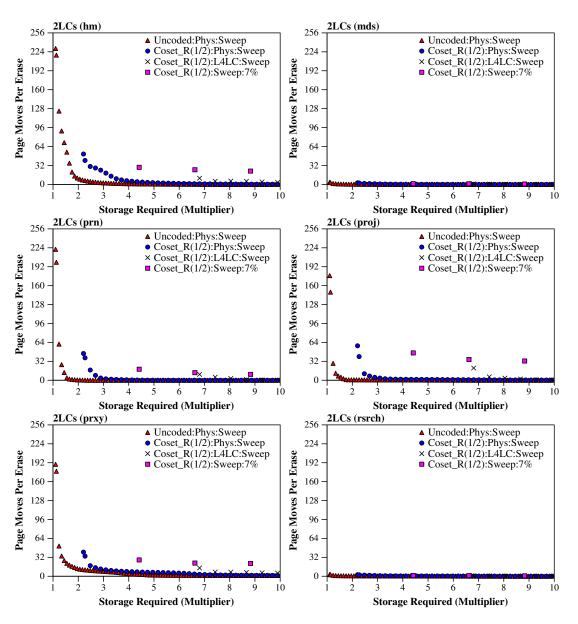

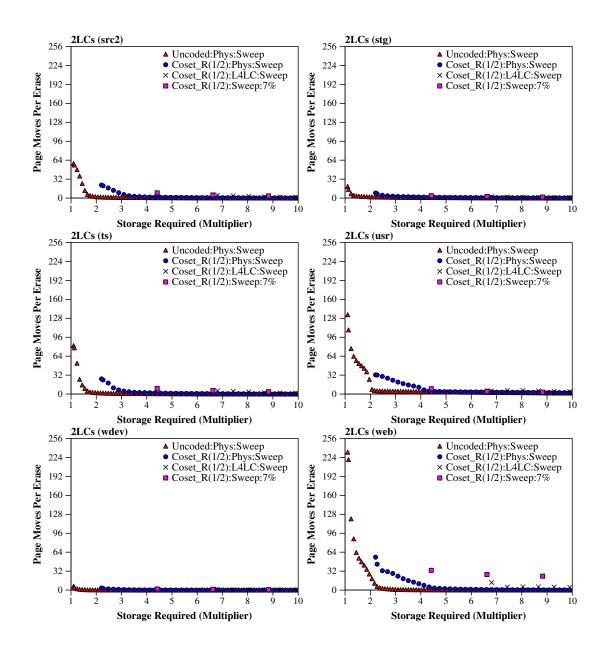

| 4.7      | .3.1 2LCs                         | 93  |

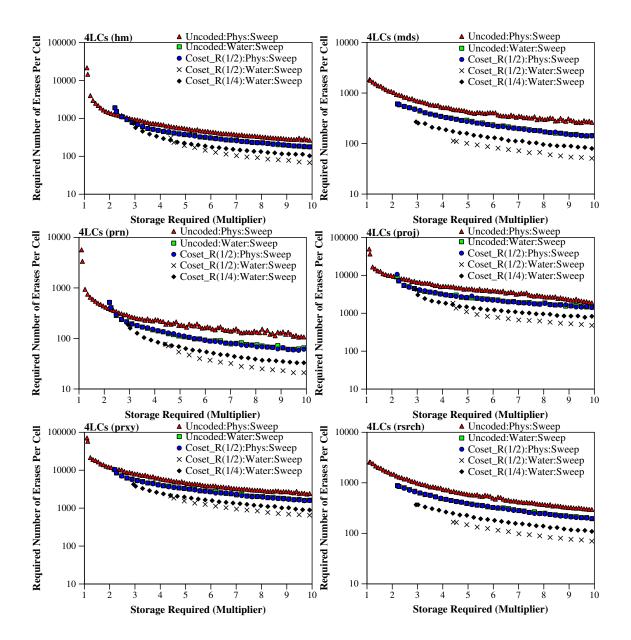

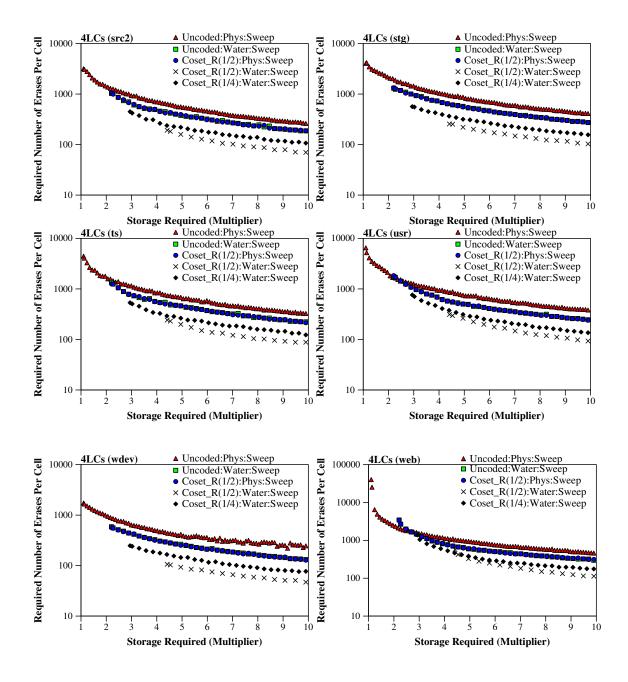

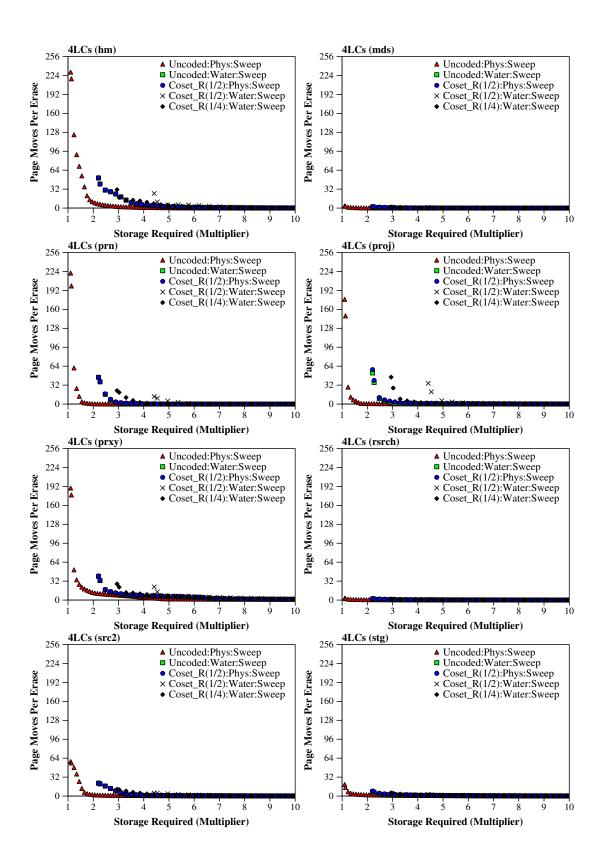

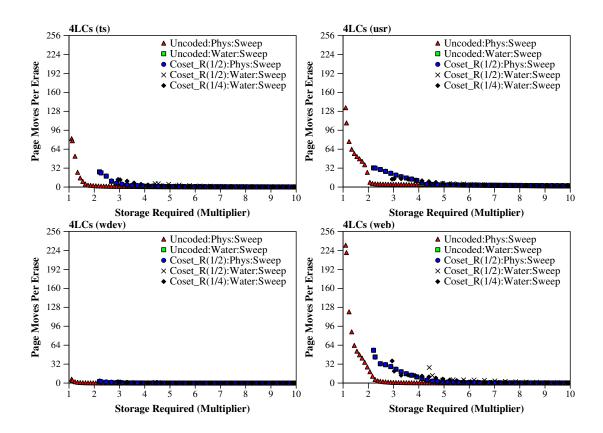

| 4.7      | .3.2 4LCs                         | 99  |

| 4.8 Co   | onclusion                         | 105 |

| 5. Concl | lusions                           | 107 |

# **List of Tables**

| Table 1: Memory Technology Properties2                                                     |

|--------------------------------------------------------------------------------------------|

| Table 2: Matrices Used as Part of Our Coset Coding Encoding/Decoding Implementation        |

| Table 3: PCM lifetime extension schemes. We quantitatively compare to un-shaded rows 24    |

| Table 4: 2-Bit to 3-Bit Repetition Coset Code                                              |

| Table 5: Bit Flip Reduction                                                                |

| Table 6: FlipMin with Different Block Codes                                                |

| Table 7: Coset Coding Encoder Costs                                                        |

| Table 8: Coset Coding Decoder Costs                                                        |

| Table 9: Schemes to Extend Memory Lifetime                                                 |

| Table 10: BFR schemes compared (CV 0.05)45                                                 |

| Table 11: BFR schemes compared (CV 0.2)                                                    |

| Table 12: FlipMin compared to error/stuck-at tolerance schemes (CV 0.05)                   |

| Table 13. FlipMin compared to error/stuck-at tolerance schemes (CV 0.2)                    |

| Table 14: BFR + stuck-at tolerance compared to error/stuck-at tolerance alone (CV 0.05) 50 |

| Table 15. BFR + stuck-at tolerance compared to error/stuck-at tolerance alone (CV 0.2)51   |

| Table 16: FM-RM(1,3) Compared to DoubleMem (CV 0.05)                                       |

| Table 17. FM-RM(1,3) Compared to DoubleMem (CV 0.2)54                                      |

| Table 18: System Configuration54                                                           |

| Table 19: Random Data Input Two-Write Probabilities For a Single Cell                      |

| Table 20: Floating Code Write Sequences                                                    |

| Table 21: Information Used in the Metric Functions                                         |

| Table 22: Evneriment Setup.                                                                |

| Table 23: Page Re-Writing Techniques We Compared                                | 76  |

|---------------------------------------------------------------------------------|-----|

| Table 24: Fields in a Map Table Entry                                           | 83  |

| Table 25: Benchmark Information                                                 | 90  |

| Table 26: Simulator Parameters                                                  | 91  |

| Table 27: Benchmarks Grouped By Data Footprint Size                             | 92  |

| Table 28: 2LC Schemes Evaluated                                                 | 94  |

| Table 29: Lifetime Graphs Y-Axis Min and Max Values (Erases Required Per Block) | 96  |

| Table 30: 4LC Schemes Evaluated                                                 | 100 |

# **List of Figures**

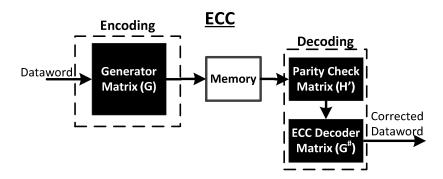

| Figure 1: Coset Code Encoding Process                                                  | 6       |

|----------------------------------------------------------------------------------------|---------|

| Figure 2: Coset Coding Decoding Process Both Without (top) and With (bottom) Error Cor | rection |

|                                                                                        | 6       |

| Figure 3: Coset Coding Encode and Decode Processes                                     | 8       |

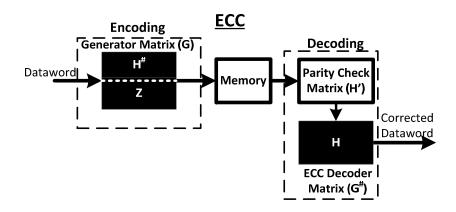

| Figure 4: ECCC Encoding and Decoding Proceses                                          | 10      |

| Figure 5: Encoding/Decoding ECC                                                        | 11      |

| Figure 6: ECC Encoding/Decoding Process with ECCC Matrices                             | 14      |

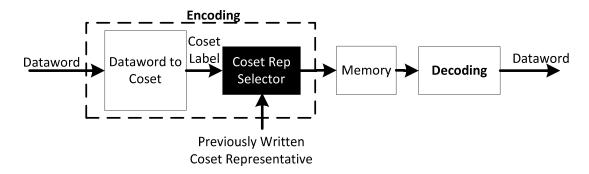

| Figure 7: Coset Rep Selector Highlighted in the Coset Coding Encoding/Decoding Process | 14      |

| Figure 8: Example Setup for Forming a Translate Coset                                  | 15      |

| Figure 9: Formation of a Translate Coset Representative                                | 16      |

| Figure 10: Exhaustive Search-Based Coset Rep Selector                                  | 17      |

| Figure 11: Enumerating the Zero Coset                                                  | 18      |

| Figure 12: Finding a Translate Coset Representative                                    | 18      |

| Figure 13: Enumerating the Translate Coset                                             | 19      |

| Figure 14: Viterbi-Based Coset Rep Selector                                            | 20      |

| Figure 15: PCM Cell in Low and High Resistance States                                  | 22      |

| Figure 16: Selecting the Preferred Coset Rep to Write Using FlipMin                    | 28      |

| Figure 17: FlipMin Coset Representative Selection Process with the Repetition Coset C  | ode in  |

| Table 4                                                                                | 30      |

| Figure 18: Coset Erasure Matching Example                                              | 31      |

| Figure 19: Example PCM Implementation that Integrates FlipMin into PCM Chips           | 34      |

| Figure 20: Hardware Block Diagram for Coset Label Generation                           | 35      |

| Figure 21: Generating the Translate Coset Label                                                |  |

|------------------------------------------------------------------------------------------------|--|

| Figure 22: Generating the Translate Coset                                                      |  |

| Figure 23: Coset Metric Calculation and Selection Logic                                        |  |

| Figure 24: Determining the Coset Rep to Write from the Translate Coset Leader and Previously   |  |

| Written Coset Representative                                                                   |  |

| Figure 25. Hardware Block Diagram for Decoding                                                 |  |

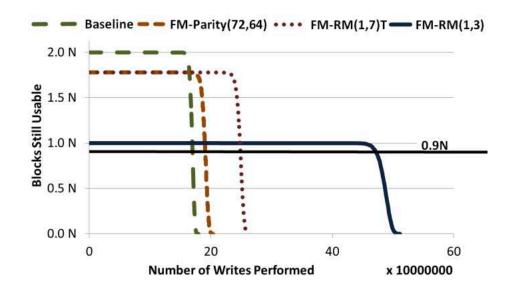

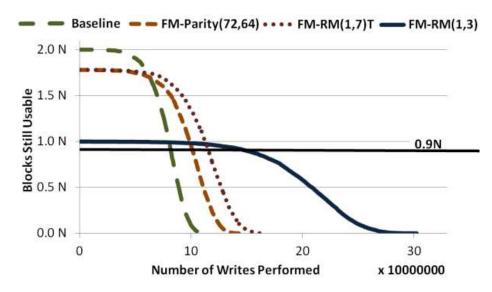

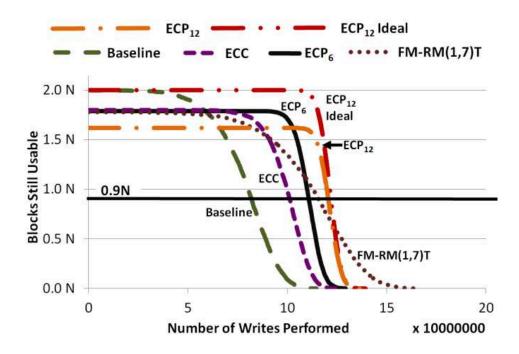

| Figure 26. BFR Schemes (CV 0.05)                                                               |  |

| Figure 27. BFR Schemes (CV 0.2)                                                                |  |

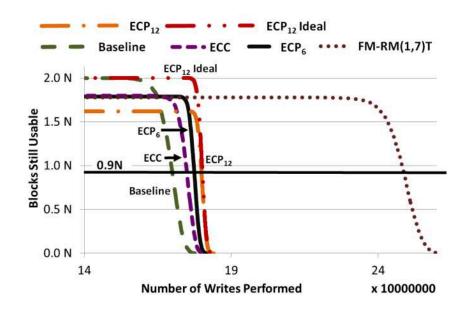

| Figure 28. Stuck-at Tolerance Compared to FlipMin (CV 0.05)                                    |  |

| Figure 29. Stuck-at Tolerance Compared to FlipMin (CV 0.2)                                     |  |

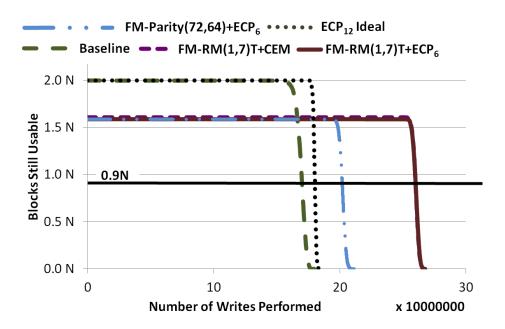

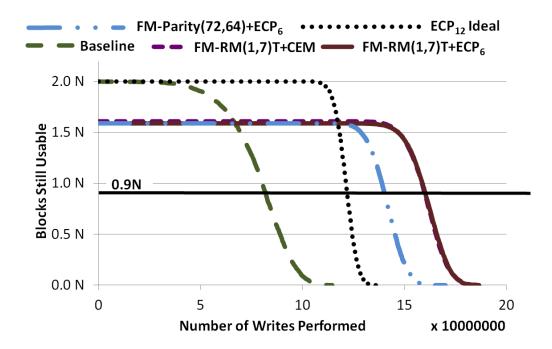

| Figure 30. FlipMin Combined With Stuck-at Tolerance (CV 0.05)50                                |  |

| Figure 31. FlipMin Combined with Stuck-at Tolerance (CV 0.2)                                   |  |

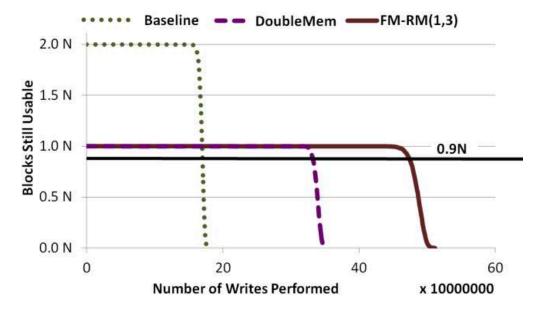

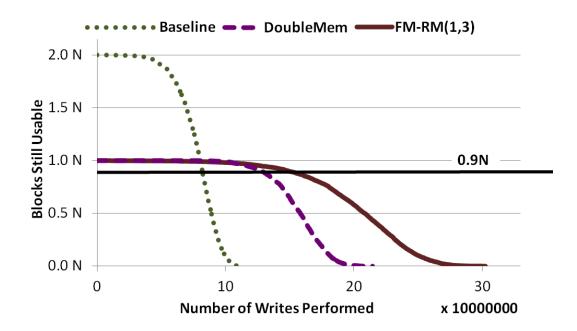

| Figure 32. FM-RM(1,3) Compared to DoubleMem (CV 0.05)52                                        |  |

| Figure 33. FM-RM(1,3) Compared to DoubleMem (CV 0.2)53                                         |  |

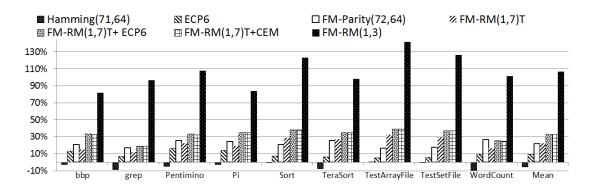

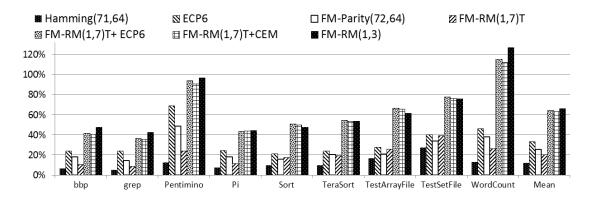

| Figure 34. Lifetime extension schemes compared using Hadoop inputs. CV 0.0556                  |  |

| Figure 35. Lifetime extension schemes compared using Hadoop inputs. CV 0.257                   |  |

| Figure 36: Example Mapping Between Cell Levels and Bits                                        |  |

| Figure 37: Coset Coding Write Process Compared to Write Process Used Today72                   |  |

| Figure 38: Coset Coding Read Process Compared to Standard Read Process Used Today73            |  |

| Figure 39: Stuck-At Cell Pointers74                                                            |  |

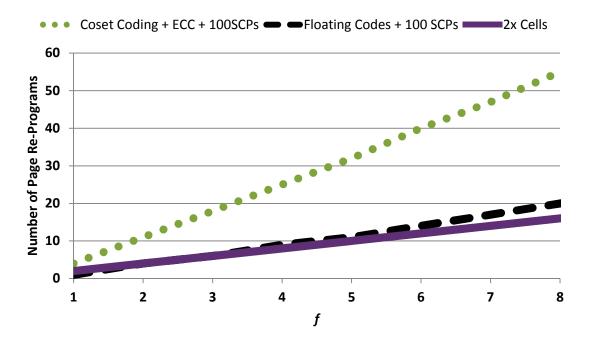

| Figure 40: Single Page Re-Write Count for Random Data Writes Using Re-Write Schemes 78         |  |

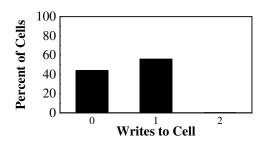

| Figure 41: Cell Wear Distribution Before Erase Using Metric Function BFR+SCI+WL With $f = 179$ |  |

| Figure 42: Single Page Re-Write Count for Random Data Writes Using Re-Write Sc | hemes + 100 |

|--------------------------------------------------------------------------------|-------------|

| SCPs                                                                           | 81          |

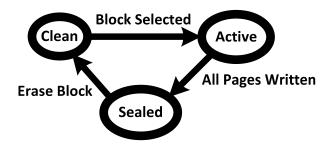

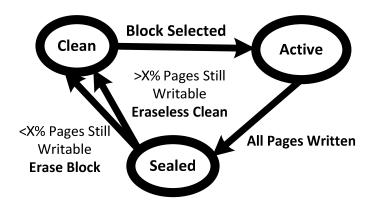

| Figure 43: Standard Garbage Collection                                         | 85          |

| Figure 44: Coset Coding Garbage Collection                                     | 86          |

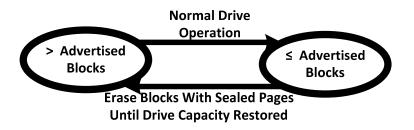

| Figure 45: Ensuring Sufficient Blocks are Available in the Drive               | 87          |

| Figure 46: Standard Write Process                                              | 88          |

| Figure 47: Coset Coding Write Process                                          | 89          |

| Figure 48: Required Number of Erases Per Cell (2LCs)                           | 96          |

| Figure 49: Average Number of Page Moves Per Erase (2LCs)                       | 98          |

| Figure 50: Required Number of Erases Per Cell (4LCs)                           | 102         |

| Figure 51: Average Number of Page Moves Per Erase (4LCs)                       | 104         |

# Acknowledgements

This research was supported in part by the National Science Foundation under grant 111-5367 and through XSEDE resources provided by the XSEDE Science Gateways program.

## 1. Introduction

Memory is used to store data in computing systems. Memory is organized into fixed sized locations composed of *memory cells*—hardware elements that store one or more bits. For example, Dynamic Random-Access Memory (DRAM) [59] cells consist of a single transistor. Some new next-generation memory technologies produced to replace and/or augment existing memory technologies have cells that are *write-limited*, i.e., they fail after a certain number of writes. When a single memory cell fails in a memory location, the entire memory location becomes unusable<sup>1</sup>. This dissertation introduces methods to increase the lifetime of memory locations composed of write-limited memory cells.

In this introduction, we introduce a number of memory technologies and indicate which memories are write-limited. Section 1.1 lists the different memory technologies, their status, and whether they are write-limited. Section 1.2 presents the goals and contributions of this dissertation. Section 1.3 presents how this dissertation is organized and the contributions of each chapter.

# 1.1 Memory Technologies

Modern computing systems incorporate many different memory technologies. Table 1 lists memory technologies currently in-use and next-generation memory technologies that are being developed for new computing systems. Unshaded rows are memories used in current production systems, and shaded rows are memories either in development or in the process of being integrated into production systems. Table 1 also lists which memory technologies are write-limited and which memory technologies are in mass production. In this dissertation, we

<sup>&</sup>lt;sup>1</sup> Techniques have been developed to tolerate failed cells in a memory location [25][54]

focus on improving the lifetime of memory locations composed of Phase Change Memory (PCM) cells and Flash cells. Both PCM and Flash are write-limited and are being mass-produced. Flash is currently in the process of being integrated into new and existing computing systems ranging from cell phones [62] to large scale datacenters [5] and super-computers [57]. PCM has started to enter mass production, but has not yet been integrated into new and existing computing systems.

**Table 1: Memory Technology Properties**

| Memory Technology | Write-Limited | Mass Produced | Highest Level<br>Used |

|-------------------|---------------|---------------|-----------------------|

| SRAM              | No            | Yes           | Cache                 |

| Memristors [54]   | Yes           | No            | Cache                 |

| eDRAM [19]        | No            | Yes           | Cache                 |

| DRAM              | No            | Yes           | Main Memory           |

| PCM [68]          | Yes           | Limited       | Main Memory           |

| STT-RAM [29]      | No            | No            | Main Memory           |

| ReRAM [5]         | Yes           | No            | Main Memory           |

| FeRAM [7]         | No            | No            | Main Memory           |

| RRAM [73]         | No            | No            | Main Memory           |

| Flash [44]        | Yes           | Yes           | Secondary Storage     |

| Hard Drives       | No            | Yes           | Secondary Storage     |

| Optical           | No            | Yes           | Archival Storage      |

| Tape              | No            | Yes           | Archival Storage      |

#### 1.2 Goals and Contributions

This dissertation introduces methods to extend lifetime of memory locations composed of write-limited memory cells. We focus on extending the lifetime of memory locations composed of either PCM cells or Flash cells, both of which are write-limited. We propose methods to extend the lifetime of memory locations with either PCM or Flash cells by incorporating coding techniques during the write process.

This dissertation makes three main contributions:

- We extend the lifetime of write-limited memories by modifying a coding technique used in digital communications to shape the signals input to a Gaussian channel. We apply this technique to memory composed of both Flash and PCM cells respectively.

- We develop enhancements to our method that extend lifetime and allow writes even when the stored value of a subset of the memory cells cannot be changed.

- We provide implementations of an encoder and a decoder of our coding technique for both PCM and Flash.

#### 1.3 Outline

This dissertation has five chapters including the introduction (Chapter 1). Chapter 2 provides background on the coding technique we use. Chapter 3 discusses how we extend the lifetime of memory locations composed of PCM cells using coding. Chapter 4 discusses how we extend the lifetime of memory locations composed of Flash cells using coding. Chapter 5 concludes the dissertation and provides insight into future research directions.

# 2. Coset Coding

This section introduces coset coding [18][19] and our use of it to create a technique to extend the lifetime of memory locations composed of PCM (Chapter 3) and Flash memory cells (Chapter 4). Current memory writing techniques have a one-to-one map between a given *dataword* (the data the host wants to write) and a given *codeword* (the data that is written). In contrast, coset coding has a one-to-many map between a dataword and a set of codewords. Each codeword in the set can be mapped back to the dataword. Coset coding enables the selection of a representative codeword to write from a number of possibilities. We use the flexibility of the coset coding technique to write many possible codewords to minimize wear on a given memory location.

Coset coding was first introduced in the context of communications [11][18][19] to reduce average transmitted signal power in voiceband modems. When used in voiceband modems, all vectors in a given coset represent the same information and the vector sent over the communication line is chosen to minimize signal power.

The following sections provide background information on the different mechanisms we used in our implementation of coset coding. Section 2.1 introduces coset coding terminology. Section 2.2 discusses the steps required to read and write to memory. Sections 2.3 and 2.4 discuss how we implemented the steps.

# 2.1 Coset Code Terminology

We use the following coset coding terminology throughout our discussion. Coset coding is based on the creation of *cosets*—sets with special properties we use to represent a single dataword

with multiple codewords. A codeword inside a coset that represents the coset is a *coset* representative. Encoding is the process of mapping from a dataword to the corresponding coset label (the coset representative that has a one-to-one mapping with the dataword). Decoding is the process of mapping from a coset representative back to the corresponding dataword. Encoding occurs during the write process, and decoding occurs during the read process.

# 2.2 Coset Coding Encoding and Decoding Steps

This section presents the steps we used in our coset coding technique to encode using coset coding for writing codewords to memory and to decode using coset coding for reading codewords from memory. We implemented coset codes both without error correction (for PCM) and with error correction (for Flash). Section 2.2.1 discusses the process for encoding. This process is the same for coset coding both with and without error correction. Section 2.2.2 discusses the processes for decoding both with and without error correction, respectively.

### 2.2.1 Encoding Steps

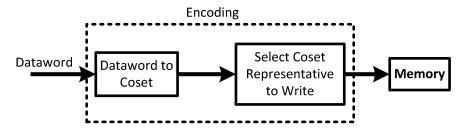

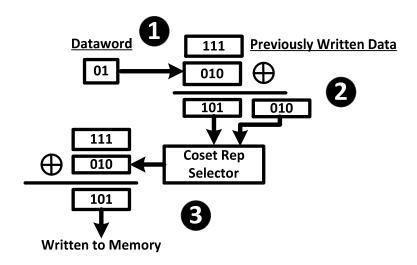

The coset coding encode process consists of mapping from a dataword to the coset representative that, when written, has the least impact on memory location lifetime. The coset coding encode process consists of the two steps as illustrated in Figure 1. The first step is mapping from a dataword to a coset. The second step is selecting the coset representative to write. A coset contains multiple write options all of which represent the original dataword. After encoding, we write the selected coset representative to memory. We present our implementation of step 1 and step 2, respectively, in Sections 2.3 and 2.4.

**Figure 1: Coset Code Encoding Process**

# 2.2.2 Decoding Steps

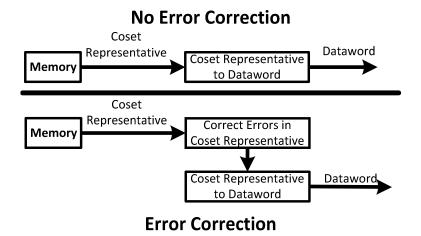

Figure 2 shows the coset code decoding process. The top of the figure shows how we decode coset codes without error correction (a single step process). The bottom of the figure shows how we decode coset codes with error correction (a two-step process). To decode, we map from the read-out coset representative back to the corresponding dataword by correcting any errors in the coset representative and then mapping back to the corresponding dataword.

Figure 2: Coset Coding Decoding Process Both Without (top) and With (bottom) Error Correction

### 2.3 Mapping Between Dataword and Coset

In this dissertation, we use matrices to map between datawords and cosets. We describe how we create coset coding matrices in general in Section 2.3.1 and how to construct coset coding matrices that can also perform error correction in Section 2.3.2.

#### 2.3.1 Coset Code Matrix Construction

Table 2 lists the three matrices we used and their function in the coset code encoding and decoding processes. We named each matrix based on the matrix's function. We first create the *Zero Coset Generator Matrix* (**Z**) that we used to generate the zero coset representatives (the zero coset is defined as the coset that maps to the all zero dataword [17]) (Section 2.3.1.1). From **Z**, we are able to create the *Decoder Matrix* (**H**), which is used to map from the read-out coset representative to the corresponding dataword, and the *Coset Label Generator Matrix* (**H**\*), which maps between the dataword and the coset label (Section 2.3.1.2).

Table 2: Matrices Used as Part of Our Coset Coding Encoding/Decoding Implementation

| Process Matrix is Used | Matrices                                 | Purpose                  |

|------------------------|------------------------------------------|--------------------------|

| Encoding               | Zero Coset Generator Matrix ( <b>Z</b> ) | To generate the zero     |

|                        |                                          | coset representatives    |

|                        | Coset Label Generator Matrix             | To map from the          |

|                        | (H <sup>#</sup> )                        | dataword to the coset    |

|                        |                                          | label                    |

|                        | Decoder Matrix ( <b>H</b> )              | To map from the read-    |

| Decoding               |                                          | out coset representative |

|                        |                                          | to the corresponding     |

|                        |                                          | dataword.                |

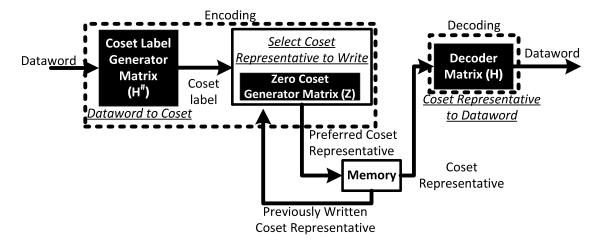

Figure 3 shows the location of each matrix in the encoding and decoding processes. Each step is labeled in italics and underlined, and each matrix is shown in white text on a black background.

Both the "Dataword to Coset" and "Coset Representative to Dataword" steps consist of the **H**<sup>#</sup> and **H** matrices, respectively; and the "Select Coset Representative to Write" step uses **Z**.

Figure 3: Coset Coding Encode and Decode Processes

#### 2.3.1.1 The Zero Coset Generator Matrix (Z)

In our experiments, we obtained the zero coset generator matrix (**Z**) from binary block and convolutional codes that have been shown to be well suited for coset coding [18]. All the other matrices in a given coset code (listed in Table 2) can be generated from the **Z** matrix. We evaluated coset coding for PCM using the Reed-Muller [52] and repetition binary block codes. We evaluated coset coding for Flash using convolutional codes [38].

We use the zero coset as part of our processes for searching for the best coset representative to write from the input dataword coset. We discuss how we use the zero coset with exhaustive search in Section 2.4.3 and with Viterbi search in Section 2.4.4.

#### 2.3.1.2 The Decoder Matrix (H) and Coset Label Generator Matrix (H\*)

We used **Z** to generate the decoder matrix (**H**). **H** maps from a coset representative back to a dataword as part of the decoding process. Generating **H** requires meeting the following conditions:

**Condition 1:**  $ZH^T = 0$ , where 0 is the matrix of all zeroes, and where "T" is the transpose operator [45]. This condition ensures that all coset representatives in a given coset will map back to the same dataword.

**Condition 2:** All rows of **H** must be linearly independent [75] over GF(2) [66]. For mathematical operations with coset codes, we use GF(2), a mathematical structure where values are calculated modulo 2. This condition ensures that all coset representatives multiplied by **H** will produce a unique dataword.

**Condition 3:**  $H^{\#}H = I$ , where "I" is the identity matrix [67]. This condition ensures that the dataword mapped to the coset representative during encoding is the same dataword that is recovered during decoding.

The process of creating **H** is specific to the code used. For example, we evaluated extending the lifetime of PCM using Reed-Muller codes as coset codes. We generated **H** for a Reed-Muller coding using the method presented in Lin and Costello Jr. [38] as this **H** generation method ensured meeting both conditions 1 and 2. For the repetition code, we decoded using the method presented in Cho et al. [14].

To create  $\mathbf{H}^{\#}$  and meet condition 3 for  $\mathbf{H}$  ( $\mathbf{H}^{\#}\mathbf{H} = \mathbf{I}$ ), we generated  $\mathbf{H}^{\#}$  from  $\mathbf{H}$  by taking the left pseudo-inverse [44] of  $\mathbf{H}$  over GF(2).

### 2.3.2 Error Correcting Coset Code (ECCC) Matrix Construction

The process we use for building ECCC matrices builds on the process used to create coset code matrices as discussed in Section 2.3.1. ECCC matrices are still used to perform coset coding but they produce coset reprsentatives that can be checked for errors. To check for errors, an ECCC

incorporates an error correcting code (ECC). Previously developed ECCs include Hamming codes [25].

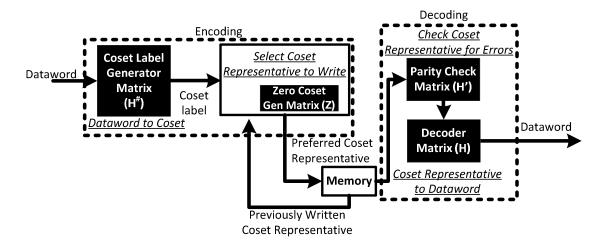

Figure 4 shows the ECCC encoding and decoding process. Each step in each respective process is labeled in italics and underlined. Each matrix is shown in white text on a black background. The ECCC encoding step is identical to the non-error correcting coset encoding process shown in Figure 3, where H<sup>#</sup> converts the dataword into a coset, and Z generates zero coset representatives that are used as part of the coset representative selection process (described in Section 2.4). We add a fourth *Parity Check Matrix* (H') in the decoding process to check a coset representative produced by an ECCC matrix for errors and to provide repair information. During decoding, H' checks the coset representative for errors, the decoder corrects as many errors as possible, and H converts the coset representative to the corresponding dataword.

**Figure 4: ECCC Encoding and Decoding Proceses**

ECCC matrices meet the requirements of both an ECC and a coset code. A single matrix can fit the requirements of multiple codes. Since both **Z** and **H**<sup>#</sup> the requirements of a coset code and of

an ECC, coset representatives generated from them are also ECC codewords that can be checked for errors. Section 2.3.2.1 discusses the requirements for the ECC matrices. Section 2.3.2.2 discusses how we created **Z**, **H**<sup>#</sup> and **H** so that they meet the requirements of both the ECC we used and the coset code we used.

#### 2.3.2.1 ECC Matrices

The ECCs we used are defined by three matrices: the generator matrix (**G**), the ECC Decoder Matrix (**G**\*), and the parity check matrix (**H**') [38]. Figure 5 shows how each matrix is used during the ECC encoding/decoding processes. The ECC encoding/decoding process differs from the ECCC encoding/decoding process (shown for illustrative purposes only in Figure 5). During the encoding process, **G** maps the dataword to the corresponding ECC codeword that is then written to memory. During the two-step decode process, the parity check matrix (**H**') checks the readout ECC codeword for errors, corrects them, and **G**\* is then used to convert the corrected ECC codeword back into the corresponding dataword.

Figure 5: Encoding/Decoding ECC

**Requirements for the Generator Matrix (G).** In Chapter 4, we use a Hamming code as our ECC. Creating a Hamming ECC **G** matrix requires that two conditions are met [42]:

**Condition 1.** All rows in G are linearly independent over GF(2).

**Condition 2.** All columns in **G** are different

Requirements for the ECC Decoder Matrix ( $G^*$ ).  $G^*$  is the pseudo-inverse of G over GF(2) [28].

Generating the Parity Check Matrix (H'). A Hamming parity check matrix H' requires that  $\mathbf{GH'}^T = \mathbf{0}$ , where "T" is the transpose operator [45]. We used a Hamming code for ECC in Chapter 4 and used the method presented in Lin and Costello Jr. [42] to generate H'.

# 2.3.2.2 Z (Zero Coset Generator Matrix), H# (Coset Generator Label Matrix), and H (Decoder Matrix) for Error Correction

This section presents our construction of the ECCC matrices that do not have an ECC. These matrices are **Z** (Zero Coset Generator Matrix), **H**<sup>#</sup> (Coset Generator Label Matrix), and **H** (Decoder Matrix).

Generating the Zero Coset Generator Matrix (Z) and the Coset Label Generator Matrix (H<sup>#</sup>).

G is the combination of Z and H<sup>#</sup>. If Z and H<sup>#</sup> combine to form G then all coset representatives are also ECC codewords. Combining Z and H<sup>#</sup> to form G requires meeting the following two conditions in addition to those listed in Section 2.3.2.1:

**Condition 1.** The number of columns in  $\mathbf{H}^{\#}$ ,  $\mathbf{Z}$  and  $\mathbf{G}$  must be the same. If the number of columns were different, then  $\mathbf{G}$ ,  $\mathbf{H}^{\#}$ , and  $\mathbf{Z}$  would produce different length codewords. For  $\mathbf{Z}$  to be within  $\mathbf{G}$ , the generated codeword length of both matrices and the number of columns of both matrices must be the same.

**Condition 2.** H# and Z vertically concatenated must form G.

In our experiments, we selected **Z** from a previously developed coset code that has requirements compatible with **G**. We used a **Z** where all columns differ to ensure that all columns in **G** differ (Since **Z** and **H**<sup>#</sup> are vertically concatenated, all of the columns in **G** by definition are different). We generated **H**<sup>#</sup> based on the requirements listed in Section 2.3.1.2 and the requirements for **G**. We made the number of columns in **H**<sup>#</sup> the same as **Z** to satisfy Condition 1 for **H**<sup>#</sup>. To satisfy condition 2, we randomly generated linearly independent rows for **H**<sup>#</sup> over GF(2) until **Z** and **H**<sup>#</sup> had sufficient rows to form **G**.

**Generating the Decoder Matrix (H).** Since coset representatives are also ECC codewords, the ECC Decoder Matrix (**G**<sup>#</sup>) is the same as **H**. To generate the decoder matrix **H**, we took the pseudo-inverse of **G** over GF(2) [44]. Since both **Z** and **H**<sup>#</sup> combine to form **G**, and **H**<sup>#</sup> produces a coset representative, then **H** as the pseudo-inverse of **G** produces the corresponding dataword.

ECCC matrices can be used solely for error correction as presented in Section 2.3.2.1. Figure 6 shows the ECC encode/decode processes using the ECCC matrices. The ECC matrix names are shown in black text and the ECCC matrices are shown in white text on a black background. The generator matrix **G** is composed of **H**<sup>#</sup> and **Z**. Any dataword multiplied by the combination of these two matrices produces a coset representative that is also an ECC codeword. **H'** is used to check the ECC codeword/coset representative for errors. Finally, **G**<sup>#</sup> (a.k.a **H)** is used to decode the ECC codeword/coset representative back into the corrected dataword.

Figure 6: ECC Encoding/Decoding Process with ECCC Matrices

## 2.4 Selecting a Coset Representative to Write from a Coset

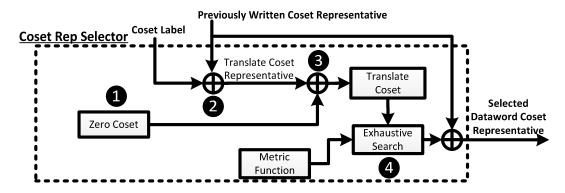

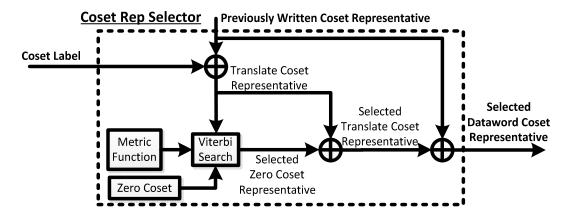

The coset rep selector selects a coset representative from a coset to write as part of the coset code encoding process. Figure 7 shows the location in the encoding process of the coset rep selector. Given a coset label and the previously written coset representative, the coset rep selector picks a coset representative from the *dataword coset*—the coset that represents the dataword—to write to memory.

Figure 7: Coset Rep Selector Highlighted in the Coset Coding Encoding/Decoding Process

The coset rep selector requires the following four pieces of information: 1) the zero coset, 2) the translate coset—a coset that provides information on how writing the given coset will change a the value in a given memory location (Section 2.4.1); 3) a metric function—a function that

provides a lexicographic ordering to a set (Section 2.4.2); and 4) a *search function*—an algorithm for applying a metric function (Section 2.4.3, exhaustive search and Section 2.4.4, the Viterbi algorithm). The search function determines how the coset rep selector uses each of the four components listed above to find a coset representative to write.

#### 2.4.1 Translate Coset

This section discusses the translate coset and its part in the coset code encoding process. A translate coset represents how writing a given coset will change the value in a given memory location. The coset representative to write.

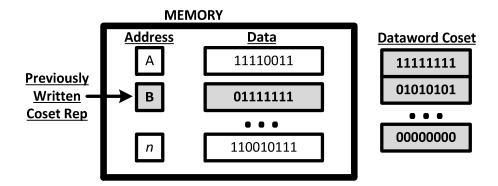

Figure 8 shows the different types of data needed to form a translate coset. Forming a given translate coset requires both the dataword coset and the previously written coset representative. The coset representatives in this example come from the extended Hamming (8,4) coset code (shown for illustrative purposes only in Figure 8). The three vectors in the memory box in the figure have been written to Flash memory in addresses "A", "B" and "C". The right side of the figure shows the dataword coset to be written.

Figure 8: Example Setup for Forming a Translate Coset

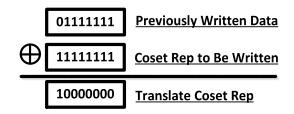

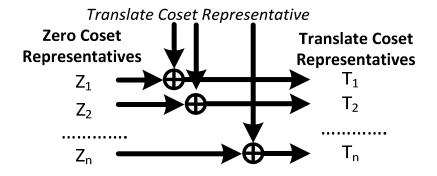

Creating a translate coset consists of XORing the coset representatives in the dataword coset with the previously written coset representative. Figure 9 shows the formation of a translate coset representative. The encoder XORs the previously written data (01111111) and a coset representative from the dataword coset (11111111) to produce the translate coset representative 10000000. For translate coset representatives, a "1" indicates a bit will be flipped during the write while a "0" indicates a bit will not be flipped. For example, writing the dataword coset representative corresponding to the translate coset representative 10000000 will flip the 1st bit from the left. Performing this operation for all of the dataword coset representatives forms the translate coset.

Figure 9: Formation of a Translate Coset Representative

#### 2.4.2 The Metric Function

A metric function assigns a single numerical value to a coset representative. These values are used to order representatives within a coset. An exemplary metric function is counting the number of 1s in a coset representative. For example, if we had the following coset representatives, {0000,0001,0010,0011}, applying this metric function results in metric values {0,1,1,2}. If we wanted to pick coset representatives with the lowest metric value to write, we would pick 0000 because it has metric value 0. Other metric functions have been proposed in prior work [16].

#### 2.4.3 Exhaustive Search

Exhaustive search consists of *enumerating*—finding all of the elements in a given set—each coset and then choosing the best coset representative. Figure 10 shows the four steps in an exhaustive search-based coset rep selector which are also listed below:

- 1. Enumerating the zero coset;

- 2. Finding a translate coset representative;

- 3. Enumerating the translate coset; and

- 4. Using a metric function to select a coset representative.

Figure 10: Exhaustive Search-Based Coset Rep Selector

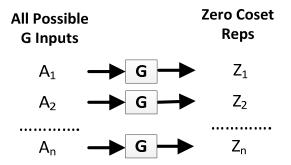

**Step 1: Enumerate the Zero Coset (Figure 11).** We first enumerate the coset representatives in the zero coset. To obtain the zero coset, we multiply all possible inputs by **G.** The results of these multiplications are the zero coset representatives.

Figure 11: Enumerating the Zero Coset

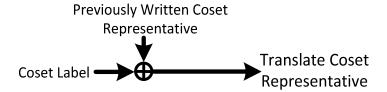

**Step 2: Find a Translate Coset Representative (Figure 12).** We find coset representative in the translate coset by XORing the coset label and the previously written data.

Figure 12: Finding a Translate Coset Representative

**Step 3: Enumerate the Translate Coset (Figure 13).** We enumerate the translate coset using the dataword coset by XORing the coset representatives in the zero coset with a translate coset representative. This process produces all the translate coset representatives.

**Figure 13: Enumerating the Translate Coset**

**Step 4: Use a Metric Function to Select a Coset Representative.** We use a metric function on the translate coset to find the coset representative to write in the dataword coset. Exhaustive search applies the metric function to translate coset representatives to generate a corresponding metric value for each representative. These metrics are then used to select a translate coset representative.

#### 2.4.4 The Viterbi Algorithm

As an alternative to exhaustive search, we can design the coset rep selector using the Viterbi algorithm (Viterbi) [20]. Viterbi is well suited for searching cosets with a large number of coset representatives such as with the codes presented in Chapter 4. For large coset sizes, Viterbi requires less power and less area than exhaustive search. For small coset sizes, exhaustive search may be preferable due to its lower base overheads.

Figure 14 shows how we can use Viterbi as part of the coset rep selector. Inputs and outputs are shown in bold, and components that are built into the coset rep selector are shown with white boxes with black text. The two inputs to the coset rep selector are used to form the translate coset representative. The metric function, translate coset representative, and zero coset are fed

into the Viterbi algorithm which produces a zero coset representative. To convert back to a dataword coset representative the zero coset representative is first XORed with the translate coset representative and then XORed with the previously written coset representative to produce the selected dataword coset representative.

Figure 14: Viterbi-Based Coset Rep Selector

Viterbi has two conditions that exhaustive search does not have. The metric function for Viterbi must produce non-negative numbers and the zero coset must be representable as a finite state machine (FSM). These conditions allow Viterbi to use dynamic programming to calculate the path metrics inductively. We designed our metric functions when using Viterbi so that the produced metric values are non-negative. Both binary convolutional codes and binary block codes [38] have a zero coset that can be represented as an FSM.

# 3. Extending the Lifetime of Phase Change Memory

This chapter presents our application of coset coding to extend the lifetime of memory locations composed of PCM cells. We apply the coset coding technique presented in Chapter 2 to extend PCM memory lifetime by flipping fewer bits per write compared to writing un-coded datawords. Flipping fewer bits results in writing less and thus extends lifetime of PCM memory.

Section 3.1 provides background on PCM. Section 3.2 discusses the PCM failure modes. Section 3.3 discusses other work on extending the lifetime PCM. Sections 3.4 and 3.5 introduce *FlipMin*, our proposed application of coset coding to extend the lifetime of memory locations composed of PCM cells, and provides an evaluation of how well FlipMin reduces the number of bit flips per write. Section 3.6 presents exemplary hardware implementations of a FlipMin encoder and decoder. Section 3.7 presents the area, energy, and latency costs from using our hardware implementations of a FlipMin encoder and decoder. Sections 3.8 and 3.9 discuss how we setup our experiments and present the results of our evaluation of FlipMin for both random and program inputs. Section 3.10 concludes the chapter.

This chapter makes the following contributions:

- Shows how to use coset coding to extend the lifetime of PCM memory by minimizing bit flips per write,

- Presents a method for synergistically combining FlipMin with the ability to tolerate erasures,

- Presents and evaluates exemplary hardware implementations of both a FlipMin encoder and decoder, and

- Presents an evaluation of how well FlipMin extends the lifetime of memory locations composed of PCM cells for both random and program inputs.

# 3.1 Background

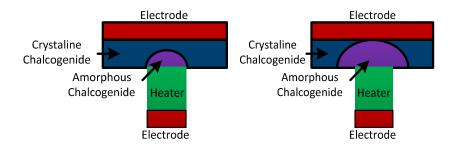

PCM is an emerging memory technology that is poised to either replace or complement Flash memory in computing systems. PCM has faster program/erase times than Flash as well as greater endurance. A PCM cell has three parts: an electrode on top that is used to sense the cell level; the PCM chalcogenide material that changes state; and a heater to change the state of the material. A PCM cell stores a single bit using two states, each of which has a different resistance.

A PCM cell has a low-resistance and a high resistance state. Figure 15 depicts both resistance states of a given PCM cell. The left side of the figure shows the low-resistance state of a PCM cell and the right side of the figure shows the high-resistance state of a PCM cell. To write a PCM cell, a heater melts part of the chalcogenide material and cools it at a given rate. A current is then passed through the cell to read the resistance value. When cooled at a fast rate, the chalcogenide turns amorphous and has a high resistance. When cooled at a slower rate, the chalcogenide turns crystalline and has a low resistance. When the resistance of a PCM cell is low (i.e., the chalcogenide is mostly crystalline), one bit value is read out; when the resistance of a PCM cell is high (i.e., the chalcogenide is mostly amorphous), the other bit value is read out.

Figure 15: PCM Cell in Low and High Resistance States

Although PCM holds promise as an emerging non-volatile storage technology, it is a *write limited memory,* i.e., repeatedly writing to PCM cell eventually results in the cell unable to change state.

### 3.2 Failure Modes

PCM cells have been shown to exhibit two different failure modes [60] due to repeated writes: the observed failure modes are stuck in low resistance (i.e., closed) and stuck in high resistance (i.e., open). A PCM stuck-at closed failure is due to elemental segregation in the chalcogenide material. A PCM stuck-at open failure is due to voids between the chalcogenide material and the electrode. A PCM cell that cannot change resistances cannot change value and is referred to as a "stuck-at" cell. A stuck-at PCM cell can be read but cannot be written.

Stuck-at closed and stuck-at open PCM failure modes result from repeated cycling between states. A PCM cell can change state a fixed number of times before failing. We extend the lifetime of the memory location by reducing the number of PCM cells that change states per write compared to writing un-coded data directly.

#### 3.3 Related Work

We group existing schemes for extending the lifetime of memory locations composed of PCM cell into four categories. We list prior schemes in Table 3; shaded schemes in the table represent those that we will not quantitatively compare against in this chapter. With respect to the non-shaded schemes in the table, Section 3.3.1 discusses schemes that use bit flip reduction (BFR). Section 3.3.2 discusses schemes that use error correction based techniques. Section 3.3.3 discusses the technique of adding additional memory cells. Section 3.3.4 discusses wear-leveling techniques.

Table 3: PCM lifetime extension schemes. We quantitatively compare to un-shaded rows.

| Approach            | Scheme                  | Instantiation      | Granularity      | Overhead       | Why No Quant.<br>Comparison |

|---------------------|-------------------------|--------------------|------------------|----------------|-----------------------------|

| bit flip reduction  | Flip-N-Write (FnW) [16] | FnW per-byte       | 8 bits           | 1 bit=12.5%    |                             |

|                     |                         | FnW per-word       | 64 bits          | 1 bit=1.56%    | subsumed by FnW<br>per-byte |

|                     | Coset Coding            | discussed in paper | 64 bits          | tunable        |                             |

| error/erasure       | ECC                     | Hamming (72,64)    | 64 bits          | 8 bits=12.5%   |                             |

| Correction          | ECP [60]                | ECP <sub>6</sub>   | block ~ 512 bits | 61 bits=11.9%  |                             |

|                     |                         | ECP <sub>12</sub>  | block ~ 512 bits | 121 bits=23.6% |                             |

|                     |                         | ECP-ideal          | block ~ 512 bits | 0              |                             |

|                     | Pay-As-You-Go [55]      |                    | entire memory    | tunable        | subsumed by ECP-<br>ideal   |

|                     | SAFER [62]              | SAFER8             | block ~ 512 bits | 22 bits=4%     | subsumed by ECP-<br>ideal   |

|                     |                         | SAFER32            | block ~ 512 bits | 55 bits=10.7%  | subsumed by ECP-<br>ideal   |

|                     | RDIS [46]               | RDIS3              | block ~ 512 bits | see †          | subsumed by ECP-<br>ideal   |

|                     | FREE-P [71]             |                    | block ~ 512 bits | 64 bits=12.5%  | requires OS support         |

|                     | DRM [31]                |                    | page ~4KB        | see ‡          | requires OS support         |

| adding memory cells | DoubleMem               |                    | 64 bits          | 64 bits*=100%  |                             |

<sup>†</sup> Overhead is listed as 18%, but RDIS does not account for overheads to track erasures.

## 3.3.1 Postponing Wear-out: BFR

One can extend the lifetime of memory locations composed of PCM cells by writing a codeword that flips fewer bits per write compared to writing an un-coded dataword. All else being equal, flipping fewer bits when writing to a memory location results in that location lasting for a greater number of writes. To the best of our knowledge, the only prior work in this area is Flip-N-Write [14]. At each write, Flip-N-Write chooses to write either the dataword or its inverse, depending on which requires fewer bit flips. Flip-N-Write adds a single bit per location to indicate whether the data is inverted or not. Flip-N-Write is coset coding with the repetition code with a metric function that minimizes bit flips. In this dissertation, we explore the repetition code and other coset codes for reducing the number of bit flips per write to postpone wear-out of a memory location composed of PCM cells.

<sup>‡ 12.5%</sup> to track erasures plus 100% for paired pages plus a single 1KB "ready table"

<sup>\*</sup> Actual overhead is greater than 64 bits due to extra state bits to track which copy of the location is being used.

A non-coding method for minimizing bit flips is to combine multiple writes in a buffer composed of memory that is not write-limited [37] before writing to a memory location composed of PCM cells. Write coalescing is a useful technique that is orthogonal to all prior work and to our work.

## 3.3.2 Tolerating Wear-out: Error Correction

One can extend the lifetime of memory locations composed of PCM cells by tolerating bit errors after wear-out occurs. Tolerating wear-out is effective when a minority of memory cells at some location granularity (e.g., byte, line, etc.) fail far earlier than average making the entire location unusable. Example schemes include ECC and some techniques developed for PCM [27][40][49][56][63]. One prominent scheme is Error Correcting Pointers (ECP) [54]. The ECP scheme tolerates errors in known bit positions (i.e., *erasures*) in memory locations by maintaining pointers to these bit positions and adding bits to be used as replacements. For example, ECP<sub>6</sub> operates at a 512-bit location granularity, and it keeps six 9-bit pointers (log<sub>2</sub>(512) = 9) and 6 replacement bits for tolerating up to 6 erasures in the 512-bit location. There has been a large amount of work that extends and optimizes ECP, including Pay-As-You-Go [49], SAFER [56], and RDIS [40]. We both compare to and combine our coset coding based scheme with ECP with the intent of extending the lifetime of memory locations composed of PCM cells.

# 3.3.3 Adding Memory Cells

One can extend the lifetime of memory locations composed of PCM cells by adding more memory cells and using these memory cells for purposes of extending memory location lifetime rather than increasing memory capacity. For example, if a memory location is logically 64-bits, we can use 128 physical bits in a scheme we call DoubleMem. With DoubleMem, initially the

first 64 bits of the physical location are used to store data. When the first 64-bit physical location fails, the second 64-bit physical location is used to store data. There has been research into more sophisticated methods for adding memory cells to improve lifetime, including Waterfall codes and hypercells [36], but they all share the same idea. These techniques are complementary to our work.

### 3.3.4 Wear-leveling

One can extend the lifetime of memory locations composed of PCM cells by evenly wearing memory cells in a memory module. There are two kinds of wear-leveling: intra-location wear-leveling and inter-location wear-leveling. *Intra*-location wear-level schemes level out the wear in a given location uniformly (e.g., by remapping logical bit positions) [33][64]). These schemes require state to track the current bit position mappings for each location and sophisticated heuristics to decide when and how to remap bit positions. *Inter*-location wear leveling schemes seek to avoid writing to some locations more frequently than others. These schemes [33][50][51][55][64] avoid these situations by dynamically mapping from logical locations to physical locations in ways that are similar to but simpler than virtual memory translations from virtual pages to physical pages. This work is complementary to our work.

# 3.4 FlipMin

This section presents *FlipMin*, our coset coding based technique for extending the lifetime of memory locations composed of PCM cells. FlipMin extends the lifetime of memory locations composed of PCM cells by writing coset representatives that flip fewer bits than writing datawords directly. Section 3.4.1 discusses our assumptions when developing FlipMin for PCM. Section 3.4.2 discusses how FlipMin selects a coset representative to write to a memory

location. Section 3.4.3 discusses how to use FlipMin to write to memory locations with stuck-at PCM cells.

### 3.4.1 System Model Assumptions

We assumed when designing FlipMin for PCM cells that we can 1) write both transitions 0-to-1 and 1-to-0 with equal cost (a formal model for this is known as the Write Efficient Memory (WEM) model [3]), and 2) read a memory location before writing to it (a requirement of using the translate coset method for determining which coset representative to write as discussed in Section 2.4.1). Both these assumptions about PCM have been made in prior work [9][14].

## 3.4.2 FlipMin Coset Representative Selection

The coset representative selection process begins with the dataword and ends with the coset representative that is written to memory. Section 3.4.2.1 lists each of the steps and provides a description of the actions taken during each step. Section 3.4.2.2 presents an example of FlipMin coset representative selection using a repetition coset code.

#### 3.4.2.1 Steps

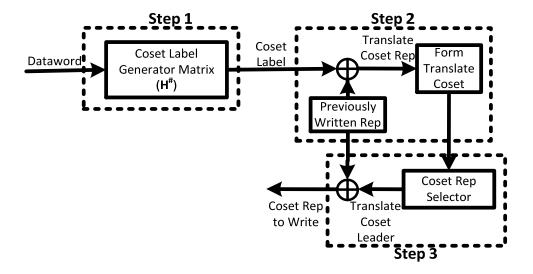

In this section we present three steps, illustrated in Figure 16 and described below, that describe how FlipMin selects a coset representative to write that maximizes BFR.

**Step 1: Generate the Coset Label.** The coset label (defined in Section 2.1) uniquely identifies the coset corresponding to the dataword. The dataword is multiplied by **H**<sup>#</sup> (defined in Section 2.3.1.2) to generate the coset label.

**Step 2: Generate the Translate Coset.** FlipMin selects a coset representative to write based on information from the translate coset (discussed in Section 2.4.1). A translate coset

representative is first generated by XORing the previously written coset representative and the coset label. The entire translate coset is then enumerated using the zero coset. The coset representatives in the translate coset indicate which cells will flip when writing each coset representative in the dataword coset.

Step 3: Generate the Coset Representative that is Written to Memory. To generate the coset representative that will be written to memory, the translate *coset leader*—the coset representative with the fewest number of 1s—is determined using exhaustive search (described in Section 2.4.3). We then use the translate coset leader to find the coset representative that will flip the fewest number of bits and XOR the translate coset leader with the previously written coset representative to produce a coset representative in the dataword coset. When written, this coset representative will flip the fewest number of bits of all the coset representatives in the dataword coset.

Figure 16: Selecting the Preferred Coset Rep to Write Using FlipMin

Whether or not writing a coset representative using FlipMin results in a BFR depends on the coset code that is used. We use the FlipMin metric function with coset codes that have coset representatives in each coset with an equal or lower weight than the corresponding un-coded dataword. Selecting coset representative to write using FlipMin from one of these coset code results in a bit flip reduction when compared to writing the un-coded dataword directly.

### **3.4.2.2 Example**

In this section, we provide an example illustrating the FlipMin coset representative selection process using the repetition code shown in Table 4. This repetition code has two coset representatives per dataword. For example, the coset representatives for 01 are 010 and 101.

Table 4: 2-Bit to 3-Bit Repetition Coset Code

| Dataword | Coset Representative 1 | Coset Representative 2 |

|----------|------------------------|------------------------|

| 00       | 000                    | 111                    |

| 01       | 010                    | 101                    |

| 10       | 100                    | 011                    |

| 11       | 110                    | 001                    |

Figure 17 shows each of the three steps to FlipMin coset representative selection using a repetition code. For this example, the previously written data is 111 and the dataword is 01. Step 1 consists of converting from the dataword (01) to the coset label (010). For the repetition code, we simply append a "0". In Step 2, the coset label (010) is converted into a translate coset representative (101) by XORing it with the previously written data (111). The other translate coset representative (010) in the translate coset is then generated by flipping all of the bits in the first translate coset representative (101). In Step 3, the translate coset representative with

the fewest number of 1s (010) is selected by the coset rep selector and XORed with the previously written data (111) to produce the coset representative to write to memory (101).

Figure 17: FlipMin Coset Representative Selection Process with the Repetition Coset Code in Table 4

## 3.4.3 Coset Erasure Matching (CEM)

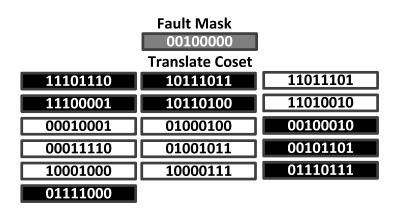

In addition to reducing bit flips, FlipMin tolerates stuck-at cells, i.e., FlipMin allows for writes to a PCM memory location with stuck-at cells; we call the FlipMin process to write to memory locations with stuck-at memory cells *coset erasure matching* (CEM). CEM tolerates stuck-at PCM cells by selecting a coset representative to write that matches the values of the stuck-at PCM cells in a given memory location. CEM first reads out a *fault mask* (a vector that indicating which bits are stuck-at) that corresponds to a given memory location and then uses the memory location fault mask to determine which bits cannot change when selecting a coset representative to write.

The following example as illustrated in Figure 18 demonstrates the CEM write process when one or more stuck-at PCM cells are present in a memory location. The figure contains an example translate coset along with a *fault mask*, defined as a vector where a "1" indicates a memory cell that cannot be changed. The fault mask here has a "1" in the third position from the left so this memory cell cannot change value during a write. The translate coset for this code is shown on the figure below the fault mask vector with the values in black with white text indicating translate coset representatives that cannot be written and values in white with black text indicating translate coset representatives that can be written. In the figure, for example, the coset representative 11101110 cannot be written because it would flip the third bit, while the coset representative 00010001 can be written since it would not flip the third bit. Even though a bit value cannot be changed, a valid coset representative can still be written when using CEM.

Figure 18: Coset Erasure Matching Example

# 3.5 FlipMin BFR Evaluation

We ran experiments to measure bit-flip reduction properties of coset codes with FlipMin. We analyzed FlipMin with the following coset codes: Parity(72,64) (equivalent to a previously developed scheme known as Flip-N-Write [14]), two Reed-Muller [52] codes FM-RM(1,3), and a

truncated version of RM(1,7) (FM-RM(1,7)T). For each coset code, we used the dual of the code listed (i.e., FM-RM(1,3) is the dual of RM(1,3)). Section 3.5.1 presents our methodology for determining the BFR of each code, and Section 3.5.2 presents our results.

## 3.5.1 Methodology

To simulate the average BFR, we used an in-house numerical tool that writes to a 64B cache line. We ran simulations for each of the three coset codes until the BFR converged to a constant value, and calculated the BFR for each coset code with FlipMin using the following equation:

$$BFR = 1 - \frac{\text{\# Bit Flips in FlipMin}}{\text{\# Bit Flips in Uncoded}}$$

#### **3.5.2** Results

We found that for our simulations the BFR of FM-RM(1,3) and FM-RM(1,7)T is higher than that of FM-Parity(72,64). Table 5 presents the BFR for FM-Parity(72,64), FM-RM(1,3), and FM-RM(1,7)T. We found that the BFR for FM-RM(1,3), FM-RM(1,7)T, and FM-Parity(72,64) codes is 31.2%, 24.5%, and 15.8%, respectively.

**Table 5: Bit Flip Reduction**

| Coset Code       | Bit Flip Reduction |

|------------------|--------------------|

| FM-Parity(72,64) | 15.8%              |

| FM-RM(1,7)T      | 24.5%              |

| FM-RM(1,3)       | 31.2%              |

The BFR of FM-RM(1,3) is higher than that of FM-RM(1,7)T because of the *covering radius*—the maximum number of bits a vector can be different from the coset representatives in the zero coset. The smaller the covering radius for a given codeword length, the larger the BFR [7][10].

Shorter Reed-Muller codes have a smaller covering radius than longer Reed-Muller codes. Since shorter Reed-Muller codes have a smaller covering radius, they have a higher BFR than longer Reed-Muller codes. The smaller covering radius of FM-RM(1,3) results in a 31.2% BFR as compared to 24.5% for FM-RM(1,7)T.

## 3.6 Implementation

We preset an exemplary hardware implementation of a FlipMin encoder and decoder that consists of an encoder for translating from input to coset representative and a decoder for translating from a coset representative back to a dataword. Section 3.6.1 describes the system model and where FlipMin can be implemented in a computer memory hierarchy; Section 3.6.2 presents a hardware implementation of a FlipMin encoder; and Section 3.6.3 presents a hardware implementation of a FlipMin decoder.

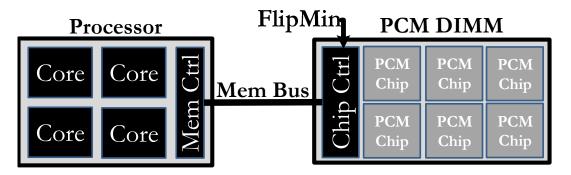

## 3.6.1 System Model

A hardware implementation of FlipMin can be integrated into any of the existing hardware units on a PCM daughter board. Ideally, any implementation of FlipMin is physically located as close to the PCM cells as possible since FlipMin requires a read before a write. Figure 19 shows one location a hardware implementation of FlipMin can be integrated into an existing computer memory system. In this figure, PCM is attached to a processor as its main memory in the form of a DIMM (possibly similar to [4]) that has PCM chips on both sides of a daughter board. If a chip were present to coordinate activities between the PCM chips and provide inter-location wear-leveling as illustrated by "Chip Ctrl" in Figure 19, a hardware implementation of FlipMin could be integrated into this chip; alternatively, we could integrate FlipMin into the write controller located inside the PCM chips.

Figure 19: Example PCM Implementation that Integrates FlipMin into PCM Chips

### 3.6.2 Encoder

This section presents the hardware for a FlipMin encoder. First, we list the different encoding steps. Then, for each step, we present our hardware implementation.

#### The Encoding Steps for our Hardware Implementation of FlipMin:

- 1. Generate the coset label (defined previously in Section 2.5.2.1 as a coset representative inside a coset that uniquely identifies the coset) from a dataword

- 2. Generate a translate coset representative

- 3. Generate the translate coset

- 4. Find the minimum weight element in the translate coset

- 5. Compute the coset representative to write from the minimum weight element in the translate coset.

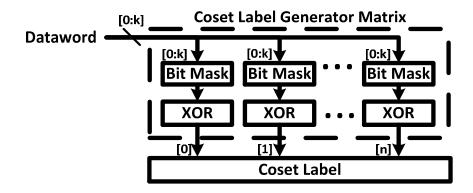

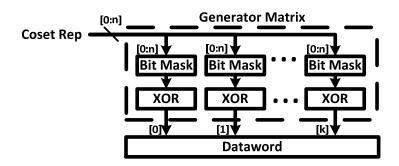

Step 1: Generate a coset label from a dataword (Figure 20). To generate the coset label from a dataword, we multiply the dataword by  $\mathbf{H}^{\#}$  (defined in Section 2.3.1.2) over GF(2). Figure 20 depicts a hardware block diagram for implementing GF(2) matrix multiplication. We define the dataword to be k bits long and we define the coset label to be n bits long. Since we are doing a

matrix multiply over GF(2), we do not use the standard addition and multiplication operations; rather, we add using XOR gates and multiply using AND gates.

Figure 20: Hardware Block Diagram for Coset Label Generation

Two hardware units are used per column to perform matrix multiply over GF(2): a unit for the multiplication and a unit for the addition. The multiplication unit consists of a *bit mask*—a unit that selects bits from a given coset representative. The bits selected correspond to the 1s in the corresponding column of the coset representative generator matrix. For example, if the matrix column has the value 101, only the first and final bits of the input dataword would be selected. The addition unit consists of a k bit XOR gate. The different bits selected by the bit mask are XORed together to produce a bit in the coset label. The bits from the different columns are concatenated to form the coset label.

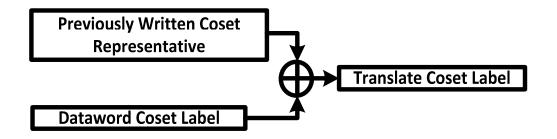

**Step 2: Generate the translate coset label (Figure 21)**. Generating the translate coset label consists of a single XOR operation between the previously written data and the data to write.

Figure 21: Generating the Translate Coset Label

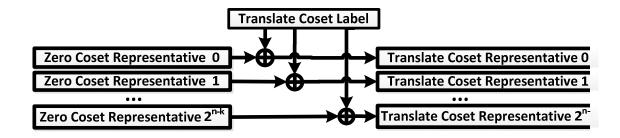

**Step 3: Generate the translate coset (Figure 22).** To obtain the translate coset, we XOR the translate coset label with the zero coset stored in a ROM. Generating the translate coset requires a single XOR operation per coset representative in the coset. The resulting vectors are the coset representatives of the translate coset.

**Figure 22: Generating the Translate Coset**

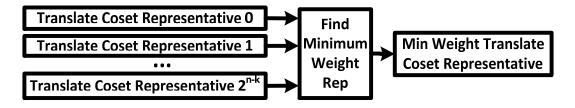

Step 4: Find the minimum weight translate coset representative (Figure 23). To find the translate coset representative with the fewest 1s, we input all coset representatives in the translate coset into the "Find Minimum Weight Rep" module. We implemented the "Find Minimum Weight Rep" module using the implementation of exhaustive search described in Section 2.4.3.

Figure 23: Coset Metric Calculation and Selection Logic

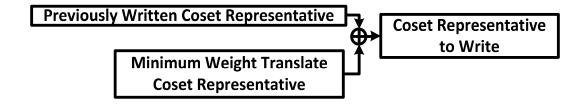

Step 5: Compute the coset representative to write from the minimum weight translate coset representative (Figure 24). The final step is finding and writing the coset representative in the original coset corresponding to the selected translate coset representative. We XOR the translate coset representative with the previously written data to produce the coset representative in the original coset. This coset representative is then written to the memory location.

Figure 24: Determining the Coset Rep to Write from the Translate Coset Leader and Previously Written Coset Representative

#### 3.6.3 Decoder

Decoding FlipMin consists of a GF(2) matrix multiply. An example decoder hardware implementation is depicted in Figure 25. The process for the GF(2) matrix multiply is the same as in Figure 20 except that the generator matrix of the code is used, the input is of length *n*, and

the output is of length k. The output of this matrix multiply is the dataword that was originally encoded using FlipMIn.

Figure 25. Hardware Block Diagram for Decoding

### 3.7 Hardware Costs

We determined the costs of using our exemplary hardware implementations of the FlipMin encoder and decoder for a set of coset codes. We compared the costs of our FlipMin encoder and decoder hardware designs to a PCM chip data sheet [41]. The PCM chip in this data sheet has 16-bit I/O width, so we multiplied the area and power costs from the data sheet by 4. Section 3.7.1 lists the different coset codes for which we designed FlipMin encoders and decoders; Section 3.7.2 presents the process we used to determine costs; Section 3.7.3 presents the costs of the encoder; and Section 3.7.4 presents the costs of the decoder.

#### 3.7.1 Coset Codes Evaluated

We evaluated the hardware implementation of FlipMin example encoders and decoders for a set of Reed-Muller codes [52] and a parity code. Other codes could be used as well provided that the code divides up a space into cosets. Table 6 lists the duals of the different Reed-Muller

and parity codes used for FlipMin for which we designed encoders and decoders. When we refer to these codes, we will be referring to the dual.

We designed our coset coding encoder and decoder to be the size of a standard word in a computing system (64-bits). For codes that accept inputs smaller than 64-bits, we divide the dataword into sub-vectors and encode each sub-vector independently. The coset codes we implemented a hardware encoder and a hardware decoder for are listed in Table 6. For the FM-Parity(72,64) and the FM-RM(1,7)T (truncated RM(1,7)) coset code, 1.125x PCM cells are required to store data compared to un-coded datawords written directly. For the FM-RM(1,3) coset code, 2x PCM cells are required to store data compared to writing un-coded datawords directly.

**Table 6: FlipMin with Different Block Codes**

| Coset Code       | Storage Overhead      | Comments                      |

|------------------|-----------------------|-------------------------------|

|                  | (per 64-bit Dataword) |                               |

| FM-Parity(72,64) | 8/64=0.125x           | Performed on 8-bit sub-vector |

| FM-RM(1,7)T      | 8/64=0.125x           |                               |

| FM-RM(1,3)       | 64/64=1x              | Performed on 4-bit sub-vector |

### 3.7.2 Process Used to Evaluate Hardware Costs

We used tools from the Synopsys suite of programs to determine the costs of our exemplary hardware implementations of a FlipMin encoder and decoder. First, we used Synopsys Design Compiler (DC) to synthesize from RTL to a gate-level netlist using gates from the Nangate 45nm semi-custom library [46]. Second, we used Synopsys VCS with 1,000 randomly generated inputs to determine the switching activity factor for the wires in the design. Third, we used Synopsys IC

to layout and floor plan the design. Finally, we used Synopsys Design Compiler topological mode to determine the area, latency, and energy costs.

#### 3.7.3 Encoder Costs

We found the cost of adding a FlipMin encoder to a PCM chip to be negligible. Table 7 lists the simulation latency, energy, and area costs for our implementations of FlipMin encoders for the codes listed in Table 6. According to our PCM datasheet [41], the write time for our PCM chip is 60-120us. The maximum delay for encoding using the RM coset codes is 12.86ns, or 0.021% of the PCM chip write latency. The worst case energy consumption for the encoder is 63.4 pJ. The typical idle current of 4 PCM devices is about 320 $\mu$ A and the minimum rail voltage is 1.7V, so the minimum idle power is approximately 544 $\mu$ W. If a block is encoded every 60 $\mu$ S, our largest encoder would take 1.06 $\mu$ W which represents 0.19% of the idle power of the PCM chip. The worst case area cost for encoding is 48,344  $\mu$ m², which we believe to be negligible given the typical size of a PCM chip and a DIMM.

**Table 7: Coset Coding Encoder Costs**

| Coset Code       | Delay (ns) | Avg Energy (pJ) | Max Energy (pJ) | Area (μm²) |

|------------------|------------|-----------------|-----------------|------------|

| FM-RM(1,3)       | 4.09       | 8.4             | 10.1            | 1,160      |

| FM-RM(1,7)T      | 12.86      | 56.1            | 63.4            | 48,344     |

| FM-Parity(72,64) | 0.84       | 0.4             | 0.6             | 503        |

### 3.7.4 Decoder Costs