Scalably Verifiable Cache Coherence

by

Meng Zhang

Department of Electrical and Computer Engineering Duke University

Date:\_\_\_\_

Approved:

Daniel J. Sorin, Supervisor

Chris Dwyer

Alvin R. Lebeck

Benjamin C. Lee

Bruce M. Maggs

Dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical and Computer Engineering in the Graduate School of Duke University

2013

#### ABSTRACT

Scalably Verifiable Cache Coherence

by

Meng Zhang

Department of Electrical and Computer Engineering Duke University

Date:\_\_\_\_\_

Approved:

Daniel J. Sorin, Supervisor

Chris Dwyer

Alvin R. Lebeck

Benjamin C. Lee

Bruce M. Maggs

An abstract of a dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical and Computer Engineering in the Graduate School of Duke University

2013

Copyright by Meng Zhang 2013

## Abstract

The correctness of a cache coherence protocol is crucial to the system since a subtle bug in the protocol may lead to disastrous consequences. However, the verification of a cache coherence protocol is never an easy task due to the complexity of the protocol. Moreover, as more and more cores are compressed into a single chip, there is an urge for the cache coherence protocol to have higher performance, lower power consumption, and less storage overhead. People perform various optimizations to meet these goals, which unfortunately, further exacerbate the verification problem. The current situation is that there are no efficient and universal methods for verifying a realistic cache coherence protocol for a many-core system.

We, as architects, believe that we can alleviate the verification problem by changing the traditional design paradigm. We suggest taking verifiability as a first-class design constraint, just as we do with other traditional metrics, such as performance, power consumption, and area overhead. To do this, we need to incorporate verification effort in the early design stage of a cache coherence protocol and make wise design decisions regarding the verifiability. Such a protocol will be amenable to verification and easier to be verified in a later stage. Specifically, we propose two methods in this thesis for designing scalably verifiable cache coherence protocols. The first method is Fractal Coherence, targeting verifiable hierarchical protocols. Fractal Coherence leverages the fractal idea to design a cache coherence protocol. The self-similarity of the fractal enables the inductive verification of the protocol. Such a verification process is independent of the number of nodes and thus is scalable. We also design example protocols to show that Fractal Coherence protocols can attain comparable performance compared to a traditional snooping or directory protocol.

As a system scales hierarchically, Fractal Coherence can perfectly solve the verification problem of the implemented cache coherence protocol. However, Fractal Coherence cannot help if the system scales horizontally. Therefore, we propose the second method, PVCoherence, targeting verifiable flat protocols. PVCoherence is based on parametric verification, a widely used method for verifying the coherence of a flat protocol with infinite number of nodes. PVCoherence captures the fundamental requirements and limitations of parametric verification and proposes a set of guidelines for designing cache coherence protocols that are compatible with parametric verification. As long as designers follow these guidelines, their protocols can be easily verified.

We further show that Fractal Coherence and PVCoherence can also facilitate the verification of memory consistency, another extremely challenging problem. One piece of previous work proves that the verification of memory consistency can be decomposed into three steps. The most complex and non-scalable step is the verification of the cache coherence protocol. If we design the protocol following the design methodology of Fractal Coherence or PVCoherence, we can easily verify the cache coherence protocol and overcome the biggest obstacle in the verification of memory consistency.

As system expands and cache coherence protocols get more complex, the verification problem of the protocol becomes more prominent. We believe it is time to reconsider the traditional design flow in which verification is totally separated from the design stage. We show that by incorporating the verifiability in the early design stage and designing protocols to be scalably verifiable in the first place, we can greatly reduce the burden of verification. Meanwhile, we perform various experiments and show that we do not lose benefits in performance as well as in other metrics when we obtain the correctness guarantee.

# Dedication

To my parents.

# Contents

| Abstract                                                   | iv   |

|------------------------------------------------------------|------|

| List of Tables                                             | xii  |

| List of Figures                                            | xiii |

| Acknowledgements                                           | XV   |

| 1. Introduction                                            | 1    |

| 1.1 Cache Coherence in Many-core Era                       | 2    |

| 1.2 Verification Problem of Cache Coherence Protocols      | 4    |

| 1.3 Incorporating Verification into Cache Coherence Design | 6    |

| 1.4 Thesis Statement and Contributions                     | 8    |

| 1.5 Thesis Outline                                         | 10   |

| 2. Background and Related Work                             | 12   |

| 2.1 Verification Definition and Approaches                 | 12   |

| 2.1.1 Verification through Simulation                      | 13   |

| 2.1.2 Verification through Formal Methods                  | 13   |

| 2.1.2.1 Model Checking                                     | 14   |

| 2.1.2.2 Theorem Proving                                    | 16   |

| 2.1.3.3 Combining Model Checking and Theorem Proving       | 17   |

| 2.2 Design Space of Cache Coherence Protocols              |      |

| 2.3 Status and Challenges of Cache Coherence Verification  | 21   |

| 2.3.1 Verification of Flat Cache Coherence Protocols       | 22   |

| 2.3.2 Verification of Hierarchical Cache Coherence Protocols  |    |

|---------------------------------------------------------------|----|

| 2.4 Designing Verifiable Cache Coherence Protocols            | 27 |

| 2.4.1 Related Work in Design for Verifiability                |    |

| 2.4.2 Verifiability Analysis of Cache Coherence Protocols     |    |

| 3. Fractal Coherence: Verifiable Hierarchical Cache Coherence |    |

| 3.1 Concept of Fractal Coherence                              |    |

| 3.2 System Architecture                                       |    |

| 3.3 Verification Methodology                                  | 35 |

| 3.3.1 Verification of Minimum System                          | 35 |

| 3.3.2 Verification of Fractal Behavior                        |    |

| 3.3.3 Proof of Cache Coherence for Arbitrary N-node System    |    |

| 3.4 Case Study: TreeFractal                                   |    |

| 3.4.1 System Design                                           |    |

| 3.4.1.1 Two-node System Design                                |    |

| 3.4.1.2 Scaled System Design                                  |    |

| 3.4.2 Verification Procedure and Results                      | 51 |

| 3.4.2.1 Verification of Minimum System                        |    |

| 3.4.2.2 Equivalence Checking of Fractal Behavior              |    |

| 3.4.3 Evaluation                                              |    |

| 3.4.3.1 Storage Overhead                                      | 54 |

| 3.4.3.2 Simulation Methodology                                |    |

| 3.4.3.3 Performance Results and Analysis                      |    |

| 3.5 Fractal Directory: Extension of TreeFractal                 | 62  |

|-----------------------------------------------------------------|-----|

| 3.5.1 Insufficiency of TreeFractal                              | 63  |

| 3.5.2 System Design of Fractal Directory                        | 63  |

| 3.5.3 Performance Evaluation                                    | 65  |

| 3.5.4 Difficulty in Verification Process                        | 66  |

| 3.5.4.1 State Explosion Problem in Verification                 | 68  |

| 3.5.4.2 Reducing State Space by Optimizing Verification Process | 68  |

| 3.5.4.3 Demanding for a Verifiable Flat Protocol                | 73  |

| 3.6 Design Space of Fractal Coherence                           | 74  |

| 3.7 Summary                                                     | 76  |

| 4. PVCoherence: Verifiable Flat Cache Coherence                 | 77  |

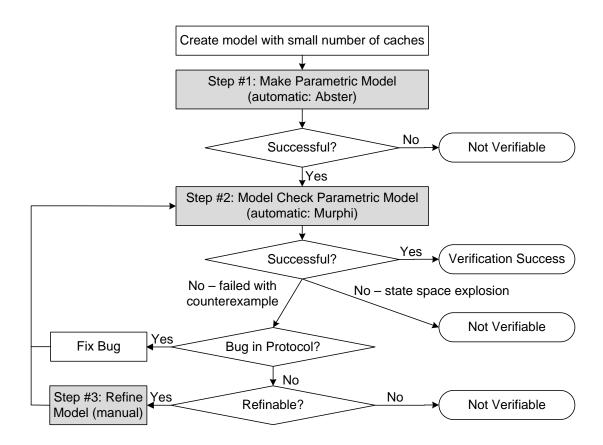

| 4.1 Parametric Verification for Cache Coherence                 | 78  |

| 4.1.1 Different Approaches to Parametric Verification           | 78  |

| 4.1.2 A Mostly Automated Method: Simple-PV                      | 79  |

| 4.2 Limitation of Simple-PV                                     | 84  |

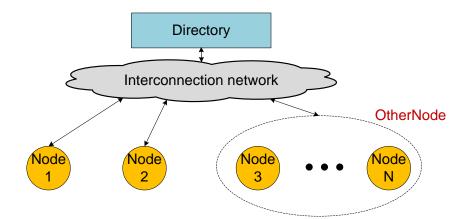

| 4.3 System Overview of PVCoherence                              |     |

| 4.4 Design Guidelines for PVCoherence Protocols                 |     |

| 4.5 Case Study: PV-MOESI                                        | 99  |

| 4.5.1 An Optimized Protocol: OP-MOESI                           | 99  |

| 4.5.2 Converting OP-MOESI to PV-MOESI                           | 100 |

| 4.5.3 Verification of PV-MOESI                                  | 104 |

| 4.5.4 Evaluation                                                | 106 |

|      | 4.5.4.1 Methodology and System Configuration                                 | 106 |

|------|------------------------------------------------------------------------------|-----|

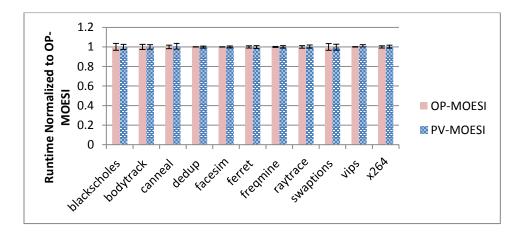

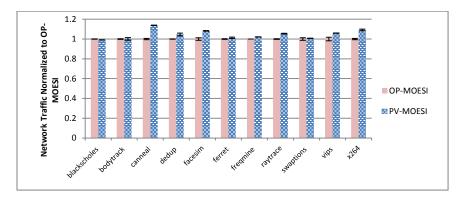

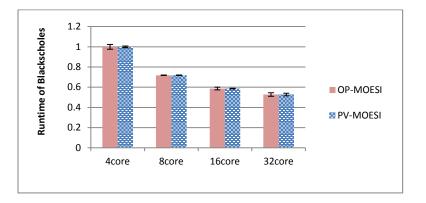

|      | 4.5.4.2 Performance Results                                                  | 107 |

|      | 4.5.4.3 Scalability Analysis                                                 | 109 |

|      | 4.5.4.4 Storage Overhead                                                     | 109 |

|      | 4.6 Combining Fractal Coherence and PVCoherence                              | 111 |

|      | 4.7 Summary                                                                  | 113 |

| 5. I | Leveraging Fractal Coherence and PVCoherence to Verify Memory Consistency    | 115 |

|      | 5.1 Difference between Cache Coherence and Memory Consistency                | 116 |

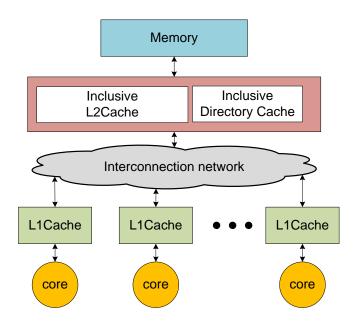

|      | 5.2 Decomposing the Verification of Memory Consistency                       | 117 |

|      | 5.3 Architecting Memory System to Facilitate the Verification of Consistency | 119 |

| 6. 0 | Conclusions and Future Work                                                  | 124 |

| Ref  | ferences                                                                     | 128 |

| Bio  | ography                                                                      | 137 |

# List of Tables

| Table 1: System configuration of TreeFractal and baselines                                                                                                                   | .59 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2: System configuration of Fractal Directory and baseline                                                                                                              | .67 |

| Table 3: High-level specifications of OP-MOESI and PV-MOESI. Ignores transient states. Differences between OP-MOESI and PV-MOESI are in bold font in PV-MOESI specification. |     |

| Table 4: Simulation Configurations of PV-MOESI and OP-MOESI                                                                                                                  | 107 |

| Table 5: TSO ordering                                                                                                                                                        | 121 |

# List of Figures

| Figure 1: Scalability problem in verification of cache coherence         | 32 |

|--------------------------------------------------------------------------|----|

| Figure 2: Possible binary tree structures                                | 34 |

| Figure 3: Minimum systems of different degree trees                      | 34 |

| Figure 4: Observational equivalence for maintaining fractal behavior     |    |

| Figure 5: Lemmas for proof of cache coherence in any N-node system       | 43 |

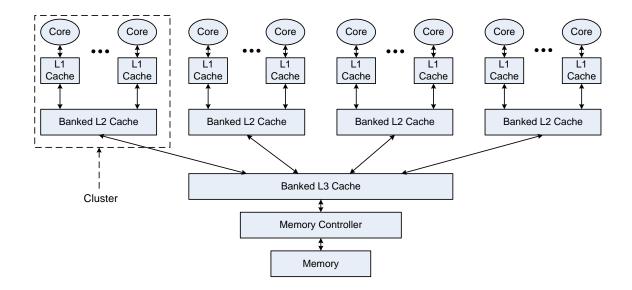

| Figure 6: System architecture of TreeFractal                             | 47 |

| Figure 7: An example of naïve design which violates the fractal behavior | 48 |

| Figure 8: Correct implementation to ensure fractal behavior              | 50 |

| Figure 9: Optimized observational equivalence checking                   | 55 |

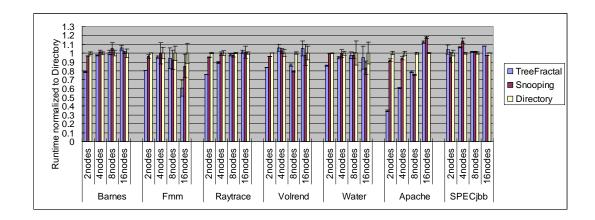

| Figure 10: Runtime normalized to Directory                               | 62 |

| Figure 11: Runtime of on-chip caching protocols normalized to Directory  | 62 |

| Figure 12: System structure of Fractal Directory                         | 65 |

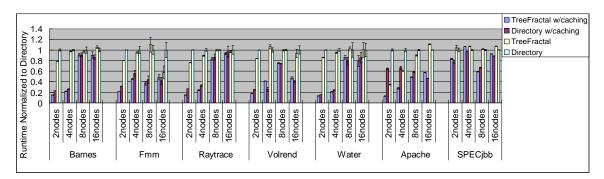

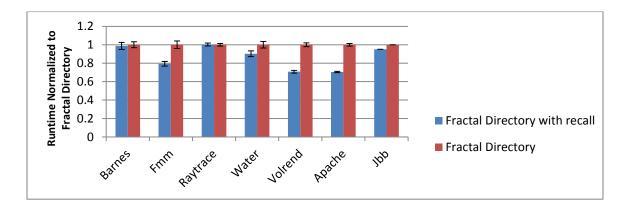

| Figure 13: Runtime of Fractal Directory                                  | 67 |

| Figure 14: Speedup with "Recall"                                         | 68 |

| Figure 15: Minimum system of Fractal Directory                           | 69 |

| Figure 16: Observtional equivalence checking of Fractal Directory        | 69 |

| Figure 17: Reduce the state space for verification                       | 74 |

| Figure 18: Making a traditional Snooping protocol fractal                | 75 |

| Figure 19: Simple-PV Verification Process                                | 80 |

| Figure 20: Parametric Model                                              | 81 |

| Figure 21: System Architecture of PVcoherence       | 87  |

|-----------------------------------------------------|-----|

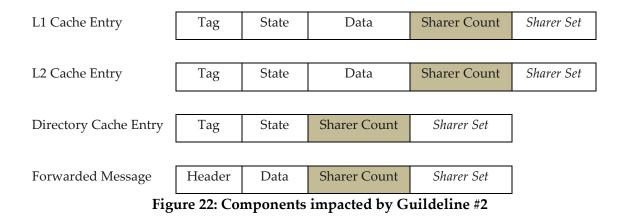

| Figure 22: Components impacted by Guildeline #2     | 90  |

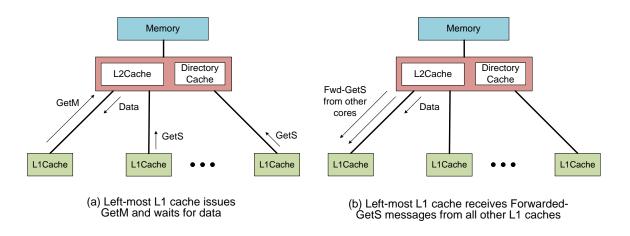

| Figure 23: Scenario #2 forbidden by Guideline #3    | 92  |

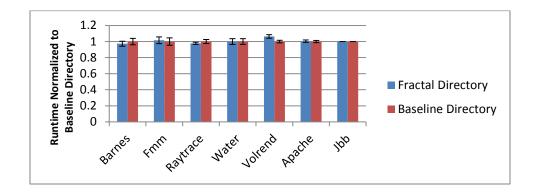

| Figure 24: Runtime comparison: OP-MOESI vs PV-MOESI | 110 |

| Figure 25: Network traffic overhead of PV-MOESI     | 110 |

| Figure 26: Performance Scalability                  | 110 |

| Figure 27: Architecture for shared-memory system    | 121 |

## Acknowledgements

I have received substantial help from my mentors, colleagues and families throughout my PhD study at Duke. I would like to express my great gratitude towards them. Without their supports, it is impossible for me to complete the studies and be able to write this thesis.

First of all, I would like to thank my advisor, Daniel Sorin, one of the greatest mentors I have ever seen. Dan not only introduces me into this field, supervises me on my research work, but also impacts me on my life attitude with his personality. Through numerous discussions with him, I learnt how to think deeply and creatively, how to improve communication and writing skills, how to manage time and balance life. As I overcome the difficulties during my studies, Dan has been always patient with me and influences me with his passion and determination. I will continue to emulate his example in my career. I am also grateful to Prof. Alvin Lebeck, who collaborates with us on two of our papers. His extensive experience and insightful thoughts are valuable to our work, helping bring them to the public. I would also like to thank all other committee members, Prof. Chris Dwyer, Prof. Ben Lee, and Prof. Bruce Maggs for taking their time to serve on my committee, and also for the feedback they have provided.

I am very fortunate to be in the Duke computer architecture group. It includes a lot of talented and interesting people, who contribute to the pleasure and freedom atmosphere. Particularly, I would like to thank a few individuals among them. Bogdan Romanescu helped me speed and complete my very first project at Duke. He also gave me useful suggestions on PhD life and career plan. Anita Lungu not only worked with me on my first paper, but also being a good friend to talk and share feelings. It is a pleasure to sit next to Blake Hechtman, who is always energetic and enthusiastic with research. Blake gave me useful feedback on my work and helped me a lot in solving the infrastructure problems. There are still many other peers in this group that have helped me and made my graduate life easier: Fred Bower, Vince Mao, Adam Jacobvitz, and Ralph Nathan.

Finally, my greatest gratitude goes to my husband, Dongtao and my son, Grayson. The life of a PhD student can be tough and dull, but they have lightened it up. I would like to thank Dongtao for cheering me up every time I was in low spirit and discussing with me every time I raise a question. He is continuously supporting and caring for me. My little boy, who cannot speak yet, gives me big smiles every day, encouraging me to pursue the study even in the most difficult time. I also want to thank my mom, who left her hometown and stay with us helping take care of Grayson. If it were not her help, I would not be able to complete this thesis in time. I am forever indebted to them.

## 1. Introduction

Single-core systems have given way to multi-core systems, or more accurately, many-core systems, which may have hundreds or even thousands of cores on a single chip. To better utilize the underlying hardware resources, parallel programming is becoming ubiquitous. However, it is extremely challenging, even for experts, to develop correct and efficient parallel programs. A shared memory is an effective way to alleviate the burden of parallel programming, since it provides the programmer with the view of a single memory address space, which greatly reduces the need of explicit data partitioning and movement. In a shared-memory many-core system, all cores have access to the entire memory locations. The communications among different cores are via the read and write operations to the shared memory.

However, together with the benefit for parallel programming, the sharedmemory paradigm also brings several problems, an important one among which is cache coherence. Cache coherence problem occurs when there are one or multiple levels of caches sitting between the cores and the memory. Each core has its private cache and may or may not share caches with other cores. Such cache hierarchies greatly reduce memory accesses and improve performance, but cause multiple copies of the same block to exist in the system. Data inconsistency may happen in these copies, either between the cache and the memory, or among the caches themselves. Both scenarios can lead to a read being unable to retrieve the updated value of the latest write. A read of a stale value can ruin the correctness of the program. Therefore, we must ensure that all writes are correctly propagated in a timely fashion and data of the same block have a consistent view across all copies. To achieve this goal, we need a mechanism to coordinate the behaviors of all the caches as well as the cores and the memory. Such a mechanism is called a cache coherence protocol. In particular, we confine our discussion to hardware cache coherence, which is implemented in most of today's computer systems. Software cache coherence is beyond the scope of this thesis.

### 1.1 Cache Coherence in Many-core Era

In a cache coherence protocol, every participating component (cores, caches, and memory) is described as a state machine, and the protocol itself is a compound state machine with all these components interacting with each other. Cache coherence protocols may have quite different features according to various system requirements. No matter what specific design choices it has made, a cache coherence protocol must satisfy two invariants to ensure correctness. The first one is permission invariant. It says that the protocol must enforce the so-called single-writer, multiple-reader (SWMR) invariant [89]. SWMR means for each block of memory, at any given time, the block either has a single writer or zero or more readers. The second one is data invariant, which states that the protocol must ensure that a read of a block returns the value of the most recent write to that block. Although cache coherence protocols may have quite different implementations, as long as the protocol can be verified to satisfy these two invariants, we are ensured that the protocol does not have a bug.

As a key factor in the overall cost and performance, cache coherence has been under extensive research for a long period and achieved great improvement. Now, with the advent of many-core era, the design of cache coherence protocols meets a new challenge: scalability. The ever expanding system requires the cache coherence protocol to scale in all different aspects. The first aspect is performance. Most previous optimizations for a cache coherence protocol have performance gain as the ultimate goal. It is a question, though, whether the performance enhancement can still be maintained as the system scales, as we know that some optimizations are naturally not scalable. Secondly, the storage overhead and power consumption of a cache coherence protocol also need to be taken into consideration for scalability. Nowadays, a single chip, which only has a limited area and power budget, may integrate a variety of functional units. So we would like to minimize the resources allocated to the cache coherence protocol. Finally, as the components in the system increase, the utilization of the interconnection network increases. It is important that the cache coherence protocol only consumes a modest bandwidth and does not lead to a burst or congestion in the network.

To satisfy the above requirements in scalability, people have designed highly aggressive cache coherence protocols with a variety of optimization techniques for current cache hierarchies, which may include one or multiple levels of caches. However, there is an important aspect that is usually overlooked, that is, whether we are able to verify the designed scalable cache coherence protocol is correct in the first place.

#### **1.2 Verification Problem of Cache Coherence Protocols**

A buggy cache coherence protocol might lead to a catastrophic failure of the shared-memory system that employs this protocol. It is quite important to carefully design and inspect the protocol. However, the carefulness is insufficient to ensure the correctness of a modern cache coherence protocol. To ensure the reliability of the protocol, verification must be done as part of implementing cache coherence protocols for real systems. This type of verification is actually "*design verification*", which occurs before the product is manufactured. Whenever we mention "verification" in the thesis, we are referring "design verification".

There are two major approaches to performing the verification of a cache coherence protocol: simulation and formal verification. Simulation is to run benchmarks, stress tests, and random code sequences and check the output to see whether the cache coherence protocol is correct. Formal verification, on the contrary, mathematically proves that the cache coherence protocol satisfies the correctness properties. The main difference between the two methods is that simulation only explores certain path of the state space, while formal verification explores the whole reachable state space.

Simulation or formal verification may work for very simple or unrealistic cache coherence protocols, but both of them have difficulty in verifying modern cache coherence protocols implemented in today's computer systems. As the size and complexity of a cache coherence protocol increase, simulation may only cover a small percentage of paths no matter how long it runs. This inability to reach all system states limits the ability of simulation methods to find subtle bugs. Previous work [19], [26], [33], [86] shows cache coherence protocols can still have bugs even after extensive simulations. Therefore, recent research has been focusing on formal verification of cache coherence protocols, which is a complete method. Formal verification also has its unavoidable problems. The most prominent problem is formal verification fundamentally requires a huge amount of resources, either in the form of memory, runtime or human efforts, which exceeds the capability that current formal verification tools could provide. As the system scales, the requirement also goes up. The increasing complexity of cache coherence protocols further exacerbates the problem. To achieve high performance, current cache coherence protocols allow multiple outstanding requests and concurrent operations. This concurrency implies numerous transient states and a much bigger state space. Moreover, there is a trend towards hierarchical cache

coherence protocols. Several levels of protocols interacting with each other further complicates the verification [23].

To allow people to determine the correctness of the designed cache coherence protocol, the verification of the cache coherence protocol, just as all the other aspects, like performance, power consumption, etc., also needs to scale as the system expands and gets more complex. Unfortunately, few people have ever considered the scalability of verification and we would like to explore this area in this thesis.

### 1.3 Incorporating Verification into Cache Coherence Design

In a traditional design process, verification is performed at a late stage where most design choices have already been made. It is the verification team's responsibility to try their best to get the verification work done. However, it is acknowledged that verification consumes a large amount of resources during the whole process, increasing both the cost and the time to market. For example, when verifying the Pentium 4 processor, Bob Bentley and Rand Gray formed a large team and spent several years performing the verification [4]. It has been estimated that about 60-70 percent of the development cost of a system is spent on verification [1], [46]. Even with such a great effort consumed, verification still cannot fulfill all its responsibilities on many occasions. Considering this fact, the traditional design paradigm may not be optimal. Taking the cache coherence protocol design as an example, there is a tension between performance and verification difficulty. Architects make great efforts to improve the performance of the protocol, which often leads to increasing amounts of parallelism and larger state space that needs to be explored. The increased parallelism and state space make the verification of protocols more difficult. In the traditional design flow, priority is given to the architects and they focus only on the performance. They are allowed to do any optimizations they want to achieve that goal. Then the cache coherence protocol is passed to the verification team, who are responsible for trying out various techniques to prove the correctness of the protocol. Unfortunately, the cache coherence protocol is usually too complex for a complete proof. The verification team thus has to either verify a scaled down system, which does not necessarily guarantee the correctness of a larger system, or employ some incomplete methods (e.g., simulation) to get the verification done. Neither of these methods is satisfying.

However, the above dilemma does not necessarily need to be the case. If the designers have more information about what features the verification people would prefer and what they would like to avoid, they may have made wiser design choices. This information is particularly helpful when the intuition of the architect to design the system is not the same as what happens later in the verification stage. For example, a specific feature that improves the performance only a tiny bit may actually lead to a

disaster for the verification team, or a feature the architect discards considering it not useful may significantly ease the verification. We would like to avoid both of these situations.

We propose to incorporate verifiability of the cache coherence protocol into the early design stage instead of considering it late. This idea follows the concept of "design for verifiability" presented by Milne [74], which is a counterpart to the "design for testability" in the formal verification area. We expect that taking formal verification effort as a first-class design constraint has the potential to ease verification effort, improve product quality, and reduce a product's time to market.

#### 1.4 Thesis Statement and Contributions

In summary, we make the following contributions:

- 1. We propose to incorporate verification into the design stage of cache coherence protocols in order to ease verification. Specifically, we suggest to tradeoff between verifiability and other design aspect, such as performance, power consumption, etc., so that the system is scalably verifiable.

- 2. We propose Fractal Coherence: a design methodology for hierarchical protocols based on fractal theory. Fractal Coherence ensures each scale of the system has the same behavior with regard to coherence. Then the verification of cache coherence for the minimum system can be scaled to

larger systems. We show that through straightforward verification with existing tools, any arbitrary scale of system can be proved cache coherent. We implement a specific Fractal Coherence protocol, TreeFractal, and present the verification process for any arbitrary N-node system with this protocol. We experimentally evaluate TreeFractal using full system simulation and show it has comparable performance to traditional cache coherence protocols without adding significant implementation costs.

3. We propose PVCoherence which provides a set of design guidelines for flat cache coherence protocols design. Following these guidelines, architects can design flat cache coherence protocols that can be parametrically verified with any number of nodes. We describe the design process of a PVCoherence protocol, called PV-MOESI, that can be verified with model checking tools and limited human intervention for any arbitrary number of nodes. We experimentally compare the performance, network traffic, scalability, and storage overhead of PV-MOESI and a highly optimized protocol, OP-MOESI, that cannot be verified with Simple-PV. The results show that following the guidelines we present does not seriously impact the protocol's performance or costs.

4. We extend the idea of scalably verifiable cache coherence to the domain of memory consistency verification. We show that using a scalably verifiable cache coherence protocol in the system can ease the verification of memory consistency model implementation.

## 1.5 Thesis Outline

In the following parts of the thesis, Chapter 2 provides some background knowledge about verification and the approaches to performing verification. It also discusses the basic concept of cache coherence protocols, current status of cache coherence verification and the related work in the field of design for verification. Chapter 4 through Chapter 6 describe the major three contributions of the thesis. Chapter 3 discusses Fractal Coherence, a method to design a cache coherence protocol in a fractal way so that the self-similarity enables the protocol to be inductively verified independent of the number of nodes. It also provides the design process of specific Fractal Coherence protocols. Any protocol from the family of Fractal Coherence must have a hierarchical structure. Chapter 4 proposes PVCoherence to design a flat protocol which can be scalably verified and describes how to convert a common protocol to a PVCoherence protocol. PVCoherence is a complement of Fractal Coherence. Chapter 5 extends the discussion to the verification of memory consistency and talks about how

Fractal Coherence and PVCoherence can facilitate the verification of memory consistency. Chapter 6 concludes the paper and proposes some future work.

# 2. Background and Related Work

This chapter provides some background knowledge of verification and describes related work in the verification of cache coherence protocols. We first introduce the concept of verification and different approaches of verification (Section 2.1). After that, we provide an overview of cache coherence protocols design space (Section 2.2). Then we describe the related work in the verification of cache coherence protocols and point out the existing problem and difficulty in these verification techniques (Section 2.3). Finally, we illustrate the motivation for the proposal of designing a verifiable cache coherence protocol and talk about previous work in design for verification as well as in verifiability analysis of cache coherence protocols (Section 2.4).

### 2.1 Verification Definition and Approaches

Verification is the process of checking whether the developed system meets a set of specifications. Verification process, on the contrary to design process, starts from the implementation of the system and ends up in confirming the implementation complies with the specification. During this process, we may find design bugs which we must fix. There are two main approaches to performing verification: simulation-based verification and formal verification. The following sub-sections discuss the pros and cons of them in more detail. Particularly, since this thesis focuses on formal verification, the majority of this section will discuss formal verification.

#### 2.1.1 Verification through Simulation

Simulation-based verification is to run the simulator as many cycles as possible to uncover design bugs. The inputs to the simulator are a variety of test cases, which can be either manually generated test vectors or pseudo-random inputs. From the methodology point of view, simulation may apply to any system no matter how big it is since we can designate how many resources can be allocated to the simulator and control for how long the simulation will run. However, the main disadvantage of simulation is it is usually incomplete. We can verify only those cases that are encountered during the simulation. As the design complexity increases, the ratio of the test cases over the overall problem state space declines. The lower the coverage, the less we can trust the simulation.

#### 2.1.2 Verification through Formal Methods

Another important approach is formal verification, which mathematically proves that a design satisfies a set of properties. Both the design (an implementation) and the properties (a specification) are formally specified. The most important advantage of formal verification is that it is a complete method. Formal verification is able to find corner cases that might be missed in simulation. Completeness is quite important for current designs since they have become so complex and it is extremely difficult to pinpoint where the corner cases might be and how to manifest them through simulation. Formal verification also has disadvantages compared to simulation, depending on which formal verification method is used. There are two main methods of formal verification: model checking and theorem proving. The following sub-sections discuss the two methods in more detail.

#### 2.1.2.1 Model Checking

Model checking is a state-based method. It exhaustively examines the entire reachable state space of the system to check whether the desired properties hold. A typical model checking process includes three tasks: modeling, specification and verification [8]. Modeling is formally describing the system in a finite state machine description language; specification is formally specifying certain properties that the system must satisfy. We need to be careful that the specification exactly describes what we want from the system. Verification is then performed by a model checker that traverses all the reachable states and checks whether the model satisfies the specification. If the model checker finds a verification failure, then a counterexample will be generated.

The most prominent advantage of model checking over theorem proving is model checking is amenable to use. First, model checking is highly automated. A model checker can perform an automatic search procedure to determine whether the specification holds in all states without any human intervention. Second, model checking facilitates the debugging process. As mentioned earlier, in face of a failure, a model checker will provide a counterexample, which is a sequence of states that leads to a violation of the specification. The counterexample gives useful information to the user to debug the system and find design errors.

However, model checking is limited by the state explosion problem. Since model checking employs an exhaustive state space traversal method, the resources used in the process, such as memory and runtime, will eventually become a bottleneck [3]. The traditional way to perform model checking is through explicit state enumeration, which explicitly stores the states in the table. To overcome the inefficiency and large memory requirement in the explicit state enumeration of model checking, there have been a number of proposals to compress the state space [47], [79], [93]. A notable one of them is symbolic algorithm [18], [68], which uses ordered binary decision diagrams (OBDDs) [17] to represent the transition relationship. An OBDD representation of the state graph is much more compact than the explicit state enumeration. However, none of these methods can fundamentally solve the state explosion problem; instead, they only defer the advent of the explosion. Generally speaking, current designs are usually too complex for model checking to thoroughly verify. What people often do is to abstract the model or reduce the scale of the system in order to formally verify it, which cannot guarantee

the correctness of the original system. Due to the state space explosion problem, model checking fails to provide a general solution for realistic systems.

#### 2.1.2.2 Theorem Proving

Different from model checking, theorem proving is a proof-based method. It derives a proof from the desired properties to show that the system adheres to these properties. In theorem proving, a system is modeled in a more expressive way than in model checking, using higher-order logic or set theory. Then, a human-driven interactive correctness proof is performed. The verification process in theorem proving can be modularized and structured into layers. In this way, the proof is reduced to a series of sub-proofs to facilitate verification [43].

Theorem proving's superiority over model checking lies in its ability to deal with much more complex systems. It can employ a variety of techniques like structural induction to prove an infinite state system [27]. Moreover, some properties that are hard to describe in model checking can be easily described in theorem proving due to its high expressiveness.

The main problem with theorem proving is that it demands a significant human input to define and guide the proofs, meaning a great deal of expertise and time is needed [31]. This also means the verification process is prone to errors caused by human intervention. Another major disadvantage is that if the theorem prover fails to prove the correctness of the system, we cannot obtain any information about why and how the failure happens. Not being able to provide counterexample makes it rather inconvenient to debug in theorem proving.

#### 2.1.3.3 Combining Model Checking and Theorem Proving

We have described the two mainstream methods of formal verification, model checking and theorem proving. We can see they have strength and weakness in different aspects. Model checking is superior in its automaticity and amenability, while theorem proving is superior in its applicability and capability. With model checking, we can more easily and quickly verify a system, but current model checking tools saturate even when verifying a very small system. With theorem proving, we can verify more complex and larger systems, but the process of performing the verification is laborious and limited to very few experts.

Since both model checking and theorem proving have their own pros and cons, there are a few methodologies proposed to combine the two methods in a certain way. The goal is to enable the verification of complex systems in a more automatic fashion, and thus achieve the advantages of both worlds. There are two major approaches to combine model checking and theorem proving. The first approach is to add theorem proving techniques to model checkers [7], [66]. This approach enables model checkers to analyze large or even infinite state space by using techniques such as data abstraction, assume-guarantee reasoning, etc. The second approach is to implement model checking algorithms in theorem provers [16], [29]. In the theorem proving process, if a subset of the problem can be translated into a finite state model checking problem, we can leverage the power of model checking algorithm to verify it. The details of these methods are beyond the scope of this thesis. We will only discuss a specific combinational method related to our research later in Section 4.

### 2.2 Design Space of Cache Coherence Protocols

The development of cache coherence protocol dates back to 1980s. We will not describe the history of cache coherence; instead, we provide an overview of the design space of current cache coherence protocols. The following aspects are among the most important design choices.

**Protocol type**. It is an important decision to choose the type of protocol we will use. Usually we have two options: snooping protocol and directory protocol. Snooping protocols usually rely on a bus to provide ordering for all coherence transactions. Requests that arrive at the bus will be broadcast to all the cores in the same order. Each core then snoops to see if it has a copy the data and responds accordingly. Snooping protocols are widely implemented in earlier small-scale machines because they are simple [34], [39], [40], [49], [81]. However, the broadcasting feature causes the major limitation for a snooping protocol to scale to large scale systems. Directory protocols, on the other hand, avoid broadcasting and have better scalability, making it more popular in modern systems [3], [9], [56], [57], [77]. Directory protocols use a directory to record the state of each memory block. With this extra information, the protocol replaces the broadcasting with point to point messages. There are various methods to implement the directory. The most straightforward one is a fullmap directory [57] which tracks the states of all memory blocks in every cache. However, due to the huge storage overhead, it is not commonly used in current computer systems. There have been a great number of optimization techniques proposed to reduce the size of the directory [20], [21], [78], [87].

States and transactions. A cache coherence protocol usually has several stable states and a few transient states. The stable states usually include M(odified), O(wned), E(xclusive), S(hared), I(nvalid). M means only this cache has a valid copy of the data, and the data in the memory is stale. S means the cache has a valid copy of the data and the data in the memory is also up-to-date. There can be other caches that also hold a valid copy of the data. I means the cache has no valid copy of data for this block. O and E are for optimization purpose. O enables a cache to respond to a read request without copying back the data to the memory. In this case, there can be multiple valid copies in caches, while the memory does not have an up-to-date copy. E allows a cache to upgrade to state M without asking for the permission. A cache in E state means the cache and the memory both have valid copies of data, but no other cache has a valid copy of data.

In order to achieve high performance, people usually assume transactions to be non-atomic, so we need to introduce transient states. The number of transient states varies according to the aggressiveness of the protocol. The existence of transient states greatly increases the complexity of the cache coherence protocol.

Interconnection network. As the number of cores increases, how to connect those cores, caches, memories and directories becomes more important since the topology may impact the performance and power consumption. For a small number of cores, crossbar, bus, or ring may work well, as shown in [48], [51]. However, when the system scales, these topologies are not practical. Instead, we require more scalable topologies, such as torus, mesh, etc. Another important feature of the interconnection network is whether it provides point-to-point ordering. With ordering, the design of cache coherence protocol can be much easier since many race conditions can be avoided. However, unordered networks allow more optimizations, such as adaptive routing [24], [38], which provides more flexibility and avoids network congestion. Thus the ordering is another tradeoff architects need to consider before making the decision.

Write policy. There are two kinds of write policies: write-invalidate and writeupdate. Write-invalidate means a cache needs to invalidate all other caches before it writes to the block, while write-update means the cache needs to update the data in all caches that have the block when it performs the write. The write-update policy propagates data faster than the write-invalidate policy, but it uses a lot more bandwidth and complicates the memory consistency [2], [89]. Due to this fact write-invalidate policy is more widely used in current cache coherence protocols.

Besides the above basic design options, there are still a variety of details that people can choose to improve their cache coherence protocols. These optimizations can help improve performance, reduce the storage overhead, or reduce the network traffic [45], [63], [91]. For example, in a directory protocol, non-blocking directory allows subsequent requests to proceed without being blocked at the directory. This technique can improve performance since it greatly reduces the waiting time on the critical path. We do not discuss various optimizations in this thesis as they are not related to our work, but it is worth mentioning that most of these optimizations can still apply to our proposed cache coherence protocols.

#### 2.3 Status and Challenges of Cache Coherence Verification

To verify cache coherence protocols, formal verification is preferable to simulation-based verification. The reasons are tow-folded. First, as mentioned in Section 2.1, simulation has low coverage in face of complex systems, while formal verification is always complete. Current cache coherence protocols in many-core systems are so aggressively optimized that a large number of concurrent events may occur. Not being able to gather all possible combinations of inputs and outputs, simulation is very likely to miss corner cases which are actually buggy. As an important functional unit in the memory hierarchy, a cache coherence protocol cannot tolerate bugs, which may lead to a system failure. We want a complete correctness guarantee of the protocol, which requires formal verification. A secondary reason for employing formal verification for cache coherence protocols is that the components involved in a protocol are usually described as several state machines that interact with each other. This state-based structure is amenable to the current formal verification tools since it is very convenient to model the cache coherence protocol in the tool.

Due to the above reasons, in the following sub-sections, we only include the research work related to formal verification of cache coherence protocols. Hereafter, whenever we mention verification, we only refer to formal verification.

#### 2.3.1 Verification of Flat Cache Coherence Protocols

Most of the research done to verify cache coherence protocols is for flat (not hierarchical) protocols. Depending on which formal verification method the work uses, it can be categorized as a model checking based method, theorem proving based method or a joint method combining model checking and theorem proving.

The model checking method is widely used in small scale examples. Stern and Dill [92] used Murphi [33] to verify the cache coherence protocol of IEEE standard for scalable coherent interface. Clarke et. al [26] used SMV [70] to formally model and verify a cache coherence protocol described in IEEE Futurebus+ standard. Fong Dong et. al [84], [85] proposed to verify cache coherence protocols based on a symbolic state expansion procedure and employed it to verify the coherence in S3.mp (Sun's Scalable Shared memory MultiProcessor). All of the work performs the verification using a fully automated model checking tool and the procedure is very straightforward. However, they all have to deal with the state space explosion problem. There have been various techniques proposed to reduce the number of states, but even with these techniques applied, those automated tools still have a limitation on the number of cores. The inability to scale is the biggest disadvantage of model checking a cache coherence protocol, since for current cache coherence protocols, there is no guarantee that the correctness of a small system implies the correctness of a much bigger system [8]. Even if we can formally verify a cache coherence protocol with 4 cores as sanity check, we cannot trust that the protocol is bug-free if we implement it for a 64-core system.

Theorem proving is more powerful in verifying complex protocols in larger systems due to its scalability. Akhiani et al. [5] used TLA+ language [73], which is based on first-order logic and set theory, to verify the cache coherence protocol for the Alpha memory model. Moore [76] proved the correctness of a write invalidate cache coherence with the ACL2 theorem proving system [50] with arbitrary number of nodes. Park and Dill [83] employed the general purpose theorem prover PVS [80] to the verify the safety properties of the cache coherence protocol in Stanford FLASH multiprocessor [53]. The problem with theorem proving is a huge amount of time and human efforts are needed to guide the verification. For example, Park and Dill [83] shows that it is a laborious process even to formulate the invariants against which the model would be verified.

We can see that model checking has automaticity, but is limited by the number of nodes in a cache coherence protocol, while theorem proving has capability, but is limited by the amount of human efforts and ingenuity required. As mentioned earlier, there is some work done to combine the capabilities of model checking and theorem proving. The verification of cache coherence protocols can also leverage the combinational method. For different approaches, the ratio of model checking and theorem proving varies, and the roles of model checking and theorem proving also vary. For example, in [67], theorem proving is used to split the problem to sub problems that can fit into the model checking tools, so the verification results of all sub problems together confirm the cache coherence protocol is correct. While in [25], since model checking is not able to handle the large number of caches, an abstraction is done to simplify the cache coherence model, which introduce spurious bugs due to over approximation. Then theorem proving acts as the human reasoning process to remove the spurious bugs found during the model checking process.

Ideally, the combination of model checking and theorem proving can find an optimal point between automaticity and capability. However, it is a big question that how general the method can be. Put another way, what kind of cache coherence protocols and properties can be verified using this method. Most previous research only shows examples of simplified or unrealistic cache coherence protocols and we doubt that modern cache coherence protocols are naturally compatible with this method.

In all, for verifying flat cache coherence protocols, various methods have been proposed, but many of them suffer from the automaticity or capability problem. There do exist some methods that aim to achieve the advantages of both worlds, but no one has studied what kind of cache coherence protocols these methods can apply to.

#### 2.3.2 Verification of Hierarchical Cache Coherence Protocols

As multiple levels of cache come to exist, there is a demand for cache coherence protocols to change from "flat" to "hierarchical" [37], [41], [57], [64]. For each level of cache, there is a coherence protocol independent of protocols for other levels. The most important advantage of hierarchical cache coherence protocols is the scalability and flexibility. In a many-core system with hundreds or thousands of cores, it is not practical to have all cores in the same coherence domain. It can easily cause a bottleneck and hinder performance. With a hierarchical structure, we can partition the cores to different clusters and probably run workloads on different domains. Moreover, we can use different cache coherence protocols at different levels if they have distinct requirements.

The verification of hierarchical cache coherence protocols has not been as actively studied as that of flat protocols. Compared to flat protocols, hierarchical cache coherence protocols are even more difficult to verify. Hierarchical protocols usually involve more components and more types of state machines, which imply a much larger state space. It is usually impossible to verify a hierarchical cache coherence protocol with only automated tools even for a small scale system.

One of the earliest work that verified hierarchical cache coherence protocol is by McMillan and Schwalbe [71]. They used SMV [70] to verify the protocol of Gigamax multiprocessor, which has two levels of snooping protocol. However, in their verification, many details about the protocol are abstracted away due to the consideration of complexity. The over simplification makes the work itself not that interesting since the correctness of the higher level does not guarantee the correctness of the actual protocol. Some other work in this field usually considers one level of the protocol at a time and abstracted away other levels. However, this kind of separation usually lacks proof and may involve bugs [23]. One piece of the most important work of verifying a hierarchical cache coherence protocol recently is by Chen et al. [23]. They developed a compositional approach based on assume-guarantee reasoning to decompose hierarchical protocols into a set of abstract protocols. The decomposition greatly reduces the verification complexity. Then each level is verified at one time. The theoretical way of separating the hierarchical cache coherence protocol ensures the correctness of all different levels implies the correctness the overall verification. However, there is no indication that their method can scale to cache coherence protocols with more levels since it still involves too much reasoning.

As seen from above, there is no standard method of verifying a hierarchical cache coherence protocol. This area is far from mature and a lot of issues need to be studied. In Chapter 3, we will show how we can standardize the verification of a hierarchical protocol by designing the protocol in a special way.

## 2.4 Designing Verifiable Cache Coherence Protocols

As discussed in Section 2.3, currently there is no clear answer what is the most efficient way to verify a flat cache coherence protocol and what kind of protocols can be verified. And the techniques for verifying a hierarchical cache coherence protocol are far from mature. Although experts in verification have struggled to come up with innovative methods to fulfill their responsibility, the current situation is many realistic cache coherence protocols are still impossible to verify. We, as architects, would like to solve this problem from a different perspective. We follow the "design for verifiability" idea and propose methodologies for designing verifiable cache coherence protocols so that the verification is easier.

## 2.4.1 Related Work in Design for Verifiability

Milne [74] presents the concept of "Design for verifiability", which proposed to limit the designer's freedom so that the hardware they designed would have fewer states and thus need less verification effort. Milne gave an example of inserting clocked latches between blocks of combinational logic to reduce the number of states. Although very simple, this example provides us with the hint that we may need to sacrifice some area and speed when modifying the design to gain the convenience in formal verification. However, as long as the cost is acceptable, we have a good reason to make such modification.

In Curzon and Leslie's paper [30], they investigate the notion "Design for verifiability" presented by Milne. They tried to find the particular part which had a high impact on verification effort. By changing the implementation of this part, they removed the problem without sacrificing too much performance. Arvind et al. [8] more directly suggested, from hardware point of view, that formal verification should be got into the design flow so that formal methods can be more widely used. Lungu and Sorin [58] explore how the microprocessor should be designed so that the verification is easier. We follow these concepts and agree that architects should add verifiability as a first class design constraint together with metrics such as performance, power, and reliability.

#### 2.4.2 Verifiability Analysis of Cache Coherence Protocols

In the context of cache coherence protocols, we are unaware of any work that proposes to design a cache coherence protocol with the verification effort as a first class constraint. There exist several pieces of work that explored the verifiability of designed cache coherence protocols. Martin [62] argues that directory protocols are superior to snooping protocols with regard to formal verification effort. His conclusion is based on qualitative analysis considering desirable properties for verification. Marty [65] compared the formal verification efforts of different cache coherence protocol designs and showed their protocol is more amenable to formal verification. However, they primal purpose was for performance instead of verification and it is not clear how general their protocol could be.

Two other papers discuss verification or design complexity after designing cache coherence protocols. HCC [55] is organized hierarchically and they argue that this tree organization facilitates the verification of liveness and consistency. HCC is verified manually, unlike the largely automated verification in our work. Vantrease et al. [95] propose an atomic coherence protocol that avoids races and is thus simpler; we expect it would be easier to verify than a typical non-atomic protocol, but verification is not discussed in the paper.

A more recent work is by Beu et al. [12], which leverage a coherence design framework called MCP [13] for composing heterogeneous protocols in a hierarchical fashion. Beu et al. show that, if each of the building block protocols is verified correct, then the hierarchical protocol is also correct by inductive reasoning. The main weakness of their paper is the lack of formal proof.

Our work is different from the above research in that we encourage architects to consider verification effort as a first class design constraint and incorporate it in early design stages. Moreover, all of designed cache coherence protocols can be formally verified with mostly automated tools instead of human analysis.

# 3. Fractal Coherence: Verifiable Hierarchical Cache Coherence

In this chapter, we propose a methodology for designing a hierarchical cache coherence protocols, called Fractal Coherence. Fractal Coherence enables the protocols to be verifiable using existing, automated, easy-to-use formal tools even for large, many-core systems. The idea and design methodology of Fractal Coherence are described from Section 3.1 through Section 3.3. In Section 3.4, a concrete example of a Fractal Coherence protocol, TreeFractal, is illustrated in detail and evaluated with full system simulation to compare with typical snooping and directory protocols. Section 3.5 shows another example, Fractal Directory, which has a larger degree tree as its structure and is more realistic than TreeFractal. Section 3.6 discusses the design space of Fractal Coherence and Section 3.7 is the summary of this chapter.

## 3.1 Concept of Fractal Coherence

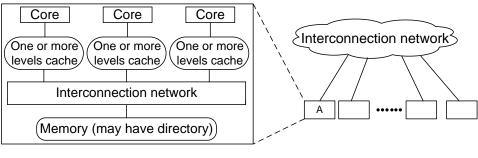

Fractal Coherence protocols originate from fractal theory and leverage the selfsimilarity characteristic of fractals. Considering the two systems in Figure 1, we assume that System A is a shared-memory system that is small enough to be verified coherent by existing formal tools. System A is part of a much larger System B. We want to formally verify that System B is cache coherent, but System B is large and way beyond the capability of existing tools. Intuitively, if there is a certain kind of similarity between

Verifiable small system: A Unverifiable large system: B

#### Figure 1: Scalability problem in verification of cache coherence

System A and System B, we may be able to extend the verification of System A to the scale of System B.

This intuition inspires us to use fractal theory. A fractal is a shape that can be split into parts in which each part is a reduced-size copy of the whole [60]. At any scale, the fractal appears exactly identical. We focus on the cache coherence behavior of each scale instead of only the structure. Thus, if System B has fractal behavior and System A is a reduced-size copy of System B, then we can prove the cache coherence of B based on the cache coherence of A.

We propose Fractal Coherence, a class of coherence protocols that leverages the self-similarity characteristic of fractal theory to enable the verification of large scale systems. A system with Fractal Coherence is architected in a manner that is formally verified to be fractal in behavior with regard to coherence.

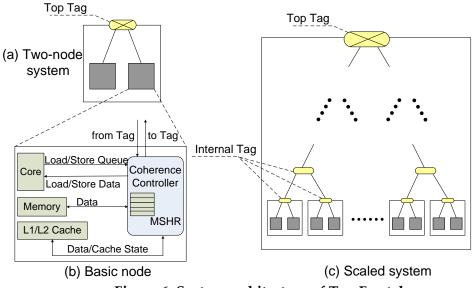

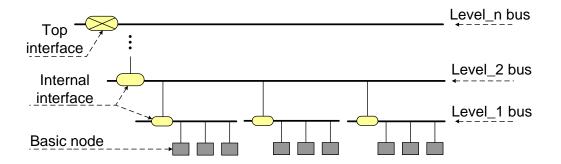

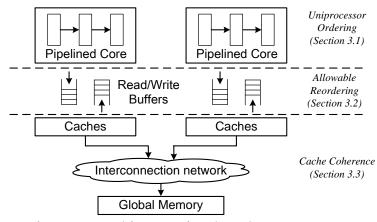

## 3.2 System Architecture

To ensure fractal behavior, Fractal Coherence requires a hierarchical logical structure. However, Fractal Coherence does not place any requirements on the physical topology of the system. The hierarchical logical structure can be implemented on any kind of physical topology, such as a 2D mesh, torus, ring, etc. Hereafter, when we refer to a system's structure, we are referring to its logical structure. In this thesis, we confine our discussion to the tree structure with a consistent degree at each level, but we believe our methodology can also apply to other hierarchical logical structures.

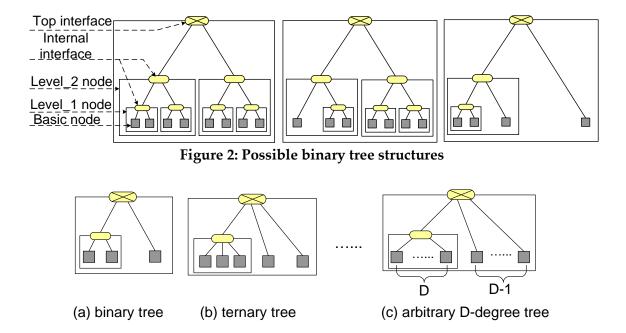

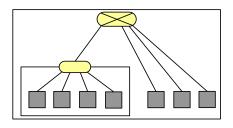

The tree structure in Fractal Coherence can be either a balanced tree or an unbalanced tree, because Fractal Coherence does not rely on the fractal structure; instead, it relies on the fractal behavior. Figure 2 shows several possible binary tree structures for Fractal Coherence. The shadowed square components are basic nodes (corresponding to the leaf nodes in the tree structure), which may have a number of caches, cores and memories. The elliptical shape components are the interfaces (corresponding to the internal nodes in the tree structure) that support the fractal behavior. Interfaces may also associate with caches. Depending on its position in the system, an interface can be categorized as a top interface (corresponding to the root node in the tree structure) or an internal interface (corresponding to internal nodes except the root node in the tree structure). Two or more basic nodes and a top interface or an

**Figure 3: Minimum systems of different degree trees**

internal interface compose a level\_1 node. Iteratively, two or more level\_n-1 nodes and a top interface or an internal interface compose a level\_n node, where "n" is the height of the node's tree. For a tree structure with a given degree, we can determine the minimum system. It is the smallest complete system that includes all the different types of components used in larger systems. The minimum system consists of a top interface, an internal interface with all its children, and other basic node(s) directly beneath the top interface. Figure 3 shows the minimum system for a binary tree, a ternary tree, and any D-degree tree.

## 3.3 Verification Methodology

To formally verify that a fractal system is cache coherent with any arbitrary number of nodes, two verification steps are needed. The first step is to verify that the smallest scale of the system is coherent. The second step is to show that the system is fractal with respect to coherence. We then present an inductive proof that these two verification steps are the only formal verification steps needed. Unlike the two verification steps, which are part of the design flow for each Fractal Coherence protocol developed, the inductive proof need only be performed once to show that the two verification steps are sufficient.

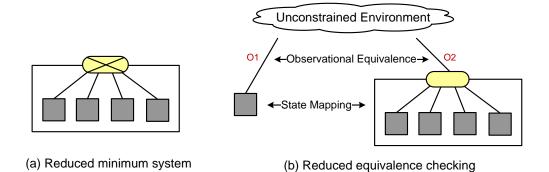

#### 3.3.1 Verification of Minimum System

Ideally, we could perform the verification of minimum system with an automated model checking tool, as long as the minimum system is small enough. If the state space of the minimum system is beyond the capability of existing tools, we probably need to combine the strength of both model checking and theorem proving. We will show the example that explodes model checking tools later in Section 3.5. In this section, we will only focus on the common case in which a model checking tool is able to verify the minimum system.

As discussed in Section 2.1.3, the model checking process includes modeling, specification, and verification. We illustrate several key points in these processes when

we verify a cache coherence protocol. First, modeling has to accurately capture the behavior of the cache coherence protocol no matter what tool and language it uses. For example, non-atomic protocol transactions should not be assumed atomic. This abstraction may cause misses of important transactions. However, there are still several reduction techniques that can safely apply to the modeling of a cache coherence protocol. For example, modeling only one block in the cache and memory instead of all the blocks is sufficient to verify the cache coherence protocol; the data values themselves can also be abstracted away since they have no impact on coherence [90]. These optimizations can all be employed in modeling the minimum system of Fractal Coherence and they help reduce the state space. Second, specification has to precisely state the properties that the protocol must satisfy. The correctness properties of a cache coherence protocol are usually specified in invariants or temporal logic. More specifically, the tool needs to verify the following properties: 1) each block can have either one writer or multiple readers at any given time, 2) the read always retrieve the value of the latest write, 3) no state machines will ever enter deadlock, and 4) the system is making forward progress at all times (i.e., there is no livelock). Finally, the tool performs the verification by walking through each possible state of the entire system (i.e., including the states of all coherence controllers) to ensure that all states adhere to the specified properties.

#### **3.3.2 Verification of Fractal Behavior**

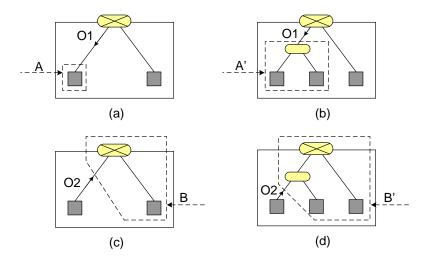

After verifying that the minimum system is coherent, we need to show that the whole system has fractal behavior in order to leverage the self-similarity to prove that larger scale systems are coherent. By fractal behavior, we mean that a system scales in a manner such that the behavior of the larger system is always the same as the smaller system. Fractal behavior ensures that coherence is maintained while scaling the system.

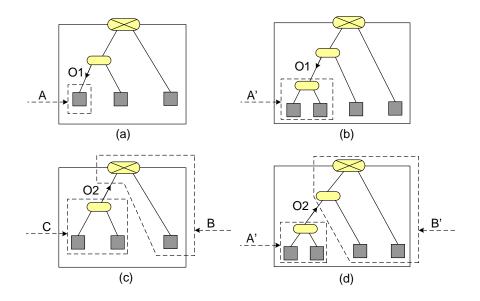

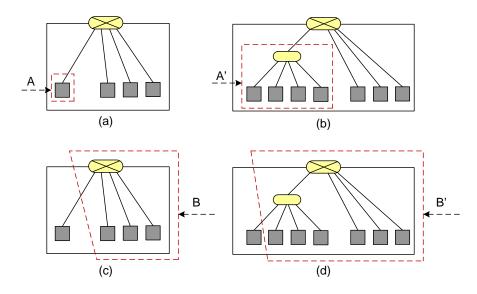

We need "equivalence checking" to verify that each scale of the system behaves the same. Because the system is constructed by iteration, it is sufficient to verify only the equivalence between the level\_1 node and the level\_2 node. We take the binary tree in Figure 3(a) as an example and show in Figure 4 the two relationships needed to be verified equivalent. We construct a 4-node binary tree, shown in Figure 4(b), by expanding node A in Figure 4(a) to node A' in Figure 4(b). To satisfy fractal behavior requirements, two verification steps must be performed. First, we must verify that A and A' have the same behavior as observed at point O1 in Figure 4(a) and Figure 4(b). This verification enables the system to scale based on substituting A with A'. The rest of the system cannot tell the difference after the substitution and has the same behavior as before. Second, we must verify that B and B' have the same behavior as observed at point O2 in Figure 4(c) and Figure 4(d). This equivalence means that C in Figure 4(c) and A' in Figure 4(d) have the same environment and thus they behave the same. This

**Figure 4: Observational equivalence for maintaining fractal behavior** verification ensures that the two basic nodes in A' behave the same as they do in a coherent system (Figure 4(c)). The two verifications together ensure that the new system (Figure 4(b)) has the same behavior as the previous one (Figure 4(a)).

These two verification steps are both "equivalence checking." Intuitively, A' has more state machines than A, and B' has more state machines than B. They cannot have exactly the same transitions. However, for verifying fractal behavior, we need to show only that they behave in a manner that is "observationally equivalent" [75], which means the external world cannot tell the difference between the two systems. The observational equivalence allows several transitions in the more complex system to match one transition in the simple system. For example, considering a simple MSI protocol without transient states, if A is in state S, the observationally equivalent states in A' are S:S, S:I and I:S, where the state before the colon is the state of the left child in A', and the state after the colon is the state of the right child in A'. The transitions between S:S, S:I and I:S are considered "internal" because they have no impact on the external world. The three states S:S, S:I and I:S are collapsed to one. We can say that A', taken as a "node as a whole," is in state S, meaning the external world considers A' to be a single node in state S. By this collapsing, A' can be simplified to have the same states and transitions as A, and B' can be simplified to have the same states as B. The external world cannot tell apart A and A' or B and B'.

This equivalence checking is also a formal method because it explores all possible states in the system. Therefore, the tool used for this verification should be an exhaustive tool. Many formal tools are able to do equivalence checking and they accept different kinds of description languages. We will show a detailed verification process of the fractal behavior of TreeFractal in Section 3.4.2.2.

#### 3.3.3 Proof of Cache Coherence for Arbitrary N-node System

We claimed that the formal verification steps described in Section 3.3.1 and Section 3.3.2 are the only steps the architect of a Fractal Coherence protocol must perform to verify the correctness of an arbitrary N-node system with Fractal Coherence. In this section, we prove by induction why these two steps are sufficient. Definition 1. We use F (L, D, N) to denote a system that has L levels, D degrees for each level, and N basic nodes in all. The subscript "s" in Fs (L, D, N) denotes that the system is a sub-system inside a larger system and not a complete system itself. In F (L, D, N) and Fs (L, D, N), L={1,2, ..., m}, D={2,3, ..., n}, and N={(D-1)\*L+1, (D-1)\*(L+1)+1, ..., DL}.

From Definition 1, we know that the minimum system can be written as F (2, D, 2\*D-1). Note that only when we use a binary tree (D=2), the number of basic nodes can be contiguous; otherwise we can have only discrete increments of (D-1) for the number of basic nodes, because we assume each level of the tree structure has the same degree. We could relax this constraint, since the missing children can be considered as always in state I and have no impact on coherence.

Definition 2. Given two systems A and B, where A is larger than B, we use the symbol " $\approx$ " to represent observational equivalence, and we use the symbol "-" to represent the subtraction of a subsystem from a larger system. So A  $\approx$  B means A is observationally equivalent to B, and A – B represents the rest of the system after removing a subsystem B from System A.

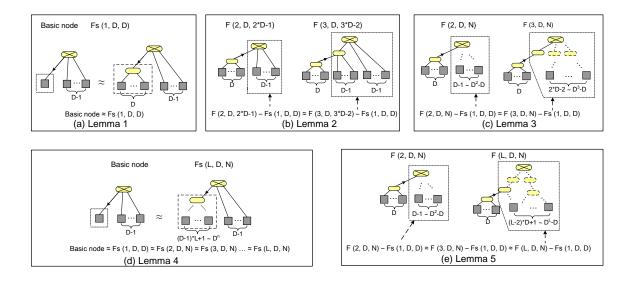

We now present five lemmas that we use in our proof. Each lemma is illustrated in Figure 5.

**Lemma 1** (Figure 5a). Basic node  $\approx$  Fs (1, D, D) by the verification result of Section II.C.

**Lemma 2** (Figure 5b). F (2, D, 2\*D-1) – Fs (1, D, D)  $\approx$  F (3, D, 3\*D-2) – Fs (1, D, D) by the verification result of Section II.C.

**Lemma 3** (Figure 5c). F (2, D, N) – Fs (1, D, D)  $\approx$  F (3, D, N) – Fs (1, D, D) by a generalization of Lemma 2 based on using Lemma 1 to do substitution.

**Lemma 4** (Figure 5d). Basic node  $\approx$  Fs (1, D, D)  $\approx$  Fs (2, D, N)  $\approx$  Fs (3, D, N) ...  $\approx$  Fs (L, D, N) by iteration on Lemma 1.

**Lemma 5** (Figure 5e). F (2, D, N) – Fs (1, D, D) ≈ F (3, D, N) – Fs (1, D, D) ≈ F (L, D,

N) – Fs (1, D, D) by iteration on Lemma 3 and by using Lemma 4 to do substitution.

Theorem. Any N-node system is coherent.

## Proof.

- Base case: when N = 2\*D -1, it is the minimum system. The cache coherence of the minimum system is formally proved (Section II.B). Note that when N<2\*D-1, the system can be formally proved coherent by just using Lemma 1 to do substitutions.

- Inductive step: We assume that, when N=k\*(D-1), the system is coherent. We must prove that, when N= (k+1)\*(D-1), the system is still coherent. To expand the k\*(D-1) node system into the (k+1)\*(D-1) node system, we

substitute a basic node in the k\*(D-1) node system with a Fs (1, D, D) that we call A'.

**Proposition 1.** For the other N-1 nodes and the A' subsystem, coherence is still maintained. Based on Lemma 1, after substituting a basic node with A', the rest of the system cannot see the difference and maintains the same behavior. At the same time, A' as a whole maintains the same coherence states as the previous basic node does.

**Proposition 2.** A' maintaining coherence indicates that all of its children maintain coherence. Based on Lemma 5, the rest of the system after subtracting A' from the N=(k+1)\*(D-1) node system is observationally equivalent to the rest of the system after subtracting A' from the N=k\*(D-1) node system. Thus A' behaves the same in the two systems. We know that, in the N=k\*(D-1) node system, A' as a whole as well as each basic node of A' maintain coherence, because the N=k\*(D-1) node system is cache coherent (the inductive assumption). Therefore, in the N=(k+1)\*(D-1) node system, A' as a whole maintaining coherence is sufficient to ensure that each basic node in A' maintains coherence.

Based on Proposition 1 and Proposition 2, we can conclude that any N-node system is coherent.

Figure 5: Lemmas for proof of cache coherence in any N-node system

## 3.4 Case Study: TreeFractal

There are many different possible Fractal Coherence protocols. We implemented a specific protocol, which we call TreeFractal, to show that the fractal design methodology is viable.

## 3.4.1 System Design

TreeFractal uses a binary tree as both the logical structure and network topology, although this is not required. In TreeFractal, each interface that maintains fractal behavior (see Figure 2) contains duplicate cache tags for all cache blocks beneath it in the tree. We call these interfaces Tags. We build up the system from a simple two-node system to a scaled system.

#### 3.4.1.1 Two-node System Design

We start our design from a two-node system, illustrated in Figure 6(a). It consists of two basic nodes and a Top Tag. The basic node, shown in Figure 6(b), consists of a core, a private L1 cache, a private L2 cache, a portion of the shared memory and a coherence controller. The coherence controller is responsible for communicating with the core, the cache, the memories and its parent Tag. The coherence controller also has MSHRs to allow for multiple outstanding requests. The Top Tag holds copies of the cache tags and coherence states of its two children, and it serves as the serialization point for coherence transactions in the two-node system. In the two-node system, the Tag is called the "Top" Tag to distinguish it from "Internal" Tags in larger systems.

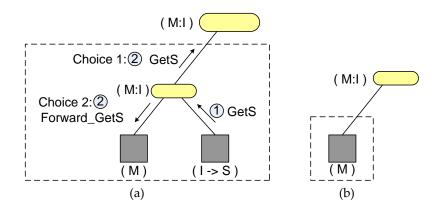

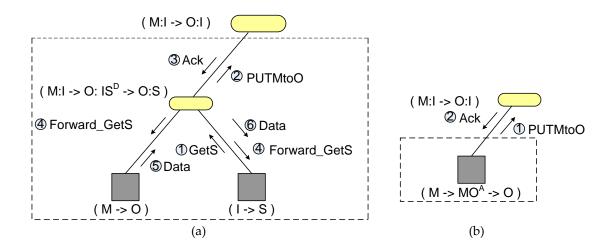

The TreeFractal coherence protocol is a MOSI protocol with numerous transient states that is neither snooping nor directory, although it has some features in common with both of those well-known classes of protocols. The coherence controller responds to load and store requests from the core. If the coherence controller cannot satisfy a load or store, it issues a coherence request up to the Top Tag. When the Top Tag receives a coherence request from one of its children cores, it looks up the state of the block in both of its children. We denote this state using X:Y notation, where X is the state of the block in the left child and Y is the state of the block in the right child. For example, the Top Tag state S:O denotes that the left child has the block in state S and the right child has the block in state O. Based on the states in the children, the Top Tag forwards the request down to either one or both of them (similar to directory protocols). Because the Top Tag is the serialization point for all transactions, it always forwards a request back to the requestor, so that the requestor knows when its request is ordered with respect to other coherence requests (similar to snooping protocols). We now present three examples to illustrate how this protocol works: