ISSN (Print) : 2320 – 3765 ISSN (Online): 2278 – 8875

# International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Issue 10, October 2013

# Seven Level Inverter Based Shunt Hybrid Active Power Filter Topology for Harmonic Reduction

### <sup>\*</sup>G. Jayakrishna<sup>1</sup>, B.Vamsipriya<sup>2</sup>

Professor, Department of EEE, Siddharth Institute of Engineering and Technology, Puttur, Andhra Pradesh, India

PG student, Department of EEE, Siddharth Institute of Engineering and Technology, Puttur, Andhra Pradesh, India

**ABSTRACT:** This paper presents a three-phase asymmetric cascaded seven level inverter (ACSLI) based Shunt Hybrid Active Power Filter (SHAPF) topology for harmonic reduction in medium voltage test system (MVTS). The proposed SHAF topology consists of ACSLI based shunt active power filter (SAPF) and shunt passive filters (SPF) connected in parallel with the load. The SHAPF topology compensates harmonic currents drawn by non-linear load. The compensation process is based on concept of synchronous reference frame theory (SRFT) used for reference compensation current estimation, carrier switching frequency sub-harmonic pulse width modulation (CSFSHPWM) for generating switching signals for ACSLI, fuzzy logic controller (FLC) for maintaining DC bus capacitor voltage constant. Three types of shunt passive filters namely single tuned, double tuned and high pass filter are used individually for enhancing the harmonic filtering performance of ACSLI based SAPF. The proposed SHAPF topology is validated through MATLAB/SIMULINK simulation for MVTS and the results were presented.

**Key words**: Asymmetric cascaded seven level inverter, Shunt hybrid active power filter, Synchronous reference frame theory, Fuzzy logic controller, Shunt passive filter.

#### I. INTRODUCTION

The usage of nonlinear loads at high voltages is increasing in industry day-by-day leading to harmonic pollution in the line current, increased losses, poor system performance and efficiency. The conventional two level active filters have limitations in medium and high voltage applications due to semiconductor reverse voltage rating constraint, high power loss, high level of dv/dt causing switching noise hence electromagnetic interference with communication system, as well as insulation degradation in electronic and electrical systems [1]. The development of multilevel inverter (MLI) has become the option for reactive power compensation and power quality improvement. Multilevel inverter topologies such as diode clamped, flying capacitor and cascade H-bridge inverters are available in the literature [2]. Out of these topologies cascade multilevel inverter requires less number of components to produce same number of levels [3]. Cascaded inverters are modified to asymmetric cascaded multilevel inverter (ACMLI) topologies to reduce number of switches with each DC source driven at different voltage level [4]. Defining 'S' as the cell number and n=1,2,...S, the ACMLIs are classified as MLI with( $2^{S-n}$ )\* V<sub>DC</sub> factor and with ( $3^{S-n}$ )\*V<sub>DC</sub> factor . In this paper MLI with ( $2^{S-n}$ )\* V<sub>DC</sub> factor is used as SAPF. In this configuration the magnitude of DC voltage sources will increase by a factor ( $2^{S-n}$ ). The output waveform has number of levels equal to ( $2^{S+1} - 1$ )[5]. In active power filter application there is no need of active power output from the inverter, therefore a separate DC source for each converter bridge is not required. Hence in this paper single DC source is used and the other storage device is replaced by a capacitor.

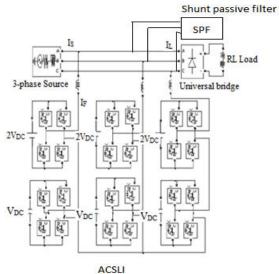

#### **II. OPERATION OF ACSLI BASED SHAPF**

The test system with ACSLI based SHAPF compensation is shown in Fig.1. It consists of a three phase medium voltage AC source connected to nonlinear diode rectifier load through a line. An ACSLI based SAPF and shunt passive filter are connected in parallel with the load. In the operation of APF, the harmonic component of load current is derived through harmonic detection circuit and reverses it as the reference compensation current. Then switching signals for ACSLI are generated such that AC side output current of APF correctly traces reference current and provides the harmonic current of the load, so that source current will be free from harmonics and approaches towards sinusoidal. In addition to SAPF, SPF is connected in parallel with the load to bye-pass some selected harmonics so that burden on active filter reduces and its filtering performance increases.

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Issue 10, October 2013

Fig1.Medium voltage test system with SHAPF compensation.

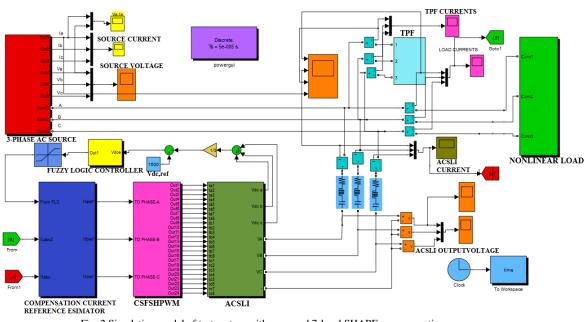

### III. SIMULINK MODEL OF MVTS WITH PROPOSED ACSLI BASED SHAPF COMPENSATION

The SIMULINK model of the test system with proposed ACSLI based SHAF compensation is depicted in Fig. 2.

Fig. 2 Simulation model of test system with proposed 7-level SHAPF compensation.

The test system consists of a three phase AC source of voltage 4500 V(peak) and 50 Hz frequency connected to a nonlinear diode rectifier load through a source and line combined reactance of 15mH/phase. The R-L load on the DC side of diode rectifier is 20 ohm and 0.1 mH.

### A. Three Phase ACSLI

The three phase ACSLI consists of two H-bridge cells namely low voltage (LV) cell of 1.5kV and high voltage (HV) cell of 3kV connected in series. Each H-bridge cell is constructed using four IGBTs with anti-parallel diodes. Since

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Issue 10, October 2013

$V_{HV}$  is two times  $V_{LV}$ , it can produce seven levels in its output wave form via +4.5kV,3 kV,1.5 kV,0,-1.5 kV,-3 kV and -4.5 kV. A DC source of 3 kV is used as storage device in HV cell and a capacitor of 4000  $\mu$ F is used on the DC side of LV cell. The DC-bus capacitor value is taken large enough to minimize the variation of its voltage based on the general principle that capacitor load time constant to be ten times to that of fundamental period [5].

#### B. Control Strategy of ACSLI

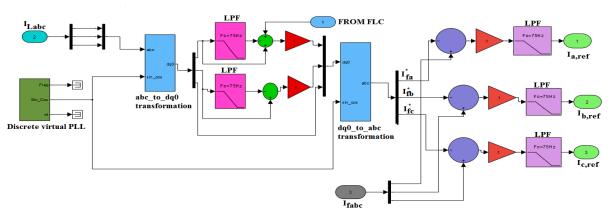

The control strategy of ACSLISAPF includes SRFT for estimating reference compensating current, CSFSHPWM for generating gating signals and FLC for maintaining LV cell capacitor voltage constant.

1) Synchronous reference frame theory (SRFT): The time domain methods namely instantaneous reactive-power theory and Synchronous reference frame theory (SRFT) are most commonly used for estimating reference compensating current [6]. SRFT transforms the three phase system voltage and current variables into a stationary reference frame using Park's transformation. The active and reactive components of the three-phase system are represented by the direct and quadrature components respectively. The fundamental components are transformed into DC quantities which can be separated easily through filtering. The system with this technique is very stable since the controller deals mainly with DC quantities and the computation is instantaneous [7]. Suppose the three phase AC source currents are  $I_{sa}$ ,  $I_{sb}$ ,  $I_{sc}$ , non-linear load currents are  $I_{La}$ ,  $I_{Lb}$ ,  $I_{Lc}$  and active filter compensating currents are  $I_{fa}$ ,  $I_{fb}$ ,  $I_{fc}$ . The load currents in a-b-c reference frame can be converted in to d-q reference frame using Park's transformation as shown in equation (1)

$$\begin{bmatrix} I_{d} \\ I_{q} \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} \cos \theta & \cos \left( \theta - \frac{2\pi}{3} \right) & \cos \left( \theta + \frac{2\pi}{3} \right) \\ \sin \theta & -\sin \left( \theta - \frac{2\pi}{3} \right) & -\sin \left( \theta + \frac{2\pi}{3} \right) \end{bmatrix} \begin{bmatrix} I_{La} \\ I_{Lb} \\ I_{Lc} \end{bmatrix}$$

These currents can be decomposed into DC component and harmonic component as shown in equation (2).

$$\mathbf{I}_{\mathrm{d}} = \mathbf{I}_{\mathrm{ddc}} + \mathbf{I}_{\mathrm{dh}}, \qquad \qquad \mathbf{I}_{\mathrm{q}} = \mathbf{I}_{\mathrm{qdc}} + \mathbf{I}_{\mathrm{qh}}$$

(2)

The harmonic component of load current is obtained by using a low pass filter and subtracting output of LPF from total load current as shown by eqn. (3).

$$I_{dh} = I_L - LPF(I_d), \ I_{qh} = I_L - LPF(I_q)$$

(3)

These reference currents are transformed into a-b-c coordinates by applying Inverse Park's transformation as shown in eqn. (4).

$$\begin{bmatrix} I_{fa}^{*} \\ I_{fb}^{*} \\ I_{fc}^{*} \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} \cos\theta & \sin\theta \\ \cos\left(\theta - \frac{2\pi}{3}\right) & -\sin\left(\theta - \frac{2\pi}{3}\right) \\ \cos\left(\theta + \frac{2\pi}{3}\right) & -\sin\left(\theta + \frac{2\pi}{3}\right) \end{bmatrix} \begin{bmatrix} I_{dh} \\ I_{qh} \end{bmatrix}$$

(4)

The SIMULINK model of SRFT used to estimate reference compensating current is shown in Fig. 3. The cut –off frequency of low pass filter is selected as 75 Hz.

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Issue 10, October 2013

Fig. 3 SIMULINK model of SRFT based compensating reference current estimator.

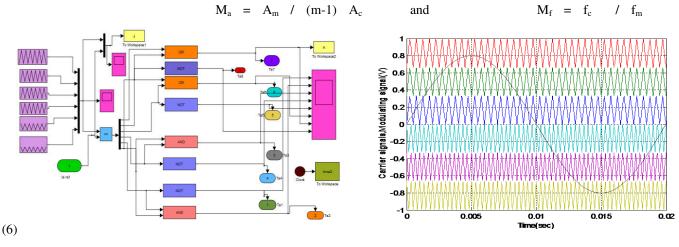

2) Carrier switching frequency sub-harmonic PWM: Most commonly used modulation techniques for MLIs are Selective harmonic elimination method[8], Space vector PWM method and Carrier based PWM methods[9,10], out of which CSFSHPWM is used in this paper due to its fast response, simple computation and its suitability for MLIs. The MATLAB/SIMULINK model of CSFSHPWM for Phase–a is illustrated in Fig. 4. In this technique six triangular signals each of 2 kHz frequency( $f_c$ ) and magnitude( $A_c$ ) of 0.33 and displaced vertically are used as carrier signals and the sinusoidal voltage wave form obtained from compensating reference current estimator is used as modulating signal as shown in Figure. 5. The reference waveform has peak to peak amplitude  $A_m$ , the frequency  $f_m$ , and its zero centered in the middle of the carrier set. The reference is continuously compared with each of the carrier signals. If the reference is greater than "s" carrier signal, then they active device corresponding to that carrier is switched off. In multilevel inverters, the amplitude modulation index " $M_a$ " and the frequency ratio " $M_f$ " are defined as

Fig. 4 SIMULINK model of CSFSHPWM for Phase –a.

Fig.5 Carrier and reference signals of CSFSHPWM for P hase-a.

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Issue 10, October 2013

*Solution 3)* Fuzzy Logic based LV cell DC Voltage Controller: Various types of controllers like Proportional-Integral (PI), adaptive, Neuro and Fuzzy Logic Controller (FLC) for DC bus voltage regulation are well presented in literature [11]. Since the fuzzy control rules are not derived from a heuristic knowledge of the system behavior, neither precise mathematical model nor complex computations are needed and is based on human like linguistic terms in the form of IF-THEN rules to capture the non-linear system dynamics, FLC is adopted in this paper to control LV Cell DC bus capacitor voltage. The LV cell DC bus voltage is compared with reference voltage of 1.5 kV to generate error signal. The error and its derivative are applied to FLC to obtain control signal which in turn applied to reference compensating current estimator to control the gating signals of VSI to maintain constant DC bus capacitor voltage at LV cell.

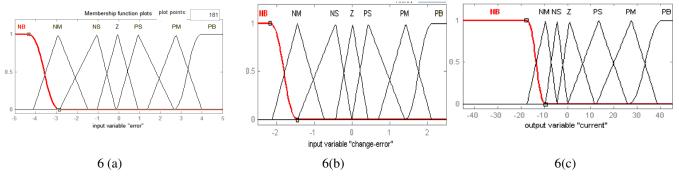

Fig. 6 The degree of membership functions for (a) The error (b) The derivative of error and (c) The output.

The two inputs and the output of FLC use seven triangular membership functions namely Negative Big (NB), Negative Medium (NM), Negative Small (NS), Zero(ZE), Positive Small (PS), Positive Medium(PM), Positive Big(PB). The membership values of input and output variables are shown in Fig. 6. Each input has seven linguistic variables, therefore there are 49 input label pairs. A rule table relating each one of 49 input label pairs to respective output label is given in Table 1. The type of fuzzy inference engine used is Mamdani and the Centroid method is used for defuzzification.

| e  |    |    |    |    |    |    |    |

|----|----|----|----|----|----|----|----|

| de | NB | NM | NS | ZE | PS | PM | PB |

| NB | NB | NB | NB | NB | NM | NS | ZE |

| NM | NB | NM | NM | NM | NS | ZE | PS |

| NS | NB | NM | NS | NS | ZE | PS | PM |

| ZE | NB | NM | NS | ZE | PS | PM | PB |

| PS | NM | NS | ZE | PS | PS | PM | PB |

| PM | NS | ZE | PS | PM | PM | PM | PB |

| PB | ZE | PS | PM | PB | PB | PB | PB |

### C. Shunt Passive Filter (SPF)

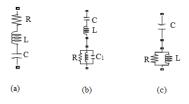

It is connected in parallel with the load to eliminate the effect of some selected harmonics. Three types of shunt passive filters namely single tuned filter, double tuned filter and high pass filter are used whose configurations are shown in Copyright to IJAREEIE <u>www.ijareeie.com</u> 4943

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Issue 10, October 2013

Figure. 7. In first case the SPF is constructed by using two single tuned passive filters connected in parallel in each phase and tuned to absorb 5<sup>th</sup> and 7<sup>th</sup> harmonic currents in the load current. The 5<sup>th</sup> order filter consists of a series R-L-C branch with a capacitor (C<sub>5</sub>), inductance (L<sub>5</sub>) and resistance (R<sub>5</sub>) and 7<sup>th</sup> order filter consists R<sub>7</sub>, L<sub>7</sub> and C<sub>7</sub> in series. Quality factor of the filter is selected as 75 and the filter capacitance value is fixed at  $30\mu$ F[12]. The parameter values of the single tuned passive filter are R<sub>5</sub>=0.2829\Omega, L<sub>5</sub>=13.504 mH, C<sub>5</sub>= $30\mu$ F, R<sub>7</sub>= 0.2021\Omega, L<sub>7</sub>= 6.892 mH and C<sub>7</sub> =  $30\mu$ F.

Fig. 7 Passive filter configurations (a)Single tuned filter( b) Double tuned filter and (c)High pass filter.

Design parameters of double tuned filter for absorbing 5<sup>th</sup> and 7<sup>th</sup> harmonic currents obtained at Q = 75 are C=30 $\mu$ F, L=9.64mH and R= 1344.65ohms. Design parameters of high pass passive filter at Cutoff frequency=50Hz and Quality factor of 75 are C = 30 $\mu$ F, R=70.73ohms and L=2mH.

### **IV. RESULTS AND DISCUSSION**

The simulation results of MVTS without any compensation are presented first, followed by basic ACSLI based SAPF compensation and the proposed ACSLI based SHAPF compensation. The performance of ACSLI based SAPF and ACSL based SHAPF with different passive filters for mitigating harmonics in MVTS is compared.

#### A. Results of MV Test System without any compensation

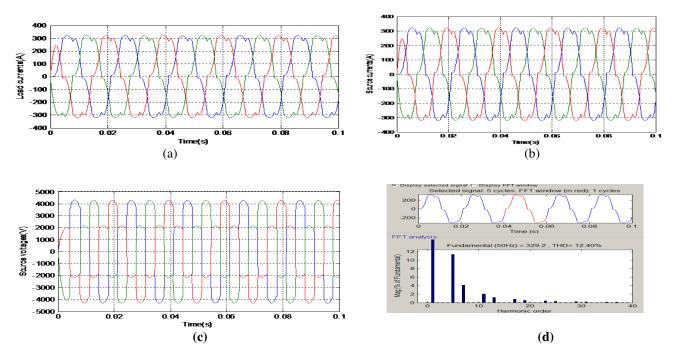

As can be seen in Fig. 8(a), that the current drawn by diode rectifier load is highly distorted and deviated significantly from sinusoidal waveform due to which the source current and source voltages are also distorted as shown in Figs.8(b) and 8(c).

Fig.8 Simulation results of MV test system without compensation a) Nonlinear load currents b) Source currents c) Source voltages d) THD analysis for source current of Phase-a

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Issue 10, October 2013

The distortion in the source voltage waveform is due to the presence of source and line inductance and distorted currents drawn by the load. The total harmonic distortion in source current of phase-a without any compensation is 12.4% as shown in the harmonic spectra of Figure 8(d). It is seen that the most dominant are 5<sup>th</sup> and 7<sup>th</sup> order harmonics in the spectra plot.

#### B. Results of MVTS with basic ACSLI based SAPF Compensation

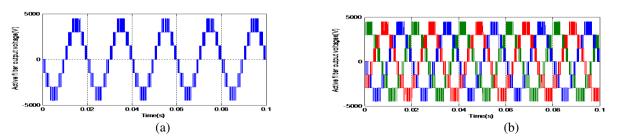

The Fig. 9 shows the single phase and three phase seven level output voltage wave forms of ACSLI based SAPF from which it is evident that CSFSHPWM worked effectively and produced seven levels in the output voltage wave form.

Fig. 9 Seven level voltages generated by the asymmetric cascaded inverter for (a) Phase-a (b) Phases a, b and c.

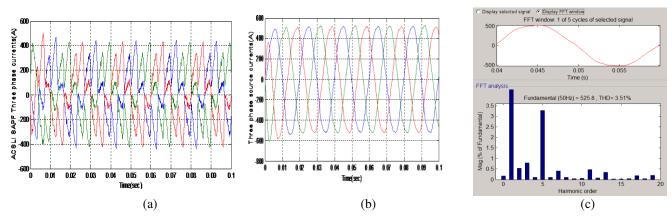

The three phase compensating currents of ACSLI based SAPF shown in Fig. 10(a) are effectively compensated the load current harmonics and the source current approached sinusoidal as shown in Fig. 10(b). The THD in source current of phase-a is reduced from 12.4% to 3.51% as shown in Fig.10(c). The ACSLI based SAPF successfully filtered the harmonic current components caused by the nonlinear load. Although the high frequency harmonic components are filtered significantly, appreciable amount of lower order harmonics (5<sup>th</sup>, 7<sup>th</sup>, 11<sup>th</sup>....) still remain in the source current spectrum. The most dominant are 5<sup>th</sup> and 7<sup>th</sup> order harmonics.

Fig. 10. (a)Three phase compensating currents of ACSLI based SAPF (b) Three phase source currents (c) Harmonic spectra of source current for Phase-a.

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Issue 10, October 2013

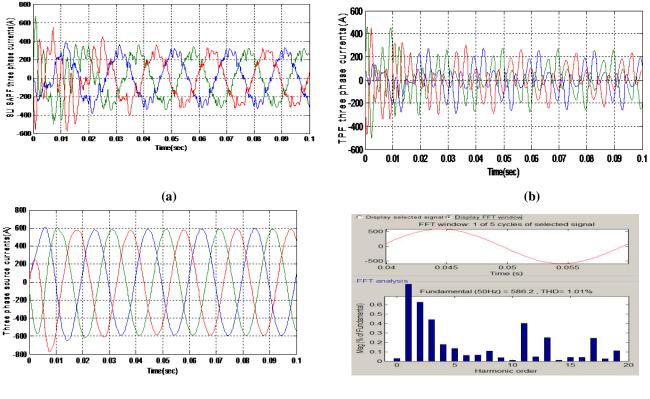

### C. Results of MVTS with proposed ACSLI based SHAPF Compensation

The three phase compensating currents of ACSLI based SAPF and TPF in SHAPF topology are shown in Fig. 11(a) and 11(b). Due to these compensating currents source current became sinusoidal as shown in Fig. 11(c) and its THD is reduced to 1.01% as shown in spectra plot of Fig. 11(d).

(c)

(d)

Fig. 11 (a) Compensating three phase currents of ACSLI based SAF (b)Tuned passive filter currents (c) Source current and (d) Harmonic spectrum of source current for Phase-a.

The source current THDs with ACSLI based SAPF and ACSLI based SHAPF compensations with different shunt passive filters are compared in Table II.

|                                                       | THD <sub>i</sub> (%)             |                 |                 |                 |

|-------------------------------------------------------|----------------------------------|-----------------|-----------------|-----------------|

|                                                       |                                  | I <sub>sa</sub> | I <sub>sb</sub> | I <sub>sc</sub> |

| V                                                     | 12.4                             | 12.4            | 12.4            |                 |

| With A                                                | 3.51                             | 3.28            | 3.44            |                 |

| With proposed<br>ACSLI based<br>SHAPF<br>compensation | With single tuned passive filter | 1.01            | 1.29            | 1.25            |

|                                                       | With double tuned passive filter | 2.09            | 2.04            | 2.01            |

|                                                       | With High pass passive filter    | 1.84            | 1.83            | 1.84            |

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Issue 10, October 2013

### V. CONCLUSIONS

The SRFT based compensating current estimator worked effectively in estimating compensation current and CSFSHPWM produced switching signals for ACSLI to produce seven levels in the output voltage. Based on the results, the proposed SHAPF topology is capable of responding effectively to the harmonics caused by the three-phase diode rectifier load and compensated the harmonics effectively. The total harmonic distortion of the source current without any compensation is 12.4 % in each phase and it is reduced to 3.51% with ACSLI based SAPF and to 1.01% for phase-a with proposed ACSLI based SHAPF compensation which is fairly good. Thus the performance of SAPF is improved by connecting shunt passive filters in the proposed ACSLI based SHAPF topology.

#### REFERENCES

- [1]. N.S. Choe and J.G. Cheo, "A General Circuit Topology of Multilevel Inverter", in IEEE-PESC 91 Conference Record, 1991, pp.96-103.

- [2]. T. A. Meynard and H. Foch, "Multi-Level Conversion: High Voltage Choppers and Voltage-Source Inverters", in Proceeding of Power Electronics Specialists Conference (PESC '92), 1992, vol. 1, pp.397–403.

- [3]. M. Marchesoni, M. Mazzucchelli, and S. Tenconi, "A Nonconventional Power Converter for Plasma Stabilization", *IEEE Transactions on Power Electronics*, vol. 5, no. 2, 1990, pp. 212–219.

- [4]. G. Miguel Lopez, T. Luis Mortin, C. Jose Espinoza and R. Juan Dixon, "Performance Analysis of A Hybrid Asymmetric Multilevel Inverter for High Voltage Active Power Filter Applications", in Proc. of IEEE Industrial Electronics Society Annual Conference, 2003, pp. 1050-1055.

- [5]. Du Zhong, L. M. Tolbert, J. N. Chiasson and B. Ozpineci, "A Cascade Multilevel Inverter using a Single dc Source", in *Proceeding of Applied Power Electronics Conference and Exposition (APEC '06)*, 2006, pp. 426–430.

- [6]. Z. Du, L.M. Tolbert and J.N. Chiasson, "Active Harmonic Elimination for Multilevel Converters", *IEEE Trans. on Power Electronics*, Vol.21, No.2, March 2006, pp.459-469.

- [7]. D. Chen and S. J. Xie, "Review of Control Strategies Applied to Active Power Filters", *Proceedings of the IEEE International Conference on Electric Utility Deregulation, Restructuring and Power Technologies (DRPT)*. April 5-8, 2004. Hong Kong: IEEE. 2004, pp. 666-670.

- [8]. Z. Du., et.al., "Reduced Switching Frequency Active Harmonic Elimination for Multi Level Converters", *IEEE Trans. on Ind. Electronics*, Vol. 55, No. 4, 2008, pp.1761-1770.

- [9]. B.P. McGrath and Holmes, "Multicarrier PWM Strategies for Multilevel Inverter," *IEEE Transactions on Ind. Electronics.*, vol.49, no.4, Aug.2002, pp.858-867.

- [10]. RoozbehNaderi, and AbdolrezaRahmati, "Phase Shifted Carrier PWM Technique for General Cascaded Inverters," IEEE Transactions on Power Electronics, Vol.23, No.3, May 2008, pp.1257-1269.

- [11]. P. Karuppanan and M. Kamala Kantha, "PLL with PI, PID and Fuzzy Logic Controllers based Shunt Active Power Line Conditioners", *IEEE PEDES-International Conference on Power Electronics Drives and Energy Systems*, 2010.

- [12]. J. C. Das, "Passive Filters Potentialities and Limitations", IEEE Trans. on Industry Applications, 40(1), 2004, pp. 232-241.

#### BIOGRAPHY

*G.Jayakrishna* received B.Tech, M.Tech and Ph.D degrees in Electrical Engineering from Jawaharlal Nehru Technological University, Anantapur, India in 1993,2004 and 2013 respectively. Currently he is with department of Electrical and Electronics Engineering, Siddharth Institute of Engineering and Technology, Puttur, India. His research interests include Power Quality, Electrical drives and Power Systems.

**B.Vamsipriya** received B.Tech degree in Electrical and Electronics Engineering from Jawaharlal Nehru Technological University, Anantapur, India in 2012. Currently she is pursuing M.Tech (Power Electronics) in Siddharth Institute of Engineering and Technology, Puttur, India.