Università degli Studi di Cagliari

## **DOTTORATO DI RICERCA**

## IN INGEGNERIA ELETTRONICA ED INFORMATICA

Ciclo XXIV

## **ELECTRONIC BIDIRECTIONAL INTERFACES TO THE PERIPHERAL NERVOUS SYSTEM FOR PROSTHETIC APPLICATIONS**

Settore scientifico disciplinare di afferenza ING-INF/01 (Elettronica)

Presentata da:

Caterina Carboni

Coordinatore Dottorato: Prof. Alessandro Giua

Tutor/Relatore:

Dr. Massimo Barbaro

Esame finale Anno Accademico 2010 - 2011

# Contents

| A   | knowledgements                                                                                | vii |

|-----|-----------------------------------------------------------------------------------------------|-----|

| In  | troduction                                                                                    | ix  |

| 1 N | eural-machine interfaces                                                                      | 13  |

| 1.1 | Motivation and Project Description                                                            | 13  |

| 1.2 | Neural system                                                                                 | 14  |

|     | 1.2.1 Neural cells                                                                            | 15  |

|     | 1.2.2 Neural signal generation in biological cells                                            | 16  |

|     | 1.2.3 Nerve structure                                                                         | 19  |

| 1.3 | Implantable nerve electrodes                                                                  | 19  |

|     | 1.3.1 Cuff electrodes $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 20  |

|     | 1.3.2 Longitudinal electrodes                                                                 | 21  |

|     | 1.3.3 Penetrative electrodes                                                                  | 21  |

|     | 1.3.4 Regenerative electrodes                                                                 | 22  |

| 1.4 | Implementation issues                                                                         | 24  |

|     | 1.4.1 Neural recording issues                                                                 | 24  |

|     | 1.4.2 Neural stimulation issues $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$            | 26  |

| 1.5 | State of art                                                                                  | 27  |

|     | 1.5.1 Neural recording and stimulation systems                                                | 27  |

|     | 1.5.2 Patch clamp circuits for Ion channel current detection .                                | 38  |

|     | eural recording and stimulation: a COTS device                                                | 47  |

| 2.1 | O I                                                                                           | 47  |

| 2.2 | 0                                                                                             | 49  |

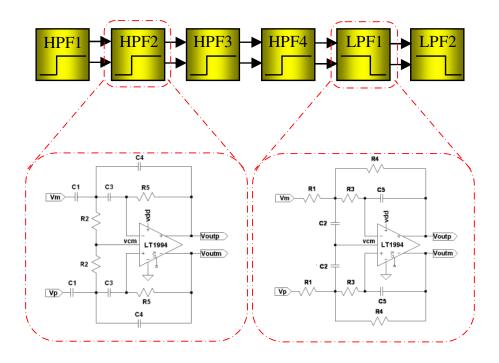

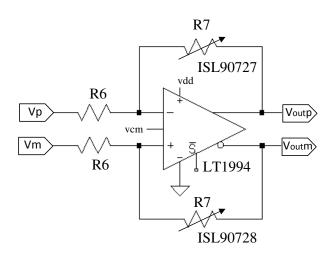

|     | 2.2.1 Recording unit                                                                          | 50  |

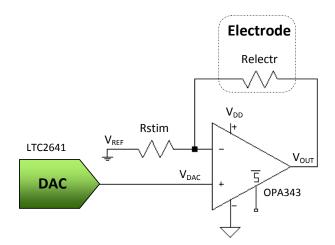

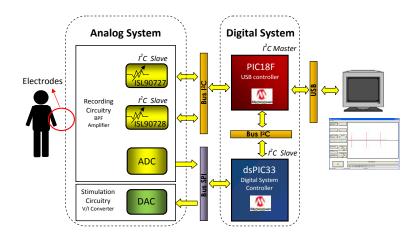

|     | 2.2.2 Stimulation unit                                                                        | 52  |

|     | 2.2.3 Digital control unit                                                                    | 53  |

| 2.3 | 1 0                                                                                           | 54  |

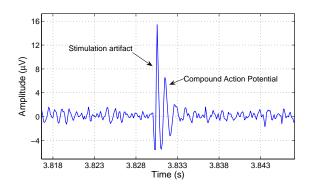

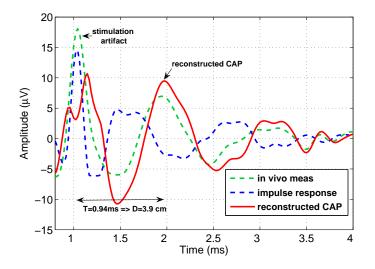

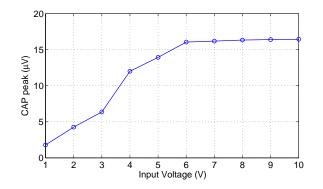

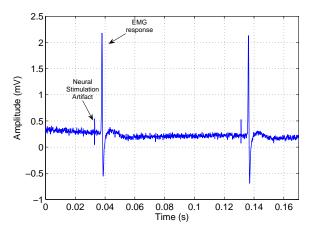

|     | 2.3.1 Recording mode                                                                          | 56  |

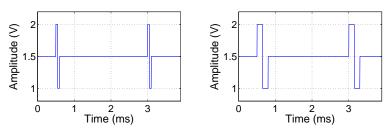

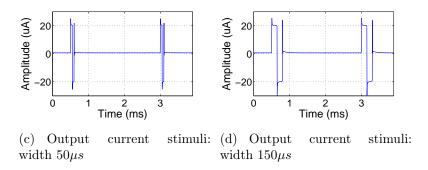

|     | 2.3.2 Stimulation mode                                                                        | 56  |

|          |      | 2.3.3 Stimulation-Recording mode                                                                                                                           | 57 |

|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|          |      | 2.3.4 Impedance measurement mode                                                                                                                           | 57 |

|          |      | 2.3.5 Test mode                                                                                                                                            | 58 |

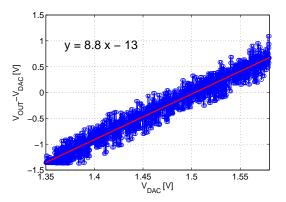

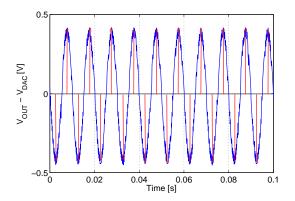

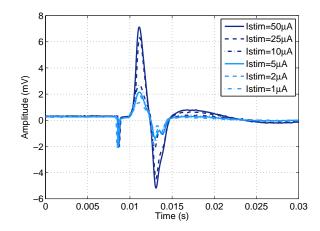

|          | 2.4  | Experimental results                                                                                                                                       | 59 |

|          |      | 2.4.1 Electrical tests                                                                                                                                     | 59 |

|          |      | 2.4.2 In-vivo tests $\ldots \ldots \ldots$ | 65 |

|          | 2.5  | Results discussion                                                                                                                                         | 72 |

| 3        | An   | Integrated Circuit for neural signal acquisition 7                                                                                                         | 77 |

|          | 3.1  | Design Specifications                                                                                                                                      | 77 |

|          | 3.2  | System architecture                                                                                                                                        | 78 |

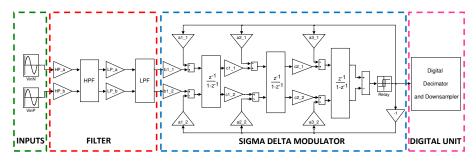

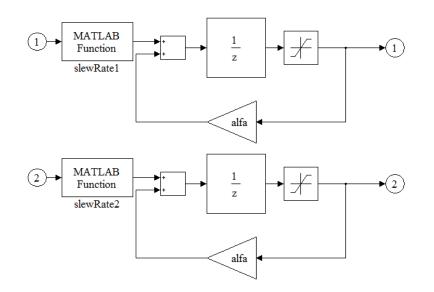

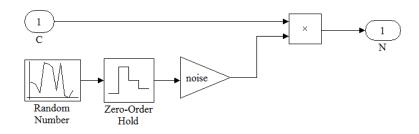

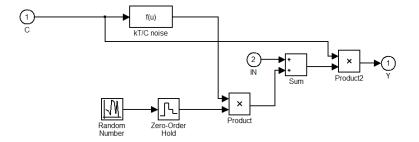

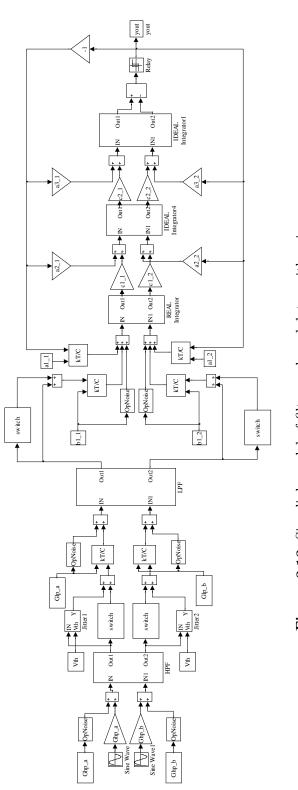

|          | 3.3  | Behavioral model design                                                                                                                                    | 79 |

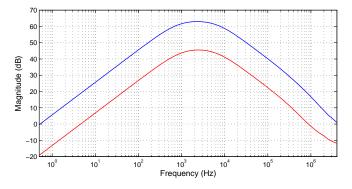

|          |      | 3.3.1 Filter behavioral model                                                                                                                              | 80 |

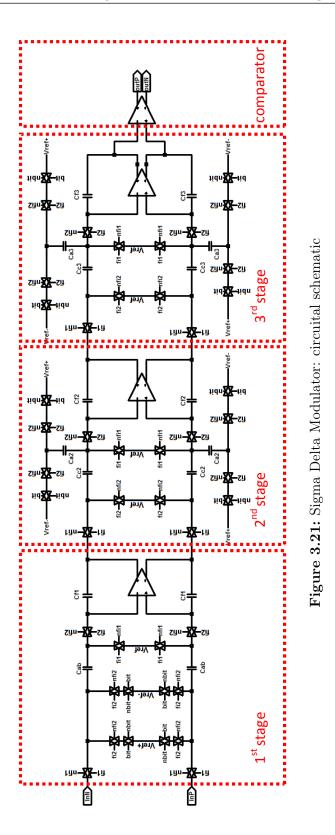

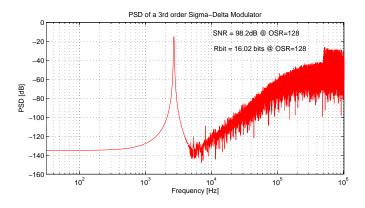

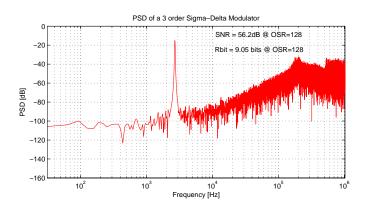

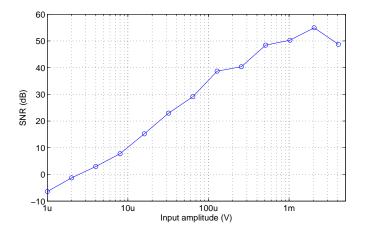

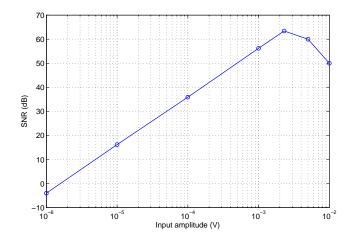

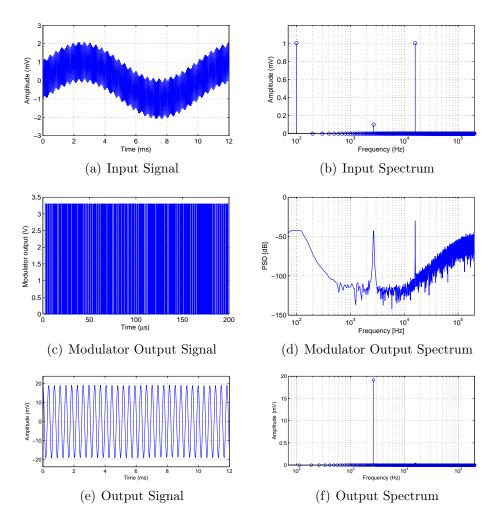

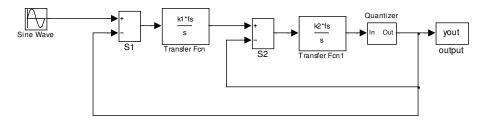

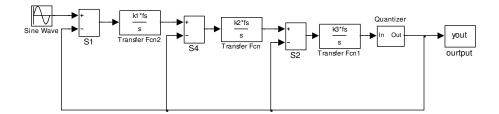

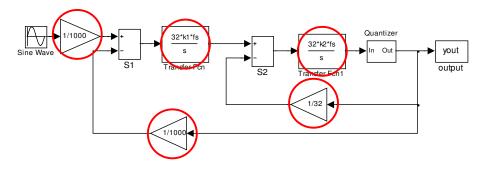

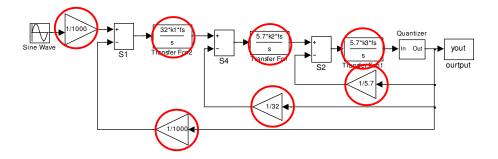

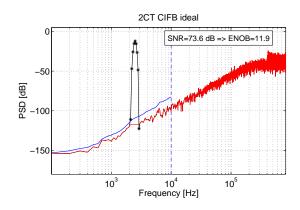

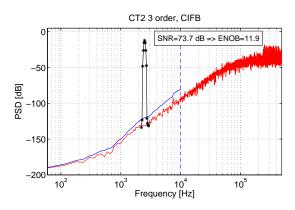

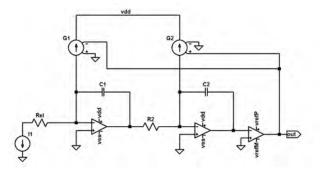

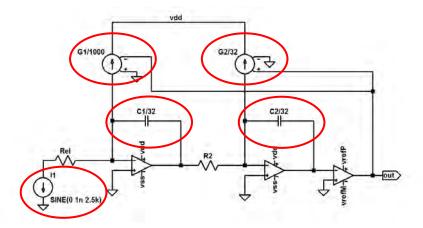

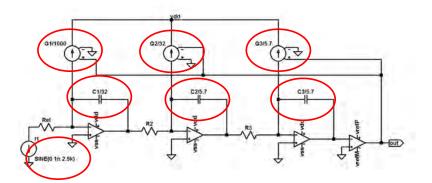

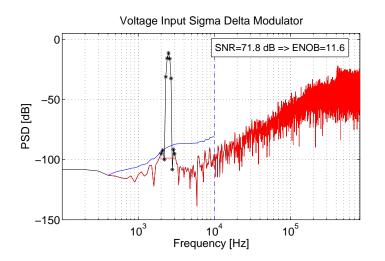

|          |      | 3.3.2 Delta Sigma modulator behavioral model 8                                                                                                             | 82 |

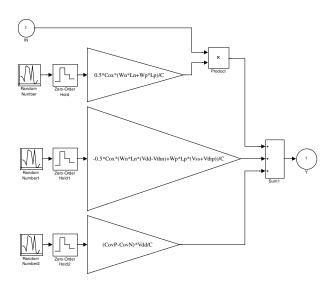

|          |      | 3.3.3 Noise sources behavioral models                                                                                                                      | 82 |

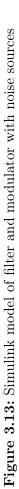

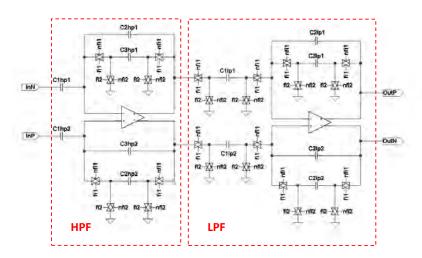

|          | 3.4  | Transistor level circuitry design                                                                                                                          | 90 |

|          |      | 1 0                                                                                                                                                        | 90 |

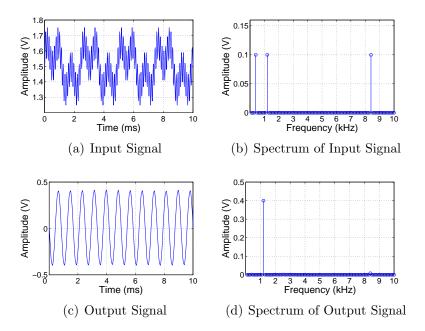

|          |      |                                                                                                                                                            | 92 |

|          | 3.5  | Experimental results                                                                                                                                       | 97 |

|          |      | 3.5.1 Behavioral simulation results                                                                                                                        | 97 |

|          |      | 3.5.2 Transistor level simulation results                                                                                                                  | )0 |

| <b>4</b> | Ion  | channel readout interfaces based on patch-clamp circuits11                                                                                                 | 1  |

|          | 4.1  | Design specifications                                                                                                                                      | 11 |

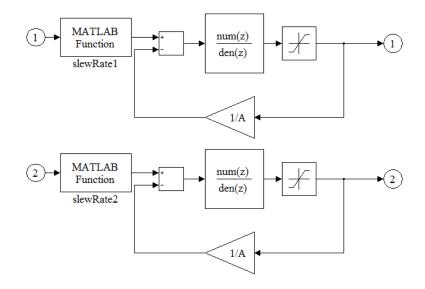

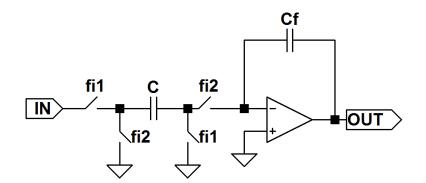

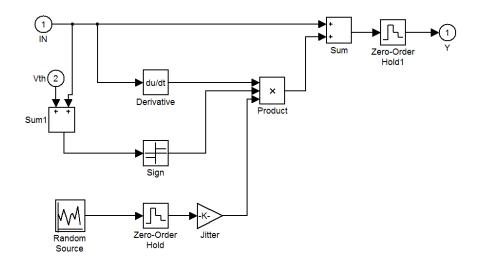

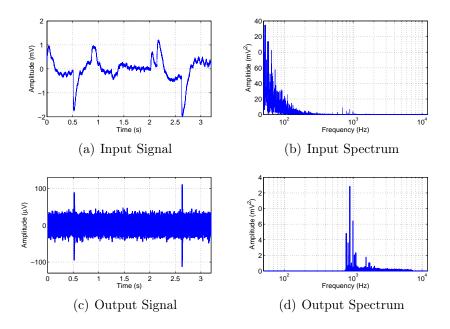

|          | 4.2  | Simulink behavioral model                                                                                                                                  | 13 |

|          | 4.3  | VerilogA behavioral model                                                                                                                                  | 15 |

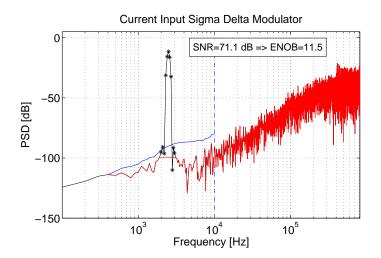

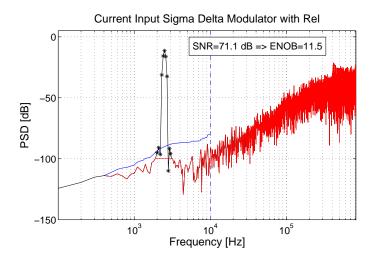

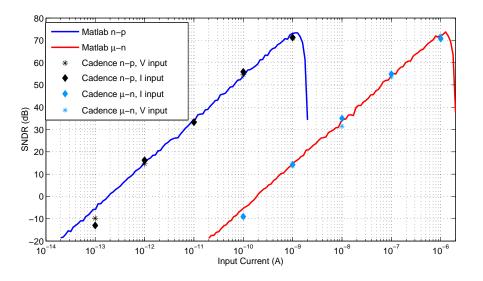

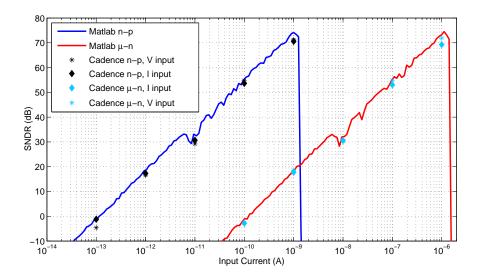

|          |      | 4.3.1 From voltage to current mode sigma delta modulator . 11                                                                                              | 16 |

|          |      | 4.3.2 Circuit sizing                                                                                                                                       | 19 |

|          | 4.4  | Experimental results                                                                                                                                       | 19 |

|          | Cor  | nclusions 12                                                                                                                                               | 27 |

|          | List | of figures 13                                                                                                                                              | 32 |

|          | List | of tables 13                                                                                                                                               | 34 |

## Acknowledgements

I apologize with those who will not be able to understand these lines, but I want to say thanks to everyone in his own language.

Potrà sembrarvi strano ma in questi ringraziamenti non troverete il vostro nome, per dire il vero di nomi non ne troverete affatto. Ho scelto così un po' per rendere queste righe meno noiose e un po' per comodità, perché non voglio rischiare di dimenticare nessuno. Sono comunque convinta che nessuna delle persone che, nei modi più vari, hanno contribuito a questa tesi, avrà difficoltà a riconoscersi nelle parti che la riguardano.

Grazie dunque a chi mi ha guidato in questi anni e mi ha consentito di arrivare fin qui. Grazie per avermi dato fiducia, permettendomi di lavorare ad un argomento affascinante, in cui credo, e che avrei riscelto ogni giorno tra mille altri possibili. Grazie davvero, per la pazienza, per i preziosi consigli e per l'esempio di ogni giorno. Grazie a tutti quelli che hanno lavorato con me, fianco a fianco allo sviluppo di questo progetto, sapete bene che il lavoro descritto in questa tesi e i risultati raggiunti sono tanto miei quanto vostri.

Grazie a tutti quelli che hanno condiviso con me questi anni all'EOLAB. Grazie ai compagni (almeno un paio di voi rabbrividiranno per l'uso di questo termine) dei mille SCRUCCHI in mensa, di pasti da sparviero, di insalate di riso al web e di panini da chicco. Grazie per le risate interminabili e le lunghe chiacchierate. Senza di voi questi anni sarebbero stati decisamente più PIWERI.

Dank denen, die mich in einem fremden Land aufgenommen, mich in einem neuen Projekt-gefahren und mich jeden Tag, sechs Monate lang, mit Leidenschaft und Begeisterung beispiellos ermutigt haben. Dank an allen den Erasmus-Freunden: für die viele schöne Tage, die wir zusammen verbracht haben, die Ausflüge am Samstag, das Schnitzel vom Tacheles, die Spaziergänge auf den Schlossberg, aber vor allem für die Mission "blaue Brücke", die eine unauslöschliche Erinnerung für mich bleiben wird.

Grazie a chi ha condiviso con me ogni momento della stesura di questa tesi grazie davvero perché con te è stato tutto più semplice a questo punto immagino penserai che stia ringraziando latex invece ti stupirò lo dico qui in un documento ufficiale word non é poi cosi male. Manca qualcosa a questa parte? Ah si le virgole ma sai bene che non ne sono capace as a consequence le dovrai mettere tu :D

Grazie a tutti quelli che hanno iniziato con me l'università come colleghi, e che negli anni sono diventati amici preziosi e sinceri, con i quali ho condiviso ben più di lezioni ed esami. È soprattutto grazie a voi se gli anni dell'università sono stati in assoluto gli anni più belli. Su tutti, un posto speciale é per chica e chica, sapete che siete per me come sorelle e che mi basta essere con voi per sentirmi a casa ovunque nel mondo.

Grazie a tutte le altre amiche che, pur non avendo preso parte direttamente a quest'avventura, ne sono state sempre partecipi. A chi mi ha accompagnato in interminabili e frequentissime camminate senza una meta precisa, e a chi mi ha regalato mille risate e tanto buonumore con chiacchierate senza fine sia dal vivo, sia su fb quando, spesso, le distanze non ci consentivano di vederci.

Infine, un grazie speciale a chi ha creduto in me da sempre ("io non credo che non ce la puoi fare..." "vae, puite no andas?"), incoraggiandomi costantemente e dandomi supporto in  $anni^{18}$  (che nerd che sono) di studio, su tutti i fronti, non facendomi mancare mai niente... (soprattutto in frigo :D). Grazie a chi mi ha lavato, stirato, cucinato in questi  $anni^{11}$  qui a Cagliari, standomi vicino sempre (anche un po' troppo...) e con lo scatto alla risposta sempre pronto. Grazie a chi avrebbe voluto comprarmi il còmputer (leggi come è scritto) ma è dovuto andar via prima del previsto, grazie a chi ogni mattina mi dava il buongiorno, anzi il buongiornissimo. Grazie alla zia migliore del mondo, che è sempre disponibile, qualunque cosa io le chieda, e che ha sempre colmato nel migliore dei modi le mie mancanze. Siete il migliore esempio che possa avere e il mio punto di riferimento sempre.

## Introduction

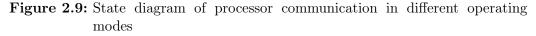

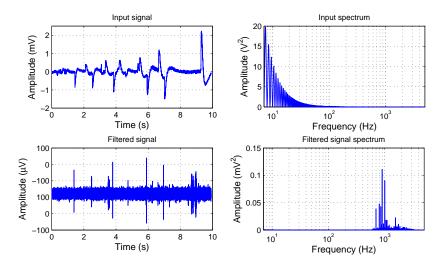

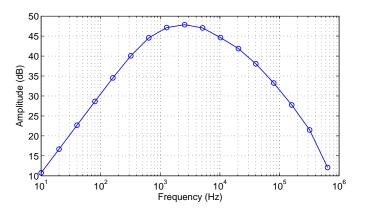

Human beings have always been fascinated by the sophisticated and intricate nervous system that regulates and coordinates our organism. The possibility to extract and elaborate the information generated by the brain is a gripping idea that has inspired a lot of science-fiction writers and movie directors over the years. Obviously, the possibility to "read minds" is still confined in the science-fiction field, but combining together the impressive advancements in microelectronics, robotics and biomaterials achieved in last decades, many of those ideas thought to be impossible to fulfill up to ten years ago, are now closer to become reality. One of these subjects is the possibility to extract neural signals from the Peripheral Nervous System (PNS) and to use them outside of the human body: this is precisely the goal of the present thesis. The final aim of the project in which this work is involved is in fact the realization of a prosthetic hand controlled using neural signals. In particular in this thesis the focus has been put on the development of special electronic devices for neural signal acquisition and PNS stimulation. The commercially available prosthesis are based on Electromyographic (EMG) signals, their use implies unnatural movements for the patient that needs a special training to develop the control capabilities over the mechanical limb. The proposed approach offers a number of advantages compared to the traditional prosthesis, first because the signals used are the same used to control the biologic limb, allowing a more comfortable solution for the patient that will be closer to feel the robotic hand as a natural extension of his/her body. Secondly, placing temperature and pressure sensors on the limb surface, it is possible to trasduce such information in an electrical current that, injected into the PNS, can restore the sensory feedback in amputees. The weakness of the neural signals (neural spike amplitudes can span from few microvolts to hundreds of microvolts) makes their recording a critical operation and requires special care in terms of low noise and low power design. Neural spike bandwidth lies in the frequencies from 500Hz to 10kHz with a peak around 2kHz and it partially overlaps with that of EMG signals which have amplitudes several order of magnitude higher than that of neural signals.

EMG signals are, for this reason, the most serious interference to cope with. Fortunately the spectral signature of EMG decreases with frequency and, at 800Hz has an energy lower than that of neural signals. Using a proper filter stage in the front-end circuit, it is then possible to isolate the neural signals and to prevent the EMG to mask them completely. On the other hand, the stimulation circuitry must provide current pulses whose amplitude, duration and frequency evoke the programmed stimulus without damaging the tissues. In this contest, our final goal is the development of a fully implantable device able to perform a bidirectional communication between the robotic hand and the patient. Due to small area, low noise and low power constraints, the only possible way to reach this aim is the design of a full custom Integrated Circuit (IC). However a preliminary evaluation of the key design features, such as neural signal amplitudes and frequencies as well as stimulation shape parameters, is necessary in order to define clearly and precisely the design specifications. A low-cost and short implementation time device is then needed for this aim, the Components Off The Shelf (COTS) approach seems to be the best solution for this purpose. A Printed Circuit Board (PCB) with discrete components has been designed, developed and tested, the information extracted by the test results have been used to guide the IC design.

In the first chapter an overview on the main characteristics of the neural cells and on the electrochemical processes involved in the neural spikes generation is presented. A brief description of the project in which this research is part is also provided, finally an analysis on the state of art concerning the neural-machine interfaces is presented.

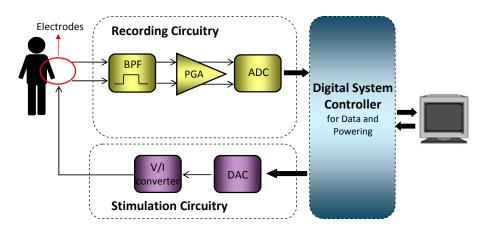

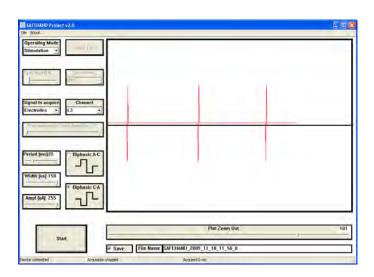

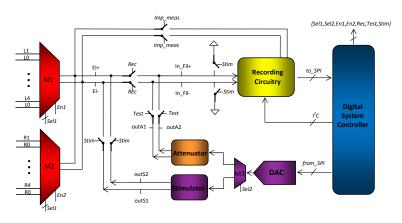

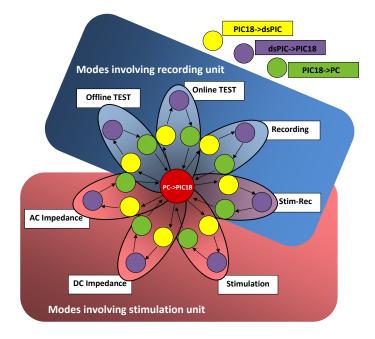

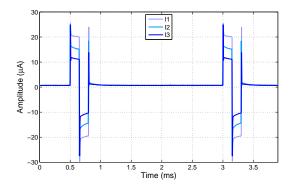

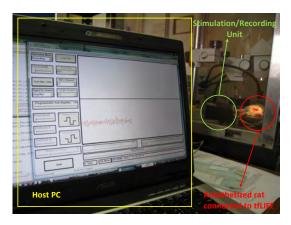

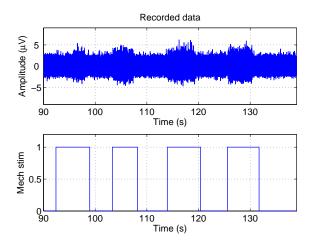

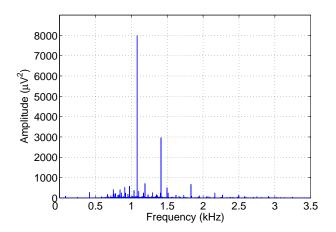

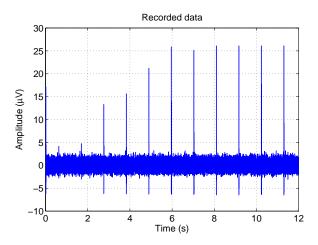

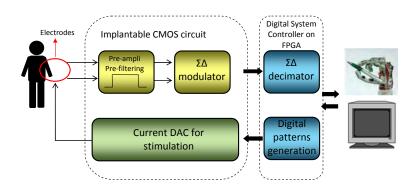

The second chapter is aimed to the developing of a PCB system for neural recording and stimulation. The proposed neural interface allows the bidirectional communication between an electrode inserted in the PNS and a host computer. The designed system is composed by three main blocks: the recording circuit, the stimulation unit and the digital system controller. The extracellular signals are extracted from a 8 channel electrode then they are acquired and filtered by a recording circuitry in order to remove noise and other biological interferences. The stimulation circuitry delivers trains of electrical charge pulses to excitable tissue, via the electrode. The system receives stimulus patterns from the digital controller and converts them into a stimulation current to be injected into the PNS. The digital system controller has two main tasks. First, it provides power from a rechargeable battery to ensure the isolation of the patient from the electric grid (both for safety reasons and to reduce the interferences injected by the grid). Main task of the module, however, is managing the configuration of the whole system with the generation of timing signals, programmable gain and stimulation patterns.

#### Introduction

For a high-speed real time data transmission a Universal Serial Bus (USB) controller has been integrated in the system. A Graphical User Interface, that allows the user to have a real time control on the acquisition and on the stimulation and to modify the programmable parameters, has also been developed. The system has been successfully tested with in-vivo experiments on rats performed at the "Universitat Autonoma de Barcelona" thanks to Prof. Xavier Navarro. The results confirmed the capability of the system to record neural signals of few microvolts and to provide stimulation patterns capable to elicitate the PNS of the rat. The design, implementation and testing of all the COTS system has been developed in close collaboration with Ing. Daniela Loi at the Department of Electrical and Electronic Engineering at University of Cagliari.

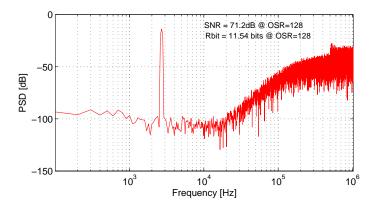

The third chapter presents an IC system for neural recording composed by the cascade of a preamplifier/ prefiltering block and a sigma delta modulator. The signal acquisition chain has been designed using two parallel models: a high level simulation model in Simulink environment has been used for a first rapid evaluation of the system properties and to define the needed specifications for each sub-module. Consequently, a transistor level simulation model, developed in cadence environment, describes precisely the circuit components and gives more reliable information on the specification meeting. The task of the preamplifier/prefiltering block is first to amplify the signal in order to avoid its corruption due to noise and secondly to attenuate the huge EMG interferences avoiding the amplifier saturation. The signal is then digitalized by a 10 bit resolution, third order, single loop, delta sigma modulator. The resulting 1 bit data stream is finally sent to the decimator and stored in the pc for further processing. First simulation results show a good agreement between the two models, and the capability of the system to record without corruption signals in the order of magnitude of few microvolts.

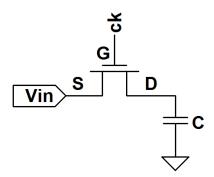

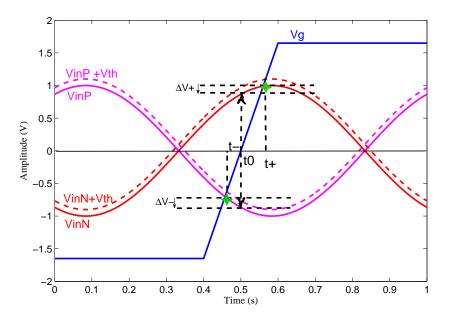

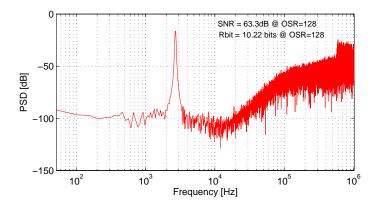

The system level implementation of a Read out circuit for ion channel current detection is discussed in the fourth chapter. This part of the work has been carried on during my permanence at the "Institut fuer Mikrosysthemtechnik" of the "Albert Ludwigs Universitaet " in Freiburg im Breisgau, under the supervision of Prof. Yannos Manoli and Dr. Matthias Keller. The generation of electrical signals in biological cells, such as neural spikes, is possible thanks to ions that move across the cell membrane. In many applications it is important, not only to record the spikes, but also to measure these small currents (their range varies from pA to  $\mu A$ ) in order to understand which electro-chemical processes are involved in the signal generation and to have a direct measurement of the ion channels involved in the reaction. Ion currents, in fact, play a key role in several physiological processes, in neural signal generation, but also in the maintenance of heartbeat and in muscle contraction. The traditional method used to measure these currents is called patch clamp and consists in fixing the external membrane potential to a control voltage and in recording the current that flows across the membrane using proper electronic devices. For this purpose, a current feedback delta sigma modulator has been developed in a high level behavioral model (verilogAMS in cadence environment).

## Chapter 1

# Neural-machine interfaces

At a first glance the biological world seems to be far away by the modern electronic equipments that surround our lives. A more detailed analysis can reveal how this impression is false and that the signals used by the cells to communicate with each other are electrical currents and voltages, exactly how it happens in electronics. This fact makes it possible, on one side, to read the biological signals flowing into the body and, on the other side, to apply electrical signals to the cells from the external in order to stimulate them restoring lost functionalities. It should be clear that the implementation of such interfaces has an enormous potential in the field of biomedicine and on the fight against a wide range of diseases. That is the reason why nowadays bioelectronics and human-machine interfaces are widely propelled and are subjected to a great deal of attention by scientists.

In this chapter a brief summary on biological cells and on the characteristics of electrical signals generated inside them is presented. A special attention is payed to neural cells and to the way in which neural signals are generated. The state of art concerning low noise electronic devices used to read such signals is finally discussed.

## 1.1 Motivation and Project Description

The work described in this thesis is part of two wider projects, called Safe-Hand ad OpenHand, funded within the PRIN initiative of Italian Ministry of Education, University and Research (MIUR), aimed at realizing a neurallycontrolled prosthetic hand able to provide appropriate, graded and distally referred tactile and proprioceptive sensations to the wearer. In this way, the artificial hand would be intuitively controlled and felt by the amputee as the natural one.

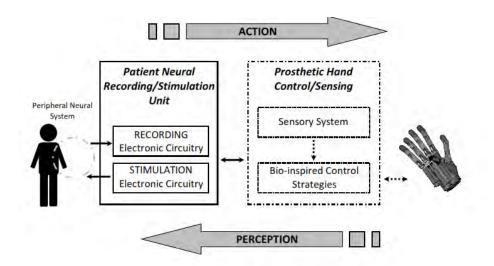

Figure 1.1: Safehand - Openhand project

To reach this aim, the platform shown in Fig. 1.1 was conceived. It consists of a recording and stimulation electronic system, a bio-mechatronic prosthetic hand and a bio-inspired control system (developed at ARTS Lab, Scuola Superiore Sant'Anna, Pisa, Italy and at Università Campus Biomedico, Rome, Italy). In such framework, special attention has been paid to the implementation of the electronic unit for conditioning the efferent bio-signals and generating the afferent signals in order to reach the final goal of the clinical evaluation of the platform on selected patients. This approach has several advantages with respect to commercially available solutions based on EMG signals, because the possibility to control the prosthesis with the thought clearly allows the patient to feel more conformable with the artificial limb. Nevertheless, also in the neural prosthetics there are several possible approaches, the one pursued in these projects takes advantage by signals acquired by means of intraneural electrodes, thus allowing a stronger signal detection compared with extraneural recordings and a better selectivity, since the electrode insertion inside the nerve permits to discriminate among the single nerve fascicles within the nerve.

## 1.2 Neural system

The neural system can be described as the infrastructure that allows the communication among the different parts of the body. It is divided into two main parts: the *Central Neural System (CNS)*, composed by the brain and the spinal cord, and the *Peripheral Neural System (PNS)* whose function is

to bring the signals elaborated in the CNS towards the rest of the body and viceversa. Due to the final aim of this thesis, the focus will be put overall on the PNS. It is composed by nerves fascicles, depending on the direction of the signal, the nerves are called motor nerves (the signal flows from the brain to the periphery), or sensor nerves (the signals acquired by the environment and transduced into electrical signals are forwarded to the brain). Afferent and efferent signals can also be transmitted on the same nerve, but in different cells.

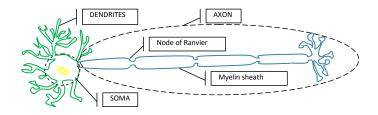

Figure 1.2: Neuron parts: Soma, Dendrites and Axon

#### 1.2.1 Neural cells

The cells that make up the neural system are divided in two classes: the neurons and the glial cells that give them structural support. A typical neuron of a peripheral nerve is shown in Fig. 1.2, it is composed by three main parts:

- *soma*: is the body cell and contains the nucleus.

- *dendrites*: are very thin branches that carry the signal from a connection with another neuron (synapsis) to the soma.

- *axon*: is the part that transports the signal from the soma to the next cell.

A neuron can have a lot of dendrites but only one axon that, in humans can reach lengths up to 1m. Axons play a key role in nerve signal propagation, the conduction is facilitated by the *Myelin sheath*, a special sheath that surrounds the neuron and shields the signal preventing its scattering outside the nerve. Moreover special interruptions of the sheath *Nodes of Ranvier* in which there is a concentration of Sodium-Potassium channels (see next paragraph) allow for a faster propagation called saltatory conduction.

### 1.2.2 Neural signal generation in biological cells

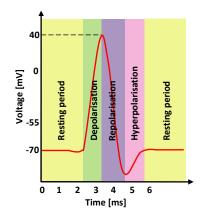

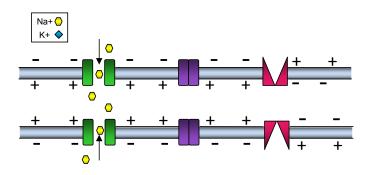

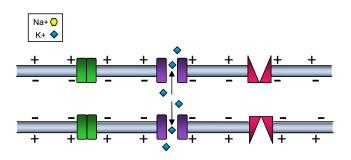

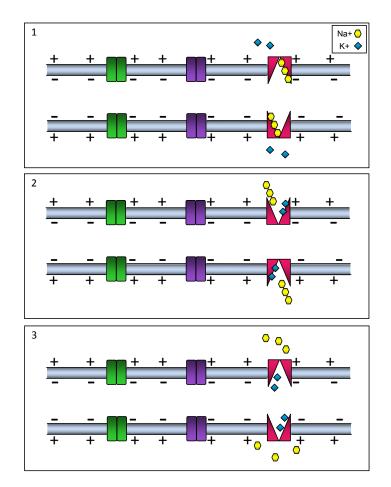

In Fig. 1.3 the shape of a classical neural spike is depicted, the changes of the voltage potential can be explained looking at the membrane cell configuration. In fact, the signal propagation across the nerve is possible thanks to the ion currents that flow across the cell membrane.

Figure 1.3: Action potential voltage spike

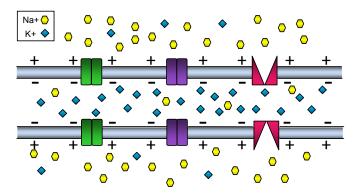

Inside the cell there is a major concentration of potassium ions (K+) while outside the Sodium (Na+) concentration is prevalent. In resting conditions the internal side of the membrane is more negative than the external creating a resting potential of -70mV (Fig. 1.4). When an over-threshold voltage stimulus (the threshold is around -55mV) is applied to the membrane the Sodium channels open, allowing the Sodium ions to enter inside the cell (Fig. 1.5), this causes the inside to become more positive that the outside increasing the membrane voltage up to 40mV (depolarisation phase), due to this change of polarity the potassium channels open and ions flow out of the cell (Fig. 1.6), by this way a negative potential is restored inside the cell (repolarisation phase). The Potassium channels are slower than the Sodium ones, for this reason the number of Potassium ions flowing from the inner to the outside is higher than that of Sodium ions flowing in the opposite direction, as a result a hyperpolarization phase occurs. To restore the resting potential the Sodium-Potassium pump is needed, by this way potassium ions are bring back to the inside and Sodium ions pushed out of the cell (Fig. 1.7). During this time interval, called refractory period, the action potential propagation is blocked. Note that the Sodium-Potassium pump is an active process because it moves ions against their gradients, so it requires energy to work that is provided by a coenzyme called Adenosine triphosphate (ATP).

Figure 1.4: Ion cells concentration in resting conditions

Figure 1.5: Cell membrane during depolarisation phase

Figure 1.6: Cell membrane during repolarisation phase

Figure 1.7: Cell membrane during hyperpolarisation phase

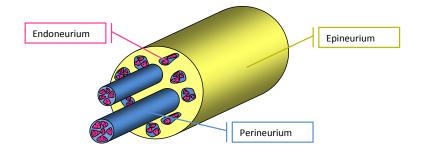

### 1.2.3 Nerve structure

Peripheral nerves consist of bundles of nerve fibers. Each group is surrounded and protected by a thick layer of dense connective tissue, called epineurium, which endures most of the mechanical tension applied to the nerve. The connective tissue layer wrapping the individual bundles, called perineurium, bears the elongation load. While the space between individual nerves fibers is filled by a delicate layer of loose connective tissue, the endoneurium. A schematic sketch of the nerve structure is shown in Fig. 1.8.

Figure 1.8: Peripheral nerve structure

## **1.3** Implantable nerve electrodes

In amputees and in patients with neural diseases, the biological structure described in 1.2 needs some help to communicate with the external. The electrodes represent the link between the biological tissues and sensing electronics. It is desirable to develop the communication in both directions. On one hand the device must allow to record neural signals, on the other hand to send stimulating signals from the external to the nervous system. Major properties for electrodes are selectivity and non-invasivity.

Selectivity plays a key role because of the nerve bundle structure. In the inner part of the nerve, there are several fascicles and each fascicle contains different axons, therefore the electrode must be able to isolate a single neural signal from the other electrical activities around it. In this way, with electrodes placed close to neural fibers, it becomes possible to record a stronger signal, improving Signal to Noise Ratio (SNR). From the patient point of view, it is suitable to minimize invasivity. These two requirements are clearly in contrast. In fact, if the aim is to have a high selectivity, than it is necessary to increase invasivity inserting the electrode into the body (non superficial electrode) or even within the nerve (intraneural electrode). In these years several categories of electrodes have been developed, they can be divided in two categories: extraneural (i.e cuffs) which are less selective but also less invasive, and intraneural (longitudinal, penetrative and regenerative) which are preferred for their better selectivity but imply a higher invasivity. A brief summary on the main electrode types is presented in the following.

## 1.3.1 Cuff electrodes

Among extra-neural electrodes the more used are cuff electrodes. As depicted in Fig. 1.9, they are a cylindrical wrapping that envelops the nerve from the outside.

Figure 1.9: Cuff electrode

Electrical contacts are placed in the inside, in this way the recorded signal is as strong as possible. There are two main sorts of cuffs: split-cylinder and spiral cuff. The first ones have the shape of a semi-open cylinder and must be closed around the nerve with suture, this makes them uneasy to implant. It would be also suitable to have an electrode with an adaptable diameter; a too large section will produce a neural signal too weak whereas a device too tight may cause nerve diseases. In order to overcome these problems spiral cuffs have been introduced. They are fabricated with a stretch sheet that allows the electrodes to follow the nerve shape [1]. The advantage of cuffs compared to the others extraneural electrodes is the precision with which they can be placed around the nerve. The placement of the contact in the inside of the cylinder means that stimulation can occur with lower current than those used in other extraneural electrodes. The main drawback of extraneural electrodes is their low selectivity. In fact, being wrapped around the nerve, they record the whole electrical activity of the nerve which is the sum of all axonal signals. Moreover, in order to reach afferent axons from outside, they must provide high stimulation currents with respect to the intraneural ones. For these reasons electrodes able to penetrate the nerve have been introduced.

### 1.3.2 Longitudinal electrodes

Longitudinal electrodes get the name from their insertion way and are often indicated as LIFE (Longitudinal Intra-Fascicular Electrodes). In fact they are implanted throughout perinervium and placed, parallel to the axe of nerve, inside the nervous fascicles. They host multi-active sites composed of a thin conductor wire made of Platinum-Iridium or fabricated with metalized Kevlar fibers, covered with an insulating sheath. Multi-channel structures allow understanding better the signal propagation along the nerve. LIFEs drawbacks regard their radial symmetry [2], since the fixed distance between electrode and nerve limits selectivity. Moreover the electrode stiffness causes micro-movements that, in the long term, may damage the nerve.

Figure 1.10: tfLIFE electrode

The thin film Longitudinal Intra-Fascicular Electrode is an evolution of LIFE that overcomes these problems. It is composed of a double sided structure with contacts dislocated in different parts of the electrode. Its flexible structure allows a better adaptation to the nerve shape preventing all damages due to an excessive stiffness. The need for electrodes able to move within the nerve, approximating the electrical contacts to nervous fibers, have brought to a new generation of tfLIFEs based on Shape Memory Alloy (SMA) materials. A serpentine shape can be memorized in the SMA, placing electrical contacts in the crests of serpentine. In this way, when the electrode reaches a determined temperature, its shape can be modified and active sites moved closer to the axon [3]. An interesting application of tfLIFEs is in neural prosthesis development.

## **1.3.3** Penetrative electrodes

Penetrative electrodes are constituted of an array of needles attached to a rigid support (Fig. 1.11). In their simplest configuration they are called shaft

electrodes and they are composed of only one needle. Structures with many electrodes are called MEA (Multi Electrode Array), a widely used version of MEAs has been developed at Utah University and it is called UEA (Utah Electrode Array) [4].

Figure 1.11: MEA electrode

Penetrative electrodes were used primarily in the CNS, but there are also applications related to PNS although their stiffness and their difficult implantation does not make them particularly suitable for this purpose. When the electrode is used in CNS, needle can penetrate trough the skin in the skull reaching cerebral neurons. In the PNS, needles penetrate within nervous fascicles, implantation is facilitated by pneumatic insertion techniques that, increasing insertion velocity, allow preserving nerve integrity [5]. Recent studies show that a valid alternative, that can guarantee a better mechanical stability and a high biocompatibility, is in implementing MEAs with carbon nanotubes. Tests demonstrate that impedance in this electrode is one to two orders of magnitude smaller than that measured using traditional MEAs, thus significantly improving the performance of neural electrode [6]. Electrodes array have been used in numerous applications, implanted within acoustic nerve for auditory function restoring [7] and in the skull for recording brain signals in animals and also implanted in humans for robotic limb control [8].

#### 1.3.4 Regenerative electrodes

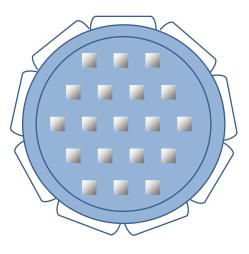

The last electrode that will be analyzed is regenerative electrode or sieve electrode. These electrodes are inserted in the nerve transversally and are shaped as a grid that can be either circular or square, a schematic example is shown in Fig. 1.12.

Figure 1.12: Sieve electrode

Neural fibers may regenerate through the holes of the grid hence the name of regenerative electrode. Active sites are situated around the holes, thus they can reach single axons, making them the more selective among all electrodes presented. A crucial issue in sieve electrodes fabrication is the number and the dimension of vias. Different studies demonstrate that too small vias can inhibit neural tissue regeneration. On the other hand increasing diameter, the distance between vias increases leading to an excessive deflection of neural fibers with a consequently difficulty in neural tissue regeneration. A good compromise seems to be the fabrication of electrodes with a diameter range from  $45\mu m$  to  $60\mu m$  [9]. In the case of prosthesis control, it is useful to divide electrode in reference areas contacting different vias with the same electrical contact, to record specifics neural patterns [10]. The implementation of multi-via electrodes (some sieves contain 800 vias) is facilitated by the introduction of polyamide electrodes. This material is more flexible than silicon and allows to reduce risk of nerve diseases during implantation. Moreover the high biocompatibility degree of polyamide permits longer time implantation than that of silicon [11]. The main advantages of sieve electrodes are their high selectivity and the stability of the electrode-tissue interface once that the neural tissue regeneration has occurred. Drawbacks are their high invasivity and the fact that neural signal cannot be recorded until regeneration is completed and this process takes at least 12 weeks. The high invasivity of sieves has not yet allowed their implantation on humans, however encouraging experiments have been carried out on frogs, rats and fishes [9].

## **1.4** Implementation issues

The neural signals weakness makes their recording a critical operation and requires special care in terms of low noise and low power design. On the other hand, the stimulation circuitry must provide current pulses whose amplitude, duration and frequency evoke the programmed stimulus without damaging the tissues (in muscles, for instance, a heating corresponding to only  $80mW/cm^2$  can cause necrosis [12]). As it can be easily understood, there are several issues to take into consideration during the design, in this section a brief discussion on the main problems related to neural-machine interfaces is presented.

### 1.4.1 Neural recording issues

As displayed in Fig. 1.3, the neural spikes measured in the cell membrane have an amplitude of 70mV, the surrounding layers shield the signal, and this causes a radial drop of its amplitude. Nevertheless, the signal can still be detected, but its weakness makes it necessary to introduce in the readout circuit special techniques for low noise design. Amplitudes outside the epineurium can be lowered down to  $1\mu V$  [13], while typical amplitudes for intraneural signals range from tens to hundreds of microvolts [14, 15]. Neural spikes bandwidth lies in the frequencies from 500Hz to 10kHz with a peak around 2kHz and it partially overlaps with the *Electromyographic signals* (EMG) which have amplitudes several order of magnitude higher than that of neural signals. EMG interferences are, for this reason, the most serious interferences to cope with. Fortunately the spectral signature of EMG decreases with frequency and, at 800Hz has an energy lower than that of neural signals [13, 16]. Using a proper filter stage in the front-end circuit, it is then possible to isolate the neural signals and to prevent the EMG to mask them completely.

In addition to the biological interferences, also the noise due to the electronic devices must be considered. The main noise contributions are flicker noise and thermal noise. Flicker noise is inversely proportional to the frequency (it is also called 1/f noise), and plays a key role in low frequency applications. In a MOS transistor it can be modeled as a voltage source in series with the MOS gate given by 1.1, where  $K_f$  is a constant depending on process parameters:

$$\overline{V_{n,flicker}}^2 = \frac{k_f}{WLC_{ox}} \cdot \frac{1}{f}$$

(1.1)

Equation 1.1 shows that flicker noise is reduced if wide area transistors are

used. Physical causes of Flicker noise are not well known, the phenomena has been explained with charge fluctuation at oxide-semiconductor interface due to presence of traps. As the p-conduction occurs in depth while n-conduction is superficial, very close to the interface with the oxide, PMOS devices exhibit less flicker noise than NMOS ones. The thermal noise expression is given by equation 1.2, where  $\gamma$  represents the channel length modulation effect.

$$\overline{V_{n,th}}^2 = \frac{4KT\gamma}{g_m}\Delta f \tag{1.2}$$

The noise is reduced when  $g_m$  increases [17]. In terms of MOS size, this means that a large and short channel MOS minimizes thermal noise. A useful parameter for the evaluation of flicker noise incidence with respect to thermal noise is the corner frequency. It is the frequency at which flicker noise and thermal noise give the same contribute to the circuit. It can be calculated equating 1.1 and 1.2, obtaining 1.3.

$$f_{corner} = \frac{K_f}{WLC_{ox}} \frac{3}{8KT} g_m \tag{1.3}$$

Input Referred Noise (IRN) is the most widely used parameter to estimate the effect of noise in a circuit. It resumes all noise sources into a single voltage noise source, placed at the input of the amplifier. By this way it is immediate to understand how much noise is degrading the input signal. A key role in neural signal acquisition is also played by low powering. Since the tendency is to acquire more signals simultaneously, the use of more amplifiers is required, causing the power reduction available for each of them. Unfortunately low-noise and low-power designs are in contrast since power scales as  $1/(V_{noise})^2$  [18]. For this reason, the major effort of researchers is to find a good compromise between these two crucial issues. Noise Efficiency Factor (NEF) is an indicator used to compare the power-noise performances of different amplifiers. It has been introduced in [19] and describes how many times the noise of a system, with the same current drain and bandwidth, is higher compared to the ideal case. Its value is given by 1.4.

$$NEF = V_{rms,in} \sqrt{\frac{2 \cdot I_{tot}}{\pi \cdot U_t \cdot 4kT \cdot BW}}$$

(1.4)

The minimum value for NEF is reached by an amplifier with a single bipolar transistor, in this case without considering flicker noise, NEF = 1. Basically all practical circuits have higher values [14]. Amplifiers with lower NEF can achieve the same IRN with lower power dissipation [20].

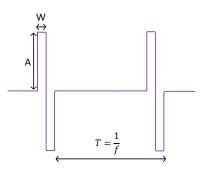

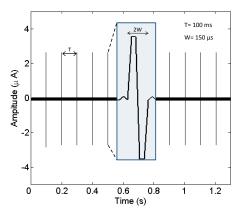

### 1.4.2 Neural stimulation issues

The ability to supervise the effects of stimulating neural tissue is essential in neuroscience research since it allows to study the function of the nervous system. In particular, the ability to provide a controlled application of electrical signal to specific afferent nerves (Functional Electrical Stimulation or FES), enables to restore and to enhance neural functions in people with nervous system dysfunctions. Examples of useful stimulation applications include clinical treatment of epilepsy, tremors associated with Parkinson's disease, retinal and cochlear implants and multiple sclerosis [21–24]. The stimulation system must be capable of generating a wide range of electrical signals for nerve stimulation via implantable nerve electrodes. From an electrochemical point of view when the stimulation signal is provided, a charge transfer between the electrons in the metal electrode and the ions in the biological tissue is created. The ionic flow can be induced by two primary mechanisms, the capacitive and the Faradaic reaction. In the first one no electron transfer occurs, just a redistribution of charged chemical species in the tissue. While during the second mechanism, an exchange of electrons across the electrode-tissue interface is involved, resulting in reduction or oxidation of some chemical species. A Faradaic process can be classified as reversible or irreversible depending on the rate of electrons transfer at the interface. A reversible Faradaic reaction is characterized by fast kinetics, this allows to achieve large currents with small potential excursions away from equilibrium. Moreover, since the reaction takes place near the electrode surface, by passing a current in the opposite direction it can be reversed back into its initial form. Instead in a irreversible reaction, slow electron transfer kinetics produce the diffusion to the surface of new chemical species, that can alter the chemical composition of the tissue, generating the beginning of corrosion or oxidation. Then, in order to prevent toxic reaction and tissue or electrode damages, in a neural stimulation system only reversible Faradaic processes can be used for charge injection. Regarding safety during electrical stimulation, several analysis and models have been presented in literature. Some studies focus on electrode material and geometric area [25, 26], using as selection criteria the reversible charge injection limit of the material. Such quantity depends on the reversible processes that are available over the duration of the stimulus, as well as the stimulus waveform shape and frequency [27, 28]. Considering the methods of controlling charge injection, two categories are available: current-controlled and voltage-controlled. Several works consider the currentcontrolled method the most effective because the effects of such stimulation take place near the electrode and can be directly calculated and easily understood [26, 29]. Current pulses allow to eliminate variations in the stimulation threshold even with changes in the electrode-tissue impedance and are commonly used for functional electrical stimulation of excitable tissue. However many researchers prefer voltage stimulation in terms of electrode safety. In fact, current pulses can cause high electrode voltages with a following electrochemical damage of the electrode [30]. Choice of stimulus parameters is then very important in the design of neural stimulation circuitry and depends on the type of stimuli to generate. Charge-injection for neural stimulation is usually applied in the form of rectangular pulses but in the recent years different waveform types have been explored. The results obtained in [31] and [32], suggest that Gaussian waveforms, compared to rectangular stimulus, reduce the non-uniformity of the current density distributions on the electrode surface while maintaining stimulation efficacy and requiring the smallest electrode surface area.

## 1.5 State of art

Neural signals can be considered both in terms of voltages and currents. In fact, as explained in Section 1.2.2, voltage spikes are generated by means of ion channel currents. According to what reported in literature, in this thesis the main focus is on the neural voltage recording. Nevertheless an analysis and a high implementation of a front-end circuit for ion channel current detection is also presented. For these reasons in this section the state of art related to both type of measures is presented, the voltage signal acquisition and the ion current readout circuits. An overview on literature related to neural stimulation is also provided.

### **1.5.1** Neural recording and stimulation systems

In last decades great advancements have been reached in biomedicine, in particular as described in Section 1.3 the introduction of intraneural electrodes has made it possible to work with stronger signals. Nevertheless, amplitudes remain in the order of magnitude of tens of microvolts, therefore the noise is still the major concern. A low noise front-end stage is then mandatory to prevent the signal destruction. Many researchers are currently working on low noise neural interfaces, aimed to different applications. This kind of devices indeed can be very useful for many purposes: to find a solution against neural-degenerative diseases like Parkinson and Alzheimer for instance, as well as for injured patients with permanent damages to the spinal cord and, as in the work presented in this thesis, to restore lost functionalities in amputees thanks to neuroprosthesis. According to the pursued goal, different specifications drive the neural interface design. In the recording systems related to CNS, for example, also neural signals different from action potentials can be useful (Local Field Potential (LFP) for instance). Their amplitudes are in the order of magnitude of mV and their frequency overlaps with EMG interferences [33–35]. The recording is still possible because EMG, in CNS recordings, are not of a such importance, due to the fact that there are no muscles moving into the brain. For this kind of applications the bandwidth includes also very low frequencies (in the mHz - 100Hz range) [7, 14, 36, 37]. The neural signal weakness together with the strong interferences drive the designers to develop solutions capable to filter and amplify the signal as close as possible to the electrode, the miniaturization and optimization of electronics for neural activity stimulation and registration seems to be then, the new challenge. Attempts to solve this issue are based on two different approaches: the use COTS electronics or the realization of a custom IC. The first approach is utterly useful for a preliminary analysis because it is a low-cost solution and has a rapid implementation time so it is suitable for short-term experiments, especially on animals. Moreover, since neural signal characteristics in terms of bandwidth and stimulation pulse amplitudes are patient and electrode dependent, the possibility to easily modify the electronic configuration represents a great advantage in the first stages of research. The IC approach, on the contrary, allows the realization of low noise and compact devices, combining low power consumption and small sizes [14, 38, 39] and is, therefore, more suitable for long-term implantation. Nevertheless, design time and prototyping costs are large and the custom device usually lacks flexibility and adaptability. To sum up all the typical approach is to start with a COTS device and, only once that the terms of the problem are better known, a custom integrated circuit can be developed on a solid ground.

Several works aimed at the realization of neural interfaces with discrete components have been presented, but many of them include only the recording module [40–43]. On the other hand, papers including the stimulation circuitry use a simple recording unit with low order filters and single-ended signal paths [34, 37, 44–46]. Moreover, such discrete component systems are focused on the study of the Central Nervous System (CNS). For what concerns the integrated circuit approach, many papers have been presented but the majority is still aimed to process cortical neural signals [14, 33, 35, 39, 47–51]. Several integrated circuits for PNS have also been developed [13, 38, 52–54], but in most cases they do not include the stimulation unit and are focused on cuff electrodes. The IC circuits have the great advantage on their discrete system counterpart, to allow the designer to have the complete control on all the system parameters, by this way it is possible to find a better fitting between the specifications and the prototype. The drawback is obviously a major project complexity due to the enormous degree of freedom that must be handled by the designer. In the following a survey on literature regarding the amplifier, the filter, the Analof to Digital Converters (ADC) and the stimulator used in neural signal interfaces is presented.

#### Amplifiers

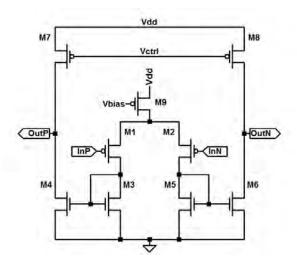

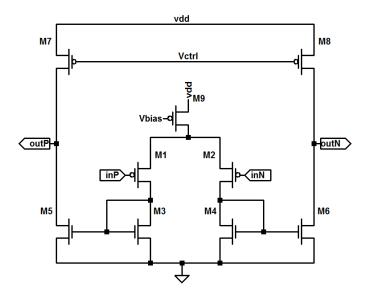

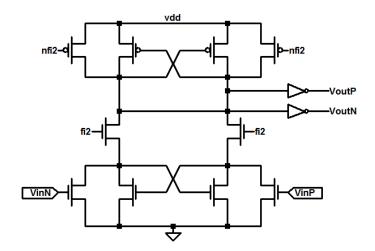

One of the key points concerning the recording module is to realize a low noise amplifier. Different choices have been made in this direction but the most pursued one has been to use a Symmetrical OTA topology of Fig.1.13. Thanks to its simple circuitry, in fact, it guarantees the minimum IRN comparing with other topologies as Folded Cascade and Miller OTA. Many papers present such solution for neural implementation in its single ended [7, 14, 55, 56] or fully differential versions [36].

Figure 1.13: Simmetrical OTA in Fully differential configuration

Using Symmetrical OTA architecture, thermal noise is given by equation 1.5.

$$\overline{V_{n,th}}^2 = \left[\frac{16kT}{3g_{m1}}\left(1 + 2\frac{g_{m5}}{g_{m1}} + \frac{g_{m8}}{g_{m1}}\right)\right]$$

(1.5)

Where  $g_{m1}$  is the transconductance of the input differential pair, while  $g_{m5}$  and  $g_{m8}$  are the transconductances of the transistors in the output branch. In order to reduce noise, a designer must have special care in MOS sizing.

Equation 1.5 shows that thermal noise minimization requires  $g_{m1} \gg g_{m5}, g_{m8}$ . Since the  $g_m$  expression for a MOS in saturation region is given by

equation 1.6, a low noise amplifier can be achieved by using large and short differential pair and narrow and long mirror transistors.

$$g_m = \sqrt{2\mu C_{ox} \frac{W}{L}} \tag{1.6}$$

The consequence in choosing large transistor for input differential pair is that the device enters in weak inversion region. In such region  $g_m$  is maximized and becomes independent from MOS size, depending only upon drain current. Thus, once that the differential pair MOS is in weak inversion, the only way to further increase the transconductance is to increase the current with a consequent increase of power. Taking everything into account, the majority of papers choose to maximize  $g_{m1}$  by using a large input differential pair in weak inversion without increasing current, and to minimize  $g_{m5}$ and  $g_{m8}$  by putting M5 and M8 in strong inversion [57–60]. This approach is not used only in Symmetrical OTA configuration but also in Folded Cascade [18, 61] and Miller OTA [52]. Such choice has advantages in terms of flicker noise reduction. As already shown in equation 1.1, this noise is in fact reduced when MOS dimensions are increased. Almost all researchers prefer a PMOS differential pair to NMOS for its lower sensitivity to flicker noise. Nevertheless, analysis carried out in [62] shows as such assumption is true only comparing NMOS and PMOS with the same  $g_m$ . The noise reduction, in this case, derives from a larger implementation area of PMOS transistors. Considering the same biasing and area it is demonstrated that a NMOS amplifier presents higher  $g_m$  than a PMOS one and then a better figure noise. Another approach that has positive effects on noise is the use of a fully differential topology. Having two branches, in which the signal is mirrored and propagated, is an advantage in terms of common mode noise. Such noise spreads in the same way along the two differential paths of the circuit and is canceled taking the difference of the two output voltages. These benefits are paid with a large occupation area due to the duplication of feedback networks of the filters and to the introduction of common-mode feedback (CMFB) blocks. Although the use of fully differential architectures would be desirable, only few papers adopt this strategy [53, 60, 61, 63]. Even if symmetrical OTA is the most widely used configuration, other topologies have been exploited. The modified folded cascade proposed in [18] allows to obtain a NEF of 2.67 which is one of the lower values reported today. This result is achieved reducing power by means of current reduction in folded branches (1/16 with)respect to input branches) that may imply worse noise performance. This drawback is avoided using degenerating resistors in series with M5 and M6. An appropriate choice of these resistances may significantly reduce the contributions to total noise. First because thermal noise in resistors can be

significantly lower than in MOS and second because the resistance gives no contributes to flicker noise. A folded cascade topology has been used by [64] that, taking advantage by the current-splitting technique, reaches a NEF of 3.09 with an  $IRN = 3.07 \mu V_{rms}$ . Among the other topologies exploited in neural amplifiers, Wang et al., in [52], propose a preamplifier stage based on Miller OTA configuration. The circuit gives a gain of 20 dB and it is followed by an instrumentation amplifier that brings the gain to 80 dB. Sacristan and Oses [65] present instead a multi-stage architecture. In the design of the first stage, represented by a simple preamplifier, authors have paid particular attention in noise reduction and CMRR, using large area transistors and high biases current. The second stage takes advantage by a DDA (Difference Differential Amplifiers), composed by two pairs of differential inputs. Inputs are applied to the first pair while in the second two, feedback loops are implemented. One feedback loop imposes the gain, while the other introduces zero and poles for filter implementation. The third stage consists of a simple RC high pass filter followed by a fixed gain amplifier, needed to adjust the gain to the level required by the ADC. This circuit solution allows to achieve particularly low noise levels  $(0.35\mu V \text{ in the bandwidth of } 100Hz - 5kHz)$ , at the cost of a high power consumption (2mW). In [53], a different solution employing an instrumentation amplifier has been proposed. In order to reduce the noise, a fully differential approach is used and the input stage is constituted by a PMOS differential pair with large area. Despite that, the noise at 1kHz is about  $0.73\mu V/\sqrt{Hz}$ . Integrated in the neural useful band (250Hz-5kHz) an IRN value of  $50\mu V$  is obtained, still too high if compared with the weak amplitude of neural signals.

#### Filters

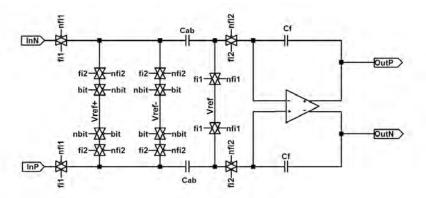

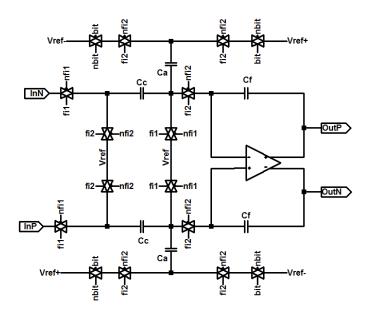

Several approaches in neural filter design have been implemented. The major degree of freedom in filter design is the choice of the filter type. In integrated systems, filter strategies can be classified in Continuous Time Filters (R-C or MOSFET-C and Gm-C) and Discrete Time Filters (Switched-Capacitor) [66, 67]. The most used are MOSFET-C filters for their ability to reach very low cut-off frequencies useful for LFP recording [14, 18] as well as for *Fast Ripples (FR)* detection in epileptic patients [64]. Since the cut-off frequency is given by the inverse of the product of the MOSFET equivalent resistance and the capacitance, a very low value can be obtained using a high capacitor or a high resistance. But as both solutions imply large area implementation, a widely used approach is to employ a MOSFET biased in triode region that emulates a resistive behavior. By this way, the relationship between drain current and the drain-source voltage is linear, as expected

from a resistor. This particular application requires large values of resistance (to achieve a mHz cut-off frequency with a capacitor in the pF range, it is necessary an equivalent resistance in the order of hundreds of  $G\Omega$ ). For this reason, bipolar transistors compatible with CMOS process are used [68]. This technique allows achieving resistances of several hundreds of  $G\Omega$ . The discrete time approach is rarely used but it presents several advantages with respect to continuous time filters. In this case, cut-off frequency is set by the ratio of two capacitors. The ratio of parameters of the same kind of device is more precise than the ratio of a transconductance and a capacitor (Gm-C filters) since it is affected by statistical fluctuations of the same manufacturing process. Moreover, Switched Capacitor filters allow an effective use of silicon area, making possible to realize low cut-off frequencies with small areas. A great advantage is also given by the flexibility due to the dependence of the filter parameters on the clock frequency. In [53] a six order band-pass filter is proposed. The architecture consists in three fully differential biquad stages, in which the filter signal flow is based on ladder-type implementation. Gusmeroli et al., in [69] use a first order switched capacitor high pass cell, changing the high pass cut-off frequency in order to reduce the recovery time during stimulation. Trough switching capacitor technique, it is sufficient to increase the clock frequency to achieve a time recovery reduction. In the solution proposed in [70] the switching capacitor stages are preceded by a continuous time filter in order to avoid aliasing and to prevent input corruption due to switching noise. Regarding the heavy incidence of flicker noise in neural signal acquisition, some researchers [57, 71] have overcome this problem introducing a chopper stabilization technique. The working principle is to modulate input signal in order to translate it into high frequency where the flicker noise effect becomes irrelevant. The modulated signal is band-pass filtered and then demodulated in the baseband. Uranga et al. in [61] propose a signal chain composed by a modulator followed by a pre-amplifier stage and by a band-pass filter centered at chopping frequency. The pass-band removes the undesirable spikes introduced in chopping process due to non-idealities of switches. A post amplifier stage has been introduced after the band-pass, then a demodulator folds the signal into base band and finally a low pass filter isolates the neural signal from noise. Both band-pass and low-pass continuous time filters have been designed using the Gm-C technique. The advantage of this approach is that the noise can be reduced simply increasing the chopper frequency. On the other hand, this implies an increase of the amplifier cut-off frequency that must be higher than the clock frequency, in order to avoid any harmonic distortion of the modulated signal. Gosselin et al. [63] present a multi-channel structure composed by a front-end stage and a mixed-signal compression module that uses an analog wavelet transform process followed by an ADC. The front-end stage is present for each acquisition channel while the wavelet signal processing block is shared among all channels. The front-end stage is based on Chopper Stabilization technique. After modulation, the signal is amplified with a rail-to-rail CMOS amplifier and filtered with a second order Gm-C stage. The signal is then demodulated into the baseband while the equivalent noise is added to the amplifier input after that the modulation process has occurred. Thus, noise is subject only to one modulation process (the same used for signal demodulation) that translates the noise out of the band of interest. Another technique, called autozeroing, has been exploited in order to reduce low-frequency noise and offset at the amplifier input. Between Chopper Stabilization and autozeroing there is a clear distinction: while the first is a modulation technique, the latter is a sampling technique. The basic idea of autozeroing is to sample the offset voltage value and the noise and to hold them in a capacitor. Once that these values have been stored, the input is put into the amplifier and the unwanted quantities can be subtracted from the instantaneous input.

translates the noise out of the band of interest. Another technique, called autozeroing, has been exploited in order to reduce low-frequency noise and offset at the amplifier input. Between Chopper Stabilization and autozeroing there is a clear distinction: while the first is a modulation technique, the latter is a sampling technique. The basic idea of autozeroing is to sample the offset voltage value and the noise and to hold them in a capacitor. Once that these values have been stored, the input is put into the amplifier and the unwanted quantities can be subtracted from the instantaneous input. With the offset voltage this process works well since offset is constant, the problem is a bit more complex considering time-varying and random flicker noise. The efficiency of autozeroing strongly depends on the correlation between the noise sampled and held in the capacitor and the instantaneous noise value from which such sample is subtracted. It can be stated that this process reduces also the flicker noise because the autocorrelation between two consecutive samples of flicker noise decreases slowly enough to allow the cancellation when the subtraction occurs. The main drawback of this approach is the aliasing. Since this is a sampling technique, the aliasing noise is folded into the base band [72]. Chan et al. [60] propose a neural amplifier based on autozeroing technique: the design consists of three stages. The first one is a variable gain amplifier composed by two differential pair, one for input recording and the other for offset-noise adjustment. The second stage is a low Gm-C high-pass filter and the third is a low-pass Gm-C amplifier. From the point of view of power consumption, autozeroing seems to give better performances than chopper. The modulation implies a wider amplifier bandwidth and to this aim, it is necessary to increase current and then power consumption. A summary on the main features of the neural recording system presented in literature has been reported in Tables 1.1 and 1.2. It should be clear that each system has his own characteristics, thus a mere comparison of the parameters can be unfair. For this reason in the last column the number of channel to which the parameters are referred has been reported.

#### Analog-to-digital conversion and spike sorting

Once the signal has been properly amplified and filtered, the last operation is digitalization. At this regard, two main approaches have been proposed. The first consists in a traditional digital conversion, where the neural signal morphology is held and transmitted to external for processing and classification. The second approach consists in spike detection; in this case the signal morphology is lost and the only information kept is about spike occurrences. The A/D conversion is exploited in several works. In [7, 53, 65], an 8 bit successive-approximation register (SAR) ADC has been used. This solution involves low power consumption and small layout area. Watkins et al. in [73] make use of a 10 bit SAR ADC but, since the signal is acquired from 100 different channels, it would be too onerous to convert all signals. The proposed solution converts only one channel, while for the others there is a spike detection block that recognizes if a spike has occurred or not. In this way there is a considerable reduction in bandwidth requirement for the external communication link. Horiuchi et al. [56] use the spike detection approach, but their circuit is more elaborate than a simple comparator and it is able to discern between peaks and troughs of spikes and gives also information about spikes amplitude. Another approach proposed is based on oversampling converters. Due to the low frequencies of the neural signals in fact, large OverSampling Ratio (OSR) can be achieved, without using high sampling frequencies. In [74] a first order sigma delta converter has been designed, reaching a 8 bit resolution with a 40 oversampling ratio over a 6.25 kHz frequency. A second order sigma delta modulator that exploits a new superinverter amplifier has been proposed in [75] and allows to reach a 11 bit resolution considering a 8kHz bandwidth.

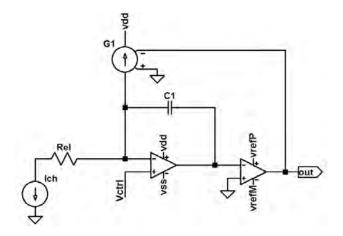

#### Stimulation circuitry

Stimulation circuit is present only in a few of the neural conditioning systems mentioned above. Basically, the stimuli are generated through a Digital to Analog Converter (DAC) while the stimulation parameters as frequency, duration and intensity are controlled by a digital unit or an external microcontroller ( $\mu C$ ). In [53], a current-mode microstimulator for cuff electrodes has been implemented. It is made up of a thermometer DAC, which generates an output current from 0 to 1mA with 8 bits of resolution. The maximum value for the stimulation current has been chosen estimating a load resistance of  $1k\Omega$ . In [65] a 6 bit binary weighted DAC with a full-scale current of  $128\mu A$  is used to generate stimulating currents. The architecture of such device assures a high flexibility and programmability, making it useful for different types of electrodes (as sieve, cuff, LIFE or microneedle) and for several stimuli shapes. A novel modification to the binary-weighted DAC has been presented in [76]. It is based on distributed multiple bias potential in transistors of same size. Relative currents are controlled by gate bias rather than by geometry, this significantly reduces the circuit area which scales linearly versus number of bits. Since the major disadvantage of DACs for implantable stimulators is the implementation area which grows exponentially with resolution, the multi-bias approach offers important benefits.

| Ref. | Tech.           | Band [Hz]                             | Gain [dB] | $V_{DD}$ [V] | Area           | Power        | IRN                    | NEF  | Ch.      |

|------|-----------------|---------------------------------------|-----------|--------------|----------------|--------------|------------------------|------|----------|

| [2]  | CMOS $0.5\mu$   | 5 - 7.2k                              | 36        | 3            | $2.25mm^2$     | $M \eta 66$  | $9\mu V$               | n.a. | 64       |

| [14] | CMOS $1.5\mu$   | 25m-7.2k                              | 39.5      | $\pm 2.5$    | $0.16mm^2$     | $80\mu W$    | $2.2\mu V$             | 4    | 9        |

| [18] | CMOS $0.5\mu$   | 45 - 5.32k                            | 40.8      | 2.8          | $0.16mm^2$     | $7.56 \mu W$ | $3.06 \mu V$           | 2.67 |          |

| [35] | CMOS $0.18\mu$  | 16 - 5.3k                             | 40        | 1.8          | $2.7mm^2$      | $89 \mu W$   | $18.9 \mu V$           | n.a. | $\infty$ |

| [36] | SOI $0.18\mu$   | 0.6m-7.1k                             | 39.5      | 1.5          | $0.004 mm^{2}$ | $6\mu W$     | $3.07 \mu V$           | 2.8  |          |

| [38] | CMOS $0.8\mu$   | 310 - 3.3k                            | 80        | $\pm 2.5$    | $12mm^2$       | 24mW         | 291 nV                 | n.a. | 10       |

| [39] | BiCMOS $0.6\mu$ | n.a 5k                                | 60        | 3.3          | $25.38mm^2$    | 8mW          | $4.8 \mu V$            | n.a. | 100      |

| [41] | COTS            | 445 - 6.6k                            | 70 - 94   | $\pm 2$      | $80.19 cm^{2}$ | 130 mW       | $1 \mu V$              | n.a. | 16       |

| [47] | CMOS $0.35\mu$  | $(0.5 \div 50) -$<br>$(500 \div 10k)$ | 54 - 73   | co           | $8.5mm^2$      | 9.3mW        | $6.08 \mu V$           | 5.6  | 128      |

| [48] | CMOS $0.35\mu$  | $(30 \div 925) -$<br>$(970 \div 18k)$ | 54        | $\pm 1.5$    | $6.25mm^2$     | n.a.         | $32\mu V$              | n.a. | 16       |

| [49] | CMOS $0.6\mu$   | 0.5-15k                               | 30 - 80   | 5            | $45.75mm^2$    | 135m         | $2.4 \mu V$            | n.a. | 126      |

| [53] | CMOS $0.35\mu$  | 250 - 5k                              | 80        | 3 - 4        | $4mm^2$        | 2.25 mW      | $0.73 \mu V/\sqrt{Hz}$ | n.a. | 1        |

| [54] | CMOS $1.5\mu$   | 300 - 6k                              | 40 - 60   | $\pm 1.5$    | $41.84 mm^{2}$ | 1m           | $1.95 \mu V$           | n.a. | 1        |

| [55] | CMOS $0.35\mu$  | 10-10k                                | 46 - 74   | 3.3          | $13.5mm^2$     | 6mW          | $13\mu V$              | n.a. | 256      |

|      |                 |                                       |           |              |                |              |                        |      |          |

Table 1.1: Main characteristics of neural recording system presented in literature

Neural-machine interfaces

| Ref. | Tech.              | Band [Hz]                | d [Hz] Gain [dB] | $V_{DD}$ [V] | Area           | Power       | IRN                 | NEF  | Ch. |

|------|--------------------|--------------------------|------------------|--------------|----------------|-------------|---------------------|------|-----|

| [56] | CMOS $1.5\mu$      | 22-1.7k                  | 42.5             | 1.5          | $81 \mu m^2$   | $0.8 \mu W$ | $20.6 \mu V$        | n.a. | 1   |

| [57] | CMOS $1.5\mu$      | 100 - 5k                 | 38               | Q            | $1mm^2$        | 28mW        | $1.13nV/\sqrt{Hz}$  | n.a. | -   |

| [59] | CMOS $0.5\mu$      | 73 - 2.18k               | 20               | $\pm 2.5$    | $0.33mm^2$     | $180 \mu W$ | $2.76 \mu V$        | n.a. | -   |

| [09] | CMOS $0.18\mu$     | 200 - 2k                 | 55               | 1.8          | $0.245 mm^{2}$ | $26\mu W$   | $4.24 \mu V$        | 14   | -   |

| [61] | CMOS $0.7\mu$      | n.a 3k                   | 74               | IJ           | $2.7mm^2$      | 1.3mW       | $0.453 \mu V$       | 5.3  | -   |

| [63] | CMOS $0.18\mu$     | 100 - 6k                 | 80               | 1.8          | $0.064mm^2$    | $20 \mu W$  | $30 nV/\sqrt{Hz}$   | n.a. | 100 |

| [64] | CMOS $0.6\mu$      | 250 - 486                | 38.5             | 2.8          | $0.45mm^2$     | $4.5 \mu W$ | $2.46 \mu V$        | 7.6  | 1   |

|      |                    | 106 - 5.1k<br>110 - 5.1k |                  |              |                |             |                     |      |     |

| [65] | [65] CMOS $0.7\mu$ | 201 - 5.1k               | 76 - 102         | $\pm 2.5$    | $1.13 mm^{2}$  | 4mW         | $0.35 \mu V$        | 3.6  | 1   |

|      |                    | 352 - 5.1k               |                  |              |                |             |                     |      |     |

| [68] | CMOS $0.35\mu$     | 2-20k                    | 64               | $\pm 1.65$   | $8.96mm^2$     | 33mW        | $2.9 \mu V$         | n.a. | 64  |

| [69] | CMOS $0.35\mu$     | 100 - 10k                | 20               | $\pm 1.65$   | $5mm^2$        | n.a.        | $10\mu V$           | n.a. | 1   |

| [02] | CMOS $0.5\mu$      | 530 - 5.3k               | 61 - 73          | $\pm 2.5$    | $15.96mm^2$    | n.a.        | $27.7 nV/\sqrt{Hz}$ | n.a. | 17  |

| [73] | CMOS $0.5\mu$      | 1.1k - 5k                | 60.1             | 3.3          | $27.3mm^2$     | 13.5mW      | $5.1 \mu V$         | n.a. | 100 |

|      |                    |                          |                  |              |                |             |                     |      |     |

**Table 1.2:** Main characteristics of neural recording system presented in literature

1.5 State of art

# 1.5.2 Patch clamp circuits for Ion channel current detection

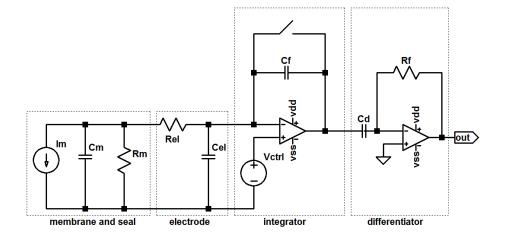

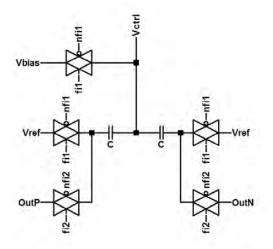

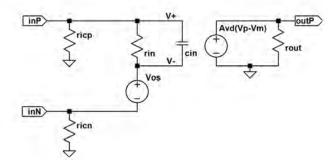

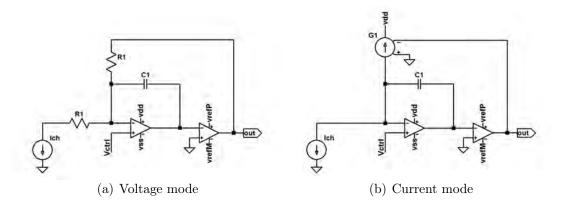

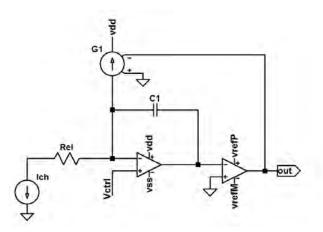

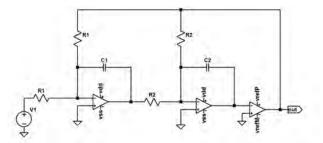

As explained in Section 1.2.2, the generation of electrical signals in biological cells is possible thanks to ions that move across the cell membrane. In many applications it is important to record these currents in order to understand which electro-chemical processes are involved in the signal generation and to have a direct measurement of the ion channels involved in the reaction. Ion currents, in fact, play a key role in several physiological processes, in neural signal generation, as already discussed, but also in the maintenance of heartbeat and in muscle contraction [77]. The signal is recorded by means of a pipette, depending on the way the pipette is attached to the membrane. It is possible to record the electrical activity of the whole cell or of a small patch of channels (even a single channel current can be measured) [77–79]. The recording of a small cluster of channels is possible because the contact between the pipette and the membrane cell forms a Gigaohm seal [77, 80], allowing to isolate the electrical activity of a small area of the membrane. The patch clamp working principle consists in fixing the external membrane potential to a control voltage and in recording the current that flows across the membrane using proper electronic devices. These devices can be implemented, as in a wide number of paper presented in literature [77, 79, 81], as the cascade of an integrator and a differentiator (Fig. 1.14) or, as also proposed in this thesis, as a current feedback delta sigma modulator (Fig. 1.15) [82–87]. In Fig. 1.14, it is also shown the equivalent electrical circuit

Figure 1.14: Patch Clamp circuit based on integrator-differentiator approach

for the membrane-seal connection and for the electrode. Typical values for these equivalent components are given in Table 1.3

| $C_m$  | $C_{el}$ | $R_m$                 | $R_{el}$               |  |

|--------|----------|-----------------------|------------------------|--|

| 300 fF | 500 fF   | $20G\Omega-40G\Omega$ | $10M\Omega-140M\Omega$ |  |

Table 1.3: Equivalent electrical parameters for membrane and electrode

Figure 1.15: Patch Clamp circuit based on a sigma-delta approach

The circuits traditionally used to detect ion channel currents, are very similar to potentiostats used to record redox current in electrochemical sensing devices [88–90]. In fact in both cases the aim is to detect a current in a range from hundreds of fA to few  $\mu A$ . The control voltage in the case of ion channel detection is used to set the membrane potential while in potentio-stat it sets the redox voltage. The advantages of the delta-sigma approach are that the current is directly recorded as a digital pattern without need of differentiator, and the reset switch of Fig. 1.14 can be avoided considering that the current, at the input node, is supplied or sinked according to the feedback bit, avoiding the amplifier saturation.

# Bibliography

- G. Naples, J. Mortimer, A. Scheiner, and J. Sweeney, "A spiral nerve cuff electrode for peripheral nerve stimulation," *IEEE transaction on biomedical engineering*, vol. 35, pp. 905–916, 1988.