## **THÈSE**

pour obtenir le grade de

#### **DOCTEUR DE L'UNIVERSITÉ DE TOULOUSE**

Délivré par l'Institut National des Sciences Appliquées de Toulouse

École Doctorale : Génie Électrique, Électronique, Télécommunications Discipline : Conception des Circuits Microélectroniques et Microsystèmes

présentée et soutenue

par

## Piotr Zając

le 30 juin 2008

# **Fault Tolerance through Self-configuration** in the Future Nanoscale Multiprocessors

#### Directeurs de thèse:

M. Jacques Henri COLLET et M. Andrzej NAPIERALSKI

#### **JURY**

- M. Jean-Marie DILHAC, Président

- M. Christian LANDRAULT

- M. Andrzej NAPIERALSKI

- M. Michael NICOLAIDIS

- M. Stanislaw PIESTRAK

- M. Jacques Henri COLLET

## Acknowledgements

This work has been carried out at the Laboratory of Analysis and Architecture of Systems of the French National Research Center (LAAS-CNRS). I wish to express my gratitude to the successive directors of the LAAS-CNRS, Mr. Malik Ghallab and Mr. Raja Chatila, for the facilities provided in the laboratory.

This thesis was conducted as a part of a cotutelle agreement between Technical University of Lodz and Institut National des Sciences Appliquées of Toulouse. It was partially financed by the Cotutelle PhD Scholarship from the French Ministry of Foreign Affairs.

I owe my sincere thanks to my thesis supervisor, Mr. Jacques Henri Collet, without whom this thesis would not be possible. I appreciate his vast knowledge and I am most grateful to him for offering me the opportunity of working in the interesting area of research, for his guidance, advice and time he devoted to read my thesis.

I am also deeply grateful to my second supervisor, Mr. Andrzej Napieralski, for his many helpful suggestions and constant encouragement during the course of this work and I want to thank him for his expertise, understanding and patience.

I wish to express my gratitude to Mr. Christian Landrault and Mr. Michael Nicolaidis for examining my thesis, to Mr. Jean-Marie Dilhac for granting me the honor of presiding over my thesis jury and to Mr. Stanislaw Piestrak for his valuable remarks concerning the manuscript.

I want to thank all members of the TSF group for accepting me in their midst and providing a friendly atmosphere during my work at LAAS-CNRS. I would especially like to acknowledge Mr. Yves Crouzet and Mr. Jean Arlat for their insightful comments on my work.

I have also benefited from many valuable discussions with my colleagues, Cezary Maj and Michal Olszacki.

Finally, I would like to thank my family: my parents, my grandparents and my sister for their love and constant support in all my endeavors.

# RESUMÉ DE THÈSE

## Table des matières

| F1. INTRODUCTION F-1 |                                                               |      |

|----------------------|---------------------------------------------------------------|------|

| F2. AUT              | O-CONFIGURATION                                               | F-3  |

| F2.1                 | ARCHITECTURE RÉPLICATIVE MULTI-CŒUR                           | F-3  |

| F2.2                 | PRINCIPES D'AUTO-CONFIGURATION                                | F-4  |

| F2.3                 | AUTO-DIAGNOSTIQUE DU CHIP BASÉ SUR LE TEST MUTUEL ENTRE CŒURS |      |

|                      | ADJACENTS                                                     | F-5  |

| F2.4                 | AUTO-CONFIGURATION DES ROUTES DE COMMUNICATION                | F-7  |

| F2.5                 | ETUDE DE LA DÉCOUVERTE DES ROUTES                             | F-8  |

| F2                   | 5.1 Architecture uniport                                      | F-8  |

|                      | 5.2 Architecture multi-port                                   |      |

| F3. ALL              | OCATION ET EXÉCUTION DES TÂCHES                               | F-13 |

| F4. CON              | NCLUSION                                                      | F-17 |

#### F1. Introduction

Depuis trente ans, la puissance du calcul des processeurs a continûment augmenté pour les raisons suivantes :

- la miniaturisation de la taille des transistors a permis une augmentation du nombre de transistors intégrés sur les puces et l'accroissement de la fréquence d'horloge.

- les changements dans l'architecture (ajout de plusieurs niveaux de cache, parallélisme d'instructions, prédiction de branchement, etc..) ont permis de contrebalancer l'allongement du temps d'accès a la mémoire RAM exprimé en cycle processeur.

- les nouveaux modèles d'exécution (hyperthreading, multithreading) ont aussi contribué à augmenter la puissance du calcul par l'exploitation du parallélisme.

En ce qui concerne la miniaturisation, la question se pose de savoir si la diminution de la taille des transistors continuera indéfiniment ou, si par contre, des barrières physiques (en particulier la granularité de matière) rendront impossible la fabrication de transistors plus petits. Aujourd'hui, les concepteurs et les fabricants de puces conviennent généralement que la taille des transistors continuera à diminuer jusque des dimensions nanométriques et qu'ils seront capables de fabriquer des nanopuces (c'est-à-dire, les puces avec les transistors nanométriques) dans la prochaine décennie. Alors, le nombre de transistors sur une puce atteindra des centaines de milliards. Est-ce que pour autant la conception des puces ne rencontra plus aucun problème et que l'augmentation constante de la performance des processeurs est garantie? En dépit des pronostics optimistes, il faut tenir compte que des défis apparaissent plus nombreux qu'a n'importe quel moment de l'histoire de la conception des processeurs. Dans cette thèse, nous nous concentrons sur les trois problèmes suivants :

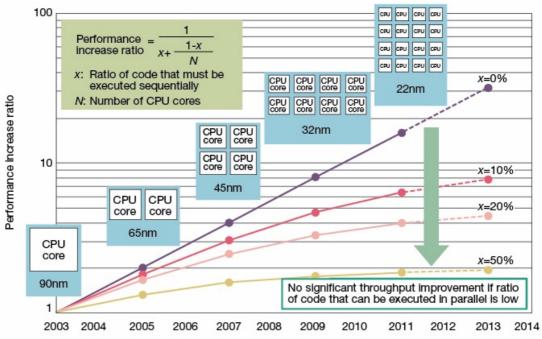

1. L'extensibilité. L'architecture uniprocesseur ne garantit plus l'augmentation de la performance parce qu'il y a une crise au niveau d'une « utilisation » efficace du nombre augmenté de transistors. Autrement dit, il n'y a aucune nouvelle solution architecturale pour monoprocesseur qui garantirait une augmentation de la performance désirée. La tendance actuelle consiste à l'augmentation du nombre de cœurs dans le cadre d'architectures multiprocesseurs symétriques. Pourtant, cette architecture ne permet pas le passage à l'échelle et ce n'est donc pas une solution viable à long terme.

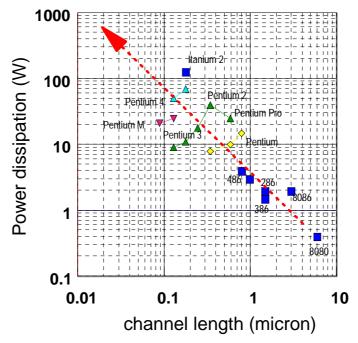

- 2. **La puissance dissipée**. La course aux hautes fréquences a été arrêtée parce la dissipation d'énergie devient prohibitivement grande aux fréquences élevées.

- 3. La sûreté du fonctionnement dans les technologies massivement défectueuses. La longueur du canal d'un transistor nanométrique devient si petite qu'elle est de l'ordre de quelques couches atomiques ce qui entraîne une dispersion plus grande des caractéristiques de transistors et, par conséquent un accroissement de la fraction d'éléments défectueux (et potentiellement défaillants).

Dans cette thèse nous présentons des solutions au niveau architectural pour améliorer la sûreté de fonctionnement des futures puces en augmentant progressivement la performance. Nous proposons une nouvelle méthodologie de conception d'une puce multiprocesseur pour résoudre au moins partiellement les problèmes mentionnés dans le paragraphe précédent. Notre approche est basée sur deux idées principales :

- En raison de l'augmentation de la complexité, les futures puces devraient évoluer vers des architectures régulières et réplicatives.

- Les mécanismes de test de et de configuration (nécessaire pour tolérer les blocs défectueux) devraient être exécutés par la puce elle-même, avec un contrôle externe réduit au minimum. Autrement dit, les futurs nanochips fabriqués dans les technologies massivement défectueuses devraient mettre en oeuvre des mécanismes auto-immunitaires, comme les tissus biologiques, pour maintenir leur capacité de traitement.

Dans cette thèse, nous considérons comme mécanismes auto-immunes l'auto-diagnostique du chip par tests mutuels entre cœurs adjacents et l'auto-configuration des communications. Nous étudions la limite de l'efficacité de ces mécanismes en fonction de la fraction de cœurs et liens défectueux. A l'exécution, nous décrivons et étudions l'implémentation de mécanismes d'exécution redondants afin d'éliminer les erreurs induites par les fautes transitoires ou permanentes.

## F2. Auto-configuration

## F2.1 Architecture réplicative multi-cœur

Nous étudions dans cette thèse des architectures comportant des centaines de cœurs basées sur des topologies d'interconnexion régulières. L'idée d'architectures multi-cœurs massivement parallèles et régulières est fondée sur les raisons présentées dans la partie précédente, c'est-à-dire que :

- Seules des architectures permettant le passage à l'échelle (c'est-à-dire dont le réseau peut être étendu sans remettre en cause la connectivité de chaque nœud) peuvent fournir des solutions garantissant l'accroissement constant de la puissance de traitement.

- Les technologies à l'échelle nanométrique seront inévitablement défectueuses.

- Le taux élevé de défauts au niveau du transistor et le grand nombre de transistors sur une puce rendront la production des puces sans défauts pratiquement impossible. En conséquence, toute puce comportera une fraction de blocs de base défectueux.

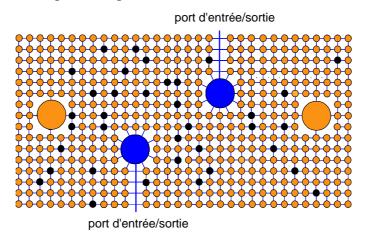

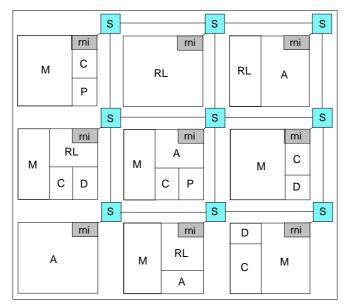

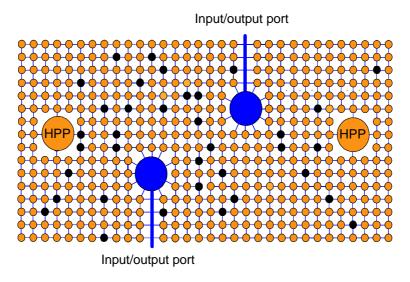

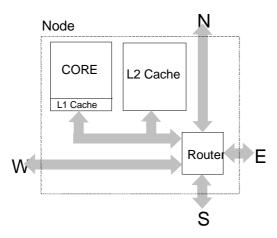

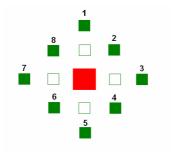

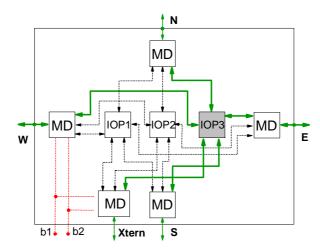

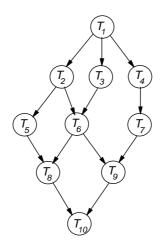

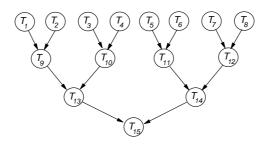

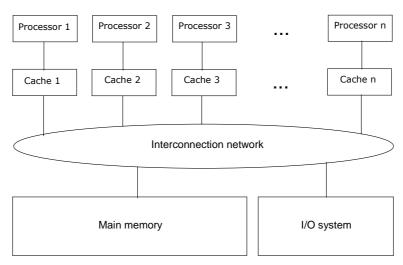

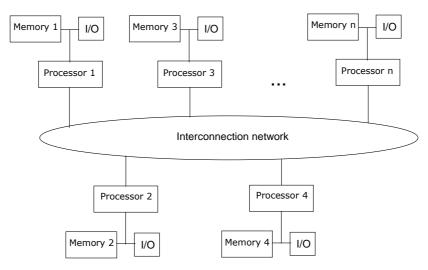

Figure 1. Modèle de l'architecture réplicative

La figure ci-dessus présente un exemple d'architecture multi-cœurs réplicative. Les cercles représentent des nœuds qui dans notre exemple sont organisés comme un réseau carré. Bien sûr, d'autres topologies peuvent aussi être considérées et nous étudions dans le mémoire des topologies dont la connectivité de chaque nœud s'échelonne de 3 (réseau héxagonal) à 5 (réseau carré à 2 couches). Comme nous considérons des technologies défectueuses, les cercles noircis représentent des nœuds défectueux qui ne peuvent pas participer au traitement.

Les méthodes décrites dans notre travail ont pour but essentiel de faire que ce type d'architectures multi-cœurs tolère les nœuds défectueux, c'est-à-dire qu'une fraction de cœurs défectueux provoque un affaiblissement de la puissance de traitement de la puce et non une défaillance globale. Notons également que les positions des nœuds défectueux sont a priori inconnues. Chacun des nœuds comprend un cœur et un router assurant la communication avec des cœurs voisins. En général, la complexité des cœurs peut être variable : les grands cercles représentent des cœurs plus puissants que les autres. Cependant, dans ce travail nous considérons un réseau homogène ou tous les cœurs sont identiques. Le port d'entrée/sortie (PES) est un circuit spécial responsable de la communication avec l'extérieur, par exemple avec de la mémoire RAM.

## F2.2 Principes d'auto-configuration

Les idées principales que nous proposons concernant l'auto-configuration d'une puce incluent :

- L'auto-diagnostique du chip basée sur des tests mutuels entre cœurs adjacents.

- L'auto-désactivation des cœurs isolés.

- L'auto-configuration des routes de communication.

- L'allocation dynamique et l'exécution redondante de tâches.

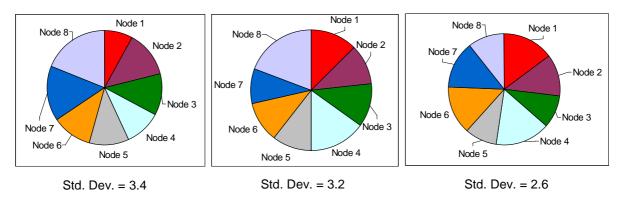

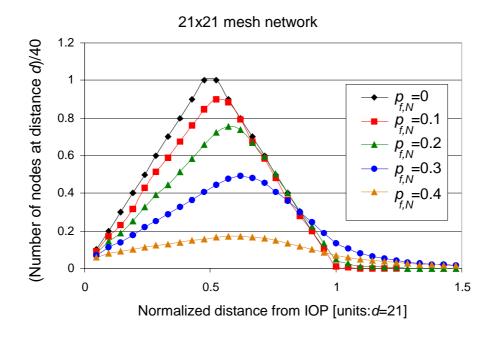

Ainsi, ce travail peut être considéré comme la présentation d'une méthodologie de l'auto-configuration qui permet de tolérer de défauts permanents et des fautes transitoires dans les puces multi-cœurs massivement défectueuses. Nous étudions également l'efficacité des mécanismes d'auto-configuration proposés en fonction de la fraction de nœuds défectueux Typiquement, on considère que l'architecture multicoeurs peut comporter jusque 40% de coeurs défectueux. Il faut souligner que ce paramètre ne dépend pas seulement de la technologie, mais aussi de la complexité du coeur. Il faut considérer la probabilité  $p_{f,N}$  du coeur d'être défectueux comme un paramètre résultant d'un compromis entre la puissance recherchée du coeur (plus le coeur est complexe et donc puissant, moins les contraintes de parallélisation des applications sur plusieurs cœurs sont fortes) et la fraction acceptable de coeurs défectueux dans le réseau, qui n'est rien d'autre en moyenne que  $p_{f,N}$ .

# F2.3 Auto-diagnostique du chip basé sur le test mutuel entre cœurs adjacents

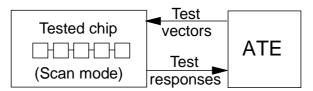

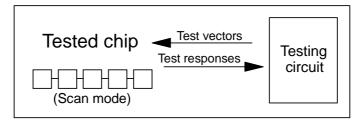

L'idée de l'autotest résulte de l'évidence que le diagnostique externe des nano-puces très complexe devient très difficile à mettre en œuvre, voire impossible. L'autotest est fondé sur l'idée que tout le processus de diagnostic des cœurs défaillants est exécuté par le chip luimême. De plus, les mécanismes du test doivent être associés à des actions de configuration visant à isoler les cœurs défectueux pour assurer malgré tout un fonctionnement correct du circuit même si la puissance de traitement est réduite.

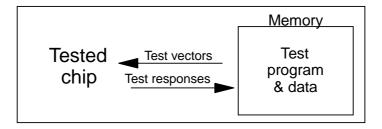

L'autotest logiciel est une méthode relativement nouvelle basée sur un test fonctionnel. Il est surtout adapté au diagnostique des processeurs. Son avantage important est que chaque processeur joue le rôle d'un circuit de test. Toutes les phases du test, c'est-à-dire la génération des vecteurs de test, le test lui-même ainsi que la collection de réponses, sont exécutées par le processeur lui-même. Autrement dit, le processeur est testé au moyen de l'exécution d'un programme de test.

Il faut souligner que dans la méthodologie proposée, la découverte des cœurs défectueux n'est exécutée qu'une seule fois, au démarrage. Les résultats du test initial sont gardés dans la mémoire non volatile des cœurs pour ne pas disparaître quand le chip n'est pas alimenté.

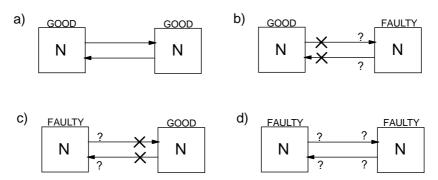

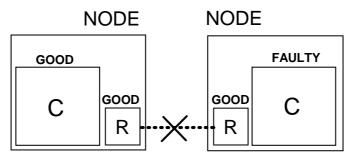

Dans la méthode la plus simple, chaque nœud s'auto-diagnostique. Cependant, cette approche est dangereuse puisque la sûreté de fonctionnement repose sur des actions décidés justement par les nœuds défectueux, donc au comportement imprévisible. En particulier, un nœud défaillant peut se déclarer non-défaillant. Dans ce travail, nous étudions les tests mutuels qui éliminent ce problème. Plus précisément, chaque nœud compare les résultats de son propre test avec ceux de ses voisins adjacents. Puis, il exécute une action simple : il arrête toute communication avec chaque voisin ayant produit des résultats différents. En d'autres termes, les liens vers ces nœuds adjacents sont logiquement déconnectés. Il faut souligner que l'on suppose que les nœuds défaillants peuvent opérer de façon aléatoire alors ils peuvent (mais ne doivent pas forcément) déconnecter leurs voisins.

#### Globalement, il résulte que :

- les bons nœuds seront toujours connectés entre eux.

- les bons nœuds seront toujours déconnectés des nœuds défaillants.

- les nœuds défaillants peuvent être connectes ou déconnectés mais cela est sans importance. Ce qu'il est capital de souligner, c'est que le mécanisme d'isolation basé sur les tests réciproques dépend uniquement des actions des bons nœuds sans faire aucune hypothèse sur les actions des nœuds défaillants.

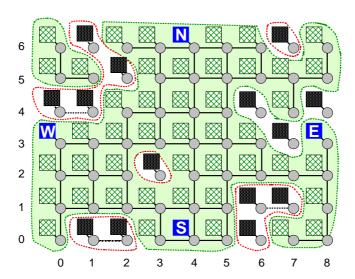

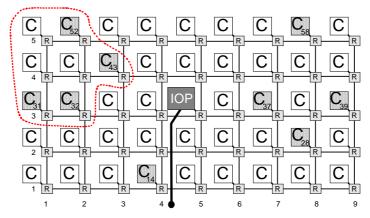

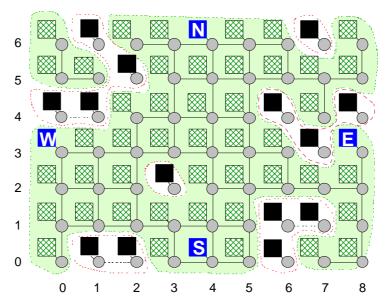

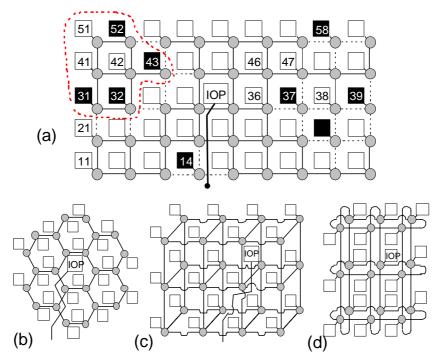

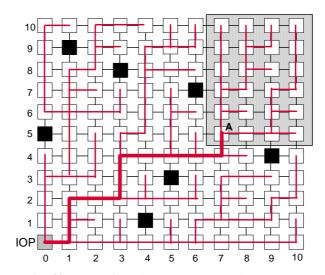

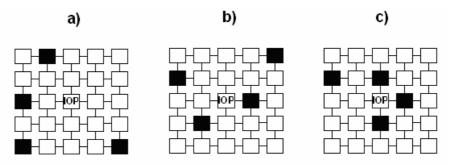

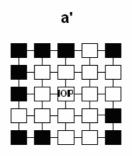

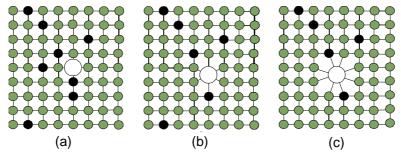

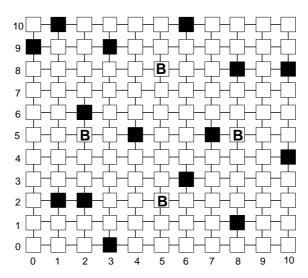

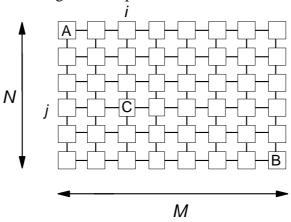

La figure suivante est un exemple qui montre le résultat des tests adjacents pour une architecture en grille comportant 9x7 coeurs. Cette architecture comporte 4 ports d'entrée sortie (marqués N,W, S, E) et 14 cœurs défectueux représentés par des carrés de couleur noir. La figure montre que tous les nœuds défaillants ont été isolés et n'exercent aucune influence sur les autres nœuds. Nous voyons aussi que quelques bons nœuds (en particulier ceux en haut à gauche) ont été isolés de la zone principale comprenant les PES si bien qu'ils ne pourront pas être contactés pour participer au traitement. Dans les chapitres suivants nous étudions l'impact de la fraction des nœuds défaillants sur l'accessibilité des nœuds dans le réseau multi-cœur.

Figure 2. Exemple d'auto-partitionnement de la puce multi-cœur résultant de tests réciproques.

Globalement, la figure montre que les tests entre premiers voisins découpent le réseau en zones simplement connexes de cœurs valides interconnectés. Le problème posé cependant est d'assurer les communications entre les cœurs valides dans une topologie comportant des trous (i.e., des cœurs diagnostiqués comme défaillants) en positions indéterminées.

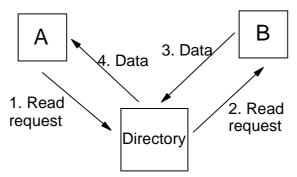

## F2.4 Auto-configuration des routes de communication

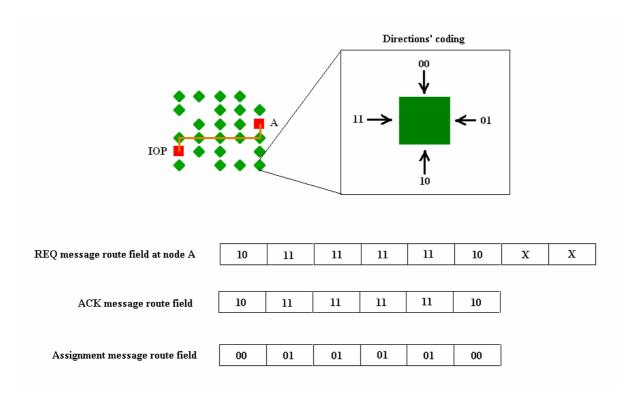

Les protocoles de communication doivent garantir la communication sans échec entre les nœuds. Comment transmettre les messages en présence des nœuds défectueux et isolés? La plupart des mécanismes de découverte de trajets sont basés sur la diffusion (broadcast) d'un ou plusieurs messages. Cependant, diffuser fréquemment des messages peut causer une augmentation significative (voire une congestion) du trafic conduisant à l'accroissement des latences de communication et la réduction de la puissance de traitement de la puce. La solution que nous considérons pour éviter ce problème peut être décomposée en trois phases comme suit :

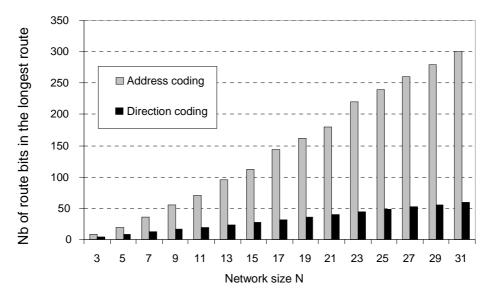

- 1) Au démarrage, chaque port d'entrée/sortie (PES) diffuse un message de *Route* (MR) à tous les nœuds. Ce message comporte un champ de route qui est mis à jour pendant la propagation, c'est-à-dire que chaque nœud traversé ajoute à ce champ le routage exécuté localement. Par exemple on peut coder le routage local sur 2 bits si la connectivité du nœud est 4. Autrement dit, le message stocke la route suivie durant sa propagation de sorte qu'un nœud le recevant possède une route complète vers le PES l'ayant émis.

- 2) Chaque nœud stocke le trajet vers le PES dans sa mémoire locale. Il envoie ensuite un message de *Confirmation* (MC) au PES en incluant le trajet. Notons que le message de confirmation n'est pas diffusé de façon isotrope mais qu'au contraire, il suit en sens inverse le trajet indiqué par le MR.

- 3) Le PES reçoit tous les messages de confirmation et stocke dans sa mémoire locale toutes les routes découvertes durant cette phase et menant vers tous les nœuds accessibles. Les routes ainsi stockées dans la mémoire peuvent être utilisés ultérieurement pour permettre les communications dans une puce en opération.

Il faut souligner que l'espace mémoire nécessaire pour stocker les routes est assez petit dès lors que l'on n'utilise que quelques bits de codage par nœud traversé. Bien sûr, le mécanisme de découverte des routes pourrait être répété périodiquement en opération pour accroître la sûreté de fonctionnement.

#### F2.5 Etude de la découverte des routes

Le nombre de nœuds accessibles sur une puce est un paramètre important que l'on peut utiliser pour décider de valider un circuit lors de sa fabrication. Pour étudier ce paramètre, nous avons utilisé le simulateur MASS. Brièvement, ce logiciel multiagent, écrit au LAAS en langage C++, permet de simuler la communication dans une puce multi-cœur. Le mécanisme de découverte des routes suit les trois phases décrites dans la section précédente. Nous avons étudié l'accessibilité (c'est-à-dire le nombre de cœurs accessibles par le PES) en fonction de la fraction de cœurs ou de liens défectueux dans des architectures uni- ou multi-ports, et pour différentes topologies d'interconnexion. Nous avons étudié l'accessibilité pour:

- 1) Le réseau hexagonal de connectivité C=3 (chaque nœud possède trois voisins, sauf pour les nœuds sur les bords).

- 2) Le réseau carré de connectivité C=4 (chaque nœud possède quatre voisins, sauf pour les nœuds sur les bords).

- 3) Le tore de connectivité C=4 (chaque nœud possède quatre voisins). Cette topologie est repliée et ne comporte plus de bords.

- 4) Le réseau carré à deux couches de connectivité C=5 (chaque nœud possède cinq voisins, sauf pour les nœuds sur les bords).

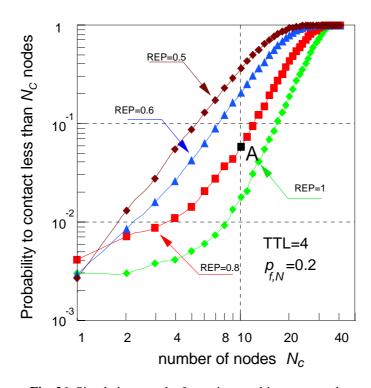

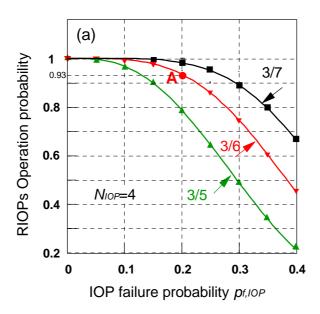

## F2.5.1 Architecture uniport

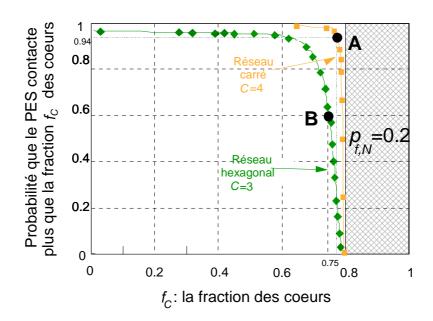

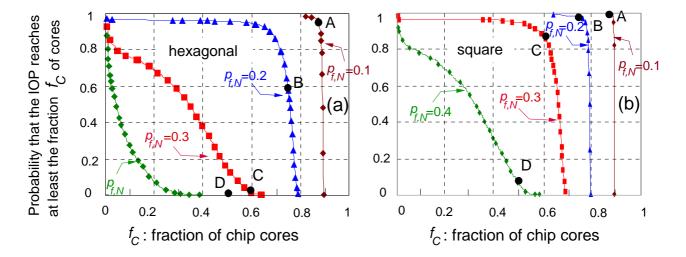

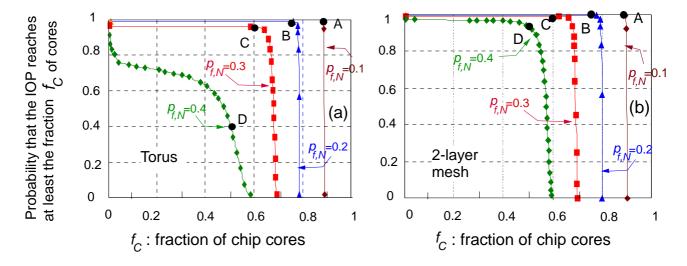

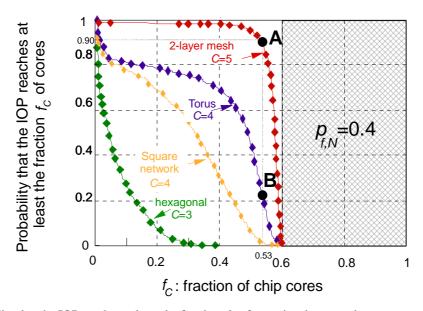

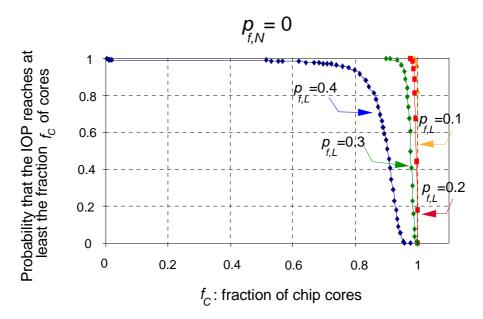

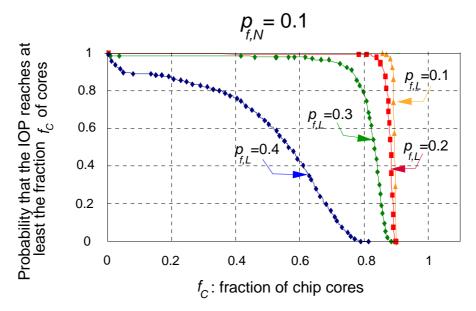

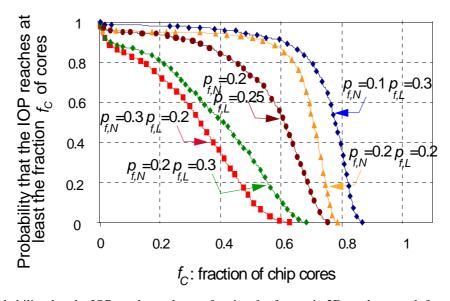

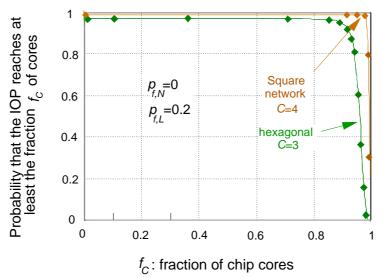

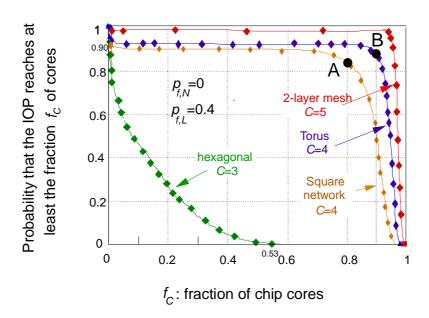

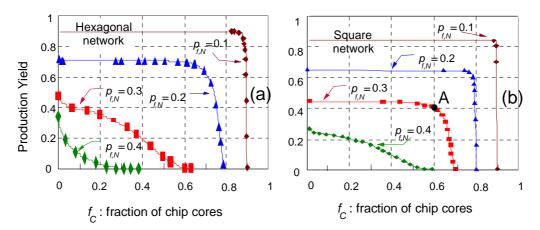

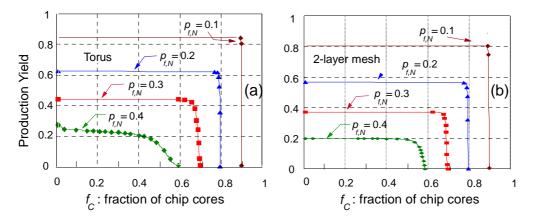

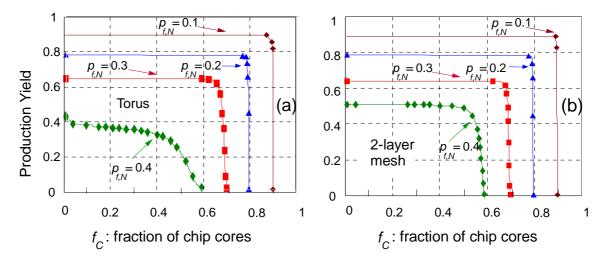

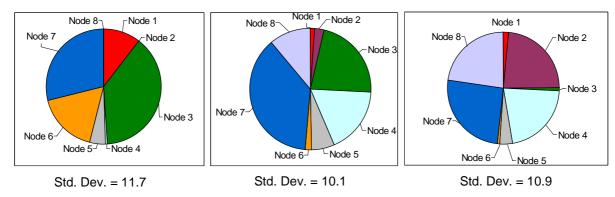

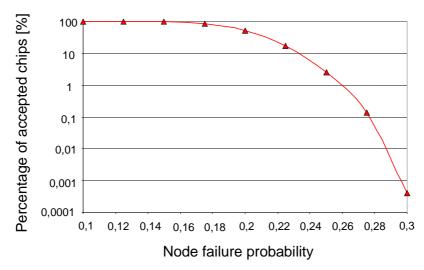

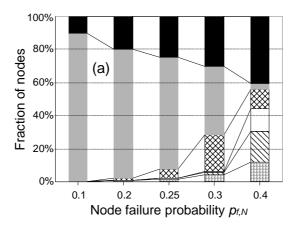

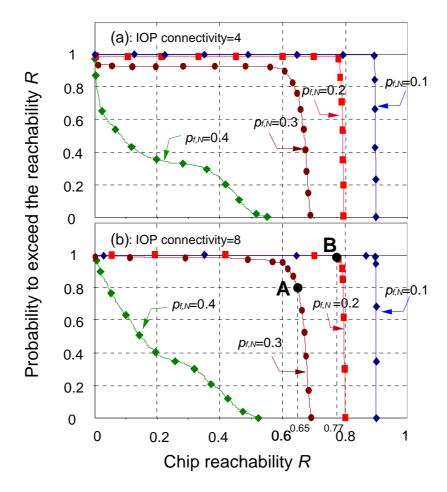

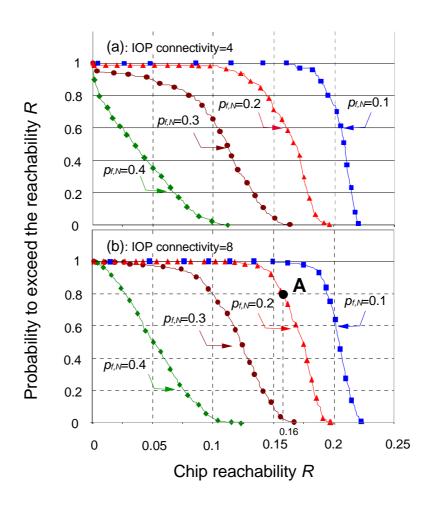

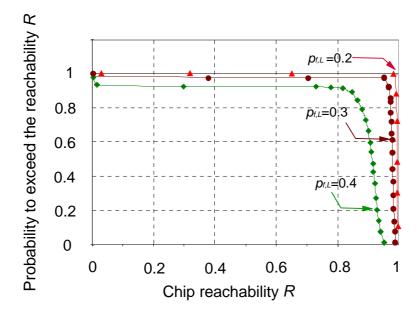

Les résultats des simulations d'accessibilité présentés dans ce résumé de thèse ne représentent qu'une très faible fraction des résultats reportés dans la thèse qui comporte environ 140 pages. Les figures 3 et 4 ci-après présentent la réduction de l'accessibilité du PES dans une architecture uniport en fonction de la fraction de cœurs défectueux (et isolés dans le réseau) pour les quatre topologies d'interconnexions. L'accessibilité est décrite de la manière suivante : l'axe x représente la fraction accessible de cœurs de la puce  $(f_C)$  alors que l'axe y représente la probabilité  $p(f_C)$  qu'au moins la fraction  $f_C$  soit accessible, donc disponible pour

exécuter des tâches. La probabilité  $p(f_C)$  a été calculée en tant que moyenne statistique à partir d'un grand nombre de simulations. Cette façon de présenter les résultats de simulation permet en fait de déterminer le pourcentage des puces fabriquées qui auront une accessibilité plus grande qu'un seuil  $f_C$  défini par l'utilisateur. Considérons par exemple la figure 3. Elle correspond à un réseau comportant 20% de cœurs défaillants, de sorte que de toute façon, l'accessibilité (moyenne) du PES ne peut dépasser 0.8. Cela explique la présence de la zone grisée inaccessible sur la partie droite de la figure. Maintenant, considérons le point B situé sur la courbe C=3, c'est-à-dire pour un réseau hexagonal. Ce point signifie que la probabilité que le PES atteigne 75% des cœurs n'est que de 0,6. Donc, statistiquement, si on choisit de sélectionner les puces qui permettent de joindre au moins 75% des cœurs sur 80 % possibles, le rendement de production ne sera que de 60 %. Similairement, le point A montre que la probabilité de contacter au moins 77 % des cœurs (sur 80% non-défectueux) est égale à 0.94 pour le réseau carré.

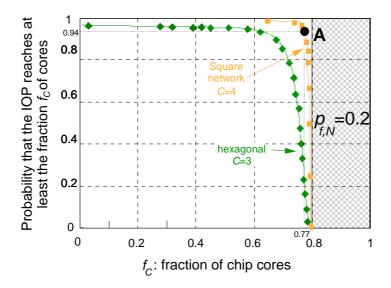

Figure 3. Simulations d'accessibilité dans un chip comportant 20% de cœurs défaillants

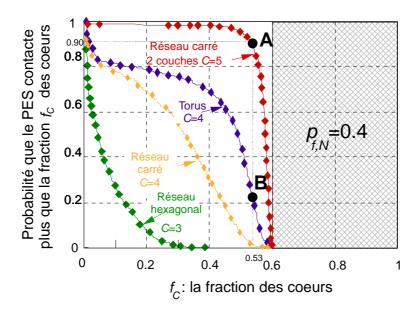

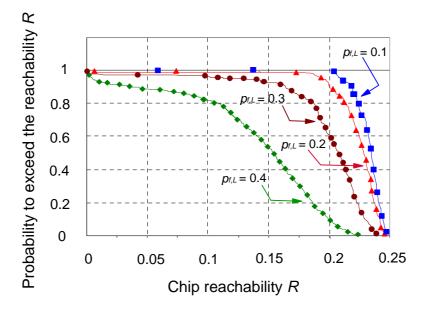

La figure 4 suivante montre que l'accessibilité se dégrade radicalement quand il y a 40% de cœurs défectueux dans le réseau. En effet, supposons que l'on exige que le PES puisse contacter au moins 53% des cœurs (parmi 60% non-défectueux). La figure montre que cela est quasi-impossible dans un réseau hexagonal ou un réseau carré! Les résultats pour le tore (représentés par le point B) sont légèrement meilleurs, sans être satisfaisants puisque

seulement 20% des puces réaliseraient la condition mentionnée. Seule la topologie avec la plus haute connectivité C=5 (c'est-à-dire le réseau carré à 2 couches) fournit des résultats satisfaisants, puisque la probabilité de contacter au moins 53% des cœurs est égale à 0.9.

Figure 4. Simulations d'accessibilité dans un chip comportant 40% de cœurs défaillants

Ces deux figures illustrent un résultat général de la thèse qui est que la topologie carrée (donc de connectivité 4) peut être considérée comme une solution satisfaisante aussi longtemps que la probabilité que le nœud soit défectueux ne dépasse pas 0.2. Au-delà de ce seuil, la connectivité du nœud doit être augmentée pour maintenir l'accessibilité à des valeurs élevées, disons typiquement supérieure à 80-90 %.

Nous avons aussi étudié la réduction de l'accessibilité due à la présence de liens défectueux dans le réseau (section 4.2.2 de la thèse). En fait, les interconnexions défectueuses sont mieux tolérées que les cœurs du point de vue du maintien de l'accessibilité, ce qui n'est pas une réelle surprise. Nous avons conclu que pour la plupart des topologies étudiées (réseau hexagonal, carré, en tore ou à deux couches), une fraction R de liens défectueux réduit approximativement deux fois moins l'accessibilité que le même pourcentage des cœurs défectueux. Cette conclusion peut être utilisée pour équilibrer la protection que l'on décide d'implémenter pour protéger la puce à la fois contre les liens et les cœurs défectueux. Les

résultats de simulation ont permis d'estimer le rendement de production en fonction de la probabilité de défaillance du nœud ou de l'interconnexion selon la topologie du réseau.

Comme la découverte des routes basée sur la diffusion isotrope (broadcast) peut provoquer des congestions dans le réseau résultant de la corrélation des trajets dans un réseau asynchrone, nous avons développé et simulé une nouvelle méthode pour équilibrer le trafic (section 4.2.4 de la thèse).

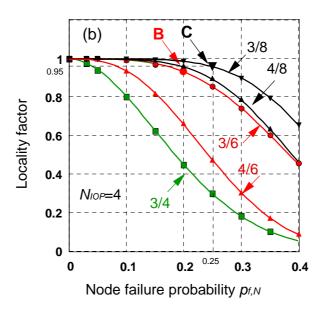

### F2.5.2 Architecture multi-port

Les architectures multiports ont aussi été étudiées extensivement. Nous avons :

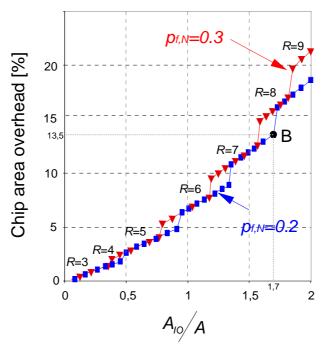

- Calculé le surcoût en circuiterie (i.e., en redondance d'implémentation) nécessaire pour tolérer les PES défectueux (section 4.4.1 de la thèse). Il ne faut pas oublier que les PES sont des éléments particulièrement critiques de la puce puisqu'ils sont des points de passage obligés de ses communications avec son environnement. Il faut donc implémenter des redondances pour tolérer à la fois l'occurrence des fautes de fabrication et des fautes dynamiques en opération dans les PES. On a conclu que la protection des ports devient extrêmement difficile si la probabilité de défaillance du nœud dépasse 0.3, surtout si la taille du PES est comparable avec la taille du nœud.

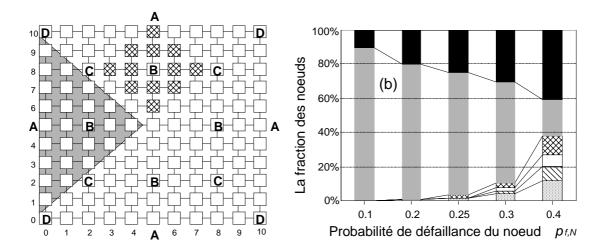

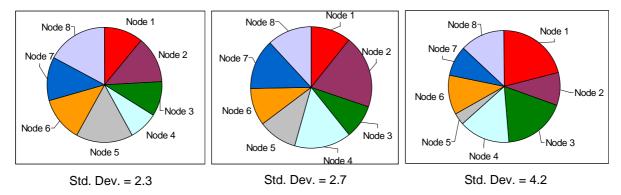

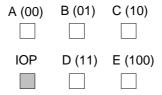

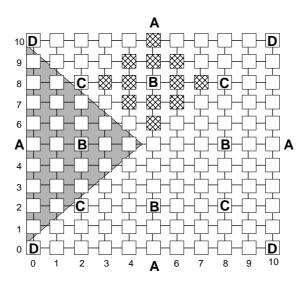

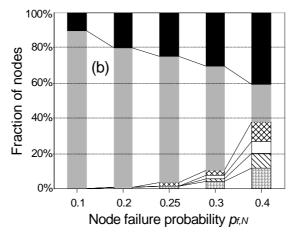

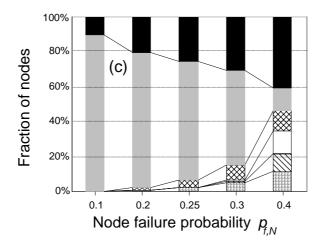

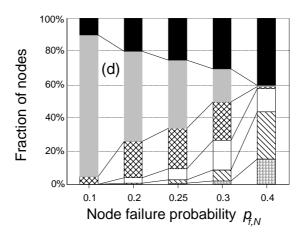

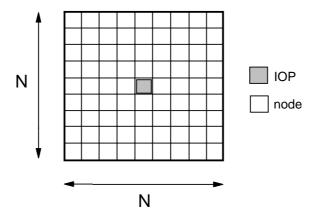

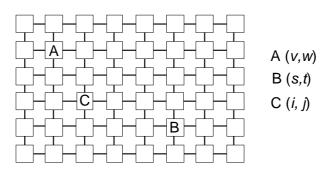

- Etudié le meilleur placement des ports dans le réseau carré comportant des cœurs défectueux du point de vue du partage des cœurs et de l'accessibilité des PES (section 4.4.2 de la thèse). La figure 5 illustre cette étude. Elle représente un réseau carré avec 100 nœuds et quatre PES qui peuvent être positionnés dans les places indiquées par les lettes A, B, C ou D. La figure à droite donne le partage des cœurs, c'est-à-dire la fraction de cœurs qui sont soit défaillants (■), soit accessibles par 1 à 4 PES (symboles ⋈, □, ⋈, ), soit inaccessibles (□) en fonction de la fraction de nœuds défaillants dans le réseau. La figure montre clairement que l'accessibilité par plusieurs PES se dégrade quand plus de 25% des cœurs sont défaillants dans le réseau. La meilleure accessibilité aux cœurs est obtenue quand les PES sont positionnés sur les places marquées par les lettres B.

Figure 5. Architecture multiport et les résultats d'étude de l'accessibilité des nœuds. ■ : Cœurs défaillants, □ : cœurs partagés par 4 PES, ⊠ : cœurs partagés par 3 PES, □ : cœurs partagés par 2 PES, □ : cœurs partagés par un seul PES; □ : cœurs inaccessibles

- Etudié l'efficacité de la découverte des routes et défini deux métriques de validation des puces (section 4.4.3 de la thèse). Les métriques reposent (comme pour les architectures uniport) sur la capacité des ports de contacter les cœurs selon la distribution de la charge de traitement. Les simulations montrent que dans le cas de lourde charge de travail, il est très difficile de garantir l'équilibre de la charge de travail parmi les ports si la fraction de nœuds défectueux dans le chip dépasse 20%. L'impact de liens défectueux sur l'accessibilité des nœuds est moins grande (par rapport à l'impact des nœuds défectueux) que dans le cas des architectures uniport.

- Montré que l'accroissement de la connectivité des PES (importante pour préserver la bande passante du PES en présence de lien défaillants) n'a qu'un effet positif mineur sur la capacité du port de contacter les cœurs (section 4.4.3 de la thèse).

### F3. Allocation et exécution des tâches

L'allocation des tâches sur les cœurs disponibles afin d'exécuter un traitement ne peut être effectuée que de façon dynamique (c'est-à-dire à l'exécution) dans les puces défectueuses. Il a deux raisons essentielles à cela :

- 1. Le compilateur ne peut pas savoir quels cœurs sont défectueux dans une puce. En effet, leurs positions changent d'une puce à l'autre.

- 2. Il ne peut pas savoir non plus quels cœurs sont disponibles pour exécuter un traitement à un instant donné puisque cela dépend de la compétition entre les différents PES (pour verrouiller les ressources de traitement) et de l'historique de traitement de la puce.

Aussi avons-nous développé un protocole de verrouillage des cœurs et d'allocation des tâches qui permet à plusieurs PES de partager les nœuds (section 5.1 de la thèse). Ce protocole est basé sur l'échange de deux messages, d'une part l'émission de requêtes de verrouillage par les PES et sur la réponse (accord ou rejet) des cœurs disponibles pour réserver le traitement. C'est une variante du *contract net protocol* (CNP). Il faut souligner que l'arbitrage dans la réservation des ressources de traitement est fait par chaque nœud contacté (qui donne ou ne donne pas sont accord. Ce mécanisme est donc totalement distribué et ne requiert aucune coordination entre les PES. Il est aussi indépendant du nombre de PES.

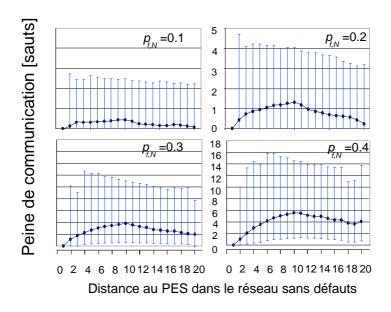

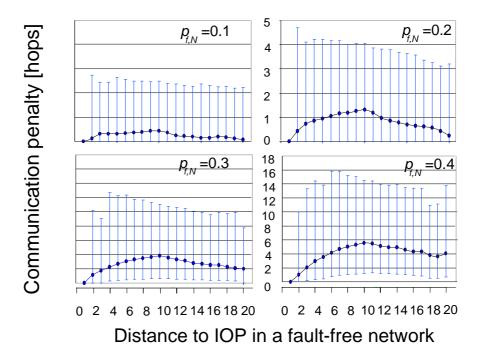

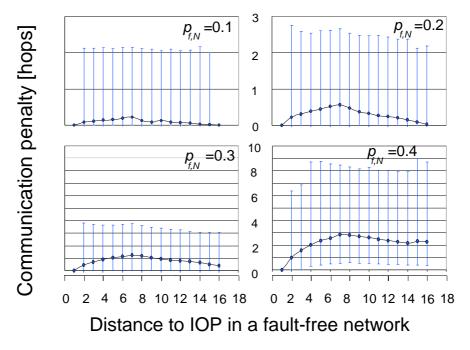

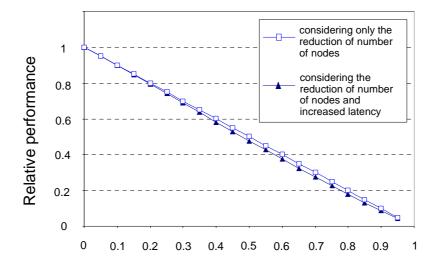

Nous présentons également des simulations qui calculent l'accroissement de la latence de communication induite par la présence des nœuds défectueux (section 5.2). Néanmoins, il a été estimé que la dégradation de la performance provoquée par la latence est négligeable en comparaison avec la dégradation provoquée par la réduction du nombre des bons nœuds sur une puce. La figure ci-dessous montre la peine de communication pour le réseau carré. Elle est mesurée comme le nombre moyen des sauts additionnels entre un nœud et le PES résultant de la présence des nœuds défectueux. Les barres verticales démontrent l'écart type autour de la moyenne. Clairement, l'accroissement de la latence devient important quand  $p_{f,N}$  dépasse 0.2.

Figure 6. L'accroissement de la latence de communication dans le réseau carré

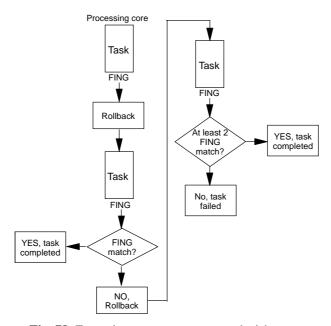

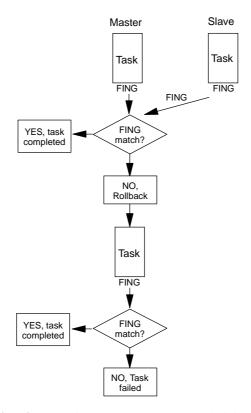

Nous avons également présenté et comparé trois méthodes d'exécution des tâches basées sur la redondance spatiale ou temporelle (section 5.3 de la thèse) permettant de tolérer l'occurrence de fautes transitoires en opération. Les meilleurs résultats de simulations (conformément à nos modèles) ont été fournis par la méthode basée sur la redondance d'exécution temporelle. Cependant, la méthode basée sur la duplication spatiale devrait être privilégiée (bien qu'elle donne des résultats un peu moins bons) parce qu'elle permet aussi de tolérer les fautes permanentes présentes en opération, éventuellement des fautes non détectées pendant la phase de diagnostique (en raison de la couverture incomplète du test initial) ou bien des fautes dues au vieillissement.

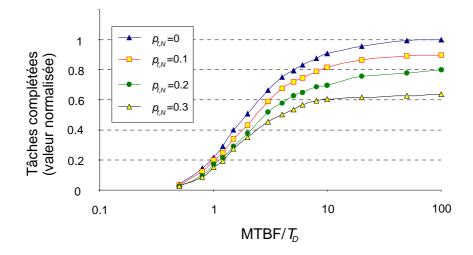

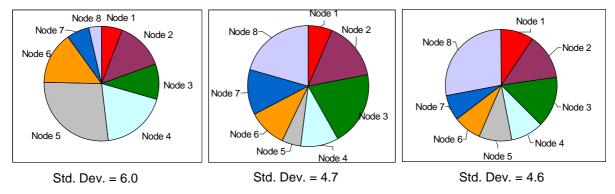

A titre illustratif, nous décrivons brièvement ci-dessous l'étude de l'efficacité de traitement lorsque l'on considère la redondance d'exécution temporelle en présence de fautes transitoires. L'étude est menée de la façon suivante en utilisant le simulateur MASS :

- 1) On simule un réseau carré 10x10= 100 processeurs avec 4 PES.

- 2) Le simulateur génère au hasard une fraction de nœuds défectueux dans le réseau, conforme au paramètre  $p_{f,N}$ .

- 3) Chaque port exécute le mécanisme de découverte des routes.

- 4) Chaque port commence à allouer des tâches en exécutant le CNP décrit précédemment, ce qui permet de partager dynamiquement les cœurs disponibles.

- 5) Pendant l'exécution de la tâche par un cœur, le simulateur génère aléatoirement des erreurs transitoires conformes au temps moyen entre défaillance (MTBF).

- 6) Le mécanisme d'exécution des tâches basé sur la redondance temporelle est implémenté : chaque cœur exécute une tâche deux fois. La troisième exécution est nécessaire si les résultats des deux exécutions précédentes sont différents comme conséquence d'une erreur transitoire.

- 7) Le simulateur compte le nombre de tâches complétées par tous les cœurs au cours de la simulation.

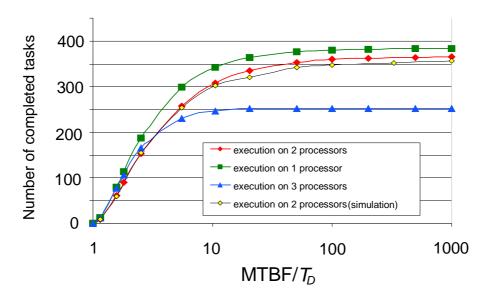

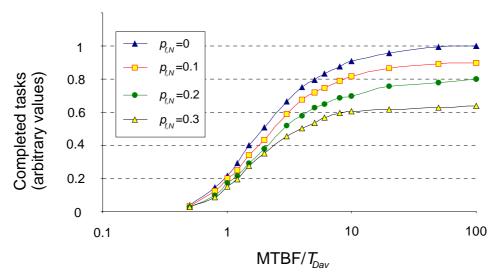

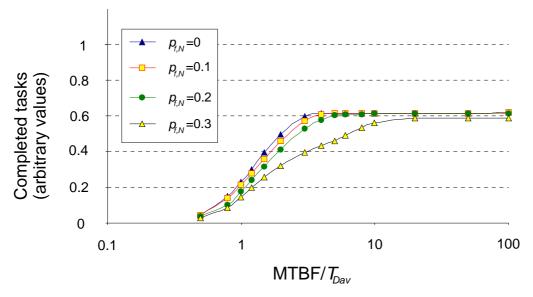

Figure 7. Résultats des simulations de l'allocation et l'exécution des tâches

La figure 7 permet d'analyser l'impact des fautes transitoires et permanentes sur la performance d'une puce. Elle montre que la fraction de nœuds défectueux est le facteur dominant entraînant une réduction de la performance. Néanmoins la dégradation induite par les erreurs transitoires devient dominante quand le temps moyen entre pannes devient comparable à la durée moyenne de la tâche  $T_D$ . De plus, nous avons révélé qu'il est très difficile d'estimer l'impact des fautes sur la puissance de traitement d'une puce parce que la dégradation de la performance dépend largement des paramètres d'opération du chip tel que la charge de travail.

#### F4. Conclusion

Comment assurer la sûreté de fonctionnement des futures puces complexes fabriquées dans les futures nanotechnologies ? L'accroissement des défauts (lié à la réduction des dimensions) sera probablement si important que la protection des circuits et la tolérance aux fautes dans la seule couche physique sera insuffisante pour garantir la sûreté de fonctionnement. Elle devra être acquise en mettant en œuvre des mécanismes de protection et de tolérance aux fautes dans les différentes couches, c'est-à-dire au niveau du composant, du circuit, au niveau architectural et dans les mécanismes d'exécution. Plus précisément, le rôle de la protection exécuté par chaque couche est de réduire l'impact des fautes non tolérées et se propageant depuis les couches inférieures. C'est donc la protection combinée de tous les niveaux qui permettra d'assurer la sûreté du fonctionnement des futures puces.

Cette thèse propose une méthodologie de tolérance aux fautes au niveau architectural dans les puces multi-cœurs massivement défectueuses. L'idée principale de ce travail est qu'une puce devra être organisée en une architecture réplicative (ce qui résout en grande partie le problème de la complexité) et devenir aussi autonome que possible pour augmenter sa résilience contre les défauts permanents et les erreurs transitoires apparaissant en opération. C'est pourquoi nous introduisons plusieurs méthodes d'auto-configuration de la puce qui permettent de détecter et isoler les cœurs défectueux, de désactiver les cœurs isolés, de configurer les communications et de diriger l'allocation et l'exécution des tâches. L'efficacité des méthodes est étudiée en fonction de la fraction d'interconnexions ou de cœurs défectueux et du taux d'erreurs transitoires. S'il faut simplement résumer ce travail sur un seul résultat, la conclusion principale est que jusqu'à typiquement 20% de cœurs défectueux, les méthodes d'auto-configuration proposées permettent de tolérer efficacement les éléments fautifs dans des réseaux carrés, mais qu'il devient bien difficile de les tolérer au-delà de cette valeur limite. Une solution est alors d'accroître la connectivité des nœuds.

# **Table of contents**

| 1. | INTRODUCTION                                              | 1  |

|----|-----------------------------------------------------------|----|

| 2. | ISSUES AND CHALLENGES IN CURRENT VLSI CHIPS               | 5  |

|    | 2.1 Introduction                                          | 5  |

|    | 2.2 VARIABILITY PROBLEM IN THE FUTURE NANOTECHNOLOGIES    |    |

|    | 2.2.1 Manufacturing faults                                |    |

|    | 2.2.2 Transient faults                                    |    |

|    | 2.3 Complexity problem                                    |    |

|    | 2.4 POWER CONSUMPTION ISSUE                               |    |

|    | 2.5 PROBLEMS RELATED TO GLOBAL CLOCKING                   | 16 |

|    | 2.6 MEMORY-PROCESSOR PERFORMANCE GAP                      | 18 |

|    | 2.7 SCALABILITY IN MULTIPROCESSOR ARCHITECTURES           | 20 |

|    | 2.7.1 Small-scale multiprocessors                         | 20 |

|    | 2.7.2 Networks-on-chip                                    | 21 |

|    | 2.7.3 Topology                                            | 23 |

|    | 2.7.4 Chip multiprocessor                                 | 24 |

| 3  | SELF-CONFIGURATION MECHANISMS                             | 27 |

|    | 3.1 GENERAL-PURPOSE NANOCHIP ARCHITECTURE                 | 27 |

|    | 3.1.1 Memory architecture                                 |    |

|    | 3.1.2 Self-configuration methodology                      |    |

|    | 3.2 SELF-DIAGNOSIS THROUGH MUTUAL TESTS                   |    |

|    | 3.2.1 Comparison of testing methods                       | 32 |

|    | 3.2.2 Defect locations                                    |    |

|    | 3.2.3 Mutual tests                                        | 37 |

|    | 3.2.4 Isolation of defective nodes and links              | 38 |

|    | 3.3 SELF-DISCOVERY OF ROUTES                              | 41 |

|    | 3.3.1 Introduction                                        | 41 |

|    | 3.3.2 A brief reminder on communication                   | 41 |

|    | 3.3.3 Comparison of the efficiency of multicast protocols | 42 |

|    | 3.3.4 Route discovery mechanism                           | 45 |

|    | 3.4 Self-deactivation of defective cores                  | 47 |

|    | 3.5 Summary                                               | 50 |

| 4  | STUDY OF ROUTE DISCOVERY IN DEFECTIVE GRID                | 51 |

|    | 4.1 Introduction                                          | 51 |

|    | 4.2 ROUTE DISCOVERY IN UNIPORT ARCHITECTURES              | 52 |

|    | 4.2.1 Reachability in the presence of defective cores     | 53 |

|    | 4.2.2 Reachability in the presence of defective links     | 56 |

|    | 4.2.3 Production yield                                    | 61 |

|    | 4.2.4 Route randomization                                 |    |

|    | 4.3 CHIP SORTING AND VALIDATION                           | 71 |

|    | 4.3.1 Node importance factor method                       | 71 |

|    | 4.3.2 Allocation capacity method                          |    |

|    | 4.4 MULTIPORT ARCHITECTURES                               |    |

|    | 4.4.1 Protection of the IOPs                              | 79 |

| 4.4.2 Positioning of the IOPs                                    | 84  |

|------------------------------------------------------------------|-----|

| 4.4.3 Route discovery in multiport architectures                 |     |

| 4.5 SUMMARY                                                      |     |

| 5 DYNAMIC ALLOCATION AND REDUNDANT EXECUTION                     | 95  |

| 5.1 DYNAMIC TASK ALLOCATION                                      | 95  |

| 5.2 CALCULATION OF COMMUNICATION LATENCY                         |     |

| 5.3 REDUNDANT EXECUTION OF TASKS                                 | 104 |

| 5.3.1 Introduction                                               | 104 |

| 5.3.2 Transient faults in future nanoscale chips                 | 105 |

| 5.3.3 Error detection methods                                    | 105 |

| 5.3.4 Comparison of redundant execution methods                  | 109 |

| 5.3.5 Impact of permanent and transient faults on task execution | 113 |

| 5.4 Summary                                                      | 117 |

| 6 CONCLUSION                                                     | 119 |

| APPENDIX A: A BRIEF REMINDER ON COMMUNICATION                    | 121 |

| APPENDIX B: MASS SIMULATOR                                       | 124 |

| APPENDIX C: MULTIPROCESSOR ARCHITECTURES                         | 128 |

| APPENDIX D: NODE IMPORTANCE FACTOR                               | 131 |

| APPENDIX E: COMPARISON OF EXECUTION METHODS                      | 134 |

| REFERENCES                                                       | 137 |

#### 1. Introduction

The invention of general-purpose processor truly revolutionized the world. Who would have thought in 1970 that the simple Intel 4004 chip will be one of the most important human inventions in the 20<sup>th</sup> century? The idea behind designing this microprocessor was quite simple: it was meant to be used in a calculator! Actually, the only reason why Intel developed a general-purpose chip (GPC) was that they had no experience in designing dedicated chips. Other processor architectures were designed in the following years and with the Intel 8080 processor, manufactured in 1974, a new era of microprocessors became a reality. Processors became the leader chips in the world of constantly evolving electronics. Many new ideas and technologies in electronics were first implemented to improve the processing power of microprocessors. In fact, some ideas were even especially and intentionally developed to be used in the microprocessor design.

The permanent increase during over three decades of the processing power of GPC results from the conjunction of miniaturization (i.e., the reduction of dimensions of transistors and interconnects), of architectural evolutions of GPCs and of changes in the execution model of applications:

- Miniaturization enables increasing the number of transistors and the operation frequency.

- Changes in the architecture (such as the introduction of several levels of cache, of the instruction parallelism and of branch prediction, etc.) have mostly enabled mitigating the increase of access latency to the main SDRAM memory.

- New execution models (such as multi or hyper-threading) have also been contributing to increase the processing power by avoiding pending states of the processor in multitask context.

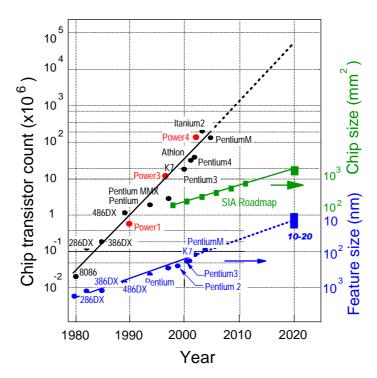

Regarding miniaturization, we must settle the inevitable question to know whether the observed downsizing will continue indefinitely or if ultimately, some physical barriers (in particular the granularity of matter) will make the fabrication of smaller transistors impossible. This question was raised several decades ago but, until now thanks to constant technology evolutions, chip manufacturers have been able to sustain this trend. Today, designers and manufacturers generally agree that the transistor size will continue to decrease to reach nanometric dimensions and that they will be able to fabricate nanochips in the next decade (i.e., chips with nanometric transistors). Fig. 1 displays the evolution of the transistor count, the chip area and the technology feature size. It also shows the trends expected until 2020, on the basis on an exponential extrapolation which is the continuation of the evolution during 3 decades. In particular, the upper most curve shows that the number of transistors on

chip is expected to increase to reach hundreds of billions. Does that mean that designers face no problems and that the constant increase of the processor's performance is ensured?

Fig. 1: Processor architecture roadmap

Despite the optimistic extrapolations shown in Fig. 1, there are now more challenges that need to be taken into consideration than in any moment of processor design history. In this thesis, we focus on the three following problems:

- 1. The architectural scalability: Uniprocessor architecture no longer guarantees the desired performance gain because there is a crisis on how efficiently "using" the increased number of transistors. In other words, there are no new architectural solutions in uniprocessors which would ensure the desired performance gain. The current trend consists in increasing the number of cores in the framework of symmetrical multiprocessor architecture. However, this architecture lacks scalability and is not a long-term solution.

- 2. **The power dissipation**: Designers can no longer increase the chip operating frequency because the power dissipation would become prohibitively large at higher frequencies.

- 3. The operation dependability in massively defective technologies: The transistor channel size is becoming so small that it will be comparable to atomic dimensions, increasing the dispersion of transistor characteristics and consequently the fraction of defective (and potentially failing) elements. In fact, the defect ratio will probably become so high that the production of fault-free chips will be very difficult and the production yield will dramatically decrease. Moreover, the risk of transient errors during the processor operation will have to be considered especially in the nanoscale technologies.

Not surprisingly, designers already work on new ideas and solutions which will enable overcoming in the future the above mentioned problems. The improvements are possible at many levels, from the component-level to the application-level.

In this thesis we present architectural-level solutions to improve the operation dependability and steadily increase the performance of multi-core chips. We present our idea of a future multiprocessor architecture and (re)configuration mechanisms which partially solve the problems mentioned in the previous paragraph. Self-organization is the basic and underlying idea of this thesis. Our view is that:

- 1. Due to the increase in complexity, future chips should evolve towards replicated architectures built from a small number of well-controlled building blocks, and above all that

- 2. The basic mechanisms of fault diagnosis and configurations (necessary to tolerate the faulty blocks) should be executed by the chip itself, with as little as possible external control. In other words, future nanochips fabricated in the massively defective technologies should exhibit some kind of autoimmune mechanisms similarly to biological tissues to maintain their processing capabilities. In this thesis, we essentially consider chip self-test via mutual diagnosis and route self-configuration (RSC) as autoimmune mechanisms, and we study the limit of the RSC efficiency as a function of the fraction of defective building blocks. We consider two kinds of defective blocks: cores, or internode links. At runtime, special mechanisms based on execution redundancy should be also implemented to eliminate errors induced by transient faults.

#### This thesis is organized as follows:

- In the second chapter, we present the current challenges in the design and fabrication of VLSI chips. We also briefly introduce some new emerging solutions which should be envisaged in the future nanoscale technologies.

- In the third chapter, we present the architecture of general-purpose nanochips, which we consider to be a solution to the challenges presented in chapter two. Moreover, we describe several chip self-configuration mechanisms, which allow coping with faults in the future nanoscale chips.

- The fourth chapter concentrates on estimating the impact of permanent faults on chip communication performance. Both core defects and interconnect defects are studied and we present both simulation results and analytical calculations.

- In the fifth chapter, we analyze the impact of both permanent and transient faults on task allocation and execution in a chip. Several protection methods against transient faults are described and compared.

- The general conclusion is presented in the sixth chapter.

| Chapter 1. Introduction |

|-------------------------|

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

## 2. Issues and challenges in current VLSI chips

#### 2.1 Introduction

The world's first microprocessor was introduced in 1971, a simple Intel 4004 architecture which was composed of only 2,300 transistors. According to Moore's Law [1], the number of transistors in a chip should double every 18 months. In other words, every year and 6 months twice more complex chips should be fabricated. Following this rule, the processing core evolved from the relatively primitive 4004 processor to powerful multicore processors with almost billion transistors. The list of major improvements to the architecture of mainstream single core processors is shown below:

- 8 bit bus width in 8008 processor (1972)

- Single 5V supply voltage in 8085 processor (1974)

- Instruction pipelining in 8052 processor (1975)

- 16 bit bus width in TMS9900 processor (1976)

- Interrupt controller and DMA controller on chip in 80186 processor (1982)

- 32 bit bus width in iAPX432 processor (1981)

- Multitasking in 80286 processor (1982)

- Branch prediction in SPARC processor (1985)

- Level 1 cache on chip in 80486 processor (1989)

- Integrated floating point unit chip in 80486 processor (1989)

- Out-of-order execution in POWER1 processor (1990)

- 64 bit bus width in PowerPC 620 processor (1994)

- Superscalar architecture in Pentium processor (1995)

- Level 2 cache on chip in Pentium Pro processor (1995)

- SIMD instruction set in Pentium Pro processor (1997)

- SIMD instruction set for floating point operations in K6-2 processor (1998)

- Advanced Transfer Cache in Pentium II Xeon processor (1998)

- Prefetch cache predictor and a translation look-aside buffer in Athlon 4 processor (2001)

- HyperThreading in Pentium 4 processor (2002)

- HyperTransport in Athlon 64 processor (2003)

Note that meanwhile, the operating frequency increased from 104 kHz to impressive several gigahertz, the supply voltage decreased from 12V to about 1.3V and the transistor channel size reached nanometer dimensions.

As we scroll down the above list, we may notice that the architectural improvements themselves have become more and more complex in terms of functionality and especially in terms of transistors' number. All these changes were made to achieve one main goal: increasing the chip processing power. It is undisputable that along three decades, this struggle has been successful. The processing abilities of contemporary processors reached a performance level that the manufacturers of the first processors never dreamt of.

However, in any domain, it is always necessary to question the cost of the success. More precisely, in the field of processor design, we should compare the processing power gain with the transistor count increase. We can introduce here a sort of efficiency metrics  $perf/n_t$ , where perf is the performance (measured for instance as the number of instructions executed per second) and  $n_t$  the transistor count. Of course, ideally  $perf/n_t$  should (at least) stay constant, which means that doubling of the number of transistors would allow twice greater performance, tripling of the number of transistors would allow three times greater performance etc. Nevertheless, in reality, the increase of the processing power is far from this ideal case. The relation of the performance perf versus the number of transistors  $n_t$  for different type of processors shows that simpler processors are usually more efficient than the most complex ones! Moreover, the ratio  $perf/n_t$  has systematically decreased as the chip size increased. In other words, the price to pay in terms of number of transistors (or chip area) for gaining more and more power has grown inexorably. Moreover, recent studies show that the dissipated power per transistor also increases which, as the chip size increases, is quickly becoming a significant design problem.

In the following sections of this chapter, we precisely describe the problems which have to be solved so that processors continue to evolve toward more processing power.

## 2.2 Variability problem in the future nanotechnologies

### 2.2.1 Manufacturing faults

Current processors are fabricated using the 45-nm process technology will scale down, the manufacturers will face new problems resulting from atomic fluctuations. Let us now describe these problems more precisely. Intuitively, one may guess that the influence of atomic fluctuations will increase greatly when reducing the transistor dimensions. For example, as the doping density stays at the same level, we might be able in the future to fabricate a transistor with a channel area so small that it will contain only one single doping atom. Not only will it be hard to predict the transistor's properties, but also it will be extremely difficult to fabricate transistors with reproducible properties. One may even settle a more provocative question: what happens if the technology scales down so much that there will be some transistors with no doping atoms in the channel area?

Currently, the transistor failure rate (TFR, defined as the percentage of malfunctioning transistors) is held at acceptable level, but inevitably nanometric technologies will be much more defective. It is almost impossible to warrant that all transistors will be fault-free in the future large ULSI including hundreds of billions transistors. One may of course perform testing after production and select only fault-free chips, but if the TFR is high, the production yield will be unacceptably low. There would have no sense to manufacture chips if for instance 98% of them could not be validated for deployment.

However, the studies conducted by the major chip manufacturers show the variability of transistor parameters is becoming in the future nanoscale technologies a problem more critical than the occurrence of defective transistors [2][3][4]. More precisely, most transistors will have different physical characteristics because of the variations in the process parameters such as:

- diffusion depths,

- density of impurities,

- resolution of the photolithographic process.

As a result, all (or most) transistors work, but a significant fraction of them will have reduced performance. The changes in the transistor parameters affected by the process variations may lead to:

- changes in the channel geometry,

- reduced  $I_D$  current,

- dispersion of threshold voltage  $V_{T_i}$

- increased gate capacitance.

<sup>(1) 45</sup> nm is the MOSFET transistor channel length.

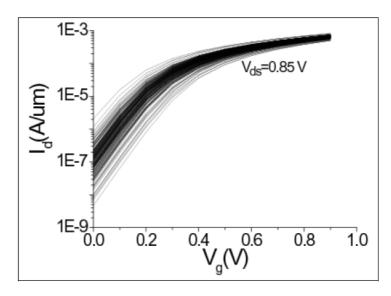

Fig. 2: Dispersion of transistor characteristics (source: [4])

Fig. 2 shows the estimation of the dispersion of the current/voltage characteristics for 200 transistors fabricated in a nanoscale technology. The transistors are of 30x30 nm size and are macroscopically identical. However, it can be easily seen that the differences in their current-voltage threshold are very significant. The variability will probably increase when considering transistors with reduced channel length.

Why are the fluctuations of intrinsic transistor parameters dangerous for the proper circuit operation? Let us reuse the example presented in [4]. In a 10-billion-transistor chip, if we assume some Gaussian distribution of transistor parameters, at least 20 transistors are expected to have a  $6\sigma$  deviation in their parameters ( $\sigma$  being a standard deviation). If the threshold voltage standard deviation is in the range of 20–30 mV and if the supply voltage is 0.85 V, there will be at least 20 transistors with threshold voltage equal to zero or to half the supply voltage.

Moreover, fluctuations may not directly cause the complete failure of the transistor, but the dispersion of propagation times on critical paths. This in turn may lead to device malfunction, as most modern synchronous chips operate under very strict timing constraints. Consequently, the production yield will decrease, as not all chips will be able to operate at the nominal frequency. The manufacturer will be forced to decrease the nominal frequency (to increase the yield) or to sort the chips versus their top operation frequency.

The fundamental question is: what will be the TFR of future nanotechnology? Currently, the TFR of a CMOS transistor is quite low. According to Infineon, the typical TFR in the 0.35-µm CMOS process is of the order of 1-2x10<sup>-8</sup> [6]. According to Nikolic et al [7], the TFR was in the range 10<sup>-7</sup>-10<sup>-6</sup> in 2002. We show below that when the TFR will reach approximately 10<sup>-5</sup> (which is very likely to happen in the nanoscale technologies), we have to abandon the idea of producing fault-free chips, even when applying redundancy-based protection techniques in the physical layer.

The most popular protection technique, called N-modular redundancy (see for example [8]), is based on dividing the chip into "elementary" blocks and replicating each block N times. The voting technique is then used to provide fault-free operation even if some defective transistors

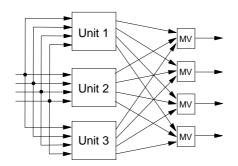

are present in some blocks. More precisely, even if a block provides a faulty output, the other corresponding blocks will "outvote" it (assuming of course that the majority of blocks and the voter are fault-free). Fig. 3 below displays a simple example of 3-modular redundancy.

Fig. 3: Three modular redundancy example

The figure shows the example of such a redundant block, which includes majority-vote gates (MV). Each unit replicates a 4-bit combinatorial block. The relative overhead sacrificed for redundant elements is N-1, when the area needed for the voting circuit may be neglected.

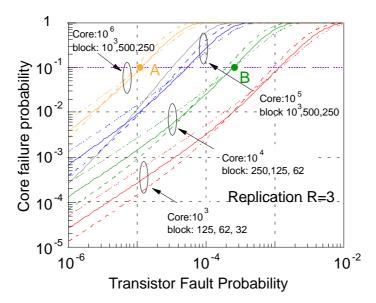

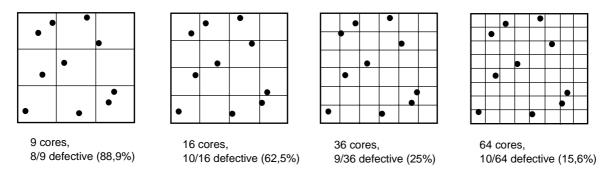

Let us now consider an example of a multi-core chip. Fig. 4 shows the dependence between the transistor fault probability (TFP) and the failure probability of a core split in basic blocks of various sizes. It must be emphasized here that this figure is based on the pessimistic assumption that one defective transistor causes the failure of the entire block. It is assumed that each block is protected using triple modular redundancy (TMR). The core size ranges from one million transistors (see the 3 uppermost curves in the top left corner) to thousand transistors (see the 3 bottommost curves). For each core size, we consider several sizes of the basic building block. For instance, the 3 curves in the top left corner show the variation of the failure probability of the million-transistor core when we consider its decomposition in blocks with 1000, 500 or 250 transistors.

**Fig. 4**: Core failure probability versus transistor fault probability for chips protected with triple modular redundancy

Point A for example shows that the failure probability of a 1-million transistor core is approximately 10<sup>-1</sup> when the transistor failure probability is 10<sup>-5</sup>. Consequently, it means that even if we use heavy protection in the physical layer by using TMR, there will still exist 10% of defective cores in a multicore chip. Thus, the figure clearly shows that even triple modular redundancy technique is not enough to assure failure-free chip operation.

#### 2.2.2 Transient faults

Transient (runtime) faults are perhaps even more menacing to the operation dependability of future chips than the permanent faults [9]. These errors are possibly caused by crosstalk, electromagnetic noise or cosmic radiation. In the future nanoscale chips operating at very high frequencies, the radiation noise from the gates will inexorably induce soft errors, especially when the gate operation voltage will be low. Moreover, additional errors may be caused by crosstalk. Already today, it is a great problem for large scale supercomputers [10]. As the dimensions and the supply voltage decrease, the same problems will appear in general-purpose processor chips. It may be safely stated that transient errors will constitute in the future a serious threat to the dependability of chip operation. A more detailed analysis of this problem can be found in section 5.3.2, page 105.

Therefore, we feel that assuming that nanochips will be fault-free would be dangerously misleading. Moreover, architecture designed with the assumption that there are no defects in the chip would be catastrophically inefficient or even inoperable if defects actually occur. Hence, in our work not only do we assume a defective technology, but also we consider nanochips to be massively defective. By massively defective we mean that a chip could comprise from several percent to as much as 40% of defective cores. One may wonder if indeed such defective technology would ever be implemented. The problem is that the core failure probability does not depend only on the technology and the transistor failure rate but also on the core complexity as shown in Fig. 4.

## 2.3 Complexity problem

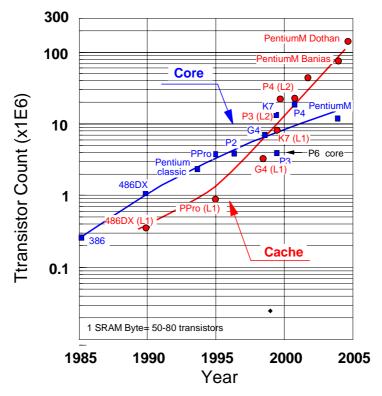

Until the end of the  $20^{th}$  century, the efficiency ratio  $perf/n_t$  (see section 2.1, page 5) was still at acceptable level. Designers succeeded in making significant improvements in the chip architecture, adding for instance more and more cache and, consequently, the processing power constantly increased. As shown in the figure below, in the eighties and in the beginning of the nineties, the size of processing cores and the size of caches evolved almost at the same rate. However, in the beginning of the 21th century, we may observe a significant change of trend: the cache memory size began to increase much faster than the processing core size.

Fig. 5: Evolution of core and cache memory architectures

The main cause of this evolution is that there has been a kind of crisis in the architectural evolution of single-core architecture because the investigations to improve the core processing power do not offer significant performance gain. Why? Perhaps, the main reason is that designers are unable to "simply" increase the processing power of computers because of the large access latency to the main memory [11] which is in fact a longstanding architectural problem. Even the most innovative changes to the core micro-architecture produce little performance gain when the latency necessary to access data (or instructions) in the main memory does cease increasing in processor cycle units. Or in other words, designers could probably succeed in increasing the processor's performance, but at unacceptable cost. For example, creating a new architectural solution which requires doubling the number of transistors on chip and provides only 5% of performance gain would clearly be inadvisable.

In this context, pure investigations on processor architectures were progressively reduced (or even stopped) at the end of the nineties, and the palliative solution has consisted in adding

more and more on-chip cache to mitigate the large off-chip memory access latency. It is exactly what is shown in Fig. 5. Of course, one may continue increasing the size of caches, maybe even introducing another cache level, but this solution leads to a dead end and becomes more and more inefficient due to the increase of the memory access latency.

A radical change of approach is needed, perhaps integrating the whole main memory on chip. The alternative solution which attracted many researchers recently is 3D stacked memory [12]. More precisely, the main memory is stacked on top of the processing chip and connected with it using through silicon vias (TSV) [13][14] which are in fact vertical interconnections between different chip layers. This solution provides very high bandwidth reaching dozens of GB/s and decreases the power consumption. See section 2.7.4, page 24 for a more detailed description of such a system.

## 2.4 Power consumption issue

The table below illustrates how the power consumption in processors has increased as processors became more and more complex in conjunction with the increase of the operating frequency.

Fig. 6: Power dissipation in the mainstream processors

As we can see, the power consumption in processors in the recent years has become dangerously high. High power dissipation means high temperatures which, unless complex cooling techniques are applied, may simply destroy a chip during operation. As early as in 2003, the major processor manufacturers stopped the frequency race (partly because of power dissipation problems) and began to switch to multi-core architectures. The tables below present the power dissipation in the mainstream single core processors (Table 1) and multi-core processors (Table 2).

| Processor type                       | Clock speed | Power consumption [W] |

|--------------------------------------|-------------|-----------------------|

| Pentium                              | 75 MHz      | 8.0                   |

| Pentium                              | 200 MHz     | 15.5                  |

| Pentium II                           | 450 MHz     | 27.1                  |

| Pentium III                          | 866 MHz     | 26.1                  |

| Athlon Thunderbird                   | 1000 MHz    | 54.3                  |

| Pentium III<br>(FC-PGA2)             | 1400 MHz    | 31.2                  |

| Athlon XP <i>Palomino</i><br>1700+   | 1433 MHz    | 64.0                  |

| Athlon XP<br>Thoroughbred B<br>2200+ | 1800 MHz    | 62.8                  |

| Athlon XP <i>Barton</i> 3200+        | 2250 MHz    | 76.8                  |

| Athlon 64<br>Clawhammer 3400+        | 2400 MHz    | 89                    |

| Pentium 4-C                          | 2.4 GHz     | 67.6                  |

| Pentium 4 HT                         | 3.06 GHz    | 81.8                  |

| Xeon                                 | 3.2 GHz     | 110                   |

| Pentium D960 B1<br>Stepping          | 3.6 GHz     | 130                   |

Table 1. Power consumption in various single-core processors

| Processor type                                 | Clock speed | Power consumption [W] |

|------------------------------------------------|-------------|-----------------------|

| Core Duo T2500                                 | 2.0 GHz     | 31                    |

| Core 2 Duo E6600                               | 2.4 GHz     | 65                    |

| Dual Core Xeon<br>5060                         | 3.2 GHz     | 95                    |

| Athlon 64 X2 4800+<br>(Socket 939)             | 2.4 GHz     | 110                   |

| Athlon 64 X2 4800+<br>Brisbane (Socket<br>AM2) | 2500 MHz    | 65                    |

| Athlon 64 X2<br>Windsor 6000+                  | 3000 MHz    | 125                   |

| Core 2 Quad<br>QX9650                          | 3.0 GHz     | 130                   |

**Table 2.** Power consumption in various multi-core processors

If we compare the two tables shown above we see that the power dissipated in quad core processors is at the same level as in single core processors but of course multicore processors have much higher processing power.

Why exactly multicore processors allow reducing power consumption? The power dissipation can be approximated by the following equation:

Eq. 1

$$P = P_{dyn} + P_{stat} = ACV^2 f + VI_{leakage}$$

The first factor is of course the dynamic power which is lost due to charging/discharging chip capacities. The second factor is the static power lost because of leakage current. C represents the total capacitance of all gates and A is the percentage of switching gates.

Although the reduction of the transistor's channel dimensions provoked a considerable rise of the leakage current, the dynamic power is still the dominant factor in the above equation. So, in what follows, we will take only the dynamic power into account.

For the sake of our analysis, we assume that the operating frequency is proportional to the voltage. Consequently, we obtain:

Eq. 2

$$P \sim V^3$$

Bearing this in mind, let us now compare the power consumption and performance of single and dual-core processor. For the sake of analysis, we assume that the both cores in dual-core system correspond exactly to a single core processor. Assuming arbitrary units, the power consumption of a single core processor is 100% and its performance is equal to 100%. Following the analysis presented in [15], if we scale down in a dual core system the supply voltage to 85% of the value of the single core supply voltage. As a result we obtain:

- 15% reduction in frequency (as frequency is proportional to voltage)

- power consumption stays at the same level because there are two cores and each consumes 50% less power because of lower voltage (see Eq. 2)

- performance can be estimated at 180%

Thus, a significant performance gain is expected<sup>(2)</sup> without increasing the power consumption. This clearly proves that multicore architectures provide a good solution to increase processing power without largely increasing the power dissipation.

15

<sup>&</sup>lt;sup>(2)</sup> The principal weakness of this approach occurs when executing applications which cannot be parallelized, as they must be executed by a single core, which of course has reduced processing power with respect to the single core chip.

## 2.5 Problems related to global clocking

Contemporary high-performance microprocessors are still being built as completely synchronous chips. One single clock is distributed to all parts of the chip. Chip designers must ensure that the clock signal arrives at the same time to all parts of the chip (or at least within acceptable time limits). If this constraint is not fulfilled, the chip will simply function incorrectly. Until now, chip manufacturers have succeeded in designing synchronous chips but at great cost. According to [16], even 40% of total power consumption in a chip is sacrificed to distribute the global clock signal!

Another dramatic problem appears as the technology scales down to nanometer dimensions and the chip is getting larger, due to the increase of latency of the interconnects. If the interconnect latency between any two parts of the chip becomes comparable with the clock cycle, the chip will be desynchronized and should be designed differently. Moreover, the transistor speed increases significantly faster than that of interconnects. Therefore, in the near future, the delay caused by onchip interconnects will be so high that it will limit the operating frequency of synchronous chips. Paradoxically, the chip operation frequency will not be limited by the transistor speed as today, but by the interconnect speed. Ultimately, the high-speed integrated circuits would have to be designed without global clocking.

What are then the possible alternatives to global clocking? Completely asynchronous systems [18][19] may be considered. Although we are perfectly capable of manufacturing completely asynchronous systems in theory, they are unlikely to be widely accepted in the near future. The problems of this solution are: lack of CAD tools, lack of experienced designers and very difficult testing. Recently, EPSON manufactured 8-bit asynchronous microprocessor [17]. However, most other manufacturers agree that such dramatic change in approach is not entirely sound.

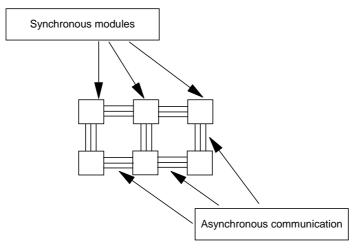

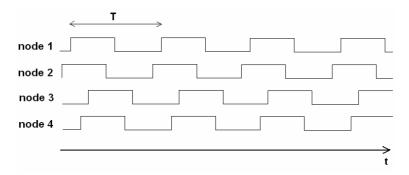

GALS (Globally Asynchronous Locally Synchronous) systems [20][21][22] are a compromise between synchronous and asynchronous systems. The chip includes multiple synchronous domains, but the domains' clock signals are not synchronized (see Fig. 7). Within one domain, the designers are able to use all tools and solutions applicable to synchronous systems. The problems arise on the verge of two asynchronous domains. The communication between the synchronous parts is asynchronous and special solutions have to be applied to ensure the fault-free transfer of signals between the synchronous zones.

Fig. 7: An outline of a GALS system

The major problems of GALS systems are:

#### - Metastability:

This problem has been known for many years [23] and it is especially dangerous in GALS systems. Let us now briefly outline the metastability problem. Metastability in flip-flops occurs when the value of input changes right before of right after the clock edge which triggers the flip-flop.

#### - Communication latency:

Data transfer between two asynchronous domains is considerably longer than the transfer between two synchronous domains. The latency overhead is needed to ensure correct synchronization and fault-free transfer of data. Multiple solutions have been proposed to maximize transfer speed in GALS [25][26]. However, the fastest transfer speed in GALS systems is still slower than the transfer speed in synchronous mode.

A solution similar to GALS has been proposed by Intel [27]. Their 80-core chip includes 80 independent 3mm<sup>2</sup> tiles. The "teraflop" chip has been designed to allow for the clock to arrive at individual cores out of phase. This mesochronous solution enables considerable power savings. Intel estimates that the power required for clock distribution to all of the tiles on the chip at 4 GHz is 2.2 W, which constitutes only 1.2% of total power consumption under load.

#### 2.6 Memory-processor performance gap

66 Mhz

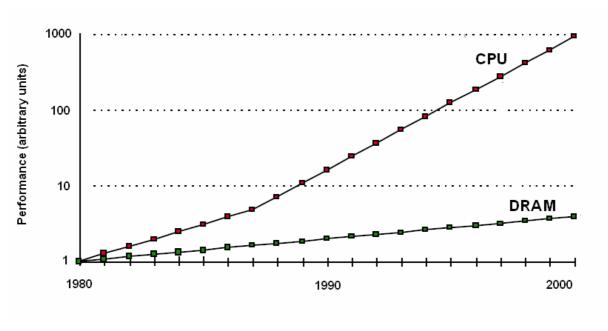

The large access latency to the data in the DRAM memory is perhaps the most important and permanent problem which has influenced the design of computers. Whereas the processor's frequency increased in accordance with Moore's Law, the frequency of DRAMs increased much slower. Therefore, the difference of performances of the CPU and the main memory (known as memory gap) also steadily grows (see Fig. 8 and Fig. 9).

Peak instructions per DRAM access

## 700 600 500 400 300 200 100 0 Pentium Pentium-Pro Pentium III Pentium 4

#### 200 Mhz 4 Ghz

Fig. 8: Number of executed instructions per DRAM access (source: [15])

1100 Mhz

Fig. 9: CPU-memory gap (source: inst.eecs.berkeley.edu/~cs162/fa06/Lectures/lec13-cachetlb.pdf)

Why exactly is the memory gap dangerous? The memory and CPU are parts of the computer system. When the processor executes a program, it must read a sequence of instructions and operands in the memory. Consequently, the processor is pending (of course in a simple sequential operation) as long as it accesses, reads and retrieves this information in the memory. This is especially dramatic in modern high-performance systems where the access latency to the memory amounts to hundred processor cycles. In this context, most of the architectural evolutions implemented during the last decade, have consisted on speeding up the access to data (or the instructions) without reducing the latency to the memory. Concretely, the memory gap problem has been mitigated by adding one, two, three cache levels, by increasing the cache size, by adding a prefetch mechanism, a branch prediction, and using multithreading in multitask execution mode.

However, it may soon become apparent that a more radical change in approach is needed to "close" the memory gap. An example of such radical approach is integrating the main memory on chip [28]. A more conservative solution to reduce the access latency to the memory is to build 3D chips with memory stacked on top of the processor (see section 2.7.4).

## 2.7 Scalability in multiprocessor architectures

Parallelism has always been a dream of computer designers [29]. Execution of multiple tasks simultaneously is believed to be the solution which could considerably increase computing performance. Processors used pipelined architectures in the eighties. Then, in the next decade instruction-level parallelism (ILP) was developed, as a way to execute multiple instructions in the same processor cycle. Super scalar processors [30] boosted considerably the processing power. However, it seems that for the reason given in section 2.3, there is no or very little possibility to exploit ILP on a uniprocessor. Recently, thread level parallelism was introduced allowing a significant performance gain and this trend is supposed to continue as multi-core processors emerged on the market. Consequently, it seems that we enter an era of thread-level parallelism as multicore processors will allow simultaneous execution of multiple threads.

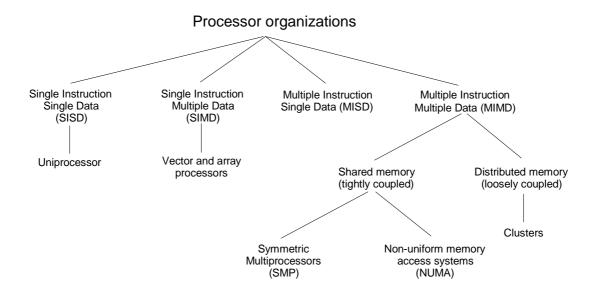

The detailed description of some well-known multiprocessor systems is presented in Appendix C. In what follows, we will mainly concentrate on the scalability problem in parallel architectures. A multi-core system is said scalable if it provides a constant improvement of the processing power as new cores are added to the system. In other words, adding new cores has no negative side effects on the communication bandwidth, the power consumption, etc. of the entire system and therefore, the performance rises almost linearly with the number of cores.

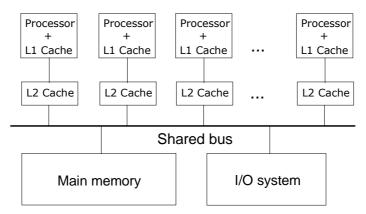

## 2.7.1 Small-scale multiprocessors

By small-scale multiprocessors, we mean architectures comprising typically up to 32 cores. Currently, the most popular architecture is based on the shared memory system with cores connected by a common bus. This solution, called Symmetrical Multiprocessors (SMP) is shown in Fig. 10 [31].

Fig. 10: Symmetric multiprocessor architecture

It is an example of UMA system (see Appendix C) and all cores are identical with the same access time to the main memory. SMP architecture is currently the most popular one. All cores can contact the shared memory via the shared address bus. The I/O subsystems are also shared by all cores. The management of task scheduling and execution is controlled by an

operating system which is in charge of the communication between processes. Note that this architecture provides high degree of interaction between processes contrarily to loosely-coupled multiprocessor systems like clusters.

The advantages of SMPs are the following:

- the existence of multiple cores transparent to the programmer,

- identical memory access times,

- easy inter-process communication,

- snoopy-based cache coherence,

- no need for routing protocol.

Note that this implicates that the failure of one core does not cause the failure of the entire system. For example, the Intel Core Solo processors [32] are simply dual core SMP with one faulty core.

SMP architecture has many important advantages. However, it is not scalable, just because the bus architecture is not scalable. More precisely, connecting more than several dozen cores to the same bus brings no performance gain because the heavy traffic on the bus prevents the efficient use of processors' resources and results in limited processing power. We may conclude that the solution based on symmetrical multiprocessors seems transitory and that the future belongs to scalable architectures, which have been extensively studied for decades in relation with the development of supercomputers.

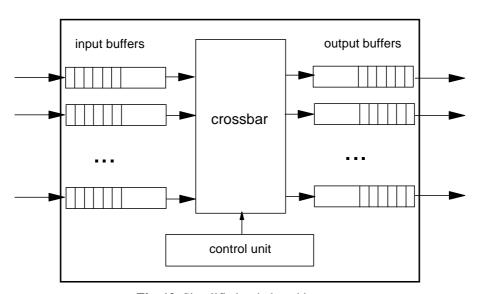

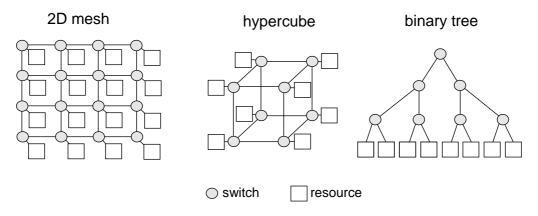

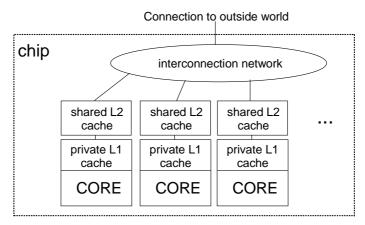

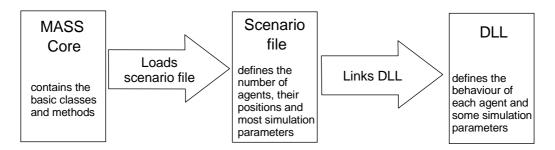

### 2.7.2 Networks-on-chip