# ÉCOLE DE TECHNOLOGIE SUPÉRIEURE UNIVERSITÉ DU QUÉBEC

# MÉMOIRE PRÉSENTÉ À L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

COMME EXIGENCE PARTIELLE À L'OBTENTION DE LA MAÎTRISE EN GÉNIE ÉLECTRIQUE M. Ing.

# PAR Nik RENQUINHA

AMÉLIORATION DE LA TECHNIQUE DE TEST ET DIAGNOSTIC CDIDDQ

MONTRÉAL, LE 10 JANVIER 2014

©Tous droits réservés, Nik Renquinha, 2013

## PRÉSENTATION DU JURY

# CE MÉMOIRE A ÉTÉ ÉVALUÉ

# PAR UN JURY COMPOSÉ DE :

M. Claude Thibeault, directeur de mémoire Département de génie électrique à l'École de technologie supérieure

M. Ghyslain Gagnon, codirecteur de mémoire Département de génie électrique à l'École de technologie supérieure

M. Nicolas Constantin, président du jury Département de génie électrique à l'École de technologie supérieure

Mme Catherine Laporte, membre du jury Département de génie électrique à l'École de technologie supérieure

# IL A FAIT L'OBJET D'UNE SOUTENANCE DEVANT JURY ET PUBLIC LE 12 DECEMBRE 2013

À L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

#### REMERCIEMENTS

J'aimerais tout d'abord remercier Claude Thibeault, mon directeur de maîtrise, pour sa patience exceptionnelle et sa détermination à avoir bien voulu me ramener sur le bon chemin tout au long de ma maîtrise. Il a été d'un très grand support moral et m'a toujours poussé à vouloir me dépasser et perfectionner mes compétences actuelles. Je suis, en grande partie, grâce à lui, un professionnel qui a toujours envie d'en savoir plus sur les sujets qui me passionnent. Son soutien m'a été d'une aide inestimable. Je le remercie aussi de ne pas avoir perdu confiance en la rédaction de ce mémoire malgré mon incapacité à organiser et formuler mes idées correctement. Il a toujours cru en mes idées et je lui dois une grande reconnaissance. Merci également à mon co-directeur, Ghyslain Gagnon, pour ses commentaires et suggestions.

J'aimerais aussi remercier ma copine Lysanne Arseneault-Fontaine pour l'appui moral, les encouragements et, bien sûr, la correction des fautes d'orthographe et de syntaxe de ce mémoire. Elle a grandement contribué à la bonne compréhension de cet écrit et elle a su passer un grand nombre d'heures à s'assurer que ce mémoire soit impeccable et représentatif de mes recherches.

Finalement, merci à Christelle Hobeika pour avoir rendu mes journées de rédaction et de recherche plus agréables tout en restant dans un environnement professionnel. Elle m'a donné plusieurs sources et idées qui m'ont été essentielles à la rédaction de ce document et elle a su me motiver tout au long de mes travaux de recherche. Son aide et son appui ont su me donner envie de me surpasser et d'en découvrir davantage dans ce domaine.

# AMÉLIORATION DE LA TECHNIQUE DE TEST ET DIAGNOSTIC CDIDDQ

#### Nik RENQUINHA

#### RÉSUMÉ

Ce mémoire a pour objectif l'amélioration de la technique de test et diagnostic CDIDDQ. Le travail réalisé consiste au perfectionnement de l'application du test CDIDDQ sur des circuits intégrés de type FPGA précédemment développée par Haithem (2011) afin d'accroître la capacité à détecter des défectuosités de type court-circuit. Ce mémoire débute par une présentation des notions de base ainsi qu'une revue de littérature où sont présentées différentes notions liées aux pannes de circuits intégrés, l'émulation de pannes sur FPGA, les techniques de tests basées sur le courant ainsi que les travaux passés dans l'application de la technique de test CDIDDQ.

Par la suite, la technique de génération des patrons de test CDIDDQ ainsi que les vecteurs associés à ceux-ci sont présentés. Nous avons utilisé la simulation afin de valider le fonctionnement des patrons de test pour ensuite passer à leur application sur des circuits intégrés de type FPGA. Comme première application expérimentale, nous avons choisi de refaire celle employée par Haithem (2011) en utilisant toutefois un différent système de mesure, ce qui nous a donné des résultats similaires.

Suite à cela, nous avons apporté des modifications sur le montage afin de réduire au maximum le bruit sur l'alimentation. Nous avons utilisé le même FPGA, mais cette fois-ci, sur une autre carte de développement, ce qui nous a permis d'augmenter notre capacité à détecter des pannes de court-circuit. Nous nous sommes aussi intéressés à l'application de la technique sur des circuits plus énergivores allant de 70mA à 3A.

Pour finir, nous présentons en détail la technique d'application expérimentale avec laquelle nous avons pu obtenir les meilleurs résultats. À ce stade, nous utilisons un différent montage, une différente architecture pour le testeur CDIDDQ, une différente technique d'acquisition et un logiciel spécialement mis au point pour les tests CDIDDQ. Ces modifications nous ont, entre autres, permis de détecter des pannes de court-circuit induisant des courants cinq fois plus faibles.

Mots-clés: FPGA, CDIDDQ, court-circuit, test

# AMÉLIORATION DE LA TECHNIQUE DE TEST ET DIAGNOSTIC CDIDDQ

#### Nik RENQUINHA

#### **ABSTRACT**

This thesis aims to improve the CDIDDQ test and diagnostic technique. The experiments consist in improving the CDIDDQ application, previously developed by Haithem, to detect short-circuit type defect in a FPGA circuit. This thesis begins with an introduction to basic concepts as well as a literature review describing integrated circuit fault concepts, FPGA fault emulation, current-based test techniques, and previous work on the CDIDDQ test technique applications.

Subsequently, the CDIDDQ test pattern generation technique as well as its associated vectors is presented. Simulation was used to validate test patterns in order to apply them on FPGA integrated circuits. We redid Haithem's (2011) experiment using a different measurement system, which produced almost identical results.

Afterwards, modifications were done on the setup in order to reduce power induced noise as much as possible. The same FPGA was used but on a different prototype board, which increased the ability to detect short circuit defects. We also looked into the application of the technique on energy-hungry circuits from 70mA to 3A.

Finally, the applied experimentation techniques with which we obtained the best results is laid out in detail. At that point, a different setup was used, as well as a different architecture for the CDIDDQ tester, a different acquisition technique and a software custom made for CDIDDQ tests. These modifications allowed us to detect bridge faults with a current five times smaller.

**Keywords:** FPGA, CDIDDQ, short-circuit, testing

# TABLE DES MATIÈRES

|      |                |                                                              | Page         |

|------|----------------|--------------------------------------------------------------|--------------|

| INTR | RODUCTIO       | ON                                                           | 1            |

| СНА  | PITRE 1 N      | OTIONS DE BASE ET REVUE DE LA LITTÉRATURE                    | 5            |

| 1.1  |                | tion                                                         |              |

| 1.2  |                | de base du test                                              |              |

| 1.3  |                |                                                              |              |

|      | 1.3.1          |                                                              |              |

|      | 1.3.2          | CDIDDQ                                                       | 8            |

|      | 1.3.3          | Émulation d'ASIC à l'aide de FPGA                            | 9            |

| 1.4  | Techniqu       | ues de mesure de courant pour le test                        | 10           |

|      | 1.4.1          | Utilisation de deux sources                                  | 11           |

| 1.5  |                | s CDIDDQ antérieur                                           |              |

| 1.6  | Conclusi       | on                                                           | 13           |

| СНА  | PITRE 2 L      | ES PATRONS DE TEST CDIDDQ                                    | 15           |

| 2.1  |                | tion                                                         |              |

| 2.2  | Les patro      | ons et vecteurs                                              | 15           |

| 2.3  | Générati       | on des patrons de CDIDDQ                                     | 15           |

|      | 2.3.1          | Modification en vue du test                                  |              |

|      | 2.3.2          | L'extraction des capacités parasites                         |              |

|      | 2.3.3          | Génération des vecteurs                                      |              |

|      | 2.3.4          | Génération des deux premiers vecteurs                        |              |

|      | 2.3.5          | Génération des deux derniers vecteurs                        |              |

| 2.4  |                | tion des patrons de test CDIDDQ                              |              |

| 2.5  |                | on des patrons de test CDIDDQ                                |              |

| 2.6  |                | ion expérimentale de CDIDDQ                                  |              |

|      | 2.6.1          | $\mathcal{C}$ 1                                              |              |

| 2.7  |                | re de courant de consommation                                |              |

|      | 2.7.1          | 1 1                                                          |              |

| 2.0  | 2.7.2          | Logiciel d'acquisition des mesures de courant                |              |

| 2.8  | • • •          | résultat expérimental de CDIDDQ                              |              |

|      | 2.8.1          | Le montage                                                   |              |

|      | 2.8.2          | Validation                                                   |              |

|      | 2.8.3<br>2.8.4 | Application des vecteurs et résultats                        |              |

| 2.0  |                | Analyse des résultats                                        |              |

| 2.9  | Conclusi       | on                                                           | 42           |

| СНА  |                | pplication des vecteurs CDIDDQ sur la carte de développement | Sparkfun .43 |

| 3.1  | Introduct      |                                                              |              |

| 3.2  |                | de développement Sparkfun                                    |              |

|      | 3 2 1          | Test de consommation de la carte Sparkfun                    | 11           |

|       | 3.2.2     | Modification du montage pour la carte Sparkfun            | 45 |

|-------|-----------|-----------------------------------------------------------|----|

|       | 3.2.3     | Conception de l'adaptateur                                |    |

|       | 3.2.4     | Script d'automatisation de la programmation               | 47 |

|       | 3.2.5     | Résultats et discussions                                  |    |

| 3.3   | Explorat  | tion et utilisation des différentes alimentations du FPGA | 50 |

|       | 3.3.1     | Mesure sur le 3.3 volts                                   |    |

|       | 3.3.2     | Analyse des résultats                                     | 52 |

| 3.4   | Conclusi  | ion                                                       | 55 |

| CHAF  | PITRE 4   | Application des vecteurs CDIDDQ sur des montages          |    |

|       |           | surconsommation de courant                                |    |

| 4.1   |           | tion                                                      |    |

| 4.2   |           | le courant basée sur le LT3080                            |    |

| 4.3   |           | 080                                                       |    |

| 4.4   |           | ent de la source de courant                               |    |

| 4.5   |           | ent de la source de courant                               |    |

| 4.6   |           | s et analyse                                              |    |

| 4.7   |           | le courant N6705A                                         |    |

| 4.8   | Conclusi  | ion                                                       | 69 |

| CHAF  | PITRE 5 M | Montage final                                             | 71 |

| 5.1   | Introduc  | tion                                                      | 71 |

| 5.2   | Le testeu | ır FPGA                                                   | 72 |

|       | 5.2.1     | La communication série                                    | 74 |

|       | 5.2.2     | Le décalage des données                                   | 80 |

| 5.3   | Le logici | iel PC                                                    | 82 |

|       | 5.3.1     |                                                           |    |

|       | 5.3.2     |                                                           |    |

|       | 5.3.3     | La prise de mesures                                       |    |

| 5.4   | Validatio | on du système                                             | 85 |

| 5.5   | L'autom   | atisation                                                 | 88 |

| 5.6   | Résultats | s et analyse                                              | 89 |

|       | 5.6.1     | Le patron de test 17                                      | 90 |

|       | 5.6.2     | Les patrons de test 5, 6 et 29                            | 94 |

| 5.7   | Conclusi  | ion                                                       | 96 |

| CONC  | CLUSION   |                                                           | 97 |

| LISTF | E DE RÉF  | ÉRENCES BIBLIOGRAPHIOUES                                  | 99 |

# LISTE DES TABLEAUX

|             |                                                                        | Page |

|-------------|------------------------------------------------------------------------|------|

| Tableau 2.1 | Exemple de vecteurs CDIDDQ                                             | 22   |

| Tableau 2.2 | Patron de test 5                                                       | 24   |

| Tableau 2.3 | Patron de test 6                                                       | 24   |

| Tableau 2.4 | Patron de test 17                                                      | 25   |

| Tableau 2.5 | Patron de test 29                                                      | 25   |

| Tableau 2.6 | Source des nœuds testés                                                | 26   |

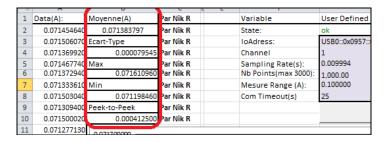

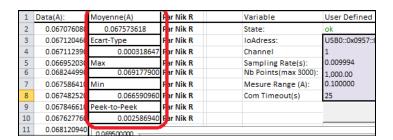

| Tableau 2.7 | Résultats obtenus (A)                                                  | 40   |

| Tableau 2.8 | Résultats d'Haithem (mA)                                               | 40   |

| Tableau 3.1 | Résultat avec la carte Sparkfun                                        | 48   |

| Tableau 3.2 | Rappel des résultats avec la carte Nexys 2                             | 49   |

| Tableau 3.3 | CDIDDQ (en ampère) pour les 3 alimentations                            | 50   |

| Tableau 3.4 | Résultat obtenu avec la carte Sparkfun sur 3.3 volts, sans régulateur. | 52   |

| Tableau 3.5 | Rappel des résultats obtenus avec la carte Sparkfun                    | 53   |

| Tableau 4.1 | Montage avec surconsommation de 200Ma                                  | 61   |

| Tableau 4.2 | Montage avec surconsommation de 1A                                     | 61   |

| Tableau 4.3 | Montage avec surconsommation de 3A                                     | 62   |

| Tableau 5.1 | Tableau des commandes                                                  | 80   |

| Tableau 5.2 | Résultat, patron de test P17                                           | 90   |

| Tableau 5.3 | En utilisant le seuil d'Haithem (CDIDDQ(infini))                       | 92   |

| Tableau 5.4 | Résultat, patron de test P5                                            | 94   |

| Tableau 5.5 | Résultats patron de test P6                                            | 95   |

| Tableau 5.6 | Résultats patron de test P29                                           | 95   |

# LISTE DES FIGURES

|             |                                                                   | Page |

|-------------|-------------------------------------------------------------------|------|

| Figure 1.1  | Court-circuit                                                     |      |

| Figure 1.2  | Utilisation de 2 sources pour l'alimentation et mesure du courant | 12   |

| Figure 1.3  | Ajout d'une source courant pour supprimer un courant de décalage  | 12   |

| Figure 2.1  | Remplacement d'une bascule normale par une bascule à balayage     | 16   |

| Figure 2.2  | Chaîne de bascule à balayage                                      | 17   |

| Figure 2.3  | Entrées et sorties du logiciel DFTadvisor                         | 17   |

| Figure 2.4  | Patron de test FastScan                                           | 19   |

| Figure 2.5  | Génération des deux premiers vecteurs                             | 20   |

| Figure 2.6  | Statistiques des pannes TDF pour le circuit S1196                 | 20   |

| Figure 2.7  | Vecteurs TDF Vw et Vx                                             | 21   |

| Figure 2.8  | Création du vecteur Vy                                            | 21   |

| Figure 2.9  | Création du vecteur Vz                                            | 22   |

| Figure 2.10 | Fichier texte des vecteurs                                        | 27   |

| Figure 2.11 | Machine à état du banc de test                                    | 28   |

| Figure 2.12 | Programme de génération de vecteurs pour le banc de test          | 28   |

| Figure 2.13 | Simulation du patron 5                                            | 29   |

| Figure 2.14 | Simulation du patron 6                                            | 29   |

| Figure 2.15 | Simulation du patron 17                                           | 30   |

| Figure 2.16 | Simulation du patron 29.                                          | 30   |

| Figure 2.17 | Redirection des nœuds testés                                      | 31   |

| Figure 2.18 | Montage expérimental                                              | 32   |

| Figure 2.10 | Mesure du courant                                                 | 33   |

| Figure 2.20 | L'analyseur de puissance N6709            | 33 |

|-------------|-------------------------------------------|----|

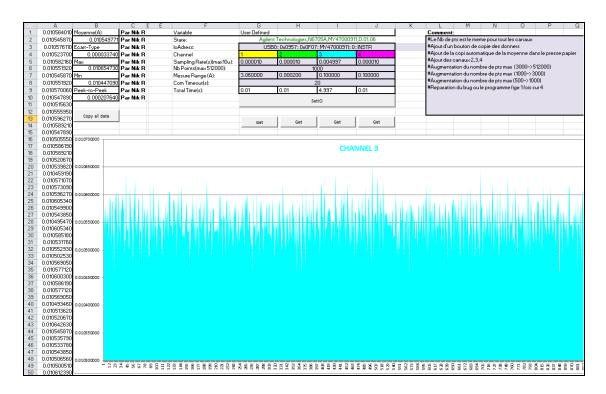

| Figure 2.21 | Programme d'acquisition pour le N6705A    | 35 |

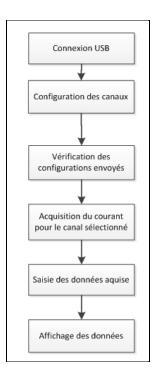

| Figure 2.22 | Étapes de la mesure de courant            | 36 |

| Figure 2.23 | Montage d'Haithem                         | 37 |

| Figure 2.24 | Vz (0-0)                                  | 38 |

| Figure 2.25 | Vy (1-1)                                  | 38 |

| Figure 2.26 | Vx (0-1)                                  | 38 |

| Figure 2.27 | Vw (1-0)                                  | 39 |

| Figure 2.28 | Procédure de mesure CDIDDQ                | 39 |

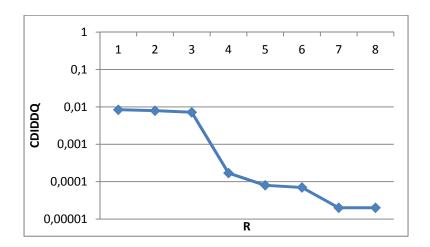

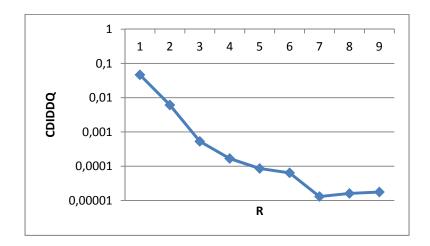

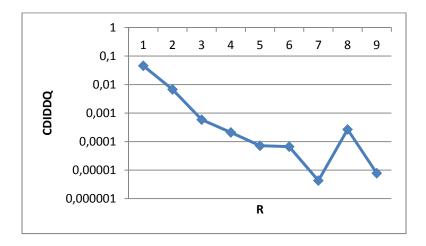

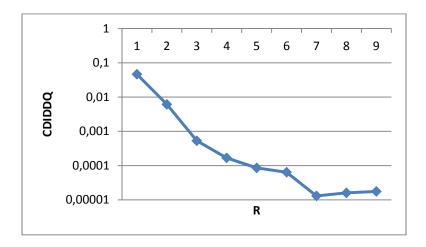

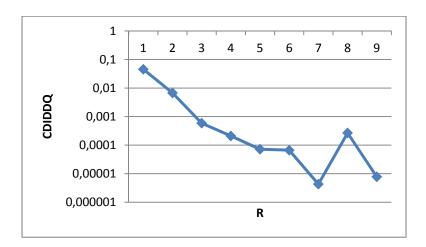

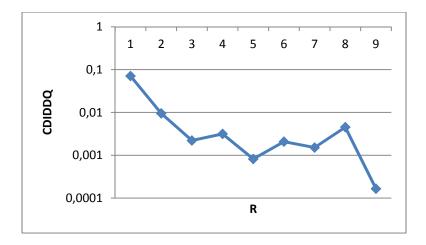

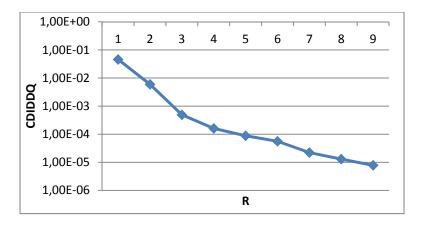

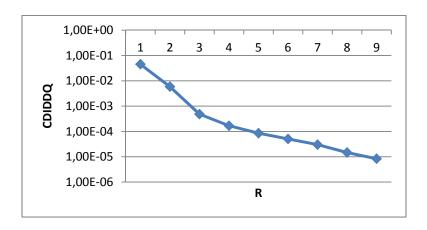

| Figure 2.29 | Graphique de CDIDDQ obtenus (A)           | 41 |

| Figure 2.30 | Graphique de CDIDDQ d'Haithem             | 41 |

| Figure 3.1  | Carte Sparkfun                            | 44 |

| Figure 3.2  | Carte Nexys 2                             | 44 |

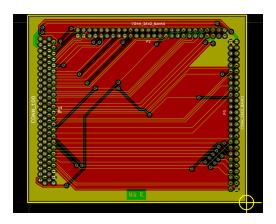

| Figure 3.3  | Routage de l'adaptateur                   | 46 |

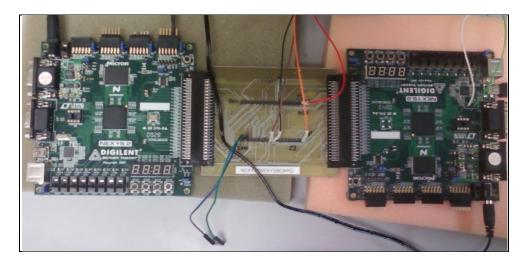

| Figure 3.4  | Montage avec une carte Nexyx II(testeur)  | 46 |

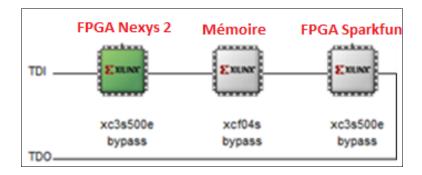

| Figure 3.5  | Chaîne JTAG du montage                    | 47 |

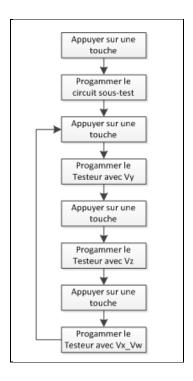

| Figure 3.6  | Organigramme du script de programmation   | 48 |

| Figure 3.7  | Carte Sparkfun 5 volts, avec régulateurs  | 51 |

| Figure 3.8  | Carte Sparkfun 3.3 volts, sans régulateur | 52 |

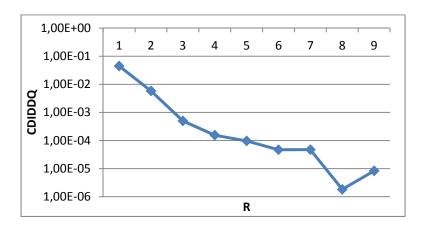

| Figure 3.9  | CDIDDQ 3.3 volts, sans régulateur         | 54 |

| Figure 3.10 | CDIDDQ 5 volts, avec régulateurs          | 54 |

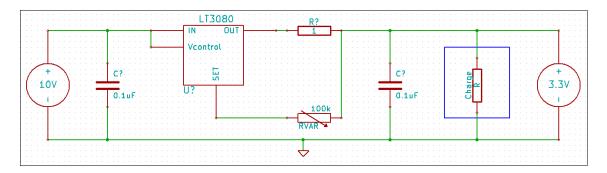

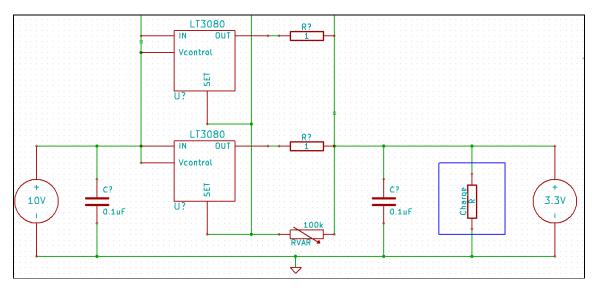

| Figure 4.1  | Montage avec source courant               | 58 |

| Figure 4.2  | Source de courant avec le LT3080          | 58 |

| Figure 4.3  | Parallélisations de la source de courant  | 59 |

|             |                                           |    |

| Figure 4.4  | Montage                                              | 60 |

|-------------|------------------------------------------------------|----|

| Figure 4.5  | Graphique CDIDDQ à 200mA                             | 63 |

| Figure 4.6  | Graphique CDIDDQ à 1A                                | 63 |

| Figure 4.7  | Graphique CDIDDQ à 3A                                | 64 |

| Figure 4.8  | Mesure du courant, 7 résistances                     | 65 |

| Figure 4.9  | Mesure du courant, 15 nœuds                          | 66 |

| Figure 4.10 | Interaction des deux sources                         | 68 |

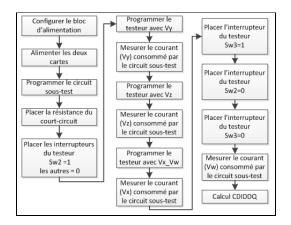

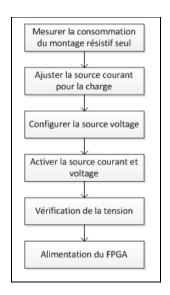

| Figure 4.11 | Étapes de la configuration des deux sources          | 69 |

| Figure 5.1  | Configuration de la prise de mesure                  | 72 |

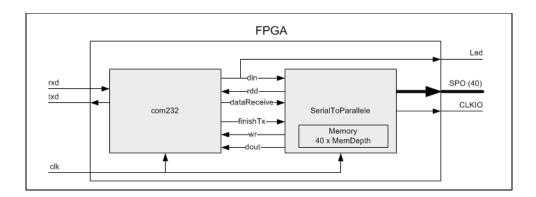

| Figure 5.2  | Schéma bloc du testeur FPGA                          | 73 |

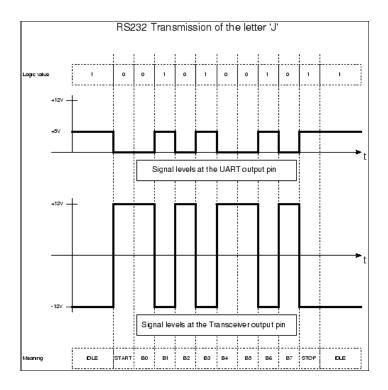

| Figure 5.3  | Envoi du caractère 'J'                               | 75 |

| Figure 5.4  | Schéma du bloc de transmission                       | 76 |

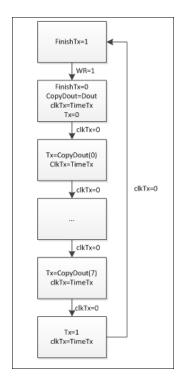

| Figure 5.5  | Organigramme de la transmission                      | 77 |

| Figure 5.6  | Schéma du bloc de réception                          | 78 |

| Figure 5.7  | Organigramme de la réception                         | 78 |

| Figure 5.8  | Simulation du module RS-232                          | 79 |

| Figure 5.9  | Validation de l'implémentation du module RS-232      | 80 |

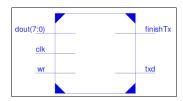

| Figure 5.10 | Décalage des données                                 | 81 |

| Figure 5.11 | Interface de vecteurs de test                        | 82 |

| Figure 5.12 | Fichier texte envoyé au testeur FPGA                 | 83 |

| Figure 5.13 | Configuration du décalage                            | 84 |

| Figure 5.14 | Interface de configuration de la communication série | 84 |

| Figure 5.15 | La prise de mesure                                   | 85 |

| Figure 5.16 | Vérification du système                              | 86 |

# XVIII

| Figure 5.17 | Paire 0-0                      | 86 |

|-------------|--------------------------------|----|

| Figure 5.18 | Paire 1-1                      | 87 |

| Figure 5.19 | Paire 0-1                      | 87 |

| Figure 5.20 | Paire 1-0                      | 87 |

| Figure 5.21 | Interface d'automatisation     | 88 |

| Figure 5.22 | Mesures à vide                 | 89 |

| Figure 5.23 | Mesure avec la carte Sparkfun  | 89 |

| Figure 5.24 | Configuration de l'acquisition | 90 |

| Figure 5.25 | 2 sources 200mA                | 92 |

| Figure 5.26 | 2 sources 1A                   | 93 |

| Figure 5.27 | 2 sources 2A                   | 93 |

| Figure 5.28 | 2 sources 3A                   | 93 |

# LISTE DES ABRÉVIATIONS, SIGLES ET ACRONYMES

ASIC Application-specific integrated circuit

ATPG Automatic test pattern generation

CMOS Complementary Metal-Oxide-Semiconductor

CUT Circuit under test

CDIDDQ Complementary delta direct drain quiescent current

DC Direct current

DIDDQ Delta direct drain quiescent current

DFT Design for testability

ÉTS École de technologie supérieure

FPGA Field-programmable gate array

IDDQ Direct drain quiescent current

IO Input/output

JTAG Joint test action group

PC Personal computer

PROM Programmable read-only memory

RTL Register to transistor level

TDF Transition delay fault

USB Universal serial bus

VBA Visual Basic for applications

VHDL Very high speed integrated circuit hardware description language

#### INTRODUCTION

Au cours des dernières décennies, le développement de la microélectronique s'est fait à un rythme exponentiel soutenu. Ce rythme de développement suit la fameuse « loi de Moore », selon laquelle les circuits intégrés voient leur densité d'intégration doubler tous les 18 mois (Moore 1965). La miniaturisation des transistors qui lui est associée a permis de développer des systèmes de plus en plus petits et performants. Cependant, cette miniaturisation vient également avec son lot de défis à relever, défis qui évoluent avec la technologie et les procédés de fabrication de plus en plus complexes. Par exemple, ces procédés permettent l'intégration d'un nombre croissant de niveaux de métal, avec des traces de plus en plus rapprochées. Ceci a entre autres mené à l'augmentation des défectuosités dans la fabrication des circuits, particulièrement au niveau des courts-circuits entre les traces de métal (Zorian et Mourad 2000). Ainsi, même avec une conception qui respecte toutes les règles de design du manufacturier, il est possible d'avoir des circuits intégrés qui soient défectueux. Dans ce contexte, il est important que les méthodes de test utilisées évoluent avec la technologie et les défectuosités introduites par les procédés de fabrication.

L'objectif du test est la détection de manière efficace de tout problème pouvant affecter un circuit intégré. Cela permet de garantir que le système est fonctionnel et répond aux spécifications. C'est une étape importante, car elle permet d'assurer la qualité du produit. La complexité grandissante des circuits intégrés a rendu cette tâche plus ardue. Face à cette complexité grandissante, on a pu voir l'apparition de différentes techniques de test.

Parmi ces techniques on retrouve le test dit logique, qui constitue la technique la plus utilisée. Sur la base de la représentation au niveau porte, le test logique vérifie le niveau logique, 0 ou 1 (respectivement représenté par les tensions 0 et Vdd), d'un ou plusieurs nœuds d'un circuit intégré afin de vérifier le bon fonctionnement de celui-ci. Sans apport d'informations supplémentaires, cette technique s'avère peu efficace pour détecter les pannes de court-circuit (Rajsuman 2000). En effet, lorsqu'on utilise comme information seulement le niveau porte, le nombre de courts-circuits potentiels est de l'ordre de N<sup>2</sup> où N représente le nombre

de noeuds dans le circuit (Zorian et Mourad 2000). De plus, afin de procéder au test logique, on doit propager les valeurs des nœuds internes sur les sorties du circuit. Cela vient donc complexifier la génération des vecteurs de test. Aussi, puisque le niveau de tension du court-circuit dépend de la résistivité du court-circuit et des dimensions des transistors, il est difficile de savoir le résultat logique équivalent, qui, dans le pire cas, pourrait être une valeur mitoyenne (Rajsuman 2000). Aussi, notons que même si un court-circuit n'affecte pas la fonctionnalité, il cause la dégradation de la fiabilité du circuit, ce qui est préoccupant dans la majorité des cas (Rajsuman 1991).

Pour pallier les faiblesses du test logique pour la détection des courts-circuits, une autre technique s'est imposée comme alternative. Il s'agit du test basé sur le courant de consommation statique (« IDDQ testing »), présentée plus en détail au chapitre suivant. Le test IDDQ, qui offre de manière inhérente une très grande observabilité, a été développé en tirant profit du fait que les circuits CMOS, en mode statique, ne consommaient à l'époque qu'une minime quantité de courant (Riezeman 1991), et que les défectuosités telles les courts-circuits causaient en général une augmentation significative du courant. Ainsi, un court-circuit devenait facilement détectable. Malheureusement, la diminution de la taille des transistors, ainsi que l'augmentation de la taille des circuits intégrés ont contribué à augmenter le courant de fuite des circuits sans pannes, ce qui a réduit l'efficacité du test IDDQ (Engelke 2006). En effet, l'utilisation de la technique nécessite que le courant de fuite d'un circuit sans panne soit beaucoup plus petit que celui d'un circuit avec panne, ce qui de nos jours n'est plus le cas (Powell 2000).

Afin de prolonger l'utilisation du courant de consommation statique durant le test, un certain nombre d'approches ont été proposées, la plupart basées sur le post-traitement des mesures de courant. Une des approches très utilisées est Delta-IDDQ (DIDDQ) (Thibeault 1999), qui sera également décrite de manière un peu plus détaillée au chapitre suivant. Cette approche fait la différence entre deux mesures consécutives de courant statique. Cela permet d'éliminer le courant d'arrière-plan (plus précisément sa valeur moyenne), qui varie d'une puce à l'autre, dû aux variations inhérentes des procédés de fabrication, et donc de réduire

l'effet néfaste de grands courants de fuite. Comme son prédécesseur, DIDDQ voit néanmoins son efficacité diminuer avec la réduction de la taille des transistors, en raison des variations qui apparaissent d'une mesure de courant à l'autre.

Une nouvelle approche a été récemment proposée afin d'éliminer l'effet des variations affectant DIDDQ. Cette approche, appelée test CDIDDQ (Thibeault et Hariri 2009) et décrite en détail au chapitre 1, s'appuie sur une nouvelle façon de générer les vecteurs de test et d'effectuer le post-traitement des mesures de courant, qui permet d'éliminer l'effet de toutes les variations (d'une puce à l'autre, d'une mesure à l'autre), sauf celles liées au bruit de la mesure du courant. Cette élimination facilite la détection de courts-circuits, pourvu que le niveau de courant supplémentaire soit suffisant pour être distingué du bruit de mesure.

La validation expérimentale de CDIDDQ sur des circuits ASIC émulés sur FPGA (Haithem 2011) a démontré l'efficacité de cette technique de test. L'application a été faite sur deux approches distinctes : le test indépendant de l'application et celui dépendant de l'application. Les tests permettent de détecter des courts-circuits dans le FPGA pour l'approche indépendante ou dans l'ASIC émulé dans le FPGA pour l'approche dépendante. Les résultats expérimentaux ont démontré qu'il était possible de détecter des pannes de courts-circuits d'une résistivité d'environ 80k ohms et moins sur des circuits émulés sur le FPGA à faible consommation de courant.

Ce projet de maîtrise vise à obtenir de meilleurs résultats dans la détection de pannes de court-circuit pour les ASIC, émulés sur FPGA. La principale contribution de ce mémoire est l'amélioration de la technique de test et diagnostic CDIDDQ précédemment utilisée, grâce 1) à l'utilisation d'une meilleure méthodologie d'application du test CDIDDQ, 2) au développement de logiciels d'acquisition, et 3) à l'amélioration du montage. Ces améliorations permettent d'obtenir des résultats validant la possibilité de détecter des pannes de court-circuit à haute résistivité sur des circuits intégrés émulés sur FPGA, et ce, en présence d'une grande consommation de courant. Le mémoire est structuré comme suit :

- 1- Le chapitre 1 présente les notions de base nécessaires à la compréhension de ce mémoire ainsi que l'état de l'art dans le domaine du test des circuits. De plus, nous expliquons tout ce qui traite du processus de génération des vecteurs CDIDDQ.

- 2- Dans le chapitre 2, nous expliquons en premier lieu la génération des patrons de test CDIDDQ qui saura par la suite les valider en simulation. En second lieu, nous expliquons le fonctionnement de l'application expérimentale de CDIDDQ sur des circuits FPGA. Enfin, nous procéderons à la reproduction des résultats déjà obtenus (Haithem 2011) afin de revalider l'application de la méthode CDIDDQ.

- 3- Dans le chapitre 3, nous appliquons les patrons de test CDIDDQ sur une autre carte de développement comportant le même FPGA. Nous présentons en détail le nouveau montage et explorons les différentes possibilités d'alimentation de la carte.

- 4- Le chapitre 4 s'intéresse à l'application des patrons de test CDIDDQ sur des montages plus énergivores. On y présente le montage ainsi que les techniques qui ont été utilisés afin d'obtenir les résultats présentés.

- 5- Dans le chapitre 5, nous présentons les différentes améliorations appliquées pour la méthode CDIDDQ ainsi que les résultats expérimentaux obtenus grâce à ceux-ci. Nous terminerons avec un tableau récapitulatif affichant les résultats de différents patrons de test CDIDDQ pour différents montages.

#### **CHAPITRE 1**

# NOTIONS DE BASE ET REVUE DE LA LITTÉRATURE

#### 1.1 Introduction

Dans ce chapitre, nous allons dans un premier temps présenter les notions de base nécessaires à la compréhension de ce mémoire. Les notions couvertes seront les tests, IDDQ, Delta-IDDQ, CDIDDQ et l'émulation d'ASIC sur FPGA. Par la suite, nous allons procéder à la revue de la littérature qui nous positionnera face aux autres recherches existantes et justifiera notre contribution au domaine de la détection de courts-circuits dans les ASICs de type CMOS. Nous nous attarderons à la littérature traitant de la mesure de courant et l'utilisation de deux sources. Pour finir, nous présenterons les résultats obtenus avec le montage d'Haithem (Haithem 2011).

#### 1.2 Notions de base du test

Bien que la simulation d'un circuit intégré indique que ce dernier est fonctionnel, il est possible qu'il n'effectue pas la fonction désirée une fois implémenté. En effet, il est possible, par exemple, qu'il y ait des défectuosités introduites par le procédé de fabrication qui engendrent des dysfonctionnements. Dans le but de détecter les défectuosités et d'assurer la fiabilité d'un circuit intégré, il est impératif de le tester (Breuer 1976). Le test est défini comme étant la série d'actions entreprises après la fabrication d'un circuit intégré menant à la détection de tout problème, comparativement au diagnostic qui permet de connaître la source du problème. Pour tester le circuit, nous devons générer des vecteurs de test. Les vecteurs comprennent la valeur à injecter à l'entrée ainsi que leurs sorties correspondantes. Avec la complexité des systèmes courants, il est nécessaire de faire appel à des logiciels de génération automatisée de vecteur (ATPG). Afin de simplifier le processus de génération, les vecteurs sont produits pour des modèles abstraits de panne. Selon (Mourad, S. and Y. Zorian 2000) il y a quatre principaux modèles de pannes : la panne collé-à, la panne ouverte, la panne de délais et la panne de court-circuit.

La panne collé-à (stuck-at), qui est le modèle le plus utilisé dans le test de circuit (Bushnell, M. L. et V. D. Agrawal 2000), représente un nœud collé à une valeur. La valeur du nœud comportant la défectuosité est soit toujours à 1 (VDD) ou soit toujours à 0 (GND), ce qui vient de ce fait altérer le fonctionnement du circuit.

La panne ouverte (stuck open) représente une panne où un nœud est laissé non connecté au reste du circuit. Nous avons donc un nœud qui est flottant, ce qui va aussi changer le fonctionnement de notre circuit.

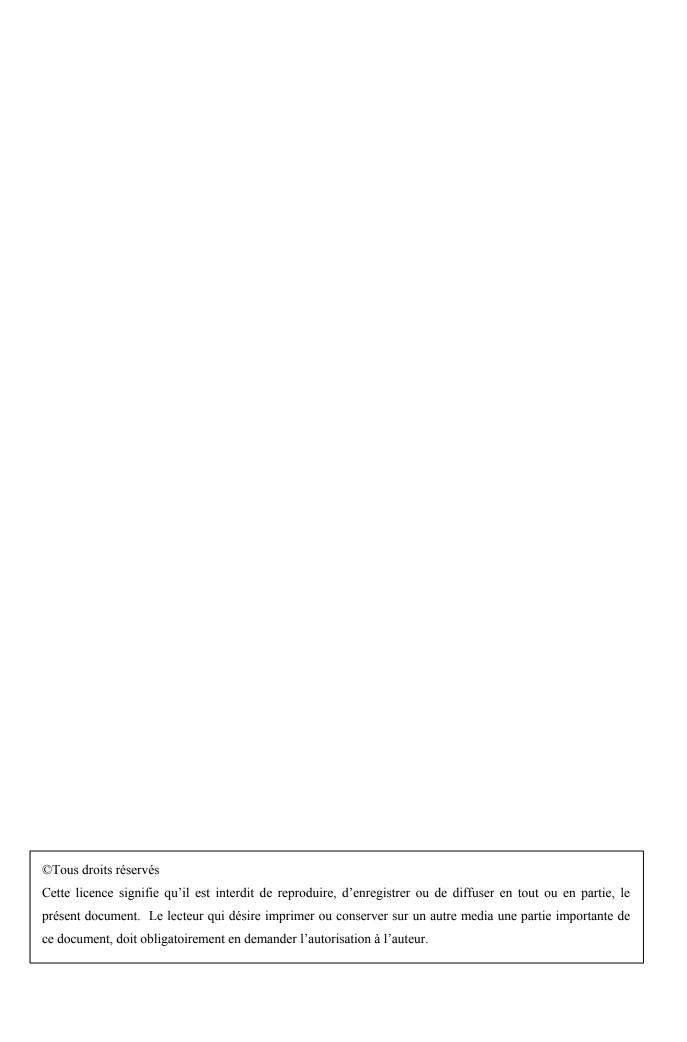

Une panne de délais représente une défectuosité temporelle affectant des signaux qui, dès lors, se propagent trop lentement ou rapidement dans le circuit. L'objectif de tout test ciblant ce genre de défectuosité est de détecter les délais qui divergent de ceux nécessaires à la bonne synchronisation du circuit. Ces pannes sont donc testées à des fréquences élevées (i.e. à des fréquences supérieures ou égales à la fréquence nominale) afin de permettre de les détecter. Il existe deux modèles de pannes de délais : les délais de transitions et les délais des chemins (Smith 1985). Le délai de transition est une transition lente à monter (0 à 1) ou lente à descendre (1 à 0), appliqué au niveau d'une porte logique de manière ponctuelle sur un nœud, tandis que le délai de chemin est appliqué de façon distribuée sur un chemin complet. La panne court-circuit (bridge faults) représente une défectuosité ou une connexion physique non désirée entre deux nœuds comme représenté dans la figure 1.1. La miniaturisation des circuits a causé l'augmentation des pannes de court-circuit étant donné la réduction de l'espace entre les traces (Mourad, S. and Y. Zorian 2000). Le lien résistif établi entre les deux signaux peut modifier le niveau des sorties des portes logiques associées. Le niveau logique est difficile à prédire puisqu'il dépend alors de la dimension des transistors, ce qui rend plus ardue la détection de ce type de faute (Kuen-Jong Lee 1991). De plus, les courts-circuits hautement résistifs sont davantage difficiles à détecter par le test logique puisque ceux-ci n'influencent pas la valeur logique. Notons que, comme mentionné dans la problématique, nous nous concentrerons dans ce mémoire sur la détection des pannes de court-circuit. L'objectif est de détecter tous les courts-circuits, causant ou non une modification du fonctionnement du système.

Figure 1.1 Court-circuit

#### 1.3 IDDQ

La technique de test IDDQ permet, grâce à la lecture du courant statique, de détecter une anomalie causant une augmentation de ce courant dans un circuit intégré. Cette technique a été développée en s'appuyant sur le fait que les circuits CMOS en statique ne consommaient qu'un petit courant de fuite provenant des transistors (Riezeman 1991). Ainsi, une surconsommation de courant provenant du circuit indiquait la présence d'une défectuosité. IDDQ permet de détecter certaines défectuosités manquées par les autres techniques de test, par exemple un faible (i.e très résistif) court-circuit ne causant qu'un petit délai supplémentaire, insuffisant pour mener à une erreur de synchronisation. Un autre avantage du test par le courant est que nous ne nous soucions pas de l'observabilité (Shinogi, T. 1998). L'observabilité est un paramètre qui définit la facilité à pouvoir lire la valeur d'un nœud dans un circuit. Puisque nous lisons directement le courant fourni via le bloc d'alimentation au circuit, nous n'avons pas à nous soucier de ce paramètre. Cela est un grand avantage pour la détection des pannes de court-circuit. Ceci a contribué au départ à la popularité d'IDDQ pour la détection de ce type de panne.

#### 1.3.1 **DIDDO**

La diminution de la taille des transistors a réduit l'efficacité d'IDDQ (Engelke 2006). En effet, la technique implique que le courant de fuite d'un circuit intégré sans panne est beaucoup plus petit que celui d'un circuit avec panne. Malheureusement, la diminution de la taille des transistors ainsi que l'augmentation de la taille (et densité) des circuits intégrés ont

contribué à augmenter le courant de fuite des circuits sans panne. IDDQ s'avère donc plus sensible face au bruit et aux variations des procédés de fabrication qui se traduisent par une variance des mesures d'une puce à l'autre et d'un vecteur de test à l'autre. Grâce à des analyses expérimentales (Thibeault 1998), on a pu démontrer qu'en soustrayant la mesure de courant de deux vecteurs IDDQ consécutifs pour une même puce, on arrive à diminuer la variance des distributions de courant et à réduire le décalage du courant de fuite des transistors. Par exemple, si la première mesure donne 100mA et la deuxième 110mA et que l'on place un seuil à 5mA, on considérera la puce comme défectueuse. Cette technique de post-traitement des mesures de courant statique, appelée Delta IDDQ (DIDDQ), permet en effet de réduire l'effet des variations de courant d'une puce à l'autre, en éliminant le courant statique moyen consommé par chaque circuit intégré.

#### 1.3.2 CDIDDQ

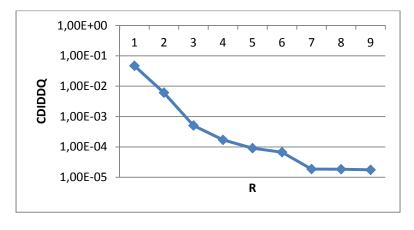

Comme son prédécesseur, DIDDQ voit son efficacité diminuer avec la réduction de la taille des transistors. Cette diminution est liée aux variations grandissantes des mesures de courant observées d'un vecteur de test à l'autre. Afin d'étendre la vie de l'utilisation du test par consommation de courant Thibeault et Hariri (2009) ont mis au point une nouvelle technique de test appelée CDIDDQ, expliquée en détail au chapitre suivant. Cette technique est basée sur la génération adaptée des vecteurs de test en sous-ensembles de 4 vecteurs dont la combinaison des mesures de courant donne, en théorie, 0. L'équation 1.1 décrit la combinaison des mesures.

$$CDIDDQ = 0 = I(Vy_{1-1}) + I(Vz_{0-0}) - (I(Vw_{1-0}) + I(Vx_{0-1}))$$

(1.1)

Où  $I(V_j)$  est la mesure de courant statique prise au vecteur  $V_j$ . L'objectif est de pouvoir, grâce aux quatre mesures, éliminer la variation du courant de fuite des transistors d'un vecteur à l'autre. De ce fait, si le résultat CDIDDQ est supérieur à un certain seuil, déterminé en fonction de la variation due à la mesure de courant, on considère le circuit défectueux. Il est à noter que cette dernière variation est la seule qui demeure, les autres (d'une puce à l'autre et

d'un vecteur à l'autre) ayant été éliminées. Tel que décrit plus loin, cette technique a été validée (Haithem 2011) en l'appliquant sur différents circuits du banc d'essai ISCAS89 (Brglez 1989). L'objectif de ce projet est d'améliorer l'application de cette technique pour détecter des courts-circuits plus faibles (résistifs) pour des circuits consommant plus de courant.

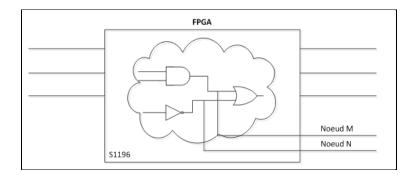

#### 1.3.3 Émulation d'ASIC à l'aide de FPGA

Les ASICs sont des circuits intégrés dédiés. Une puce dédiée est conçue et fabriquée dans le but de répondre à des spécifications particulières. L'intérêt de ce genre de circuits intégrés est dans la production de masse où les coûts par puce sont faibles, dans la mesure où les frais non récurrents sont amortis par le très grand volume de vente. Le design et la fabrication de puces dédiées ASIC coûtent très cher et nécessitent beaucoup de temps (Maxfield 2004). De plus, une fois le design complété et la pièce implémentée, nous faisons face à un système gelé (*Frozen system*), ce qui signifie qu'il est impossible de le modifier. Il nous apparaît alors l'importance d'avoir un circuit parfaitement fonctionnel pour la fabrication. Afin de pouvoir a priori valider la fonctionnalité du design avant la fabrication, il est possible d'utiliser des FPGAs (Courtoy, M. 1995).

Les FPGAs comportent, de nos jours, plusieurs millions de portes logiques équivalentes et permettent de réaliser pratiquement n'importe quel système numérique par le biais d'une simple programmation (Maxfield 2004). Il y a plusieurs avantages au prototypage sur FPGA. Notons entre autres que la conception sur FPGA a l'avantage d'être peu coûteuse et rapide en plus d'être modifiable une fois implémentée, contrairement aux ASICs. En plus de pouvoir être utilisée pour les tests de fonctionnalité, l'émulation d'ASICs sur FPGA peut aussi servir pour l'injection d'un grand nombre de pannes (De Andres 2006) puisque l'on peut générer un circuit avec des défectuosité logique. Le FPGA étant déjà testé par le manufacturier, nous supposons ce dernier sans défectuosité. Ainsi, il est possible d'implémenter sur le FPGA le design original modifié comportant des fautes, en connectant par exemple deux nœuds ensemble pour créer un court-circuit. L'objectif étant soit de vérifier le comportement du

design face à la faute ou bien de valider la détection de la faute par le système de test. Pour ce projet, nous allons émuler un ASIC sur FPGA afin d'expérimenter la technique de test CDIDDQ. Nous ne nous servirons pas de l'émulation dans le but de test fonctionnel puisque nous utiliserons les circuits ISCAS-89 qui ont déjà été vérifiés. Nous utiliserons plutôt l'émulation pour insérer des pannes de type court-circuit, afin de procéder à leur détection grâce à CDIDDQ. Nous nous intéressons donc à la détection de la panne plutôt qu'à son impact sur la fonctionnalité du circuit.

## 1.4 Techniques de mesure de courant pour le test

L'utilisation d'une technique de test basé sur la mesure de courant nécessite une attention particulière à l'endroit de la prise et du paramétrage de la mesure. Selon (Chakravarty et Thadikaran 1997), il existe trois endroits où cette mesure peut être effectuée. En effet, il est possible de mesurer le courant à l'intérieur du circuit à tester à l'aide de senseurs (built-in current monitors), avec un circuit spécialisé externe inséré entre le bloc d'alimentation et le circuit (loadboard monitors), ou bien directement dans le bloc d'alimentation (tester based monitors). La mesure à l'intérieur de la puce, grâce à sa position rapprochée du point de mesure, permet d'atteindre des vitesses de mesure très élevées. En général, la lecture de courant est exécutée à des endroits spécifiques ce qui permet d'éviter les grands courants DC à l'intérieur du circuit et ainsi augmenter la précision des mesures. De plus, la mesure de courant interne est comparée à une valeur prédéfinie et seulement le résultat de la comparaison est retourné (succès ou échec) et non la mesure. Pour leur part, les circuits spécialisés externes se trouvent en général très près de l'unité à tester, ce qui leur permet une vitesse de mesure relativement élevée. Ils ont la possibilité d'être dédiés à des applications particulières et on retrouve une grande diversité sur le marché de ce type de produit. Le principal inconvénient est que cette approche nécessite l'ajout d'un module supplémentaire sur la plateforme de test déjà existante. Pour finir, la mesure qui provient du bloc d'alimentation, se trouvant à la plus grande distance du circuit à tester, est en général moins rapide que les deux autres. Cela rend aussi ce type de mesure plus flexible que les autres puisqu'elle est moins dédiée à une application en particulière.

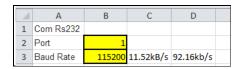

Dans le cadre de ce projet, nous ne pouvons pas utiliser la mesure de courant à l'intérieur du circuit, car de tels modules n'existent pas dans les FPGAs. Nous avions donc le choix entre la mesure de courant provenant du bloc d'alimentation ou d'un circuit externe spécialisé. Selon (Hans Manhaeve 2005), il est préférable d'utiliser un circuit externe spécialisé, comme le QD-1011HC de Q-Star, qui permet d'avoir une erreur moyenne plus basse et une vitesse d'acquisition plus grande par rapport au bloc d'alimentation. L'erreur moyenne est un paramètre important dans la mesure de courant puisqu'il nous indique quelle variation de courant maximum peut être détectée de façon répétable. Ainsi, pour un système de mesure dont l'erreur moyenne est de 20µA, on ne peut détecter de façon répétable, donc à chaque mesure, que des défectuosités qui génèrent une variation de courant de plus de 20µA (Hans Manhaeve 2005). Le bloc d'alimentation, le N6705 d'Agilent par exemple, possède une erreur de 30µA tandis que le module QD-1011HC de Q-Star est de 4µA, tous deux pour une plage de 100mA. Aussi, le QD-1011HC peut effectuer les mesures bien plus rapidement que le bloc d'alimentation. Malgré que le QD-1011HC possède de meilleures caractéristiques, nous n'avons pas choisi ce module. Il nécessitait l'ajout d'un module supplémentaire au montage, ce qui le complexifiait et en augmentait les coûts. Finalement, ce module offre une plage de lecture limitée à 2A contrairement à 3A pour le bloc d'alimentation, qui fut par conséquent notre choix. Il est clair, cependant, que le module de Q-Star pourrait être mis à contribution dans l'application de CDIDDQ pour les circuits intégrés dont la consommation ne dépasse pas 2A. L'utilisation de ce module pourrait faire l'objet de travaux futurs.

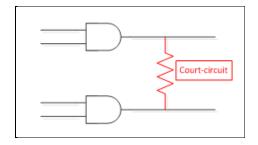

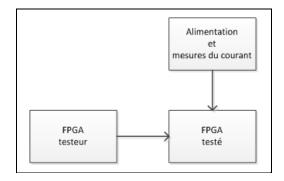

#### 1.4.1 Utilisation de deux sources

Dans notre montage, afin de pouvoir garder une erreur moyenne de 30 µA pour une plage plus élevée que 100mA, par exemple 3A, nous utilisons deux sources pour nos tests. En effet, l'augmentation de la plage de lecture entraîne aussi l'augmentation de l'erreur moyenne, ce qui est néfaste pour la précision de nos mesures de courant. Le montage comporte une source de courant et une source de tension qui alimentent le circuit sous test, comme affiché à la

figure 1.2. La source de courant est utilisée pour fournir le courant de base au circuit afin que la source de tension ne soit utilisée que pour mesurer la variation du courant.

Figure 1.2 Utilisation de 2 sources pour l'alimentation et mesure du courant

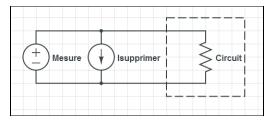

Ainsi, pour un circuit consommant 3A, la source courant pourrait fournir 2.99A afin que la source de tension ait à fournir moins de 100mA pour rester dans la plage de 100mA et d'avoir une erreur moyenne de 30 μA. Cette méthode permet donc de conserver une erreur moyenne plus basse que si nous utilisions la plage de 3A, qui possède une erreur moyenne de 1350μA. L'utilisation de deux sources, comme affiché à la figure 1.3, est souvent employée pour retirer un courant d'arrière-plan afin de cibler la mesure de courant pour l'application. C'est entre autres le cas pour des mesures de petits courants et grandes résistances.

Figure 1.3 Ajout d'une source courant pour supprimer un courant de décalage Tirée de Making Precision Low Current and High Resistance Measurements (2012, p.5)

Comme on peut le constater, l'ajout d'une source de courant externe ( $I_{SUPRESS}$ ) peut permettre d'éliminer un courant de consommation supplémentaire ( $I_{OFFSET}$ ) si ceux-ci sont égaux. Ainsi le courant mesuré est celui consommé par  $I_M$ .

## 1.5 Résultats CDIDDQ antérieurs

Dans le cadre d'un travail de maîtrise (Haithem 2011), on a pu démontrer l'efficacité de CDIDDQ à détecter des pannes de courts-circuits d'une résistivité moyenne sur des circuits émulés sur un FPGA à faible consommation de courant. Les résultats ont en effet montré la capacité à détecter des pannes de court-circuit de l'ordre de 80k Ω sur un montage comprenant uniquement le circuit émulé sur FPGA qui consomme environ 70mA. Notons que l'application de CDIDDQ utilisée, l'ensemble des résultats associés et le montage expérimental sont présentés dans le chapitre 2.

Sachant que le bruit est un grand préjudice aux tests utilisant la mesure de courant (Chakravarty, S. et P. J. Thadikaran 1997) nous allons dans le cadre de ce projet le réduire de manière considérable en vue d'obtenir de meilleurs résultats que précédemment. Nous parviendrons à ce point en épurant le montage sur lequel les mesures de courant sont faites en plus d'un meilleur paramétrage et utilisation de l'appareil de mesure. Nous allons par la suite ajouter au montage une surconsommation afin de voir l'efficacité de CDIDDQ pour des circuits intégrés plus énergivores. L'objectif est donc d'approfondir et élargir les résultats pour le test CDIDDQ. À l'extérieur du laboratoire, ces résultats tentent de fournir des résultats solides pour prouver aux compagnies la validité et l'étendue de la technique.

#### 1.6 Conclusion

Dans ce chapitre, nous avons présenté les notions de base des modèles de pannes, de l'émulation des ASICs et des résultats expérimentaux avec CDIDDQ déjà obtenus. Nous avons pu constater que les modèles de pannes existants qui couvrent les courts-circuits possèdent certaines lacunes, lorsqu'utilisés par des techniques de test basées sur les valeurs logiques (ou tension), d'où l'utilisation des tests par mesure de courant. La perte d'efficacité

de ces derniers a mené à la création de techniques de post-traitement des mesures de courant, auxquelles appartient CDIDDQ. Pour les circuits à haute consommation, il est possible d'ajouter une source de courant supplémentaire afin que celle utilisée pour les mesures ne fournisse qu'un petit courant, ce qui permet de garder une échelle de mesure avec une bonne résolution. Aussi, l'expérimentation de CDIDDQ sur des ASIC émulés sur FPGA a permis de prouver le fonctionnement de cette technique pour laquelle nous visons à obtenir de meilleurs résultats. Dans le prochain chapitre, nous validons les vecteurs CDIDDQ générés en simulation. Ensuite, nous expliquons le fonctionnement de l'application expérimentale de CDIDDQ sur des circuits FPGA. Enfin, nous procéderons à la reproduction des résultats déjà obtenus (Haithem 2011) afin de revalider l'application de la méthode CDIDDQ.

#### **CHAPITRE 2**

#### LES PATRONS DE TEST CDIDDQ

#### 2.1 Introduction

Dans ce chapitre, nous allons en premier lieu donner un peu plus de détails sur le fonctionnement et la génération des patrons de test CDIDDQ. Par la suite, nous allons expliquer comment procéder pour appliquer ces patrons de test. Pour finir, nous allons présenter les premiers résultats obtenus de l'application d'un de ces patrons de test sur un montage comportant un ASIC émulé sur FPGA.

#### 2.2 Les patrons et vecteurs

Comme expliqué dans le chapitre précédent, CDIDDQ est une technique de test basée sur la lecture du courant. Afin d'effectuer le calcul CDIDDQ, nous devons avoir la lecture du courant consommé par le circuit lorsque les deux nœuds testés sont respectivement aux niveaux logiques 0-0, 0-1, 1-0 et 1-1. Afin d'obtenir ces niveaux logiques, nous devons fournir au circuit les bons stimuli aux entrées de celui-ci. Il nous est donc nécessaire de générer ces stimuli qui seront sous la forme de vecteurs afin de les appliquer au circuit.

## 2.3 Génération des patrons de CDIDDQ

Il n'existe présentement aucun outil ATPG commercial qui permet de générer directement l'ensemble des vecteurs de test CDIDDQ. Une méthode (Hariri 2009) a été mise au point pour générer ces vecteurs de test. Nous n'allons ici résumer que l'essentiel en expliquant les modifications que l'on doit apporter au circuit en vue du test ainsi que la génération des vecteurs de test CDIDDQ.

#### 2.3.1 Modification en vue du test

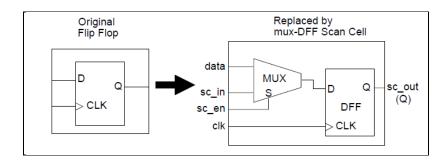

Pour créer les vecteurs de test, on doit premièrement avoir un circuit qui est testable. Cette première étape consiste conventionnellement à l'insertion de chaînes de bascules à balayage (scanchains). Ceci permet d'augmenter la contrôlabilité et l'observabilité du test. On rappelle que la contrôlabilité exprime la facilité à pouvoir appliquer une valeur à n'importe quel nœud du circuit tandis que l'observabilité exprime la facilité à pouvoir capturer une valeur de n'importe quel nœud du circuit. Cette insertion nécessite d'abord le remplacement des bascules comprises dans le circuit par des bascules à balayage (scan flip-flops), illustré à la figure 2.1. Il est important de noter que le remplacement des bascules modifie le circuit et augmente le nombre de transistors nécessaire à la réalisation du circuit.

Figure 2.1 Remplacement d'une bascule normale par une bascule à balayage Tirée de Scan and ATPG Process Guide (2008 p.66)

Comme on peut le constater avec les bascules à balayage, il est désormais possible de choisir le signal d'entrée des bascules par le biais d'un multiplexeur. En connectant ensuite les bascules en série (voir figure 2.2), on crée un (ou plusieurs) registre(s) à décalage à l'intérieur de notre circuit intégré. Ainsi, il est possible de lire ou d'écrire la valeur de chacune des bascules. Nous pourrons donc placer les bascules de notre circuit dans un état précis en vue du test.

Figure 2.2 Chaîne de bascule à balayage Tirée de Scan and ATPG Process Guide (2008 p.41)

Les bascules à balayage nécessitent donc l'utilisation de trois signaux, soit Sc\_en, Sc\_in et Sc\_out. Le signal Sc\_en permet de sélectionner entre le signal originalement connecté à la bascule et le signal Sc\_in. Le signal Sc\_in sera utilisé pour injecter les valeurs désirées aux bascules, tandis que Sc\_out sera utilisé pour lire la valeur des bascules.

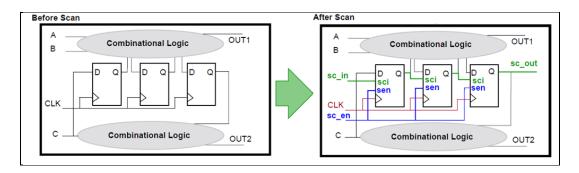

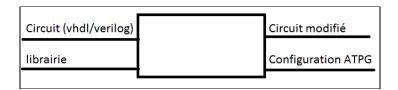

Afin de procéder à l'insertion des bascules de scan, nous utilisons le logiciel DFTadvisor. Comme illustré à la figure 2.3, on doit fournir au logiciel DFTadvisor la description du circuit (sous format Verilog ou VHDL) dans lequel on désire faire l'insertion des chaînes de bascules à balayage ainsi que la librairie qui définit ces bascules. En retour, DFTadvisor produira le circuit avec les bascules à balayage ainsi que le fichier de la configuration APTG qui sera utilisé par le logiciel de génération de patron de test (ATPG) expliqué un peu plus loin.

Figure 2.3 Entrées et sorties du logiciel DFTadvisor

# 2.3.2 L'extraction des capacités parasites

La prochaine étape à compléter afin de générer les vecteurs de test est d'obtenir le dessin des masques de notre circuit et d'en extraire les sites comportant des capacités parasites. Les sites à capacités parasites représentent les endroits du circuit où les traces sont les plus rapprochées. De ce fait, ces sites ont une plus grande probabilité d'être victimes de pannes de courts-circuits. Ne cibler que les sites probables réduit le nombre de vecteurs CDIDDQ à produire. L'extraction des capacités parasites est une étape obligatoire dans l'application de CDIDDQ pour le test d'un circuit ASIC. Dans le cadre de ce projet, comme nous émulons les circuits ASIC à l'aide d'un circuit FPGA, nous considérons que les sites potentiels de courts-circuits ont déjà été identifiés, soit par cette extraction effectuée à partir du dessin des masques ou encore de manière aléatoire. Pendant nos expérimentations, nous allons tenter de détecter un nombre restreint de pannes de court-circuit via le test de CDIDDQ.

#### 2.3.3 Génération des vecteurs

Nous avons maintenant tous les prérequis pour la génération des vecteurs. Rappelons l'équation de CDIDDQ :

$$CDIDDQ = I(Vy_{1-1}) + I(Vz_{0-0}) - (I(Vw_{1-0}) + I(Vx_{0-1}))$$

(2.1)

En ce sens, nous devons donc être en mesure de produire des sous-ensembles de quatre vecteurs qui appliqueront les valeurs 1-1, 0-0, 0-1 et 1-0 sur les deux nœuds où l'on teste une panne de court-circuit. Ce processus se divise en deux étapes qui nous fourniront chacune deux des quatre vecteurs.

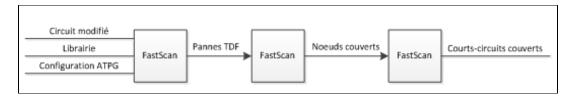

## 2.3.4 Génération des deux premiers vecteurs

Comme mentionné précédemment, aucun outil commercial ne peut générer l'ensemble des vecteurs CDIDDQ. Toutefois, il est possible d'utiliser le logiciel FastScan pour la génération

des deux premiers vecteurs CDIDDQ de chaque sous-ensemble. Ce dernier nous permet de générer des vecteurs de tests pour plusieurs modèles de pannes, comme ceux présentés au chapitre 1. Nous allons générer les patrons de tests de pannes de délais de transition (TDF) pour l'ensemble du circuit.

Un patron de test comprend un ou des vecteurs à injecter au circuit afin de faire apparaître la panne sur un ou des nœuds spécifiques ainsi que la réponse attendue du nœud face à ces vecteurs. La figure 2.4 affiche un exemple d'un patron de test généré par FastScan pour le modèle de panne collé-à.

Figure 2.4 Patron de test FastScan

Le paramètre chain1 représente au départ la suite de valeurs qui sera injectée via Sc\_in dans la chaîne de registres à balayage qui a été au préalable insérée, PI les valeurs à injecter aux entrées et PO les valeurs à mesurer aux sorties du circuit. La deuxième apparition du paramètre chain1 représente la suite de valeurs attendues via Sc\_out. Rappelons toutefois que dans le cas de CDIDDQ, seuls les vecteurs d'entrée nous importent, les sortie n'étant pas vérifié puisque le test est basé sur le courant et non sur le niveau logique résultant des vecteurs d'entrée.

Pour obtenir la liste des pannes de transition, nous devons fournir à FastScan le circuit comportant les bascules à balayage, la librairie que nous avions utilisée précédemment avec DFTadvisor et la configuration ATPG fournie par DFTadvisor. Nous aurons alors une liste de patrons de tests qui, une fois les vecteurs injectés, créeront des transitions pour des nœuds

spécifiques du circuit. Nous allons utiliser cette liste de patrons dans FastScan afin de connaître les nœuds couverts par chacun des patrons. Finalement, nous allons utiliser la liste des nœuds couverts pour obtenir la liste de ceux couverts par les pannes de court-circuit. Les étapes sont affichées à la figure 2.5.

Figure 2.5 Génération des deux premiers vecteurs

Suite à l'analyse de cette liste, on connaît maintenant quels patrons couvrent quels courts-circuits dans le circuit. C'est à ce moment que l'on doit comparer les courts-circuits couverts avec les sites à capacités parasites afin de déterminer quels vecteurs nous sélectionnerons pour le test. À titre informatif, les pannes TDF générées par FastScan pour le circuit s1196 d'ISCAS-89, que nous utiliserons dans nos tests, comprennent 420 patrons qui couvrent 6054 pannes comme affiché dans la figure 2.6.

```

Statistics:

Test Coverage = 99.17%

Total Faults = 6054

DS (det_simulation) = 3367

DI (det_implication) = 118

UU (unused) = 2540

AU (atpg_untestable) = 29

Total Patterns = 420

```

Figure 2.6 Statistiques des pannes TDF pour le circuit S1196

#### 2.3.5 Génération des deux derniers vecteurs

Nous possédons, pour chaque patron, deux vecteurs qui généreront des transitions sur deux ou plusieurs nœuds. Nous devons créer les deux autres vecteurs manquants pour chacun des

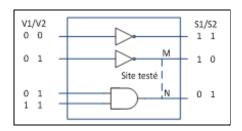

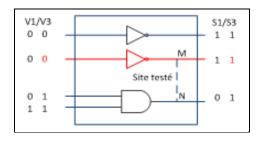

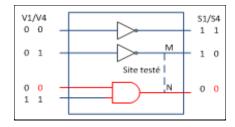

sous-ensembles de quatre vecteurs. La figure 2.7 est un exemple simplifié, dans lequel on a omis les bascules, où sont appliqués des vecteurs TDF sur les nœuds M et N d'un circuit.

Figure 2.7 Vecteurs TDF Vw et Vx

On peut remarquer que, dans l'exemple, on obtient, grâce aux deux transitions créées par l'application de vecteurs, les niveaux 1-0 et 0-1 sur les nœuds M et N qui sont respectivement les vecteurs Vw et Vx de CDIDDQ. Notons que les deux vecteurs qui sont générés par FastScan ne sont pas toujours utilisables comme vecteurs Vw et Vx. On doit en effet s'assurer, à l'aide un test d'indépendance, de pouvoir séparer chacune des transitions sur les deux nœuds dans l'optique de créer les autres vecteurs manquants, soit ici Vy (1-1) et Vz (0-0) qui sont respectivement les vecteurs Vy et Vz de CDIDDQ. Dans notre exemple, on constate facilement que les transitions sont indépendantes, car il est possible de les exécuter séparément et sans influencer les autre partie du circuit, comme la porte inverseur qui n'a pas de lien avec notre court-circuit. Cette indépendance est nécessaire, car les 2 vecteurs supplémentaires doivent être créés de telle sorte que la combinaison des 4 mesures de courant élimine les courants de fuite statique des transistors. Pour commencer, nous allons créer une transition seulement sur le nœud N comme illustré à la figure 2.8.

Figure 2.8 Création du vecteur Vy

Nous avons alors le troisième vecteur, Vy, qui nous permet d'obtenir le niveau 1-1. On remarque que l'on ne modifie pas l'état de la porte inverseur qui n'est pas en lien avec la panne. Il ne nous reste plus qu'à procéder de la même façon pour le nœud M.

Figure 2.9 Création du vecteur Vz

Comme affichés dans la figure 2.9, nous avons créé le dernier vecteur, Vz, qui nous permet d'obtenir le niveau 0-0. Dans ce cas de figure, les vecteurs CDIDDQ seraient comme dans le tableau 2.1.

| Nom du vecteur | Valeur des Vecteurs | Nœud M | Nœud N |

|----------------|---------------------|--------|--------|

| Vx             | 0111                | 0      | 1      |

| Vy             | 0011                | 1      | 1      |

| Vz             | 0101                | 0      | 0      |

| Vw             | 0001                | 1      | 0      |

Tableau 2.1 Exemple de vecteurs CDIDDQ

Avec les mesures de courant pour chaque vecteur, on peut alors appliquer CDIDDQ.

$$CDIDDQ = I(Vy_{1-1}) + I(Vz_{0-0}) - (I(Vw_{1-0}) + I(Vx_{0-1}))$$

(2.2)

Il est important de comprendre que, pour un circuit plus complexe, il est difficile et long de déterminer manuellement si les transitions sont indépendantes et de créer les vecteurs manquants qui mènent à l'élimination des courants de fuite. C'est pourquoi un logiciel a été mis au point (Thibeault et Hariri 2009) permettant de vérifier l'indépendance des transitions et de générer les deux vecteurs manquants aux patrons de test des pannes de transition fournis par FastScan.

## 2.4 Présentation des patrons de test CDIDDQ

Chaque patron (sous-ensemble de 4 vecteurs) de test CDIDDQ permet de tester (au moins) une panne de court-circuit à un endroit distinct. Précédemment, seulement un patron, généré pour le circuit S1196 d'ISCAS-89, a été testé expérimentalement (Haithem 2011) : le patron p17. Dans le cadre de ce projet, nous allons expérimenter la technique de test CDIDDQ avec trois autres patrons (p5, p6 et p29) pour le même circuit afin de confirmer sa capacité à détecter des courts-circuits à divers endroits du circuit. Le nom des patrons réfère aux numéros de patrons de la liste de test TDF générée pour le circuit s1196 par FastScan, donc p17 est la 17<sup>e</sup> patron de la liste. Le choix des patrons n'a pas été fait au hasard, il n'aurait pas été possible de prendre, par exemple, les patrons 1, 2, 3 et 4, car ils ne couvraient pas des courts-circuits et/ou les quatre transitions n'étaient pas indépendantes. Les tableaux 2.2, 2.3, 2.4 et 2.5 affichent les quatre patrons de test CDIDDQ pour le circuit s1196 d'ISCAS-89. On peut voir dans ce tableau les valeurs pour les signaux d'entrée Gx et Sc\_en nécessaire pour obtenir chacun des vecteurs CDIDDQ.

Tableau 2.2 Patron de test 5

| Vecteurs | G                   | G | G  | G  | G  | G  | G | G | G | G | G | G | G | G | Sc_en |

|----------|---------------------|---|----|----|----|----|---|---|---|---|---|---|---|---|-------|

|          | 0                   | 1 | 10 | 11 | 12 | 13 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 |       |

| Vw       | 0                   | 1 | 0  | 0  | 0  | 0  | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1     |

| Vy       | 1                   | 1 | 0  | 0  | 0  | 0  | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0     |

|          |                     |   |    |    |    |    |   |   | • | • | • |   | • |   |       |

| Vw       | 0                   | 1 | 0  | 0  | 0  | 0  | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1     |

| Vz       | 1                   | 1 | 0  | 0  | 0  | 1  | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0     |

|          |                     |   |    |    |    |    |   |   | • | • | • |   | • |   |       |

| Vw       | 0                   | 1 | 0  | 0  | 0  | 0  | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1     |

| Vx       | 1                   | 1 | 0  | 0  | 0  | 1  | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0     |

|          |                     |   |    |    |    |    |   |   |   |   |   |   |   |   |       |

| Scan-In  | 1101100000010010001 |   |    |    |    |    |   |   |   |   |   |   |   |   |       |

Tableau 2.3 Patron de test 6

| Vecteurs | G                  | G | G  | G  | G  | G  | G | G | G | G | G | G | G | G | Sc_en |

|----------|--------------------|---|----|----|----|----|---|---|---|---|---|---|---|---|-------|

|          | 0                  | 1 | 10 | 11 | 12 | 13 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 |       |

| Vy       | 0                  | 0 | 0  | 1  | 0  | 1  | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1     |

| Vz       | 0                  | 1 | 1  | 1  | 1  | 0  | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0     |

|          |                    |   |    |    |    |    |   |   |   |   |   |   |   |   |       |

| Vy       | 0                  | 0 | 0  | 1  | 0  | 1  | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1     |

| Vx       | 0                  | 1 | 0  | 1  | 1  | 0  | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 0     |

|          | •                  |   |    |    |    |    |   |   | • |   | • |   | • |   |       |

| Vy       | 0                  | 0 | 0  | 1  | 0  | 1  | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1     |

| Vw       | 0                  | 1 | 1  | 1  | 1  | 0  | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0     |

|          |                    |   |    |    |    |    |   |   |   |   |   |   |   |   |       |

| Scan-In  | 001011011110110101 |   |    |    |    |    |   |   |   |   |   |   |   |   |       |

Tableau 2.4 Patron de test 17

| Vecteurs | G                | G | G  | G  | G  | G  | G | G | G | G | G | G | G | G | Sc_en |

|----------|------------------|---|----|----|----|----|---|---|---|---|---|---|---|---|-------|

|          | 0                | 1 | 10 | 11 | 12 | 13 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 |       |

| Vw       | 1                | 1 | 1  | 0  | 1  | 0  | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 1     |

| Vx       | 0                | 1 | 1  | 1  | 1  | 1  | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0     |

|          |                  | • | •  | •  | •  | •  | • | • |   | • |   | • | • |   |       |

| Vw       | 1                | 1 | 1  | 0  | 1  | 0  | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 1     |

| Vy       | 0                | 1 | 1  | 0  | 1  | 1  | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0     |

|          |                  | • | •  | •  | •  | •  | • | • |   | • |   | • | • |   |       |

| Vw       | 1                | 1 | 1  | 0  | 1  | 0  | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 1     |

| Vz       | 0                | 1 | 1  | 1  | 1  | 1  | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0     |

|          |                  |   |    |    |    |    |   |   |   |   |   |   |   |   |       |

| Scan-In  | 0010011101010110 |   |    |    |    |    |   |   |   |   |   |   |   |   |       |

Tableau 2.5 Patron de test 29

| Vecteurs | G                  | G | G  | G  | G  | G  | G | G | G | G | G | G | G | G | Sc_en |

|----------|--------------------|---|----|----|----|----|---|---|---|---|---|---|---|---|-------|

|          | 0                  | 1 | 10 | 11 | 12 | 13 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 |       |

| Vz       | 0                  | 1 | 0  | 0  | 0  | 0  | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1     |

| Vy       | 0                  | 1 | 0  | 0  | 1  | 1  | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0     |

|          |                    |   |    |    |    |    |   |   |   |   |   |   |   |   |       |

| Vz       | 0                  | 1 | 0  | 0  | 0  | 0  | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1     |

| Vw       | 0                  | 1 | 0  | 0  | 1  | 0  | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0     |

|          | •                  |   |    |    |    |    | • | • | • |   | • |   | • |   |       |

| Vz       | 0                  | 1 | 0  | 0  | 0  | 0  | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1     |

| Vx       | 0                  | 1 | 0  | 0  | 0  | 1  | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0     |

|          |                    |   |    |    |    |    |   |   |   |   |   |   |   |   |       |

| Scan-In  | 111110000000101011 |   |    |    |    |    |   |   |   |   |   |   |   |   |       |

Ces 4 tableaux exposent les patrons de tests CDIDDQ contenant les paires de vecteurs que l'on doit mettre aux entrées du circuit s1196 pour obtenir les niveaux voulus sur le nœud à tester en plus de la suite de valeurs qui doit être injectée dans la chaîne de bascules à balayage afin de placer les bascules à un état prédéterminé.

## 2.5 Simulation des patrons de test CDIDDQ

Il est impératif de valider les vecteurs des patrons de test CDIDDQ présentés précédemment. En effet, nous devons nous assurer que ces vecteurs placent les nœuds à tester au niveau désiré. On doit premièrement identifier les deux nœuds testés par chaque patron grâce à la liste des nœuds couverts fournie par FastScan. La source et le nom des nœuds testés pour chaque patron sont écrits dans le tableau 2.6.

Tableau 2.6 Source des nœuds testés

| Patron | M                        | N                        |

|--------|--------------------------|--------------------------|

| 5      | Sortie du NOT_71, nœud   | Sortie du NAND_56, nœud  |

|        | G501                     | G166                     |

| 6      | Sortie du NOT_11, nœud   | Sortie du NOT_10, nœud   |

|        | G536                     | G533                     |

| 17     | Sortie du NAND2_12,      | Sortie du NOT_37, nœud   |

|        | nœud G74                 | G275                     |

| 29     | Sortie du U28, nœud n188 | Sortie du U27, nœud n189 |

Il est toutefois important de noter qu'un patron de test peut tester plus d'un nœud à la fois. Par exemple, le test CDIDDQ du patron 6 crée simultanément les transitions requises sur plusieurs nœuds. Comme nous créerons pour notre test un seul court-circuit résistif, nous n'utiliserons que deux nœuds parmi ceux possédant les transitions nécessaires. Le choix de la paire de nœuds fournissant les transitions voulues a été fait aléatoirement.

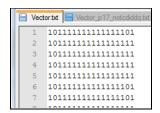

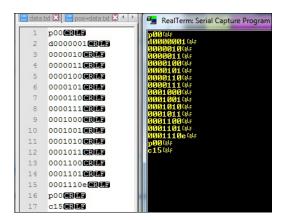

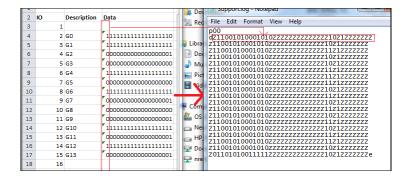

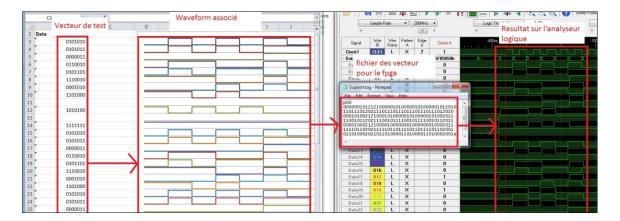

La prochaine étape consiste à la mise au point d'un banc de test qui injectera les vecteurs aux entrées du circuit à tester, soit le S1196. Ce banc de test agit comme un registre à décalage : il effectue la lecture d'un fichier texte comportant les valeurs à assigner aux broches d'entrée et les décale vers les broches d'entrées du circuit sous test à chaque coup d'horloge. La figure 2.10 affiche un fichier texte comportant les valeurs d'entrée à injecter au circuit.

Figure 2.10 Fichier texte des vecteurs

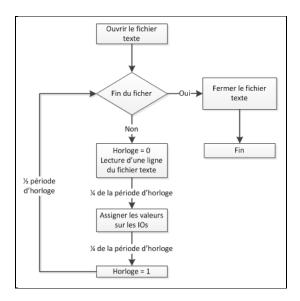

Plus précisément, on commence par initialiser l'horloge aux niveaux bas et on procède à la lecture d'une ligne du fichier texte. Par la suite, on attend ¼ de la période d'horloge avant d'affecter les valeurs des entrées lues dans le fichier texte. Le délai entre la lecture et l'assignation a uniquement été mis en place afin de faciliter la lecture du chronogramme. On attend alors un autre ¼ de la période d'horloge avant de créer un front montant sur le signal d'horloge. Pour finir, on attend ½ de la période d'horloge, ce qui complète notre cycle, avant de boucler jusqu'à ce que le fichier texte ne comporte plus de nouvelle ligne. Dans ce cas, on procède à la fermeture du fichier texte et on arrête la simulation. La figure 2.11 affiche la machine à état du banc de test.

Figure 2.11 Machine à état du banc de test

En concevant le banc de test ainsi, il est possible de l'utiliser sans modification pour les quatre patrons de tests, puisque seul le fichier texte comportant la valeur des entrées à injecter doit être modifié.

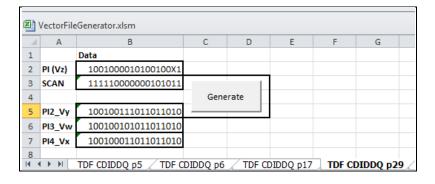

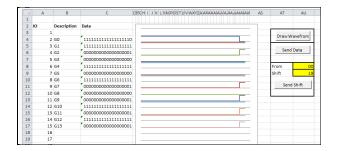

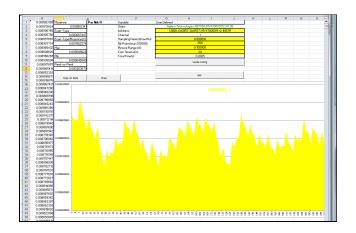

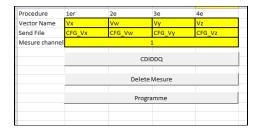

Afin d'éviter d'avoir à écrire manuellement les valeurs dans un fichier texte, un programme Excel a été conçu. L'objectif principal de ce programme est de pouvoir créer le fichier texte nécessaire au banc de test directement avec les vecteurs CDIDDQs. La figure 2.12 affiche l'onglet du logiciel permettant de générer le fichier texte nécessaire afin de tester le patron 19 du s1196 sur notre banc de test.

Figure 2.12 Programme de génération de vecteurs pour le banc de test

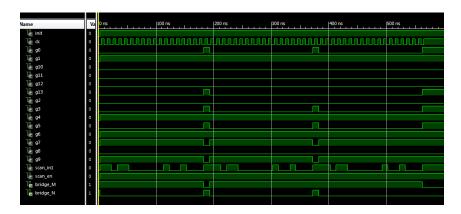

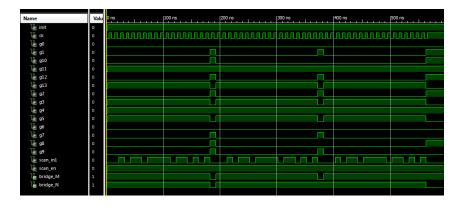

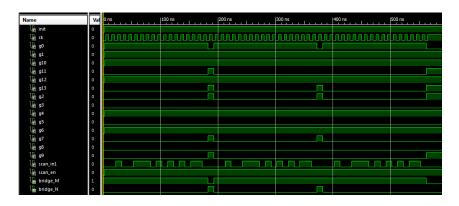

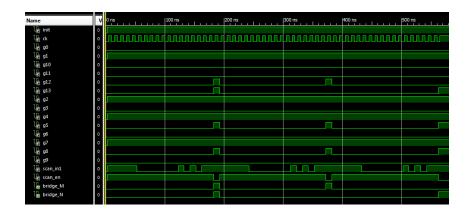

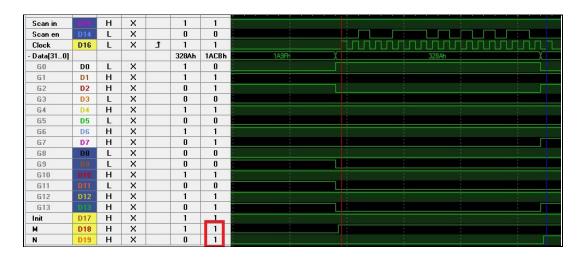

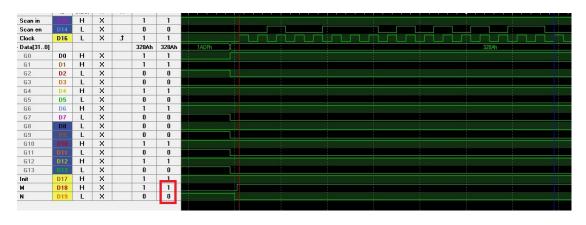

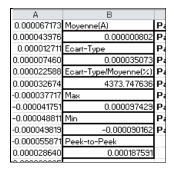

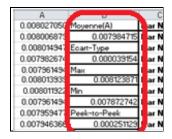

Les vecteurs transposés dans un fichier texte et le banc de test nous permettent de passer à la simulation des vecteurs CDIDDQ. Pour la simulation, nous avons utilisé ISIM de Xilinx. Les figures 2.13, 2.14, 2.15 et 2.16 affichent le résultat des simulations pour les quatre patrons de test présentés précédemment.

Figure 2.13 Simulation du patron 5

Figure 2.14 Simulation du patron 6

Figure 2.15 Simulation du patron 17

Figure 2.16 Simulation du patron 29

Comme on peut le constater, la simulation nous confirme que nous avons les transitions voulues sur les nœuds M et N lors de l'application des vecteurs CDIDDQ. En observant les chronogrammes, on remarque que l'application des deux premiers vecteurs crée une transition sur les deux nœuds tandis que les deux autres vecteurs créent une seule transition sur un seul des nœuds. On remarque aussi que l'ordre de ces transitions diffère d'un patron à l'autre. Ainsi, la première paire de vecteurs du patron 6 crée une transition 1 à 0 sur M et N, alors que la première paire de vecteurs du patron 29 crée une transition 0 à 1 sur M et N. Comme expliqué précédemment, ceci est causé par FastScan qui crée des transitions montantes ou descendantes.

En résumé, la simulation des patrons de test CDIDDQ sur le circuit s1196 nous a permis de valider que les vecteurs plaçaient les nœuds à tester au bon niveau. Nous sommes donc en mesure d'affirmer que les patrons et les circuits correspondant à ceux-ci sont fonctionnels et prêts à l'implémentation.

## 2.6 Application expérimentale de CDIDDQ

Grâce à la simulation, nous avons pu confirmer que les vecteurs de test CDIDDQ appliquaient les niveaux requis sur les nœuds à tester. Puisque nous désirons être en mesure d'appliquer les tests CDIDDQ pour détecter une panne de court-circuit, nous devrons en insérer une entre les deux nœuds testés. Le court-circuit inséré devra être résistif afin de pouvoir déterminer jusqu'à quel point nous sommes en mesure de détecter la panne. Pour procéder à l'insertion d'un court-circuit résistif variable, nous allons implémenter le circuit sur un FPGA en dirigeant les nœuds à tester sur des broches de sortie afin d'y placer la résistance voulue pour créer un court-circuit résistif. La figure 2.17 reflète l'approche décrite.

Figure 2.17 Redirection des nœuds testés

Puisque chacun des sous-ensembles de quatre patrons de test couvre un endroit différent du circuit et que nous désirons tester 4 sites de courts-circuits différents, nous devrons donc générer quatre circuits modifiés afin de pouvoir diriger les nœuds testés vers des broches du FPGA.

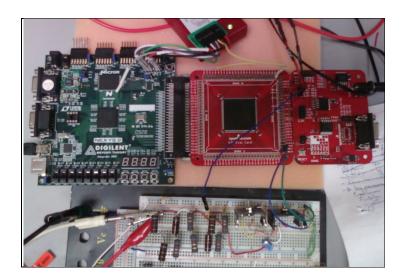

# 2.6.1 Montage expérimental

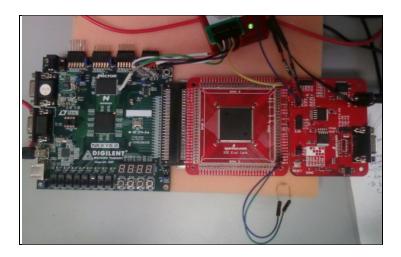

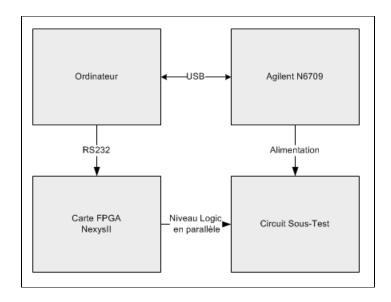

Afin d'injecter les vecteurs au FPGA qui émule le circuit à tester, nous allons utiliser un deuxième FPGA qui agira comme testeur CDIDDQ; nous allons donc avoir un FPGA qui teste un autre FPGA. Nous allons alimenter le FPGA sous test avec le bloc d'alimentation duquel nous lirons la consommation de courant. Bien que la configuration exacte du montage ait changé à travers le temps, le principe de base, lui, n'a pas changé. La figure 2.18 résume notre montage expérimental.

Figure 2.18 Montage expérimental

#### 2.7 La mesure de courant de consommation

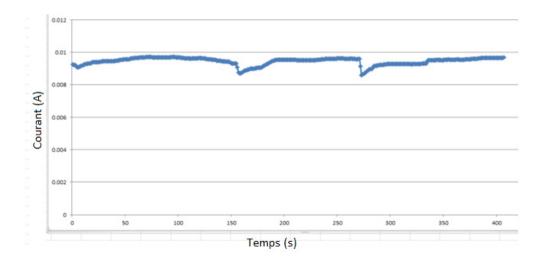

Nous avons les vecteurs CDIDDQ qui exerceront les transitions sur les nœuds à tester. Comme mentionné précédemment, nous allons utiliser une résistance externe afin de simuler un court-circuit résistif entre les nœuds M et N. Pour procéder au calcul de CDIDDQ afin de détecter la défectuosité, nous devrons lire la consommation de courant du circuit face aux quatre niveaux logiques (0-0, 0-1, 1-0 et 1-1) appliqués aux nœuds à tester. Comme on a pu le constater plus tôt, on doit appliquer trois paires de vecteurs pour obtenir les quatre niveaux désirés. Chaque paire de vecteurs crée deux niveaux logiques. Le premier vecteur de chaque paire est toujours le même, donc on le mesure une seule fois. Ainsi, pour l'application de la première paire nous allons procéder à deux mesures de courant contrairement aux deux

autres paires de vecteurs pour lesquels on procédera à une seule mesure. La figure 2.19 affiche, dans le chronogramme, le moment de la capture des mesures.

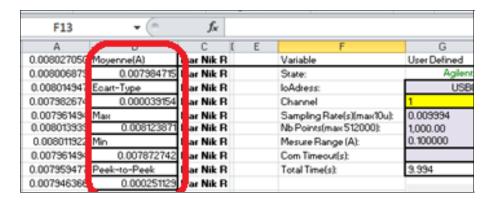

Figure 2.19 Mesure du courant