#### Efficient Protocol Design Flow for Embedded Systems

Von der Fakultät für Mathematik, Naturwissenschaften und Informatik der Brandenburgischen Technischen Universität Cottbus

zur Erlangung des akademischen Grades

Doktor der Ingenieurwissenschaften

(Dr.-Ing.)

genehmigte Dissertation

vorgelegt von

# Dipl.-Inf. Daniel Dietterle

geboren am 10. Februar 1978 in Eberswalde-Finow

Gutachter: Prof. Dr.-Ing. Rolf Kraemer

Gutachter: Prof. Dr.-Ing. Jörg Nolte

Gutachter: Prof. Dr.-Ing. Adam Wolisz

Tag der mündlichen Prüfung: 25. Februar 2009

## Abstract

It is predicted that, in the next years, wireless sensor networks could be massively deployed in a wide variety of application areas, such as agriculture, logistics, automation, or infrastructure monitoring. An extremely low power consumption, high dependability, and low cost are common requirements for sensor nodes in all these applications. This can be achieved only by tiny, power-efficient microcontrollers and communication systems integrated on a single chip.

Formal description techniques, such as SDL (Specification and Description Language), are suitable to formally prove properties of models designed in these languages. Code generators facilitate the automatic transformation of SDL models into software implementations, while preserving the properties of the model and, thus, achieving high system dependability. The implementations consist of the translated state machine behavior and, additionally, require a run-time environment for model execution.

The objective of this work was to investigate an integrated design flow for embedded systems, which should allow the development of efficient and dependable system implementations from abstract SDL specifications. In this thesis, concepts for minimal SDL run-time environment have been devised and realized by an example implementation.

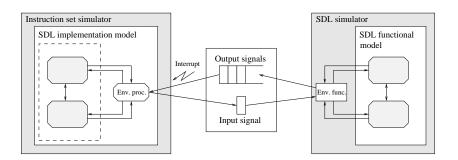

Not only pure software implementations should be considered, but starting from these also the hardware/software (HW/SW) partitioning of the system should be supported. For this purpose, a cosimulation framework that allows the coupling of an instruction set simulator (ISS) with a functional SDL simulation has been investigated and prototypically implemented within the scope of this thesis.

By shifting functionality to dedicated hardware components it is possible to take computational load from the microcontroller and to decrease the overall energy consumption by reducing the clock frequency and lowering the supply voltage. Due to the use of SDL, the design flow lends itself particularly to the implementation of communication protocols, and is limited to applications with soft real-time requirements.

For an SDL-based design flow targeted to resource-constrained embedded systems, concepts and real implementations of minimal SDL run-time environments were lacking. Available software tools, indeed, enable the transformation of SDL models into C code, however for an efficient implementation, an integration into existing real-time operating systems (RTOS) for small microcontrollers is essential.

A prototypical implementation of a run-time library for the Reflex RTOS has been created to validate our general concepts. It is about 30 % faster and consumes less than half of the program memory compared to the operating system independent run-time environment of the tool vendor Telelogic. For simple SDL models, the application requires in total less than 8 kbytes program memory and 1 kbyte RAM.

For the evaluation of design alternatives that realize different hardware/software partitionings, instruction set simulators are particularly suitable. They facilitate the identification of performance bottlenecks of the HW/SW system.

Test stimuli are required in order to measure the performance and response time of systems under design. The development of an environment that generates such test signals can be a laborious task. Thus, it is reasonable, especially in the design of protocols, to use an SDL simulation of a communication network to generate these test stimuli. Such an SDL model already exists and is the basis for the implementation. The protocol implementation simulated by the ISS then becomes part of the network simulation. An efficient coupling of SDL simulations with instruction set simulators had to be investigated, and a solution is presented in this thesis.

Based on the general concepts, a cosimulation framework for the ISS TSIM for the LEON2 processor was realized by the author. The joint SDL and instruction set simulation is very fast, which could be demonstrated by connecting a software implementation of the complex IEEE 802.15.3 medium access control (MAC) protocol with an SDL simulation of a network consisting of four devices. The real execution time for 10 seconds of simulation time amounted to just 50 seconds.

The overall design flow was validated by means of a HW/SW implementation of the IEEE 802.15.3 wireless MAC protocol. The author designed a complete SDL model of the protocol and integrated it into Reflex. By using our cosimulation environment for the TSIM simulator, the model was partitioned into hardware and software. For the hardware part, a dedicated protocol accelerator was designed by the author. This hardware component was integrated on a single chip with the LEON2 processor and, finally, manufactured.

It could be shown that the presented methodology enables the design and implementation of efficient HW/SW systems. Consequently, it can be applied to the development of dependable and energy-efficient wireless sensor nodes and other embedded systems.

**Keywords:** Model-based design, protocol engineering, cosimulation, IEEE 802.15.3.

## Zusammenfassung

Es wird vorausgesagt, dass in einigen Jahren eine riesige Menge von drahtlos kommunizierenden Sensorknoten in den verschiedensten Anwendungsgebieten, etwa der Landwirtschaft, Logistik, Automatisierung oder der Überwachung von Infrastruktur, Einzug halten könnten. Diesen Geräten ist gemeinsam, dass sie einen äußerst geringen Stromverbrauch, hohe Zuverlässigkeit und geringe Kosten aufweisen müssen. Dies ist nur mit kleinen, Strom sparenden Mikrocontrollern und auf einem einzigen Chip integrierten Kommunikationssystemen erreichbar.

Formale Beschreibungssprachen, wie SDL (Specification and Description Language), eignen sich dazu, Eigenschaften von in dieser Sprache beschriebenen Modellen formal zu beweisen. Durch Code-Generatoren wird die automatische Umsetzung von SDL-Modellen in eine Software-Implementation unterstützt, welche die Eigenschaften des Modells erhalten soll und somit eine hohe Zuverlässigkeit des Systems erreicht. Neben der Umsetzung des Zustandsmaschinenverhaltens wird auch eine Laufzeitumgebung zur Ausführung benötigt.

Die Zielstellung dieser Arbeit war es, einen durchgängigen Entwurfsprozess für eingebettete Systeme auf der Basis von SDL zu untersuchen, der es erlaubt, von abstrakten Spezifikationen in SDL zu effizienten und zuverlässigen Systemimplementationen zu gelangen. Es wurden neue Konzepte für minimale Laufzeitumgebungen erarbeitet und beispielhaft umgesetzt.

Es sollte jedoch nicht nur die Generierung von reinen Software-Implementationen betrachtet werden, sondern von diesen ausgehend auch die Hardware/Software- (HW/SW-) Partitionierung der Systeme unterstützt werden. Zu diesem Zweck wurde im Rahmen dieser Arbeit ein Cosimulations-Ansatz zur Kopplung eines Befehlssatzsimulators (Instruction Set Simulator, ISS) mit einer abstrakten SDL-Simulation untersucht und prototypisch implementiert.

Durch die Verlagerung von Funktionen in eigens dafür entworfene HW-Komponenten ist es möglich, Last vom Mikrocontroller zu nehmen und den Gesamtenergieverbrauch des eingebetteten Systems durch das Absenken der Taktfrequenz und Versorgungsspannung zu verringern. Wegen der Verwendung von SDL eignet sich der Entwurfsprozess besonders für die Implementierung von Kommunikationsprotokollen und ist auf Anwendungen mit weichen Echtzeitanforderungen beschränkt.

Für eine SDL-basierte Entwurfsmethodik ausgerichtet auf extrem ressourcenbeschränkte eingebettete Systeme fehlten bislang Konzepte und tatsächliche Implementationen von minimalen SDL-Laufzeitumgebungen. Verfügbare Werkzeuge erlauben zwar die Übersetzung von SDL-Modellen in C-Code, für eine effiziente Implementation ist jedoch die Integration in vorhandene Mikrocontroller-Echtzeitbetriebssysteme (RTOS) erforderlich.

Eine prototypische Implementation einer Laufzeitbibliothek für das RTOS Reflex wurde entwickelt, um die allgemeinen Konzepte zu validieren. Verglichen mit der betriebssystem-unabhängigen Laufzeitumgebung des Werkzeugherstellers Telelogic ist diese Implementation um ca. 30 % schneller und benötigt weniger als die Hälfte des Programmspeichers. Bei kleinen SDL-Systemen benötigt die gesamte Applikation weniger als 8 kB Programmspeicher und 1 kB RAM.

Zur Bewertung von Entwurfsalternativen, die unterschiedliche HW/SW-Partitionierungen realisieren, eignen sich besonders Befehlssatzsimulatoren. Diese erlauben die taktgenaue Simulation der Ausführung von Programmen auf einem Prozessor, häufig auch von Modellen eigener HW-Komponenten, und sind um Größenordnungen schneller als reine HW-Simulationen. Mit ihnen lassen sich zeitkritische Teile eines HW/SW-Systems identifizieren.

Um Reaktionen des zu evaluierenden Systems hervorzurufen und dessen Performance messen zu können, werden Teststimuli benötigt. Die Entwicklung einer Umgebung, welche solche Testsignale erzeugt, kann sehr aufwändig sein. Daher ist es naheliegend, gerade im Bereich der Entwicklung von Protokollen, die Teststimuli durch die Simulation eines Kommunikationnetzes in SDL zu erzeugen. Ein solches SDL-Modell liegt ja bereits der Implementierung zu Grunde. Die im ISS ausgeführte Protokollimplementierung wird dann Teil der Netzwerksimulation. Die möglichst effiziente Kopplung von SDL-Simulationen mit dem ISS musste untersucht werden und wurde im Rahmen dieser Arbeit gelöst.

Basierend auf den allgemeinen Konzepten wurde eine Cosimulation mit dem ISS TSIM für den LEON2-Prozessor vom Autor realisiert. Die gemeinsame Simulation ist sehr schnell, was anhand der Kopplung einer SW-Implementation des sehr komplexen MAC-Protokolls IEEE 802.15.3 mit einer SDL-Simulation eines aus vier Stationen bestehenden Netzes nachgewiesen wurde. Die reale Simulationszeit für 10 Sekunden simulierte Zeit betrug gerade einmal 50 Sekunden.

Der gesamte Entwurfsprozess wurde anhand einer HW/SW-Implementierung des im Standard IEEE 802.15.3 festgelegten drahtlosen Medienzugriffsprotokolls validiert. Dazu wurde vom Autor ein komplettes SDL-Modell des Protokolls entwickelt, dieses in Reflex integriert und in einem HW/SW-Codesign-Prozess partitioniert. Dabei wurde die Cosimulationsumgebung mit dem TSIM-Simulator verwendet. Für die HW-Partition wurde vom Autor ein Protokollbeschleuniger entworfen. Dieser wurde gemeinsam mit dem LEON2-Prozessor auf einem Chip integriert und gefertigt.

Somit wurde nachgewiesen, dass die vorgestellte Methodik geeignet ist, um effiziente HW/SW-Systeme zu entwerfen und zu implementieren. Sie kann folglich zur Entwicklung von zuverlässigen und Strom sparenden drahtlosen Sensorknoten und anderen eingebetteten Systemen angewendet werden.

## Acknowledgements

I would like to express my gratitude to my supervisor Prof. Rolf Kraemer for giving me the opportunity to conduct my research work at the IHP and for his enormous support throughout the last years.

A special thanks to Prof. Peter Langendörfer for the scientific discussions and guidance in the phase of writing the manuscript.

Many people from IHP's Systems Department contributed to or supported me in my work, without their help this thesis would not have been possible. I would like to thank Dr Irina Babanskaja, Jerzy Ryman, and Dr Kai Dombrowski for contributing to the design of the IEEE 802.15.3 MAC protocol and its validation. The model architecture is largely inspired by previous work done by Klaus Tittelbach-Helmrich, whom I would also like to thank for his efforts to apply this model to a communication system in the 60 GHz band and the valuable feedback that led to many improvements.

Gerald Wagenknecht put a lot of effort into designing the first version of the tight integration library for Reflex. His work and our discussions together with Dr Jean-Pierre Ebert led us to a deeper understanding of the output of the CAdvanced code generator and not to get lost in the dozens of macros. I very much appreciated the support from the developers of Reflex, in particular from Karsten Walther from BTU Cottbus and my colleague Marcin Brzozowski, on questions related to this new operating system.

I owe special gratitude to a number of colleagues who made it possible that at the end of many years of research and implementation work the results from the application of our novel design flow to the IEEE 802.15.3 MAC protocol implementation have been turned into an ASIC and can be demonstrated on a prototyping board: Dr Zoran Stamenkovic, Goran Panic, and Gunter Schoof for the design and synthesis of the LEON2 processor system; Silvia Hinrich, Brigitte Cheuffa-Tchako, Peter Dähnert, and Christoph Wolf for testing the chip; Jens Lehmann, Jörg Domke, and Horst Frankenfeldt for designing and assembling the PCB.

Many thanks to Mike Turi and Jonathan Cree from Washington State University for proofreading the manuscript.

I received tremendous support from my friends and family, your love and motivation have created the confidence that is needed to complete such a huge task. So, this thesis belongs also to all of you. Thank you for being there for me at all times!

## Contents

| 1        | Int  | roduction                                                   | 1   |

|----------|------|-------------------------------------------------------------|-----|

|          | 1.1  | Scope of the thesis                                         | 1   |

|          | 1.2  | Problem statement                                           | 3   |

|          | 1.3  | Contributions                                               | 12  |

|          | 1.4  | Overview                                                    | 14  |

| <b>2</b> | Des  | sign of Embedded Communication Systems                      | 15  |

|          | 2.1  | Protocol engineering                                        | 16  |

|          |      | 2.1.1 Protocol mechanisms                                   | 17  |

|          |      | 2.1.2 Wireless medium access control protocols              | 22  |

|          |      | 2.1.3 Specification and design of communication protocols   | 28  |

|          |      | 2.1.4 Protocol development                                  | 36  |

|          | 2.2  | Hardware/software codesign                                  | 47  |

|          |      | 2.2.1 Architectural components of hardware/software systems | 48  |

|          |      | 2.2.2 System modeling                                       | 53  |

|          |      | 2.2.3 Hardware/software partitioning                        | 57  |

|          |      | 2.2.4 Tools                                                 | 61  |

| 3        | Rel  | ated Work                                                   | 67  |

|          | 3.1  | System design with SDL                                      | 68  |

|          | 3.2  | Communication protocol implementations based on SDL         | 81  |

| 4        | Inte | egrated Design Flow based on SDL                            | 87  |

|          | 4.1  | General overview                                            | 88  |

|          | 4.2  | SDL run-time environment for deeply embedded systems        | 96  |

|          | 4.3  | Cosimulation with an instruction set simulator              | 108 |

| 5        | Effi | cient Integration of SDL Models into Reflex                 | 121 |

|          | 5.1  | Output of the CAdvanced code generator                      | 122 |

|          |      | 5.1.1 Transformation of system structure                    | 122 |

|          |      | 5.1.2 Transformation of process state machines              | 124 |

|          | 5.2  | Tight integration model for Reflex                          | 125 |

|          |      | 5.2.1 The operating system Reflex                           | 126 |

|          |      | 5.2.2 Mapping of SDL processes                              | 129 |

|    |                    | 5.2.3  | Memory management for signal buffers             | 133 |

|----|--------------------|--------|--------------------------------------------------|-----|

|    |                    | 5.2.4  | Timer handling                                   | 135 |

|    |                    | 5.2.5  | Interfacing the environment                      | 136 |

|    |                    | 5.2.6  | Putting it all together: the SDLSystem class     | 137 |

|    | 5.3                | Implei | mentation results                                | 139 |

| 6  | SDI                | Cosi   | mulation with the TSIM Instruction Set Simulator | 145 |

|    | 6.1                | The ir | nstruction set simulator TSIM                    | 146 |

|    | 6.2                | Integr | ating TSIM with Telelogic's SDL simulator        | 149 |

|    | 6.3                | Imple  | mentation of the cosimulation framework          | 150 |

| 7  | Des                | ign Re | esults                                           | 159 |

|    | 7.1                | SDL n  | nodel of the IEEE 802.15.3 MAC protocol          | 160 |

|    |                    | 7.1.1  | Model architecture                               | 161 |

|    |                    | 7.1.2  | Behavioral description                           | 162 |

|    |                    | 7.1.3  | Results                                          | 166 |

|    | 7.2                | Partit | ioning into hardware and software                | 167 |

|    | 7.3                | Protoc | col accelerator design                           | 176 |

|    |                    | 7.3.1  | Target hardware platform                         | 177 |

|    |                    | 7.3.2  | Architecture                                     | 178 |

|    |                    | 7.3.3  | Transmission queue                               | 179 |

|    |                    | 7.3.4  | Support for flexible timing                      | 181 |

|    |                    | 7.3.5  | Software interface                               | 182 |

|    |                    | 7.3.6  | Results                                          | 182 |

| 8  | Crit               | ical A | ssessment and Future Work                        | 185 |

| 9  | Con                | clusio | ns                                               | 193 |

| Li | List of Acronyms 1 |        |                                                  |     |

| Bi | bliog              | graphy |                                                  | 199 |

| Cı | urric              | ulum ' | Vitae                                            | 215 |

## List of Tables

| 4.1        | Environment functions that are called by the SDL simulator and must be supplied by the designer                                                          | 118        |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 5.1        | Explanation of the most common macros found in the generated                                                                                             | 107        |

| 5.2        | PAD functions                                                                                                                                            | 127        |

| 5.3        | implemented with the light integration approach                                                                                                          | 141        |

| 5.4        | implemented with the tight integration approach Sizes of the text, data, and bss segments (in bytes) of the executable                                   | 141        |

|            | for the Ping2 application with the light and tight integration approaches, respectively.                                                                 | 142        |

| 5.5        | Performance results for the SDL model Ping2 obtained with different compiler optimization levels ( $O2$ and $Os$ ) for the mspgcc                        | 143        |

| 5.6        | Processing time with varying number of signals sent into the SDL model                                                                                   | 143        |

| 6.1        | Overview of the most important functions exported by the TSIM library                                                                                    | 148        |

| 6.2        | Relevant functions that have to be provided by user-defined I/O devices                                                                                  | 149        |

| 6.3        | Comparison of the real simulation times for wireless network simulations with and without an external instruction set simulator                          | 158        |

| 7.1        | Results from the simulation of data transmissions by the PNC with different frame lengths. (All times are relative to the start of the                   | 1 = 0      |

| 7.0        | data frame transmission.)                                                                                                                                | 173        |

| 7.2<br>7.3 | Protocol accelerator registers and their purpose                                                                                                         | 183<br>184 |

| 8.1        | Sizes of the text, data, and bss segments (in bytes) of the executable for the S-MAC demonstration application created from an SDL model of the protocol | 190        |

|            |                                                                                                                                                          | 100        |

# List of Figures

| Estimated growth of transistor density in SRAM and logic cells according to the ITRS roadman 2005 [ITR05]                                                                                        | 2                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| Overview of the complete design flow starting from an initial SDL                                                                                                                                | 6                                          |

| The instruction set simulation of the target system including models of the hardware partition is embedded in the overall network simulation based on SDL                                        | 11                                         |

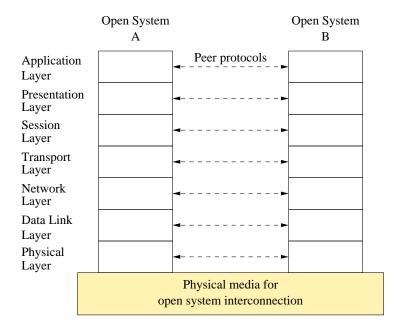

| Seven layer OSI reference model and peer protocols [ISO94]                                                                                                                                       | 17                                         |

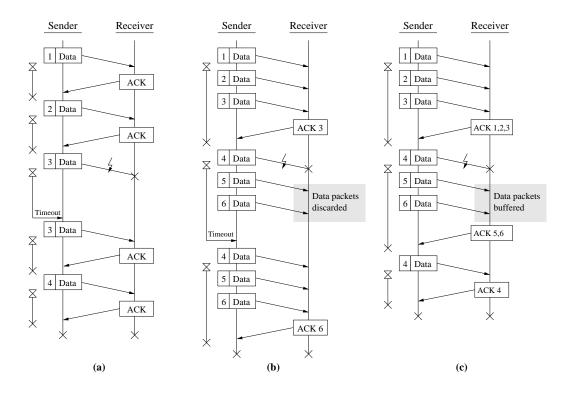

| Illustration of the three ARQ schemes Stop-and-Wait (a), Go-Back-                                                                                                                                | 20                                         |

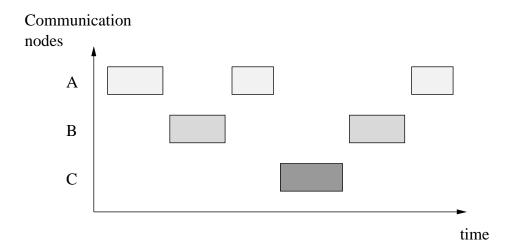

| Communication nodes share the wireless channel in the time division multiple access (TDMA) scheme. Each node may access the channel, i.e. transmit data, exclusively in a time slot in some pre- | 23                                         |

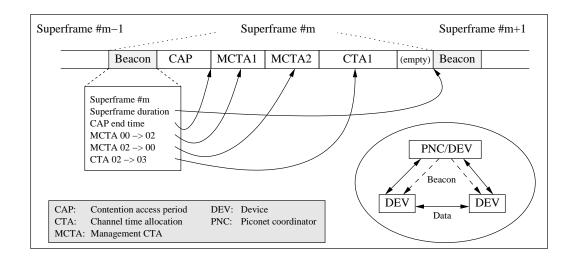

| Superframe structure, beacon contents, and basic network topology                                                                                                                                | 27                                         |

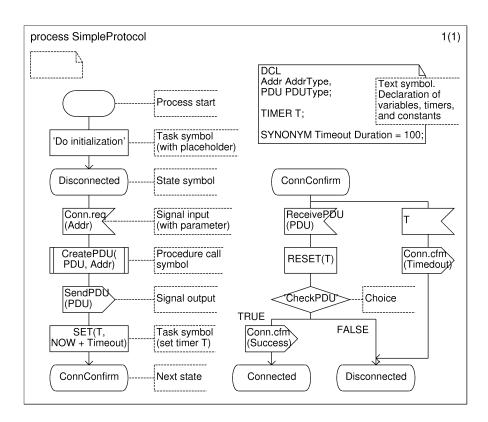

| Fragment of a simplified protocol specification as part of an SDL                                                                                                                                | 32                                         |

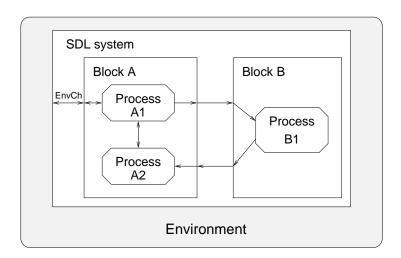

| 1                                                                                                                                                                                                | 34                                         |

| · ·                                                                                                                                                                                              | 37                                         |

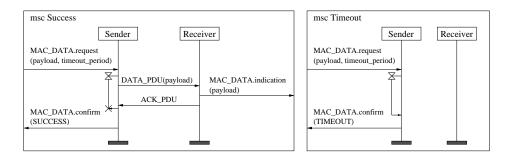

| Two exemplary Message Sequence Charts as part of a service spec-                                                                                                                                 | 38                                         |

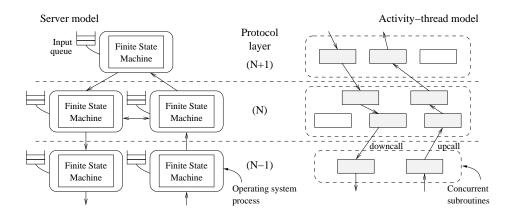

| Implementation models for multi-layer communication systems:                                                                                                                                     | 43                                         |

| Possible software implementation of the server model using a table                                                                                                                               |                                            |

|                                                                                                                                                                                                  | 45                                         |

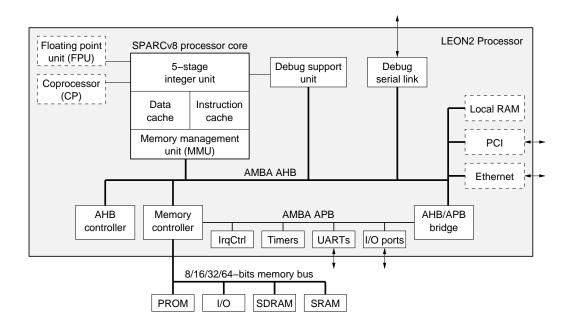

| Architecture of the LEON2 processor as an example of a 32-bit microcontroller (adapted from [Gai05])                                                                                             | 49                                         |

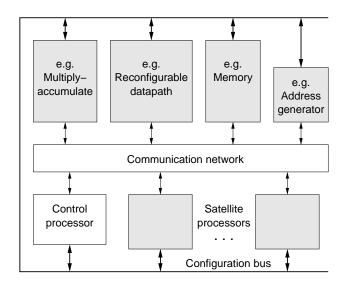

| The Pleiades architecture template (adapted from [AZW <sup>+</sup> 02])                                                                                                                          | 53                                         |

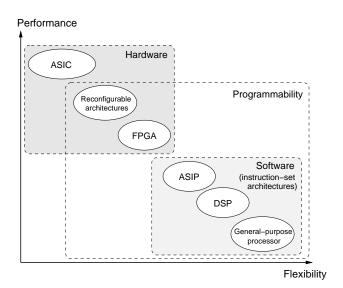

| Comparison of the hardware and software target architecture com-                                                                                                                                 |                                            |

| ponents with respect to flexibility and relative performance                                                                                                                                     | 54                                         |

| Separation of concerns in the platform-based design methodology, adapted from $[KMN^+00]$                                                                                                        | 56                                         |

|                                                                                                                                                                                                  | according to the ITRS roadmap 2005 [ITR05] |

| 2.15 | Example of a system architecture and corresponding architecture graph (left), and the problem graph for a frequency filtering application (right)                                                          | 58 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.16 | Mapping of the functional model (top-left) to an architecture (right) in Metropolis by means of constraints (bottom-left) that link events in the two models to each other                                 | 63 |

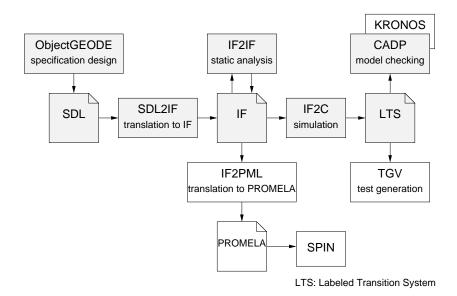

| 3.1  | Tools and languages used for the verification experiment of the MASCARA protocol [JG01]. The shaded boxes mark the used verification flow, alternative tools and languages are also shown                  | 69 |

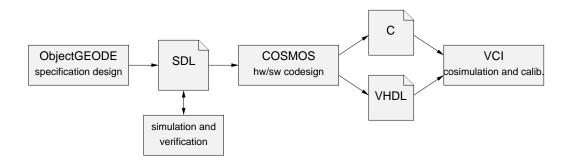

| 3.2  | Hardware/software codesign flow based on the COSMOS tool                                                                                                                                                   | 71 |

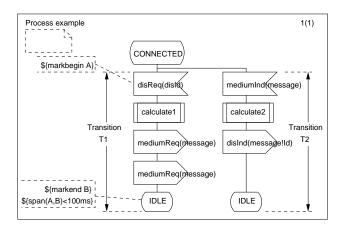

| 3.3  | Modeling of timing constraints with SDL*, taken from [DMTS00].                                                                                                                                             | 72 |

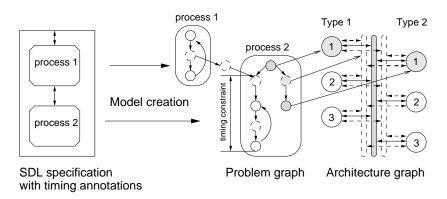

| 3.4  | Generation of the problem graph from the SDL* specification and binding of architectural resources, from [DMTS00]                                                                                          | 73 |

| 3.5  | Codesign flow with CORSAIR [DMTS00]                                                                                                                                                                        | 73 |

| 3.6  | Hardware synthesis process for a rapid prototyping system as described by Muth [Mut02]                                                                                                                     | 77 |

| 3.7  | Hardware architecture generated by the REAR system presented in [Mut02] for the example Specification and Description Language (SDL) partition in Fig. 3.6                                                 | 78 |

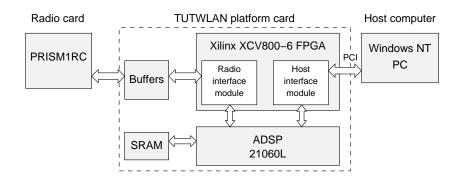

| 3.8  | Target platform for the TUTWLAN system reported in [SHH02]. A MAC protocol hardware accelerator is part of the radio interface module implemented in the FPGA                                              | 83 |

| 3.9  | Hardware accelerator functional blocks for the implementation of the IEEE 802.15.3 MAC protocol reported in [HBB04]                                                                                        | 85 |

| 4.1  | Specification and design phase of our proposed methodology. The SDL model is the starting point for the following transformation steps                                                                     | 90 |

| 4.2  | Software synthesis and integration with a target operating system.                                                                                                                                         | 91 |

| 4.3  | Starting from an initial software partition (target executable), an optimal hardware/software system is obtained in a cyclic process                                                                       |    |

|      | by making use of our cosimulation framework                                                                                                                                                                | 93 |

| 4.4  | The instruction set simulation of the target system including models of the hardware partition is embedded in the overall network                                                                          |    |

|      | simulation based on SDL                                                                                                                                                                                    | 94 |

| 4.5  | Sequence of the final steps in design flow: hardware and interface design, synthesis, integration, and test                                                                                                | 96 |

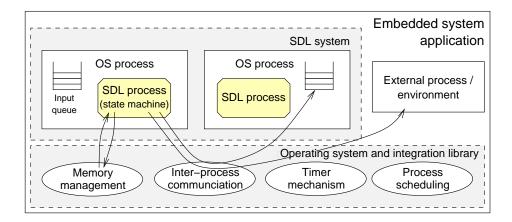

| 4.6  | Software architecture for an embedded system application consisting<br>of an SDL system, external (environment) process, and operating<br>system. The tight integration library provides the links between |    |

|      | SDL model and operating system                                                                                                                                                                             | 98 |

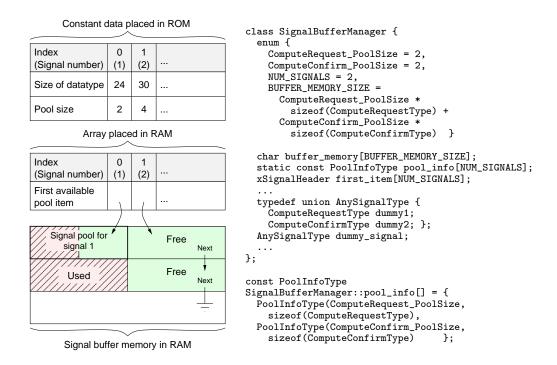

| 4.7         | The realization of statically allocated signal buffer pools by using two arrays with control information and a memory area for the actual buffers is shown schematically on the left. On the right-hand side, a source code example of a SignalBufferManager class for |       |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|             | the SDL system in Fig. 5.2 adopting this implementation scheme is                                                                                                                                                                                                      |       |

|             | presented. xSignalHeader is the base class for all signal buffer types                                                                                                                                                                                                 | s.104 |

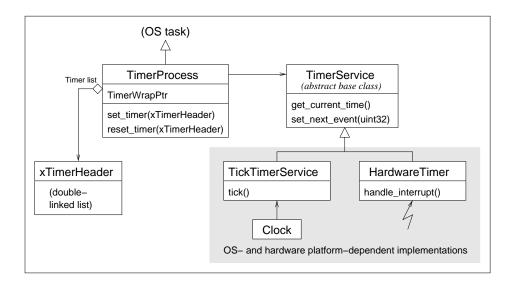

| 4.8         | General software architecture for the timer management showing                                                                                                                                                                                                         |       |

|             | two variants for the detection of timer expiration                                                                                                                                                                                                                     | 106   |

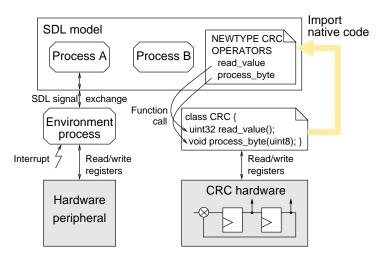

| 4.9         | Principles for interacting with the environment, including hardware,                                                                                                                                                                                                   | 100   |

| 4.10        | from the SDL model                                                                                                                                                                                                                                                     | 108   |

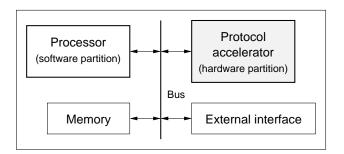

| 4.10        | Principle building blocks of our target architecture for the hard-ware/software codesign process                                                                                                                                                                       | 111   |

| <i>1</i> 11 | The target implementation simulated by the instruction set sim-                                                                                                                                                                                                        | 111   |

| 4.11        | ulator receives inputs from and sends responses back to the SDL                                                                                                                                                                                                        |       |

|             | network simulation. An optional timing rules checker is used to                                                                                                                                                                                                        |       |

|             | flag violations of the protocol's timing specification by the target                                                                                                                                                                                                   |       |

|             | implementation                                                                                                                                                                                                                                                         | 112   |

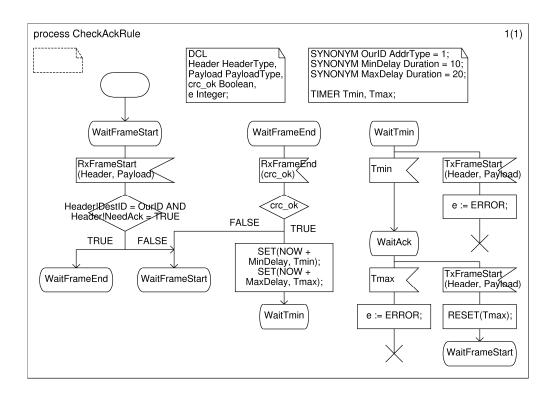

| 4.12        | SDL process that illustrates a timing rule check. An acknowledg-                                                                                                                                                                                                       |       |

|             | ment frame is expected to be sent within an interval of 10 to 20 mi-                                                                                                                                                                                                   |       |

|             | croseconds after the end of a successfully received frame                                                                                                                                                                                                              | 113   |

| 4.13        | Principle of connecting an SDL simulator with an instruction set                                                                                                                                                                                                       |       |

|             | simulator (ISS). A FIFO signal queue is required to store all SDL                                                                                                                                                                                                      |       |

|             | signals sent from the functional model before the simulation time is                                                                                                                                                                                                   |       |

|             | advanced. In the other direction, from ISS to SDL simulation, at most one signal is sent at a time, because the ISS stops immediately                                                                                                                                  |       |

|             | when a signal was sent, and it is consumed by the SDL simulator.                                                                                                                                                                                                       | 115   |

| 4.14        | Principle operation of the interleaving algorithm to synchronize SDL                                                                                                                                                                                                   | 110   |

|             | and instruction set simulations                                                                                                                                                                                                                                        | 119   |

|             |                                                                                                                                                                                                                                                                        |       |

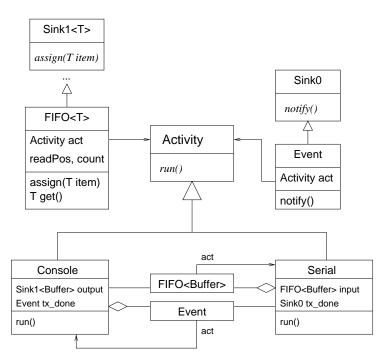

| 5.1         | Hierarchical structure of SDL systems and corresponding output                                                                                                                                                                                                         | 400   |

| - 0         | files from the CAdvanced code generator                                                                                                                                                                                                                                | 123   |

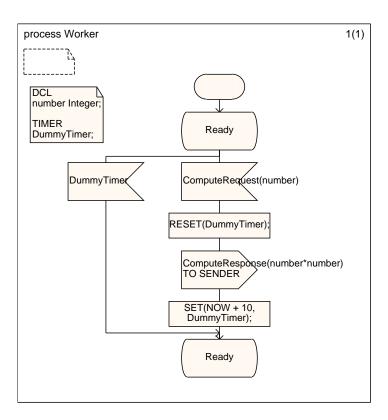

| 5.2         | SDL process state machine with signal input and output as well as                                                                                                                                                                                                      | 105   |

| 5.3         | timer functions                                                                                                                                                                                                                                                        | 125   |

| 5.5         | shown in Fig. 5.2                                                                                                                                                                                                                                                      | 126   |

| 5.4         | Simplified representation of a wireless sensor node application illus-                                                                                                                                                                                                 | 120   |

| 0.1         | trating the event-flow model of Reflex                                                                                                                                                                                                                                 | 128   |

| 5.5         | Class diagram showing the inheritance and interaction relationships                                                                                                                                                                                                    |       |

|             | between activity classes and trigger variables in Reflex                                                                                                                                                                                                               | 129   |

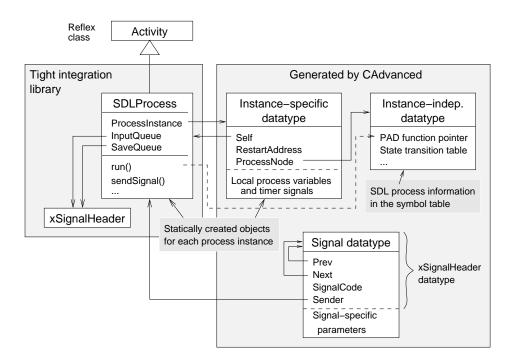

| 5.6         | Diagram depicting the relationship between the process wrapper                                                                                                                                                                                                         |       |

|             | class SDLProcess and the objects created by the code generator                                                                                                                                                                                                         |       |

|             | CAdvanced                                                                                                                                                                                                                                                              | 130   |

| 5.7         | Pseudocode representation of the run() function of the SDLProcess                                                                                                                                                                                                      | 101   |

|             | class                                                                                                                                                                                                                                                                  | 131   |

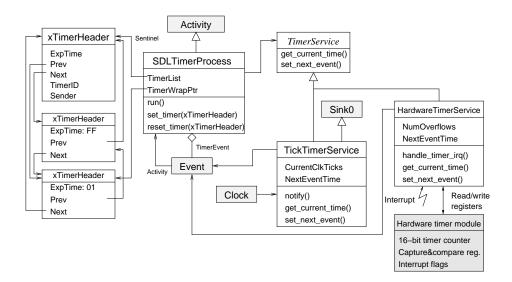

| 5.8  | Implementation of the signal buffer manager functions in $C++$                                                                                                                                                                                            | 134  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

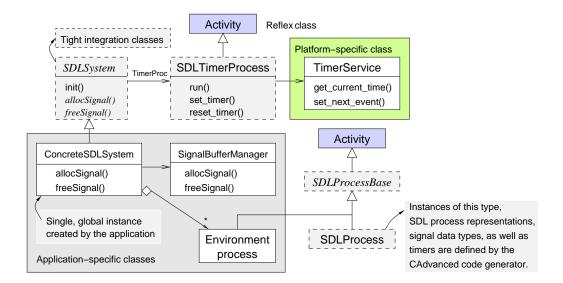

| 5.9  | Software architecture around the SDLTimerProcess class                                                                                                                                                                                                    | 136  |

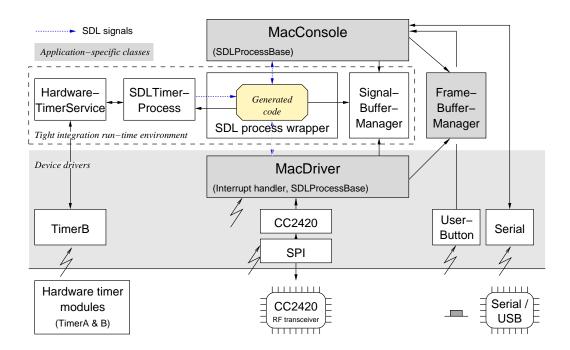

| 5.10 | Classes required to build an application from an SDL model. Application- and platform-specific classes as well as those belonging to the Reflex operating system and to our tight integration library are distinguished                                   | 138  |

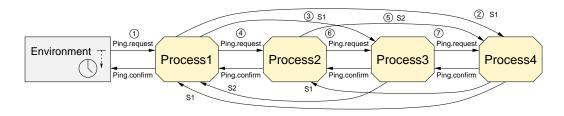

| 5.11 | Simple SDL models composed of 2, 4, or 8 processes used for performance measurements                                                                                                                                                                      | 140  |

| 5.12 | Performance measurements for an SDL model composed of 4 processes with signals S1 and S2 placed in the save queue                                                                                                                                         | 140  |

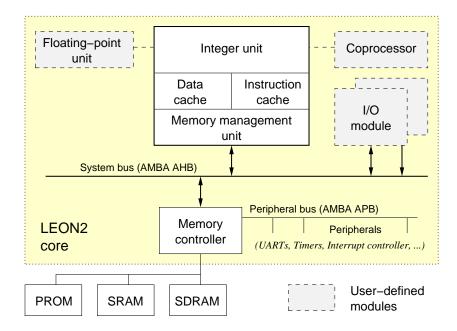

| 6.1  | Architecture of the LEON2 processor. All the depicted components are simulated by TSIM                                                                                                                                                                    | 146  |

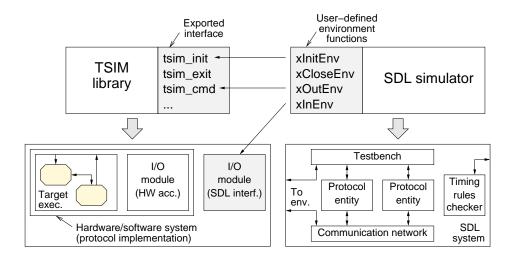

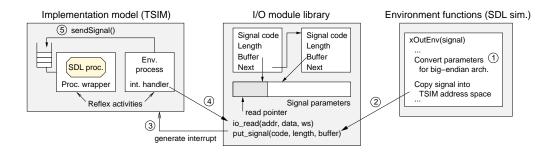

| 6.2  | Applied scheme for coupling the SDL simulator with TSIM. The functions realizing the interface are shaded in gray                                                                                                                                         | 150  |

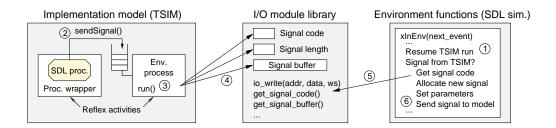

| 6.3  | Chain of actions related to the output of an SDL signal from the implementation model simulated by TSIM to the external SDL system                                                                                                                        | .151 |

| 6.4  | Interactions between the SDL simulator, I/O module, and TSIM related to the exchange of SDL signals from the Telelogic simulator to the implementation model                                                                                              | 152  |

| 6.5  | Pseudocode implementation of the environment functions                                                                                                                                                                                                    | 154  |

| 6.6  | Source code extracts for the I/O module library                                                                                                                                                                                                           | 155  |

| 6.7  | Interactions between the environment functions of the SDL simulator, the TSIM library, and the I/O module. The example shows the exchange of signals in both directions                                                                                   | 156  |

| 6.8  | Screenshot from the SDL simulation of the example in Fig. 6.7                                                                                                                                                                                             | 157  |

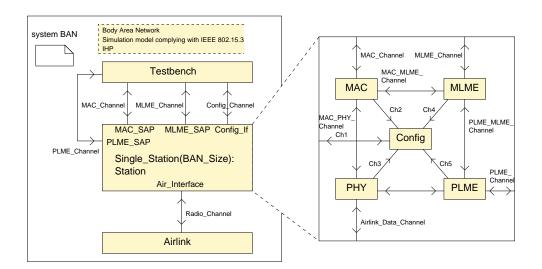

| 7.1  | Structure of our SDL model for the IEEE 802.15.3 standard                                                                                                                                                                                                 | 161  |

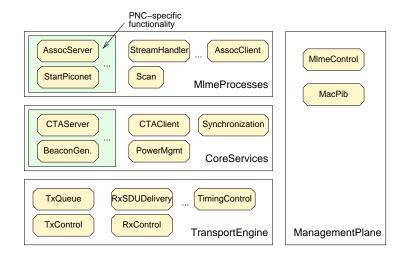

| 7.2  | Functional layering of the processes in the MLME block                                                                                                                                                                                                    | 163  |

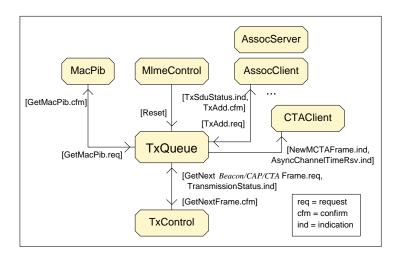

| 7.3  | Process interaction diagram for the TxQueue process                                                                                                                                                                                                       | 166  |

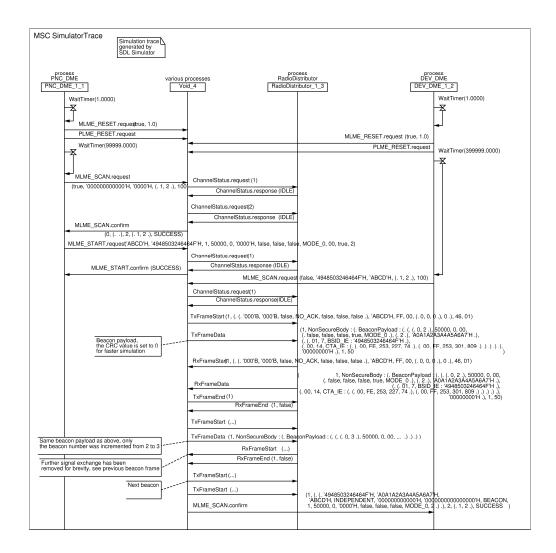

| 7.4  | Message sequence chart showing the signal exchange from the higher layer (device management entity, DME) which initiates the formation of a new piconet.                                                                                                  | 167  |

| 7.5  | Continued message sequence chart from Fig. 7.4 showing synchronization with the PNC and association of a device. The frame exchange over the wireless medium is presented much shortened                                                                  | 168  |

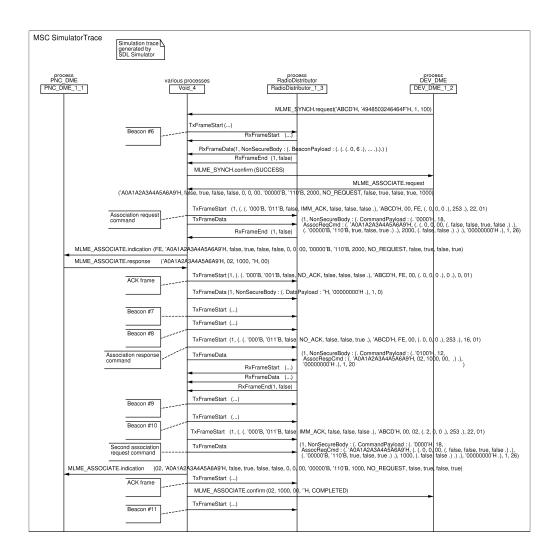

| 7.6  | Experimental setup for the simulation of an IEEE 802.15.3 network consisting of a piconet coordinator (PNC) device and a non-PNC device. The latter is simulated by TSIM in order to obtain performance results for the MAC protocol implementation model | 169  |

|      | mance results for the MAC, protocol implementation model                                                                                                                                                                                                  | Inv  |

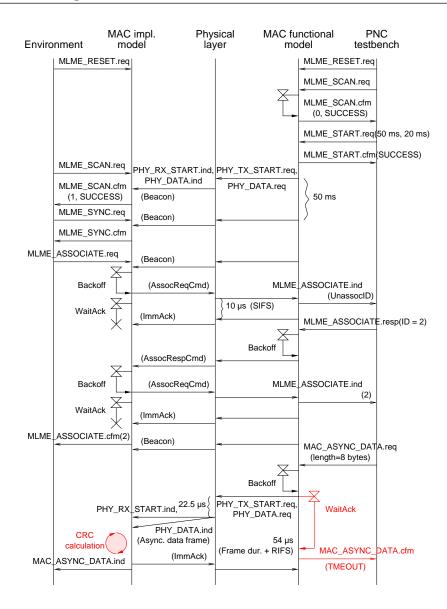

| 7.7        | Message sequence chart showing the service primitives exchanged via the MAC and PHY layer interfaces for the start of a new pi- |       |

|------------|---------------------------------------------------------------------------------------------------------------------------------|-------|

|            | conet, association procedure, as well as asynchronous data exchange                                                             |       |

|            | by the PNC. The data frame exchange fails because of the immediate                                                              |       |

|            | acknowledgment frame being transmitted too late by the implemen-                                                                |       |

|            |                                                                                                                                 | 1 7 1 |

| 7.0        | tation model                                                                                                                    | 171   |

| 7.8        | Hardware design of the 32-bit CRC algorithm consisting of 32 D flip-                                                            |       |

|            | flops and a number of XOR gates according to the generator poly-                                                                | 1 7 4 |

| <b>-</b> 0 | nomial specified by the standard [IEE03a]                                                                                       | 174   |

| 7.9        | Single-chip wireless communication platform consisting of the                                                                   |       |

|            | LEON2 processor, protocol accelerator, and modem. It can be eas-                                                                |       |

|            | ily used for the design of wireless sensor nodes                                                                                | 178   |

| 7.10       | Interface between MAC protocol accelerator and the physical layer.                                                              |       |

|            | TX_Ready is applied when the TX buffer is not full, RX_Start_ind                                                                |       |

|            | when the reception of new frame has started, and RX_Ready when                                                                  |       |

|            | the RX buffer contains data                                                                                                     | 178   |

| 7.11       | Hardware architecture of the protocol accelerator (direct memory                                                                |       |

|            | access data path highlighted by dashed blue lines) [DEK07]                                                                      | 180   |

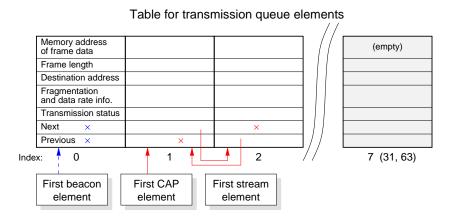

| 7.12       | Structure of the transmission queue table and its elements                                                                      | 181   |

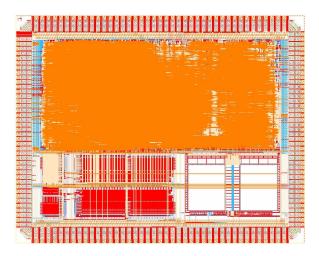

|            | MAC processor chip layout                                                                                                       | 184   |

| 8.1        | Elements of an ideal design flow that supports hardware/software                                                                |       |

|            | system synthesis by an automatic transformation from high-level                                                                 |       |

|            | specifications                                                                                                                  | 186   |

| 8.2        | Software architecture of the S-MAC demonstration application on                                                                 | 100   |

| 0.2        | Reflex. It incorporates automatically generated code from the SDL                                                               |       |

|            | model of the protocol                                                                                                           | 189   |

|            |                                                                                                                                 | 109   |

## Chapter 1

## Introduction

The purpose of this chapter is to set the scene for the presentation of our research work on an efficient protocol design flow for embedded systems and its application for the implementation of the IEEE 802.15.3 medium access control (MAC) protocol.

First, background on embedded systems is provided, characteristics of protocol design as opposed to the design of other applications are presented, and the role of an integrated design flow is highlighted.

Having introduced the main challenges in the design and implementation of protocols for embedded systems, we state our scientific contributions that address these problems. This thesis shall be useful as a guideline for engineers facing these challenges.

Concluding this chapter, an overview on the structure of the thesis is given.

#### 1.1 Scope of the thesis

Digital systems can be classified in general-purpose information processing systems and application-specific systems. Personal computers (PCs) are a good example of general-purpose systems. They are programmable and support a wide range of applications.

Application-specific systems, on the other hand, are designed to fulfill a very specific task, for instance to control the operation of a washing machine. It is typical for such systems to be contained within a larger environment. Therefore, application-specific systems are often referred to as *embedded systems*.

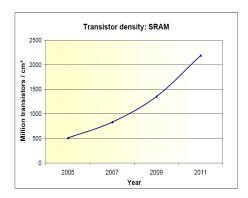

Figure 1.1: Estimated growth of transistor density in SRAM and logic cells according to the ITRS roadmap 2005 [ITR05]

In the past decades, embedded systems have replaced many non-computing systems, such as car window openers, and are now ubiquitous. Their wide adoption has become economically feasible by the mass production of digital hardware components. Since embedded systems are often part of another product that may be sold by the millions, they must be very cheap. The price of an integrated circuit is determined by its die size; the less area a chip consumes the cheaper it is. So, for economic reasons, embedded systems have only a fraction of the computing and memory resources available that a modern PC has built in.

Another aspect that is important for many embedded system applications is the need for *low power consumption*. Since a high clock frequency and a large chip size lead to increased dynamic and static power dissipation, embedded system designers must design systems that perform the required task using the lowest clock frequency and smallest chip size possible.

Moore's Law, which states the observation that the number of transistors on integrated circuits doubles roughly every 18 months, still holds true today and is reflected by the current ITRS roadmap [ITR05] that predicts the future development of semiconductor technology. Consequently, more transistors can be integrated on the same area (cf. Fig. 1.1) for roughly the same price. This leads to a growing complexity of future embedded computing systems.

A further trend that can be observed and is predicted for the future is that more and more electronic devices will be *networked*. The Wireless World Research Forum (WWRF) assumes that by the year 2017 there will be one thousand wireless devices at service for each individual. Already now, new applications making use

of wireless personal area networks (WPAN) and wireless sensor networks (WSN) are emerging. Application areas include, but are not limited to, home automation and security, personal health care, logistics, traffic control, process and factory automation, agriculture.

Communication protocols define rules for the interconnection of communication endpoints [Kön03]. Protocols are therefore the basis for the realization of computer networks, in general, and for wireless sensor networks, in particular. They can be *implemented* in hardware, in software, or as a mix between the two. The implementation method influences the efficiency and other parameters, such as the flexibility to introduce later protocol extensions or bug fixes. However, protocols are designed on an abstract level without having any specific implementation method in mind.

What makes protocol design for embedded systems special in contrast to application development in general? Even though one may find applications that exhibit similar features as protocols, there are a number of reasons to treat protocol design as a special case. Protocol behavior is often controlled by the expiration of *timers*, for instance to set a limit on the time to wait for a response from a communication partner. In the next section, we will address the issue of real-time requirements specifically.

Furthermore, there are *complex interactions* between one or more protocol instances at communication partners that can be interleaved with each other. This complexity, paired with the time dependency, causes a vast number of possible protocol states and protocol runs. In any case, it must be guaranteed that the protocol instance does not end up in a deadlock and that from each state that has been reached any other state can be reached again, i.e. that there are no livelocks. The required robustness and correctness, especially within the context of embedded systems that must operate reliably for months or years without maintenance, makes a tailored design approach, that is methods and tools, necessary.

#### 1.2 Problem statement

Challenges in current embedded systems design methodologies According to the HiPEAC roadmap on embedded systems [V<sup>+</sup>06], the increased system complexity makes new tools for verification and testing necessary. Up to the year 2009, an aggregated annual growth rate for design and test automation tools of

nearly 20% is predicted. The current de facto situation in the semiconductor industry is that the validation of embedded systems and complex SoCs may consume up to 80% of the total design cost and time [MED03]. This can potentially prevent the embedded system product under development from being successful on the market. Hence, a main challenge in the electronic design automation (EDA) field is to provide new methods that can enable the rapid validation of embedded systems leading to low-cost devices  $[V^+06]$ . The aforementioned vision of the WWRF can only be reached with appropriate tool support.

System-level design languages have the potential of shortening product development cycles by providing validation and system simulation at an early design phase, as reported in  $[V^+06]$ . For this reason, an increase of projects that rely on system-level design languages has been predicted. Similarly, a recent study [Cel05] by Celoxica on system design trends has revealed that there is currently a transition from paper-based system specifications to electronic specification languages such as UML, Matlab or C taking place in the industry. Model-based design and the use of hardware/software partitioning tools are not yet common, though they promise to speed up the development process and reduce the number of design errors.

Not only models and architectures are important for developing new implementations within a short time, but also a tailored design flow and corresponding tools that support various steps of the design flow. As outlined in the previous section, reliability and energy efficiency must be addressed in the design of embedded systems.

SDL-based protocol design flow for embedded systems Specification and Description Language (SDL) is a popular high-level language to formally specify system behavior. In particular, it has been successfully applied to protocol engineering and has attracted a lot of attention from the research community of this field. SDL not only allows the simulation of models, but also their formal verification. The purpose of verification is to identify and eliminate incorrect behavior, such as deadlocks or livelocks, that may occur under a particular sequence of events.

In the past, a number of tools [IAJ94], [ÖBE<sup>+</sup>97], [DMTS00] have been proposed that support an integrated design flow from high-level SDL specifications to system implementations. It is possible to automatically transform SDL spec-

ifications into executable software and even generate hardware designs from the specification by special-purpose compilers. These approaches will be discussed in Chapter 3 in more detail.

In this work, the author has focused on adapting and extending the protocol engineering design flow based on SDL to the requirements of deeply embedded systems. The motivation for choosing SDL was its suitability to formal verification as well as mature tool support for simulation and implementation.

The existing approaches, however, are not targeted specifically to embedded systems and the tight processing and memory requirements of, for instance, 16-bit microcontrollers with less than 64 kbytes of memory. Rather, the previous work has focused on high-performance communication processors or rapid prototyping systems.

The adaptation of the SDL-based design methodology for communication protocols to the requirements of embedded systems demands for solutions to the research problems listed below.

- General concepts for an efficient use of real-time operating systems and embedded systems hardware platforms as *run-time environments* for SDL models have to be investigated.

- Mechanisms for connecting an *instruction set simulator* with an SDL simulator have to be studied.

These items will be motivated and further explained in the remainder of this section by discussing the limitations of the current approaches. The feasibility of the new concepts has to be shown experimentally. This is achieved by

- a prototypical implementation of an SDL run-time environment for a target operating system, its validation and performance comparison with existing approaches, and

- a proof of concept for the cosimulation framework by realizing an interface between a particular instruction set simulator and Telelogic's SDL simulator.

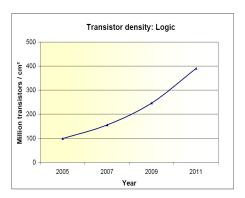

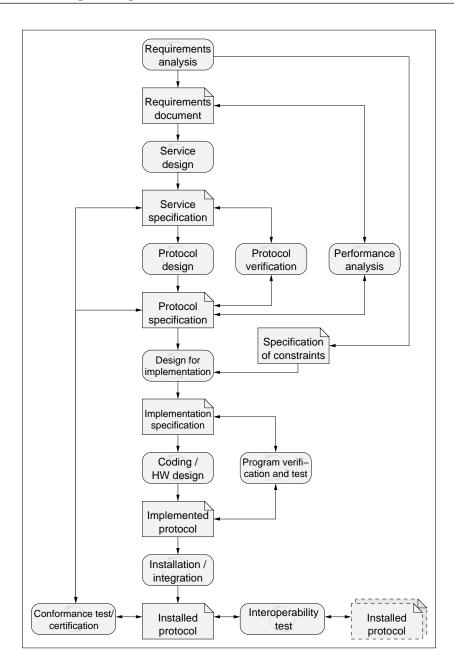

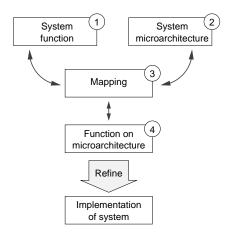

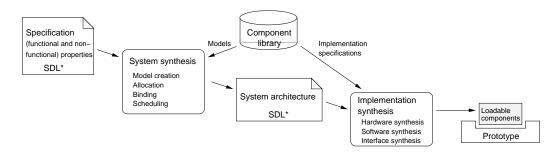

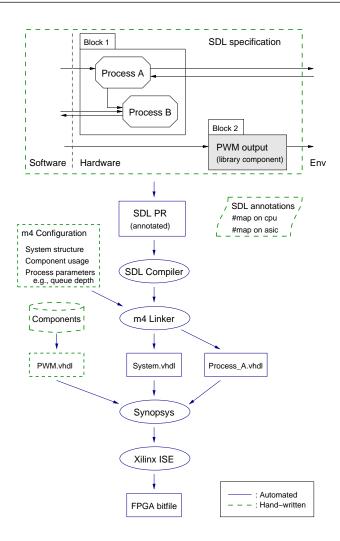

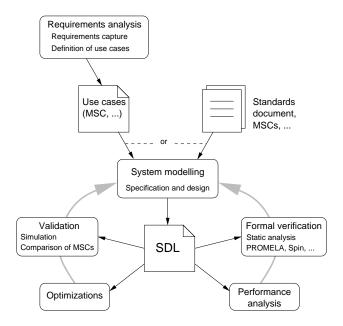

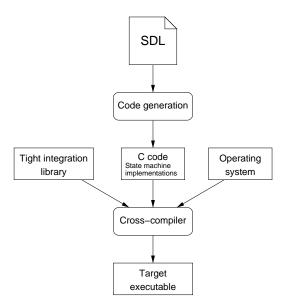

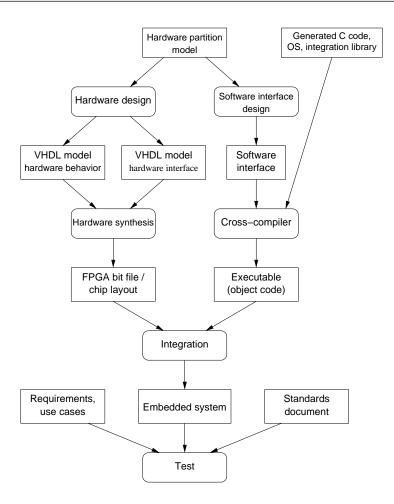

Figure 1.2 shows the integrated SDL-based design flow. The novel elements that have to be introduced to target resource-limited embedded systems are highlighted. They comprise an optimized run-time environment for embedded systems (denoted as tight integration library in the figure) and a cosimulation framework.

Figure 1.2: Overview of the complete design flow starting from an initial SDL model to a hardware/software implementation.

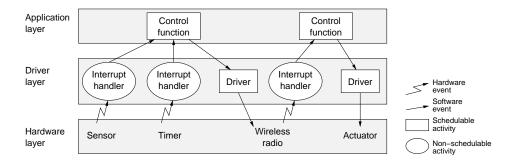

For resource-constrained embedded systems, designers typically choose operating systems with a very small memory footprint and, consequently, a very limited set of features and available services. TinyOS [LMP+05], Contiki [DGV04], or Reflex [WN07] are examples of the most commonly used operating systems for wireless sensor nodes, a particular kind of deeply embedded system. One of the challenges in targeting SDL specifications to such operating systems is to map SDL concepts to the available mechanisms of the operating system. Furthermore, the features of the hardware platform, such as programmable timers, must be exploited as efficiently as possible.

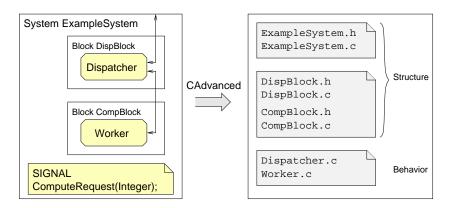

So far, no general framework for targeting SDL models to operating systems

for deeply embedded systems has been presented. Our objective was to close this gap by investigating concepts for a mapping that has a small memory footprint and little run-time overhead. We base our work upon the output of the very successful commercial code generator CAdvanced from Telelogic, as the generated code facilitates the integration with a target operating system.

With our conceptual ideas and their realization as a software framework for lightweight SDL run-time environments, it should be easily possible to create integration models for different real-time operating systems and hardware platforms. The performance of system implementations that are developed on the basis of our concepts will be significantly better than with the standard approach which uses a generic SDL run-time environment.

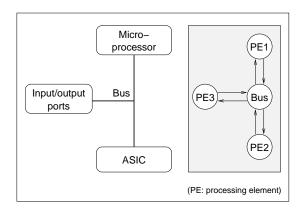

Embedded systems may consist of general-purpose microcontrollers and dedicated hardware blocks. Since the dedicated hardware is designed for a specific purpose, its performance is typically several magnitudes higher than that of microcontrollers if hardware parallelism can be exploited and required operations are not directly supported by the instruction set of the processor. Hence, a mixed hardware/software implementation may provide the best tradeoff between the required flexibility, which can be ensured by the use of software, and performance. By using dedicated hardware for time-critical and processing-intensive tasks, the general-purpose processor has less strict performance requirements and its clock frequency could be reduced. This way, the energy efficiency of the system is increased. This is particularly important for battery-powered devices.

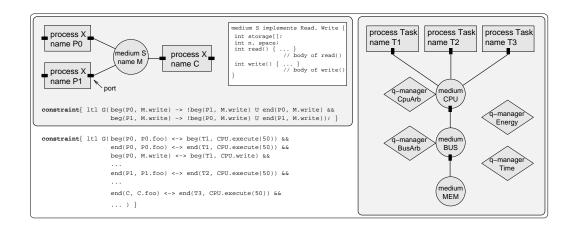

Hardware/software codesign tools support the designer in finding optimal system partitionings with respect to user-defined constraints such as real-time behavior, power consumption or resource usage. Some tools allow the automatic generation of hardware from high-level specifications. Such a tool, which uses annotated SDL as system specification language, was proposed by Muth [Mut02] for rapid prototyping applications. The designer has to specify which SDL processes shall be generated as hardware based on their computational complexity and timing requirements. A worst-case real-time analysis is conducted by the tool and checked against the requirements. This way, the designer can be sure that a chosen partitioning satisfies the timing specification. We consider this work as the most advanced integrated design flow based on SDL.

The granularity of mapping complete SDL processes to either hardware or software is rather coarse in this approach. It causes significant overhead in terms of hardware area and signal exchange delay, because of required buffer space for hardware signal queues and the time needed to transfer signal parameters into the buffers. For this reason, we discard the automatic generation of hardware from SDL specifications from our design flow. Instead, we prefer a fine-grained partitioning of SDL processes into hardware and software. The manual design of dedicated hardware and its interfaces to the software partition promises to yield more efficient systems, however increases the design effort.

During design space exploration, i.e. the process where the designer investigates different system architectures and hardware/software partitionings, usually a profiling of the system is performed. The objective of the profiling is to obtain information about the execution time and bottlenecks of the current design alternative. The profiling information can be gathered either by using a real execution of the system, which may require significant design effort to create such a system, or by simulations. Simulations can be conducted with more or less accuracy depending on the chosen system model. Naturally, the closer the profiling results reflect the reality, the better decisions can be made in the design exploration phase.

Our work particularly addresses the design flow for communication protocols. In this case, the designer must analyze whether a given hardware/software implementation model of the protocol interacts with its environment, i.e. the upper and lower protocol layers, according to the timing specification, and analyze what parts of the implementation model are bottlenecks. This can be concluded from a static worst-case execution analysis or, as stated above, by simulating and profiling the design. A worst-case analysis might yield too pessimistic results and, hence, lead to an implementation which is overdesigned. While such an approach is necessary for hard real-time systems, it is likely to require more resources and computing power for the average case.

A short note on real-time behavior with respect to wireless communication protocols: A computer system that must react on external stimuli and produce a result within a certain time is called a *real-time system*. If missing a deadline could possibly cause catastrophic consequences, this computer system is said to have *hard* (or safety-critical) real-time requirements. Otherwise, it is called a *soft* real-time system.

In wireless communications, loss of messages over the wireless channel is quite common due to the presence of noise and interference. Therefore, other devices will not see a difference between missing a deadline in one protocol instance or a transmission error. Protocols are designed to tolerate and recover from transmission errors. Even if a message is occasionally sent late and interferes with another message, this will only lower the performance, but not break the system. If an application with hard real-time constraints shall relies on a wireless communication system, the application designer must account for the occasional loss of messages and provide a fail-save operation. Hence, the application and the protocol implementation could just as well be in two different domains, where the protocol implementation has less strict requirements with respect to timing.

Therefore, the design flow presented in this thesis targets soft real-time embedded systems only. Still, the designer shall be supported in identifying where the implementation fails to meet the specified timing constraints and what are the bottlenecks. This is an important requirement for the hardware/software partitioning process.

Obtaining profiling information from system simulations is a viable and better suited approach than a static worst-case analysis, in the area of communication protocol design, as long as there are no hard real-time requirements. The performance of implementation models can be estimated by different methods.

One possibility is to annotate transitions in SDL processes with a user-defined duration. Additionally, fixed process scheduling and signal exchange overhead can be included. The performance of the SDL system is then measured by simulating the model and advancing the simulation time according to the timing annotations. Since these annotations are only more or less accurate estimations, the performance results obtained from the simulations may not correspond well to the real execution times.

An improvement would be to use the real execution time of the SDL model on the host computer as a basis and scale the simulation results to the computational performance of the target embedded system microcontroller. Again, the confidence in the accuracy of the performance measurements is low due to the different instruction set architectures, effects caused by caches, etc. In particular when simulating systems with external components that trigger interrupts, accuracy can be low.

The most accurate profiling results can be obtained by simulating the execution of a hardware/software system on the target processor. A tool that allows such kind of performance measurements is an instruction set simulator. They are freely or commercially available for many microcontrollers. Though the simulation runs

require more time than the previously described methods, the profiling results are very accurate, especially for cycle-true simulations.

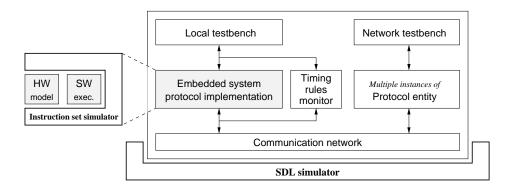

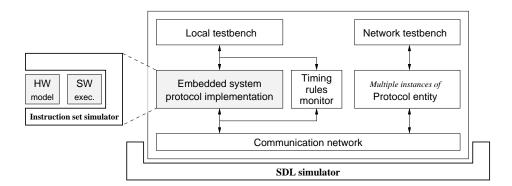

When simulating a particular communication protocol implementation, there must be a *test bench* that creates stimuli for the system under test. The test bench reflects the behavior of the peer communication entities as well as the lower and upper protocol layers.

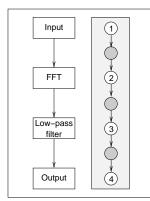

The development of a comprehensive test bench for a communication protocol implementation is a time-consuming task. This development time can be saved by reusing the SDL model of the communication system. In order to validate the protocol functionality before starting the implementation phase, designers typically create a simulation environment that can instantiate and interconnect several protocol entities in a network model. This can be easily done in SDL by introducing models for the lower protocol layers and a physical network. Stimuli for a simulation of the protocol implementation model can be directly obtained from the simulation of the network model by using the SDL signals exchanged with a particular protocol instance.

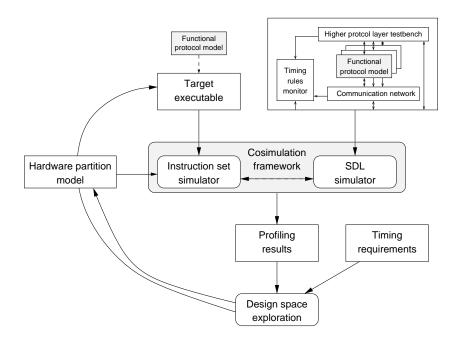

Ideally, these signals could be used as an input for the protocol implementation model simulated by an instruction set simulator (ISS). The signals generated as output by the implementation model could be directly introduced back into the SDL simulation of the communication network. This way, an interactive *cosimulation* run can be performed. As a result, profiling results for the implementation model are gathered, and it can be checked whether the model satisfies all timing requirements of the protocol.

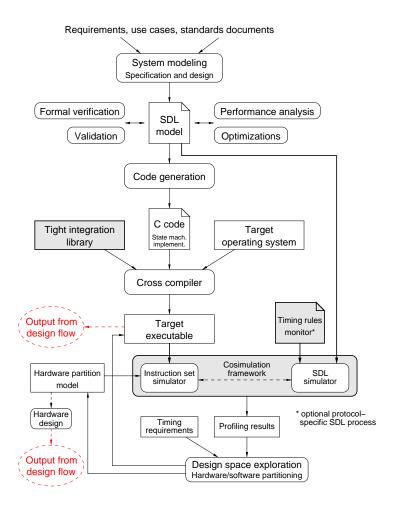

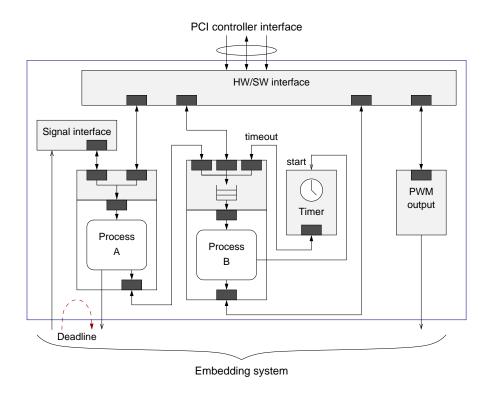

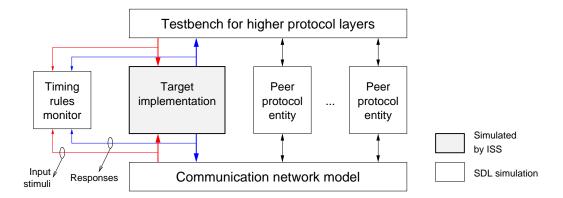

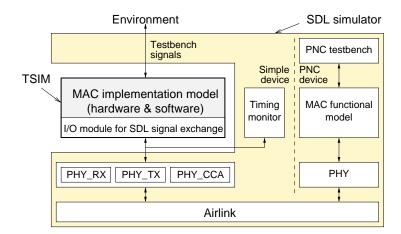

The concept of integrating an instruction set simulation of a protocol implementation into the functional network simulation in SDL is shown schematically in Fig. 1.3

To support the designer in detecting all cases where the implementation model did not respond to a received stimulus in time, i.e. missed a real-time requirement, the author has created the concept of a *timing rules monitor*. This is an SDL process that receives all SDL signals that are sent as stimuli to the implementation model and all of its responses, which are also SDL signals. The designer may specify a set of rules describing the acceptable behavior of the implementation model. The reason for the introduction of the timing rules monitor is the weak semantics of SDL with respect to specifying real-time requirements as will be outlined in more detail later in this thesis. The only way to observe a deviation from the acceptable

Figure 1.3: The instruction set simulation of the target system including models of the hardware partition is embedded in the overall network simulation based on SDL.

timing behavior without the timing rules monitor would be to notice differences in the protocol runs. Such differences, however, are difficult to spot, especially when long test benches are used and, possibly, communication failures leading to timeouts are part of the normal behavior in the simulated protocol run.

To our knowledge, the cosimulation of SDL specification models and implementation models in an ISS has not been treated before. Therefore, mechanisms for an efficient coupling, which also preserve the semantics of SDL, have to be investigated. Furthermore, based on the general considerations, a prototypical implementation is needed to prove the validity of the concept and to serve as a tool in the design flow.

Validation of our work The SDL-based protocol design flow has been validated by applying it to an implementation of the IEEE 802.15.3 medium access control protocol [IEE03a]. This implementation is part of a generic wireless communication platform, which has an IEEE 802.15.3-compliant physical layer offering data rates between 11 and 55 Mbit/s. The MAC protocol can be considered as very complex. Among other features, it provides an asynchronous and isochronous data service.

From a practical point of view, we had to answer the question if and how it would be possible to implement such a complex MAC protocol for a batterypowered sensor node. In tackling this problem we had the freedom to develop protocol software as well as to design dedicated hardware as a protocol accelerator. As will be reported later in Chapter 7, our concepts for an embedded systems design methodology and the tools implementing these concepts supported the hardware/software design process and led to an efficient system-on-chip implementation of the above mentioned MAC protocol. This example shows that the methodology can also be successfully applied to other protocols that are typically used within the area of wireless sensor networking or embedded systems. They will likely have lower complexity and data rates compared to IEEE 802.15.3. Examples of such protocols are S-MAC [YHE02], T-MAC [vDL03], IEEE 802.15.4 [IEE03b] or Bluetooth [IEE05].

#### 1.3 Contributions

The author has addressed the design challenges presented in the previous section by

- creating an integrated design flow that is based on SDL,

- studying concepts for an efficient tight integration layer, i.e. an SDL run-time environment, for the CAdvanced code generator from Telelogic,

- investigating general problems of connecting an instruction set simulator with an SDL simulation,

- implementing the theoretical concepts for an efficient run-time environment and using the real-time operating system for extremely resource-constrained devices Reflex [Nol09] as an example,

- implementing a cosimulation framework that couples the Telelogic SDL simulator with the LEON2 instruction set simulator TSIM, and

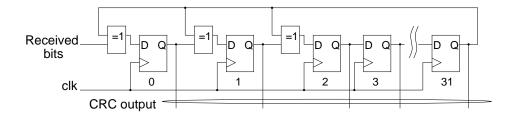

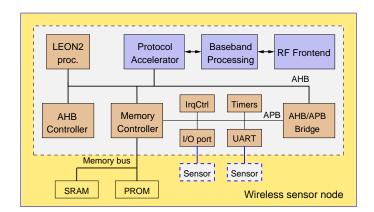

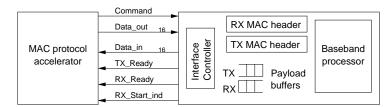

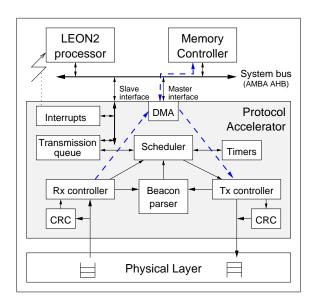

- successfully applying the methodology and newly developed tools to the design and implementation of the IEEE 802.15.3 MAC protocol.