## IMPLEMENTATION OF SYNCHRONIZED CHAOTIC SYSTEMS BY FIELD PROGRAMMABLE GATE ARRAY

A Thesis Submitted to the Graduate School of Engineering and Sciences of İzmir Institute of Technology in Partial Fulfillment of the Requirements for the Degree of

**MASTER OF SCIENCE**

in Electrical and Electronics Engineering

by Can EROĞLU

October 2007 İZMİR We approve the thesis of Can EROĞLU

**Prof. Dr. F. Acar SAVACI** Supervisor

Assoc. Prof. Dr. Uğur ÇAM Committee Member

Assist. Prof. Dr. Orhan COŞKUN Committee Member

> 17 October 2007 Date

**Prof. Dr. F. Acar SAVACI** Head of the Department of Electrical and Electronics Engineering **Prof. Dr. Hasan BÖKE** Dean of the Graduate School of Engineering and Science

## ACKNOWLEDGEMENTS

I would like to express my sincere gratitude to my advisor Prof. Dr. F. Acar Savacı for his valuable guidance and support. I am very proud that i had the chance to work with him.

I would like to thank to the members of my Thesis Committee Assoc. Prof. Dr. Uğur Çam and Asst. Prof. Dr. Orhan Coşkun for their useful comments. I also would like to thank to Dr. Tolga Yalçın for his unfailing support.

Finally, I am deeply thankful to my parents Dudu and Zafer, and my sister Irmak for their support and endless love through my life.

## ABSTRACT

## IMPLEMENTATION OF SYNCHRONIZED CHAOTIC SYSTEMS BY FIELD PROGRAMMABLE GATE ARRAY

In this thesis, the geometric properties of chaotic systems are used to determine their synchronization. First, each system is constructed with MATLAB Simulink blocks. Afterwards, feedback control system for synchronization of chaotic systems is proposed by using complete synchronization approach. In the next stage, Simulink designs are translated into System Generator design so that *bitstream* file which is used to program FPGA is obtained. Finally, the design is implemented into FPGA by dowloading *bitstream* file into FPGA. As an application of FPGAs the synchronization of chaotic systems have been achieved.

## ÖZET

## SENKRONİZE EDİLMİŞ KAOTİK SİSTEMLERİN ALAN PROGRAMLANABİLİR KAPI DİZİLERİ UYGULAMALARI

Bu tezde, kaotik sistemlerin senkronizasyonunu sağlamak amacıyla bu sistemlerin geometrik özellikleri kullanılmıştır.İlk olarak, her sistem MATLAB Simulink blokları kullanılarak oluşturulmuştur. Daha sonra, tam senkronizasyon yaklaşımı kullanılarak, kaotik sistemlerin senkronizasyonunu sağlamak amacıyla geri beslemeli kontrol sistemi önerilmiştir. Bir sonraki aşamada, yapmış olduğumuz Simulink tasarımları, FPGA' i programlamada kullanacağımız *bitstream* dosyasını elde etmek için, System Generator tasarımına çevirilmiştir. Son olarak, tasarım, *bitstream* dosyasının FPGA' e yüklenmesi ile FPGA uygulaması tamamlanmıştır. FPGA uygulaması olarak kaotik sistemlerin senkronizasyonu başarı ile gerçekleştirilmiştir.

## TABLE OF CONTENTS

| LIST OF TABLES                                           | viii |

|----------------------------------------------------------|------|

| LIST OF FIGURES                                          | ix   |

| CHAPTER 1. INTRODUCTION                                  | 1    |

| CHAPTER 2. THE ORIGIN OF FIELD PROGRAMMABLE GATE ARRAY . | 3    |

| 2.1. Basic Process Technology Types                      | 3    |

| 2.1.1. A Simple Programmable Function                    | 3    |

| 2.1.2. Fusible Link Technologies                         | 4    |

| 2.1.3. Antifuse Technologies                             | 5    |

| 2.1.4. Mask-Programmed Devices                           | 7    |

| 2.1.5. Programmable Read-Only Memories                   | 8    |

| 2.1.6. EPROM Technologies                                | 9    |

| 2.1.7. EEPROM Technologies                               | 10   |

| 2.1.8. Static Random-Access Memory Based Technologies    | 11   |

| 2.2. Programmable Devices and FPGAs                      | 12   |

| 2.2.1. SPLDs and CPLDs                                   | 13   |

| 2.2.1.1. PROMs                                           | 13   |

| 2.2.1.2. Programmable Logic Arrays                       | 15   |

| 2.2.1.3. PALs and GALs                                   | 17   |

| 2.2.2. Complex Programmable Logic Devices                | 18   |

| 2.2.3. Application-Specific Integtrated Circuits         | 19   |

| 2.2.3.1. Full Custom                                     | 19   |

| 2.2.3.2. Gate Arrays                                     | 19   |

| 2.2.3.3. Standart Cell Devices                           | 21   |

| 2.2.3.4. Structured ASICs                                | 21   |

| 2.2.4. Field Programmable Gate Arrays                    | 23   |

| CHAPTER 3 . CHAOTIC GENERATORS                           | 27   |

| 3.1. Chaotic Systems                                     | 27   |

| 3.1.1. Lorenz System                                           | 27  |

|----------------------------------------------------------------|-----|

| 3.1.2. Rössler System                                          | 29  |

| 3.1.3. Linz and Sprott System                                  | 32  |

| 3.1.4. Chua System                                             | 35  |

| CHAPTER 4. SYNCHRONIZATION OF CHAOTIC SYSTEMS                  | 41  |

| 4.1. Chaos Synchronization                                     | 41  |

| 4.2. Synchronizability from Control of Chaotic Systems         | 42  |

| 4.2.1. Local Controllability for Complete Synchronizability    | 43  |

| 4.2.2. Local Observability for Complete Synchronizability      | 44  |

| 4.3. Complete Synchronizability                                | 45  |

| 4.4. Synchronization of Lorenz System                          | 46  |

| 4.5. Synchronization of Rössler System                         | 57  |

| 4.6. Synchronization of Linz and Sprott System                 | 65  |

| 4.7. Synchronization of Chua System                            | 72  |

| CHAPTER 5. FPGA IMPLEMENTATION                                 | 80  |

| 5.1. Implementation Process                                    | 80  |

| 5.1.1. Implementation of Synchronized Lorenz System            | 84  |

| 5.1.2. Implementation of Synchronized Rössler System           | 92  |

| 5.1.3. Implementation of Synchronized Linz and Sprott System . | 100 |

| 5.1.4. Implementation of Synchronized Chua System              | 107 |

| CHAPTER 6. CONCLUSION                                          | 116 |

| REFERENCES                                                     | 119 |

## LIST OF TABLES

| <u>Table</u> |                                                        | Page |

|--------------|--------------------------------------------------------|------|

| Table 3.1.   | Parameters used to plot the Chua's attractors          | 38   |

| Table 5.1.   | MATLAB function "module.m"                             | 81   |

| Table 5.2.   | The source used by synchronized Lorenz system          | 88   |

| Table 5.3.   | The source used by synchronized Rössler system         | 95   |

| Table 5.4.   | The source used by synchronized Linz and Sprott system | 105  |

| Table 5.5.   | The source used by synchronized Chua system            | 111  |

## LIST OF FIGURES

## Figure

### Page

| Figure 2.1.  | A simple programmable function                | 4  |

|--------------|-----------------------------------------------|----|

| Figure 2.2.  | The device with unprogrammed fusible links.   | 4  |

| Figure 2.3.  | Programmed fusible links.                     | 5  |

| Figure 2.4.  | Unprogrammed antifuse links.                  | 6  |

| Figure 2.5.  | Programmed antifuse links.                    | 6  |

| Figure 2.6.  | Growing an antifuse                           | 7  |

| Figure 2.7.  | A transistor-based mask programmed ROM cell   | 8  |

| Figure 2.8.  | A transistor-and-fusible-link-based PROM cell | 8  |

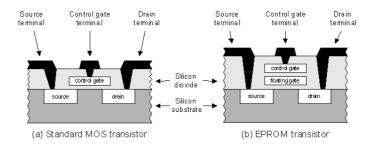

| Figure 2.9.  | Standart MOS versus EPROM transistors         | 9  |

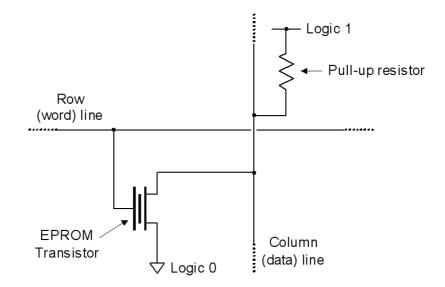

| Figure 2.10. | An EPROM transistor-based memory cell.        | 10 |

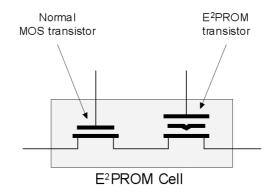

| Figure 2.11. | An EEPROM - cell                              | 10 |

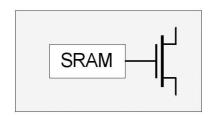

| Figure 2.12. | An SRAM-based programmable cell               | 11 |

| Figure 2.13. | Summary of programming technologies.          | 12 |

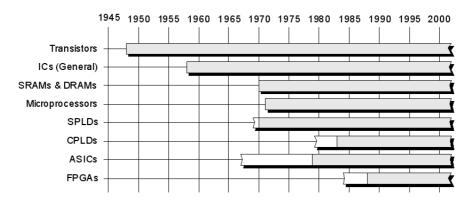

| Figure 2.14. | Technology timeline.                          | 12 |

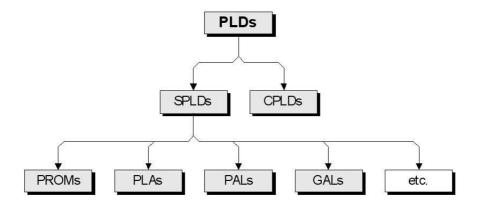

| Figure 2.15. | Classes of PLDs                               | 13 |

| Figure 2.16. | Unprogrammed PROMs.                           | 14 |

| Figure 2.17. | A small block of combinational logic.         | 14 |

| Figure 2.18. | Programmed PROM.                              | 15 |

| Figure 2.19. | Unprogrammed PLA.                             | 16 |

| Figure 2.20. | Programmed PLA.                               | 16 |

| Figure 2.21. | Unprogrammed PAL.                             | 17 |

| Figure 2.22. | A generic CPLD structure.                     | 18 |

| Figure 2.23. | Different types of ASIC.                      | 19 |

| Figure 2.24. | Examples of simple gate array basic cells.    | 20 |

| Figure 2.25. | Channeled gate array architectures.           | 20 |

| Figure 2.26. | Example of structured ASIC tiles.             | 22 |

| Figure 2.27. | Generic structured ASIC.                      | 22 |

| Figure 2.28. | The gap between PLD and ASICs.                | 23 |

| Figure 2.29. | A simplified view of a LC.                                                     | 24 |

|--------------|--------------------------------------------------------------------------------|----|

| Figure 2.30. | Configuring a LUT.                                                             | 24 |

| Figure 2.31. | A <i>slice</i> containing two LCs                                              | 25 |

| Figure 2.32. | A CLB containing four <i>slices</i>                                            | 25 |

| Figure 2.33. | Top-down view of simple FPGA architecture.                                     | 26 |

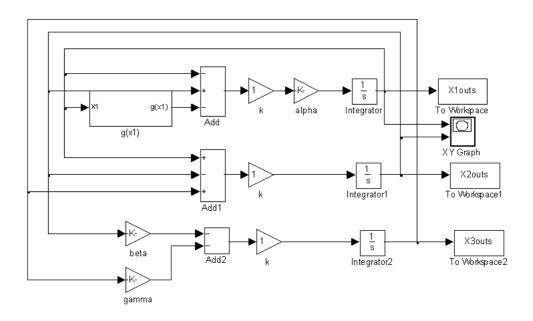

| Figure 3.1.  | Simulink structure of Lorenz's equations                                       | 28 |

| Figure 3.2.  | X1outs, X2outs and X3outs outputs of Lorenz's equations                        | 28 |

| Figure 3.3.  | The attractor of Lorenz's Simulink block diagram.                              | 29 |

| Figure 3.4.  | Simulink structure of Rössler equations.                                       | 30 |

| Figure 3.5.  | Four different Rössler's attractors.                                           | 30 |

| Figure 3.6.  | X1outs, X2outs and X3outs outputs of Rössler equations                         | 31 |

| Figure 3.7.  | Three dimensional Rössler's attractor for $\gamma = 5.7 \dots \dots \dots$     | 31 |

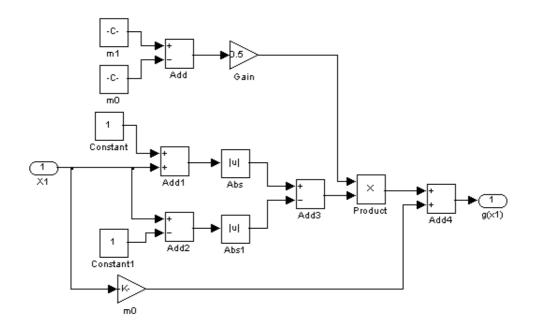

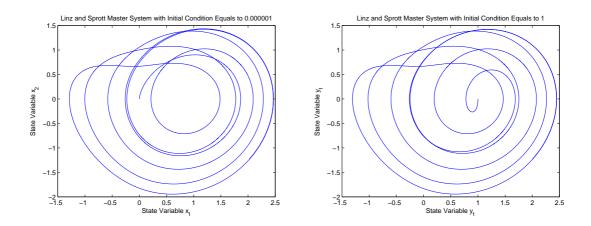

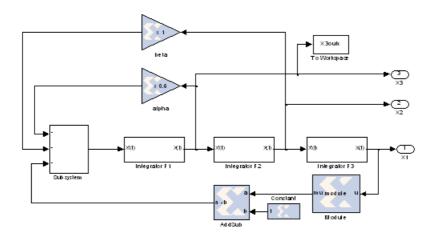

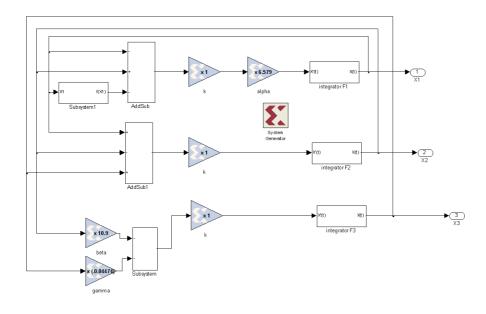

| Figure 3.8.  | Simulink structure of Linz and Sprott equations.                               | 33 |

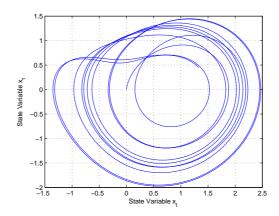

| Figure 3.9.  | The attractor of the Linz and Sprott's Simulink block.                         | 33 |

| Figure 3.10. | Xlouts, X2outs and X3outs outputs of Linz and Sprott Equation                  | 34 |

| Figure 3.11. | Three dimensional Linz and Sprott's attractor for $\alpha = 0.6$               | 34 |

| Figure 3.12. | Chua's circuit.                                                                | 35 |

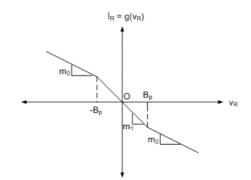

| Figure 3.13. | Chua's circuit non-linear characteristic.                                      | 35 |

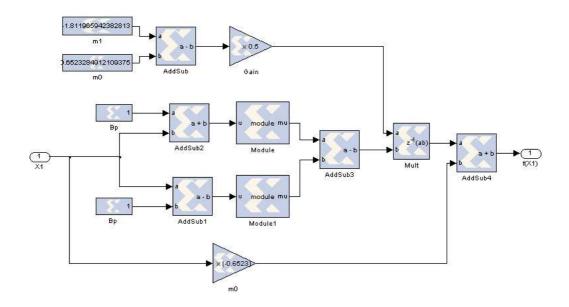

| Figure 3.14. | Simulink structure of Chua equations.                                          | 36 |

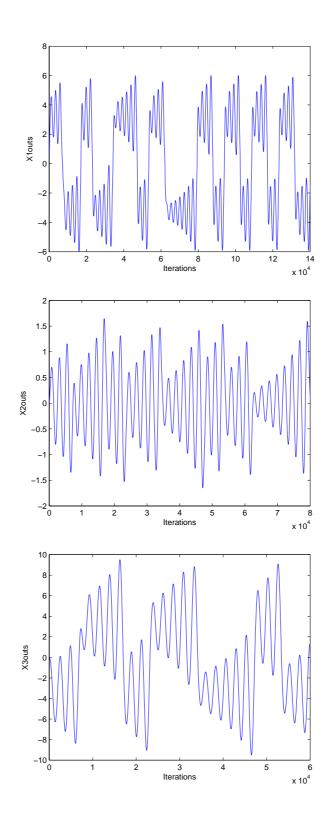

| Figure 3.15. | Non-linear function $g(x_1)$                                                   | 36 |

| Figure 3.16. | Xlouts, X2outs and X3outs outputs of Chua Equation                             |    |

|              | for parameter set A                                                            | 39 |

| Figure 3.17. | Chua's attractor with A, B and C parameters                                    | 40 |

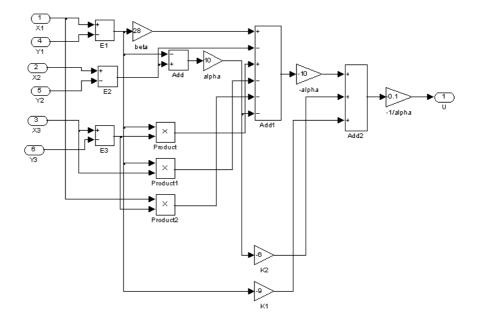

| Figure 4.1.  | Simulink block diagram of the control command                                  |    |

|              | u for Lorenz system                                                            | 54 |

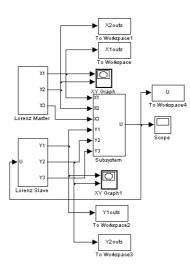

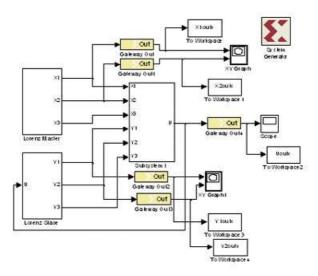

| Figure 4.2.  | Simulink block diagram of synchronized Lorenz system                           | 55 |

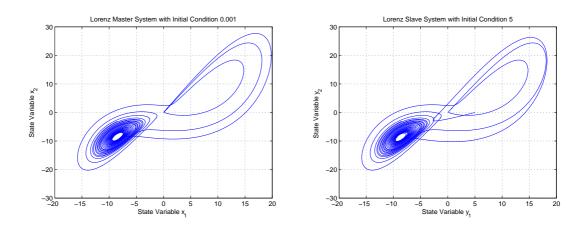

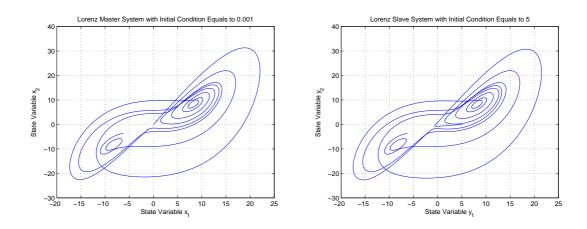

| Figure 4.3.  | Lorenz master and slave system with different initial conditions               | 55 |

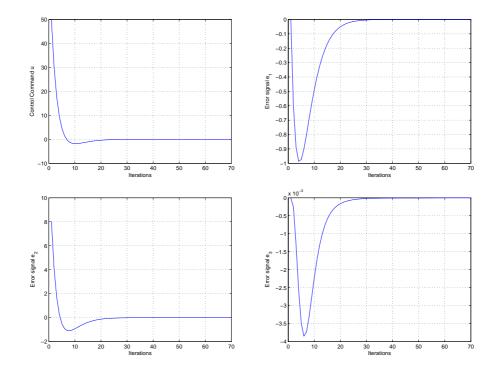

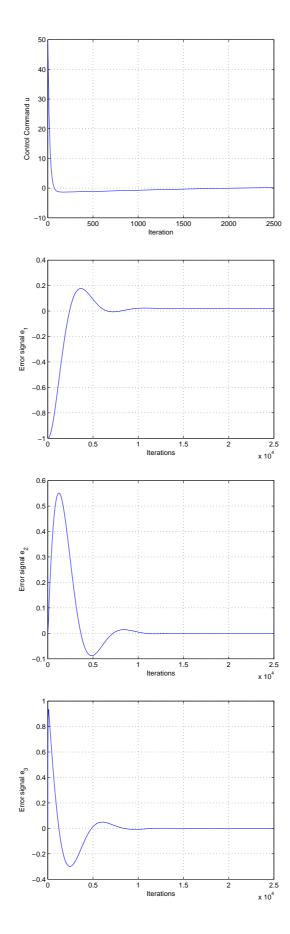

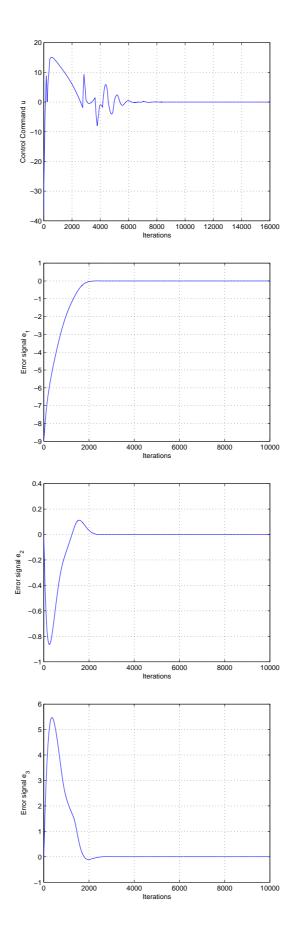

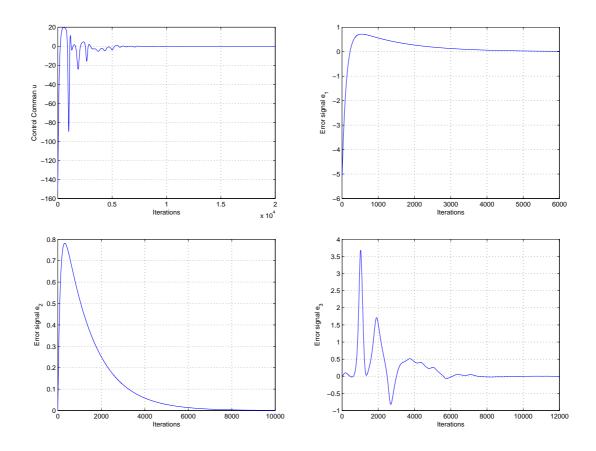

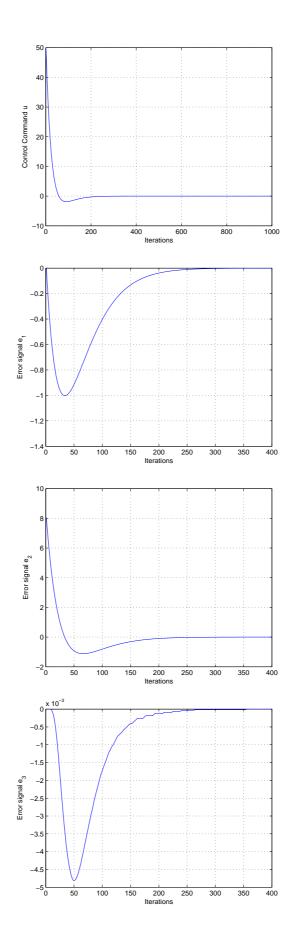

| Figure 4.4.  | The control command $u$ and error signals $e_1, e_2$ and $e_3, \ldots, \ldots$ | 56 |

| Figure 4.5.  | Simulink block diagram of the control command                                  |    |

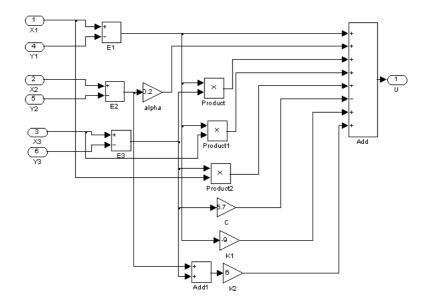

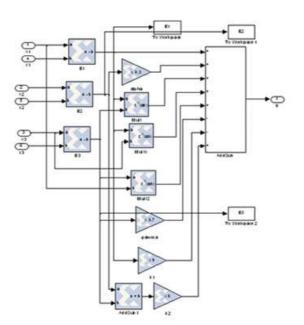

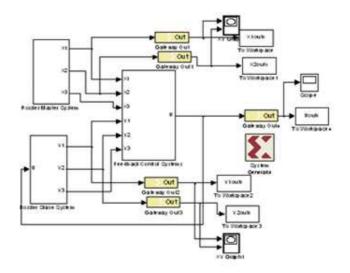

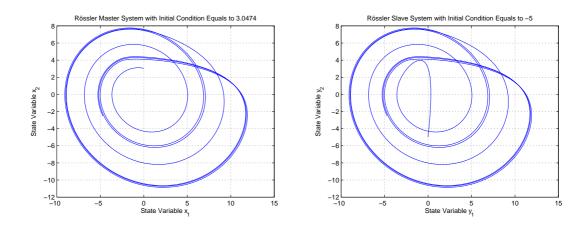

|              | <i>u</i> for Rössler system.                                                   | 63 |

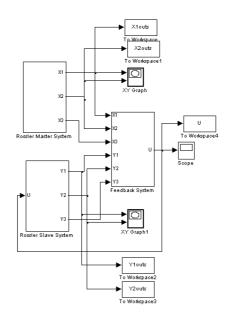

| Figure 4.6.  | Simulink block diagram of the synchronized Rössler system                      | 63 |

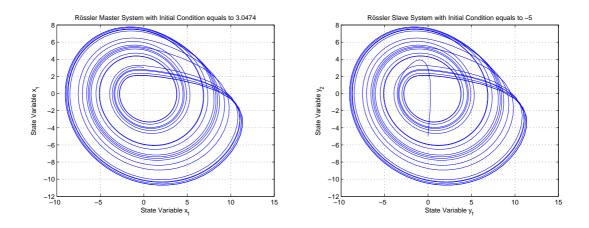

| Figure 4.7.  | Rössler master and slave system with different initial conditions              | 64  |  |

|--------------|--------------------------------------------------------------------------------|-----|--|

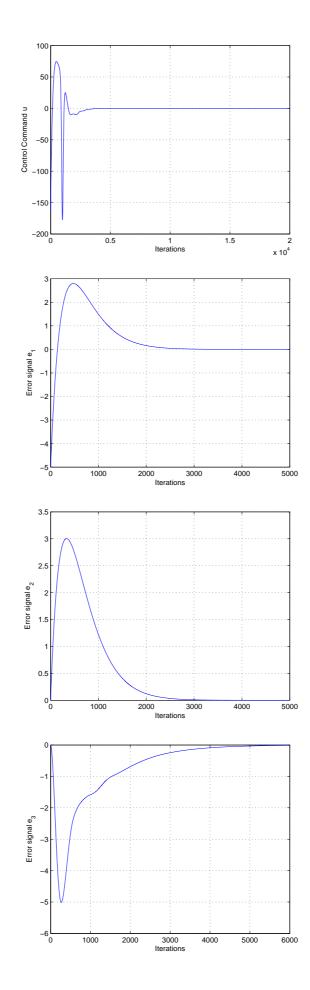

| Figure 4.8.  | The control command $u$ and error signals $e_1, e_2$ and $e_3, \ldots, 64$     |     |  |

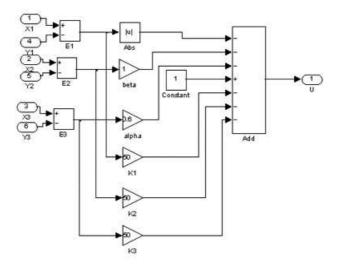

| Figure 4.9.  | Simulink block diagram of the control command                                  |     |  |

|              | u for Linz and Sprott system                                                   | 69  |  |

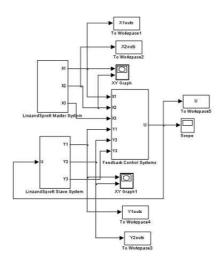

| Figure 4.10. | Simulink block diagram of the synchronized                                     |     |  |

|              | Linz and Sprott system.                                                        | 70  |  |

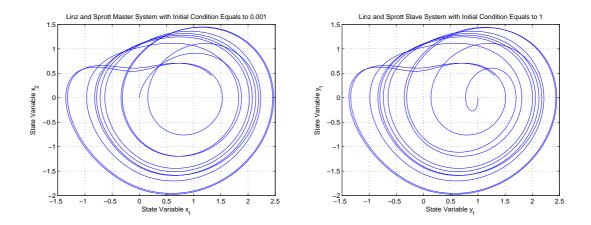

| Figure 4.11. | Linz and Sprott master and slave system with                                   |     |  |

|              | different initial conditions.                                                  | 70  |  |

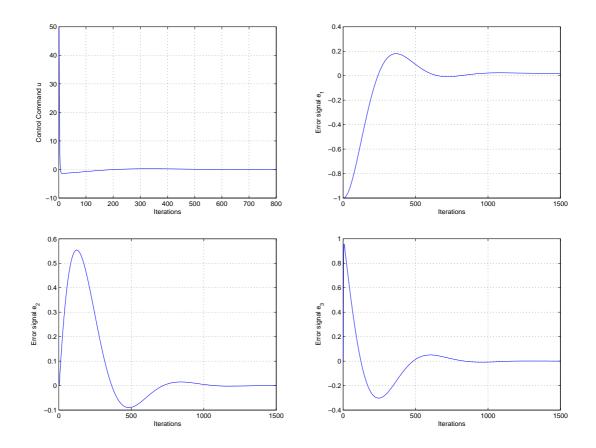

| Figure 4.12. | The control command $u$ and error signals $e_1, e_2$ and $e_3, \ldots, \ldots$ | 71  |  |

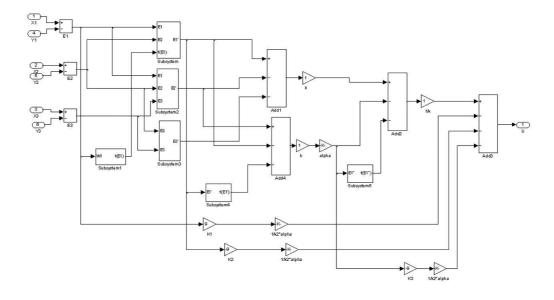

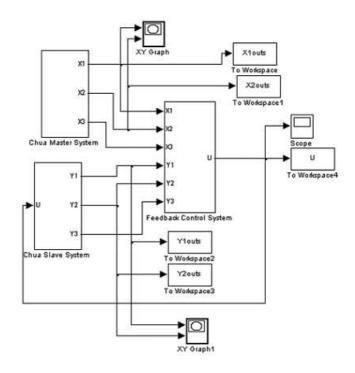

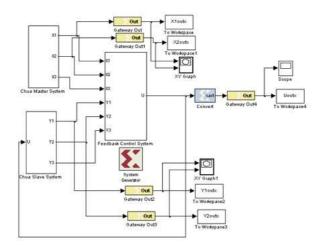

| Figure 4.13. | Simulink block diagram of the control command                                  |     |  |

|              | u for Chua systems                                                             | 77  |  |

| Figure 4.14. | Simulink block diagram of the synchronized Chua systems                        | 78  |  |

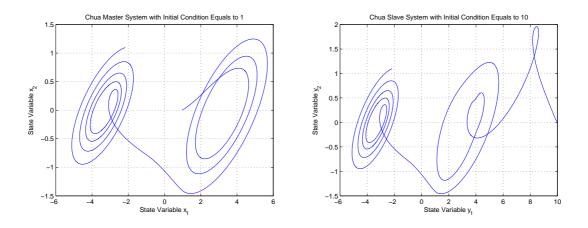

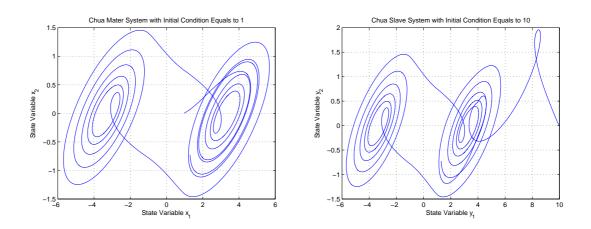

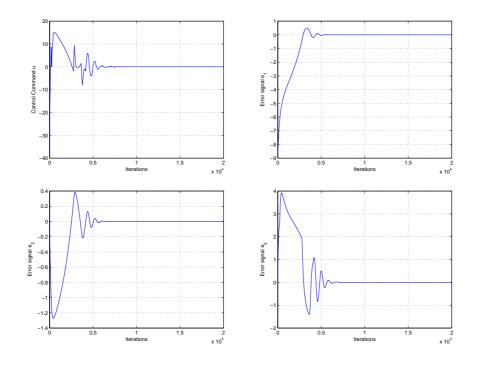

| Figure 4.15. | Chua master and slave system with different initial conditions                 | 78  |  |

| Figure 4.16. | The control command $u$ and error signals $e_1, e_2$ and $e_3, \ldots, \ldots$ | 79  |  |

| <b>F</b> '   | MC 1 Vilian Disala                                                             | 0.1 |  |

|              | MCode Xilinx Block.                                                            | 81  |  |

|              | <i>MCode</i> Xilinx block parameters.                                          | 81  |  |

| -            | Integrator model using Xilinx blockset library.                                | 82  |  |

| •            | System Generator block in Xilinx blokset library                               | 83  |  |

|              | Source window of ISE                                                           | 83  |  |

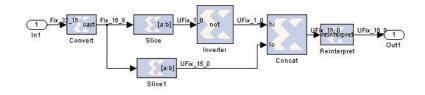

|              | Reduction of resolution and inverting of most significant bit                  | 84  |  |

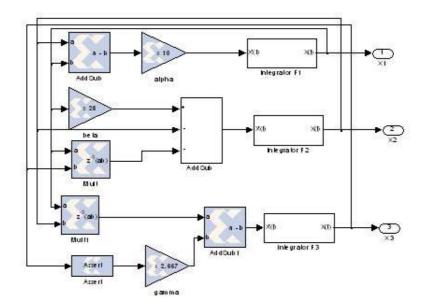

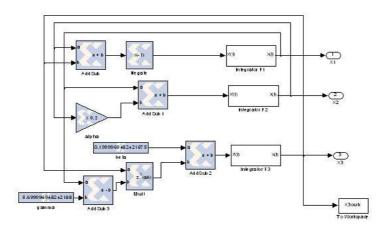

| Figure 5.7.  | Lorenz system by System Generator.                                             | 85  |  |

| Figure 5.8.  | Lorenz system attractor.                                                       | 85  |  |

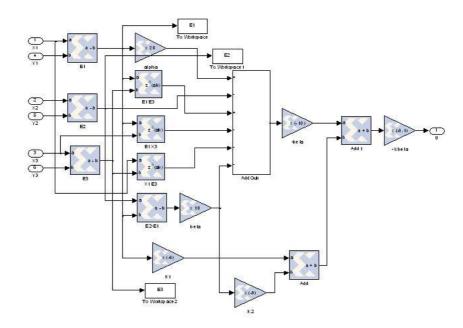

| Figure 5.9.  | The control command <i>u</i> for Lorenz system by                              |     |  |

|              | System Generator.                                                              | 86  |  |

| Figure 5.10. | Synchronized Lorenz system by System Generator.                                | 87  |  |

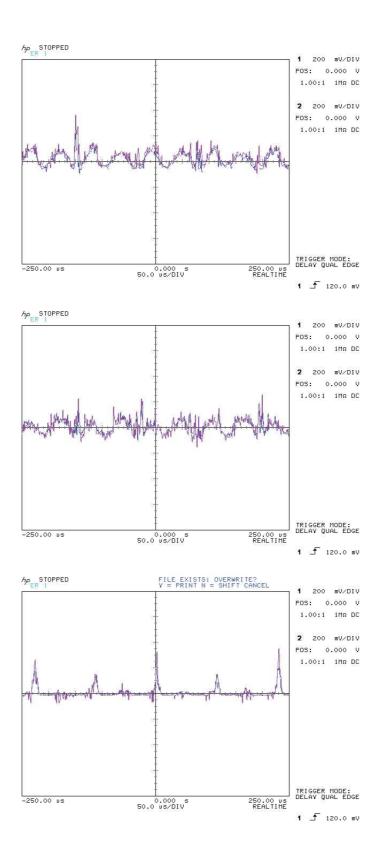

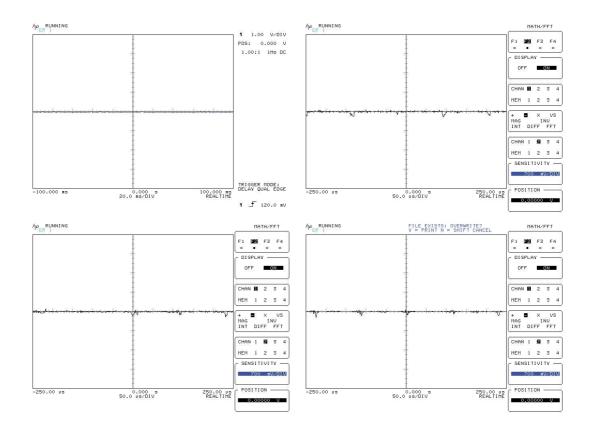

| Figure 5.11. | Synchronized Lorenz system attractors                                          | 87  |  |

| Figure 5.12. | The control command $u$ and error signals                                      |     |  |

|              | $e_1, e_2$ and $e_3$ respectively.                                             | 88  |  |

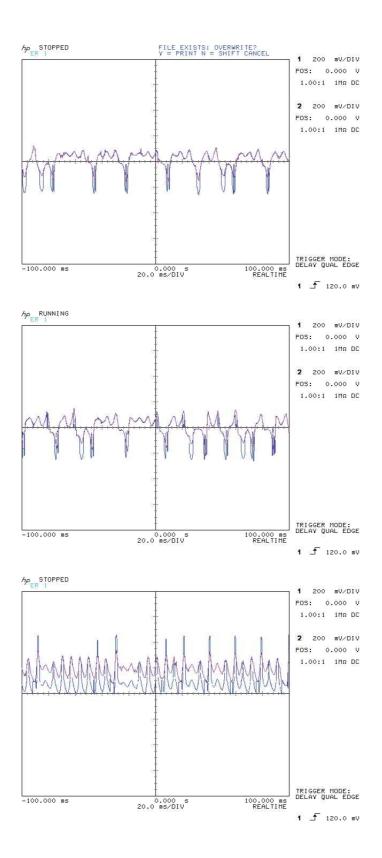

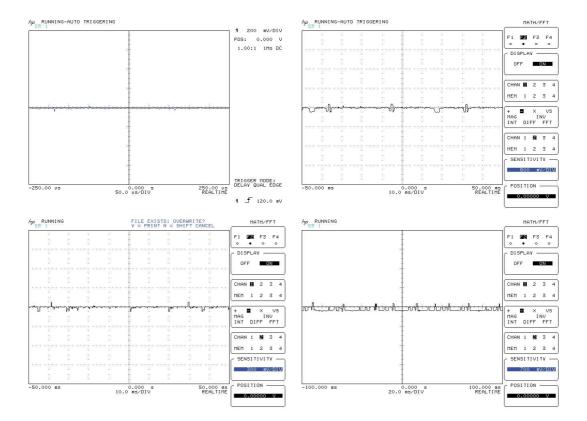

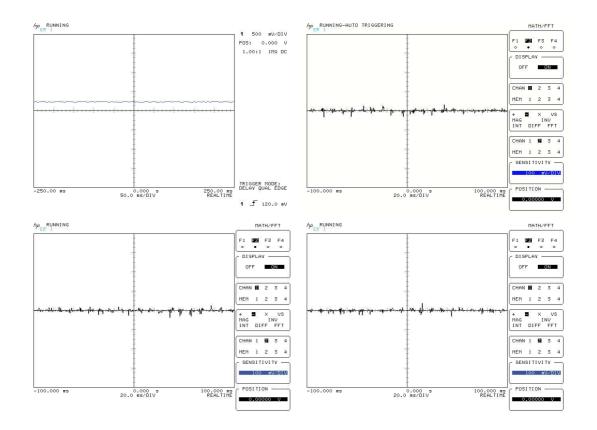

| Figure 5.13. | Lorenz master system state variables and Lorenz                                |     |  |

|              | slave system state variables                                                   | 89  |  |

| Figure 5.14. | The control command $u$ and error signals                                      |     |  |

|              | $e_1, e_2$ and $e_3$ for Lorenz system.                                        | 90  |  |

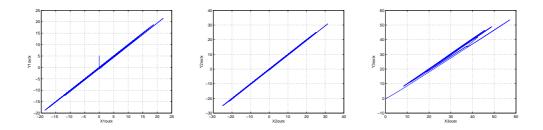

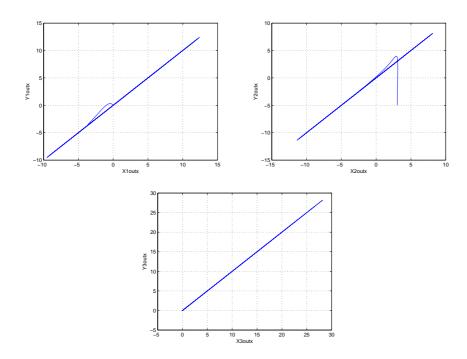

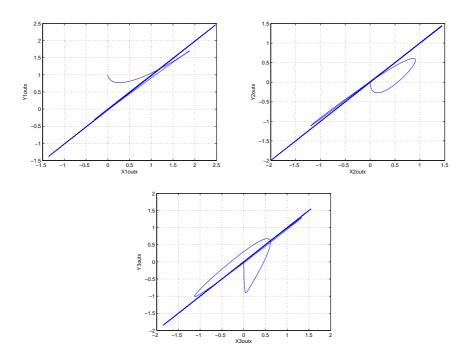

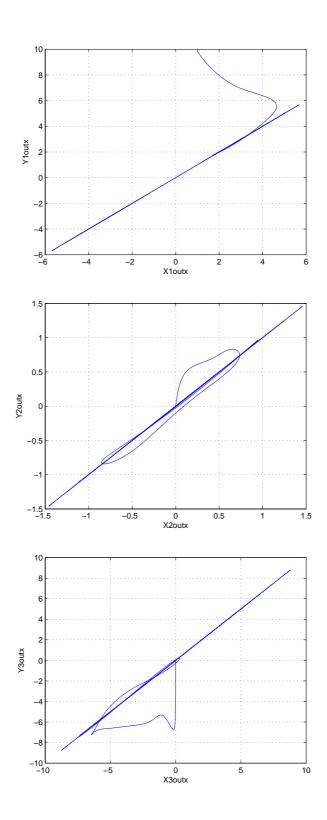

| Figure 5.15. | $x_1$ versus $y_1$ , $x_2$ versus $y_2$ and $x_3$ versus $y_3$    |     |

|--------------|-------------------------------------------------------------------|-----|

|              | by System Generator.                                              | 91  |

| Figure 5.16. | $x_1$ versus $y_1$ , $x_2$ versus $y_2$ and $x_3$ versus $y_3$    |     |

|              | after implementation.                                             | 91  |

| Figure 5.17. | . Rössler system by System Generator.                             | 92  |

| Figure 5.18. | . Rössler system attractor                                        | 93  |

| Figure 5.19. | . The control command $u$ for Rössler system by System Generator  | 93  |

| Figure 5.20. | . Synchronized Rössler system by System Generator.                | 94  |

| Figure 5.21. | . Synchronized Rössler system attractors.                         | 94  |

| Figure 5.22. | . The control command $u$ and error signals                       |     |

|              | $e_1, e_2$ and $e_3$ for Rössler system.                          | 96  |

| Figure 5.23. | . Rössler master system and Rössler slave system state variables  | 97  |

| Figure 5.24. | . The control command u and error signals                         |     |

|              | $e_1, e_2$ and $e_3$ for Rössler system.                          | 98  |

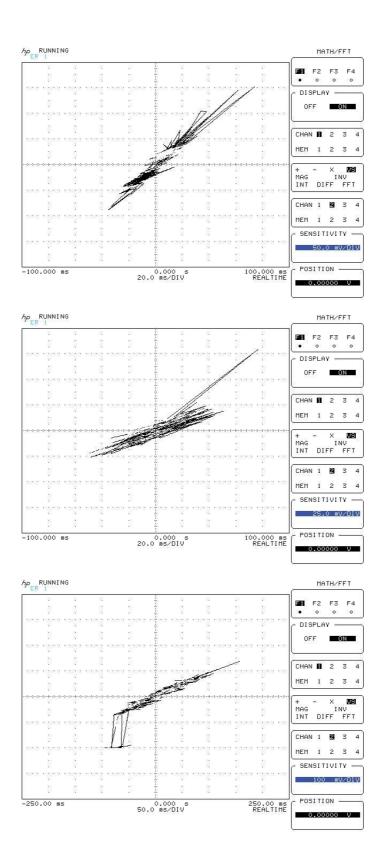

| Figure 5.25. | $x_1$ versus $y_1$ , $x_2$ versus $y_2$ and $x_3$ versus $y_3$    |     |

|              | by System Generator.                                              | 99  |

| Figure 5.26. | $x_1$ versus $y_1$ , $x_2$ versus $y_2$ and $x_3$ versus $y_3$    |     |

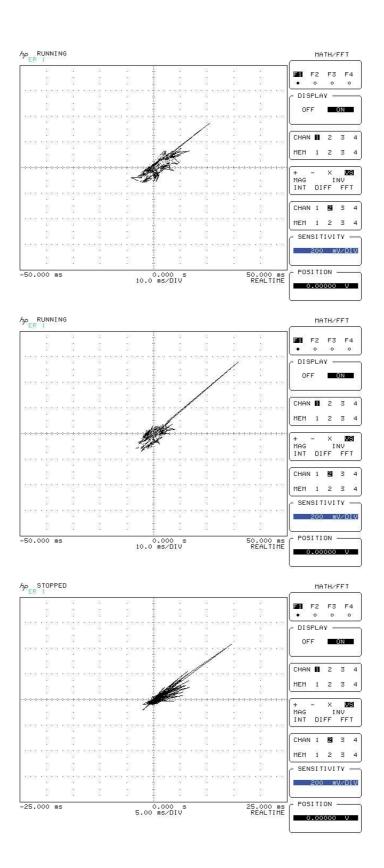

|              | after implementation.                                             | 100 |

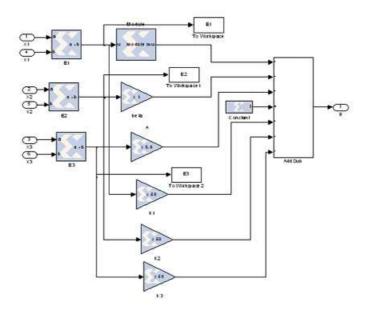

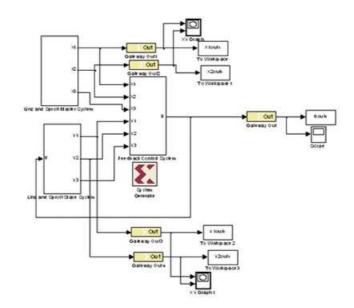

| Figure 5.27. | . Linz and Sprott system by System Generator                      | 101 |

| Figure 5.28. | Linz and Sprott system attractor.                                 | 101 |

| Figure 5.29. | . The control command <i>u</i> for Linz and Sprott                |     |

|              | system by System Generator.                                       | 102 |

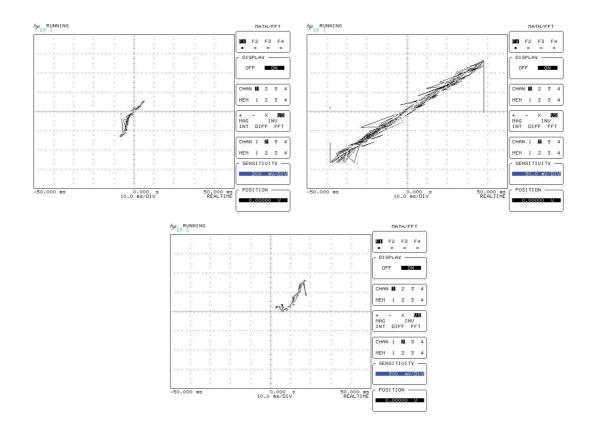

| Figure 5.30. | . Synchronized Linz and Sprott by System Generator.               | 103 |

| Figure 5.31. | . Synchronized Linz and Sprott system attractors                  | 103 |

| Figure 5.32. | The control command $u$ and error signals $e_1$ , $e_2$ and $e_3$ | 104 |

| Figure 5.33. | Linz and Sprott master and Linz and Sprott                        |     |

|              | slave system state variables                                      | 105 |

| Figure 5.34. | The control command u and error signals $e_1$ , $e_2$ and $e_3$   | 106 |

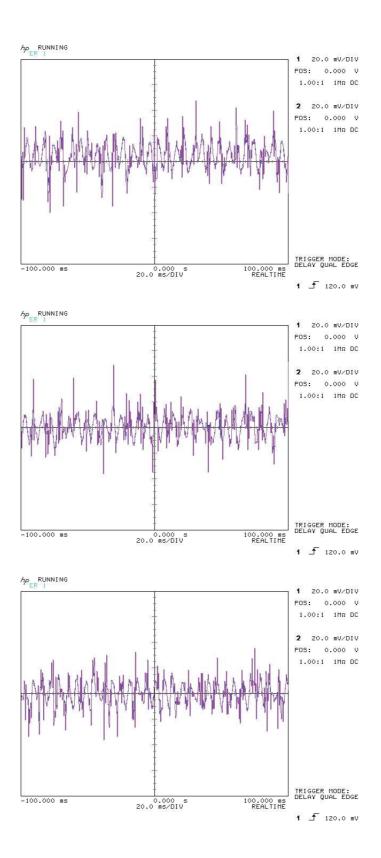

| Figure 5.35. | $x_1$ versus $y_1$ , $x_2$ versus $y_2$ and $x_3$ versus $y_3$    |     |

|              | by System Generator.                                              | 107 |

| Figure 5.36. | $x_1$ versus $y_1$ , $x_2$ versus $y_2$ and $x_3$ versus $y_3$    |     |

|              | after implementation.                                             | 108 |

| Figure 5.37. Chua system by System Generator.                                  | 108 |

|--------------------------------------------------------------------------------|-----|

| Figure 5.38. Non-linear function.                                              | 109 |

| Figure 5.39. Chua system attractor.                                            | 109 |

| Figure 5.40. System Generator block diagram of the control command             |     |

| u for Chua systems.                                                            | 110 |

| Figure 5.41. Synchronized Chua system by System Generator.                     | 110 |

| Figure 5.42. Chua master and slave system with different initial conditions    | 111 |

| Figure 5.43. The control command $u$ and error signals $e_1$ , $e_2$ and $e_3$ | 112 |

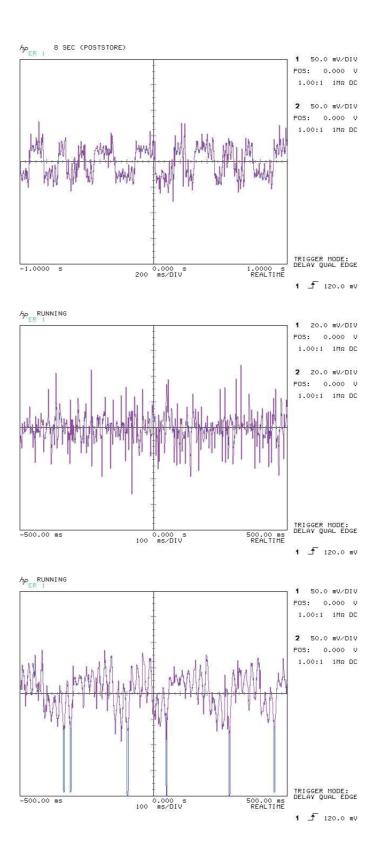

| Figure 5.44. Chua master system state variables and Chua slave system          |     |

| state variables.                                                               | 113 |

| Figure 5.45. The control command u and error signals $e_1$ , $e_2$ and $e_3$   | 114 |

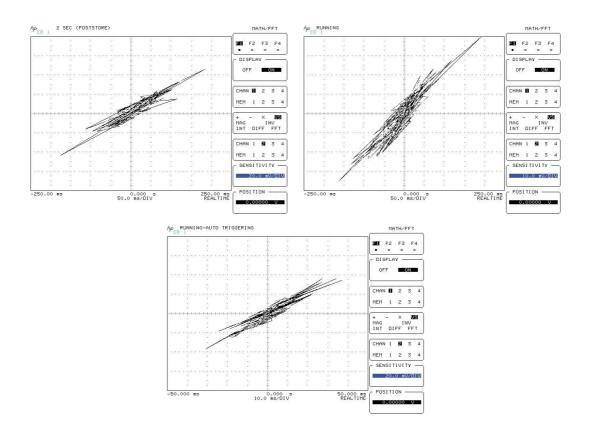

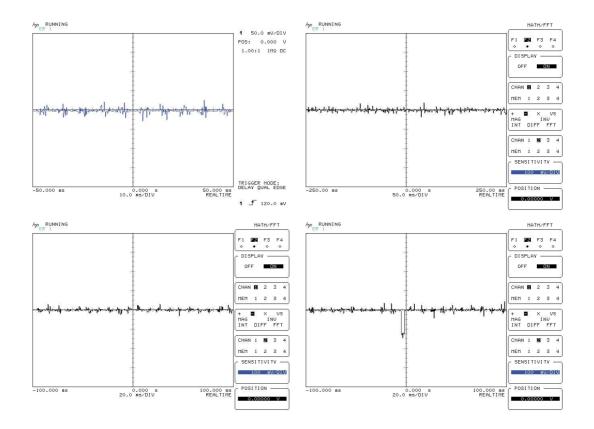

| Figure 5.46. $x_1$ versus $y_1$ , $x_2$ versus $y_2$ and $x_3$ versus $y_3$    |     |

| by System Generator.                                                           | 115 |

| Figure 5.47. $x_1$ versus $y_1$ , $x_2$ versus $y_2$ and $x_3$ versus $y_3$    |     |

| after implementation.                                                          | 116 |

### **CHAPTER 1**

### INTRODUCTION

In this thesis an implementation of a geometric nonlinear controller for chaos synchronization in a Field Programmable Gate Array (FPGA) is presented. Chaotic systems are used to show the implementation of chaos synchronization via nonlinear controller implemented in a Xilinx FPGA Virtex - IV XC4VSX35-10ff668. The main idea is to design a nonlinear geometric controller which synchronizes a slave chaotic system to a master chaotic system and then embeded them the FPGA. The aim is to show that a reconfigurable device can perform a complicated operation such as the chaos synchronization. The verification of each chaotic system was simulated with MATLAB Simulink and Xilinx System Generator. After verification process is completed, FPGA is configured to perform designed systems so that the results can be obtained by experimentally.

In chapter 2, basic process technology types will be presented. After giving information basic process technology types, programmable devices are introduced. They are programmable logic devices, application-specific integrated circuits and field programmable gate arrays, respectively. Because synchronization of chaotic generators are chosen as an application of FPGAs which are more attracted than other programmable devices. FPGAs offer wide variety of applications such as : Digital signal processor (DSP) (Lund, et al. 2004), software-defined radio (Cummings and Haruyama 1999), aerospace and defense systems (Li, et al. 2000), medical imaging (Leeser, et al. 2005), computer vision (Sen, et al. 2005), speech recognition (Marcus and Nolazco-Flores 2005), cryptography (Mentens, et al. 2006), bioinformatics (Luethy and Hoover 2004) can be counted as recent studies.

Lorenz, Rössler, Linz and Sprott and Chua generators as an application of synchronization problem will be presented and simulated by Matlab Simulink program, in chapter 3.

Synchronization of chaotic generators will be examined in chapter 4. Synchronization problem in chaotic system can be achieved by geometric approach (Solis-Perales, et al. 2003).

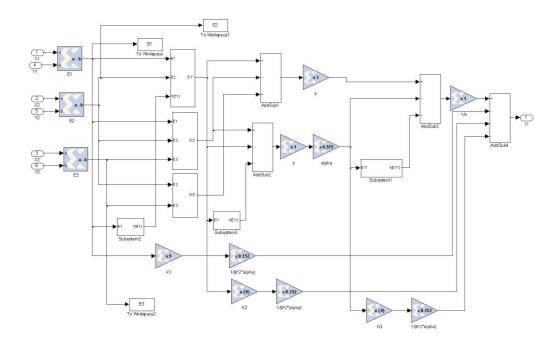

Implementation of synchronized chaotic systems can be seen in chapter 5. By

using Xilinx System Generator program, VHDL code can be generated. After VHDL code is obtained by using ISE program, FPGA can be configured to perform properly.In this chapter simulation and experimental results can be seen.

## **CHAPTER 2**

# THE ORIGIN OF FIELD PROGRAMMABLE GATE ARRAY

Field Programmable gate arrays (FPGAs) are digital integrated circuits (ICs). FP-GAs contain configurable (programmable) logic blocks and configurable interconnects between these blocks. The logic blocks also include memory elements which may be simple flip-flops or more complete blocks of memories. FPGAs are programmed to perform a variety of tasks.

There are two types of FPGAs. One of them is programmed one time. A device which can be programmed one time is referred to as one-time programmable (OTP). The other one is reprogrammed several times.

#### 2.1. Basic Process Technology Types

In this section, some basic technology types will be mentioned. They are fusible link technologies, antifuse technologies, mask-programmed devices, programmable readonly memories, erasable programmable read-only memories, electrically erasable programmable read-only memories and SRAM-based technologies, respectively.

#### **2.1.1.** A Simple Programmable Function

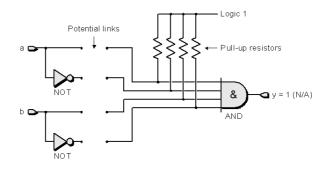

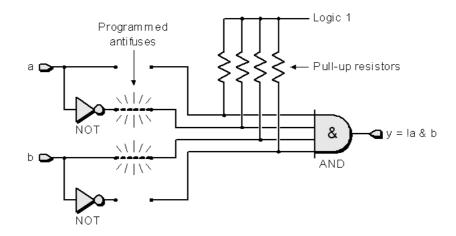

As a basis for basic process technology, it is better to start with a simple programmable function so that we can understand the basis of programmable devices. A simple programmable function can be constructed by using two NAND gates and a AND gate as in the Figure 2.1.

NOT gates are used for having inverting form of inputs so there are both unmodified inputs and inverting inputs. As can be seen in the Figure 2.1 there is no connection between inputs and output so the output is always a logic 1 for this case since all of the inputs to the AND gate are connected by pull-up resistors to a logic 1 value. In order to obtain different outputs depending on inputs, The potential links can be established via

Figure 2.1. A simple programmable function.

some mechanism. These mechanisms will be seen next sections.

#### 2.1.2. Fusible Link Technologies

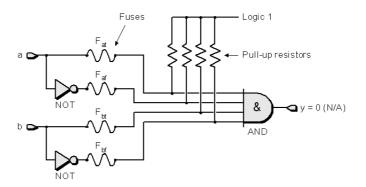

The fusible-link technology is one of the first methods to program the devices by users and is still used for programming devices. In this case, the device is fabricated with fuses as can be seen in Figure 2.2.

Figure 2.2. The device with unprogrammed fusible links.

These fuses work principle is the same as household products. For example, when something that consumes too much power from the television then its fuse will burn out. This cause an open circuit which protects the rest of unit from harm. Of course, the fuses which are used in programmble devices are microscopically small.

At first, all of the fuses of the programmable device are initially intact. This means that, the output of programmable function is always logic 0 since there are all combination

of inputs. For example, if input *a* is 0, then the output will be 0 because of the AND gate. Alternatively, if input *a* is 1 then copmlementary of *a* is 0 then again the output is 0.

The thing is that undesired fuses are removed by applying relatively high voltage or current to the device's inputs in order to achive desired function. For instance, what happens if we remove fuses  $F_{af}$  and  $F_{bt}$  as in Figure 2.3.

Figure 2.3. Programmed fusible links.

The complementary of input *a* and the input *b* are removed from the circuit so we obtain new function which is y = a&!b. (AND operation is represented by & character and NOT operation is represented by ! character. The process of removing fuses is called programming the device or burning the device. Fusible-link based devices are said to be one-time programmable (OTP), since after blowing fuse there is no way to replace blown fuse.

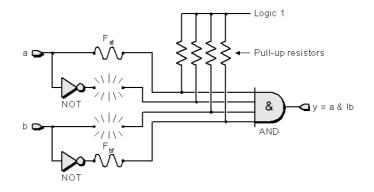

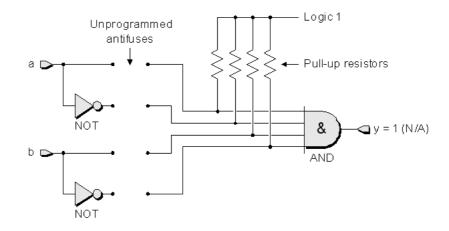

#### 2.1.3. Antifuse Technologies

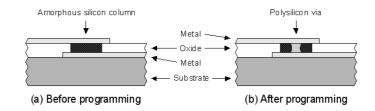

As an alternative to fusible-link technologies, there are antifuse technologies. In this time each configurable path is called antifuse. At first, in unprogrammed state of antifuses, an antifuse has such a high resistance that it acts as a insulator so there is no current flow through unprogrammed antifuse. This time the output is always logic 1 because of pull-up resistors as in Figure 2.4.

In order to achive desired function by applying relatively high voltage or current to the device's inputs so that antifuses can be programmed or grown. For example, the complementary version of input *a* and input *b* are grown by applying proper voltage or current then the device will perform the function y = !a&b as in Figure 2.5.

Figure 2.4. Unprogrammed antifuse links.

Figure 2.5. Programmed antifuse links.

In unprogrammed state there is amorphous silicon (Figure 2.6.a) link between nodes. it act as an insulator so there is no current flow. By converting the insulating amorphous silicon to conducting polysilicon (Figure 2.6.b) by applying relatively high voltage or current, the programmed link between nodes will be constructed.

Figure 2.6. Growing an antifuse.

Like fusible-link technologies, antifuse technologies are also said to be one time programmable because after growing an antifuse there is no way to replace grown antifuse.

#### 2.1.4. Mask-Programmed Devices

There are two types of memory in electronic systems. One of them is read-only memory (ROM) and the other one is rendom-access memory (RAM).

ROMs can be programmed one time after that the data is read from ROMs but new data cannot be written after they are pogrammed once. The written data remains even power is removed from the system. This kind of system is called nonvolatile system. On the contrary, data can be both written into and read from RAM devices. The written data does not remain when power removed from the system. This kind of system is called volatile system.

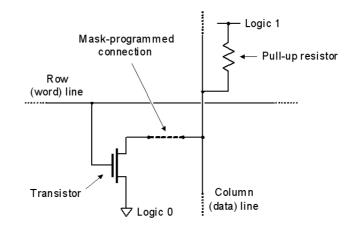

Basic ROMs are mask-programmed devices since process of constructing ROMs are done by means of photo-mask which are used to create the transistors and the metal tracks. For instance, a transistor-based ROM cell can be seen in Figure 2.7.

In order to understand how to program mask-programmed ROM cell two options wil be examined. One of them is that there is a mask-programmed connection and the other one is that there is no mask-pogrammed connections. Now consider a row line is active state. In the first case, there is a connection between transistor and the column line so transistor acts as a resistor then the output will be logic 0. The second case because

Figure 2.7. A transistor-based mask programmed ROM cell.

there is no connection because of pull-up resistor the output will be logic 1.

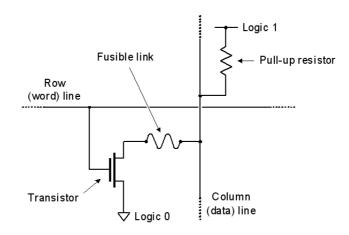

#### 2.1.5. Programmable Read-Only Memories

The programmable read-only memory devices were developed since maskprogrammed devices have problem with their cost and producing time. PROM devices were created usnig a nichrome-based fusible-link technology (Maxfield 2004). As an example, simplified representation of a transistor-and-fusible-link based PROM cell as can be seen in Figure 2.8.

Figure 2.8. A transistor-and-fusible-link-based PROM cell.

At first, all of the fusible links in the device exist.Now consider a row line is active state so transistors act as a resistor then the output will be logic 0. In order to obtain desired function some of fusible links are burnt by applying relatively high voltage

and current. Because of burning some of the fusible links the output will be logic 1. As can be undestood these devices are also OTP because they use fusible link technolgies as well.

#### 2.1.6. EPROM Technologies

As was previously seen previous section PROM devices are one time programmable devices. For this reason,new devices which could be programmed, erased and reprogrammed were developed. This was erasble programmable read-only memory (EPROM).

An EPROM transistor has the same basic structure as a standart MOS transistor. The difference is that there is extra polysilicon floating gate isolated by layers of oxide (Maxfield 2004) as can be seen in Figure 2.9.

Figure 2.9. Standart MOS versus EPROM transistors.

Before programmed the device, EPROM transistors work as standart MOS transistors. When the relatively high voltage is applied between the control gate and drain terminals EPROM transistors are programmed. Afer programming process even though programming signal is removed from the system, negative charge remains on the floating gate.

EPROM transistor-based devices are established as all of the floating gates transistors are uncharged as in Figure 2.10. Consider, a row line in its active state so EPROM transistors act as a resistor then output will be pulled down to logic 0. In order to program device, the floating gates are charged by relatively high voltage so there is no current flow through transistors then the output will be logic 1.

The main difference between PROM and EPROM is that an EPROM cell can be erased by discharging the electrons on Floating gate. The discharge operation needs

Figure 2.10. An EPROM transistor-based memory cell.

energy which is provided by ultraviolet (UV) radiation. In order to erase the device, the device is removed from its host circuit board and then it is placed in an enclosed enclosed container with an intense UV source.

#### 2.1.7. EEPROM Technologies

Electrically erasable programmable read-only memories were developed so that erasing process could be done by electrically. EEPROM cell is approximately 2.5 times larger than EPROM cell since EEPROMcell include two transistor (as can bee seen in Figure 2.11), on the other hand EPROM cell include only one.

Figure 2.11. An EEPROM - cell.

The EEPROM transistor has similar form of EPROM transistor. EEPROM tran-

sistor has also contain floating gate but it is thinner than the one in EPROM cell. The normal MOS transistor in EEPROM cell is used for erasing the cell electrically.

#### 2.1.8. Static Random-Access Memory Based Technologies

There are two types of RAM devices. One of them is dynamic RAM (DRAM) and the other one is static RAM (SRAM). In the case of DRAMs, each cell is fromed from transistor-capacitor pair. In order to keep the data unchanged, that has been loaded into a DRAM cell each cell must be periodically recharged. In order for that there must be a control circurity. It makes design complex and cost effective.

SRAM-based programmable cell do not need to be refreshed. When the data has been loaded into an SRAM cell it will remain unchanged until power is removed from the system. SRAM-base programmable cell can be seen in Figure 2.12.

Figure 2.12. An SRAM-based programmable cell.

The SRAM-baed programmable cell is composed of transistors. One of them is used for driving the output whether it is logic 0 or logic 1 depending on the contents of the storage element. The number of transistors are used for a latch is either 4 or 6 so SRAM cells consume a significant amount of silicon area estate. Another disadvantage is with respest to fuse and antifuse technologies that when power is removed from the system the data will be lost. On the other hand, SRAM based programmable devices can be reprogrammed quickly and repedeately.

Figure 2.13 shows which technologies are used to program SPLDs, CPLDs and FPGAs.

| Technology                    | Symbol | Predominantly associated with   |

|-------------------------------|--------|---------------------------------|

| Fusible-link                  |        | SPLDs                           |

| Antifuse                      |        | FPGAs                           |

| EPROM                         |        | SPLDs and CPLDs                 |

| E <sup>2</sup> PROM/<br>FLASH |        | SPLDs and CPLDs<br>(some FPGAs) |

| SRAM                          |        | FPGAs (some CPLDs)              |

Figure 2.13. Summary of programming technologies.

### 2.2. Programmable Devices and FPGAs

In order to understand the development process of FPGAs we will examine related programmable technologies. As can be seen in Figure 2.14 which technologies appeared on the scene in order.

Figure 2.14. Technology timeline.

The white part of the bars indicate that although those technologies existed, they were not paid attention effectively by system designers because of some reasons. For example, the first FPGA was introduced in 1984 by Xilinx but design engineers did not realized how important FPGA is untill 1990s.

In Figure 2.14, there are eight technologies but we will examine four of them which are more closer to FPGAs.

#### 2.2.1. SPLDs and CPLDs

The programmable logis devices (PLDs) are the first programmable integrated circuits (ICs). PROMs can be counted as the first example of PLDs. They were on the scene in 1970 but they were rather simple so more complex versions became available at the end of the 1970s. So as to seperate comlex ones and simple ones they were called as complex PLDs (CPLDs) and simple PLDs (SPLDs). SPLDs can be divided into four main classes as PROMs, PLAs, PALs and GALs as cen be seen in Figure 2.15. CPLDs will be examined as one class.

Figure 2.15. Classes of PLDs.

#### 2.2.1.1. PROMs

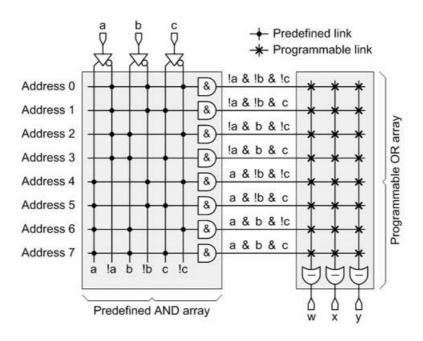

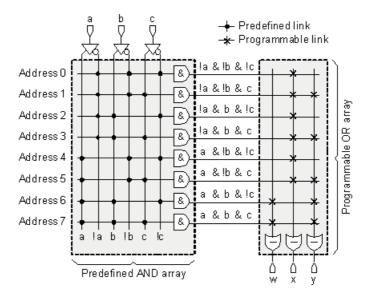

PROMs were the first simple PLDs. They were on the scene in 1970. In order to see how PROM performs, simple example of PROM will be examined. PROM consists of a fixed array of AND gates driving a programmable array of OR gates. 3-input, 3 output PROM (as in Figure 2.16) can be considered as an example of basic PROM cell.

Fusible links, EPROM transistors or EEPROM cells can be used to constructe programmable links in the OR array. In fact Figure 2.16 is an illustration. It does not represent an actual circuit diagram since in reality, each AND gate in the AND array has 3 inputs and similarly each OR gate in the OR array has 8 inputs provided by the outputs from the AND array.

The PROM can be used to implement any block of combinational logic provided that it does not have too many inputs or outputs. In Figure 2.16, the simple 3-input, 3-output PROM can be seen. It can be used to implement any combinational logic function

Figure 2.16. Unprogrammed PROMs.

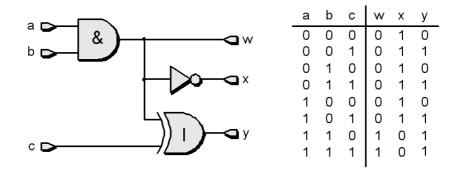

with up to 3 inputs and 3 outputs. Example of 3-input and 3-output combinational logic function can be seen in Figure 2.17.

Figure 2.17. A small block of combinational logic.

In order to construct above combinational function the PROM can be programmed such a way that the same resutls can be obtained. It can be done by programming the appropriate links in the OR array. By using that truth table the outputs can be obtained as in Equation 2.1 below:

Figure 2.18 shows programmed PROM. As can be seen in Figure 2.18, unnecessary links were removed so that desired ouputs w, x, and y are obtained.

Figure 2.18. Programmed PROM.

The example in Figure 2.17 is very simple. It is just for illustraiton of real PROMs. Indeed, real PROMs have more inputs and outputs so they are capable of implementing larger blocks of combinational logic. Before PROMs, combinational logic was usually implemented by means of integrated circuits such as the TI 74xx series devices (Maxfield 2004).

#### 2.2.1.2. Programmable Logic Arrays

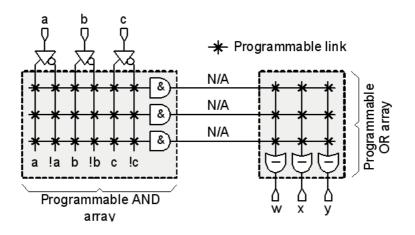

Programmable logic arrays (PLAs) became first available circa 1975. Because both the AND array and OR array were programmable, PLAs were the most user configurable of the SPLDs. For example, 3-input, 3-output unprogrammed PLA can be seen in Figure 2.19.

Figure 2.19. Unprogrammed PLA.

The number of AND gates in the AND array is independent of inputs to the device. Similarly, the number of OR gates in the OR array is independent of inputs to device and the number of AND gates in the AND array.

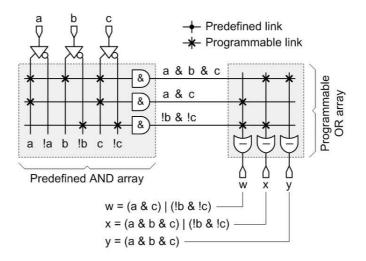

Assume that three equations (Equation 2.2) are implemented by PLA. After PLA is programmed, the programmed PLA diagram can be seen in Figure 2.20.

$$w = (a\&c)|(!b\&!c)$$

$$x = (a\&b\&c)|(!b\&!c)$$

$$y = (a\&b\&c)$$

(2.2)

Figure 2.20. Programmed PLA.

PLAs were useful for large designs whose logical equations has a lot of common product terms. Common product terms can be used multiple outputs, for example, the term (!b&!c) is used in both the w output and x output in Figure 2.20. This feature might be called as product-term sharing.

On the other hand, because both their AND and OR arrays were programmable, signals take long time to pass through programmable links compared to their predefined counterparts. Therefore, PLAs were significantly slower than PROM.

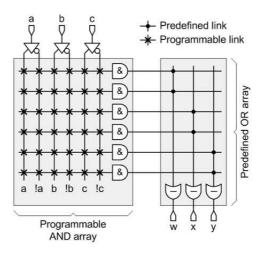

#### 2.2.1.3. PALs and GALs

A next class of device called programmable array logic (PAL) was introduced in the late 1970s. PAL is almost the excat opposite of a PROM since it has a programmable AND array and predefined OR array. As an example, 3-input, 3-output PAL can be seen in Figure 2.21.

Figure 2.21. Unprogrammed PAL.

The advantage of PALs is that thay are faster than PLAs since the only one of PALs arrays is programmable. On the other hand, they are more limeted as compered to PLAs because they are not capable of being programmed by OR gates in OR array.

The Generic Array Logic (GAL) device was an innovation of the PAL and was invented by Lattice Semiconductor. The GAL was an improvement on the PAL because one device was able to take the place of many PAL devices or could even have functionality not covered by the original range. In addition, it was eraseable and reprogramable making prototyping and design changes easier for engineers (Wikipedia 2007a).

#### 2.2.2. Complex Programmable Logic Devices

Because bigger (in terms of functional capability), smaller (in terms of physical size), faster, more powerful and cheaper devices were needed, complex programmable devices (CPLDs) were devoloped at the end of the 1970s.

Altera introduced CMOS-based EPROM technologies which make CPLDs popular in 1984. Because CMOS-based transistors allowed CPLD to achieve functional density and complexity while consuming little power. Because of EPROM technologies, CPLDs were used to develop prototyping environments.

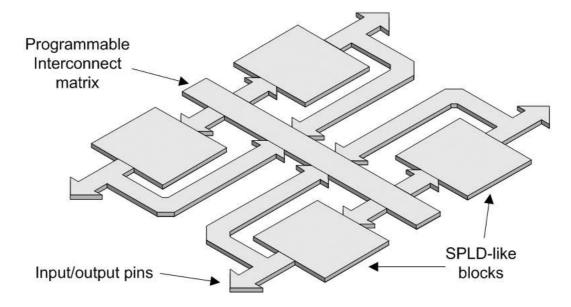

A generic CPLD consists of a number of SPLD blocks (usually PALs). There is a programmable interconnection matrix which make SPLD-like blocks connect each other as can be seen in Figure 2.22.

Figure 2.22. A generic CPLD structure.

The programmable interconnection matrix is used to program links between SPLD-like blocks. SPLD-like blocks are also programmable so in order to achive desired function, both the SPLD-like blocks and programmable interconnection matrix are programmed properly.

#### 2.2.3. Application-Specific Integtrated Circuits

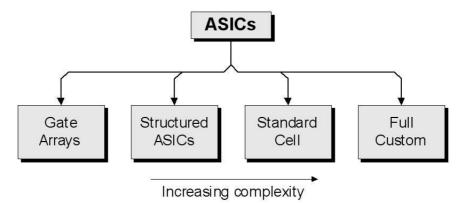

There are four types of aplication-specific integrated circuits (ASICs) which are full custom, gate arrays, standart cell devices, sructured ASICs in the order of time. ASIC types can be seen in Figure 2.23 in the order of the complexcity. ASIC types will be described in the order of time in next subsections.

Figure 2.23. Different types of ASIC.

#### 2.2.3.1. Full Custom

The full custom ASICs are like microprocessors. They were designed in order to be used by a specific company. In the case of full custom devices, every mask layer used to fabricate the silicon chip is controlled completely by design engineers. No components are prefabricated in full custom ASICs and they do not have any libraries of predefined logic gates and functions.

The design of full custom devices is highly complex and time-consuming, but the resulting chips contain the maximum amount of logic with minimal waste of silicon real estate (Maxfield 2004).

#### 2.2.3.2. Gate Arrays

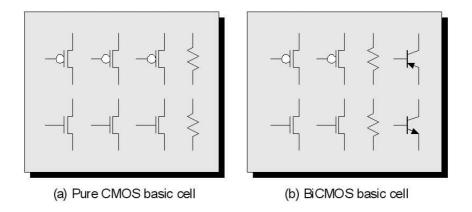

CMOS-based gate array technology became available in the mid-1970s. The idea of gate arrays is that a collection of unconnected transistors and resistors were implemented on basic cell. Each ASIC vendor decides the optimum mix of components provided in its particular basic cell. As an example of basic cell can be seen in Figure 2.24.

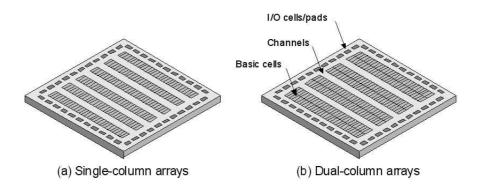

The basic cells are typically presented as either single-column or dual-column arrays. The free areas between the arrays are called as the channels (Figure 2.25).

Figure 2.24. Examples of simple gate array basic cells.

Figure 2.25. Channeled gate array architectures.

A gate level netlist is used to describe the logic gates and connections between them. Special mapping, placement, and routing software tools are used to assign the logic gates to specific basic cells and define how the cells will be connected together (Maxfield 2004). The component inside the basic cells and the basic cells itself are linked together by the metalization layer which is created by the photo-mask.

An advantage of gate arrays is that they have considerable cost advantages because the components in basic cell are prefabricated like transistors so the only thing which needs to be customized is the metalization layers. On the other hand, the power consumption and performance of design are not effective since the most designs leave significant amounts of internal resources unutilized.

#### 2.2.3.3. Standart Cell Devices

Standart cell devices became available in the early of 1980s. In the case of standart cell devices, cell library is defined by ASIC vendor so as to be used by design engineers. The vendor also offers hard-macro and soft-macro libraries, which include elements such as processors, communication functions, RAM and ROM functions.

As compored to gate arrays, no components are prefabricated on the chip. Unlike gate arrays, the concept of a basic cell are not used in standart cell devices. Special tools are used to place each logic gate in the netlist. They are also used to determine the optimum way which the gates are to be linked.

The standart cell devices provide each logic function to be constructed by using the minimum number of transistors. Standart cell device, hence, offer more optimal solution for the silicon real estate than gate arrays do.

#### 2.2.3.4. Structured ASICs

Structured aplication-specific integrated circuits were seen at first at the begining of the 1990s but they were not used effectively at all. ASIC manufacturers started to investigate reducing ASIC design cost and development times circa 2001. In 2003, structured ASIC became available.

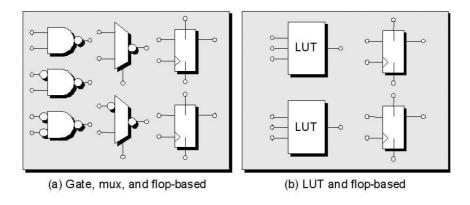

Structured ASIC devices have fundemental element called a module by some and a tile by others. Module or tile element might contain prefabricated generic logic (either as gates, mutiplexers, or a lookup table), registers and possibly a little local RAM as can be seen in Figure 2.26 (Maxfield 2004).

An array (sea) of tiles is prefabricated. If the tile contains only generic logic in the form of prefabricated gates, multiplexers etc. then it can be called base tile. By combaning base tiles and adding registers, small memory elements and other logic to base tile, the master tile can be obtained. Master tiles are also prefabricated on the chip. RAM blocks, clock generators, boundary scan logic are also prefabricated on chip as can be seen in Figure 2.27.

Structured ASIC can be configured using only the metalization layers like a standart gate array. The difference is that, the tile of structured ASIC is more sophisticated rather than the standart gate array so most of the metalization layers are predefined as

Figure 2.26. Example of structured ASIC tiles.

Figure 2.27. Generic structured ASIC.

well.

On the other hand, structured ASICs require three times the real estate and consume two to three times the power of a standart cell device to perform the same function because predefined functions which structured ASIC use is more sophisticeted than the standart cell device so these functions consume much power and much real estate.

#### 2.2.4. Field Programmable Gate Arrays

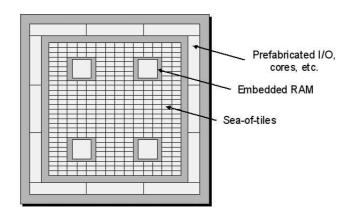

A field programmable gate array (FPGA) is a general-purpose integrated circuit that is programmed by the designer rather than the device manufacturer (Xilinx 2007a). FPGAs were available at the beginning of the 1980s. There was a gap between PLDs and ASICs(Figure 2.28). PLDs were highly configurable and had fast design and modification times, but they could not support large or complex functions. On the other hand, ASICs could support large and complex functions, but they were time-consuming to design and, once a design was implemented, it can not be changed. FPGAs filled the gap by being placed between PLDs and ASICs since FPGAs were programmable like PLDs and they could support large and complex functions to be performed like ASICs.

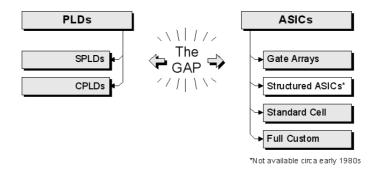

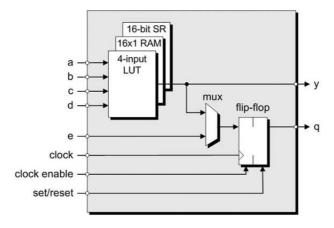

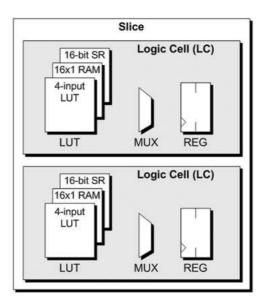

Figure 2.28. The gap between PLD and ASICs.

The first FPGAs were based on CMOS and used SRAM cells for configuration purposes (Maxfield 2004). Early FPGAs were simple and contained few gates as compered to recent FPGAs. The early devices were based on a programmable logic block (PLB). PLBs contain a 3-input lookup table (LUT), a register that could act as a flip-flop or a latch and a multiplexer. Recent FPGAs contain a 4-input LUT which can be used as  $16 \times 1$  RAM or a 16-bit shift register, a multiplexer and flip-flop as can be seen in Figure 2.29. The new form of PLB is called Logic Cell (LC) which will be used next sections.

Figure 2.29. A simplified view of a LC.

Every logic block in the device could be configured to perform a different function by means of appropriate SRAM programming cells. A flip-flop can be configured to keep the data in it until being trigged by a positive or negative-going-clock. The multiplexer can be configured to select the output from the LUT or an independent input from LC input.

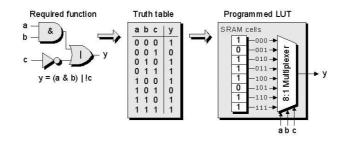

The example is given to understand how LC works. In order to perform y = (a&b)|!c function the LUT cell has to be loaded appropriate output values as can be seen in Figure 2.30. By means of the multiplexer in the LUT, the output of function can be selected among the inputs in the SRAM cell.

Figure 2.30. Configuring a LUT.

The next step up the hierarchy is called as *slice*. Each slice contains two LCs as can be seen in Figure 2.31. The board we used to implement synchronized chaotic

systems has 15360 *slices*. There are internal wires between LCs they are not drawn for simplicity.

Figure 2.31. A *slice* containing two LCs.

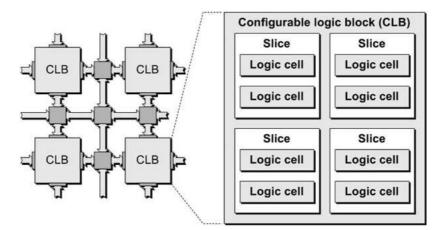

The next step up the hierarchy is called as configurable logic block (CLB). Each CLB contains usually four *slices* as can be seen in Figure 2.32. The CLB of the board we used has four *slices* as well. There is fast programmable interconnect within the CLB as well. This interconnect is used to connect slices which are placed at the same CLB.

Figure 2.32. A CLB containing four slices.

As can be understood previous paragraphs, the hierarchy of FPGA is like this LC  $\longrightarrow$  *Slice* (with two LCs)  $\longrightarrow$  CLB (with four slices). The hierarchy is complemented by

an equivalent herarchy in the interconnect. Therefore, there is the fastest interconnect between the LCs in a *slice*, then slightly slower interconnect between *slice* in a CLB, there is the slowest interconnect between CLBs. These interconnects hierarchy were constructed to avoid interconnect-related delays.

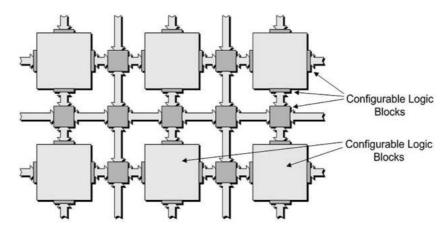

The complete FPGA contains a large number of programmable CLBs surrounded by programmable interconnects as can be seen in Figure 2.33. Besides programmable CLBs and interconnects, FPGA include primary input/output (I/O) pins. By means of its own SRAM cells, the interconnect can be programmed such that the primary inputs to the device are connected to the inputs of one or more CLBs, and the outputs from any CLB can be used to drive the inputs to any other logic block, the primary outputs from the device, or both (Maxfield 2004).

Figure 2.33. Top-down view of simple FPGA architecture.

At the end, FPGAs successfully fill the gap between PLDs and ASICs. They are highly configurable like PLDs and capable of implementing large and complex functions like ASICs. In addition, they have fast design and modification times as compered to PLDs and they are able to be reprogrammed unlike ASICs.

# **CHAPTER 3**

## **CHAOTIC GENERATORS**

#### **3.1. Chaotic Systems**

In the next subsections, Lorenz sytem, Rössler system, Linz and Sprott system and Chua system will be studied. The differential nonlinear equations of these systems will be presented and the chaotic behaviour will be studied. Simulink model will be constructed for each chaotic system, so the results of mathematical simulations of these chaotic differential equations can be seen.

#### 3.1.1. Lorenz System

$$\frac{dx_1}{dt} = \alpha(x_2 - x_1)$$

$$\frac{dx_2}{dt} = \beta x_1 - x_2 - x_1 x_3$$

$$\frac{dx_3}{dt} = x_1 x_2 - \gamma x_3$$

(3.1)

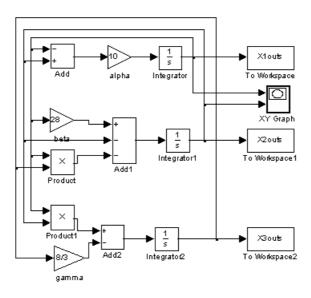

where the parameters  $\alpha = 10$ ,  $\beta = 28$  and  $\gamma = 8/3$ . Lorenz's equations (Lorenz 1963) have two nonlinearities responsible for the chaotic behaviour: the products  $x_1x_3$  and  $x_1x_2$ that are performed by two multipliers. The equations are simulated using the Simulink block diagram presented by Figure 3.1. At least, one of the integrators presented in this diagram must have a non-zero initial condition in order to produce non-zero outputs. In this diagram the block *Integrator* has internal initial condition set to 0.001. *Integrator1* and *Integrator2* blocks have zero initial condition.

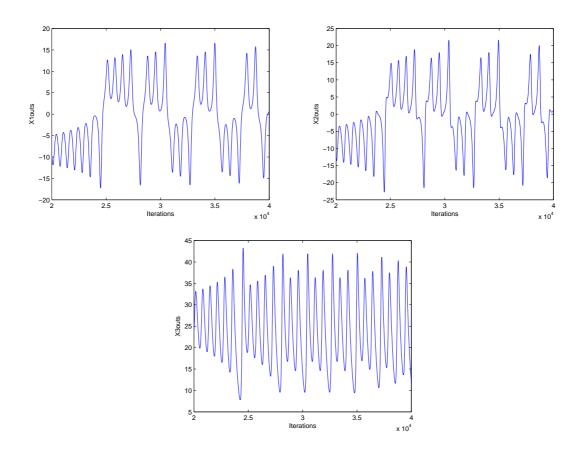

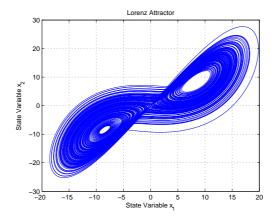

Figures 3.2 shows the outputs *X1outs*, *X2outs*, *X3outs* produced by the Simulink block diagram of Figure 3.1. The Lorenz's attractor (Figure 3.3) is also produced by the Simulink block diagram of Figure 3.1. The Figure 3.3 is obtained by plotting the output variabe *X1outs* versus *X2outs*.

Figure 3.1. Simulink structure of Lorenz's equations.

Figure 3.2. Xlouts, X2outs and X3outs outputs of Lorenz's equations.

Figure 3.3. The attractor of Lorenz's Simulink block diagram.

### 3.1.2. Rössler System

Rössler equations were created by Otto Rössler (Rössler 1976). Rössler system was described with three non-linear differential Equations 3.2. Rössler's system is simpler than Lorenz's, in which there is only one nonlinear term  $x_1x_3$  in the third equation.

$$\frac{dx_1}{dt} = -(x_2 + x_3)$$

$$\frac{dx_2}{dt} = x_1 + \alpha x_2$$

$$\frac{dx_3}{dt} = \beta + x_3(x_1 - \gamma)$$

(3.2)

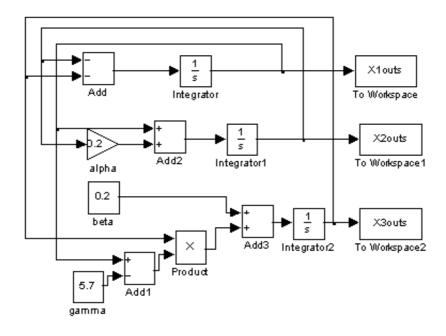

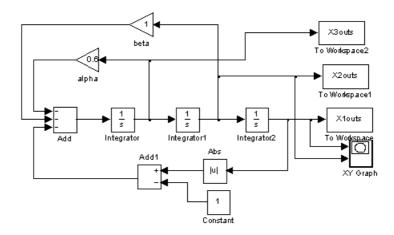

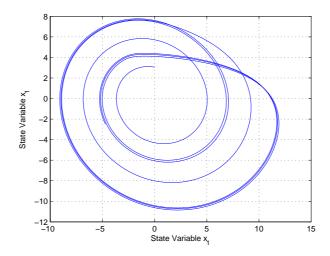

Figure 3.4 below presents Simulink block diagram of the Rössler system described with three non-linear differential equations as can be seen in Equations 3.2. In this Simulink design, the parameters are set to:  $\alpha = 0.2$ ,  $\beta = 0.2$  and  $\gamma = 5.7$ . Integrators initial conditions are set to zero, except the *integrator1* block which is set to 3.0474. The simulation parameters use a *Fixed - Step* solver type with *fixed step* size equal to 0.1 in Simulink configuration box.

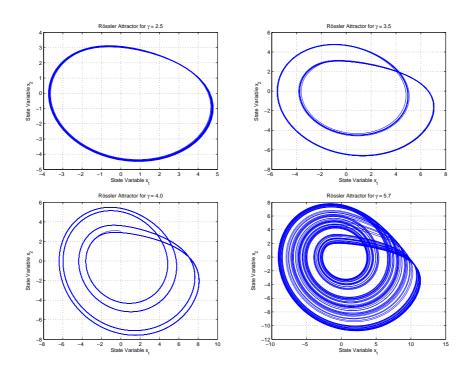

By setting the parameters  $\alpha$  and  $\beta$  equal to 2 and varying the parameter  $\gamma$ , the chaotic behaviour of Rösser system can be seen. Period one ( $\gamma = 2.5$ ), period two ( $\gamma = 3.5$ ) and period four trajectories ( $\gamma = 4.0$ ) can be easily seen in Figure 3.5. These period doubling lead eventually a chaotic state as shown by the last attactor plotted for  $\gamma = 5.7$ .

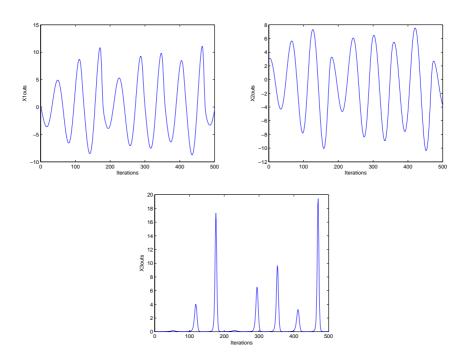

The behaviour of the  $x_3$  state variable in the chaotic state ( $\gamma = 5.7$ ) is understood by looking at time series in Figure 3.6. From Figure 3.6,  $x_3$  state variable is small most of

Figure 3.4. Simulink structure of Rössler equations.

Figure 3.5. Four different Rössler's attractors.

Figure 3.6. Xlouts, X2outs and X3outs outputs of Rössler equations.

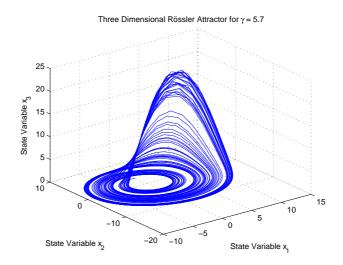

Figure 3.7. Three dimensional Rössler's attractor for  $\gamma = 5.7$

the time which means that trajectories mostly are close to the x - y plane. But sometimes there are spikes in the  $x_3$  time series. For reference, the time series for the  $x_1$  and  $x_2$ variables can be also seen in Figure 3.6.

The full three - dimensional phase portrait of Rössler system is shown in Figure 3.7. This is the attractor for the system. Note that the attractor lies in a bounded region. However, it does not show random behaviour at all so it is clear that deterministic chaos is different from noise or randomness.

#### **3.1.3.** Linz and Sprott System

Linz and Sprott propose the chaotic system presented in Equation 3.3 below, that exhibits chaos for  $\alpha = 0.6$  and  $\beta = 1$ . The constant  $\beta = 1$  affects only the size of the attractor. Chaos also occurs in Equation 3.3 with the nonlinear term  $|x_1|$  replaced by  $|x|^n$ , for nonzero value of the exponent *n* (Linz and Sprott 1999).

$$\frac{dx_1}{dt} = x_2

\frac{dx_2}{dt} = x_3

\frac{dx_3}{dt} = -\alpha x_3 - \beta x_2 \pm (|x_1| - 1)$$

(3.3)

This system also exhibits a period-doubling for  $\alpha = 0.675$ ,  $\beta = 1$ . Linz has recently proved that chaos can not exist in this system if any of the terms of the equation above are set to zero (Linz and Sprott 1999).

Simulink block diagram of Linz and Sprott's chaotic system is presented in Figure 3.8. All integrator blocks are set to a zero initial condition, except block *integrator2*, which has initial condition equals to 0.000001. In the third part of Equation 3.3 above there is a  $\pm$  sign; only the negative sign is used in this Simulink realization, as can be seen in block *Add*.

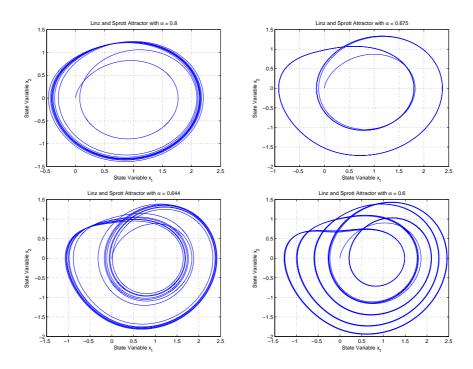

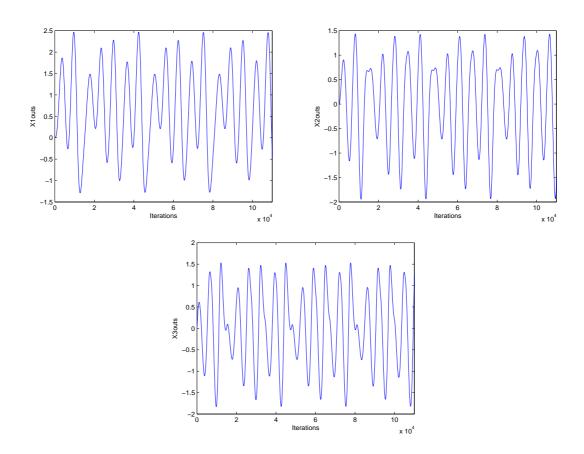

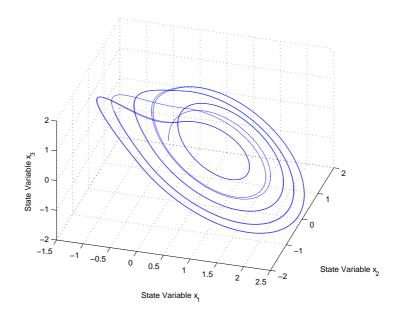

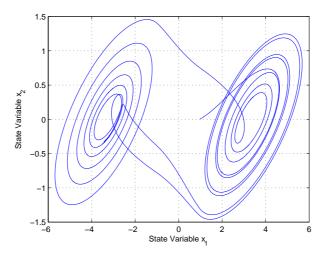

Figure 3.9 presents the attractors of Linz and Sprott's chaotic system for  $\beta = 1$ and for 4 different values of  $\alpha$  equal to 0.8, 0.675, 0.644 and 0.6. The system oscillates but does not present chaotic behaviour for  $\alpha = 0.8$ ,  $\alpha = 0.675$  and  $\alpha = 0.644$ . When  $\alpha$ equals to 0.6 then the chaotic behaviour can be seen (the values of both outputs *X1outs* and *X2outs* never cross in the phase portrait of the system). *X1outs*, *X2outs* and *X3outs* of Rössler equations can be seen in Figure 3.10 for  $\alpha = 0.6$ .

Figure 3.8. Simulink structure of Linz and Sprott equations.

Figure 3.9. The attractor of the Linz and Sprott's Simulink block.

Figure 3.10. Xlouts, X2outs and X3outs outputs of Linz and Sprott Equation.

Figure 3.11. Three dimensional Linz and Sprott's attractor for  $\alpha = 0.6$

### 3.1.4. Chua System

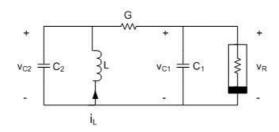

Chua's system is the third order circuit. It is simple since it can be constructed by 4 linear circuit elements (1 resistor, 1 inductor and 2 capacitor) and 1 nonlinear element. The circuit can be seen in Figure 3.12 (Chua, et al. 1986). The dynamic of Chua's system is described by Equation 3.4, where  $g(V_R)$  is the non-linear function described by Equation 3.5. Three diffrential Chua's equations can be easily obtained by analysing the circuit in Figure 3.12 by Kirchhoff's law then Equations 3.4 can be obtained.

Figure 3.12. Chua's circuit.

Figure 3.13. Chua's circuit non-linear characteristic.

$$C_{1} \frac{dv_{c_{1}}}{dt} = G(v_{c_{2}} - v_{c_{1}}) - g(v_{R})$$

$$C_{2} \frac{dv_{c_{2}}}{dt} = G(v_{c_{1}} - v_{c_{2}}) + i_{L}$$

$$L \frac{di_{L}}{dt} = -v_{c_{2}} - R_{L}i_{L}$$

(3.4)

$$g(v_R) = m_0 v_R + \frac{1}{2}(m_1 - m_0)(|v_R + B_P| - |V_R - B_P|)$$

(3.5)

Figure 3.14. Simulink structure of Chua equations.

Figure 3.15. Non-linear function  $g(x_1)$ .

By using a change of variables as in Equation 3.6, the differential equation presented in Equation 3.4 and the nonlinear function in Equation 3.5. can be turned into the state Equations 3.7 and 3.8 respectively.

$$G = 1$$

$$k = \frac{1}{C_2}$$

$$\alpha = \frac{C_2}{C_1}$$

$$\beta = \frac{C_2}{L}$$

$$\gamma = \frac{R_L C_2}{L}$$

$$v_{c_1} = x_1$$

$$v_{c_2} = x_2$$

$$i_L = x_3$$

(3.6)

$$\frac{dx_1}{d\tau} = k\alpha(x_2 - x_1 - g(x_1))

\frac{dx_2}{d\tau} = k(x_1 - x_2 + x_3)

\frac{dx_3}{d\tau} = k(-\beta x_2 - \gamma x_3)$$

(3.7)

$$g(x_1) = m_0 x_1 + \frac{1}{2}(m_1 - m_0)(|x_1 + B_P| - |x_1 - B_P|)$$

(3.8)

Equations 3.7 and Equations 3.8 are simulated by means of Simulink block diagram presented in Figure 3.14 below. Note that the non-linear Equation 3.7 is indicated by the one-input / one-output block g(x1) in Figure 3.15. The block g(x1) is detailed in Figure 3.15 below.

FPGA implementation of Equations 3.7 and 3.8 have an advantage over the analog implementation of Equations 3.4 and 3.5. In FPGA implementation, it is easier to deal with negative resistances, capacitances or inductances than analog domain because it is easier to adjust the system parameters by means of System Generator blocks. 3-different parameters set were used in Figures 3.17 below that it can be seen how easy paremeters

|          | A Parameters | <b>B</b> Parameters | C Parameters |

|----------|--------------|---------------------|--------------|

| α        | 6.579229467  | -1.458906000        | -1.301814000 |

| β        | 10.897662619 | -0.093071920        | -0.013607300 |

| $\gamma$ | -0.044744029 | -0.321434600        | -0.02969968  |

| $m_0$    | -0.652335418 | -0.512843600        | -0.476782200 |

| $m_1$    | -1.811973075 | 1.218416000         | 0.169081700  |

| k        | 1            | -1                  | 1            |

Table 3.1. Parameters used to plot the Chua's attractors

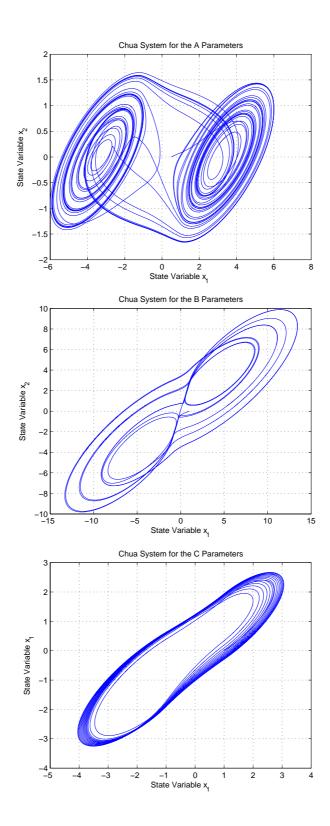

can be adjusted. Using Simulink structure of Figure 3.14, different chaotic behaviours can be simulated. Figures 3.17, shows respectively 3 different chaotic attractors of the Chua's system. These attractors have the parameters given above in Table 3.1.

*X1outs*, *X2outs* and *X3outs* present respectively,  $x_1$ ,  $x_2$  and  $x_3$  outputs of Chua's circuit in time domain.

Figure 3.16. *X1outs*, *X2outs* and *X3outs* outputs of Chua Equation for parameter set A.

Figure 3.17. Chua's attractor with A, B and C parameters.

# **CHAPTER 4**

# SYNCHRONIZATION OF CHAOTIC SYSTEMS

Synchronization of chaos is a phenomenon that might occur when two, or more, chaotic oscillators are coupled. Due to the butterfly effect, which causes the exponential divergence of the trajectories of two identical chaotic system started with nearly the same initial conditions, having two chaotic system evolving in synchrony might appear quite surprising. However, synchronization of coupled chaotic oscillators is a phenomenon well established experimentally and reasonably understood theoretically (Wikipedia 2007b). There are various notions of chaos synchronizations such as generalized synchronization (Afraimovich, et al. 1987), complete synchronization(Pecora and Carrol 1990) and (Solis-Perales, et al. 2003), partial synchronization (Maistrenko and Popovych 2000) and phase synchronization (Rosenblum, et al. 1997) have been devoloped. The pioneering work (Pecora and Carrol 1990), has increased the interest in synchronization after having recently found many applications particularly in telecommunications (Abel and Schwarz 2002), in mechanical systems (Blekhman, et al. 1995) and in control theory (Nijmeijer 2001). Some different forms of synchronization between third-order chaotic systems has been studied by Femat and Solis Perales (Femat and Solis-Perales 1999). In this study, chaotic generators will be synchronized by using complete synchronizability of chaotic systems: a geometric approach (Solis-Perales, et al. 2003).

#### 4.1. Chaos Synchronization

In this study, the chaos synchronization problem will considered as the tracking of the master system trajectories by the slave system. The difference between master and slave system is called as error system which can be constructed as in the following definition.

**Definition 4.1**  $\dot{\mathbf{x}} = \mathbf{F}_M(x)$  and  $\dot{\mathbf{y}} = \mathbf{F}_S(y) + \mathbf{g}(y)u$  be two chaotic systems in a manifold  $\mathbf{M} \subset \mathbb{R}^n$ .  $\mathbf{F}_M$ ,  $\mathbf{F}_S$  smooth vector fields with output functions  $s_M = h(x)$ ,  $s_S = h(y)$  and  $\mathbf{x}, \mathbf{y} \in \mathbb{R}^n$  and  $\mathbf{g}(y) \in \mathbb{R}^n$  is a smooth input vector. The dynamical error system can be

found as  $\dot{\mathbf{e}} = \mathbf{F}_M(x) - \mathbf{F}_S(y) - \mathbf{g}(y)u$ . Because  $\mathbf{e} = \mathbf{x} - \mathbf{y}$  then  $\mathbf{y} = \mathbf{x} - \mathbf{e}$  so the dynamical error system can be written as  $\dot{\mathbf{e}} = \mathbf{F}_M(x) - \mathbf{F}_S(x - e) - \mathbf{g}(x - e)u$ , where  $u \in \mathbb{R}$  is the control command (Solis-Perales, et al. 2003).

From Definition 4.1, synchronization error system can be written in the form as  $\dot{\mathbf{e}} = \mathbf{F}_S(e) - \mathbf{g}(e)u + \Psi(x, e)$ . Because  $\Psi(x, e)$  depends on the solution of master system, the synchronization error system is extended so that  $\dot{\mathbf{x}} = \mathbf{F}_M(x)$  can be considered. Extended synchronization error system can be written in the form as follows:

$$\dot{\mathbf{x}} = \mathbf{F}_M(x), \tag{4.1}$$

$$\dot{\mathbf{e}} = \mathbf{F}_M(x) - \mathbf{F}_S(x-e) - \mathbf{g}(x-e)u, \qquad (4.2)$$

$$Y_e = h(x, e)$$

$Y_e$  is the output of the synchronization error system. Extended synchronization error system can be written in affine form as:

$$\dot{\mathbf{X}} = \mathbf{F}(X) + \mathbf{G}(X)u, \tag{4.3}$$

where  $\mathbf{X} = [\mathbf{x}, \mathbf{e}]^T$ ,  $\mathbf{F}(X) = [\mathbf{F}_M, \mathbf{F}_M - \mathbf{F}_S]^T$  and  $\mathbf{G}(X) = [\mathbf{0}, -\mathbf{g}]$ . In this study, complete synchronization is considered (Solis-Perales, et al. 2003), which means that the slave and the master system display the same pattern at the same time. In order to achieve complete synchronization, synchronization error system in Equation 4.2 should be stabilized around the point  $e^* = 0$ .

Synchronization error system in Equation 4.2 can be stabilized at the origin by means of the control command *u*. If such control command is found, complete synchronization of chaotic system can be achieved. The proper control command can be found by using the geometrical tools. These tools are the properties of controllability and observability of non-linear affine systems (Nijmeijer, van der Schaft 1990). The controllability and observability of chaotic systems will be explained in sections 4.2 and 4.3 respectively.

### 4.2. Synchronizability from Control of Chaotic Systems

A definition for synchronizability can be considered for complete synchronization between chaotic systems.

**Definition 4.2**  $\exists u = u(x_M - x_S) \in \mathbb{R}$  such that  $|x(t) - y(t)| \approx 0$ , with  $x, y \in \mathbb{R}^n$  for all  $t > t^* < \infty$  and any initial conditions  $x_0 = x(t = 0)$  and  $y_= = y(t = 0)$  belonging to that manifold  $\mathbf{M} \subset \mathbb{R}^{2n}$  (Solis-Perales, et al. 2003).

The controllability and observability conditions can be used in order to find a tangent space at stabilization point e = 0. The vector **G** can be calculated such that it generates a tangent space with constant dimension at  $(x, 0)^T$ . As previously defined  $Y_e = h(x, e)$  which is an output function of sychronization error system. The computation of  $Y_e$  involves conditions for synchronizability of chaotic systems which will be shown in following sections.

#### 4.2.1. Local Controllability for Complete Synchronizability

We start this section by giving Lemma 4.1 as following below:

**Lemma 4.1** C(x,e) be the accessibility distribution with constant dimension d at e = 0 then system (Equation 4.3) is locally accessible (locally controllable) and the contrallable space has dimension d (Nijmeijer, van der Schaft 1990).

The local coordinate transformation can be found such that system in Equation 4.3 can be partially or completely transformed into a linear controllable system around (x, 0) by taking into account 4.1. In order for local coordinate transformation, accessibility distribution needs to be found. In order to find accessibility distribution function, Lie brackets and Lie derivative are needed to be known. Definition 4.3 given below explains Lie brackets and Lie derivative respectively.

**Definition 4.3** Let F and G be two vector fields in a manifold M, the vector field  $[F, G](X) = \frac{\partial G}{\partial X} \cdot F - \frac{\partial F}{\partial X} \cdot G$  is called the Lie bracket of F and G. The Lie derivative of a real-valued function h(x, e) along the vector field F is defined as  $L_F h(x, e) = \langle \partial h, F \rangle$  (Vidyasagar 1993).

The accessibility distribution  $\mathbf{C}(x, e)$  can be expressed as  $\mathbf{C}_d = span\{ad_F^{d-1}\mathbf{G}\}\$ where  $ad_F = [\mathbf{F}, \mathbf{G}]$  and  $ad_F^{d-1} = [\mathbf{F}, [\mathbf{F}, [..., [\mathbf{F}, \mathbf{G}], ..., ]]]$  for d = 1, ..., n.

**Remark 4.2** Equation 4.3 is composed of two subsystems (Equations 4.1 and Equations 4.2) the tangent space locally generated at  $(x, 0)^T$  has dimension  $d \le n$ .  $C_d$  is generated

by d linearly independent vector fields that span of dimension  $d \le n$  because Equations 4.1 are unidirectionally coupled with Equations 4.2.

There are two restrictions concerning the controllability for synchronizability of master/slave systems:

(i) The constant dimension  $Dim(\mathbf{C}_d(x, 0)) = d$

(ii) The distribution  $C_{d-1}$  should be involutive.

At the end there is a Proposition 4.1 given by (Solis-Perales, et al. 2003) as follows

**Proposition 4.1** Suppose that the internal dynamics is stable and assume that accessibility distribution C has constant dimension d (i.e., C is involutive) in a neighborhood  $U^0$  of (x, 0), then system is locally controllable.

#### 4.2.2. Local Observability for Complete Synchronizability

The output function  $Y_e = h(x, e)$ , where h is real-valued function of the system in Equation 4.3. It is related to the observability of the synhronization system. Let us consider the following Definition 4.4 (Nijmeijer, van der Schaft 1990).

**Definition 4.4** Consider an affine system  $\dot{X} = F(X) + G(X)u$ , with an output function  $Y_e = h(x)$ . It is said that the system has relative degree  $\rho$  at  $x^0$  if (i)  $L_G L_F^k h(x) = 0$  for all x in a neighborhood of  $x^0$  and  $k \le \rho - 1$ , (ii)  $L_G L_F^{\rho-1} h(x^0) \ne 0$ .

If the system in Equation 4.3 has relative degree  $\rho$  at  $(x, 0)^T$ , the Lie derivatives of the output function are given by h(x),  $L_F h(x)$ ,  $L_F^2 h(x)$ , ...,  $L_F^{\rho-1} h(x)$ , and the covector fields  $\partial h(x)$ ,  $\partial L_F h(x)$ ,  $\partial L_F^2 h(x)$ , ...,  $\partial L_F^{\rho-1} h(x)$ , which are independent in the neighborhood U of  $(x, 0)^T$  (Nijmeijer, van der Schaft 1990). In this way, by using the Lie derivatives of h(x, e), a local coordinate transformation can be defined at  $(x, 0)^T$ .

Such a transformation  $z = \Phi(x, e)$  is defined as  $\Phi_1 = h(x), \Phi_2 = L_F h(x), ..., \Phi_{\rho} = L_F^{\rho-1} h(x)$  and the  $2n - \rho$  complementary functions are obtained by finding the Jacobian matrix of  $z = [\Phi_1, \Phi_2, ..., \Phi_n, ..., \Phi_{2n}]^T$  be nonsingular at (x, 0) and  $L_G \Phi_i(x, e) = 0$ , with  $i = \rho + 1, ..., 2n$  and (x, e) in a neighborhood of (x, 0) (Solis-Perales, et al. 2003).

**Proposition 4.2** Suppose that the system in Equation 4.3 has relative degree  $\rho$  at (x, 0) and the codistribution  $ker(span\{\partial h(x, 0), \partial L_F h(x, 0), \partial L_F^2 h(x, 0), ..., \partial L_F^{\rho-1} h(x, 0)\})$  has dimension  $\rho$ , then the system in Equation 4.3 is locally observable at (x, 0) (Solis-Perales, et al. 2003).

#### 4.3. Complete Synchronizability

If Propositions 4.1 and 4.2 hold for complete synchronizability for Equation 4.3 then that system is linearizable by feedback. By using this property, an invertible coordinates transformation and a control command can be calculated. The Theorem 4.3 which was proposed by (Solis-Perales, et al. 2003) comprises stabilizing conditions mentioned before.

**Theorem 4.3** Consider the system in Equation 4.3. Suppose that there exist  $2n - \rho$ functions  $\Phi_i(x, e)$  such that  $L_G \Phi_i(x, e) = 0$ ,  $i = \rho + 1, ..., 2n$ . This system is feedback linearizable at (x, 0) if and only if if there exists a function h(x, e) such that  $(i) < \partial h, ad_F^{k-1}\mathbf{G} > (x, e) = 0$  for  $k = 1, ..., \rho - 1; \rho > 1$  and (x, e) in a neighborhood U of (x, 0),  $(ii) < \partial h, ad_F^i\mathbf{G} > (x, 0) \neq 0$  for  $i = \rho, ..., n$  at (x, 0), where  $\rho = d$  stands for the dimension of the tangent space.

Theorem 4.3 satisfies sufficient and necessary conditions for complete synchronizability of the same order systems. In addition to that, conditions (i) and (ii) in Theorem 4.3 can be used to calculate proper output function in order to make the system in Equation 4.3 locally observable at (x,0). Then there is a Corollary 4.4 as given below by (Solis-Perales, et al. 2003).

**Corollary 4.4** Two chaotic systems with the same order are completely synchronizable if and only if the dynamical error system is feedback linearizable at (x, 0).

The system Equation 4.3 is called feedback linearizable if there exist a smooth reversible change of coordinates  $z = \Phi(x, e)$  and smooth transformation of the feedback (Andrievskii and Fradkov 2003)

$$u = \lambda(x, e) + \mu(x, e)v, \qquad (4.4)$$

where  $v \in \mathbb{R}^m$  is the new control if the closed-loop is linear. If the linearizability criterion is satisfied, then by means of transformations

$$z = \Phi(x, e) = col(h(x, e), L_F h(x, e), ..., L_F^{\rho-1} h(x, e))$$

$$u = \frac{1}{L_G L_F^{\rho-1} h(x, e)} (-L_F^{\rho} h(x, e) + v)$$

(4.5)

$$\lambda(x,e) = \frac{-L_F^{\rho}h(x,e)}{L_G L_F^{\rho-1}h(x,e)}$$

(4.6)

$$\mu(x,e) = \frac{1}{L_G L_F^{\rho-1} h(x,e)}$$

(4.7)

$$\nu = \mathbf{K}_i(z_i - z_i^*) \tag{4.8}$$

where  $\kappa_i$  with  $i = 1, ..., \rho$  are the control gains and chosen in such a way that the closed-loop subsystem  $\dot{z}$  converges to origin and  $z_i^*$ 's are the coordinates of the stabilization point. In order to achieve complete synchronization  $z_i^*$ 's are set to zero.

Complete synchronization approach will be applied to chaotic generators and then by using Syimulink in MATLAB, results will be seen in following sections.

### 4.4. Synchronization of Lorenz System

Firstly, Lorenz system will be examined in order to see whether complete synchronization approach is valid for this system. For simplicity, the master and slave systems are considered as they have the same parameter values,

$\dot{x} = \mathbf{F}_M(x)$

$$\dot{x}_{1} = \alpha(x_{2} - x_{1})

\dot{x}_{2} = \beta x_{1} - x_{2} - x_{1}x_{3}

\dot{x}_{3} = x_{1}x_{2} - \gamma x_{3}$$

(4.9)

and  $\dot{y} = \mathbf{F}_S(y) + \mathbf{g}(y)u$

$$\dot{y_1} = \alpha(y_2 - y_1) + g_1(y)u

\dot{y_2} = \beta y_1 - y_2 - y_1 y_3 + g_2(y)u

\dot{y_3} = y_1 y_2 - \gamma y_3 + g_3(y)u$$

(4.10)

where the parameters  $\alpha = 10$ ,  $\beta = 28$  and  $\gamma = 8/3$ .  $g_1(y)$ ,  $g_2(y)$  and  $g_3(y)$  are the corresponding elements in the input vector of the slave system. The difference between master and slave system are found by calculating e = x - y then it is easily seen that  $\dot{e} = \dot{x} - \dot{y}$ .

$$\dot{e}_{1} = \alpha[(x_{2} - y_{2}) - (x_{1} - y_{1})] - g_{1}(x - e)u$$

$$\dot{e}_{2} = \beta(x_{1} - y_{1}) - (x_{2} - y_{2}) + [x_{1}x_{3} - (x_{1} - e_{1})(x_{3} - e_{3})] - g_{2}(x - e)u$$

$$\dot{e}_{3} = x_{1}x_{2} - [(x_{1} - e_{1})(x_{2} - e_{2})] - \gamma(x_{3} - y_{3}) - g_{3}(x - e)u$$

(4.11)

From Definition 4.1 extended synchronization error system can be calculated as follows:

$$\begin{aligned} \dot{x_1} &= \alpha(x_2 - x_1) \\ \dot{x_2} &= \beta x_1 - x_2 - x_1 x_3 \\ \dot{x_3} &= x_1 x_2 - \gamma x_3 \\ \dot{e_1} &= \alpha(e_2 - e_1) - g_1(x - e) u \\ \dot{e_2} &= \beta e_1 - e_2 + e_1 e_3 - e_1 x_3 - x_1 e_3 - g_2(x - e) u \\ \dot{e_3} &= -e_1 e_2 - \gamma e_3 + e_1 x_2 + x_1 e_2 - g_3(x - e) u \end{aligned}$$

(4.12)

This is  $\dot{e} = \mathbf{F}_M(x) - \mathbf{F}_S(y) - \mathbf{g}(x - e)u$ . Equation 4.12 can be written in affine form as:  $\dot{\mathbf{X}} = \mathbf{F}(X) + \mathbf{G}(X)u$ , where  $\mathbf{X} = [x, e]^T$ ,  $\mathbf{F}(X) = [\mathbf{F}_M, \mathbf{F}_M - \mathbf{F}_S]^T$  and  $\mathbf{G}(X) = [\mathbf{0}, -\mathbf{g}(x - e)]^T$ .

$$\mathbf{F} = \begin{bmatrix} \alpha(x_2 - x_1) \\ \beta x_1 - x_2 - x_1 x_3 \\ x_1 x_2 - \gamma x_3 \\ \alpha(e_2 - e_1) \\ \beta e_1 - e_2 + e_1 e_3 - e_1 x_3 - x_1 e_3 \\ -e_1 e_2 - \gamma e_3 + e_1 x_2 + x_1 e_2 \end{bmatrix}$$

(4.13)

$$\mathbf{G} = \begin{bmatrix} 0 \\ 0 \\ 0 \\ -g_1(x-e) \\ -g_2(x-e) \\ -g_3(x-e) \end{bmatrix}$$

(4.14)

In order to achieve complete synchronization, conditions of Theorem 4.3 will be considered. Because subsystem Equations 4.11 has three state variable so k = 1, ..., 3 then,  $C_1(x, e)$ ,  $C_2(x, e)$  and  $C_3(x, 0)$  has to be calculated. The distributions are  $C_1(x, e) =$  $span\{G\}$ ,  $C_2(x, e) = span\{G, ad_FG\}$  and  $C_3(x, e) = span\{G, ad_FG, ad_F^2G\}$ . By choosing  $G = [0 \ 0 \ 0 \ -g_1 \ -g_2 \ -g_3]^T$  with  $g_1, g_2$  and  $g_3$  as constants. In order to obtain  $C_2(x, e)$  and  $C_3(x, e)$ , at first  $C_1(x, e)$  has to be written down as follows:

$$\mathbf{C}_{1}(x,e) = span \left\{ \begin{bmatrix} 0\\0\\0\\-g_{1}\\-g_{2}\\-g_{3} \end{bmatrix} \right\}$$

(4.15)

In order to find  $C_2(x, e)$ ,  $ad_F G = [F, G]$  should be calculated. From Definition 4.3,  $ad_F G$  can be written as follows:

$$ad_F \mathbf{G} = [\mathbf{F}, \mathbf{G}] = \frac{\partial \mathbf{G}}{\partial \mathbf{X}} \cdot \mathbf{F} - \frac{\partial \mathbf{F}}{\partial \mathbf{X}} \cdot \mathbf{G}$$

(4.16)

The term  $\frac{\partial \mathbf{G}}{\partial \mathbf{X}} \cdot \mathbf{F} = 0$  because **G** is constant vector. So Equation 4.16 turns into simpler form such that

$$ad_F \mathbf{G} = [\mathbf{F}, \mathbf{G}] = -\frac{\partial \mathbf{F}}{\partial \mathbf{X}} \cdot \mathbf{G}$$

(4.17)

So as to find  $ad_F \mathbf{G}$ ,  $\frac{\partial \mathbf{F}}{\partial \mathbf{X}}$  can be calculated as in Equation 4.18

$$\frac{\partial \mathbf{F}}{\partial \mathbf{X}} = \begin{bmatrix}

-\alpha & \alpha & 0 & 0 & 0 & 0 \\

(\beta - x_3) & -1 & -x_1 & 0 & 0 & 0 \\

x_2 & x_1 & -\gamma & 0 & 0 & 0 \\

0 & 0 & 0 & -\alpha & \alpha & 0 \\

-e_3 & 0 & -e_1 & (\beta + e_3 - x_3) & -1 & (e_1 - x_1) \\

e_2 & e_1 & 0 & (x_2 - e_2) & (x_1 - e_1) & -\gamma

\end{bmatrix}$$

(4.18)

Multiplying Equation 4.18 by  $-\mathbf{G}$  then  $ad_F\mathbf{G}$  can be obtained easily as in Equation 4.19