# Timing-Constrained Global Routing with RC-Aware Steiner Trees and Routing Based Optimization

#### DISSERTATION

ZUR

Erlangung des Doktorgrades (Dr. rer. nat.)

MATHEMATISCH-NATURWISSENSCHAFTLICHEN FAKULTÄT DER

RHEINISCHEN FRIEDRICH-WILHELMS-UNIVERSITÄT BONN

VORGELEGT VON

Rudolf Scheifele

AUS

Dresden

Bonn, März 2019

# Angefertigt mit Genehmigung der Mathematisch-Naturwissenschaftlichen Fakultät der Rheinischen Friedrich-Wilhelms-Universität Bonn

Gutachter: Prof. Dr. Jens Vygen

Gutachter: Prof. Dr. Stephan Held

Tag der Promotion: 7. Juni 2019

Erscheinungsjahr: 2019

## Acknowledgements

At this point I want to express my gratitude to my supervisor Professor Dr. Jens Vygen for his excellent guidance and valuable feedback. I also want to thank Professor Dr. Dr. h.c. Bernhard Korte for providing great working conditions at the Research Institute for Discrete Mathematics in Bonn.

Also, my thanks goes to my present and former colleagues for the friendly working atmosphere and productive collaboration in the past few years. In particular, I want to thank Dr. Dirk Müller for introducing me to BonnRouteGlobal and its implementation, Tilmann Bihler and Pietro Saccardi for the close collaboration on BonnRouteGlobal and for dealing with most of the matters concerning BonnRouteGlobal during the final periods of writing this thesis, and Markus Ahrens, Dr. Michael Gester and Niko Klewinghaus for their great work on BonnRouteDetailed. Furthermore, I am thankful to Siad Daboul, Professor Dr. Stephan Held, Anna Hermann, Daniel Rotter and Ulrike Schorr from the timing optimization team for their collaboration and help on timing related topics.

Further thanks goes to a number of people at IBM, especially Karsten Muuss, Dr. Sven Peyer and Dr. Christian Schulte from the routing team for the successful collaboration on BonnRoute in the last years, and Michael Kazda and Alexander Suess for the productive teamwork on the BonnRoute based optimization flow presented in this thesis.

Finally, my personal thanks goes to my parents Erika and Gustav, my sisters Anna and Edith, and my grandparents Christian and Pauline for all the support and encouragement they have given me throughout my whole life.

## Contents

| Acknowledgements |                                                    |    |  |  |  |

|------------------|----------------------------------------------------|----|--|--|--|

| Chapte           | er 1. Introduction                                 | 7  |  |  |  |

| 1.1.             | Specification and Logic Design                     | 8  |  |  |  |

| 1.2.             | Physical Design                                    | 10 |  |  |  |

| 1.3.             | Routing                                            | 13 |  |  |  |

| 1.4.             | 1.4. Thesis Overview                               |    |  |  |  |

| Chapte           | er 2. Global Routing Basics                        | 27 |  |  |  |

| 2.1.             | Basic Concepts and Definitions                     | 27 |  |  |  |

| 2.2.             | The Traditional Global Routing Problem             | 32 |  |  |  |

| 2.3.             | The Minimum Steiner Tree Problem                   | 35 |  |  |  |

| Chapte           | er 3. VLSI Timing Basics                           | 39 |  |  |  |

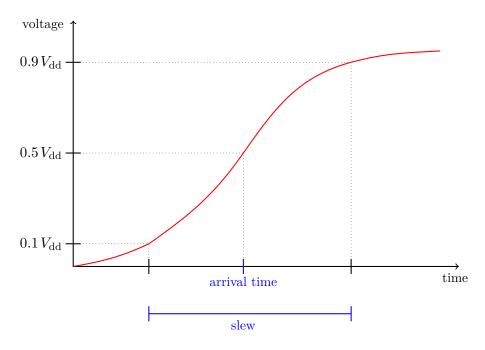

| 3.1.             | Signals                                            | 39 |  |  |  |

| 3.2.             | The Timing Graph                                   | 39 |  |  |  |

| 3.3.             | Timing Constraints                                 | 40 |  |  |  |

| 3.4.             | The Elmore Delay Model                             | 42 |  |  |  |

| 3.5.             | Slew and Capacitance Limits                        | 46 |  |  |  |

| Chapte           | er 4. Global Routing with Timing Constraints       | 47 |  |  |  |

| 4.1.             | Previous Work                                      | 47 |  |  |  |

| 4.2.             | Global Routing as Min-Max Resource Sharing Problem | 48 |  |  |  |

| 4.3.             | Incorporating Timing Constraints                   | 51 |  |  |  |

| Chapte           | er 5. The RC-Aware Routing Oracle                  | 63 |  |  |  |

| 5.1.             | Problem Formulation                                | 63 |  |  |  |

| 5.2.             | Previous Work                                      | 64 |  |  |  |

| 5.3.             | RC-Aware Paths                                     | 65 |  |  |  |

| 5.4.             | RC-Aware Steiner Trees                             | 76 |  |  |  |

| 5.5.             | Experimental Results                               | 86 |  |  |  |

6 CONTENTS

| Chapte  | r 6. Connecting to Exact Shapes    | 91  |

|---------|------------------------------------|-----|

| 6.1.    | From Projected to Exact Shapes     | 93  |

| 6.2.    | Optimizing x- and y-Coordinates    | 94  |

| 6.3.    | Assigning Layers                   | 96  |

| 6.4.    | Implementation in BonnRouteGlobal  | 114 |

| Chapter | r 7. Routing Based Optimization    | 115 |

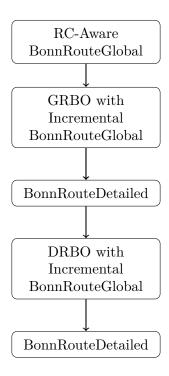

| 7.1.    | GRBO and DRBO                      | 116 |

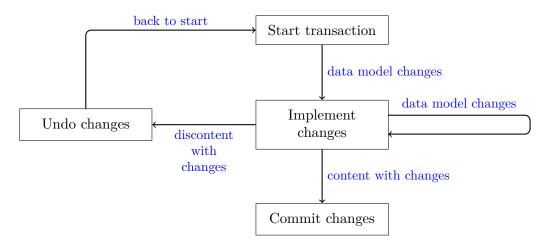

| 7.2.    | The Incremental Routing Framework  | 120 |

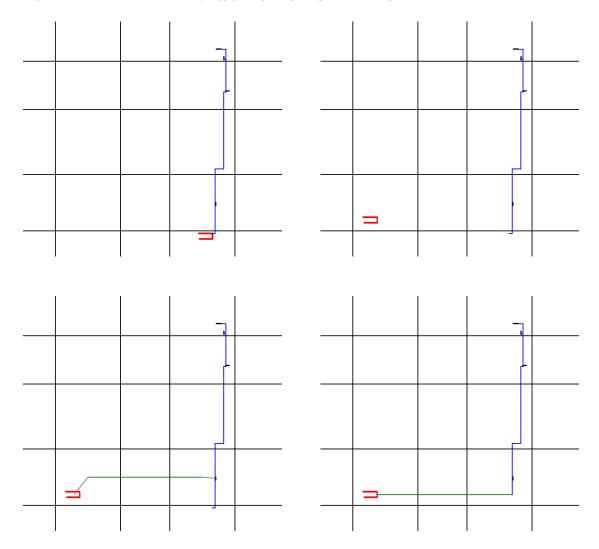

| 7.3.    | Minimal Reroutes                   | 123 |

| 7.4.    | Copy Routes                        | 143 |

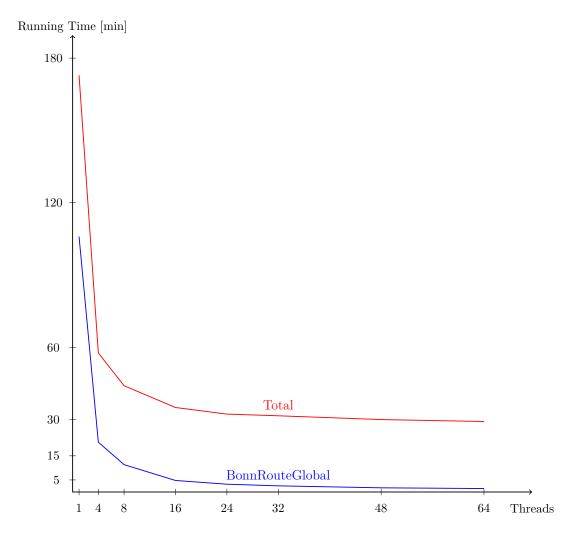

| 7.5.    | Multi-Threaded Incremental Routing | 161 |

| 7.6.    | Routing Flow Results               | 175 |

| Append  | lix A. Experimental Results        | 181 |

| A.1.    | Our Testbed                        | 181 |

| A.2.    | Our Platform                       | 181 |

| A.3.    | Metric Evaluation                  | 181 |

| A.4.    | Metrics                            | 181 |

| Append  | lix. Summary                       | 185 |

| Append  | lix. Bibliography                  | 187 |

#### CHAPTER 1

### Introduction

In today's world, computer chips are omnipresent and indispensable. They can be found in traditional computers, phones, cars and many other devices that are essential to modern living. Naturally, this need for computer chips creates a highly competitive market, and the usual objectives include making chips faster, smaller, less power consuming and less expensive to produce. As a result, modern computer chips are highly complex structures consisting of up to billions of interconnected transistors. Therefore, the VLSI design process used to create these modern computer chips is very sophisticated and requires contributions from many research areas.

In this thesis we are concerned with global routing, which is part of the VLSI routing step, whose task is to compute the layout of the wires on the chip. We present new theoretical results that are implemented and evaluated in practice. The underlying routing tool for implementing our results is BonnRoute [41], the routing tool of the BonnTools program suite [73] developed at the Research Institute for Discrete Mathematics in Bonn. BonnRoute is the main routing tool used by IBM during the design of processor chips that are among the fastest and most complex in the world and can therefore be considered as successful state-of-the-art router.

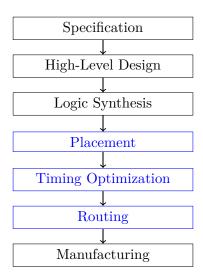

To introduce some VLSI design concepts and terminologies and to get a better understanding of the context in which global routing takes place, we outline a strongly simplified VLSI design flow in this introductory chapter. This flow is depicted in Figure 1.1 and explained in more detail in the remainder of this chapter. As it is not an essential part of this thesis, we omit any description of the manufacturing step. A more extensive introduction to VLSI design is given by Uyemura [115] and many other textbooks.

Throughout this thesis we assume that the reader is acquainted with basic concepts and terminologies in mathematics and computer science, in particular in the field of combinatorial optimization. For an introduction to combinatorial optimization, the reader is referred to the textbook by Korte and Vygen [75] or other textbooks on that topic. For examples of combinatorial optimization problems arising in VLSI design see Held et al. [52] and Korte and Vygen [74].

FIGURE 1.1. A strongly simplified VLSI design flow. The steps colored in blue constitute the physical design step.

In Section 1.1 we give a brief overview on logic design, in particular the output of this step that serves as input for physical design. We then turn towards physical design in Section 1.2, but only describe placement and timing optimization in this section. The last step, routing, is covered in Section 1.3, as it is the most important one for this thesis. At last, Section 1.4 contains a preview of the contents of this thesis.

#### 1.1. Specification and Logic Design

The starting point of the VLSI design process is a system specification, where the functionality of the product and design goals are defined. These specifications are then encoded during high-level design in a hardware description language (HDL), which is a computer language similar to a programming language that is used to describe the structure of an electronic circuit. The most commonly used HDLs at this point in time are VHDL and Verilog. This abstract description of the circuit is then translated by a logic synthesis tool into a netlist, which contains the set of circuits of the chip and the logical connectivity information that controls the signal flow. As logic synthesis is not the focus of this thesis, we leave it at that very brief description and refer the reader to [30, 33, 48] for more on this topic.

Instead, we focus our attention on the output of logic synthesis for the remainder of this section, as the output of logic synthesis constitutes (part of) the input for physical design. We introduce circuits and books in Section 1.1.1, pins in Section 1.1.2 and the netlist in Section 1.1.3. These are logical concepts in the sense that they are used to describe

the logic of the chip, but as these logical concepts must be implemented physically later, they are of course also central to physical design.

1.1.1. Circuits and Books. A circuit consists of multiple interconnected transistors and either represents a boolean function, in which case it is called a gate, or is a memory element, also called a register. Most gates compute an elementary boolean function like NAND and NOR, but also more complex boolean functions are possible. Memory elements are controlled by periodic clock signals and are used to store information at one point in time and release it later.

Although it would be theoretically possible to design chips on a transistor level, this is usually not done on a large scale due to the complexity involved. Instead, there is a predefined *library* containing *books*, which are blueprints for the physical implementation of specific circuits. When a circuit with a given functionality is required, a book implementing this functionality can just be taken from the library. As there are often multiple books with different physical properties available for implementing the same logic, picking the right books is a difficult optimization problem. However, this problem is not tackled during logic design, but later during timing optimization (cf. Section 1.2.2). For more on transistor-level layout and library design we refer to Cremer [31], Hougardy et al. [58] and Schneider [109].

1.1.2. Pins. The interface between a circuit and the chip it belongs to is given by the pins of the circuit. Each circuit contains a set of input pins and a set of output pins: Input signals for gates are received at the input pins, and the results of the boolean functions computed are present at the output pins. Likewise, signals to be stored in registers are present at their input pins, and signals to be released by registers are present at their output pins. Here, at any given point in time we associate each pin with one of two voltage levels  $V_{ss} < V_{dd}$  representing the logical values zero and one. A signal can then be regarded as a voltage change at a given pin, as it is explained in more detail later in Section 3.1. Since the input pins of a circuit are receiving signals and the output pins are distributing signals, we classify the former as sink pins and the latter as source pins.

In addition to circuit pins, the chip also contains a set of pins which constitute the interface to the exterior context in which the chip is used. These are called *primary input* and *primary output* pins, and are classified as source and sink pins, respectively. Note that while input pins of circuits are sink pins, primary input pins are source pins, with an analogous statement holding for output pins of circuits and primary output pins. In fact, the chip itself can be considered as a circuit, and if viewed from the inside, a primary input pin has the role of distributing input signals, while a primary output pin has the role of receiving output signals.

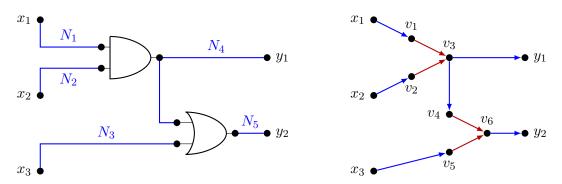

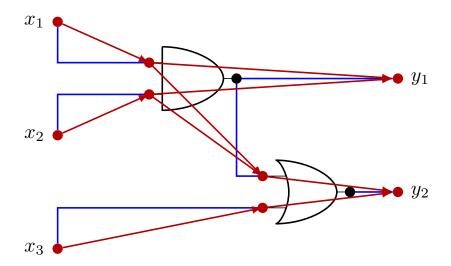

FIGURE 1.2. Left: A simple netlist with five nets  $N_1, \ldots, N_5$ , input signals  $x_1, x_2, x_3$  and output signals  $y_1, y_2$ . The boolean functions computed are  $y_1 = x_1 \wedge x_2$  and  $y_2 = (x_1 \wedge x_2) \vee x_3$ . Right: The corresponding netlist graph. We have vertices  $x_1, x_2, x_3$  for the primary input pins,  $y_1, y_2$  for the primary output pins and  $v_1, \ldots, v_6$  representing circuit pins. Edges corresponding to nets are shown in blue while circuit internal edges are shown in red.

1.1.3. The Netlist. Logical connectivity information is encoded by nets: A net is a set of pins that contains exactly one source pin and at least one sink pin. In this context, we often call the source pin of the net — and sometimes also the circuit this source pin belongs to — the driver of the net. Moreover, every pin on the chip belongs to exactly one net. The set of nets is then called the netlist, and it is often associated with a netlist graph. The netlist graph is an acyclic digraph G = (V, E) whose edge directions indicate signal flow: V is the set of pins on the chip, and there is an edge  $(v, w) \in E(G)$  if v is the source pin of the net containing w, or if v and w are input and outpin pins of the same gate. A very simple example of a netlist and its corresponding netlist graph is shown in Figure 1.2.

#### 1.2. Physical Design

The netlist computed by logic synthesis serves as input for the *physical design* step, where a detailed construction plan for physical components like wires and transistors is computed. In addition to the netlist, the input for the physical design step includes the rectangular chip area, the number of available chip layers and the locations of primary input and output pins. We assume the lowest layer to be the *placement layer* containing all transistors, while we assume all other layers to be *routing layers* containing wires connecting the nets. Our simplified physical design flow from Figure 1.1 consists of three steps: *placement*, *timing optimization* and *routing*. This is only a very brief and simplified description of physical design — a more comprehensive overview on physical design and the algorithms used in it is given by Alpert et al. [5].

We describe placement in Section 1.2.1 and timing optimization in Section 1.2.2. As the routing step is central to this thesis, we cover it in its own section, namely Section 1.3.

1.2.1. Placement. During placement, circuits are placed non-overlapping on the chip area such that objectives like timing and wire length are optimized. There are different types of placement problems: During floorplanning, a relatively small number of large circuits is to be placed. These can be smaller chips contained in a top level chip when hierarchical design is used, or other predesigned structures like intellectual property blocks designed by another company. On the other hand, during standard cell placement, all circuits classified as standard cell are placed. Here, a cell is a standard cell if it has some fixed uniform height. This height is defined by the distance of power supply stripes, called *power rails*, which are arranged in a regular pattern across the placement layer and also some routing layers of the chip. The standard cell height is then the maximum height that makes it possible to place the cell between two adjacent power rails. Floorplanning and standard cell placement can be done combined or separately. A third placement problem is the placement legalization problem, where an infeasible (i.e. not overlap-free) placement is given and the task is to compute a feasible placement that is close to the input placement. The placement legalization problem occurs continually during timing optimization and therefore also during our routing based optimization flow from Chapter 7.

All circuits (including large units placed during floorplanning) are placed on the placement layer, but they might also occupy space on routing layers. This occupied space is seen as blockage by the router. Large units might occupy a lot of space even on higher layers, while standard cells only block a small amount of space on the lowest layers. Throughout this thesis we assume that a feasible placement is given in the input for routing and do not examine this problem any further. For a comprehensive overview on the placement problem the reader is referred to Alpert et al. [5], Brenner et al. [20] and Struzyna [114].

- 1.2.2. Timing Optimization. After placement has finished, timing optimization takes place. The main task in timing optimization is to ensure that all signals arrive in the correct time window so that the chip can operate at the desired frequencies if the result of logic synthesis and placement was to be routed directly, meeting timing constraints would be impossible for all but the simplest designs. There are several operations which can be performed during timing optimization, including (but not limited to) the following:

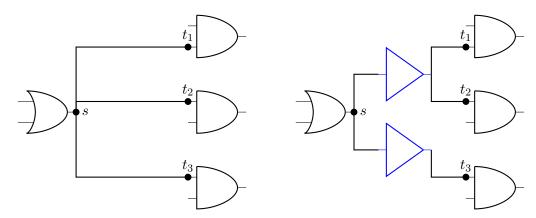

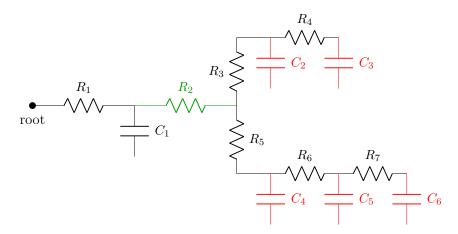

- Buffering: As will become evident after looking at the Elmore delay model [35, 99] from Section 3.4, long nets and nets with many pins must be subdivided into

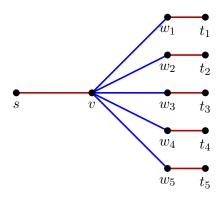

FIGURE 1.3. The net  $\{s, t_1, t_2, t_3\}$  (left) is subdivided into three nets by insertion of two buffers (right).

smaller nets in order to avoid excessive signal delays. This is done by inserting buffers or a suitable number of inverters, which implement the identity and NOT function, respectively. For simplicity, we only use the term buffer to cover buffers and inverters for the rest of this thesis.

The buffering problem involves two major subproblems: The first one, buffer insertion, consists of inserting buffers into the netlist, usually based on the structure of some routing tree given for a certain net. The second one, buffer tree generation, consists of computing the routing tree that is used for buffer insertion. While buffer insertion can be performed on an estimated routing tree, it is more accurate to combine global routing and buffering, as was done by Rotter [97]. Further references regarding buffering include Bartoschek [8] and Hu et al. [60]. A simple illustration of the buffering process is given by Figure 1.3.

- Gate sizing: The library (cf. Section 1.1.1) usually contains multiple books implementing the same boolean function, but having largely different electrical properties. The electrical properties roughly correlate to the size of the book: Larger books have a lower internal resistance and switch faster on their own, but consume more area and power and have bigger input pins that slow down predecessor nets. The task in gate sizing is to pick a suitable book for each gate (or circuit) in the netlist, as the netlist output by logic synthesis is logically correct, but not well optimized with respect to gate sizes. An overview on the gate sizing problem is given by Held and Hu [51] and Schorr [110].

- Vt optimization: The voltage threshold, or Vt level, denotes the voltage at which a transistor switches. A lower Vt level results in faster switching and therefore faster signal propagation, but it also increases power consumption.

1.3. ROUTING 13

There are usually a few different Vt levels available for each book, and the task in Vt optimization is to pick one for each circuit to improve timing without increasing power consumption too much. For more on Vt optimization see Daboul et al. [32] and Schorr [110].

- Local placement changes: Although timing is considered as major objective during placement, one can often improve timing further by deploying additional local placement changes later in the flow. Here, "local" can refer to moving only local parts of the netlist, e.g. a single circuit, but can also entail restricting changes to a local area. A method for improving timing with local placement changes is given by Bock et al. [14].

- Local logic restructuring: The netlist output by logic synthesis is logically correct, but may not be optimal with respect to timing behavior. This is particularly true as the timing of the chip is strongly influenced by placement and timing optimization, and both these steps are running after logic synthesis in the flow. Therefore, logic restructuring can be applied to improve timing. As the problem of deciding whether two netlists are logically equivalent contains the 3-SAT problem and is therefore NP-hard, very complex changes are usually avoided. For more on local logic restructuring see Held and Spirkl [55] and Werber [121].

The above steps are interrelated in the sense that to give meaningful input to one step, the other steps must already have been performed to a reasonable degree. For this reason, better results can be obtained if different timing optimization steps are combined and iterated during the course of the physical design flow. Held [50] covers several aspects of timing optimization in more detail.

As already indicated by the above description of the individual timing optimization steps, there is often a trade-off between improving timing and keeping power consumption in check. Routability also has to be considered during timing optimization. This is usually done by using various kinds of routability estimates ranging from rather simple estimates incorporated in the timing optimization tools to more accurate estimates given by a global router. An accurate method to estimate routability and timing properties of wires is given in Chapter 7, where we deal with routing based optimization, i.e. a method to perform timing optimization based on a routing that is incrementally updated by our global router.

#### 1.3. Routing

The final step in our simplified physical design flow is routing. We start with routing basics in Section 1.3.1, continue with global routing — the main focus of this thesis — in

Section 1.3.2 and then introduce track assignment and detailed routing in Sections 1.3.3 and 1.3.4, respectively. Our description of the various routing steps is tailored to Bonn-Route. Most of it should be generally applicable, but for other routers, individual details may vary. An improvement of the routing step that is not discussed in this introductory chapter is routing based (timing) optimization. We discuss this in detail in Chapter 7.

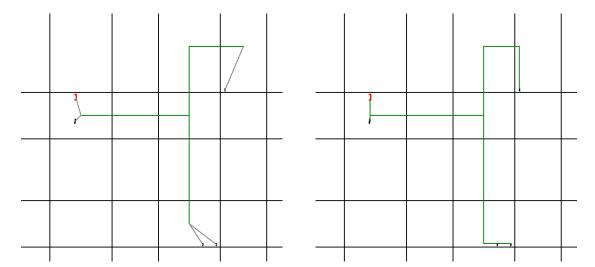

1.3.1. Routing Basics. The basic task in routing is to connect the pins of each net by metal wires, i.e. realizing the logical connectivity of the netlist by a physical implementation. These metal wires are always extending in x- or y-direction — they are never running diagonal. In principle, diagonal wiring could be used to obtain better routing solutions, but this would complicate manufacturing and physical design considerably. Wires are arranged in wiring layers, which are located above the placement layer. Different wiring layers are separated from each other by insulating material, but metal holes called vias can be cut into the insulating material to establish electrical connectivity between different wiring layers. For this reason, the layers between wiring layers are called via layers.

A central constraint for routing is that wires and vias of different nets have to obey certain minimum distance rules: If wires or vias of different nets are placed too close to each other, then this can very likely result in a short after manufacturing, rendering the chip useless. To allow for a better packing of wires, one uses the concept of preference directions: Each wiring layer has a preference direction that is either horizontal or vertical, and the large majority of the wiring on that layer will extend into that direction. Depending on the layer and the technology, wires running orthogonal to the preference direction of the layer (called jogs) may or may not be allowed. However, they should be used sparingly, as they can be a barrier for many other wires running in preference direction. For the sake of a simpler description we assume for the rest of this section that jogs are not allowed. Naturally, adjacent routing layers have different preference directions in current technologies.

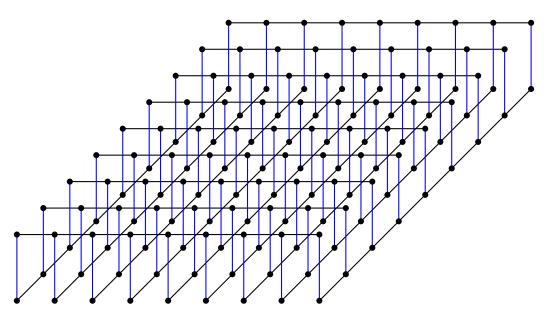

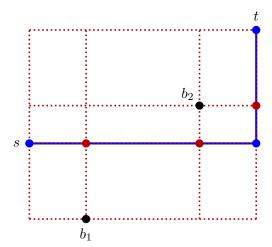

It is natural (but not mandatory) to use a graph model for solving the routing problem. The underlying graph is called  $track\ graph$ , as it is based upon  $routing\ tracks$ : On each layer, tracks extending into the preference direction of the layer are spanned over the chip area. At each point where x- and y-coordinates of two different tracks on adjacent layers coincide, vertices are added to the track graph on both layers, and both these vertices are connected by an edge representing a possible via position. Neighboring vertices on the same track and same layer are also connected by an edge. If some edges are not usable for the router (e.g. due to routing blockages), then these edges can be omitted when constructing the track graph. An illustration of the track graph is given by Figure 1.4.

1.3. ROUTING 15

FIGURE 1.4. Illustration of a track graph with two routing layers. Blue edges correspond to vias, while black edges correspond to wires.

The distance between neighboring tracks, called *track pitch*, is naturally chosen as the minimum distance such that two minimum width wires can be placed on neighboring tracks without causing a minimum distance rule violation. Here, the track pitch is not the same on every layer. It is generally larger on higher layers in order to accommodate thicker wires with better electrical properties. Modeling minimum distance rules through the construction of the track graph is more or less simple as long as only minimum width wires with minimum spacing requirements are used, but the router must also be able to deal with wires of different *wire types*, which define the exact geometries and spacing requirements of wires and vias on different layers.

Using the track graph, a simplified version of the routing problem can be formulated as a Steiner tree packing problem in graphs: Each pin corresponds to a vertex (or a set of vertices) in the track graph, and the wiring of a net is represented by a Steiner tree connecting the pins. Steiner trees of different nets must be vertex-disjoint in order to avoid violations of minimum distance rules. From a theoretical perspective, vertex-disjoint packing of Steiner trees in grid graphs is NP-complete [76, 77]. In practice, the routing problem is complicated further by the following factors:

• Complex minimum distance rules: The construction of the track graph does not ensue complete adherence to minimum distance rules, e.g. when different wire types are used. There are also specific spacing rules for vias. This makes compliance to minimum distance rules more difficult.

- Complex same-net rules: In addition to minimum distance rules, which are concerned with shapes of different nets or blockage shapes, there are also rules prescribed for the routing of a single net, called same-net rules. An example for such a rule is the minimum area rule, which dictates that any connected component of wiring on a given wiring layer must cover a certain minimum area. Some same-net rules can be hard or runtime-intensive to incorporate into an automatic routing tool. For instance, the above mentioned minimum area rule will in general not be followed when a standard path search algorithm (e.g. Dijkstra's algorithm [34]) is run on the track graph to connect two points. As outlined by Gester [40] (Section 5.4.2), many same-net rules can be incorporated into a path search algorithm by propagating multiple labels, but this usually results in a significant running time increase.

- The graph is huge: As the track pitch is very small compared to the size of the chip, the track graph can become huge. This results in track graphs with billions of vertices where millions of Steiner trees have to be packed. Therefore, running time is always a critical factor and naive approaches are most often not feasible.

The set of rules, called *design rules*, is primarily given by the foundry with the goal of preventing manufacturing problems. Usually, the number of design rule violations should be zero at the end of the physical design phase, but in some cases a few non-fatal violations might be tolerated, although this can have a negative impact on the manufacturing yield. For more on design rules in VLSI routing see Schulte [111].

On instances occuring in practice it is usually hard to find any routing solution that closes all connections while satisfying the given design rules. However, finding any routing solution is not good enough for the design of high-performance chips. In particular timing, power consumption and manufacturing yield are strongly influenced by the routing result and should be optimized accordingly. Incorporating these objectives makes the routing problem even harder. In this thesis we mainly deal with the optimization of timing during routing.

Due to the complexity involved, the routing task is usually split into two or even three major steps. The first of these steps is global routing, and it is the main focus of this thesis. The second step, track assignment, is optional, and the third step is detailed routing. We describe these three routing steps in the following sections.

1.3.2. Global Routing. Due to the inherent complexities of the routing problem outlined in Section 1.3.1, trying to solve it by packing Steiner trees directly in the track graph without any preparations is most likely futile. To this end, *global routing* is performed as the first step in the routing process: During global routing, a rough

1.3. ROUTING 17

layout called *global route* or *global wires* is computed for the routing of every net, which is then used as a guidance for the later routing steps to compute the actual detailed routing. To make this process feasible, design rules are only modeled indirectly and in a strongly simplified manner during global routing. Moreover, global routing takes place on a coarsened and much smaller version of the track graph, called the *global routing graph*. This central data structure is introduced in Section 1.3.2.1. In Section 1.3.2.2 we touch the subject of estimating global routing capacities and discuss global routing objectives in Section 1.3.2.3. Finally, we deal with the consideration of timing during global routing in Section 1.3.2.4. In this chapter we describe global routing in a rather descriptive and informal way. Formal definitions are given later in Chapter 2.

Global routing has many different applications during physical design — for example, it can be used to evaluate routability during placement and timing optimization, and it can be interwoven with the buffering step. In this thesis, we are only concerned with global routing as a preparation for track assignment and detailed routing, although part of the results from this thesis can certainly also be applied in other contexts.

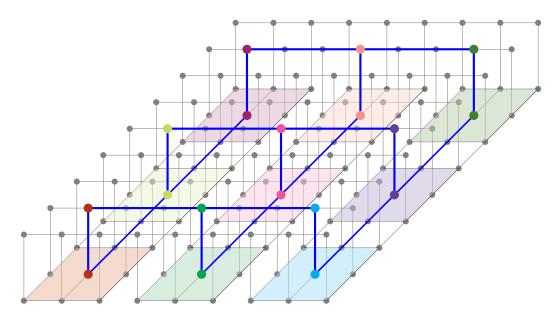

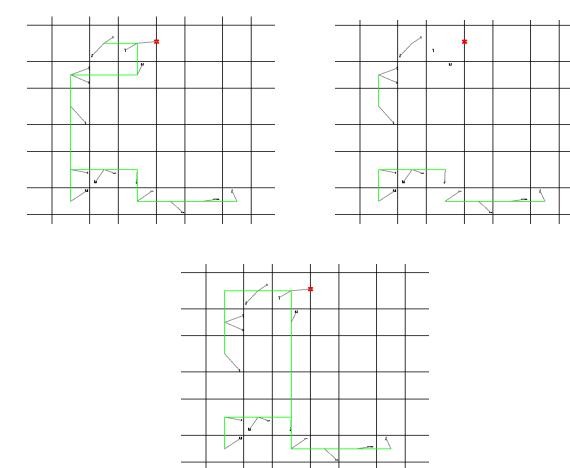

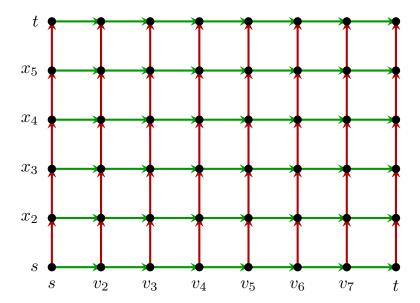

1.3.2.1. The Global Routing Graph. The global routing graph is constructed as depicted in Figure 1.5: First, the chip area  $[x_{\min}, x_{\max}] \times [y_{\min}, y_{\max}]$  is subdivided into a grid of rectangular global routing tiles through sequences  $x_{\min} = x_0 < x_1 < \ldots < x_n = x_{\max}$  and  $y_{\min} = y_0 < y_1 < \ldots < y_m = y_{\max}$  of x-cuts and y-cuts, which define the boundaries of the global routing tiles. This divides the chip area into mn rectangular regions, and all vertices of the track graph that are located in the same region and on the same layer are contracted into a single vertex. Via edges are then added between vertices corresponding to the same region on adjacent layers, and wiring edges extending into the preference direction of the layer are added between vertices corresponding to neighboring regions on the same layer. Wiring edges orthogonal to the preference direction of the layer are not added, as jogs should be short and therefore negligible during global routing. A formal definition of the global routing graph is given later by Definition 2.8.

The size of the global routing graph is determined by the size of the track graph and the sets of x- and y-cuts. Therefore, there is a trade-off between running time and precision: Fewer cuts result in a smaller graph and therefore presumably less running time, but may also result in a loss of precision. The cuts can be chosen to be equidistant, and the distance may be increased on large designs to reduce the size of the global routing graph. However, it can be beneficial to choose non-equidistant cuts, e.g. in order to align global routing tiles with large blockages, as these can cause inaccuracies in the global routing model, in particular when running through a tile. Non-equidistant cuts are used in BonnRoute [42], and they are implemented in such a way that the distance

FIGURE 1.5. Construction of the global routing graph from the track graph from Figure 1.4: Vertices of the track graph (gray) that are located in the same global routing tile (colored rectangles) and on the same layer are contracted into a single vertex in the global routing graph (colored as its tile area). The vertices of the global routing graph are then connected by via edges and wiring edges in preference direction of the given layer (blue).

between neighboring cuts does not deviate too much from some predefined value. In our experiments, we set this value to 70 times the minimum track pitch across all routing layers. One can see that in such a setting the global routing graph is significantly smaller than the track graph, but on large designs it can still have millions of vertices. For instance, the global routing graph on our largest design from Figure 1.6 contains around two million vertices, and we have to route around 1.6 million nets in it. Therefore, running time is a critical factor for any global routing algorithm.

1.3.2.2. Capacity and Routing Space Usage Estimations. In contrast to the track graph, an edge of the global routing graph does not represent part of a single routing track or a single possible via position. Instead, we associate with each edge of the global routing graph an amount of free routing space, which is called capacity of the edge. If we regard an edge of the global routing graph as a cut in the track graph, we can just define the capacity of the edge as the size of the cut. If all wires were very long, this would possibly be an acceptable model. However, in practice, this is usually not the case: Vias might connect non-adjacent layers and require only small pieces of metal on the intermediate wiring layers; pin access, local congestion and design rules might require

1.3. ROUTING 19

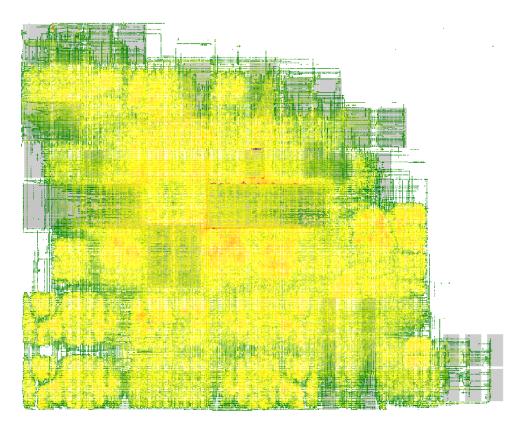

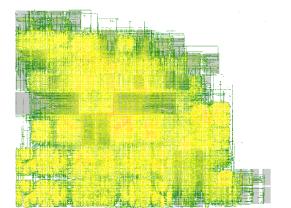

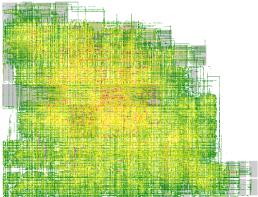

FIGURE 1.6. Congestion map of our largest unit U8. Every edge of this two-dimensional projection of the global routing graph is colored according to the maximum edge usage over all layers. The widespread yellow color indicates that congestion is a few percent below our congestion target of 90% for the most part, but some orange spots at 90% congestion exist. Around the borders of some large blockages there are a few dark-colored edges, which indicates routing overflow. Green and white regions are uncritical with respect to routing congestion.

the detailed router to make local detours; blockages and input wiring might locally block tracks; and in fact, on most designs many nets are so short that all their pins are in the same or neighboring global routing tiles.

All these things have to be considered during capacity estimation, making it a rather intricate problem in practice. Moreover, as the capacity estimation has to be tailored to the design rules and the detailed router that is used later, a fair amount of experimental studies and fine-tuning is needed to get good results.

Tightly connected to capacity estimation is the question of how to compute the routing space usage of a given wiring. In the standard model — the one that we are using

throughout this thesis — the routing space usage of a wire or via only depends on its dimensions and wire type, but not on other wires of the same or other nets.

In this thesis, we will not be particularly concerned with capacity estimation or routing space usage computations. Instead, we assume routing capacities and routing space usage functions as given. We refer the reader to Wei et al. [120] for an overview on the modeling of local congestion. They use a method where local congestion effects are estimated based on pin positions and estimated Steiner trees. On the other hand, an approach where local effects are estimated based on the local structure of the actual global routes is currently being implemented in BonnRouteGlobal, relying on the framework that we present in Chapter 6. At the time of this writing, this approach is in development for BonnRouteGlobal, but not yet usable for this thesis. An approach to compute global routing capacities based on maximum flows is given by Müller [84]. A comprehensive discussion of routing congestion is given by the book of Saxena et al. [105].

Any edge usage that exceeds its capacity is considered as routing overflow and should be minimized. In the simplest notion, a global routing solution is considered routable if there is no routing overflow. However, due to inaccuracies in the global routing model and capacity estimation and the inherent complexity in the subsequent detailed routing step, the question whether a given global routing will be sufficiently well routable by the detailed router is often not easy to answer in practice. Wei et al. [120] study the problem of routability prediction and establish global routing metrics that can be evaluated in order to predict the routability of a given global routing. They define the ACE metric, which basically represents the average congestion of the most congested edges (cf. Appendix A.4). Throughout this thesis, we use this metric in addition to the overflow metric to evaluate routability. Figure 1.6 shows a congestion map with a color scheme that represents edge usages.

1.3.2.3. Global Routing Objectives. The main objective during global routing is to output a global routing that represents routable input for track assignment and detailed routing. In that sense, producing a routable global routing, e.g. indicated by having zero routing overflow, can be regarded as a constraint. When that need is satisfied, one usually turns towards the optimization of objectives such as timing, power consumption and manufacturing yield.

The traditional objective here is to minimize total wire length and possibly via count, as for example indicated by the evaluation metrics of the ISPD 2007 and 2008 global routing contests [66, 67]. Minimizing total wire length can be understood as an indirect attempt to optimize other objectives such as timing and power consumption. It is also

<sup>&</sup>lt;sup>1</sup>In some applications for global routing, this might not be true. For the global routing preceding detailed routing, however, this is a reasonable conception.

1.3. ROUTING 21

pragmatical in the sense that minimization of wire length can be achieved by routing nets as minimum (rectilinear) Steiner trees, and the construction of approximately minimum Steiner trees is a classical optimization problem that has been studied long-since both from a theoretical and practical point of view (cf. Section 2.3).

The idea of modeling power minimization via wire length minimization during global routing stems from the fact that power consumption roughly correlates with total wire capacitance (assuming a fixed netlist), and this in turn correlates with total wire length. Here, improvements can be made by making use of the fact that wire capacitances differ (moderately) across the layer stack and by improving wire spreading. An approach to optimize power consumption during global routing is given by Vygen [117] and Müller, Radke and Vygen [87]. The important objective of satisfying timing constraints during global routing is covered in the next section.

1.3.2.4. Global Routing and Timing. When it comes to timing, then minimizing wire length correlates well with minimizing circuit delays, as these scale well with the capacitances of the nets that are driven by the output pins of the circuits. However, as the technology is advancing, wire delays are becoming increasingly important due to rapidly growing wire resistances [28]. Wire delay minimization, though, is not necessarily a byproduct of wire length minimization, as we see when discussing the choices of wire types and routing layers in Section 1.3.2.4.1 and routing topologies in Section 1.3.2.4.2. Moreover, balancing timing criticalities plays an important role in achieving good timing results, and, as Section 1.3.2.4.3 explains, it is not always covered well in traditional global routing frameworks. In this section we only provide a very short preview on the topic of considering timing during global routing. More details are then given in later chapters of this thesis that deal extensively with this topic.

1.3.2.4.1. Wire Type and Layer Assignments. In Section 1.3.1 we introduced wire types, which define the layer-dependent dimensions and spacing requirements of wires. The main reason to use width and spacing values that are larger than the minimum width and spacing imposed by manufacturing constraints is timing: Thicker wires have less resistance and more spacing means less (coupling) capacitance. This way, using wire types with larger metal widths or spacings can significantly improve signal delays, as will become evident when looking at the Elmore delay model from Section 3.4. To this end, the input to routing usually contains a wire type assignment, which assigns a wire type to every net.

For the same reason as a wire type assignment a so-called *layer assignment* is done: On modern metal stacks, the common wire widths, heights and spacings increase from lower to higher layers [119], which results in significant decreases of wire resistances on higher layers. Therefore, wire delay decreases when a net is routed on higher layers, unless the

wire length is too small and via delays outweigh the better electrical properties of the higher layers.

The task in layer assignment is to assign a contiguous layer range to each net with the intent that the router will predominantly use that layer range for routing the net, only deviating from it when it has to, e.g. for accessing pins. As wires on higher layers usually have better electrical properties, it is common to only specify a minimum allowed layer and set the maximum allowed layer to the maximum available layer of the chip.

Layer assignments are traditionally done by a timing optimization tool [6, 63, 119]. However, there are several difficulties and disadvantages inherent to this approach: Firstly, any layer assignment has to be congestion-aware, as assigning too many wires to the upper layers easily leads to overcongestion. This is usually achieved by having some sort of congestion estimation during the layer assignment step, but this congestion estimation can never be as accurate as the congestion information that the global router sees during the actual routing process. Secondly, the layer assignment step can usually only assign layers to a whole net, while it might actually be sufficient to make an assignment only for parts of the net (e.g. only wires close to the source, or only the connection to the critical sink). This can lead to a waste of routing resources. Thirdly, the layer assignment usually uses delay characteristics of estimated routing trees, and the actual tree computed by the router might diverge from the estimate.

We deal with this matter in Chapters 5 and 6: Our net router from Chapter 5 can inherently optimize Elmore delays and make good layer choices on its own. In Chapter 6 we also present a layer assignment algorithm that can assign individual wires of a fixed two-dimensional routing tree to individual layers, minimizing routing congestion and Elmore delays. As these approaches are directly integrated into our global routing algorithm, they do not suffer the disadvantanges of an external layer assignment step outlined above.

The above considerations also hold true for an externally created wire type assignment — it faces the same difficulties as an external layer assignment step. In this thesis, we are able to achieve better results by ignoring the input layer assignment during our net routing process, but we still adhere to the wire type assignment in the input. Generalizing the results from Chapters 5 and 6 to also include wire type assignments should be uncomplicated from a theoretical perspective. Working out a well-performing practical implementation is a possible task for the future.

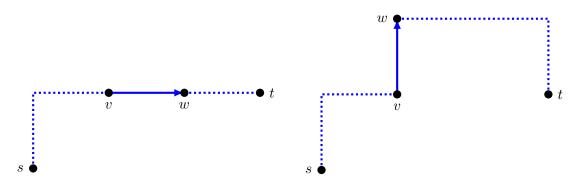

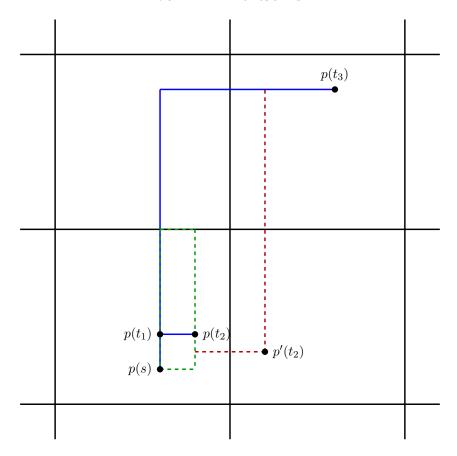

1.3.2.4.2. Routing Topologies. The routing topology can have a large impact on wire delays. Here, an intuitive insight is that wire delays depend on the source-sink path length, which is not necessarily minimized by minimum Steiner trees. However, as we will see when introducing the Elmore delay model in Section 3.4, source-sink path

1.3. ROUTING 23

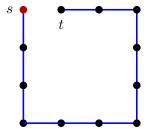

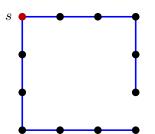

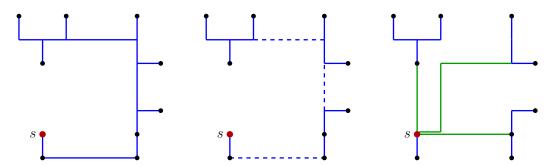

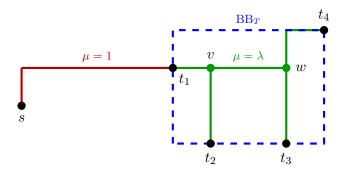

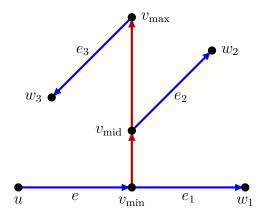

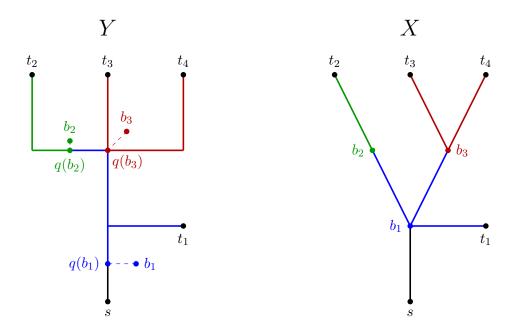

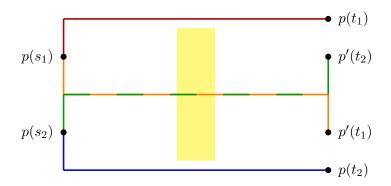

(a): A minimum Steiner tree with presumably bad delay properties due to long source-sink paths. The wire delay to t might be very large.

(b): Another minimum Steiner tree where all source-sink paths are shortest paths. Wire delays are better than in (a), but may still not be optimal.

(c): Depending on the instance parameters, this might be a better tree than (b) with respect to the very popular Elmore delay model. The tree is longer, but wire delays may be smaller due to less capacitance in some of the subtrees.

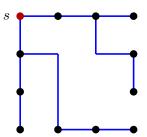

FIGURE 1.7. Three Steiner trees for the same net with very different delay properties. The source pin s is depicted by the red circle, while black circles depict sink pins.

length is not the only factor influencing wire delays. An illustration of this is given by Figure 1.7. More details on this topic and an algorithm to compute routing trees approximately minimizing Elmore delays are given in Chapter 5.

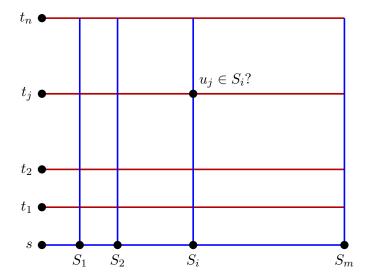

1.3.2.4.3. Timing Criticalities. Another reason why the approach of minimizing total wire length is not ideal for optimizing timing is that it does not distinguish between timing-critical and timing-uncritical nets. This can result in detours on timing-critical nets in favor of timing-uncritical nets. One attempt to alleviate this problem is to minimize the weighted sum of wire lengths over all nets, where more critical nets get higher weights. Another approach is to put constraints on the wire length of timing-critical nets, i.e. constraints that require the wire length to be within a certain factor of the length of an approximately minimum Steiner tree for the given net. Within the framework of wire length minimization, these measures are certainly useful and required for attaining good timing results. However, they still address the problem of optimizing timing during routing rather indirectly, and it is rather difficult to come up with a good set of such externally imposed constraints in advance. In this thesis, we present a better approach in Chapter 4, where we map out a global routing framework that can inherently model timing constraints and balance out timing criticalities during the course of global routing.

1.3.3. Track Assignment. Track assignment is an optional intermediate step between global and detailed routing, where the task is to assign long global wires to routing tracks. While the primary objective in track assignment is to assign as much wiring as possible, secondary objectives include optimization of wire length, timing and power consumption.

The wiring assigned by track assignment should obey most or all minimum distance rules, but it will probably not satisfy all same-net rules. However, if most of the long wires have been successfully assigned, the detailed router should subsequently be able to work mostly locally. This promises reduced detailed routing running times and an improved quality of results, as the track assignment step has a more global outlook on the routing problem than the detailed routing step.

In BonnRoute, the track assignment step is currently in development [88] and not included in the default routing flow. We therefore run all our experiments without track assignment. More details on the track assignment problem and heuristics to solve it are given by Batterywala et al. [9] and Chang and Cong [24].

1.3.4. Detailed Routing. The detailed routing step has to deal with most of the complexity of the routing step outlined in Section 1.3.1, as in this step the *detailed wires* that are later used for manufacturing are computed. However, this is done with the help of global routing and possibly track assignment: The usual approach here is to route one net after another and restrict the routing area for every net to an area encompassing the global routing for the net. This way only a small part of the track graph has to be considered when routing any given net, making the effective instance size for routing a single net manageable. At this point it becomes critical that the global router did not overuse routing capacities, and that the capacity estimation used by the global router was sound. Otherwise, detailed routing is likely to fail.

If the input from global routing is good, a well implemented ripup-and-reroute heuristic, i.e. an algorithm that routes nets sequentially with the possibility to rip out parts of previously routed nets (see e.g. Salowe [101]), is likely sufficient to produce a feasible detailed routing. If track assignment has successfully been run before detailed routing, then most long wires might already be in place, and the job of the detailed router might reduce to resolving local conflicts, accessing pins and fixing design rule violations.

Ripup-and-reroute is also implemented in BonnRouteDetailed, which is the detailed router that we use for our experiments throughout this thesis. BonnRouteDetailed uses an efficient implementation of Dijkstra's algorithm [34] as its path search algorithm and contains other techniques that improve running time and quality of results. In particular, BonnRouteDetailed does not only restrict the routing area for a net to a small area around the global wires, but also sticks to the topology of the global routing with only

local deviations [72]. This is particularly important in the context of timing-aware global routing, as global topology changes by a timing-unaware (or less timing-aware) detailed routing algorithm can negatively impact timing. For more on BonnRouteDetailed see Ahrens et al. [1], Gester et al. [41], Gester [40] and Schulte [111].

#### 1.4. Thesis Overview

After presenting this introductory material, we use this section to give a short overview on the contents of this thesis. In Chapter 2, we start with basic concepts and definitions in the context of global routing that are used throughout this thesis. It also presents the traditional way of formulating the global routing problem, which uses wire length minimization as objective. Chapter 3 then covers basic concepts of VLSI timing in a level of detail that is sufficient for the subsequent chapters. In particular, it introduces the Elmore delay model, which is the delay model that is used throughout this thesis. Chapter 4 describes our timing-aware global routing framework, i.e. a global routing framework that improves upon the traditional global routing framework from Chapter 2 by inherently modeling timing constraints. As a subroutine, this framework requires a timing-aware net router, i.e. in our case a net router that is able to minimize a weighted sum of congestion prices and Elmore delays. This net router is presented in Chapter 5. A refinement of the global routing model is then presented in Chapter 6: It outlines a process to convert a global route that is basically a subgraph of the global routing graph to a global route that is connecting exact pin and prewire shapes. It can be used for a more accurate modeling of e.g. timing and routing space usages during global routing. Moreover, Chapter 6 contains a layer assignment algorithm for minimizing a weighted sum of congestion prices and Elmore delays and is therefore an extension of the results from Chapter 5 in that regard. Finally, Chapter 7 presents the aforementioned routing based optimization step, which allows timing optimization to be performed on a fixed global or detailed routing that is incrementally updated by our global router in response to any changes introduced during timing optimization.

#### CHAPTER 2

## Global Routing Basics

In this chapter we describe basic global routing concepts. The contents of this chapter are closely related to the introductory material from Chapter 1, in particular Section 1.3.2, which introduces global routing and its purpose in VLSI design. In contrast to Chapter 1, which presents its contents in a rather informal way, we use this chapter to establish formal definitions and concepts that are then used in later chapters. We start with a collection of basic concepts and definitions in Section 2.1, introduce the Traditional Global Routing Problem in Section 2.2, and conclude this chapter with a discussion of the Minimum Steiner Tree Problem in Section 2.3.

#### 2.1. Basic Concepts and Definitions

This section provides a collection of basic concepts and definitions that are used throughout this thesis. It is primarily intended as a reference point when reading later chapters. We present a number of definitions regarding graphs. As a convention for this thesis, we usually give these definitions only for directed or undirected graphs. If the definition is trivially transferable to the other group of graphs, then it is also supposed to hold for them (unless explicitly stated otherwise). Moreover, we sometimes embed directed graphs into undirected graphs, or consider subgraphs of undirected graphs as directed based on some orientation of the edges. In the same manner, we sometimes laxly treat undirected graphs as if they were directed (also notation-wise), but the meaning should always be clear in the given context. We start our series of definitions with one regarding coordinates:

DEFINITION 2.1. For  $a \in \mathbb{R}^3$  and  $d \in \{x, y, z\}$  let  $a_d$  be the coordinate of a in dimension d.

We shortly introduce our notation to refer to neighbors of vertices in a graph:

DEFINITION 2.2. Let G be a directed graph and  $v \in V(G)$ . Then we define  $\Gamma_G(v) := \Gamma_G^+(v) \cup \Gamma_G^-(v)$  to be the neighbors of v, where  $\Gamma_G^+(v) := \{w \in V(G) : (v, w) \in E(G)\}$  and  $\Gamma_G^-(v) := \{u \in V(G) : (u, v) \in E(G)\}$ .

In general, we may leave out the graph subscript if it is clear from the context which graph is meant. The next definition deals with our notion of graphs and their embedding into the rectilinear space:

DEFINITION 2.3. Let  $S \subseteq \mathbb{R}^3$ . A graph G embedded rectilinearly into S is a graph G associated with vertex positions  $p \colon V(G) \to S$  such that for all  $(v, w) \in E(G)$  we have  $|\{d \in \{x, y, z\} : p(v)_d \neq p(w)_d\}| \leq 1$ . Given a graph G, a graph G embedded into G is a graph G associated with vertex positions  $g \colon V(H) \to V(G)$  such that  $(v, w) \in E(H) \Rightarrow (p(v), p(w)) \in E(G) \lor p(v) = p(w)$ . In that case, we define an extension  $g \colon E(H) \to E(G) \cup \{(v, v) : v \in V(G)\}$  by setting g(v, w) := (g(v), g(w)) for  $(v, w) \in E(H)$ . A graph structure that is not associated with vertex positions is called a topology.

Allowing adjacent vertices of H to be mapped to the same vertex in G is sometimes required to enforce a special structure for H. In the sense of Definition 2.3, a graph will always implicitly be associated with vertex positions p if this makes sense in the given context. When a graph H is embedded into a graph G, functions on V(G) and E(G) are extended naturally to H:

DEFINITION 2.4. Let H be a graph that is embedded into another graph G, and let  $f: V(G) \to X$  and  $g: E(G) \to Y$  for some sets X, Y be arbitrary functions. If not explicitly stated otherwise, then we implicitly extend f and g to H by setting f(v) := f(p(v)) for  $v \in V(H)$ , and g(v, w) := g(p(v), p(w)) for  $(v, w) \in E(H)$  with  $p(v) \neq p(w)$  and g(v, w) := 0 otherwise (assuming Y contains a zero element).

Usually, graphs will be embedded into the layered chip area:

DEFINITION 2.5. The *chip area* is given by a non-empty rectangle  $A := (x_{\min}, x_{\max}] \times (y_{\min}, y_{\max}] \subseteq \mathbb{R}^2$ . Given a non-empty set of layers  $Z := \{1, \ldots, n_z\}$  for some  $n_z \in \mathbb{N}$ , the *layered chip area* is defined by  $S := A \times Z$ .

The chip area in Definition 2.5 is defined half-open as a matter of convenience for subsequent definitions. We categorize the edges of a graph that is embedded rectilinearly into the chip area into two different classes:

DEFINITION 2.6. Let G be a graph that is embedded rectilinearly into the layered chip area. Then we partition  $E(G) := E_{\text{wire}}(G) \cup E_{\text{via}}(G)$ , where  $E_{\text{wire}}(G) := \{(v, w) \in E(G) : p(v)_z = p(w)_z\}$  is the set of wiring edges and  $E_{\text{via}}(G) := E(G) \setminus E_{\text{wire}}(G)$  is the set of via edges of G. If H is a graph that is embedded into G, then we set  $E_{\text{wire}}(H) := \{(v, w) \in E(H) : p(v, w) \in E_{\text{wire}}(G) \vee p(v) = p(w)\}$  and  $E_{\text{via}}(H) := \{e \in E(H) : p(e) \in E_{\text{via}}(G)\}$ .

We continue with pins and nets:

DEFINITION 2.7. Let S be the layered chip area. The set of pins on the chip is denoted by  $\Pi$  and characterized by a mapping  $p_{\text{ex}} \colon \Pi \to S$ , where  $p_{\text{ex}}(\pi)$  denotes the  $exact\ shape$  of  $\pi \in \Pi$ . The  $netlist\ \mathcal{N}$  consists of a set of nets such that  $\sqcup_{N \in \mathcal{N}} N = \Pi$ . Given a pin  $\pi \in \Pi$  we let  $N(\pi)$  denote the net containing  $\pi$ .

The netlist can be organized into a netlist graph as outlined in Section 1.1.3. In practice, pin shapes are not points, but rectilinear polygons. However, as they are usually small, modeling them as points as in Definition 2.7 is a reasonable simplification for our purposes. We now formally define the global routing graph, which has already been introduced in Section 1.3.2.1:

DEFINITION 2.8. Let  $S = (x_{\min}, x_{\max}] \times (y_{\min}, y_{\max}] \times \{1, \dots, n_z\}$  be the layered chip area. Given sequences  $x_{\min} = x_0 < x_1 < \dots < x_{n_x} = x_{\max}$  and  $y_{\min} = y_0 < y_1 < \dots < y_{n_y} = y_{\max}$  of real numbers representing x- and y-cuts for some  $n_x, n_y \in \mathbb{N}$ , the global routing tile with tile coordinate  $(i, j) \in \{1, \dots, n_x\} \times \{1, \dots, n_y\}$  is defined as  $A(i, j) := (x_{i-1}, x_i] \times (y_{j-1}, y_j]$ , and its tile center is the point  $p(i, j) := \left(\frac{x_{i-1} + x_i}{2}, \frac{y_{j-1} + y_j}{2}\right) \in A(i, j)$ . The global routing graph is a three-dimensional grid graph G with

- $V(G) = \{(i, j, k) : i = 1, \dots, n_x, j = 1, \dots, n_y, k = 1, \dots, n_z\},\$

- $E(G) = \left\{ \left\{ (i, j, k), (i', j', k') \right\} \in \binom{V(G)}{2} : |i i'| + |j j'| + |k k'| = 1 \right\}.$

With each vertex  $(i, j, k) \in V(G)$  we associate a vertex coordinate p(i, j, k) := (p(i, j), k) and a vertex area  $A(i, j, k) := A(i, j) \times \{k\}$ .

The reasoning behind Definition 2.8 is explained in Section 1.3.2. Usually, the global routing graph is defined to only contain wiring edges expanding into the preference direction of the given layer. We do not make this distinction in Definition 2.8, but instead assume that there is no available routing space for wiring edges not expanding into preference direction of the layer. When not stated differently in the given context, then G will refer to the global routing graph in this thesis. We note that when a graph H is embedded into the global routing graph G in the sense of Definition 2.3, then H may contain many Steiner vertices of degree 2. In practice, one would not store H in such a way, but allow a single long straight edge in H to correspond to multiple consecutive edges in G, potentially reducing the number of edges in H by a large amount. For simplicity of notation and presentation, however, we stick to the simpler way of embedding H into G given by Definition 2.3.

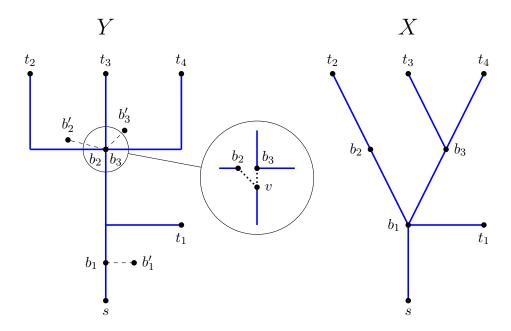

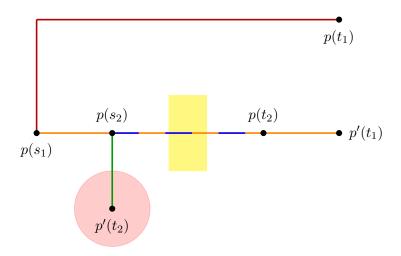

Traditionally, global routing is considered to output Steiner trees that are subgraphs of the global routing graph. Here, every pin on the chip is mapped to one vertex of the global routing graph based on the actual positions of its metal shapes. However, in the VLSI design flow where our global router is used, the global router must output Steiner trees that connect to the actual metal shapes of the pins, which are represented in a simplified manner as points by the exact pin shapes from Definition 2.7. Complementary to exact shapes, we define *projected pin shapes* that will be used predominantly during global routing:

DEFINITION 2.9. Let G be the global routing graph and  $\Pi$  be the set of pins. Projected pin shapes are defined by a mapping  $p_{\text{pr}} : \Pi \to V(G)$ . When it is clear from the context,  $p(\pi)$  for  $\pi \in \Pi$  either denotes  $p_{\text{ex}}(\pi)$  or  $p_{\text{pr}}(\pi)$ .

Most of the time  $p_{\rm pr}(\pi)$  is the vertex whose vertex area contains  $p_{\rm ex}(\pi)$ , but it is generally also possible to project pins to other vertices, e.g. neighboring vertices in cases where the capacity estimation is inadequate due to the blockage structure. Analogously to Definitions 2.7 and 2.9, exact and projected wire shapes can be defined. We refrain from a technical definition and rather use the term loosely when required. When referring to nets and pins in this thesis, we will implicitly assume exact and projected pin shapes to be given through the respective mappings. We can now distinguish between Steiner trees connecting exact and projected pin shapes:

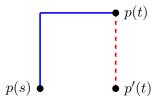

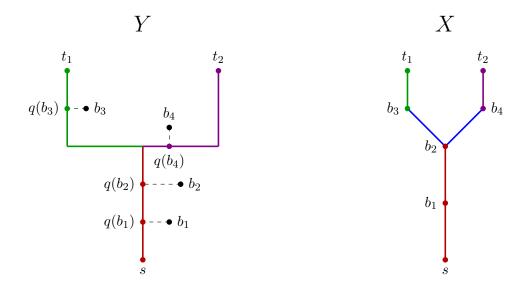

DEFINITION 2.10. Let S be the layered chip area, G be the global routing graph and  $N \subseteq N'$  for a net N'. A Steiner tree connecting the exact shapes of N is a Steiner tree Y with  $N \subseteq V(Y)$  that is embedded rectilinearly into S such that  $p(\pi) = p_{\rm ex}(\pi)$  for  $\pi \in N$ . A Steiner tree connecting the projected shapes of N is a Steiner tree Y with  $N \subseteq V(Y)$  that is embedded into G such that  $p(\pi) = p_{\rm pr}(\pi)$  for  $\pi \in N$ . When it is clear or indifferent in a given context, we just refer to a Steiner tree for N to denote a Steiner tree connecting either the exact or projected shapes of N. Moreover, unless explicitly stated otherwise, we assume that N is the set of leaves of Y. If applicable, s refers to the source pin and T to the set of sink pins of N, and Y is implicitly regarded as an arborescence rooted at s.

The requirement that N is the set of leaves of Y is not a restriction, but merely a technicality that eases notation and description at some points — a Steiner tree not fulfilling this requirement can be transformed into one that does in linear time by introducing new vertices and edges of length zero and successively removing Steiner vertices of degree one. Next, we define distances of points in the three-dimensional space or entities that are embedded into the three-dimensional space:

DEFINITION 2.11. For  $a, b \in \mathbb{R}^3$  we define  $\operatorname{dist}(a, b) := |a_x - b_x| + |a_y - b_y|$  to be the rectilinear distance of the two-dimensional projections of a and b. Let v be either

- a pin with position  $p(v) \in \mathbb{R}^3$  (either  $p(v) = p_{ex}(v)$  or p(v) is the vertex position of  $p_{pr}(v)$ ), or

- a vertex of a graph that is embedded onto a position  $p(v) \in \mathbb{R}^3$  (directly or by a chain of embeddings), or

• a point in  $\mathbb{R}^3$ , in which case we set p(v) := v.

Let the same hold true for w. Then we set dist(v, w) := dist(p(v), p(w)).

This definition of distances is rooted in our model of having a layered chip area, where the z-dimension has a different meaning than the x- and y-dimensions and is therefore treated differently. We also often use the term length in order to refer to distances, e.g. the length of an edge in a graph is the distance of its endpoints, and the length of a Steiner tree is the sum of its edge lengths. In the same manner, a shortest Steiner tree is one minimizing edge lengths. The meaning should be clear in the given context. Regarding Steiner trees as arborescences allows for the notion of subtrees rooted at certain vertices:

DEFINITION 2.12. Let Y be a Steiner tree for a net  $N = \{s\} \sqcup T$ , where s is the source pin of N, and assume that Y is directed in such a way that all vertices are reachable from s. Then Y(v) for  $v \in V(Y)$  denotes the subtree rooted at v, and  $T(Y(v)) := T \cap V(Y(v))$  denotes the sinks in Y(v). For  $v, w \in V(Y)$ ,  $P_Y(v, w)$  denotes the path from v to w in Y, where Y is defined by Y(Y) := Y(Y) and Y(Y) := Y(Y) = Y

An edge of a graph that is embedded into the chip area corresponds to a line segment:

DEFINITION 2.13. Let S be the layered chip area and  $a,b \in S$ . Then  $L(a,b) := \{\mu a + (1-\mu)b : \mu \in [0,1]\} \cap S$  denotes the straight line segment between a and b in S. Additionally, we define  $L^{2D}(a,b)$  to be the two-dimensional projection of L(a,b) (neglecting z-coordinates). If G is a graph that is embedded into S, then we define L(v,w) := L(p(v),p(w)) and  $L^{2D}(v,w) := L^{2D}(p(v),p(w))$  for  $(v,w) \in E(G)$ .

Edges of a graph embedded into the chip area may be subdivided by inserting a new vertex on the corresponding line segment:

DEFINITION 2.14. Let S be the layered chip area and H be a graph that is embedded into S. A graph H' is said to originate from H by subdivision of an edge  $(v,w) \in E(H)$  if  $V(H') = V(H) \sqcup \{x\}$ ,  $E(H') = (E(H) \setminus \{(v,w)\}) \cup \{(v,x),(x,w)\}$ , and  $p(x) \in L(v,w)$ . A graph H'' is said to be a subdivision of H if H'' originates from H through a sequence of edge subdivisions.

We continue with the bounding box:

DEFINITION 2.15. Let  $A \subseteq \mathbb{R}^2$  or  $A \subseteq \mathbb{R}^3$ . Then the bounding box BB $(A) \subseteq \mathbb{R}^2$  of A is the smallest axis-parallel rectangle containing the two-dimensional projection of A, i.e. BB $(A) := [\min_{a \in A} a_x, \max_{a \in A} a_x] \times [\min_{a \in A} a_y, \max_{a \in A} a_y]$ . Moreover, if A',  $A' \not\subseteq \mathbb{R}^2$

and  $A' \nsubseteq \mathbb{R}^3$ , is a set associated with positions  $p: A' \to \mathbb{R}^2$  or  $p: A' \to \mathbb{R}^3$ , then we set BB(A') := BB(p(A')).

We note that similarly to distances we define the bounding box always as two-dimensional, even for subsets of  $\mathbb{R}^3$ . The z-dimension will be treated separately in the given contexts. We conclude this section with a definition that allows for a more convenient notation:

DEFINITION 2.16. Let X be a set and  $f: X \to \mathbb{R}^d$ ,  $d \in \mathbb{N}$ , be a function. If applicable and not explicitly stated otherwise, we define  $f(X') := \sum_{x \in X'} f(x)$  for  $X' \subseteq X$ .

#### 2.2. The Traditional Global Routing Problem

In this section we deal with the traditional way of formulating the global routing problem. We state the problem definition in Section 2.2.1 and give an overview on previous work in Section 2.2.2. Background information regarding the global routing problem, which naturally motivates our formulation of the Traditional Global Routing Problem, can be found in Section 1.3.2. This section is only meant to give an overview, but does not go into much detail. An algorithm by Müller, Radke and Vygen [87] for solving the Traditional Global Routing Problem is described in Section 4.2.

# **2.2.1. The Problem Formulation.** We define the Traditional Global Routing Problem as follows:

#### PROBLEM 2.17: TRADITIONAL GLOBAL ROUTING PROBLEM

**Input:** The global routing graph G, edge lengths  $l: E(G) \to \mathbb{R}_{\geq 0}$ , a netlist  $\mathcal{N}$ , net weights  $w: \mathcal{N} \to \mathbb{R}_{\geq 0}$ , routing space usages usg:  $\mathcal{N} \times E(G) \to \mathbb{R}_{\geq 0}$ .

**Task:** Find a Steiner tree  $Y_N$  for all  $N \in \mathcal{N}$  connecting the projected pin shapes of N such that

$$\sum_{N \in \mathcal{N}} |\{e' \in E(Y_N) : p(e') = e\}| \cdot \operatorname{usg}(N, e) \le 1 \quad \text{ for all } e \in E(G),$$

and

$$\sum_{N \in \mathcal{N}} w(N) \cdot l(E(Y_N))$$

is minimized.

For wiring edges  $(v, w) \in E(G)$  the standard choice is to set  $l(v, w) := \operatorname{dist}(v, w)$ . For via edges  $(v, w) \in E(G)$ , l(v, w) can be used to express via costs, which can be adjusted from technology to technology. The edge usages  $\operatorname{usg}(N, e)$  for  $(N, e) \in \mathcal{N} \times E(G)$  are relative to the routing capacity of e, i.e. we assume unit capacities by adapting the

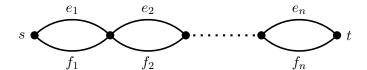

usage functions. The seemingly complicated formulation of routing capacity constraints is owed to the fact that we embed arbitrary Steiner trees into the global routing graph. In general, this allows for Steiner trees that are using the same edge in the global routing graph multiple times, which can make sense when computing RC-aware Steiner trees as in Chapter 5. However, it is easy to see that connecting a net N by a Steiner tree  $Y_N$  with  $|\{e' \in E(Y_N) : p(e') = e\}| > 1$  for some  $e \in E(G)$  is pointless in the Traditional Global Routing Problem. In that sense, the Traditional Global Routing Problem can equivalently be formulated in a model where the Steiner trees  $Y_N$ ,  $N \in \mathcal{N}$ , are subgraphs of the global routing graph.

Even simple special cases of the Traditional Global Routing Problem are NP-hard: The special case with only one net contains the Rectilinear Minimum Steiner Tree Problem [37, 46] (cf. Section 2.3.2), and the special case where usg(N,e) = 1 for all  $(N,e) \in \mathcal{N} \times E(G)$  and |N| = 2 for all  $N \in \mathcal{N}$  corresponds to the Edge-Disjoint Paths Problem in Grid Graphs [112, 118]. The latter example also shows that it is NP-hard to find any feasible solution, as violating any routing capacity constraint makes a solution infeasible. In theory, this is reasonable. In practice, however, it is too rigid — here, one usually wants to minimize routing capacity constraint violations in cases where no solution obeying all constraints can be found. This is done for example by the modeling of the Traditional Global Routing Problem as a Min-Max Resource Sharing Problem by Müller, Radke and Vygen [87], which we further examine in Chapter 4.

This formulation of the global routing problem is not inherently timing-aware. To consider timing in an indirect manner, timing-critical nets can be given higher weights. Moreover, strict adherence to wire type and layer assignments (cf. Section 1.3.2.4.1) can easily be incorporated by always using the wire type assigned to the net, and setting  $usg(N, e) = \infty$  if the layer assignment of  $N \in \mathcal{N}$  forbids the use of  $e \in E(G)$ . An inherently timing-aware global routing framework is presented in Chapter 4.

2.2.2. Previous Work. Many of the recently published global routing approaches are based on heuristics which predominantly rely on a method called ripup-and-reroute. Roughly speaking, this method consists of starting with a reasonable initial solution and iteratively improving this solution by ripping out and rerouting nets until some abort criterion is met. The routing techniques used include pattern routing, meaning that only routes consisting of very simple patterns like L- and Z-shapes may be used, monotonic routing, meaning that only routes without detours are allowed, and maze routing, which is the term used for route construction that relies on actual shortest path computations. The edge costs for the route computations are usually chosen heuristically. Such ripupand-reroute techniques are prevalently used among the contestants of the ISPD global

routing contests from 2007 and 2008 [66, 67], which we examine in Section 2.2.2.1. Another method to address global routing is via flow- and LP-based approaches, which we cover in Section 2.2.2.2. A survey on (early) global routing algorithms is given by Hu and Sapatnekar [61].

2.2.2.1. The ISPD Global Routing Contests. Noteworthy in the context of development of global routing algorithms are the ISPD global routing contests 2007 and 2008 [66, 67], where problem formulation and evaluation metrics result in a global routing problem that is very similar to the Traditional Global Routing Problem. Here, most top-ranked contestants use techniques that are similar (but not limited) to the ripup-and-reroute techniques explained above. The contestants include NTHU-Route [25], FastRoute [124], MaizeRouter [81], FGR [98], BoxRouter [26] and Archer [89]. A survey is given by Moffitt et al. in [83].

Compared to industrial global routing instances, the benchmarks used for the ISPD contests are significantly simplified. In particular, each net consumes the same amount of routing space across all layers, which is usually not given in practice. Moreover, via usages are ignored. This makes it natural to consider a simplified instance with only two layers and perform a layer assignment afterwards. An analysis of this matter and the global routing problem in general is given by Moffitt [82].

2.2.2.2. Flow- and LP-Based Approaches. Theoretically more profound approaches for solving the Traditional Global Routing Problem were first obtained through flow-based and integer linear programming formulations of global routing. An early work in this category is given by Shragowitz and Keel [113], who deal with a special case of the Traditional Global Routing Problem where |N|=2 for all  $N\in\mathcal{N}$ , which is also a special case of the well known Minimum Cost Multi-Commodity Flow Problem. They start with a cost-optimal solution ignoring routing capacities and reduce overflow afterwards by an iterative method that bears resemblance to the ripup-and-reroute approaches mentioned earlier. A multi-commodity flow formulation of the global routing problem is also solved by Carden, Li and Cheng [22]. In contrast to [113], their formulation can also handle multi-terminal nets. Wu et al. [123] use an integer linear programming formulation of the global routing problem: They subdivide the global routing problem into smaller subproblems on rectangular regions on the chip and solve these subproblems via integer linear programming allowing only a predefined set of candidate routes.

Raghavan and Thompson [93] give a linear programming formulation of the global routing problem that is based on multi-commodity flows. They show how to use a randomized rounding technique [92] to get an integral solution whose deviation from the LP solution can be bounded. However, they do not outline a method to solve the underlying

linear program. This is addressed by Albrecht [2], who uses a modified version of the multi-commodity flow approximation algorithm by Garg and Könemann [38, 39] to solve a linear programming formulation of the global routing problem. Follow-ups of this approach are given by Vygen [117], who also incorporates delay bounds and power minimization, and Müller [85], who incorporates optimization of manufacturing yield. Finally, Müller, Radke and Vygen [87] formulate global routing as a more general MINMAX RESOURCE SHARING PROBLEM and present an approximation algorithm to solve it. We examine their approach in more detail in Section 4.2 and extend it in Section 4.3 to incorporate timing constraints.

#### 2.3. The Minimum Steiner Tree Problem

As different variants of the well-known MINIMUM STEINER TREE PROBLEM appear as subproblems in different parts of this thesis, we shortly introduce them in this section. Instead of pins that are embedded into the global routing graph or the layered chip area, we conventionally speak of *terminals* that are embedded into a general graph or  $\mathbb{R}^2$  in this section. However, apart from that, the notation from Section 2.1 is used.

# **2.3.1. The Minimum Steiner Tree Problem in Graphs.** We start with the MINIMUM STEINER TREE PROBLEM IN GRAPHS:

PROBLEM 2.18: MINIMUM STEINER TREE PROBLEM IN GRAPHS

**Input:** A graph G, edge costs  $c: E(G) \to \mathbb{R}_{\geq 0}$ , a set of terminals N that are embedded into G.

**Task:** Find a Steiner tree Y for N minimizing c(E(Y)).

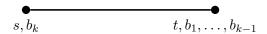

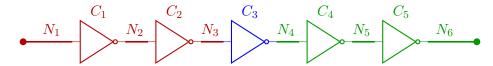

This problem is known to be NP-hard [70], but efficient constant-factor approximation algorithms exist. The best known approximation guarantee of 1.39 is achieved by the algorithm of Byrka et al. [21]. The running time is polynomial, but for our purposes presumably too large in practice. A fast running time can be achieved by making use of the fact that a minimum terminal spanning tree in the metric closure of G yields an approximation ratio of 2 for the MINIMUM STEINER TREE PROBLEM IN GRAPHS (see e.g. [75]). In our implementation we use an algorithm that is essentially the Standard Block Solver described by Müller [86] (Section 4.7.3), which iteratively connects connected components of wires and pins by shortest path computations until the whole net is connected. We will not elaborate on this any further in this thesis, but rather point to the description given in [86]. An overview on the MINIMUM STEINER TREE PROBLEM IN GRAPHS can be found in the book of Korte and Vygen [75].

**2.3.2.** The Rectilinear Minimum Steiner Tree Problem. The RECTILINEAR MINIMUM STEINER TREE PROBLEM is of major importance in VLSI design due to the fact that wires are required to run parallel to the x- or y-axis. It can be formulated as follows: