# VLSI Routing for Advanced Technology

## Dissertation

zur

Erlangung des Doktorgrades (Dr. rer. nat.)

der

Mathematisch-Naturwissenschaftlichen Fakultät

der

Rheinischen Friedrich-Wilhelms-Universität Bonn

vorgelegt von

Michael Gester

aus Freudenberg

Bonn, Januar 2015

Angefertigt mit Genehmigung der Mathematisch-Naturwissenschaftlichen Fakultät der Rheinischen Friedrich-Wilhelms-Universität Bonn

Gutachter: Prof. Dr. Jens Vygen

Gutachter: Prof. Dr. Stephan Held

Tag der Promotion: 12. März 2015

Erscheinungsjahr: 2015

# Acknowledgments

At this place I would like to express my gratitude to my supervisor Professor Dr. Jens Vygen for his excellent support over the past years. This work has benefited substantially from his valuable ideas und experience.

Special thanks go to Professor Dr. Dr. h.c. Bernhard Korte for the exceptional working conditions at the Research Institute for Discrete Mathematics which laid the foundations for this thesis.

I would like to thank my former and present colleagues in the BonnRoute team: Markus Ahrens, Niko Klewinghaus, Dr. Dirk Müller, Dr. Tim Nieberg, Christian Panten, Rudi Scheifele, and Dr. Christian Schulte. They have all contributed extensively to the success of BonnRoute, and it was a great pleasure to share ideas and develop solutions for VLSI routing in cooperation with them. Further thanks go to Professor Dr. Stephan Held, Professor Dr. Stefan Hougardy, and Jannik Silvanus for very helpful discussions on several topics, and to Markus Ahrens, Niko Klewinghaus, Dr. Dirk Müller, and Dr. Jan Schneider for proof-reading parts of this thesis. Moreover, I would like to thank Dr. Nicolai Hähnle and Dr. Jan Schneider for fruitful discussions and contributions to polygon width decompositions. I also want to thank all other colleagues for the friendly and encouraging atmosphere at the institute.

I am very grateful for the excellent cooperation with IBM that has made the success of BonnRoute possible. At this place I would especially like to thank Karsten Muuss, Dr. Sven Peyer, Dr. Christian Schulte, and Dr. Gustavo Tellez for the great collaboration.

Finally, my personal thanks go to my parents for the greatest possible assistance, and to Blanka for her continuous encouraging support and her patience while I was writing this thesis.

# Contents

| 1                                    | Intr                     | oducti | ion                                            | 1    |  |

|--------------------------------------|--------------------------|--------|------------------------------------------------|------|--|

| 2                                    | Notation and Definitions |        |                                                |      |  |

| 3                                    | 3 VLSI Routing Overview  |        |                                                | 7    |  |

| 4                                    | Pol                      | ygon I | Decompositions in VLSI Design                  | 17   |  |

|                                      | 4.1                      | Uncon  | nstrained Polygon Decomposition                | . 18 |  |

|                                      | 4.2                      |        | on Decomposition and Design Rule Checking      |      |  |

|                                      |                          | 4.2.1  | One-Dimensional Width Decomposition            | . 21 |  |

|                                      |                          | 4.2.2  | Two-Dimensional Width Decomposition            | . 26 |  |

|                                      | 4.3                      | Decon  | aposing the Union of Expanded Polygons         | . 46 |  |

| 5                                    | VL                       | SI Rou | iting for Multiple Patterning Technology       | 55   |  |

|                                      | 5.1                      | Multip | ple Patterning Setting                         | . 57 |  |

|                                      | 5.2                      | Colori | ng Given Layouts                               | . 58 |  |

|                                      |                          | 5.2.1  | Color-Symmetric Design Rules                   |      |  |

|                                      |                          | 5.2.2  | General Design Rules                           | . 65 |  |

|                                      |                          | 5.2.3  | Practical Approaches                           | . 67 |  |

|                                      | 5.3                      | Creati | ing Colorable Layouts                          |      |  |

| 5.4 Multiple Patterning in BonnRoute |                          |        | ole Patterning in BonnRoute                    | . 70 |  |

|                                      |                          | 5.4.1  | Routing Space and Automatic Coloring           | . 71 |  |

|                                      |                          | 5.4.2  | Computing Long Connections                     |      |  |

|                                      |                          |        | 5.4.2.1 Search Space and Problem Formulation   | . 74 |  |

|                                      |                          |        | 5.4.2.2 Multi-Label Shortest Paths             | . 78 |  |

|                                      |                          |        | 5.4.2.3 Multi-Label Interval-Based Path Search | . 86 |  |

|                                      |                          |        | 5.4.2.4 DRC-Aware Path Search Framework        | . 89 |  |

|                                      |                          | 5.4.3  | Implementation Details                         | . 93 |  |

|                                      |                          | 5.4.4  | Experimental Results                           | . 96 |  |

| $\mathbf{B}^{i}$                     | ibliog                   | graphy |                                                | 107  |  |

| Sı                                   | ımm                      | arv    |                                                | 119  |  |

# 1 Introduction

VLSI¹ design is the process of creating construction plans for complex integrated circuits, commonly known as chips, which contain up to billions of transistors. Due to its high complexity, this process is divided into several steps, each of them comprising hard mathematical problems from fields such as combinatorial optimization and computational geometry. VLSI design has been and still is a driving force for many research areas in these fields. It poses great challenges due to enormous instance sizes, complex constraints, and competing objective functions. In this thesis we focus on problems arising from advanced technology design rules in routing, a major step in the VLSI design process. The main contributions are as follows: In Section 4.2.2 we describe a new linear time algorithm for computing a width-preserving decomposition of a simple rectilinear polygon into rectangles in order to check width-dependent design rules in routing efficiently. In Section 5.4 we present a detailed routing approach which incorporates multiple patterning technology design rules, including experimental results which confirm that this approach is superior compared to an industry standard router (see Table 5.4).

In order to motivate the routing step we give a brief overview of the VLSI design process. The process starts with an algorithmic specification of the desired chip functionality which is first translated to a register-transfer level description where the functionality is modeled as a flow of digital signals (high-level synthesis, see Coussy and Morawiec [2010]). This description is further converted into a netlist which contains a list of circuits and their intended connectivity (logic synthesis, see Devadas et al. [1994]). These circuits are physical realizations of comparatively simple logical functions consisting of interconnected transistors. The circuits are predesigned and collected in a library which is reused for the design of different chips. Connectivity information is encoded by nets, where each net contains a set of pins that define inputs or outputs of the circuits which are to be connected.

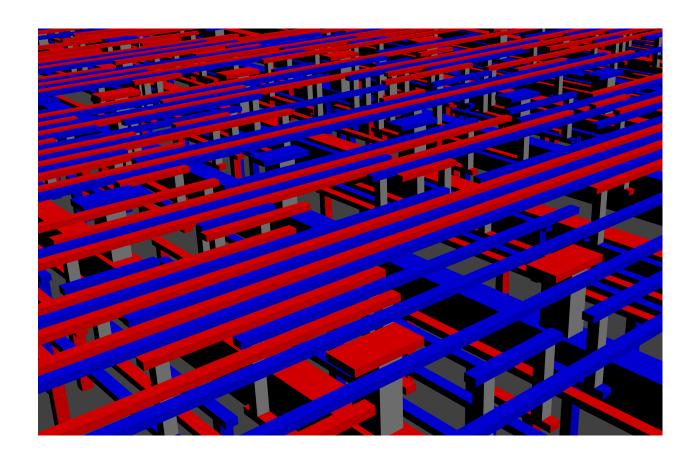

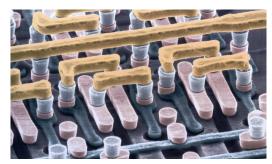

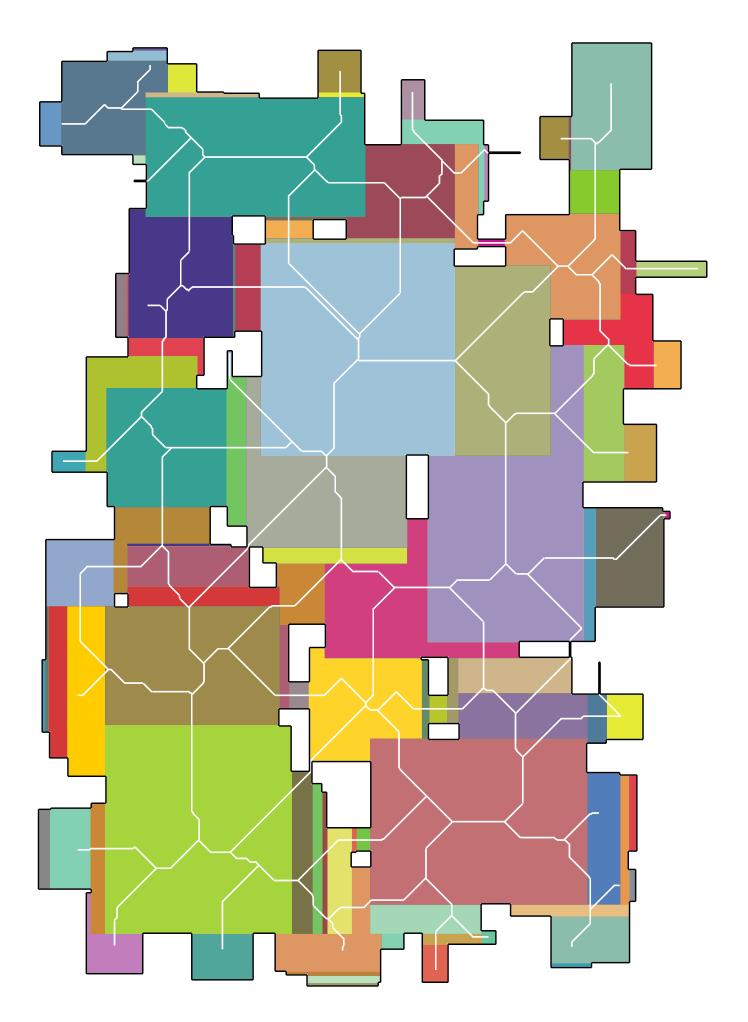

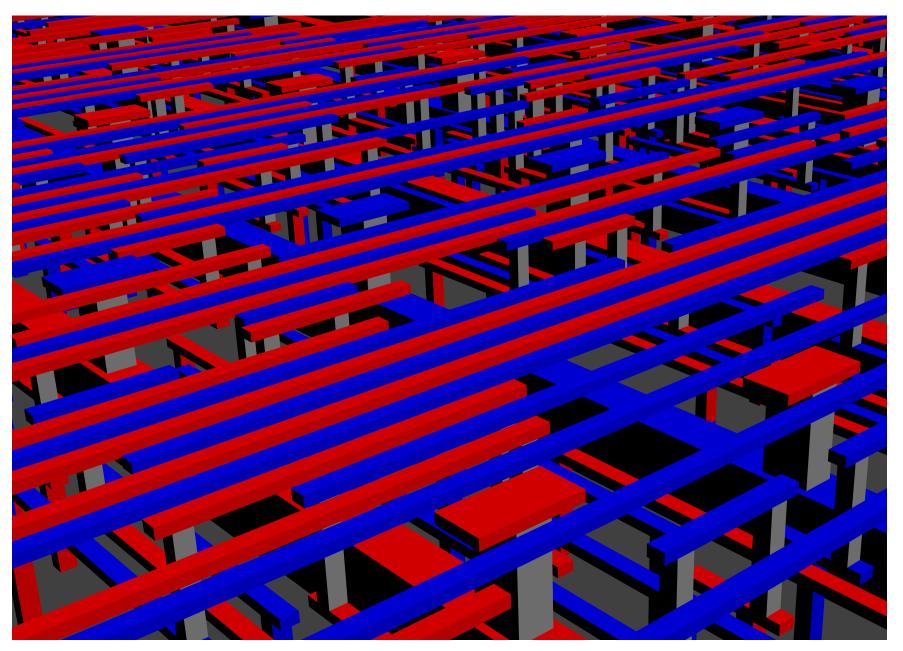

The netlist serves as input for the subsequent physical design step (Alpert et al. [2008], Held et al. [2011]) where the circuits and connections between them are located within a given three-dimensional chip area. The chip area consists of several stacked layers which are manufactured separately. One major step in physical design is routing where pins of each net are connected by wires. The wires either run horizontally or vertically on a layer or connect two layers. See the upper title picture for a section of a routed real-world chip. Wires, as well as other objects like pins or blockages, have to respect design rules such as minimum distances, minimum

<sup>&</sup>lt;sup>1</sup>Very Large Scale Integration

segment lengths, and minimum areas which reflect manufacturing requirements. Minimum distances usually depend on the width of the involved objects which are representable as rectilinear polygons on each layer. However, for simplicity reasons these polygons are usually decomposed into rectangles in routing. This motivates the question how to efficiently compute a decomposition which allows for checking of width-dependent minimum distance rules on the resulting rectangles. We answer this question for different width notions in Chapter 4.

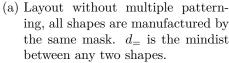

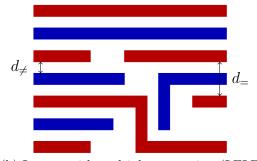

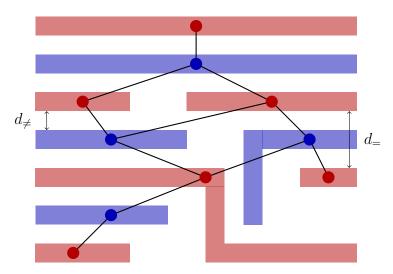

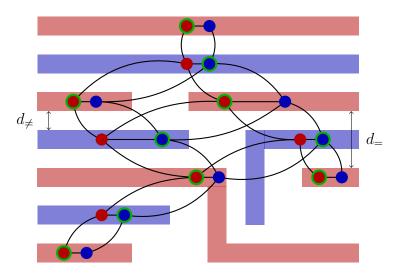

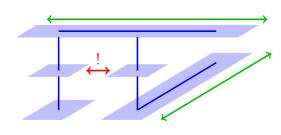

After physical design all objects (also called *features*) have fixed positions within the chip area, and they are checked with respect to manufacturing requirements (encoded by design rules) and transformed in a way such that expected manufacturing variations are compensated (Liebmann [2003]). The outcome of these steps is the final construction plan for the chip which is then manufactured by using lithographic techniques (see Jaeger [2002] for details). The lithographic manufacturing process of VLSI chips becomes increasingly difficult with the continuous shrinking of feature sizes. The wavelength of the light source used for creating the features (currently 193 nm) has not changed for more than a decade, but in spite of this new techniques have been developed to allow for increased feature density. One such technique is multiple patterning. The idea is to assign features on one chip layer to different manufacturing steps which are commonly abstracted as colors. In its simplest form, the features are assigned two different masks and the final layout on the chip is produced by two subsequent exposure steps using these masks. Here the positions of the masks are chosen such that the desired spacings between features are realized. See the upper title picture for an example of such an assignment on a real-world chip. Computing and maintaining the color assignment complicates routing substantially since design rules now depend not only on the geometry of the involved objects but also on their colors. In Chapter 5 we investigate the main challenges in routing which arise from multiple patterning and advanced technology design rules, and we present efficient solutions for these challenges.

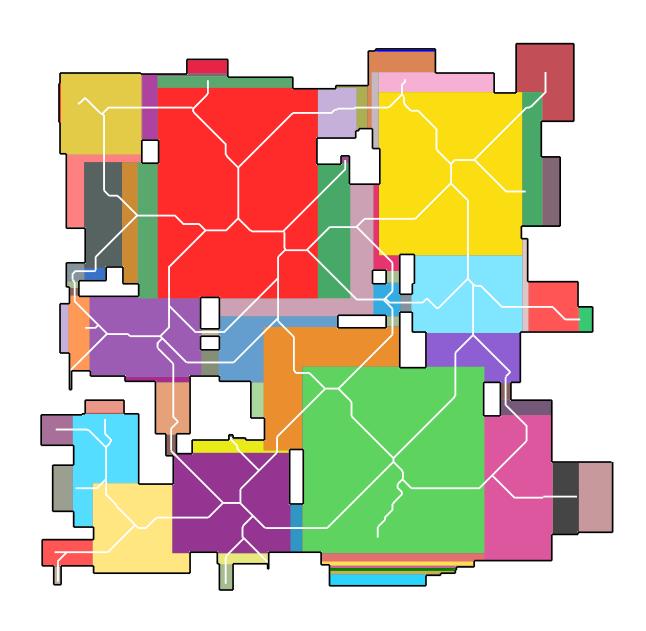

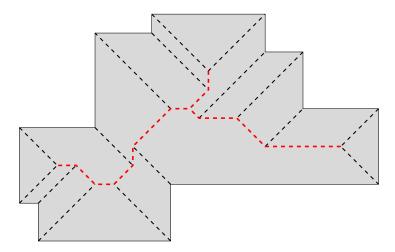

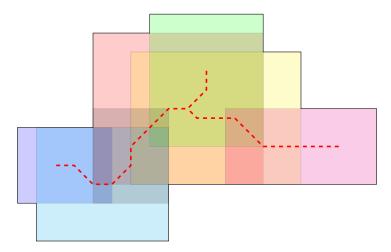

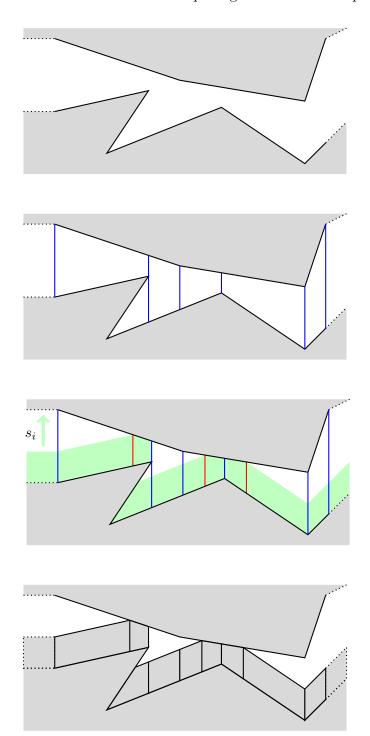

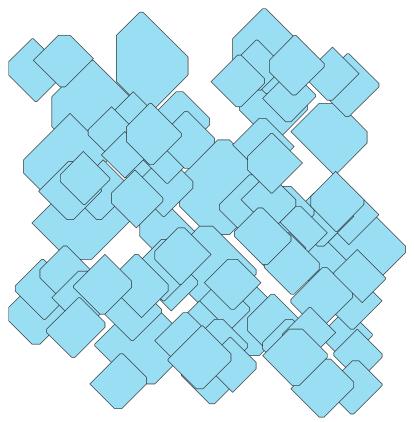

The thesis is organized as follows. After compiling the basic notation and definitions (Chapter 2) we give a short introduction to VLSI routing (Chapter 3). In Chapter 4 we investigate several polygon decomposition problems, most of them related to design rule checking in VLSI design. As a main result of this thesis, in Section 4.2.2 we give an O(n) time algorithm for decomposing a simple rectilinear polygon with n vertices into regions having uniform width. For rectilinear polygons with holes the runtime increases to  $O(n \log n)$ . Here the width at a point of the polygon is defined as the edge length of the largest square that contains the point and is contained in the polygon. See the lower title picture for an example of such a decomposition. Our algorithm makes use of the *Voronoi core*, a subset of the  $L_{\infty}$  *Voronoi diagram* of the polygon edges, which is given by white lines in the lower title picture. This algorithm can be used to preprocess polygonal shapes on a chip into rectangles such that width-dependent design rules can be checked on these rectangles instead of polygons.

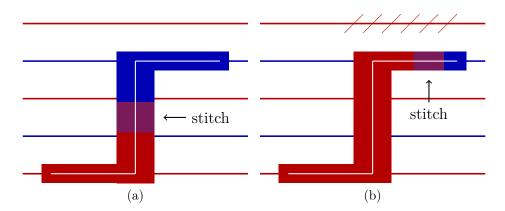

In Chapter 5 we first define multiple patterning formally and collect several related theoretical results in connection with color assignment problems. Subsequently, we present an efficient approach for managing multiple patterning and advanced technology design rules in VLSI routing (Section 5.4). This approach contains multi-label shortest paths (Section 5.4.2.2) as a key algorithmic concept. Computing shortest paths is one of the basic problems to be solved in routing. However, the paths computed by standard shortest path algorithms cannot cope with complicated design rules. The basic idea of multi-labeling is to encode certain path properties (which model design rules) as labels, and to allow only certain label transitions for the paths computed. In this way we are able to compute nearly clean (w.r.t. design rules) connections for nets, in contrast to the popular approach to first compute unclean connections and try to fix design rule violations afterwards by a post-processing step. In advanced chip technologies, such post-processing often fails (see the results in Section 5.4.4), for example due to missing space for fixing the violations locally. Further aspects of our multiple patterning approach are an efficient color management (Section 5.4.1) and a framework that uses multi-labeling only when necessary instead of always (Section 5.4.2.4). This even improves the quality of results (Section 5.4.4).

The presented multiple patterning approach has been implemented in BonnRoute (Gester et al. [2013]), the routing tool contained in the BonnTools software package which covers all major physical design steps. The BonnTools (Korte et al. [2007]) are being developed at the Research Institute for Discrete Mathematics, University of Bonn, in cooperation with IBM and have been used successfully by IBM and its customers for the design of more than thousand highly complex chips, for more than two decades. In Section 5.4.4 we present results confirming that BonnRoute produces high-quality routing solutions on real-world multiple patterning designs fast. We also compare a combined flow (BonnRoute followed by an external cleanup step) against an industry standard router used by IBM and obtain far superior results with our combined flow (see Table 5.4 on page 102). This result is one of the main contributions of this thesis. We finally note that our proposed combined BonnRoute flow is the default tool for signal routing at IBM, used for designing all their ASIC chips as well as their server chips for both single patterning and multiple patterning technologies.

# 2 Notation and Definitions

We compile some basic notation and definitions used in this thesis. For a set A we denote the set of all k-element subsets of A as  $\binom{A}{k}$ . Let  $A \subseteq \mathbb{R}^n$  for some  $n \in \mathbb{N}_{>0}$ . We denote the *border* of A as  $\partial A$ , the *interior* of A as  $A^{\circ}$ , and the *closure* of A as  $\bar{A}$ . All these terms are to be understood relatively, that means with respect to the affine hull of A. For example, the interior of a line segment in  $\mathbb{R}^2$  contains all of its points except the endpoints.

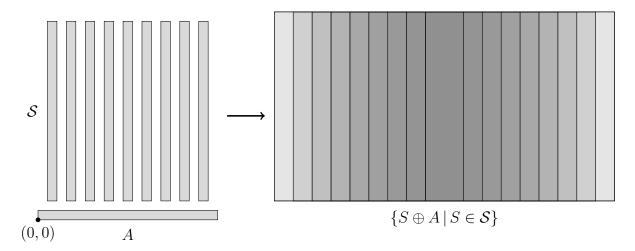

Two sets  $A, B \subseteq \mathbb{R}^n$  are called *interior-disjoint* if  $A^{\circ} \cap B^{\circ} = \emptyset$ . A set  $\mathcal{A} := \{A_1, A_2, \ldots, A_k\}$  with  $A_i \subseteq \mathbb{R}^n$  for all  $i \in \{1, 2, \ldots, k\}$  is called interior-disjoint if  $A_i$  and  $A_j$  are interior-disjoint for all  $i \neq j$ . The *Minkowski sum* of two sets  $A, B \subseteq \mathbb{R}^n$  is defined as  $A \oplus B := \{a + b \mid a \in A, b \in B\}$ .

For two points  $p, q \in \mathbb{R}^n$  we denote the line segment connecting p and q, that is the set  $\{x \in \mathbb{R}^n \mid x = p + c \cdot (q - p), 0 \le c \le 1\}$ , as  $\overline{pq}$ . For a finite sequence of points  $p_1, p_2, \ldots, p_k \in \mathbb{R}^2$  the set  $C = \overline{p_1p_2} \cup \overline{p_2p_3} \ldots \cup \overline{p_{k-1}p_k}$  is called a polygonal chain. It is called closed if  $p_1 = p_k$ , and simple if each point in  $\{p_1, p_2, \ldots, p_k\}$  is contained in at most two line segments and the inner points of each line segment are not contained in any other line segment.

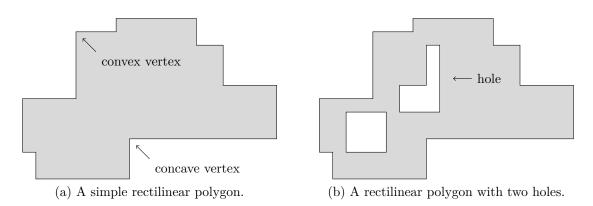

The closure of the area enclosed by a simple closed polygonal chain is a *simple polygon*. A *polygon* is a set  $P := P_1 \setminus (P_2^{\circ} \cup \ldots \cup P_k^{\circ})$ , where  $P_1, \ldots, P_k$  are simple polygons and  $P_2, \ldots, P_k$ , the *holes* of P, do not intersect pairwise and are all contained in  $P_1^{\circ}$ . The line segments of the polygonal chains defining a polygon are the *edges* and their endpoints are the *vertices* of the polygon. As usual, we assume that two neighboring edges are not contained in a common line. A vertex is called *convex* if the angle formed by the two adjacent edges inside of the polygon is less than 180° and it is called *concave* otherwise. A *rectilinear polygon* is a polygon whose edges are all parallel to the x- or y-axis. See Figures 2.1a and 2.1b for examples.

When we consider simple geometric figures like rectangles or trapezoids we often identify them with their enclosed area (including the border, if not stated differently).

For measuring lengths and distances in  $\mathbb{R}^3$  we use the following functions.

#### 2 Notation and Definitions

Figure 2.1

**Definition 2.1.** For two points  $p = (x_1, y_1, z_1), q = (x_2, y_2, z_2) \in \mathbb{R}^3$  we define

$$d_{1}(p,q) := \|p-q\|_{1} := |x_{1}-x_{2}| + |y_{1}-y_{2}| + |z_{1}-z_{2}| \qquad (L_{1}-distance)$$

$$d_{2}(p,q) := \|p-q\|_{2} := \sqrt{|x_{1}-x_{2}|^{2} + |y_{1}-y_{2}|^{2} + |z_{1}-z_{2}|^{2}} \qquad (L_{2}-distance)$$

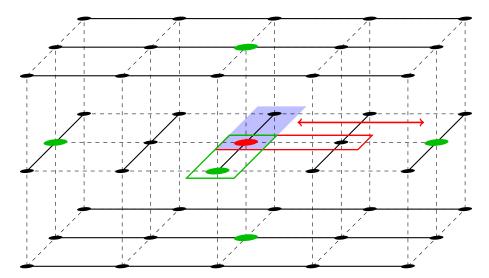

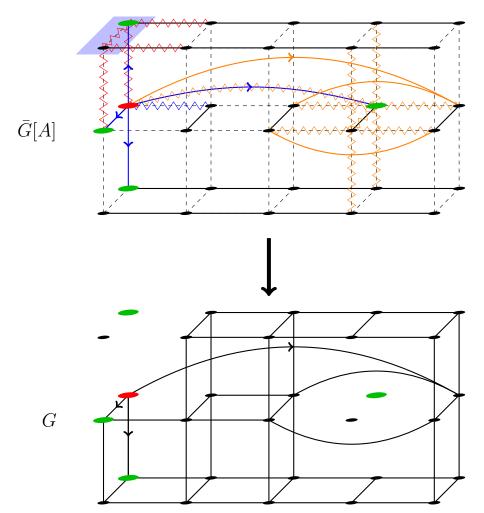

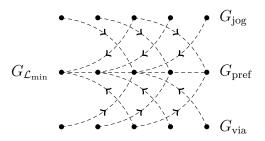

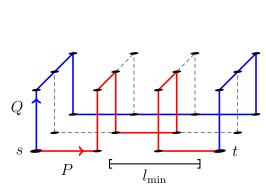

$$d_{\infty}(p,q) := \|p-q\|_{\infty} := \max(|x_{1}-x_{2}|, |y_{1}-y_{2}|, |z_{1}-z_{2}|) \qquad (L_{\infty}-distance)$$

For two closed and bounded sets  $A, B \subseteq \mathbb{R}^3$  we define

$$d_1(A, B) := \min_{p \in A, q \in B} d_1(p, q)$$

$$d_2(A, B) := \min_{p \in A, q \in B} d_2(p, q)$$

$$d_{\infty}(A, B) := \min_{p \in A, q \in B} d_{\infty}(p, q)$$

For basic notions in graph theory we refer to Korte and Vygen [2012].

# 3 VLSI Routing Overview

We now give an overview and formalization of VLSI routing with a focus on detailed routing. The description is not meant to be universal, but depicts how the routing flow works in BonnRoute.

The basic task in VLSI routing is to connect certain predetermined *pins* on a chip with *wires*. A set of pins which have to be connected is called a *net*. The pins are either inputs or outputs of small integrated *circuits* on the chip or serve as a connection to the exterior. The term circuit is ambiguous since the chip itself is also a large complex circuit, but here we consider circuits as black boxes realizing comparatively simple logical functions. Such circuits (e.g. inverter or NANDs) are usually *predesigned* and reused on different chips of the same technology. See Schneider [2014] for details on the design of such circuits which is done on a *transistor level*.

A chip consists of several stacked and parallel *layers* which are manufactured separately. The circuits and its involved transistors are placed on lower layers, and wires connecting nets are placed on *routing layers* above. We now define the search space and the basic geometric objects for routing.

**Definition 3.1.** The chip area is a nonempty rectangular cuboid

$$A_{\text{chip}} := [x_{\min}, x_{\max}] \times [y_{\min}, y_{\max}] \times [z_{\min}, z_{\max}] \subseteq \mathbb{R}^{3}$$

$$with \ x_{\min}, x_{\max}, y_{\min}, y_{\max}, z_{\min}, z_{\max} \in \mathbb{Z} \ and \ z_{\min}, z_{\max} \ even. \ We \ further \ define$$

$$Z_{\text{all}} := \{z_{\min}, \dots, z_{\max}\} \qquad (the \ set \ of \ \text{layers})$$

$$Z_{\text{wiring}} := \{z \in Z_{\text{all}} : z \ even\} \qquad (the \ set \ of \ \text{wiring \ layers})$$

$$Z_{\text{via}} := \{z \in Z_{\text{all}} : z \ odd\} \qquad (the \ set \ of \ \text{via \ layers})$$

$$A_{z} := \{(x, y, z) \in A_{\text{chip}}\} \qquad (the \ \text{chip \ area \ on \ layer} \ z)$$

We will see later how wiring and via layers relate and why they alternate. We restrict ourselves to  $Manhattan\ routing$  meaning that all wires on a chip run parallel to the x-, y- or z-axis. This restriction, allowing an easier representation of the routing solution space and the involved objects, is still common practice, although there have been attempts to soften this restriction by also allowing diagonal wires, called X architecture (Teig [2002], Ho et al. [2005], Chen et al. [2003]).

**Definition 3.2.** Let  $A := [x_1, x_2] \times [y_1, y_2] \times [z_1, z_2] \subseteq \mathbb{R}^3$ . We denote A as

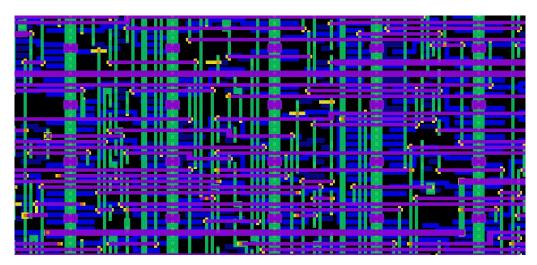

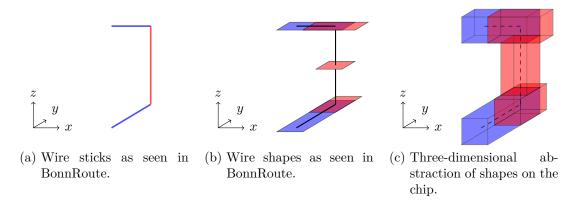

Figure 3.1: Routing snapshot showing less than  $\frac{1}{5.000.000.000}$  of a chip. Blue shapes are pins on layer 0, green shapes are plane wires on layer 2, purple shapes are plane wires on layer 4, and yellow shapes are (parts of) vias connecting two layers.

- (i) shape, if  $x_1 < x_2$ ,  $y_1 < y_2$  and  $z_1 = z_2$ ,

- (ii) stick, if exactly one of  $|x_1-x_2|$ ,  $|y_1-y_2|$ , or  $|z_1-z_2|$  is nonzero.

Hence geometrically a shape is a rectangle with an assigned z-coordinate and a stick is a line segment parallel to the x-, y-, or z-axis. We denote the layer on which a shape A lies by z(A).

There are three basic types of objects on a chip which are relevant for routing: wires, pins, and blockages. For wires, we differentiate between  $plane\ wires$  running in x- or y-dimension and vias running in z-dimension. See Figure 3.1 for a routing snapshot viewed from above.

- **Definition 3.3.** (i) A plane wire w is a pair (r, s) where r is a stick, s is a shape and  $r \subseteq s \subseteq A_z$  for some  $z \in Z_{\text{wiring}}$ . We call stick(w) := r the stick and shape(w) := s the shape of the plane wire.

- (ii) A via v is a quadruple  $(r, s_{\text{bot}}, s_{\text{cut}}, s_{\text{top}})$  with  $r = \{x\} \times \{y\} \times [z, z + 2]$  for some  $z \in Z_{\text{wiring}}$  such that  $(x, y, z) \in s_{\text{bot}} \subseteq A_z$ ,  $(x, y, z + 1) \in s_{\text{cut}} \subseteq A_{z+1}$ ,  $(x, y, z + 2) \in s_{\text{top}} \subseteq A_{z+2}$  and  $s_{\text{bot}}$ ,  $s_{\text{cut}}$ ,  $s_{\text{top}}$  are shapes. We call stick(v) := r the stick and  $\text{bot}(v) := s_{\text{bot}}$ ,  $\text{cut}(v) := s_{\text{cut}}$ , and  $\text{top}(v) := s_{\text{top}}$  the bottom, cut, and top shape of the via, respectively.

- (iii) A wire is a plane wire or a via.

- (iv) A pin is a finite set of shapes.

- (v) A blockage is a finite set of shapes.

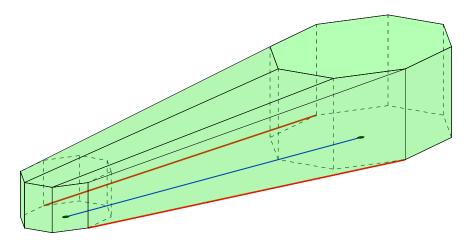

Figure 3.2: Different wire representations for two plane wires (blue) and a via (red). Overlapping parts of plane wires and via are purple.

(vi) A net is a finite set of pins.

The stick of a plane wire or via serves as one-dimensional abstraction of the two-dimensional shape(s) which is much easier to handle for example in shortest path algorithms. See Figure 3.2 for an illustration of typical wires in different representations. The shape(s) of an object shall correspond to the metalized area the object will fill out on the manufactured chip layer. We note that due to manufacturing inaccuracies and correction steps modifying the objects for the manufacturing process (such as *optical proximity correction*) the real area on a chip will not be exactly the same as the set of shapes seen in routing.

In addition to the geometry of these objects, we also manage other properties like the net a wire belongs to or the layers on which a net should be routed. To simplify notation we will use such other properties only when needed.

The basic task in routing is to compute connections between the pins of a net which will carry electrical signals on a working chip later on. For electrical connectivity it is not sufficient that two wire shapes touch in one point, but they rather have to share a common area whose minimum size is specified by an *overlap rule*. It would be quite cumbersome to always respect and check this rule in routing algorithms, so one uses the following simpler model for connectivity using the corresponding sticks which is sufficient in practice.

**Definition 3.4.** Two wires are called connected if their sticks have at least one point in common. A connection for a net  $\mathcal{N}$  is a finite set of wires C such that

- (i)  $\{\operatorname{stick}(w) \mid w \in C\}$  is a connected set

- (ii) for all pins  $P \in \mathcal{N}$  there exists a pin shape  $s \in P$  and a wire  $w \in C$  with  $s \cap \operatorname{stick}(w) \neq \emptyset$

- (iii) for all wires  $w_1, w_2 \in C, w_1 \neq w_2$ :  $|\operatorname{stick}(w_1) \cap \operatorname{stick}(w_2)| \leq 1$

In fact the wire sticks are defined exactly in such a way that they allow for this easy model for connectivity. At first sight the above model for connectivity is not sufficient to model all situations occurring in practice. For example, a pin shape may be used as part of the connection of a net which in our model is not incorporated. However, we do not go into technical details here and just mention that these and similar situations can also be modeled e.g. by inserting appropriate dummy wires.

For each wiring layer  $z \in Z_{\text{wiring}}$  we define a preferred dimension  $\text{pdim}(z) \in \{x, y\}$  in which most wires should be directed to improve space utilization (see Figure 3.1). In routing algorithms this is realized by higher costs for the usage of wires directed in the other dimension, called the non-preferred dimension ( $\text{ndim}(z) \in \{x, y\}$ ). We call a plane wire whose stick runs in the preferred or non-preferred dimension pref wire or jog, respectively.

We assume that neighboring wiring layers have orthogonal preferred dimensions which is common practice for several reasons: First, crosstalk (electrical interference) between long parallel wires on neighboring layers is avoided. Second, long jogs making efficient space utilization hard are less likely because each pair of neighboring layers covers both x- and y-dimension as preferred dimension.

Due to limitations in manufacturing a wire must have at least a certain width. While theoretically one could often use wires with arbitrary width greater than that minimum width, in practice it is reasonable to allow only a small number of different wire types.

**Definition 3.5.** A wire type is given by one shape  $s_{z,\text{cut}} \subset \mathbb{R}^2 \times \{z\}$  for each  $z \in Z_{\text{via}}$  and by four shapes  $s_{z,\text{pref}}, s_{z,jog}, s_{z,\text{bot}}, s_{z,\text{top}} \subset \mathbb{R}^2 \times \{z\}$  for each  $z \in Z_{\text{wiring}}$ . Let W be a wire type. We say that a plane wire w on layer z has wire type W if  $\text{shape}(w) = \text{stick}(w) \oplus s$ , where

$$s := \begin{cases} s_{z,\text{pref}} & \text{if } w \text{ is a pref wire} \\ s_{z,jog} & \text{if } w \text{ is a jog} \end{cases}$$

We say that a via v ranging from layer z to layer z + 2 has wire type W if the following conditions hold:

$$bot(v) = (stick(v) \cap A_z) \oplus s_{z,bot}$$

$$cut(v) = (stick(v) \cap A_{z+1}) \oplus s_{z+1,cut}$$

$$top(v) = (stick(v) \cap A_{z+2}) \oplus s_{z+2,top}$$

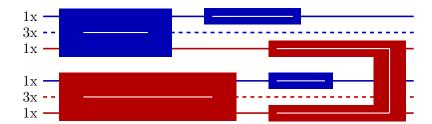

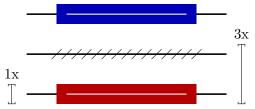

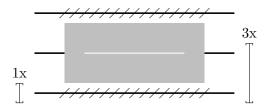

Typically, most nets on a chip use the same wire type which we call *standard wire* type and which has minimum allowed width on each layer. Wires using this wire type are denoted as *standard wires* or 1x wires. Further wire types are typically chosen in a way such that they fit well to the 1x wires with respect to width and

distance requirements. Their widths are often multiples of the minimum width, and wires using such wire types are denoted as 2x wires, 3x wires and so on. Wider wires are primarily used to speed up signals for long connections because of their lower resistance.

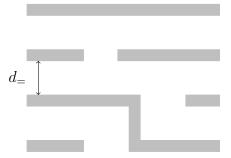

Since the main detailed routing step runs in a sequential fashion (see Algorithm 1 on page 14), allowing arbitrary positions for wires would lead to bad space utilization even if only standard wires are used. Therefore, we define a set of coordinates in dimension  $\operatorname{ndim}(z)$  for each wiring layer z where (almost) all wire stick endpoints should lie on. These coordinates are typically chosen such that standard wires lying on them can be packed as dense as possible.

**Definition 3.6.** For each wiring layer  $z \in Z_{\text{wiring}}$  with pdim(z) = x we have track coordinates  $T_z = \{t_z^1, \ldots, t_z^{|T_z|}\}$ ,  $y_{\min} \le t_z^1 < \ldots < t_z^{|T_z|} \le y_{\max}$ . We call  $\text{tracks}_z := \{[x_{\min}, x_{\max}] \times \{t\} : t \in T_z\}$  the set of tracks on layer z.

Analogously, for each wiring layer  $z \in Z_{\text{wiring}}$  with pdim(z) = y we have track coordinates  $T_z = \{t_z^1, \dots, t_z^{|T_z|}\}$ ,  $x_{\min} \leq t_z^1 < \dots < t_z^{|T_z|} \leq x_{\max}$ . We call  $\text{tracks}_z := \{\{t\} \times [y_{\min}, y_{\max}] : t \in T_z\}$  the set of tracks on layer z.

A point q = (x, y, z) with pdim(z) = x (pdim(z) = y) is called point of interest if  $x \in T_{z-2} \cup T_{z+2}$  ( $y \in T_{z-2} \cup T_{z+2}$ ) and  $y \in T_z$  ( $x \in T_z$ ). Here we use  $T_z := \emptyset$  for  $z \notin Z_{all}$ .

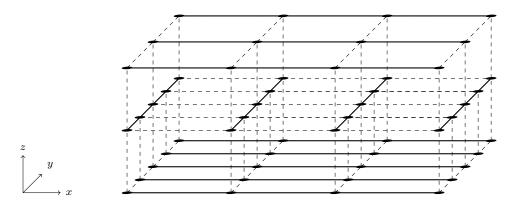

For details how tracks are computed in BonnRoute see [Müller, 2009, Section 2.4]. We are now able to define the search space for the connections to be computed, called the *track graph*.

**Definition 3.7.** The track graph  $G_T$  contains all points of interest as vertices and contains an edge between two vertices  $v_1 = (x_1, y_1, z_1)$  and  $v_2 = (x_2, y_2, z_2)$  if and only if they differ in exactly one coordinate and no other vertex is contained in the line segment  $\overline{v_1v_2}$ .

We identify vertices and edges of  $G_T$  with their corresponding points and line segments in  $\mathbb{R}^3$ . See Figure 3.3 for an example of a track graph.

**Definition 3.8.** A wire w is called on-track if stick(w) is the union of edges in  $E(G_T)$ , and it is called off-track else.

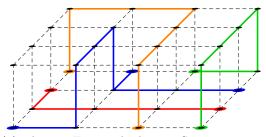

On a high level finding connections for nets using only on-track wires corresponds to packing Steiner trees in the track graph. See Figure 3.4 for an illustration of the theoretical view and the real-world view. However, the track graph may contain more than 300 billion vertices on real-world instances which makes near-optimal Steiner tree packing computation hopeless.

A natural way to overcome the huge instance size is to first compute rough connections in a coarsened version of  $G_T$ , a step called *global routing*. Here one first defines a two-dimensional grid and then contracts vertices of  $G_T$  lying on the same layer and within the same grid region (called *tile*).

Figure 3.3: Example for a track graph. Edges are depicted by solid and dashed line segments between two neighboring vertices, and tracks are drawn as solid lines.

In this much smaller graph one computes Steiner trees for all nets which lead to routing corridors (small sections of  $G_T$ ) by undoing the contraction for each tree. The actual connection for a net is then realized later in detailed routing by using only the routing corridor as search space. See Müller et al. [2011], Müller [2009] for the global routing approach used in BonnRoute which is based on an algorithm for the MIN-MAX RESOURCE SHARING PROBLEM and is able to take various objectives and constraints into account. Most important, a global router has to keep congestion low, meaning that not too many nets use the same routing corridors which will make it hard or even impossible to realize detailed connections within the corridors.

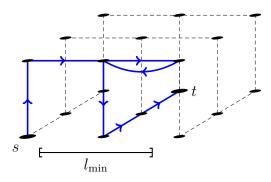

Some routing tools also use intermediate steps between global and detailed routing such as *switchbox routing* (Hitchcock [1969]) or *track assignment* (Batterywala et al. [2002], Chang and Cong [2001]) to fix long distance wires previous to detailed routing in order to further reduce detailed routing runtime and optimize objectives (e.g. *coupling* and *noise* reduction) for these long wires globally. BonnRoute does not use such a step, here the detailed connections are computed by an extremely fast *path search* algorithm (see Section 5.4.2) which can deal also with long connections fast enough in practice.

Since we focus on detailed routing in this thesis, we assume routing corridors for all nets as given from now on. We also assume that these corridors contain information on wire type usage for detailed routing.

**Definition 3.9.** A wire type region is a pair (W, R), where W is a wire type and  $R \subseteq A_{\text{chip}}$  is a union of finitely many axis-parallel cuboids. A routing corridor is a finite set of wire type regions with pairwise distinct wire types.

We assume that each net N has an assigned routing corridor corr(N) based on global routing. A connection for N is only allowed to use a wire w if there exists a wire type region (W, R) in corr(N) such that w has wire type W and  $stick(w) \subseteq R$ .

(a) Theory: Four node-disjoint Steiner trees in a three-dimensional grid graph.

(b) Real world: VLSI routing on a real chip viewed by an electron microscope. (Picture adapted from Peyer [2007])

Figure 3.4

In BonnRoute this restriction is relaxed by enlarging wire type regions gradually if no feasible connection is found otherwise.

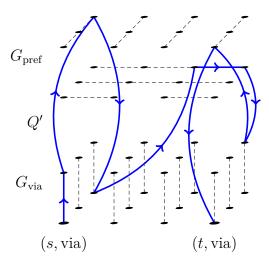

Since computing shortest Steiner trees within the given corridors would still be too slow in practice, BonnRoute computes shortest paths between connected components of a net sequentially. Here a connected component is a maximal connected set consisting of wire sticks and pin shapes of the net. We start with choosing two connected components S and T of a net N. Then we compute a restricted routing corridor  $\operatorname{rcorr}(N, S, T)$  which contains only those regions of  $\operatorname{corr}(N)$  which are relevant for finding an S-T-connection, basically following the edges of the global routing connection for N from S to T. Searching for an S-T-connection only within  $\operatorname{rcorr}(N, S, T)$  speeds up the shortest path computation significantly since many redundant label steps can be saved this way.

We compute a path consisting of wire sticks inside of  $\operatorname{rcorr}(N, S, T)$  connecting S and T and proceed with new connected components S' and T'. We iterate this procedure until N is connected. How such an S-T-connection is computed and what is done when no connection is found is explained in Section 5.4.2.

BonnRoute uses a separate routine to precompute short access paths to pins and connections between nearby pins (short connections), the pin access (see Ahrens et al. [2015], Ahrens [2014]). Accessing the pins is becoming more challenging and critical in advanced technology nodes. Our algorithm is suitable for high pin density routing of small standard circuits, and is capable of handling advanced technology design rules and various objectives. The pin access routine is important for three reasons: First, not all pins can be connected by using only on-track wires, i.e. within the track graph. Second, the sequential routing procedure sketched above may block pins when connecting another pin, leading to convergence issues, that means not all nets can be connected in the end. Third, the pin access can globally optimize objectives over all access paths and short connections, while the sequential routing step cannot.

## **Algorithm 1:** High-level overview of BonnRoute

- 1 Compute short connections and pin access paths

- 2 Compute global routing

- 3 Sort nets w.r.t. to criticality

- 4 while Not all nets connected do

- 5 Choose a not connected net N

- 6 Choose two connected components S and T of N

- 7 Compute rcorr(N, S, T) based on global routing for N

- 8 Compute connection between S and T in rcorr(N, S, T)

- 9 Post-process found connection

Algorithm 1 shows a simplified high-level overview of BonnRoute. It is important to point out that the first and second step of Algorithm 1 operate on all nets simultaneously and are thus able to globally optimize certain objective functions. In contrast to that, long connections are computed in a sequential manner until all nets are connected (lines 4 to 9). Therefore, for long connections it is of special importance to provide some guidance such that dense wire packings can be obtained, although the connections are not globally optimized. One such guidance are routing tracks, but it turns out that they are not sufficient for routing in advanced multiple patterning technologies. We will return to this important topic in Section 5.4. All routing steps in BonnRoute are efficiently parallelized, see Ahrens [2014] (pin access), Müller et al. [2011] (global routing), and Klewinghaus [2013] (long connections) for details.

One remaining question is what we do in cases where in line 8 no connection can be found. Then we allow to use wires which are only legal if some present wires are ripped out, at some high cost. If we found a connection this way, then we try to reroute (parts of) all connections where wires have been ripped out before. For these connections we may have to rip out other wires again, and so forth. If this process (called *rip-up and reroute*, see Salowe [2008]) does not converge after a certain number of iterations or we do not even find a connection when rip-up is allowed, then we allow wires to leave the restricted routing corridor by some specified margin. If still no connection is found this way (e.g. if a pin is covered by a blockage), then we compute a connection which is allowed to cross arbitrary shapes, at some very high cost. Therefore, in any case some connection for a net is computed and we finish the main loop in Algorithm 1 at some time. We use location based rip-up costs which increase over time to avoid cyclic rip-up and reroute sequences. See Hetzel [1998] for more details.

The complicated lithographic manufacturing process of a chip requires numerous design rules which have to be satisfied before the chip can be produced. These design rules tend to become more complicated with each new technology generation. We

list the most important types of design rules here, special rules arising from multiple patterning technology are discussed in Chapter 5:

- diff-net-mindist: Two shapes on the same layer and not part of the same net must have at least a certain  $L_2$ -distance.

- same-net-mindist: Two non-intersecting shapes on the same layer and of the same net must have at least a certain  $L_2$ -distance.

- minarea: Each connected set of shapes on a layer must have at least a certain area.

- **minedge:** Each edge of a rectilinear polygon representing a connected set of shapes must have at least a certain length.

- minwidth: Each shape must have a certain minimum width.

- minenclosure: The projection of a via cut shape to a neighboring wiring layer must be enclosed by shapes of this wiring layer, with some specified minimum margin.

- interlayer via mindist: The projections of two via cut shapes on neighboring via layers which are not part of the same net must have at least a certain  $L_2$ -distance.

The first and last rule are diff-net-rules, all others are same-net-rules. We simplified some rules for convenience. For more details and a formal definition of design rules see Schulte [2012]. Technically, mindist rules operate on connected components of shapes (representable as rectilinear polygons), and the required  $L_2$ -distance depends on various geometric properties of the involved polygons such as area, width, or edge lengths at those points of the polygon where distance is measured. However, in practice it would be cumbersome to permanently maintain connected components as rectilinear polygons. One is rather interested in storing objects as easy as possible, e.g. as rectangles. Therefore, an interesting question is if the polygons can be decomposed into rectangles in such a way that certain design rules can be checked on the rectangles, giving the same results as if checked on the polygons. We give a positive answer to this question in Chapter 4 for one of the most important classes of design rules, width-dependent mindist rules, and present efficient algorithms computing this decomposition. From now on we will thus assume mindist rules based on shapes as defined above. See Schulte [2012] for a justification why also for many other design rules it is sufficiently accurate to decompose polygons and check rules between rectangles later on.

In the following we assume a *checking oracle* which is able to decide if a set of shapes violates any design rule or not. This oracle is used by routing algorithms to query for legal wire locations.

**Definition 3.10.** A checking oracle is a function  $\psi$  which returns for a given set of shapes S if these shapes violate any design rule  $(\psi(S) = 0)$  or not  $(\psi(S) = 1)$ . If  $\psi(S) = 1$ , then we call S DRC-clean.

Here *DRC* stands for *design rule check*. Following the above definition, a chip is manufacturable if the set of all shapes on the chip is DRC-clean. We will give some details on the usage of the checking oracle in Section 5.4.3. We assume that the checking oracle knows to which net a shape belongs which is necessary to decide whether same-net or diff-net rules apply.

For routing algorithms same-net rules are usually much harder to obey than diffnet rules. The main reason is that with respect to diff-net rules a partial illegal connection stays illegal when wires are added (with some exceptions), but with respect to same-net rules a partial illegal connection may become legal by adding a small piece of wire (e.g. for minarea or minedge rules). Therefore, the approach to discard any illegal partial solution does not work for same-net rules. In Section 5.4.2 we describe an approach how to respect same-net rules while computing connections.

# 4 Polygon Decompositions in VLSI Design

Decompositions of polygons into simpler geometric objects have a long history in computational geometry, see Keil [2000] for a survey. These simpler objects can be for example special types of polygons such as monotone, star-shaped or convex polygons or fixed geometric shapes such as trapezoids, rectangles, squares or triangles. When using simpler objects, data structures can be kept simple and efficient which is of special importance in VLSI design where rectangles (instead of rectilinear polygons) are used as main geometric data type and occur millionfoldly.

Another main motivation for such decompositions is that many geometric problems can be solved much easier on the simpler objects than on the original polygon, so it makes sense to first decompose the polygon and then solve the problem on the simpler objects. To use this approach, one has to ensure that the problem to solve translates somehow from the polygon to the simpler objects. For example, if we are given a rectilinear polygon and a decomposition into rectangles and we want to check if a given point is contained in the polygon, then we could answer this question by just checking if the point is contained in any of the rectangles. So in this case the problem translates easily. However, if we want to determine the maximum horizontal width of the polygon, i.e. the length of a longest horizontal line segment contained in the polygon, we can not just take the maximum of the horizontal widths of all rectangles because this may be smaller. However, we can build the decomposition in such a way that it is guaranteed that some rectangle attains the maximum horizontal width of the polygon. Generally speaking, the decomposition has to obey certain contraints depending on the problem we want to solve.

In the following we focus on decomposing a rectilinear polygon into rectangles, which is of particular interest in several parts of VLSI design (Keil [2000]). Section 4.1 summarizes the most important known results for such decompositions without additional constraints. In Section 4.2 we consider constrained decomposition problems arising in VLSI design in connection with design rule checking. The main result of this chapter is a new efficient algorithm computing a two-dimensional width decomposition of a rectilinear polygon (Section 4.2.2).

Subsequently, in Section 4.3 we give an efficient algorithm for decomposing the union of expanded polygons, solving an important subproblem in *clock network design*. This result is not restricted to rectilinear polygons.

Throughout this chapter P always denotes a polygon and n is the number of border segments of P. We assume a polygon given as a set of boundaries (one outer boundary and one for each hole), each of which is stored as a doubly linked list of points in the plane, the polygon vertices.

# 4.1 Unconstrained Polygon Decomposition

We first consider the decomposition of a rectilinear polygon into rectangles without any additional constraints, using as few rectangles as possible. This classical problem in computational geometry occurs for example when translating connected metal components on a chip layer to rectangle sets in VLSI design, minimizing the storage amount for the rectangles, and in VLSI mask generation (see Keil [2000]). Depending on the application, we may or may not allow proper intersections of distinct rectangles, leading to the following two problems.

POLYGON COVERAGE PROBLEM

**Instance:** A rectilinear polygon P.

Task: Compute a minimum rectangle set covering the same area as

P.

POLYGON PARTITIONING PROBLEM

**Instance:** A rectilinear polygon P.

**Task:** Compute a minimum interior-disjoint rectangle set covering the

same area as P.

While both problems look quite similar, the difficulty of solving them differs substantially. The Polygon Coverage Problem is known to be NP-hard even for simple rectilinear polygons (Culberson and Reckhow [1988]) and MAXSNP-hard for arbitrary rectilinear polygons (Berman and DasGupta [1992]), implying that no polynomial-time approximation scheme exists, unless P=NP.

Franzblau [1989] gave a simple sweepline heuristic running in  $O(n \log n)$  time which computes a solution where the number of rectangles is at most 2m for simple polygons and at most  $O(m \log m)$  for polygons with holes, where m is the minimum number of rectangles covering the polygon. Kumar and Ramesh [2003] described the first polynomial time approximation algorithm with an  $o(\log n)$  approximation factor for polygons with holes, computing a solution with at most  $O(m\sqrt{\log n})$  rectangles.

In contrast, the Polygon Partitioning Problem can be solved optimally in linear time for simple rectilinear polygons. This result (Keil [2000]) is obtained by first applying Chazelle's algorithm (Chazelle [1991]) to obtain a triangulation of the simple polygon in linear time and then applying the partitioning algorithm of Liou et al. [1989]. For arbitrary rectilinear polygons which may also contain degenerated

holes (single points not contained in the polygon but surrounded by polygon points only) the best known algorithm runs in  $O(n^{\frac{3}{2}} \log n)$  time (Soltan and Gorpinevich [1993]) while the best known lower bound for runtime is  $\Omega(n \log n)$  (Liou et al. [1989]). Note that the POLYGON PARTITIONING PROBLEM with degenerated holes was claimed to be NP-hard by Lingas [1982] until disproven (unless P=NP) by the algorithm of Soltan and Gorpinevich [1993].

We now want to give some insight into the basic techniques used in the best known algorithms for the Polygon Partitioning Problem. Let P be an arbitrary rectilinear polygon in the following.

**Definition 4.1.** A chord of P is a line segment whose interior is contained in  $P^{\circ}$  and whose endpoints are contained in  $\partial P$ . A horizontal or vertical chord where both endpoints are concave vertices of P is called special.

Now let m be the number of concave vertices, h the number of holes, c the maximum number of non-intersecting special chords of P, and  $r_{\rm opt}$  the number of rectangles in an optimal solution for the Polygon Partitioning Problem. The following theorem gives a nice characterization for all optimal solutions.

**Theorem 4.2.** Lipski et al. [1979], Ohtsuki [1982], Ferrari et al. [1984]

$$r_{\text{opt}} = m - c - h + 1$$

This theorem can be seen as the basic module for most algorithms solving the POLYGON PARTITIONING PROBLEM optimally. The key step is to find a maximum set of non-intersecting special chords. This can be modeled as a maximum stable set in the bipartite graph  $G = (A \cup B, E)$ , where A and B contain one vertex for each horizontal or vertical special chord, respectively, and E contains an edge between two vertices if their corresponding special chords intersect.

Using the fact that G is bipartite, it is sufficient to compute a maximum matching in G from which a minimum vertex cover and finally a maximum stable set can be easily obtained, as is well known. This approach was first used by Lipski et al. [1979] who applied the previously fastest known algorithm for finding maximum matchings in bipartite graphs by Hopcroft and Karp [1973], resulting in an  $O(n^{\frac{5}{2}} \log n)$  time algorithm.

The best known algorithms for the POLYGON PARTITIONING PROBLEM cited above all use the same approach, but are based on techniques to solve the matching problem faster by exploiting the special structure of the bipartite graph.

# 4.2 Polygon Decomposition and Design Rule Checking

We now consider a problem already touched in Chapter 3: How to decompose polygons into rectangle sets such that certain design rules can be checked on the

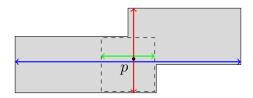

Figure 4.1: Three different possibilities to measure the width of the polygon at p: In blue the horizontal extension of the polygon at p, in red the vertical extension at p, and in green the edge length of a largest inscribed square containing p (see Definitions 4.5 and 4.12).

resulting rectangles, giving the same results as if checked on the polygons? A related problem is to preprocess polygons in a way such that later design rule checking queries can be processed faster. We will show that these problems can be solved efficiently for one of the most important classes of design rules, width-dependent mindist rules.

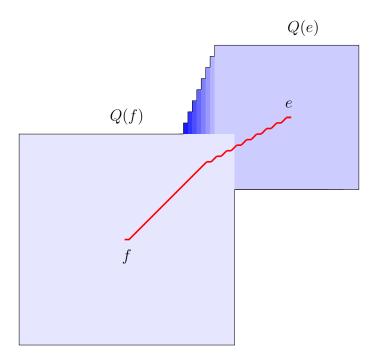

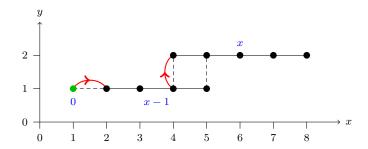

We first have to specify how the width of a polygon at a certain point is defined. There are different possible measures as illustrated in Figure 4.1. We will consider all depicted width measures (being the most important used in the context of VLSI design rules), the one-dimensional width (x-width in blue, y-width in red in Figure 4.1) in Section 4.2.1 and the two-dimensional width (green in Figure 4.1) in Section 4.2.2.

Now let us assume that we are given one of these width measures as an oracle function w, such that w(p, P) is the width at point  $p \in P$  for a rectilinear polygon P.

**Definition 4.3.** Given a width measure w, the width class of size s is the set  $C_s := \{p \in P \mid w(p, P) = s\}$ . A decomposition of P into interior-disjoint rectangles with the property that  $w(\cdot, P)$  is constant within the interior of each rectangle is called a width decomposition of P with respect to w.

**Definition 4.4.** A (width-dependent) mindist rule is a function  $\delta : \mathbb{R} \times \mathbb{R} \to \mathbb{R}$ . For two rectilinear polygons P and Q and two points  $p \in P$  and  $q \in Q$ , we say that p and q satisfy  $\delta$  if  $d_2(p,q) \geq \delta(w(p,P),w(q,Q))$ . We say that P and Q satisfy  $\delta$  if  $d_2(p,q) \geq \delta(w(p,P),w(q,Q))$  for all  $p \in P, q \in Q$ .

The following important subproblems in design rule checking (see Schulte [2012]) have to be solved millions of times in VLSI routing.

#### POINT DISTANCE RULE CHECKING PROBLEM

**Instance:** Two rectilinear polygons P and Q, two points  $p \in P$  and  $q \in Q$ ,

and a mindist rule  $\delta$ .

**Task:** Report if p and q satisfy  $\delta$ .

#### POLYGON DISTANCE RULE CHECKING PROBLEM

**Instance:** Two rectilinear polygons P and Q, and a mindist rule  $\delta$ .

**Task:** Report if P and Q satisfy  $\delta$ .

Since polygons representing pins or blockages on a chip are fixed during VLSI routing, it makes sense to spend some preprocessing time on these structures to speed up the frequent distance rule checking queries later on. The Point Distance Rule Checking Problem essentially reduces to querying  $\mathbf{w}(p, P)$ , so we get to the following problem.

POLYGON WIDTH QUERY PROBLEM

**Instance:** A rectilinear polygon P.

**Task:** Build a data structure which can report for any point  $p \in P$

the width w(p, P) fast.

Given a width decomposition of P, the Polygon Distance Rule Checking Problem reduces to checking distances between rectangles only (which is actually done in BonnRoute, see Schulte [2012] for more details), motivating the following problem.

#### POLYGON WIDTH DECOMPOSITION PROBLEM

**Instance:** A rectilinear polygon P.

**Task:** Compute a width decomposition of P with respect to w.

We now show how to solve the Polygon Width Query Problem and the Polygon Width Decomposition Problem efficiently for both one-dimensional and two-dimensional width measures. Typically the polygons occurring in the above applications are simple in practice, but we also cover polygons with holes.

# 4.2.1 One-Dimensional Width Decomposition

**Definition 4.5.** The x-width (y-width) of a rectilinear polygon P at a point  $p \in P$ , denoted as  $w_x(p, P)$  ( $w_y(p, P)$ ), is the maximum horizontal (vertical) length of a rectangle R with  $p \in R \subseteq P$ , where R is called x-width (y-width) representative for p.

In contrast to the examples in Figure 4.1 we here use the maximum length of a rectangle instead of a line segment to simplify degenerated situations. Our goal is to decompose a given rectilinear polygon P into an interior-disjoint rectangle set S containing x-width (or y-width) representatives for all  $p \in P$ . Clearly such an S also serves as a width decomposition, solving the POLYGON WIDTH DECOMPOSITION PROBLEM with respect to x-width (or y-width).

Intuitively such a decomposition forces its rectangles to be maximally extended (see Figure 4.2) which is formalized in the following definition.

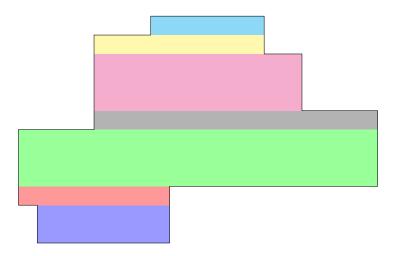

Figure 4.2: A width decomposition of a simple polygon with respect to  $w_x$ .

**Definition 4.6.** We call a rectangle set S x-maximized (y-maximized) if the left and right edge (the bottom and top edge) of each rectangle in S are completely contained in  $\partial(\cup S)$ .

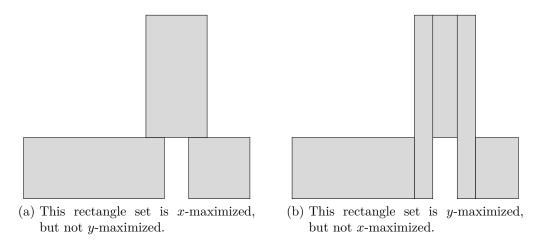

See Figure 4.3 for examples. The following lemma shows that our desired decomposition has to be an x-maximized (or y-maximized) rectangle set.

**Lemma 4.7.** Given a polygon P and an interior-disjoint rectangle set S covering the same area as P, then S is x-maximized (y-maximized) if and only if for each point  $p \in P$  there is an x-width (y-width) representative in S.

*Proof.* W.l.o.g. we consider the horizontal case. First suppose that S is not x-maximized, then we choose a rectangle R in S with a segment  $s = \{x\} \times [y_1, y_2]$  in its left or right border not intersecting  $\partial P$ . Now we choose a point  $p \in R^{\circ}$  with  $y_1 < y(p) < y_2$ . We have  $w_x(p, R) < w_x(p, P)$  and the only rectangle of S covering p is R (note that S is interior-disjoint), so p has no x-width representative in S.

On the other hand, an x-maximized rectangle set S covering P clearly contains x-width representatives for any point  $p \in P$  since every rectangle in S has maximal extension in x-dimension.

Now we can reformulate our decomposition problem as follows, adding the objective to use as few rectangles as possible.

#### Polygon Stripe Partitioning Problem

**Instance:** A rectilinear polygon P and a dimension d (x or y).

**Task:** Compute a minimum d-maximized and interior-disjoint rectan-

gle set covering the same area as P.

We now characterize optimal solutions for this problem. Let  $r_{\text{hor}}$  and  $r_{\text{ver}}$  be optimal solutions for the Polygon Stripe Partitioning Problem for dimension

Figure 4.3

x and y, respectively, and let  $c_{\text{hor}}$  and  $c_{\text{ver}}$  be the number of horizontal and vertical special chords of P, respectively. We need the following lemma which is similar to Theorem 4.2 (again m is the number of concave vertices and h is the number of holes in P).

**Lemma 4.8.**

$$r_{\text{hor}} = m - c_{\text{hor}} - h + 1$$

and  $r_{\text{ver}} = m - c_{\text{ver}} - h + 1$ .

*Proof.* W.l.o.g. we consider the horizontal case. Our proof is constructive, more precisely we construct the unique optimal solution for the POLYGON STRIPE PARTITIONING PROBLEM in dimension x and deduce the claimed equality from it.

Let C be the set of horizontal chords in P which contain at least one concave vertex of P. Let k be the number of connected components into which  $P \setminus \bigcup C$  decomposes. The boundaries of these connected components define an x-maximized and interior-disjoint rectangle set S which covers P, where |S| = k. We claim that  $k = m - c_{\text{hor}} - h + 1$ .

We first assume h=0. Then P is simply-connected, and successively subtracting all chords in C from P increases the number of connected components by |C| (one in each step), thus we obtain k=|C|+1. We have  $m=|C|+c_{\text{hor}}$  because the elements in C cover each concave vertex of P, but we have to count special chords of C twice. The combination of both equalities yields  $k=m-c_{\text{hor}}+1$ .

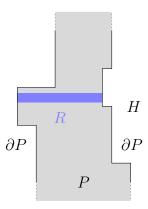

If h > 0, then we choose an arbitrary hole H and a leftmost vertical segment s in  $\partial H$ . We choose a rectangle  $R \subseteq P$  whose right border is contained in  $s^{\circ}$  and whose left border is contained in the interior of another vertical segment in  $\partial P \setminus \partial H$ , see Figure 4.4. The closure of  $P \setminus R$  defines a new polygon which we denote as P'. We have C' = C, h' = h - 1, m' = m,  $c'_{\text{hor}} = c_{\text{hor}}$ , and k' = k + 1, where C', h', m',  $c'_{\text{hor}}$ , and k' are defined analogously. By induction we obtain  $k = m - c_{\text{hor}} - h + 1$  as claimed.

Figure 4.4

Since  $\mathcal{S}$  is a valid solution for the POLYGON STRIPE PARTITIONING PROBLEM in dimension x, we have  $r_{\text{hor}} \leq |\mathcal{S}| = m - c_{\text{hor}} - h + 1$ . On the other hand, rectangles of an arbitrary x-maximized and interior-disjoint rectangle set cannot cross any chord of C, implying that  $\mathcal{S}$  is the unique optimal solution and  $r_{\text{hor}} = k = m - c_{\text{hor}} - h + 1$ .  $\square$

The unique optimal solution for the horizontal Polygon Stripe Partitioning Problem given in the above proof can be constructed in optimal linear time for simple polygons. Fournier and Montuno [1984] described a decomposition of a general simple polygon into trapezoids which gives exactly this optimal solution when applied to a rectilinear simple polygon. They also showed that this decomposition can be obtained from a polygon triangulation in O(n) time, thus for simple polygons we can apply Chazelle's famous linear time triangulation algorithm (Chazelle [1991]) and achieve a linear total runtime for the Polygon Stripe Partitioning Problem.

Despite the theoretically optimal runtime, the above approach is not very practicable since the linear time polygon triangulation method is quite involved. In the BonnTools software collection we implemented a standard sweep line approach, where (for the x-maximized case) the sweep line moves from bottom to top and keeps track of all intersecting vertical polygon segments at each time in a balanced binary search tree. Along the way all rectangles of the partition can be easily built. The worst-case runtime of this algorithm is  $O(n \log n)$  which can be easily proved by standard arguments for sweep line algorithms. Because there are only simple data structures involved, it is very fast in practice, and it also generalizes to polygons with holes. See [Boissonnat et al., 1998, Chapter 12] for more details on a similar sweep approach.

We obtain the following results for the POLYGON WIDTH DECOMPOSITION PROBLEM and POLYGON WIDTH QUERY PROBLEM with respect to one-dimensional width.

**Theorem 4.9.** Given a rectilinear polygon P and a dimension d (x or y), a width

decomposition of P with respect to  $w_d$  containing a minimum number of rectangles  $(m-c_{hor}-h+1\ many)$  can be computed in  $O(n\log n)$  time. If P is simple, then the runtime reduces to O(n).

*Proof.* By Lemma 4.7, solving the POLYGON STRIPE PARTITIONING PROBLEM does the job, producing  $m - c_{\text{hor}} - h + 1$  rectangles by Lemma 4.8. The runtimes are obtained from the results above.

**Corollary 4.10.** Given a rectilinear polygon P and a dimension d (x or y), we can build a data structure in  $O(n \log n)$  time using O(n) space which is able to report a d-width representative for any given point  $p \in P$  in  $O(\log n)$  time. If P is simple, then the preprocessing time reduces to O(n).

*Proof.* We compute a width decomposition of P, build a point location data structure in time O(n) (see e.g. Kirkpatrick [1983]) which reports for any  $p \in P$  its (at most two) covering rectangles in time  $O(\log n)$ , and we report the larger one (w.r.t. d-width) of these rectangles.

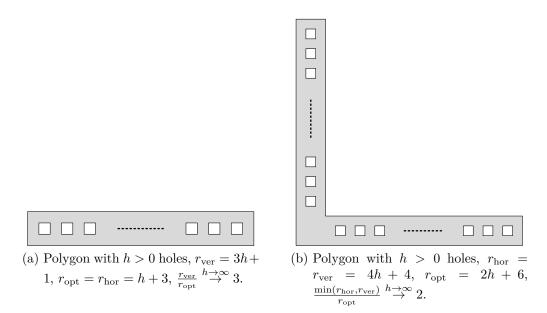

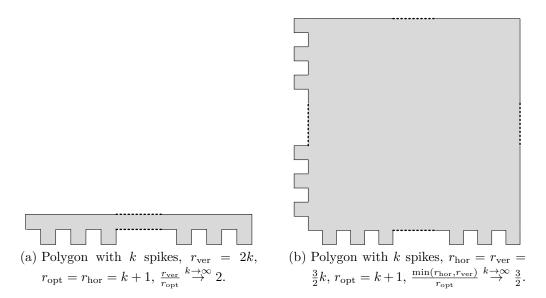

Since optimal stripe partitioning (in x or y dimension) serves as a nice unique representation for rectilinear polygons as rectangle sets, it is an interesting question how far from optimal (in terms of the number of rectangles used for the representation) this representation is in the worst case. Next we prove some sharp bounds, justifying that stripe partitioning is used as the standard decomposition method for rectilinear polygons in the BonnTools. For this the sweepline approach sketched above is used. In the following theorem we use the same notations as in Lemma 4.8.

**Theorem 4.11.** Let P be a rectilinear polygon with h holes. We have

$$\frac{r_{\text{hor}}}{r_{\text{opt}}} \le \begin{cases} 2 & \text{if } h = 0 \\ 3 & \text{else} \end{cases}, \qquad \frac{r_{\text{ver}}}{r_{\text{opt}}} \le \begin{cases} 2 & \text{if } h = 0 \\ 3 & \text{else} \end{cases}, \qquad \frac{\min(r_{\text{hor}}, r_{\text{ver}})}{r_{\text{opt}}} \le \begin{cases} \frac{3}{2} & \text{if } h = 0 \\ 2 & \text{else} \end{cases}$$

The above inequalities are best possible. In particular, running an algorithm for the Polygon Stripe Partitioning Problem for both dimensions and taking the solution with less rectangles is a 2-approximation algorithm for the Polygon Partitioning Problem. If the polygon is simple we have an approximation guarantee of  $\frac{3}{2}$ .

*Proof.* The first estimation follows by

$$\frac{r_{\text{hor}}}{r_{\text{opt}}} = \frac{m - c_{\text{hor}} - h + 1}{m - c - h + 1} \le \frac{m - h + 1}{\frac{m}{2} - h + 1} \le \begin{cases} 2 & \text{if } h = 0\\ \frac{\frac{3}{4}m + 1}{\frac{1}{4}m + 1} \le 3 & \text{else} \end{cases}$$

Here we use Theorem 4.2 and Lemma 4.8 for the first equality,  $c \leq \frac{m}{2}$  for the first inequality, and  $h \leq \frac{m}{4}$  for the else case. The proof for  $\frac{r_{\text{ver}}}{r_{\text{out}}}$  is analogous.

Figure 4.5

The third estimation follows by

$$\frac{\min(r_{\text{hor}}, r_{\text{ver}})}{r_{\text{opt}}} = \frac{m - \max(c_{\text{hor}}, c_{\text{ver}}) - h + 1}{m - c - h + 1} \le \frac{m - \frac{c}{2} - h + 1}{m - c - h + 1}$$

$$\le \frac{\frac{3}{4}m - h + 1}{\frac{m}{2} - h + 1} \le \begin{cases} \frac{3}{2} & \text{if } h = 0\\ \frac{\frac{2}{4}m + 1}{\frac{1}{4}m + 1} \le 2 & \text{else} \end{cases}$$

We use Theorem 4.2 and Lemma 4.8 for the first equality,  $c_{\text{hor}} + c_{\text{ver}} \geq c$  for the first inequality,  $c \leq \frac{m}{2}$  for the second inequality (note that the fraction attains its maximum value for  $c = \frac{m}{2}$ ), and  $h \leq \frac{m}{4}$  for the else case.

The examples in Figure 4.5 and Figure 4.6 show that the bounds are best possible for all cases.

In practice, stripe partitioning is typically much closer to the optimal solution as expressed by these worst-case bounds.

## 4.2.2 Two-Dimensional Width Decomposition

We now consider a width measure for polygons taking both dimensions into account.

**Definition 4.12.** The (two-dimensional) width of a rectilinear polygon P at a point  $p \in P$ , denoted as  $w_{2D}(p, P)$ , is the edge length of a largest square Q with  $p \in Q \subseteq P$ . We call Q width representative for p.

26

Figure 4.6

See the green line in Figure 4.1 on page 20 for an example. In the following we will always use  $w_{2D}$  as width measure. We consider the following two problems.

## POLYGON 2D WIDTH DECOMPOSITION PROBLEM

**Instance:** A rectilinear polygon P.

**Task:** Compute a width decomposition of P with respect to  $w_{2D}$ .

## POLYGON 2D WIDTH QUERY PROBLEM

**Instance:** A rectilinear polygon P.

**Task:** Build a data structure which can report for any point  $p \in P$  a

width representative for p with respect to  $w_{2D}$  fast.

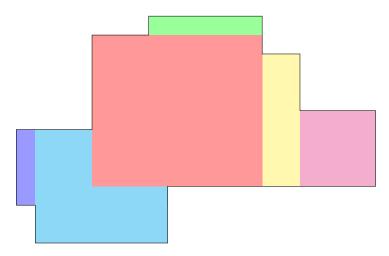

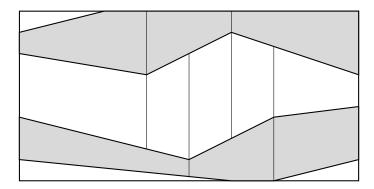

See Figure 4.7 for an example of a width decomposition with respect to  $w_{2D}$ . We first want to mention some work related to these problems.

If we are only interested in a largest width representative, that means a largest inscribed square in a polygon, we are dealing with largest empty circle problems which have been well-known in computational geometry for a long time. In its original form (Shamos and Hoey [1975]) a finite set of points in the plane is given and one is searching for the largest circle centered within the convex hull of the points and not containing any of the points in its interior. Shamos and Hoey [1975] showed how to solve this problem in  $O(n \log n)$  time using Voronoi diagrams. The problem of finding a largest empty square can be solved similarly in  $O(n \log n)$  time using  $L_{\infty}$  Voronoi diagrams (Hwang [1979], Lee and Wong [1980]). If we are given pairwise non-intersecting (but possibly touching) line segments instead of points,

Figure 4.7: A width decomposition of a simple polygon with respect to w<sub>2D</sub>.

then a largest empty square can still be obtained in  $O(n \log n)$  time by using the  $L_{\infty}$  Voronoi diagrams of line segments (Papadopoulou and Lee [2001]). This can also be used to obtain a largest inscribed square in a (not necessarily rectilinear) polygon by taking border edges of the polygon as segments.

Kaplan and Sharir [2012] considered the problem where the width measure w(p, P) is defined in terms of the radius of the largest disk that contains p but whose interior avoids P, where P is a set of n points in the plane. They showed that w(p, P) can be queried in time  $O(\log^2 n)$  after a preprocessing step taking  $O(n \log^2 n)$  time and  $O(n \log n)$  space.

A similar problem, where P is a simple polygon and w(p, P) is the radius of the largest disk inside of P containing p, was studied by Augustine et al. [2013]. They provide a solution where w(p, P) can be queried in time  $O(\log n)$  using  $O(n \log^2 n)$  preprocessing time and  $O(n \log n)$  space.

Boissonnat et al. [2001] showed that it is possible to preprocess a convex polygon P in O(n) time and space, such that given as a query a set of k points, the largest disk inside of P enclosing all k points may be computed in  $O(k \log n)$  time and O(n+k) space.

Augustine et al. [2010] proved that the problem of finding a rectangle of maximum area that avoids a given point set can be solved in  $O(\log n)$  query time, given  $O(n^2 \log n)$  time and space preprocessing.

The latter problem was also solved by Kaplan et al. [2012], using  $O(n\alpha(n)\log^4 n)$  preprocessing time,  $O(n\alpha(n)\log^3 n)$  space, and  $O(\log^4 n)$  query time, where  $\alpha(n)$  is the inverse Ackermann function.

Dumitrescu and Jiang [2012] studied the number of maximal empty axis-parallel rectangles (or boxes, in higher dimension) among a randomly chosen point set.

In the following we present a new algorithm solving the POLYGON 2D WIDTH DECOMPOSITION PROBLEM in optimal linear time for simple rectilinear polygons,

Figure 4.8: Illustration of degenerated case.

reporting a linear number of rectangular width regions. Using this result, we are able to build a data structure in linear time and size which is able to answer width queries in  $O(\log n)$  time. For rectilinear polygons with holes the preprocessing time increases to  $O(n \log n)$ . Note that for our applications in VLSI design polygons are usually simple.

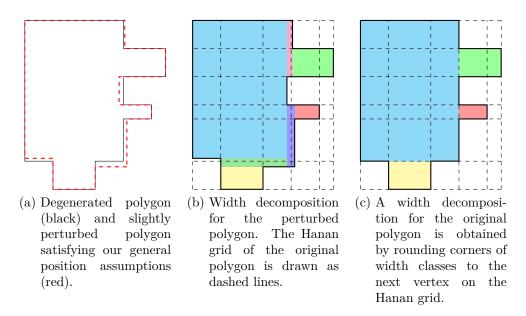

To simplify our proofs, we assume that P is in general position in the following sense. We assume that no two horizontal segments of  $\partial P$  have the same y-coordinate and no two vertical segments of  $\partial P$  have the same x-coordinate. Let  $c_1, c_2, \ldots, c_n$  be the x-coordinates of vertical segments and the y-coordinates of horizontal segments of  $\partial P$  (ordered arbitrarily). We assume that for any four distinct indices  $i, j, k, l \in \{1, 2, \ldots, n\}$  we have  $c_i - c_j \neq c_k - c_l$ . In other words, no difference between two coordinates occurs more than once.

Of course, polygons occurring in VLSI design do not fulfill these assumptions in general. Typically there are many segments that have equal x- or y-coordinates. However, we can achieve all conditions by slightly perturbing the input data. After applying our algorithm to the perturbed polygon, we can round the borders of the width classes to the next x- and y-coordinates occurring in vertices from the original polygon. This works because the shapes of width classes vary continuously with changes of the coordinates in P. This procedure is illustrated in Figure 4.8. For more details on standard perturbation techniques for geometric algorithms see Seidel [1998]. Instead of perturbing the data, the algorithm can also be adapted such that the general position assumption is not necessary.

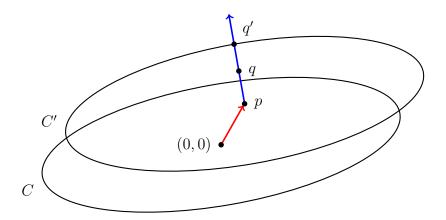

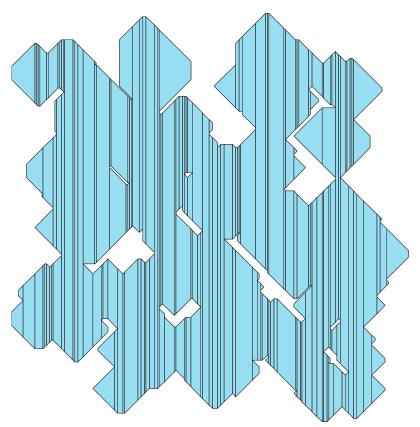

Our algorithm makes use of the  $L_{\infty}$  Voronoi diagram of P.

**Definition 4.13.** The  $L_{\infty}$  bisector of two line segments  $s_1, s_2$  is the set  $\{x \in \mathbb{R}^2 \mid d_{\infty}(s_1, x) = d_{\infty}(s_2, x)\}$ . The  $L_{\infty}$  Voronoi diagram of P is the set of all points  $p \in P$  for which there exist at least two different border segments  $s_1, s_2$  of P with

$$d_{\infty}(p, s_1) = d_{\infty}(p, s_2) = \min_{q \in \partial P} d_{\infty}(p, q).$$

The  $L_{\infty}$  Voronoi diagram can be computed in time  $O(n \log n)$  for arbitrary polygons (see Papadopoulou and Lee [2001]) and in time O(n) for simple polygons (see Chin et al. [1999]).

We will skip the term  $L_{\infty}$  in the following, when there is no risk for confusion. It is easy to see that the Voronoi diagram is a subset of the union of all bisectors between line segments of the polygon. Therefore, bisectors define the structure of Voronoi diagrams and can be viewed as their basic modules.

Bisectors of line segments may contain two-dimensional parts, see Figure 4.9a. To avoid this, we use lines with slope  $\pm 1$  as bisectors for touching segments instead of original  $L_{\infty}$  bisectors (see again Figure 4.9a). We call them refined bisectors. We are only interested in the parts of the bisectors within P. By our general position assumption, no border segment of an inscribed square in P can have proper intersection with two non-touching segments of  $\partial P$ . This implies that two-dimensional bisector parts between non-touching segments do not appear within P. For more details see [Aurenhammer et al., 2013, Chapter 7] and Papadopoulou and Lee [2001].

Using the refined bisectors to define the Voronoi diagram (more exactly, intersecting the Voronoi diagram with the union of all refined bisectors between any two border segments) results in a refined Voronoi diagram which we denote as  $\mathcal{V}_{\infty}(P)$ . In the following, we only consider this Voronoi diagram which consists of line segments only. We call points on  $\mathcal{V}_{\infty}(P)$  which lie on  $\partial P$  or have at least three incident segments in  $\mathcal{V}_{\infty}(P)$  Voronoi vertices and the parts between these vertices Voronoi edges. For more information on Voronoi diagrams in general and its applications see Aurenhammer et al. [2013] and Okabe et al. [2009].

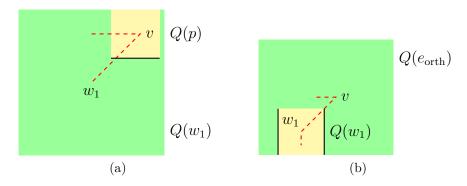

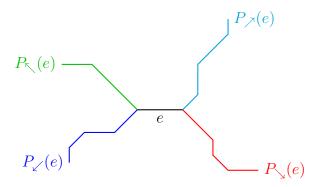

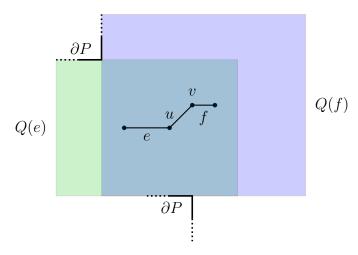

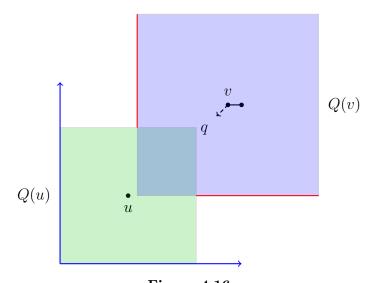

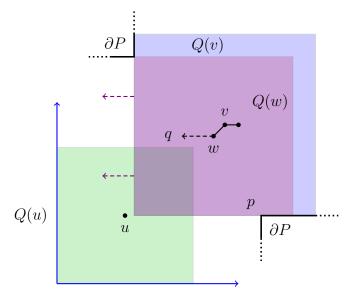

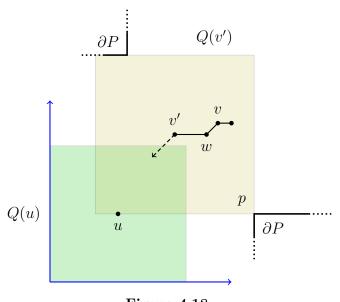

We associate with every point p lying on  $\mathcal{V}_{\infty}(P)$  the unique square Q(p) centered at p and touching the nearest segments of  $\partial P$ . The following simple but important lemma is the key relation between the POLYGON 2D WIDTH DECOMPOSITION PROBLEM and the Voronoi diagram which we use for our algorithm.

**Lemma 4.14.** All width representatives for points in P are of the form Q(q) for some q lying on  $\mathcal{V}_{\infty}(P)$ .

*Proof.* Each width representative Q for some point p touches  $\partial P$  in at least two nontouching segments, otherwise Q could be enlarged within P while still containing p, a contradiction to the definition of width representatives. Therefore, the center of Q lies on  $\mathcal{V}_{\infty}(P)$ .

Before we show how a width decomposition can be obtained efficiently by using this fact we need to prove some structural properties of  $\mathcal{V}_{\infty}(P)$ .

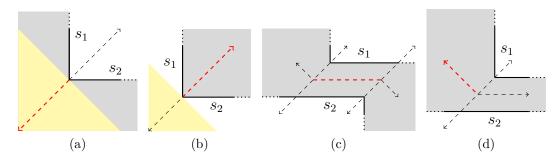

Figure 4.9: Each figure shows a section of a rectilinear polygon (gray) and refined bisectors of its segments in dashed lines. In Figures (a) and (b) the yellow areas are two-dimensional parts belonging to the original, not refined bisectors. Parts contributing to the Voronoi edge of  $s_1$  and  $s_2$  are red.

**Lemma 4.15.** All Voronoi edges of  $\mathcal{V}_{\infty}(P)$  are horizontal, vertical or diagonal segments.

*Proof.* First note that for each Voronoi edge e there exist two segments  $s_1, s_2$  of  $\partial P$ , such that each point on e has the same  $d_{\infty}$ -distance to  $s_1$  and  $s_2$ , and there is no segment of  $\partial P$  with smaller distance (just by definition of the Voronoi diagram, note that this property still holds with our redefined bisectors).

If  $s_1$  and  $s_2$  are touching, then the bisector of the segments is a diagonal line, see Figures 4.9a and 4.9b. Thus the Voronoi edge, being a connected subset of the bisector, is a diagonal segment.

If  $s_1$  and  $s_2$  are non-touching and parallel (say both horizontal, w.l.o.g.), then by our general position assumptions the segments have different y-coordinates. The part of the bisector inside of P consists of at most three pieces, and both endpoints of the horizontal piece intersect bisectors induced by vertices incident to  $s_1$  and  $s_2$  (see Figure 4.9c). The Voronoi edge of  $s_1$  and  $s_2$  clearly cannot cross these bisectors and thus consists of the horizontal segment only.

If  $s_1$  is horizontal and  $s_2$  is vertical (or vice versa), then the part of the bisector inside of P again consists of at most three pieces (see Figure 4.9d). Here only one diagonal part of the bisector contributes to the Voronoi edge, because the Voronoi edge cannot cross the bisector induced by the polygon vertex which causes the break in the bisector of  $s_1$  and  $s_2$ .

Lemma 4.15 implies that  $\mathcal{V}_{\infty}(P)$  can be interpreted as a planar straight-line graph  $G = (V, E_{\text{orth}} \cup E_{\text{diag}})$ , where  $E_{\text{orth}}$  is the set of horizontal and vertical edges and  $E_{\text{diag}}$  is the set of diagonal edges. In the following we identify vertices and edges with their embeddings in the plane. We now collect some statements about the structure of G for later use.

Figure 4.10: Illustration of contradictions in Lemma 4.19 (G in red).

The next two lemmas follow easily from the definition of  $\mathcal{V}_{\infty}(P)$  and our general position assumption, see also the proof of Lemma 4.15 and Figure 4.9.

**Lemma 4.16.** For any edge  $e = \{v, w\} \in E_{orth}$  and any point q on e,  $\partial P$  intersects both border segments of Q(q) which are parallel to e, at least one of them in its interior. If  $q \notin \{v, w\}$ , then both are intersected in their interiors.

**Lemma 4.17.** For any edge  $e \in E_{diag}$  and any distinct  $v', w' \in e$  we have either  $Q(v') \subsetneq Q(w')$  or  $Q(w') \subsetneq Q(v')$ .

**Lemma 4.18.** For all

$$v \in V$$

we have  $|\delta(v) \cap E_{orth}| = \begin{cases} 0, & \text{if } v \in \partial P \\ 1, & \text{if } v \in P \setminus \partial P \end{cases}$ .

*Proof.* If  $v \in \partial P$ , then v is a vertex of P and the only Voronoi edge containing v is diagonal (see Figures 4.9a and 4.9b), proving  $|\delta(v) \cap E_{\text{orth}}| = 0$ .

If v is a Voronoi vertex in  $P \setminus \partial P$ , then by our general position assumptions there is exactly one border segment of Q(v) whose interior does not intersect  $\partial P$ , thus we can move Q(v) in direction of this segment while touching two parallel border segments of  $\partial P$ , implying the existence of an incident horizontal or vertical Voronoi edge. By the general position assumptions we cannot have two such incident edges, so  $|\delta(v) \cap E_{\text{orth}}| = 1$ .

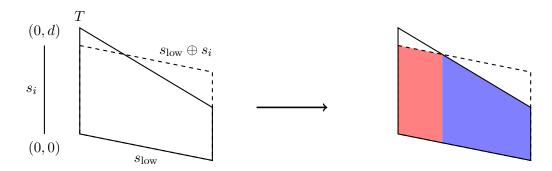

**Lemma 4.19.** Let  $e_{\text{orth}}, e_{\text{diag}} \in E(G)$  be incident edges forming a 45° angle, where  $e_{\text{diag}} = \{v, w_1\}$  is the diagonal and  $e_{\text{orth}} = \{v, w_2\}$  the horizontal or vertical edge. Then  $w_1 \in \partial P$ .

*Proof.* Suppose  $e_{\text{orth}}$  is horizontal and  $e_{\text{diag}}$  leaves the right endpoint of  $e_{\text{orth}}$  to the lower left, all other cases are symmetric.

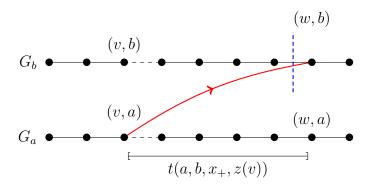

By Lemma 4.17, we have either  $Q(v) \subseteq Q(w_1)$  or  $Q(w_1) \subseteq Q(v)$ . If  $Q(w_1)$  had greater width than Q(v) (see Figure 4.10a), then we could choose a point p in the interior of  $e_{\text{orth}}$  such that the lower border segment of Q(p) (the black line in