# Universität Bonn

# Physikalisches Institut

## The Belle II DEPFET Pixel Vertex Detector: Development of a Full-Scale Module Prototype

### Mikhail Lemarenko

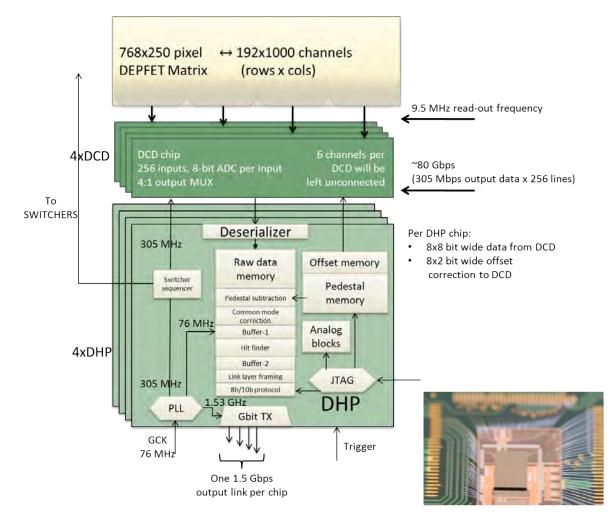

The Belle II experiment, which will start after 2015 at the SuperKEKB accelerator in Japan, will focus on the precision measurement of the CP-violation mechanism and on the search for physics beyond the Standard Model. A new detection system with an excellent spatial resolution and capable of coping with considerably increased background is required. To address this challenge, a pixel detector based on DEPFET technology has been proposed.

A new all silicon integrated circuit, called Data Handling Processor (DHP), is implemented in 65 nm CMOS technology. It is designed to steer the detector and preprocess the generated data. The scope of this thesis covers DHP tests and optimization as well the development of its test environment, which is the first Full-Scale Module Prototype of the DEPFET Pixel Vertex detector.

Physikalisches Institut der Universität Bonn Nussallee 12 D-53115 Bonn

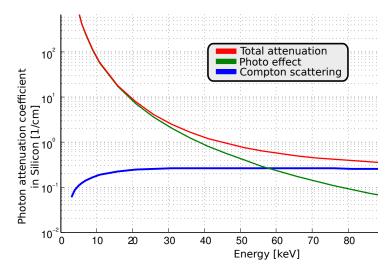

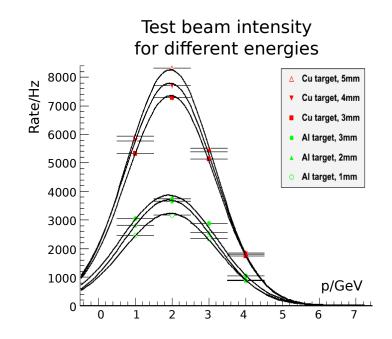

BONN-IR-2013-20 November 2013 ISSN-0172-8741

# Universität Bonn

## Physikalisches Institut

### The Belle II DEPFET Pixel Vertex Detector: Development of a Full-Scale Module Prototype

Mikhail Lemarenko aus Okoulovka

Dieser Forschungsbericht wurde als Dissertation von der Mathematisch-Naturwissenschaftlichen Fakultät der Universität Bonn angenommen und ist 2013 auf dem Hochschulschriftenserver der ULB Bonn http://hss.ulb.uni-bonn.de/diss\_online elektronisch publiziert.

1. Gutachter:Prof. Dr. Norbert Wermes2. Gutachter:Prof. Dr. Klaus Desch

Angenommen am:

31.10.2013

Tag der Promotion:

18.11.2013

### Contents

| 1 | Intro                             | duction                                        | 1                        |

|---|-----------------------------------|------------------------------------------------|--------------------------|

| 2 | <b>Bella</b><br>2.1<br>2.2<br>2.3 | e Upgrade<br>SuperKEKB                         | <b>7</b><br>7<br>8<br>10 |

| 3 | DED                               | FET Pixel Vertex Detector                      | 13                       |

| Ŭ | 3.1                               |                                                | 13                       |

|   | 3.2                               |                                                | 13<br>14                 |

|   | 3.2<br>3.3                        |                                                |                          |

|   | 3.3                               | 1                                              | 16                       |

|   |                                   |                                                | 18                       |

|   |                                   |                                                | 22                       |

|   |                                   | 1                                              | 22                       |

|   | 3.4                               |                                                | 26                       |

|   | 3.5                               |                                                | 26                       |

|   | 3.6                               | Back-end Electronics                           | 32                       |

| 4 | The                               | Data Handling Processor                        | 35                       |

| 1 | 4.1                               | -                                              | 36                       |

|   | 4.2                               |                                                | 37                       |

|   |                                   |                                                | 37                       |

|   |                                   |                                                | 37                       |

|   |                                   |                                                | 38                       |

|   |                                   |                                                | 39                       |

|   |                                   | · · · · · · · · · · · · · · · · · · ·          | 40                       |

|   |                                   |                                                | 40<br>44                 |

|   |                                   |                                                | 44<br>45                 |

|   |                                   |                                                | 43<br>46                 |

|   | 1 2                               | 1                                              | -                        |

|   | 4.3                               |                                                | 46                       |

|   |                                   |                                                | 46                       |

|   |                                   |                                                | 47                       |

|   |                                   | 4.3.3 Other Custom Modules: LVDS, DACs and ADC | 50                       |

| 5 | DHP                               | Architecture Optimization                      | 53                       |

|   | 5.1                               | •                                              | 53                       |

|   |                                   | C C                                            | 53                       |

|   | 5.2                               |                                                | 54                       |

|   | 5.3                               |                                                | 55                       |

|   | 5.4                               |                                                | 55                       |

|                  | 5.5                                                                                                                                                             | C++ Chip Model                                                                                                                                                                                                                                                | 57                                                                                                                                 |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|                  | 5.6                                                                                                                                                             | HDL Chip Verification                                                                                                                                                                                                                                         | 57                                                                                                                                 |

|                  |                                                                                                                                                                 | 5.6.1 UVM Methodology and the Test Environment                                                                                                                                                                                                                | 57                                                                                                                                 |

|                  | 5.7                                                                                                                                                             | DHP 0.2 Optimization                                                                                                                                                                                                                                          | 59                                                                                                                                 |

|                  | 5.8                                                                                                                                                             | Chip Tests and Comparison to its Model                                                                                                                                                                                                                        | 60                                                                                                                                 |

|                  | 5.9                                                                                                                                                             | From DHP 0.2 to DHPT 1.0. Further Optimization                                                                                                                                                                                                                | 61                                                                                                                                 |

|                  |                                                                                                                                                                 |                                                                                                                                                                                                                                                               |                                                                                                                                    |

| 6                | -                                                                                                                                                               | tem Tests                                                                                                                                                                                                                                                     | 65                                                                                                                                 |

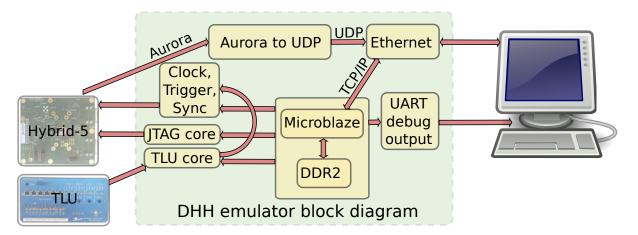

|                  | 6.1                                                                                                                                                             | FPGA DHP Emulation                                                                                                                                                                                                                                            | 65                                                                                                                                 |

|                  |                                                                                                                                                                 | 6.1.1 System                                                                                                                                                                                                                                                  | 65                                                                                                                                 |

|                  |                                                                                                                                                                 | 6.1.2 Results                                                                                                                                                                                                                                                 | 66                                                                                                                                 |

|                  | 6.2                                                                                                                                                             | The Full-Scale Module Prototype of the PXD                                                                                                                                                                                                                    |                                                                                                                                    |

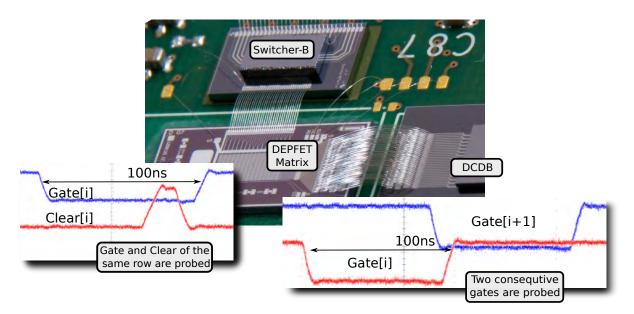

|                  |                                                                                                                                                                 | 6.2.1 Hybrid PCB                                                                                                                                                                                                                                              | 68                                                                                                                                 |

|                  |                                                                                                                                                                 | 6.2.2 FPGA Readout System                                                                                                                                                                                                                                     | 69                                                                                                                                 |

|                  | 6.3                                                                                                                                                             | DHP 0.2 Tests                                                                                                                                                                                                                                                 | 71                                                                                                                                 |

|                  |                                                                                                                                                                 | 6.3.1 System Start                                                                                                                                                                                                                                            | 71                                                                                                                                 |

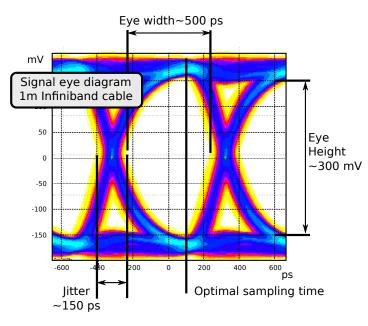

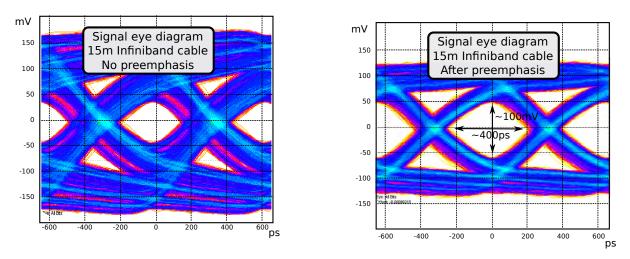

|                  |                                                                                                                                                                 | 6.3.2 Serial Link                                                                                                                                                                                                                                             | 71                                                                                                                                 |

|                  |                                                                                                                                                                 | 6.3.3 DHP 0.2 + DCDB Tests                                                                                                                                                                                                                                    | 73                                                                                                                                 |

|                  | 6.4                                                                                                                                                             | FSMP Tests                                                                                                                                                                                                                                                    | 74                                                                                                                                 |

|                  |                                                                                                                                                                 | 6.4.1 Hybrid-5 Limitations                                                                                                                                                                                                                                    | 74                                                                                                                                 |

|                  |                                                                                                                                                                 | 6.4.2 Matrix Laser Scan                                                                                                                                                                                                                                       | 74                                                                                                                                 |

|                  |                                                                                                                                                                 | 6.4.3 Source Tests                                                                                                                                                                                                                                            | 76                                                                                                                                 |

|                  |                                                                                                                                                                 | 6.4.4 Test Beam Results                                                                                                                                                                                                                                       |                                                                                                                                    |

|                  |                                                                                                                                                                 |                                                                                                                                                                                                                                                               |                                                                                                                                    |

|                  |                                                                                                                                                                 |                                                                                                                                                                                                                                                               |                                                                                                                                    |

| 7                | lec                                                                                                                                                             | hnology SEU sensitivity                                                                                                                                                                                                                                       | 81                                                                                                                                 |

| 7                | <b>Tec</b><br>7.1                                                                                                                                               | Introduction                                                                                                                                                                                                                                                  | <b>81</b><br>81                                                                                                                    |

| 7                |                                                                                                                                                                 |                                                                                                                                                                                                                                                               |                                                                                                                                    |

| 7                | 7.1                                                                                                                                                             | Introduction                                                                                                                                                                                                                                                  | 81<br>82                                                                                                                           |

| 7                | 7.1<br>7.2                                                                                                                                                      | Introduction                                                                                                                                                                                                                                                  | 81<br>82                                                                                                                           |

| 7                | 7.1<br>7.2<br>7.3                                                                                                                                               | Introduction                                                                                                                                                                                                                                                  | 81<br>82<br>87                                                                                                                     |

| 7                | 7.1<br>7.2<br>7.3                                                                                                                                               | Introduction                                                                                                                                                                                                                                                  | 81<br>82<br>87<br>88<br>88                                                                                                         |

| 7                | 7.1<br>7.2<br>7.3                                                                                                                                               | Introduction                                                                                                                                                                                                                                                  | 81<br>82<br>87<br>88<br>88<br>88                                                                                                   |

| 7                | 7.1<br>7.2<br>7.3                                                                                                                                               | IntroductionDefinitionsPXD Related BackgroundThe DHPT 0.1 Chip7.4.1Radiation Facility7.4.2Test Setup7.4.3Measurements                                                                                                                                         | 81<br>82<br>87<br>88<br>88<br>88<br>89<br>90                                                                                       |

| 7                | <ul><li>7.1</li><li>7.2</li><li>7.3</li><li>7.4</li><li>7.5</li></ul>                                                                                           | IntroductionDefinitionsPXD Related BackgroundThe DHPT 0.1 Chip7.4.1Radiation Facility7.4.2Test Setup7.4.3MeasurementsFurther Results                                                                                                                          | 81<br>82<br>87<br>88<br>88<br>89<br>90<br>92                                                                                       |

| 7                | <ul><li>7.1</li><li>7.2</li><li>7.3</li><li>7.4</li><li>7.5</li></ul>                                                                                           | IntroductionDefinitionsPXD Related BackgroundThe DHPT 0.1 Chip7.4.1Radiation Facility7.4.2Test Setup7.4.3Measurements                                                                                                                                         | 81<br>82<br>87<br>88<br>88<br>88<br>89<br>90                                                                                       |

| 8                | <ul> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> </ul>                                                                        | IntroductionDefinitionsPXD Related BackgroundThe DHPT 0.1 Chip7.4.1Radiation Facility7.4.2Test Setup7.4.3MeasurementsFurther Results                                                                                                                          | 81<br>82<br>87<br>88<br>88<br>88<br>89<br>90<br>92                                                                                 |

|                  | <ul> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> </ul>                                                                        | Introduction                                                                                                                                                                                                                                                  | 81<br>82<br>87<br>88<br>88<br>89<br>90<br>92<br>93                                                                                 |

|                  | <ul> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>Contained</li> </ul>                                                     | IntroductionDefinitionsPXD Related BackgroundThe DHPT 0.1 Chip7.4.1 Radiation Facility7.4.2 Test Setup7.4.3 MeasurementsFurther ResultsDHP Sensitivity to SEU                                                                                                 | 81<br>82<br>87<br>88<br>88<br>88<br>89<br>90<br>92<br>93<br>92<br>93                                                               |

|                  | <ul> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>Con</li> <li>8.1</li> </ul>                                              | Introduction                                                                                                                                                                                                                                                  | 81<br>82<br>87<br>88<br>88<br>89<br>90<br>92<br>93<br>93<br><b>97</b><br>97                                                        |

|                  | <ul> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>Con</li> <li>8.1</li> <li>8.2</li> </ul>                                 | Introduction                                                                                                                                                                                                                                                  | 81<br>82<br>87<br>88<br>88<br>89<br>90<br>92<br>93<br>93<br><b>97</b><br>97                                                        |

| 8                | <ul> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>Conn</li> <li>8.1</li> <li>8.2</li> <li>Offilia</li> </ul>               | Introduction .<br>Definitions .<br>PXD Related Background .<br>The DHPT 0.1 Chip .<br>7.4.1 Radiation Facility .<br>7.4.2 Test Setup .<br>7.4.3 Measurements .<br>Further Results .<br>DHP Sensitivity to SEU .<br><b>nclusions</b><br>Summary .<br>Outlook . | <ul> <li>81</li> <li>82</li> <li>87</li> <li>88</li> <li>89</li> <li>90</li> <li>92</li> <li>93</li> <li>97</li> <li>98</li> </ul> |

| 8<br>A<br>B      | <ul> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>Con</li> <li>8.1</li> <li>8.2</li> <li>Offili</li> <li>Online</li> </ul> | Introduction                                                                                                                                                                                                                                                  | 81<br>82<br>87<br>88<br>88<br>89<br>90<br>92<br>93<br>97<br>97<br>98<br>101<br>103                                                 |

| 8<br>A<br>B<br>C | 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br><b>Con</b><br>8.1<br>8.2<br><b>Offli</b><br><b>Onli</b>                                                               | Introduction                                                                                                                                                                                                                                                  | 81<br>82<br>87<br>88<br>88<br>89<br>90<br>92<br>93<br>97<br>97<br>98<br>101<br>103<br>105                                          |

| 8<br>A<br>B      | 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br><b>Con</b><br>8.1<br>8.2<br><b>Offli</b><br><b>Onli</b>                                                               | Introduction                                                                                                                                                                                                                                                  | 81<br>82<br>87<br>88<br>88<br>89<br>90<br>92<br>93<br>97<br>97<br>98<br>101<br>103                                                 |

| Bibliography     | 113 |  |

|------------------|-----|--|

| List of Figures  | 119 |  |

| List of Tables   | 123 |  |

| Acknowledgements | 125 |  |

# Chapter 1 Introduction

Consider the series 0, 1, 2, 3. . . . What is the next term? A good guess is 4. But the formula

$$n + \frac{1}{24}n(n-1)(n-2)(n-3)$$

also generates a series that begins 0, 1, 2, 3... In this case the series continues, not 4, 5, 6... but 5, 10, 21...

Martin Gardner New Mathematical Diversions [1].

Since ancient times people have attempted to understand nature in order to discover the fundamental laws that govern our universe. The hope that all observations could fit into one simple model has not yet been justified: the more we learn about this world, the theories needed to describe it become increasingly sophisticated.

Modern science has experienced a true revolution over the last 200 years. Until the beginning of the 19<sup>th</sup> century, very little was known about the basic structure of matter and its fundamental forces. Ancient Greek philosophers suggested the existence of indivisible pieces of matter, so-called *atoms* (from Greek  $\alpha \tau o \mu o \varsigma$ = atomos), but for many centuries this theory remained speculative. In 1897 J. J. Thomson discovered the electron by observing the *cathode rays* emitted from a hot filament. He demonstrated that these rays can be bent by a magnetic field and suggested that this was a stream of charged particles that he called *corpuscules*. This was soon followed by the discovery of the proton, neutron, positron and so on. By the mid 1960s, more than a hundred *elementary* particles were already known. Their embarrassingly large amount suggested that a more fundamental classification was necessary.

At present, the established theory of elementary particles and their interactions is called The Standard Model (SM). According to the SM, all matter consists of just three kinds of elementary particles (and their anti-partners): leptons, quarks and force mediators.

#### Symmetries in Nature

One of the fundamentals of modern physics is the notion of conserved quantities. Our intuition suggests that nature respects a certain class of symmetries. For example, we know from daily life that the outcome of identical experiments should be the same regardless of place, time or orientation in space. In fact, to each of these symmetries a corresponding conservation law can be assigned. In 1918 the German mathematician Emmy Noether published her famous theorem [2] in which she formalized the link between conservation laws and continuous symmetries.

Furthermore, we intuitively agree that a mirror image of a valid physical process should also be a valid physical process. This is known as the parity symmetry ( $\mathbf{P}$ ). Other examples of discrete symmetries are the time reversal symmetry ( $\mathbf{T}$ ) and the charge conjugation symmetry ( $\mathbf{C}$ ). These were accepted to be true symmetries for all processes in nature. There was such a firm belief that physics laws ought to be invariant under these transformations, that the validity of this assumption was never actually verified.

#### **CP–Violation**

A paradox, known as the "Theta-Tau Puzzle", arose in in the early 1950s of the past century [3]. Two newly discovered mesons, called  $\theta^+$  and  $\tau^+$ , were identical in every respect (mass, charge, spin and so on) except their decays ( $\theta^+$  decays into two pions and  $\tau^+$  into three pions), this suggested that they had different parities.

Yang and Lee proposed that  $\theta^+$  and  $\tau^+$  are in reality the same particle (nowadays known as  $K^+$ ), and that **P** is simply not conserved in one of the decays. This suggestion was confirmed by the experiment conducted by Chien-Shiung Wu on radioactive Cobalt 60, in which **P** was shown to be violated in weak interactions [4]. These results were published in 1957.

In the article published in the same year Lev Landau put forward the argument [5] that if  $\theta - \tau$  were not the same, the lifetime difference in neutrino involved decays should be observed. This was not experimentally confirmed and he concluded that it was indeed a unique particle. Therefore, he indirectly demonstrated that **P** was violated in weak interactions. To restore the broken parity symmetry, he introduced a new Charge-Parity (**CP**) transformation (a combination of **C** and **P**). For a number of years this transformation was believed to hold in all interactions.

However, in 1963 Cronin and Fitch reported a weak **CP**-violation observed in neutral kaon ( $K^0$ ) decays [6]. Later it was also shown for the first time that **CP** makes a distinction between matter and antimatter. For a long time this phenomenon had remained an unresolved issue until M. Kobayashi and T. Maskawa proposed a mechanism describing **CP**-violation in 1973 [7].

In fact, it is currently believed that **CP**-violation is a factor responsible for the existence of the universe as we know it. It was stated in 1967 by Andrei Sakharov [8] as one of the three necessary conditions for baryogenesis<sup>1</sup>. However, the amount of **CP**-violation discovered thus far is too small to describe the matter-antimatter asymmetry observed in the universe and more **CP**-violation sources are required.

#### **B-Factories**

For many years, neutral kaons was the only particle system for **CP**-violation studies. After the bottom quark discovery it was pointed out that neutral B-mesons can also be used for research into **CP**-violation. To enable the study of these systems, so-called 'B-factories' were constructed: the BaBar [9] experiment in California and the Belle in Japan [10]<sup>2</sup>.

Both experiments are carried out using a similar premise. For example, the Belle detector is located at the interaction region of an  $e^-/e^+$  collider, called KEKB. The collider is tuned to have a center of mass energy of  $\sqrt{s}=10.59$  GeV, which corresponds to the  $\Upsilon(4S)$  resonance (a  $b\bar{b}$  bound state). This energy is only slightly more than twice the mass of  $B_{0,\pm}$ -meson, such that  $\Upsilon(4S)$  decays almost exclusively to a pair of  $B\bar{B}$  (with a branching ratio higher than 96 %). The use of  $e^-/e^+$  provides a clean measurement environment since the energies of colliding particles are well-known and a high signal to noise

<sup>&</sup>lt;sup>1</sup> There conditions are: (1) Existence of at least one barion number violating process. (2) Existence of **C**- and **CP**-violating processes. (3) Interactions outside of thermal equilibrium.

<sup>&</sup>lt;sup>2</sup> Further in the text we address only the Belle experiment, since this is the topic of the present thesis.

ratio could be achieved<sup>1</sup>. The beam energies are asymmetric giving a non-zero total momentum to the resulting  $B\bar{B}$  states (Lorenz boost); this allows for a better spatial separation of different B-meson decay modes.

$B^0$  and  $\overline{B^0}$  can decay to a common **CP**-eigenstate  $f_{CP}$ , where the transition is dominated by the  $b \rightarrow c\bar{c}s$  process. If **CP**-violation does take place in this case, it can be characterized by the decay rate asymmetry:

$$A(t) = \frac{\Gamma(\bar{B^0} \to f_{CP}) - \Gamma(B^0 \to f_{CP})}{\Gamma(\bar{B^0} \to f_{CP}) + \Gamma(B^0 \to f_{CP})}$$

where  $\Gamma(\bar{B^0}, B^0 \to f_{CP})$  is the rate for  $B^0$  or  $\bar{B^0}$  to  $f_{CP}$  at a proper time *t* after production.

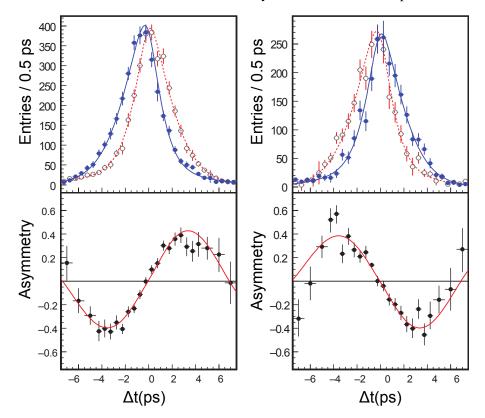

For the case, then the  $f_{CP} = J/\psi K_S$  or  $f_{CP} = J/\psi K_L$ , which are by construction both **CP**-eigenstates, the results of the **CP**-violation observation measured by the Belle detector are presented in Figure 1.1.

Figure 1.1: **CP**-violation observation in Belle for the case then one of the  $B\bar{B}$  mesons decays into the following **CP**-eigenstates:  $J/\psi K_S$  (left) and  $J/\psi K_L$  (right). Information about which one of the B-mesons decayed into the  $f_{CP}$  is extracted from the complimentary B-meson (tag) decay, which is marked in red for the  $B_0$  tags and in blue for the  $\bar{B}_0$  tags [11].

During the operation of the detector until its final shutdown in 2010, the total integrated luminosity reached 1  $ab^{-1}$ . Belle accomplished its main mission, which was the experimental verification of the Kobayashi and Maskawa proposal explaining the **CP**-violation mechanism. This experimental result was explicitly recognized by the Nobel Prize in Physics in 2008. Along with **CP**-violation observations,

<sup>&</sup>lt;sup>1</sup> Other options, like to use protons, are more complicated: a proton, being a composite particle, has its kinetic energy shared by three quarks. Therefore, only an unknown fraction of the proton energy is available for a quark–quark collision, which effectively takes place.

Belle also made important discoveries in charm physics,  $\tau$ -lepton physics, hadron spectroscopy and so on [11].

#### **Belle Upgrade**

For precise measurements of CKM<sup>1</sup> elements and for testing physics beyond the SM more statistical data is needed than has been thus far collected. Therefore, the Belle experiment is currently shut down for an upgrade.

From an accelerator point of view, this translates to the need for a luminosity increase. The planned upgrade of the KEKB (called SuperKEKB) entails two main strategies to achieve this goal: current increase and beam focusing. In total the expected luminosity will be increased by a factor of 40.

To cope with the increased background and the increased event rate a new detector, called Belle II, is being built. The upgraded central Silicon Vertex Detector (VXD) is among the main features of Belle II. For better spatial resolution, two additional layers of pixel detectors are planned together with the existing four strip layers of the VXD. For the implementation of the Pixel Detector (PXD) DEPFET technology was chosen, which has an excellent hit resolution and low material budget. Further details of this upgrade will be given in the next chapter.

#### **The Presented Work**

This thesis is devoted to the development of the Front-End readout of the PXD for Belle II; namely the Data Handling Processor (DHP) and its test environment. The DHP is a sophisticated All-Silicon Integrated Circuit that controls the PXD readout. Its second purpose is to reduce the data rates produced by the detector, which is achieved by discarding all data that does not contain a signal (zero-suppression). To do this efficiently, data have to be corrected for common mode noise and residual fixed pattern noise. To further reduce the quantity of data, an external trigger is applied. Thus, the generated ~3 Tbps of data can be reduced to 60 Gbps, which is limited by the bandwidth of all output links of the detector.

The chip is designed to meet the Belle II design specifications, i.e. to be radiation hard, to support up to 3 % of the data occupancy<sup>2</sup> and to have a high speed output link capable of transmitting the data over about 15 meters.

To meet the design goal, the chip underwent several steps of parameter space optimization and evaluation of radiation hardness. Furthermore, the chip was tested using a new specially designed test environment: a PXD module prototype, including all elements expected to be present in the detector, whilst being scaled down in channel count, i.e. a "full scale module prototype". Finally, the prototype operation was tested during the DESY test beam campaign in Hamburg, confirming that the initial goals have been achieved.

The thesis is structured as follows:

- Chapter 2 introduces the Belle II detector and its main elements. It also discusses upgrade related challenges, such as increased background and its influence on the detector implementation.

- Chapter 3 provides a detailed description of the new PXD and DEPFET technology. The PXD concept, geometry, readout technique and each steering element are presented.

- Chapter 4 introduces the DHP chip and discusses the related conceptual challenges. Furthermore, the proposed solutions are discussed.

<sup>&</sup>lt;sup>1</sup> Cabibbo-Kobayashi-Maskawa matrix.

<sup>&</sup>lt;sup>2</sup> That means that in the worst case scenario one can expect up to 3 % of pixels will contain signal information. However, this signal is mainly due to background and further offline processing to extract relevant physics events is necessary.

- Chapter 5 discusses the chip optimization, which is needed in order to satisfy the Belle II requirements.

- Chapter 6 presents the full scale module prototype of the PXD containing the full readout chain. It is followed by its performance evaluation and first test results.

- **Chapter 7**: discusses some aspects of the technology radiation tolerance. The evaluation of the potential risks and the implemented mitigation techniques are presented.

- **Chapter 8** summarizes the presented work and gives an outlook on the steps still needed to build the PXD.

Parts of the work were previously published [12, 13].

# Chapter 2 Belle Upgrade

The operation of the Belle experiment has stopped since 2010 for the upgrade of the KEKB accelerator and the Belle detector. A schematic representation of SuperKEKB including the Belle II position is sketched in Figure 2.1. In this chapter, a general description of the new experiment is given.

Figure 2.1: SuperKEKB collider and the position of the Belle II.

#### 2.1 SuperKEKB

Within the scope of the current upgrade, the KEKB accelerator will be replaced by its upgraded version, SuperKEKB, whose planned luminosity will be about 40 times higher than the initial one <sup>1</sup>. This will be mainly achieved by an increase of the beam currents  $(3.6/2.6 \text{ A in LER}^2/\text{HER}^3$  against initial 1.64/1.2 A) and by using the so-called Nano-beam scheme, in which the beam width is squeezed in one direction, thus increasing the interaction probability.

The beam-beam asymmetry was decreased from 3.5/8 GeV to 4/7 GeV [14] to solve the problem of an emittance growth due to high intra-beam scattering (see Section 2.3), which appears in the new

$<sup>^{1}</sup>$  2.11×10<sup>34</sup> cm<sup>-2</sup>s<sup>-1</sup> reached in June 2009

<sup>&</sup>lt;sup>2</sup> Low Energy Ring

<sup>&</sup>lt;sup>3</sup> High Energy Ring

Nano-Beam scheme. The smaller beam asymmetry will induce about 30 % poorer vertex resolution. However, this is planned to be compensated by the new detection system.

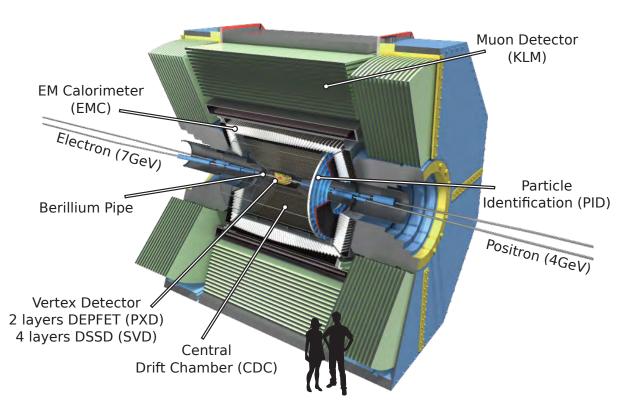

#### 2.2 Belle II

Figure 2.2 presents the Belle II detector. Typically used for collider experiments, Belle II follows an onion-like structure, covering almost the whole solid angle. As previously mentioned, Belle II is an upgraded version of the Belle detector adapted to support higher background event rate and having higher radiation hardness. A superconducting solenoid located in the inner volume of the detector provides a magnetic field of 1.5 T to bend the tracks of the charged particles.

A short description of its main subdetectors is presented below:

- Silicon Vertex Detector (VXD). To enhance *B* and *K<sub>S</sub>* vertices spatial resolution, which are produced near the PXD volume, the four layers of the Double-Sided Silicon Strip Detector (SVD) existing in the Belle design are completed with two layers of the Pixel Detector (PXD). A detailed description of the new PXD is given in Chapter 3.

- Central Drift Chamber (CDC). The CDC starts just after the SVD and extends to a larger radius than Belle previously had. CDC is the central tracking device, measuring the charged particles' track position and their momenta. The measured dE/dx is also used for particle identification. The CDC also provides a fast trigger for charged particles.

- **Particle Identification System (PID).** The PID consists of the Time-Of-Propagation Detector (TOP) and Aerogel Ring Cherenkov Detector (ARICH). Both detectors use the Cherenkov effect for particle identification, especially for separation of kaons from pions.

The Cherenkov effect can be resumed as follows: a particle flying though a medium faster than the speed of light in this medium induces a light cone along its track. The opening angle  $\theta$  of this cone depends on the medium refraction index and the particle velocity according to the following equation:

$$\cos\theta = \frac{1}{n\beta}$$

Cherenkov photons are then collected by UV-sensitive photomultipliers; their positions and arrival times are then registered for further evaluation.

- Electromagnetic Calorimeter (ECL). The ECL encloses the PID and consists of an array of CsI scintillators. It is used to detect and measure the precise energy of electrons and photons.

- $K_L$  and muon detector (KLM) is the outermost Belle II subdetector. The KLM has a sandwich structure of alternating resistive plate chambers (RPC) and iron plates. The KLM distinguishes between muons and  $K_L$  using their respective signal signatures: a muon, having a low interaction cross section, creates a clear localized signature, whereas a  $K_L$  produces hadronic showers, leaving larger clusters.

Figure 2.2: Belle II detector 3D representation, with indication of its main elements. This picture is designed by the Belle II Collaboration.

#### 2.3 Belle II Background

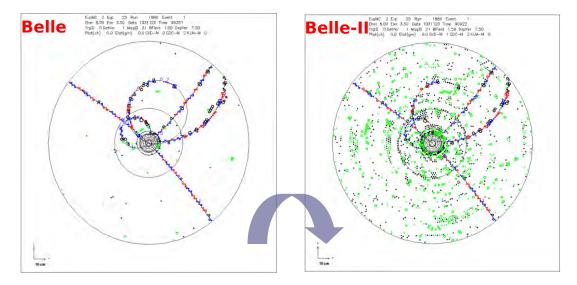

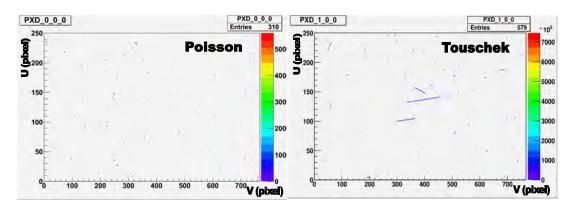

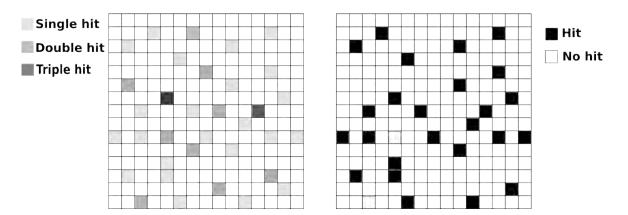

Figure 2.3: Comparative example of the background situation in Belle and Belle II experiments [14]. In the Belle II scenario, the increase of the background will make the zero suppression and the region-of-interest search non-trivial.

As mentioned above, the luminosity increase will be accompanied by a higher background level. Figure 2.3 represents an example of the background increase relative to Belle for a typical physics event. As one can see, the background will be by far the dominant data source of Belle II. It is very important to evaluate this effect for stable detector operation. In particular, the PXD is the most affected element, since it is the closest detector relative to the interaction point.

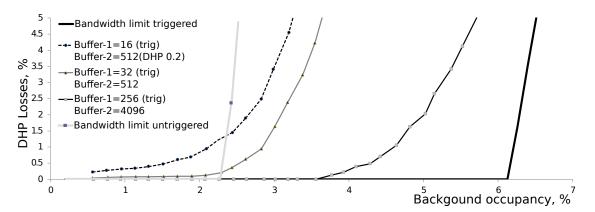

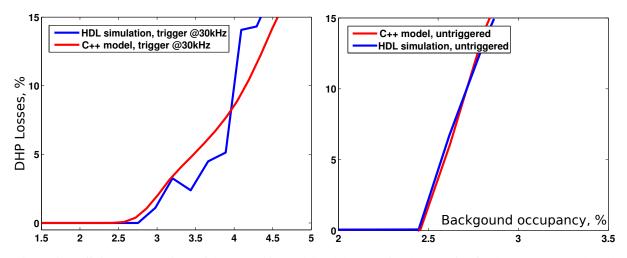

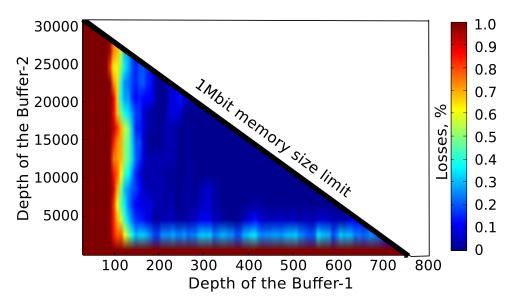

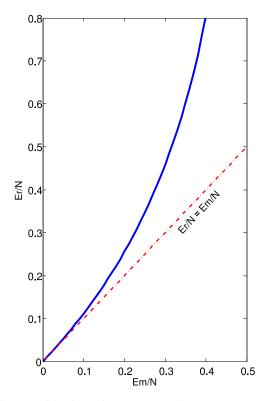

The expected background depends greatly on the implemented beam optics. In this section the main background sources are presented, and their latest simulated estimations are given. This information is relevant for the data processing logic optimization, which is implemented in the Data Handling Processor of the PXD. A detailed discussion about this optimization is presented in Chapter 5.

One can classify the background sources in the following way [15]:

- *Beam-Gas scattering*, or the scattering of the beam on residual gas. This effect is proportional to the product  $I \times P$  (beam current  $\times$  gas pressure). It results in Bremsstrahlung (energy loss due to photon emission) and Coulomb scattering (particle direction change).

- *Touschek effect* is an intra-bunch scattering. This effect is inversely proportional to the beam size and scales with  $E^{-3}$ . Therefore, the contribution from the LER dominates. Large angle Coulomb scattering causes an exchange of energy between the longitudinal and the transverse motion of the particles. Scattered particles leave the nominal beam orbit and hit the vacuum chamber and magnet walls. The resulting secondary shower particles can reach the PXD.

- *Radiative Bhabha scattering*, or e<sup>+</sup>e<sup>-</sup> scattering. In this case most of the scattered e<sup>+</sup>e<sup>-</sup> are lost very far downstream from the IP and are unlikely to produce particles that back-scatter into the detector. However, the emitted photons hit the downstream beam pipe and magnets, generating neutrons. This is the largest neutron background for the PXD (see Chapter 7).

• *Two-photon Radiation (QED)*: low momentum electron-positron pairs are produced via the two-photon process  $e^+e^- \rightarrow e^+e^-e^+e^-$ ; it is one of the largest contributors to the background.

• Synchrotron Radiation (SR). The SR is proportional to  $I \cdot E^2 \cdot B^2$  (the beam current multiplied by the beam energy squared multiplied by the magnetic field squared). This background is mainly localized in the plane of the  $e^+e^-$  ring.

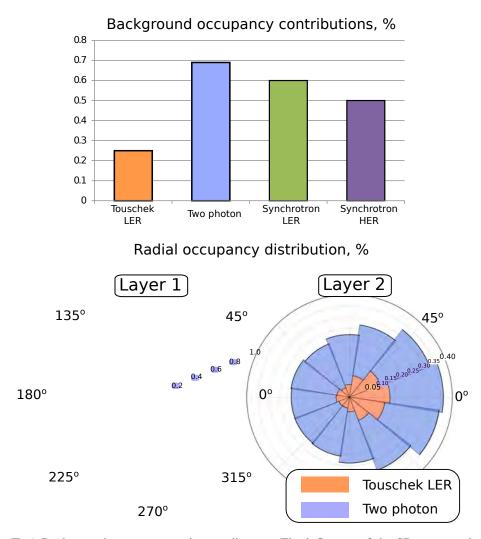

All background sources have a non-uniform contribution for both angular ( $\phi$ ) and longitudinal (z) directions; furthermore, the external layer of the PXD will see lower background as it is further away from the interaction point. A summary of their radial distributions and total occupancies per layer are presented in Figure 2.4 (SR excluded) and Table 2.1 [16]).

Figure 2.4: (Top) Background occupancy main contributors. The influence of the SR was not thoroughly investigated by the Belle II Collaboration at the time of writing this chapter. However, it is expected that the SR will be relevant only for the first layer of the detector for the plane situated in  $\phi$ =0. (Bottom) The background occupancy (in %) radial distribution (SR excluded) for the internal (Layer 1) and the external (Layer 2) PXD layers. [16]

| Background (in %)                  | Source | Layer 1          | Layer 2   |

|------------------------------------|--------|------------------|-----------|

| Two-Photon QED                     |        | 0.69             | 0.24      |

| Synchrotron Radiation <sup>1</sup> | LER    | $(0.6\pm0.15)^2$ | 0.0       |

| Synchrotron Radiation <sup>3</sup> | HER    | $(0.5\pm0.3)^2$  | 0.0       |

| Touschek                           | LER    | 0.25             | 0.18      |

| Radiative Bhabha                   | HER    | 10 <sup>-3</sup> | $10^{-3}$ |

| Radiative Bhabha                   | LER    | $10^{-4}$        | $10^{-4}$ |

| Touschek                           | HER    | 0.0              | 0.0       |

| Beam-Gas Coulomb                   | LER    | 0.0              | 0.0       |

| Beam-Gas Coulomb                   | HER    | 0.0              | 0.0       |

| Total                              |        | $2.05 \pm 0.35$  | 0.42      |

Table 2.1: Latest PXD background occupancy summary presented by the Belle II Collaboration [16, 17].

<sup>&</sup>lt;sup>1</sup> LER: for the half ladder at  $\phi = 0$ . The occupancy in the other ladders can be neglected. Source: Y. Soloviev [17].

<sup>&</sup>lt;sup>2</sup> Preliminary results with high uncertainty due to low statistics.

<sup>&</sup>lt;sup>3</sup> Available data shows that SR radiation background from HER is distributed roughly uniformly over all PXD ladders (mostly scattered photons). Y. Soloviev [17].

# Chapter 3 DEPFET Pixel Vertex Detector

This chapter is about the Pixel Detector (PXD), which consists of two layers of radially distributed sensors based on DEPFET technology. The chapter starts with general considerations as well as the detector concept, followed by a more detailed description of the main parts.

#### 3.1 Detector Resolution

The key point of the PXD is precise reconstruction of the secondary decay vertices in order to distinguish them from the primary ones [18]. This distinction can be made in the following way: a reconstructed particle track is extrapolated back to its origin. If the resulting distance to the interaction point is significantly larger than the detector resolution, it is likely that this particle does not originate from the primary vertex. To satisfy the required precision, which is in the order of several tens of microns, it is important to optimize the total spatial resolution  $\sigma_{tot}$  of the detection system.

$\sigma_{tot}$  is limited by the detector resolution error  $\sigma_{det}$  (geometry dependent) and the multiple scattering error  $\sigma_{MS}$ .  $\sigma_{tot}$  can be approximated by [18]:

$$\sigma_{tot}^2 = \sigma_{det}^2 + \sigma_{MS}^2 \tag{3.1}$$

with

$$\sigma_{MS}^2 = \sum (R_j \Delta \theta_j)^2$$

where  $\Delta \theta_j$  is the scattering angle, while traversing detector layer *j* with radius  $R_j^{-1}$ ;  $\Delta \theta_j$  is approximately given by:

$$\Delta \theta_j = \frac{0.0136}{p[\text{GeV/c}]} \sqrt{\frac{\Delta X_j}{X_0}} \left[ 1 + 0.038 \ln\left(\frac{\Delta X_j}{X_0}\right) \right]$$

(3.2)

for the material of thickness  $\Delta X_j$  with a radiation length  $X_0$ .

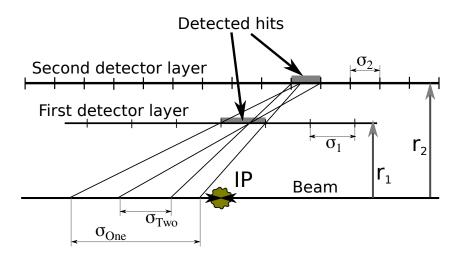

Figure 3.1 depicts a situation with two detector layers, as is envisaged in PXD<sup>2</sup>. In this case, the detector resolution error  $\sigma_{det}$  is a quadratic sum of two layers' resolutions projected on the beam axis  $\sigma_{One}$  and  $\sigma_{Two}$ :

$$\sigma_{det}^2 = \sigma_{One}^2 + \sigma_{Two}^2$$

As depicted,  $\sigma_{One}$  is obtained from the intrinsic resolution error of the first detector layer  $\sigma_1$  by projecting it to the beam axis and assuming  $\sigma_2=0$ . Correspondingly,  $\sigma_{Two}$  is a projection of the  $\sigma_2$  assuming  $\sigma_1=0$ .

<sup>&</sup>lt;sup>1</sup> In case of a single detector, the outermost layer contribution would have been not relevant.

<sup>&</sup>lt;sup>2</sup> Two dimensional simplification.

Figure 3.1: The total detector resolution is a quadratic sum of  $\sigma_{One}$  and  $\sigma_{Two}$ , which are respective projections on the beam axis of the intrinsic layer resolutions  $\sigma_1$  and  $\sigma_2$ , as is presented in the figure.

Furthermore, from simple geometrical considerations it follows that:

$$\sigma_{One} = \sigma_1 \left(\frac{r_2}{r_2 - r_1}\right)$$

$$\sigma_{Two} = \sigma_2 \left(\frac{r_1}{r_2 - r_1}\right)$$

(3.3)

Here  $r_1$  and  $r_2$  are the inner and outer layers' radii.

Several conclusions can be drawn from Equations (3.1) to (3.3) to minimize the  $\sigma_{tot}$ :

- 1. The position  $r_1$  of the first detector layer should be as close to the interaction point as possible.

- 2. The distance between layers  $r_2 r_1$  should be maximized.

- 3. Intrinsic spatial resolutions  $\sigma_1$  and  $\sigma_2$  should be small, especially  $\sigma_1$ .

- 4. The material budget of the detector, especially for its first layer, should be minimized.

Using these criteria, the detector was optimized. Simulation results show [14] that for the proposed geometry (see Section 3.2) the total PXD resolution is estimated to be  $\sigma_{tot} \sim 20 \,\mu\text{m}$ .

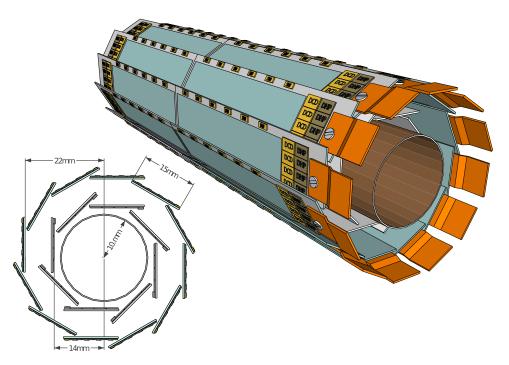

#### 3.2 Overall Structure of the Detector

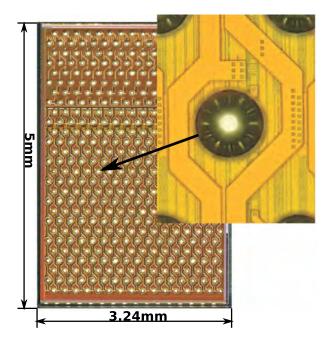

In Figure 3.2 a 3D model of the DEPFET Pixel Vertex Detector (PXD) is portrayed. It consists of two layers of independently controlled modules arranged around the beam pipe (with 10 mm radius). The inner layer is situated 14 mm away from the Interaction Point (IP) and has 8 modules with a Sensitive Area (SA) of 90 mm×12.5 mm; the outer layer is 22 mm away from the IP and has 12 modules with a SA of 124 mm×12.5 mm. Figure 3.3 presents the PXD mechanical prototype.

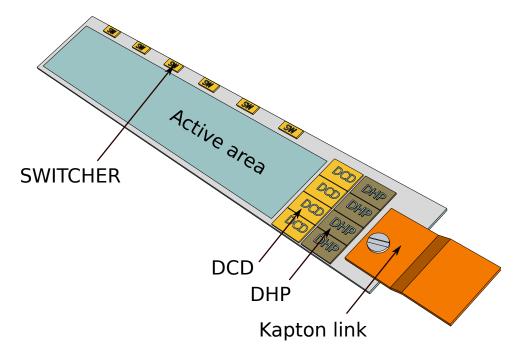

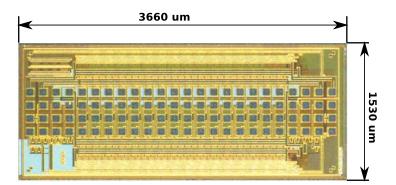

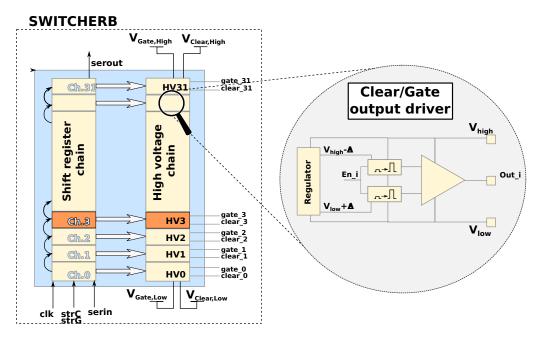

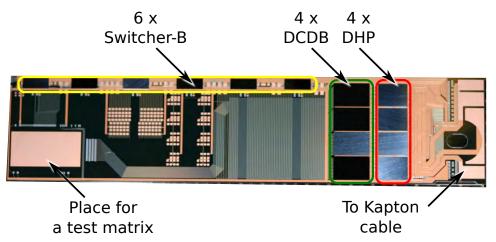

Each PXD module is an all-silicon sensor with its control and readout ASICs<sup>1</sup> directly bump-bonded on the module edges around the sensitive area. To shorten the readout period, modules are split in the middle; each half is separately steered by two independent sets of ASICs, thus each module represents two separate half-modules mechanically attached to each other. An example of this kind of half-module is shown in Figure 3.4; the related ASICs are situated outside the SA. Per half-module there are six Switcher chips responsible for the matrix control; they are situated on the 2 mm wide side-balcony.

<sup>&</sup>lt;sup>1</sup> ASIC is the standard abbreviation for Application Specific Integrated Circuit.

Figure 3.2: Isometric and front view projections of a 3D model of the detector (courtesy of Hans Krüger).

Figure 3.3: The mechanical mock-up with dummy modules of the DEPFET PXD (prepared by the MPI Munich).

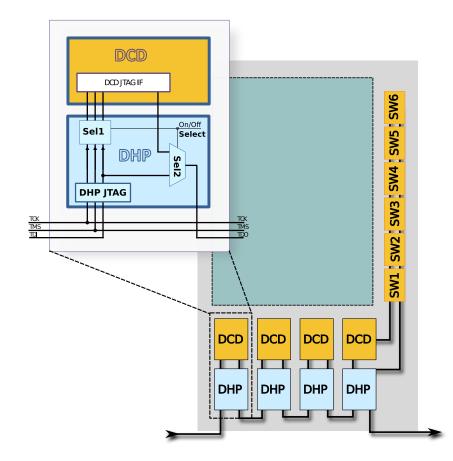

Outside the SA an additional 25 mm wide balcony is foreseen to host other sets of ASIC: four Drain Current Digitizer (DCD) chips and four Data Handling Processor (DHP) chips.

The SA is reduced to 75  $\mu$ m thickness using an anisotropic etching technique [19] to minimize track deviation of crossing particles due to multiple scattering. The balcony and end-of-stave regions have an original silicon wafer thickness (about 400  $\mu$ m) to provide better mechanical stability.

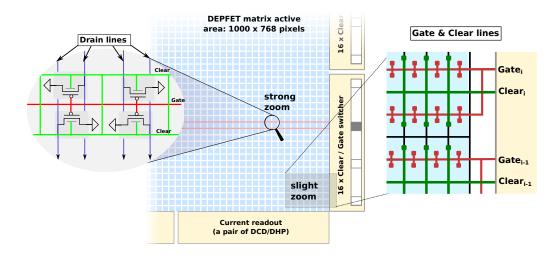

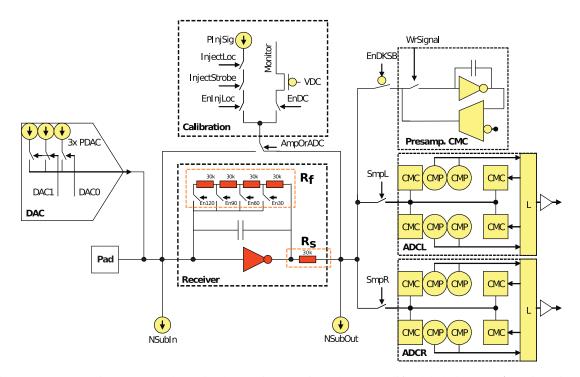

The SA is an array of  $1000 \times 192$  pixels implemented using DEPFET technology (Section 3.3). All drains of pixels belonging to a single column are connected together. The readout of the SA is done row-wise by Switcher chips. The DCD chips digitize drain currents coming from the pixels and the DHP chips pre-process the data and reduce their volume by suppressing pixels with a signal below a

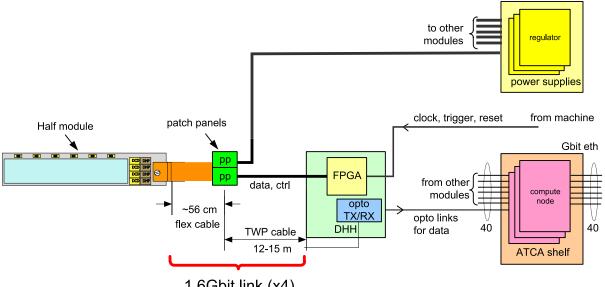

predefined threshold. The produced zero suppressed data is sent to the detector's back-end electronics through a flexible Kapton<sup>®1</sup> cable attached to each module.

Figure 3.4: A sketch of the half-module structure with bump-bonded ASICs (Switcher, DCD and DHP chips) and their arrangements. The slow control, fast synchronization signals and the serial links of the DHP chips are connected to the back-end electronics via a flexible Kapton<sup>®</sup> cable, which is mechanically attached to each module.

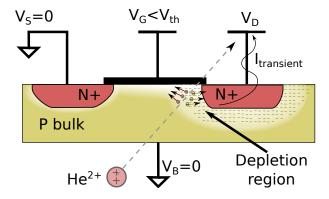

#### 3.3 DEPFET Principle

The original paper published by Kemmer and Lutz in 1987 [21] proposed using either MOSFET or JFET technology for a new detector concept, which will be described below. These concepts were known under the names DEPMOS and DEPJFET respectively. This convention was later abandoned and both implementations are now known under the generic name DEPFET (DEpleted PFET or DEPleted FET depending on publication). Historically, JFET was the preferred option. However, for the Belle II design JFET technology was abandoned in favor of MOSFETs due to feature size issues [22].

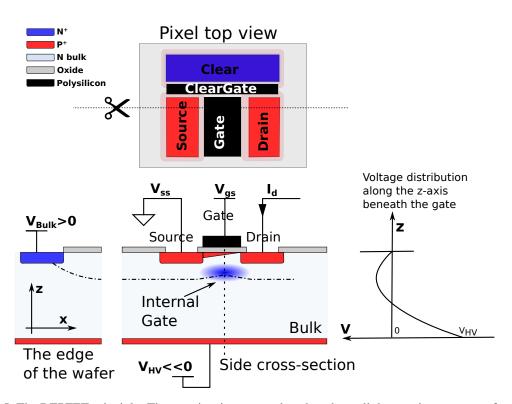

Typically, a DEPFET pixel is a PMOS transistor situated on a high-ohmic bulk. Using the sidewardsdepletion technique [23] (see Section 3.3.1 for details) the bulk is depleted in such a way that a potential minimum for electrons can be created in the region close to the transistor's channel (Figure 3.5). An additional  $n^+$  implantation deposited right beneath the gate of the transistor generates an extra positive space charge, whilst being depleted, additionally confining the minimum in the x-axis. This implantation together with the sidewards-depletion creates a global spatial potential minimum for electrons in the pixel's surrounding neighborhood. The deep–n implantation is called the pixel's internal gate (for reasons described below).

<sup>&</sup>lt;sup>1</sup> Kapton<sup>®</sup> is a polyamide film developed by DuPont that can remain stable in a wide range of temperatures, used (among others) in flexible printed circuits designs [20].

Figure 3.5: The DEPFET principle. The top view is presented to show how all the steering contacts of a pixel are arranged relative to each other. Furthermore, a cross-section in the direction of the source-gate-drain is presented; one sees the internal gate of a DEPFET relative to the external transistor gate. On the right, the voltage distribution inside bulk below the gate is drawn; the voltage maximum (the potential minimum for electrons) is situated in the internal gate region. Free electrons will drift and stay there.

Charged particles and absorbed photons leave a certain number of e-h pairs in the depleted bulk. The electric field present in the depleted bulk prevents their recombination: holes are attracted to the bulk back-side that is connected to a negative potential. Electrons in turn are collected in the potential minimum, i.e. in the internal gate.

The presence of trapped electrons near the P-channel influences its configuration and, consequently, the drain current. This explains the name 'internal gate': similar to a regular FET gate, it also controls the transistor's drain current. The stronger the coupling is (i.e. the closer the gate and the channel are), the stronger the influence is.

For the internal gate, the figure of merit is its charge referred transconductance  $g_q$ , which describes the sensitivity of the drain current  $I_{ds}$  to the change of the charge collected in the internal gate  $Q_i$ :

$$g_q = \frac{\partial I_{ds}}{\partial Q_i} = \frac{g_m}{C_{eff}} \qquad \left[\frac{nA}{e}\right] \tag{3.4}$$

It is equal to the  $V_{gs}$  referred transistor transconductance  $g_m = \partial I_{ds}/\partial V_{gs}$  divided by the effective oxide capacitance  $C_{eff}$  [21].

In the transistor saturation region, which is the normal working regime of DEPFET devices, the  $g_q$  can be expressed as a function of L and W (the length and the width of the channel):

$$g_q \propto \sqrt{\frac{I_{ds} t_{ox}}{L^3 W}}$$

(3.5)

The parameters  $t_{ox}$  (gate oxide thickness), L and W (length and width of the gate) are purely geometrical and purely technology dependent. By increasing  $I_{ds}$ ,  $g_q$  can be varied to some extent during the operation. In the saturation regime, the drain current of a MOSFET transistor is virtually independent of  $V_{ds}$  and equal to:

$$I_{ds} = 1/2 \frac{W}{L} \mu C'_{ox} \left( V_{gs} - V_{th} \right)^2$$

(3.6)

with  $C'_{ox}$  and  $V_{th}$  being the oxide capacitance per unit area and the threshold voltage respectively. Thus, the gate voltage  $V_{qs}$  change is needed to influence the drain current during the operation.

DEPFET is an excellent concept for building elementary particle detectors, thanks to its large Signalto-Noise Ratio (SNR).<sup>1</sup> The FET transistor of a DEPFET pixel provides an in-pixel pre-amplification of the charge collected in the internal gate, thus avoiding any additional parasitic capacitance that can be found in hybrid pixel detector front-ends[21]. An excellent SNR=96±4 has been reported for a measurement of the 6 keV  $k_{\alpha}$  line of the Fe<sup>55</sup> at room temperature with a shaping time of 10  $\mu$ s [24].

Furthermore, the readout of DEPFET pixel is non-destructive: the same collected charge, stored in the internal gate, can be read several times.

#### 3.3.1 Sidewards-Depletion Technique

Sidewards-depletion was invented by E. Gatti and P. Rehak [23] as a technique to run semiconductor drift chambers.

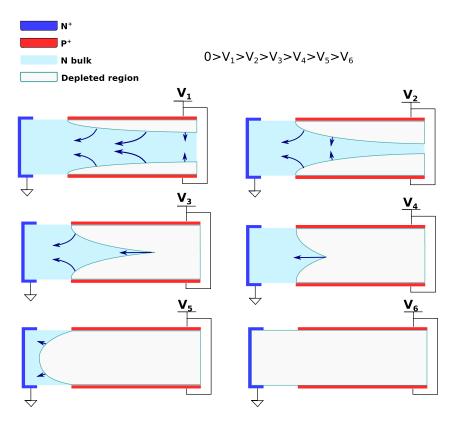

Using this technique, the depletion zone grows laterally into the bulk, as shown in Figure 3.6. The voltage needed to deplete the whole volume is four times smaller than that needed for regular depletion. This is explained by the fact that sidewards-depletion grows from both sides, therefore, the effective depletion depth is twice as small.

As in the case of  $p^+n$  junction, the depletion zone starts to grow on the border between the  $p^+$  and n zones, parallel to that border. When two depletion zones are thick enough, they merge. With a small further increase, the total depletion situation is reached.

Another important detail that makes this method so special is the voltage profile, which is orthogonal to the wafer surface. In the previous picture, the upper and bottom planes are connected to the same potential. It is clear that even in this case, the potential in the bulk in between cannot be constant: it is forbidden by Gauss' theorem as the depleted bulk is charged. To understand the potential profile shape, it is sufficient to solve the Poisson equation with corresponding Dirichlet boundary conditions:

$$\Delta \varphi = \frac{\rho}{\varepsilon \varepsilon_0}$$

$$\varphi|_{side} = 0$$

$$\varphi|_{top} = \varphi_{top}$$

$$\varphi|_{bottom} = \varphi_{bottom}$$

(3.7)

<sup>&</sup>lt;sup>1</sup> The signal left in the bulk by a charged particle is typically around several thousand electrons. To be detected it has to be amplified. It is particularly important to have the first amplification stage as clean as possible, since it has the highest contribution to the SNR.

Figure 3.6: Sidewards-depletion principle. The depletion zone increases similarly to the conditions in a planar situation. However, the growth goes in a lateral direction, parallel to the  $p^+$  contacts. With a further voltage increase, the two depletion zones merge and then, finally, the bulk is totally depleted.

In the regions far from the sensor edge, where side effects are negligible, this equation reduces to one dimension:

$$\varphi = \varphi(z) \tag{3.8}$$

$$\Delta = \frac{d^2}{dz^2}$$

In this case, Equation (3.7) can be easily solved analytically and the solution takes the following form:

$$\varphi(z) = \frac{eN_D}{2\varepsilon\varepsilon_0} z(d-z) + \frac{z}{d}(\varphi_{bottom} - \varphi_{top}) + \varphi_{top}$$

(3.9)

It is an inverted parabola reaching its maximum in the interval (0,d), whose depth depends on the doping concentration  $N_D$ . The maximum position depends on the difference between the top and the bottom potentials; it is equal to:

$$z_{min} = \frac{d}{2} + \frac{\varepsilon \varepsilon_0}{e N_D d} (\varphi_{bottom} - \varphi_{top})$$

(3.10)

By setting the appropriate voltage difference, the maximum position can be fixed at any point between two planes. This is the case of the DEPFET sensor: the voltage applied to the bottom of the substrate is very different relative to the top, such that this maximum is situated very close to the PMOS channel. This situation is presented in Figure 3.7

Figure 3.7: Potential position depending on the applied top and bottom voltages.

#### The Clear Contact

A DEPFET pixel is a dynamical system. The internal gate, while having a limited capacity, continuously gets filled with thermally generated electrons. Once totally filled, it stops attracting electrons.

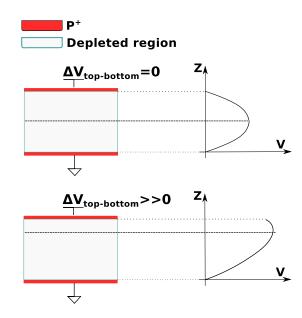

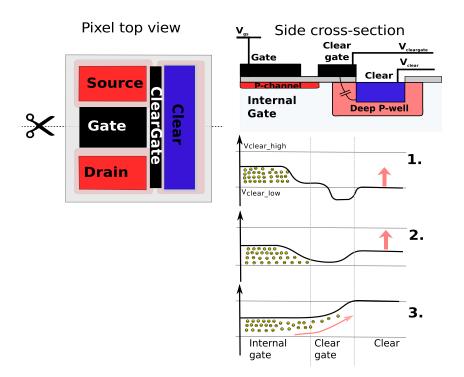

A regular refreshment procedure should be executed to maintain the device in its working state. This is the so-called 'Clear' process. In order to clear, an additional  $n^+$  implantation<sup>1</sup>, called 'Clear', is situated close to the pixel (Figure 3.8) perpendicular to the drain-source direction.

To avoid competition in detection collection between the internal gate and the Clear contact during device operation, the Clear is embedded in an additional deep p-well. While depleted, the p-well gets negatively charged; this negative charge halo serves as a potential barrier repelling electrons during the charge collection period.

To remove electrons from the internal gate a short and high positive voltage pulse is applied to the clear contact. Via the punch-through mechanism [25] an electrically favorable path is created between the Clear and the internal gate. The electrons are then removed by drift as presented in Figure 3.8.

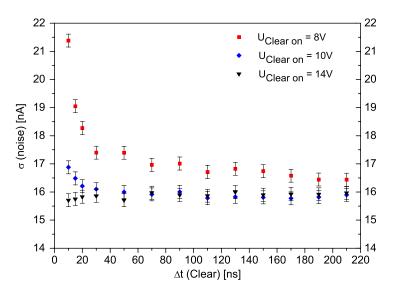

As reported by Sandow et al. [26], the clear operation can be as short as 10–20 ns, however the clear voltage should be 14 V high or more. The dependency between the clear voltage and the clear time is depicted in Figure 3.9.

#### The Clear-gate

The Clear process has for a long time been an issue for the DEPFET technology, being a timing bottleneck. To speed up the Clear process an additional gate (called clear-gate) between the Clear implantation and the internal gate has been added as depicted in Figure 3.8. It can lower the potential barrier created by the P-implantation surrounding the Clear contact; making the electrons' removal easier. First intro-

<sup>&</sup>lt;sup>1</sup> the  $n^+$  is necessary to provide the ohmic contact between the metal connection and the semiconductor

Figure 3.8: The DEPFET clear mechanism. During the clear operation, the potential of the clear contact is raised, as shown in plots (1)-(3). When the  $V_{clear}$  is high enough, the potential barrier between the internal gate and the Clear implantation disappears and the collected electrons can be removed from the internal gate by drift.

Figure 3.9: Pedestal reset noise depending on the clear pulse's duration. The measurement was based on the fact that after a complete clear the drain current is equal to its pedestal value regardless if the signal was detected before or not; hence the spread should decrease down to its plateau value while the clear pulse gets longer [26]. For high enough *clear\_on* voltage, the clear pulse can be shorter than 20 ns.

duced in 2004 in the PXD4 DEPFET design<sup>1</sup>, it was initially foreseen to activate this contact during the clear phase. However, this appeared to be not fast enough and added more complexity to the readout.

This contact is now controlled using a similar but more advanced technique, where the contact is not actively controlled by the steering logic but activated passively through the capacitive coupling with the Clear contact. This allows the fast charge removal without increasing the readout complexity. This technique is called the Capacitive Coupled Clear Gate (CCCG).

#### 3.3.2 DEPFET Electrical Model

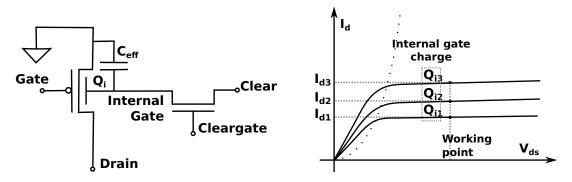

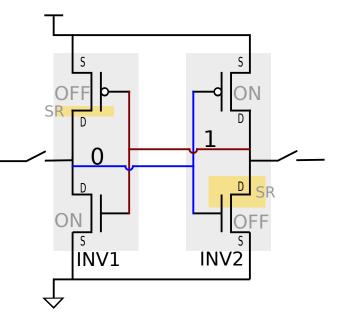

From the electrical operation point of view, a DEPFET pixel can be considered as a FET with two gate electrodes operating in parallel. Its electrical equivalent is sketched in Figure 3.10.

Figure 3.10: (left) DEPFET pixel equivalent circuit. A charge collected in the internal gate influences the drain current in the same way as the regular gate does. This charge can be removed by activating the Clear contact. (right) Drain currents for different charges collected in the internal gate.  $V_{gs}$  and  $V_{ds}$  are kept constant.

Using the small signal approximation a linear dependence between the transistor drain current  $I_{drain}$  and the charge  $Q_{int}$  collected in the internal gate can be written as:

$$I_{drain} = I_0(V_{gs}) + g_q \cdot Q_{int} \tag{3.11}$$

with  $g_q$  being the internal amplification defined before.

The pedestal current is defined as the drain current that flows when no charge is collected in the internal gate:

$$I_{ped} = I_{drain}(Q_{int} = 0) \tag{3.12}$$

In this case one obtains the collected charge using the following relation:

$$Q_{int} = \frac{1}{g_q} \left( I_{drain} - I_{ped} \right) \tag{3.13}$$

#### 3.3.3 Readout Principles

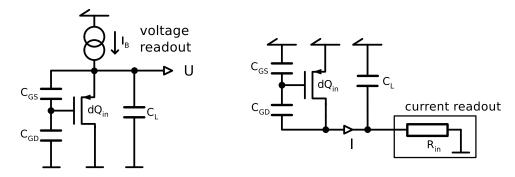

It is possible to readout the DEPFET at least in two different ways, as is reviewed in [30, 31], i.e using the voltage or the current driven readouts.

<sup>&</sup>lt;sup>1</sup> The PXD4 is the DEPFET matrix generation optimized for the ILC collider application. The ILC was the first big project where the DEPFET technology was considered to be used [27]. It still remains one of possible options [28, 29].

Figure 3.11: DEPFET readout options. Voltage readout (left) and current readout (right) [30, p.31].

#### **Voltage Readout**

The voltage driven or the source follower readout is presented in Figure 3.11(left). Here a constant bias current is applied to the transistor. The output voltage depends on the gates' configuration (external and internal ones). In this case the settling time for the output signal can be approximately given by [32, p. 42] or [31]:

$$\tau = 2.2 \frac{C_L \left(1 + \frac{C_{gs}}{C_{gd}}\right) + C_{GS}}{g_m} > \frac{C_L}{g_m}$$

(3.14)

For the long Belle II type matrix the  $C_L$  is estimated to be around 50 pF and the transconductance  $g_m$  to be 50 uS. This yields  $\tau$  in order of microseconds, which is too slow for Belle II operation<sup>1</sup>.

#### **Current Readout**

Presented by Figure 3.11 (right) the current driven readout has a fixed drain-source voltage. In this case the settling time does not longer depend on  $g_m$  but only on the load capacitance  $C_L^2$  and the input low resistance of the acquisition electronics  $R_{in}$

$$\tau = C_L R_{in} \tag{3.15}$$

Additionally, the gate switching time is limited by the driving power of the control electronics (see Section 3.5); according to estimations [33] it is expected that the gate switching time is  $\approx 5$  ns for a Belle II type matrix.

Using Equation (3.15) with the load capacitance of 50 pF it is enough to have an input resistance of 100  $\Omega$  in order to get the necessary value for  $\tau$ . This is easily achievable by a transimpedance amplifier design, as described in Section 3.5.

For this reason the current driven readout is chosen for the PXD.

#### **DEPFET Powering**

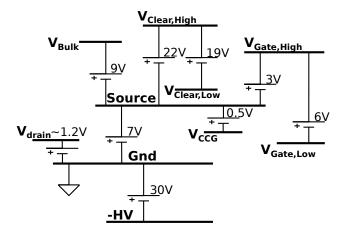

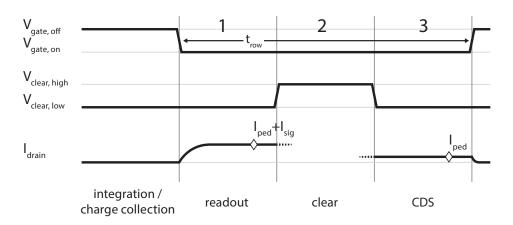

In Figure 3.12 a typical powering necessary to run a DEPFET system is presented. Below the description of each bias potential is listed.

<sup>&</sup>lt;sup>1</sup> As it will be presented in Section 3.4, the PXD readout is constrained by 100 ns per row.

<sup>&</sup>lt;sup>2</sup> Assuming that  $C_L \gg C_{GD}$  and  $C_{GS}$

Figure 3.12: DEPFET powering with an example of possible voltages set for a DEPFET matrix (PXD6).

- Source. This voltage should be high enough to set the PMOS transistor to the saturation region, which is the working point of DEPFET devices. It is convenient to set most other voltages relative to the Source and not to the Ground.

- **Drain**. Denoted in Figure 3.12 as  $V_{drain}$ , this voltage is generated by the DCDB chip. It is kept constant, as required by the Current Readout (Section 3.3.3).

- **Bulk**. As described by the sidewards depletion technique (Section 3.3.1), to properly bias the parabolic potential (Figure 3.5), the bulk voltage  $V_{Bulk}$ , should be set higher than the Source voltage. The relation between HV, Source and  $V_{Bulk}$  sets the depth of the potential minimum.

- **-HV** (Depletion Voltage). This voltage is applied to the backside of the matrix relative to the ground potential. Together with **Bulk** potential, its purpose is to deplete the sensor.

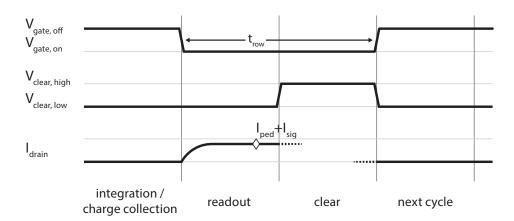

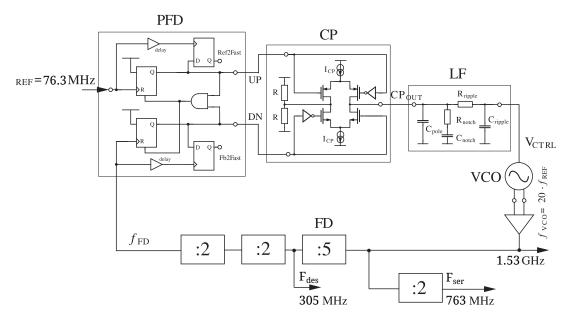

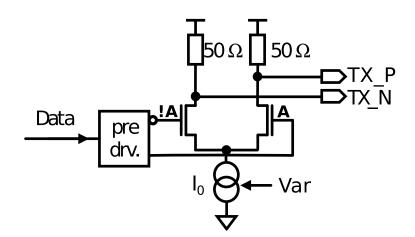

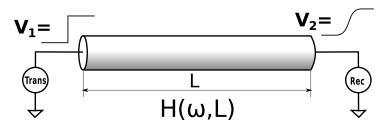

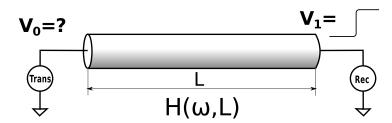

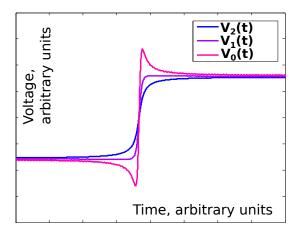

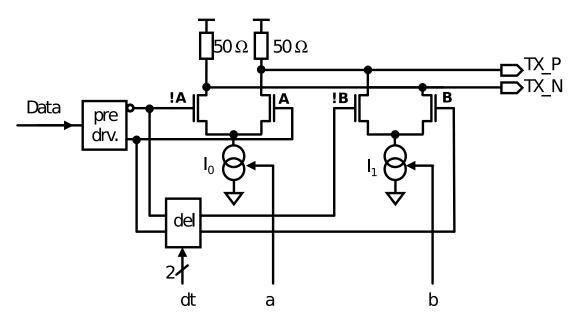

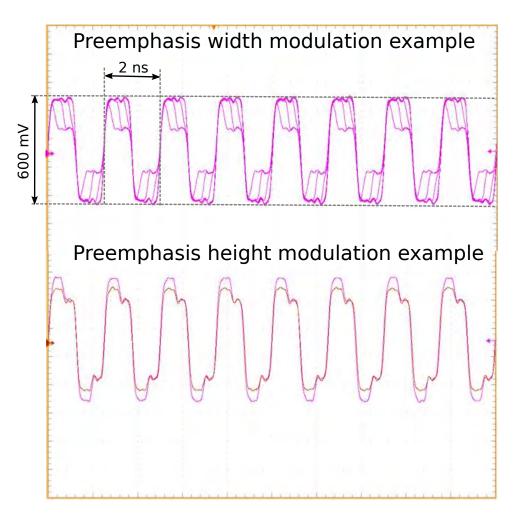

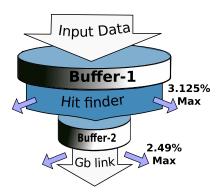

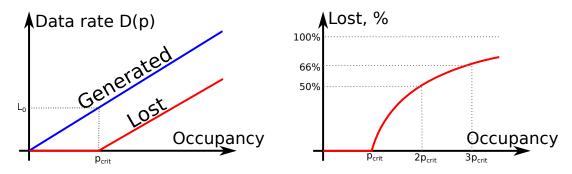

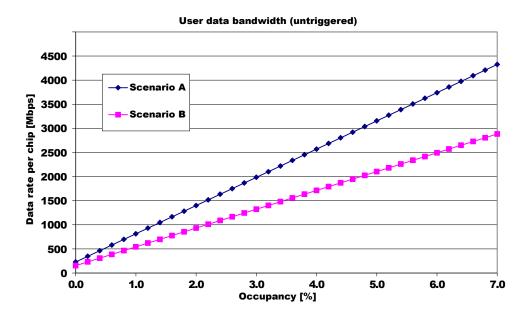

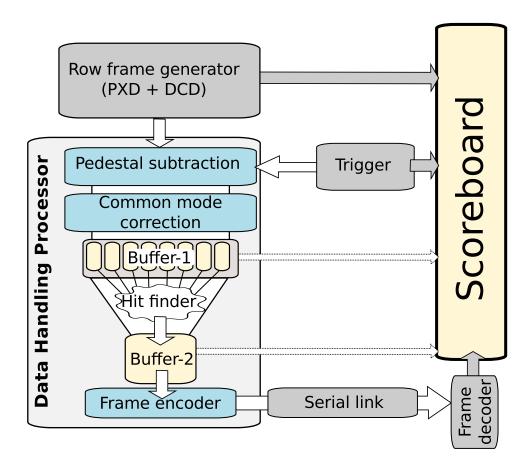

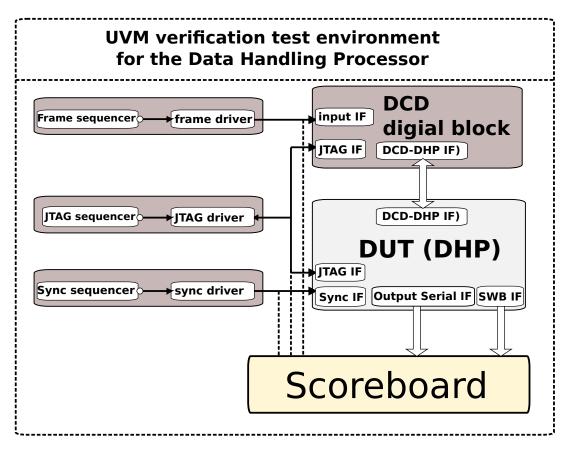

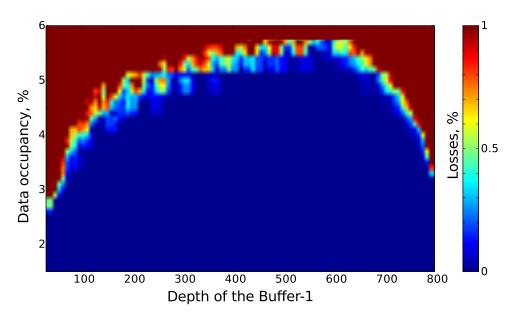

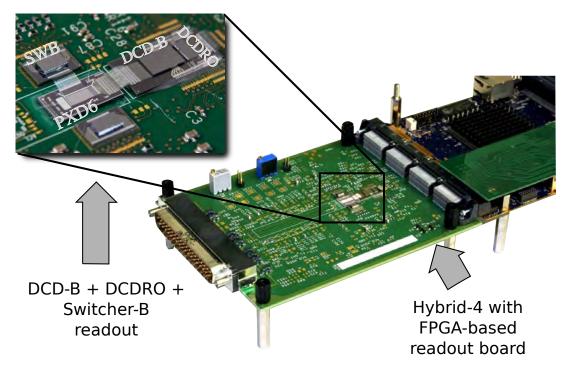

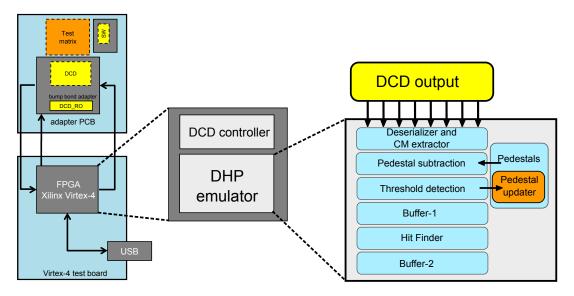

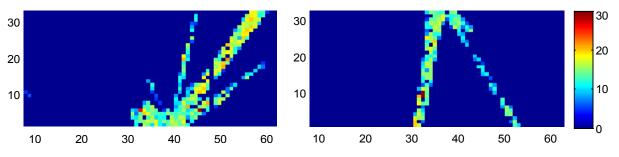

- **Gate voltages**. There are two voltage levels responsible for the gate operation. The  $V_{Gate,High}$  and the  $V_{Gate,Low}$ . The latter is used to activate and read the DEPFET pixel. The drain current (and the amplification) is defined by the  $V_{gs} = V_{Gate,Low} V_{Source}$  according to Equations 3.6 and 3.5. The  $V_{Gate,High}$  voltage is applied to the gate during the collection period. It sets the PMOS into the off-state. Additionally, by applying higher voltage relative to source, one locally influences the potential distribution beneath the gate contact, where the internal gate is situated. This can make the internal gate more attractive for electrons; in this manner the collection efficiency can be increased.