# UNIVERSITÄT BONN Physikalisches Institut

Development of high speed integrated circuit for very high resolution timing measurements

#### von Christian Mester

A multi-channel high-precision low-power time-to-digital converter application specific integrated circuit for high energy physics applications has been designed and implemented in a 130 nm CMOS process. To reach a target resolution of 24.4 ps, a novel delay element has been conceived. This nominal resolution has been experimentally verified with a prototype, with a minimum resolution of 19 ps. To further improve the resolution, a new interpolation scheme has been described.

The ASIC has been designed to use a reference clock with the LHC bunch crossing frequency of 40 MHz and generate all required timing signals internally, to ease to use within the framework of an LHC upgrade. Special care has been taken to minimise the power consumption.

Post address: Nussallee 12 53115 Bonn Germany

BONN-IR-2009-09 Bonn University October 2009 ISSN-0172-8741

# UNIVERSITÄT BONN Physikalisches Institut

Development of high speed integrated circuit for very high resolution timing measurements

> von Christian Mester

Dieser Forschungsbericht wurde als Dissertation von der Mathematisch - Naturwissenschaftlichen Fakultät der Universität Bonn angenommen.

Angenommen am: Referent: Korreferent: 22. Oktober 2009Dr. Paulo Rodrigues S. MoreiraProf. Dr. Norbert Wermes

#### Development of

high speed integrated circuit for

very high resolution timing measurements

#### Disseration

zur

Erlangung des Doktorgrades (Dr. rer. nat.)

der

Mathematisch-Naturwissenschaftlichen Fakultät

der

Rheinischen Friedrich-Wilhelms-Universität Bonn

vorgelegt von

Christian Mester

aus

Köln

Bonn 2009

## Contents

| 1 | Intro                       | oduction                                   | 1  |  |  |  |  |

|---|-----------------------------|--------------------------------------------|----|--|--|--|--|

|   | 1.1                         | Structure of the thesis                    | 1  |  |  |  |  |

| 2 | Tim                         | Time Measurements in HEP Experiments       |    |  |  |  |  |

|   | 2.1                         | Introduction                               | 5  |  |  |  |  |

|   | 2.2                         | Case Study: ALICE Time of Flight Detector  | 5  |  |  |  |  |

| 3 | Basic Principles of a TDC 1 |                                            |    |  |  |  |  |

|   | 3.1                         | Ideal TDC                                  | 13 |  |  |  |  |

|   | 3.2                         | Performance Metrics for TDCs               | 14 |  |  |  |  |

| 4 | TDC                         | TDC Data Flow Architecture 2               |    |  |  |  |  |

|   | 4.1                         | Specifications                             | 21 |  |  |  |  |

|   | 4.2                         | Clock driven architecture                  | 22 |  |  |  |  |

|   | 4.3                         | Data driven architecture                   | 23 |  |  |  |  |

|   | 4.4                         | Choice of Data Flow Architecture           | 25 |  |  |  |  |

| 5 | Tim                         | e Base Architectures Overview              | 27 |  |  |  |  |

|   | 5.1                         | Time Base Architectures                    | 27 |  |  |  |  |

|   |                             | 5.1.1 Counter based Architecture           | 28 |  |  |  |  |

|   |                             | 5.1.2 Delay line based Architecture        | 29 |  |  |  |  |

|   |                             | 5.1.3 Delay Locked Loop based Architecture | 32 |  |  |  |  |

|   |                             | 5.1.4 Phase Locked Loop based Architecture | 33 |  |  |  |  |

|   |                             | 5.1.5 Array of DLLs based Architecture     | 34 |  |  |  |  |

|   | 5.2                         | Fine Time Interpolation Techniques         | 36 |  |  |  |  |

|   |                             | 5.2.1 Dual-Slope Analogue Time Expansion   | 37 |  |  |  |  |

i

|   |     | 5.2.2   | Vernier Techniques                          | 39 |

|---|-----|---------|---------------------------------------------|----|

|   |     | 5.2.3   | Passive LC lines or RC lines                | 41 |

|   |     | 5.2.4   | DLL adjusted delay lines                    | 42 |

|   | 5.3 | Choice  | e of Time Base Architecture                 | 44 |

| 6 | TDC | :130 Ta | rget Chip Architecture                      | 47 |

|   | 6.1 | Data F  | Tow and Time Base Architecture              | 47 |

|   | 6.2 | Chann   | el Macro                                    | 47 |

|   | 6.3 | Level-  | 1 Buffer Organisation                       | 49 |

|   | 6.4 | Trigge  | r Mechanism                                 | 51 |

|   | 6.5 | Chann   | el Merging                                  | 53 |

|   | 6.6 | Reado   | ut                                          | 54 |

| 7 | TDC | 130-08  | 320 Prototype Chip Implementation           | 55 |

|   | 7.1 | Archite | ecture                                      | 55 |

|   | 7.2 | DLL I   | mplementation                               | 55 |

|   |     | 7.2.1   | Delay Element                               | 56 |

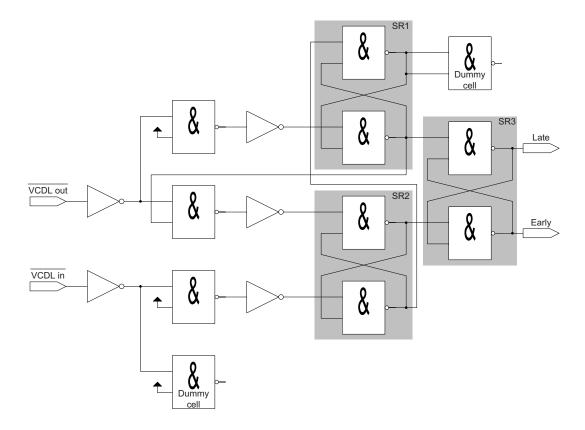

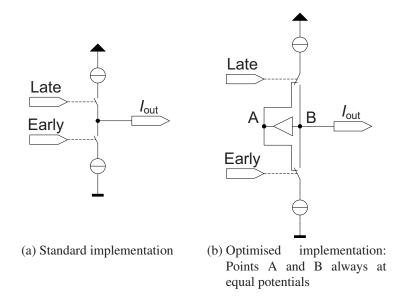

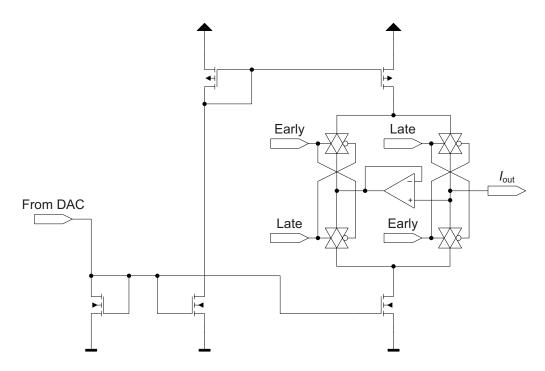

|   |     | 7.2.2   | Phase Detector                              | 61 |

|   |     | 7.2.3   | Loop Filter                                 | 64 |

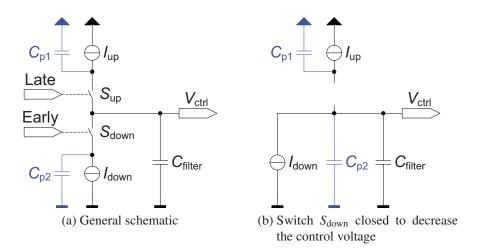

|   |     | 7.2.4   | Choice of Phase Detector and Loop Filter    | 68 |

|   |     | 7.2.5   | Transfer function                           | 69 |

|   |     | 7.2.6   | Limitations and Sources of Errors, Jitter   | 70 |

|   |     | 7.2.7   | Start-up Procedure                          | 71 |

|   | 7.3 | PLL Ir  | nplementation                               | 73 |

|   |     | 7.3.1   | Voltage Controlled Oscillator               | 73 |

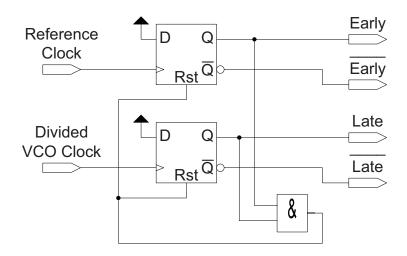

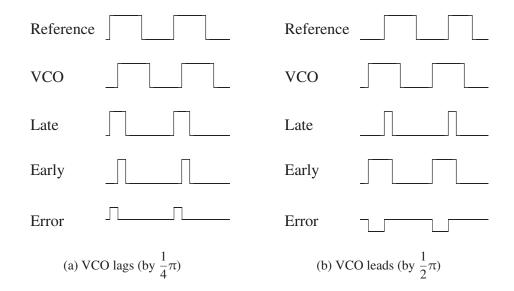

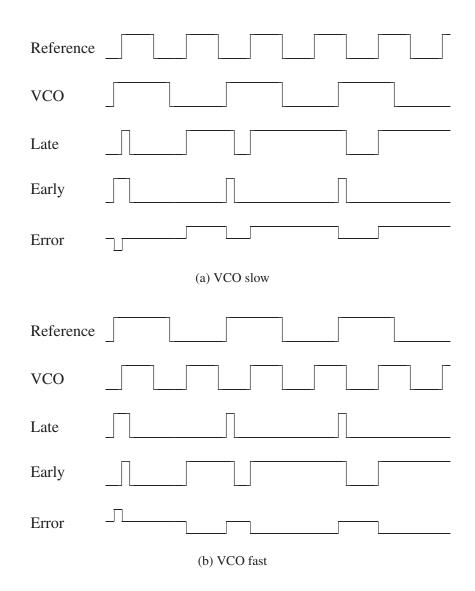

|   |     | 7.3.2   | Phase Detector                              | 75 |

|   |     | 7.3.3   | Loop Filter                                 | 78 |

|   |     | 7.3.4   | Choice of Phase Detector and Loop Filter    | 83 |

|   |     | 7.3.5   | Transfer function                           | 84 |

|   |     | 7.3.6   | Start-up Procedure                          | 87 |

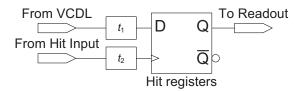

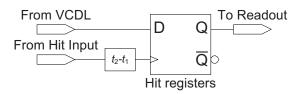

|   | 7.4 | Hit Re  | gisters                                     | 87 |

|   |     | 7.4.1   | Differential vs. Single-Ended Hit Registers | 88 |

|   | 7.5 | Hit Re  | gister Driving Circuitry                    | 90 |

|     | 7.6      | Sources | s of Errors                         | 91  |

|-----|----------|---------|-------------------------------------|-----|

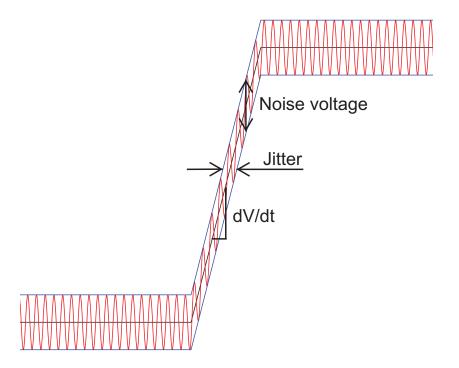

|     |          | 7.6.1   | Slew Rate                           | 91  |

|     |          | 7.6.2   | Noise on Control Voltages           | 92  |

|     |          | 7.6.3   | Power Supply and Ground Variations  | 93  |

|     |          | 7.6.4   | Thermal Noise                       | 95  |

|     |          | 7.6.5   | Flicker Noise                       | 96  |

|     |          | 7.6.6   | Shot noise                          | 97  |

|     | 7.7      | Readou  | at and Configuration                | 97  |

|     |          | 7.7.1   | Readout Shift Register              | 97  |

|     |          | 7.7.2   | Configuration Shift Register        | 98  |

| 8   | Exp      | erimen  | tal Results                         | 101 |

|     | 8.1      | PLL Cl  | haracterisation                     | 101 |

|     |          | 8.1.1   | Locking Range                       | 101 |

|     |          | 8.1.2   | Jitter                              | 101 |

|     | 8.2      | DLL C   | haracterisation                     | 102 |

|     |          | 8.2.1   | DLL locking range                   | 102 |

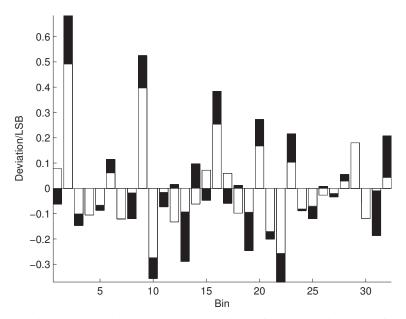

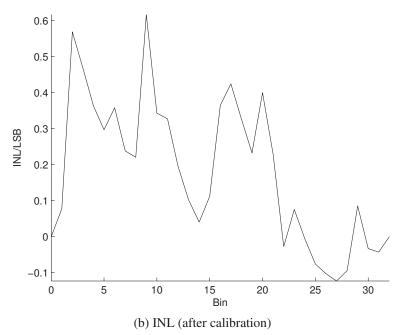

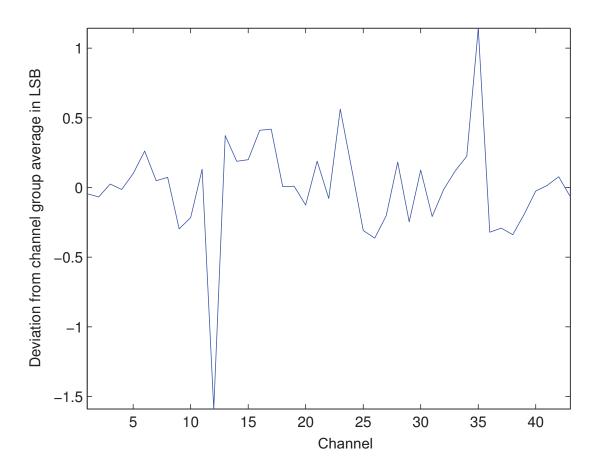

|     |          | 8.2.2   | Linearity                           | 103 |

|     |          | 8.2.3   | Jitter                              | 107 |

|     | 8.3      | Power   | dissipation                         | 109 |

| 9   | Sum      | imary a | and Outlook                         | 111 |

| Α   | Calc     | ulation | าร                                  | 113 |

|     | A.1      | RMS a   | nd Standard Deviation of LSB        | 113 |

| в   | Alte     | rnative | Implementations                     | 115 |

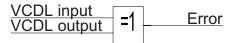

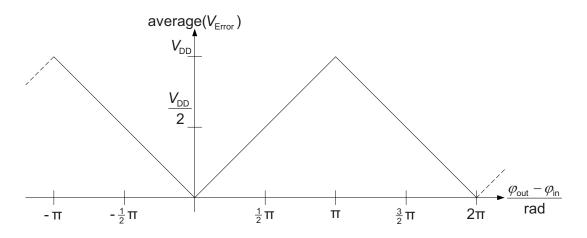

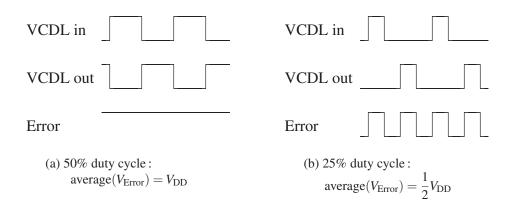

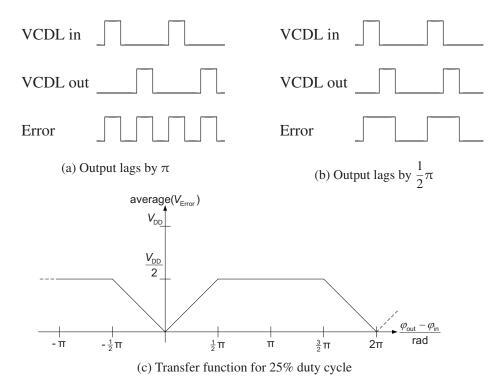

|     | B.1      |         | hase Detector: XOR                  | 115 |

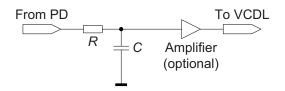

|     | B.2      | DLL L   | oop Filter: RC Filter and Amplifier | 117 |

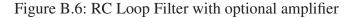

|     | B.3      |         | hase Detector: Analogue Multiplier  | 118 |

|     | B.4      |         | oop Filter: Passive RRC filter      | 121 |

| Lis | st of \$ | Symbo   | ls                                  | 123 |

Contents

| List of Abbreviations | 125 |

|-----------------------|-----|

| Bibliography          | 127 |

| List of Figures       | 133 |

| List of Tables        | 137 |

## **1** Introduction

In this thesis, the development of a Time-to-Digital Converter (TDC) Application Specific Integrated Circuit (ASIC) is described. The work has been carried out at CERN<sup>†</sup> in Geneva, Switzerland. The device is targeted at applications in the domain of High Energy Physics (HEP).

### 1.1 Structure of the thesis

The thesis is divided into 3 main parts:

- Introduction to TDCs in general and a brief description of a selected HEP application example (chapters 2 and 3),

- design of a new TDC and implementation of a prototype (chapters 4 to 7) and

- experimental results (chapter 8).

First, an example of an HEP experiment using TDCs is presented (chapter 2). It gives an overview of the requirements of a large scale high precision experiment. A very high resolution must be achieved on a large number of channels while the power consumption has to be minimised to keep the material budget low.

To compare different possible TDC architectures, a set of figures of merit is needed. As they have to be tailored to TDCs, they are developed in the course of an introduction to TDCs (chapter 3), including a comparison to Analogue-to-Digital Converters, which are more commonly known. A TDC performs a discretisation of signals, which by principle implies a loss of information. The most basic performance metrics are

<sup>&</sup>lt;sup>†</sup>European Organization for Nuclear Research/Organisation européenne pour la recherche nucléaire

therefore the smallest and the biggest time difference that can be resolved unambiguously. For any implementation of this concept, imperfections degrade the performance of the TDC, causing non-linearity, jitter and data rate limitations. When TDCs are used in a system, further properties are important, such as the number of chips required to interface a given number of channels, the power dissipation introduced by the TDC. On the system-level, the time-to-digital conversion is only a part of the required functionality. A TDC ASIC can include additional functionality required on a system-level.

Given this set of metrics and the knowledge about present applications of TDCs in the HEP domain, it is possible to specify the requirements for the TDC to be developed. The performance of a TDC is also determined by the data flow architecture. The two main TDC architectures, clock driven and data driven, are introduced. Both architectures have advantages and drawbacks. The data driven architecture is chosen for the new TDC, as it is found to be most appropriate for HEP applications (chapter 4).

The precision of a TDC timing measurement is set by the time base (chapter 5). For low power operation of a multi-channel TDC, it is convenient to have one global time base per chip that provides the time information to all channels. In this way, the time base resources are shared minimising the global power consumption and consequently the power consumption per channel. Different time base architectures fulfil this requirement. In a comparison, a DLL based time base with a counter for dynamic range extension has been found most appropriate.

The choice of the time base (chapter 5) fixes the characteristics of the TDC that are directly related to the time-to-digital conversion within the limits given by the data flow architecture (chapter 4). Not of smaller importance, other parts of the chip decide which data rates can be handled and how other parts of a complete detector system can interface with the TDC chip.

A very powerful concept for measuring very high rate events when only little readout bandwidth is available is triggering. In HEP experiments, the total rate of events is generally orders of magnitude higher than the rate of events that are worth being analysed in detail. Discarding uninteresting events inside the TDC ASIC reduces the required readout bandwidth substantially (chapter 6). All these considerations are on a high level of abstraction. Most of them are conceptual, while some require simulations.

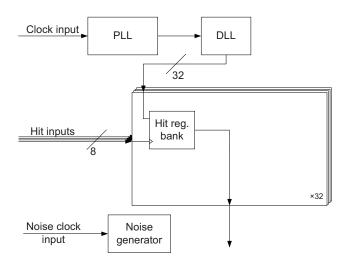

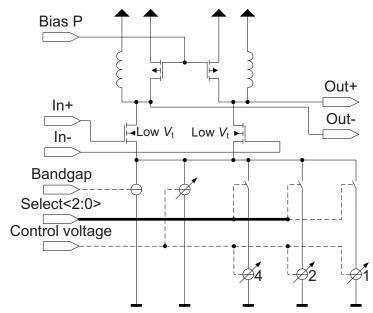

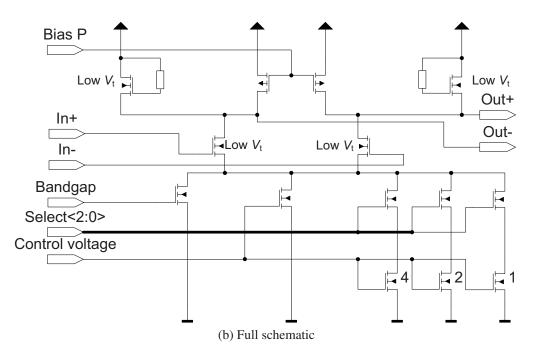

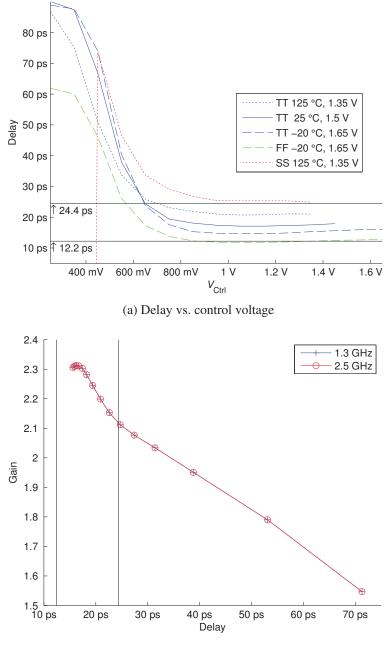

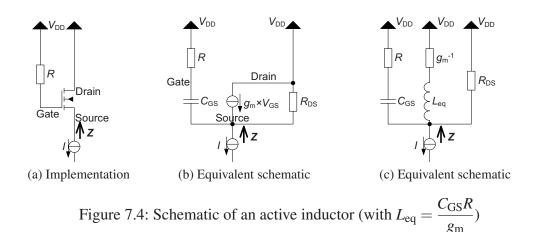

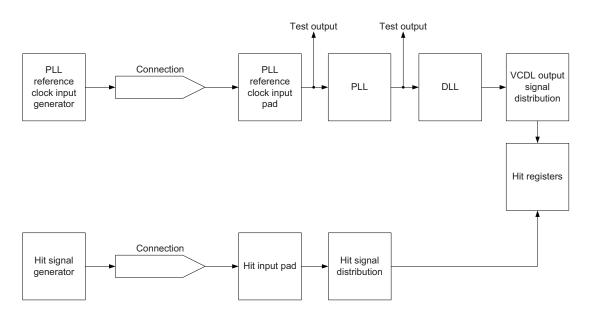

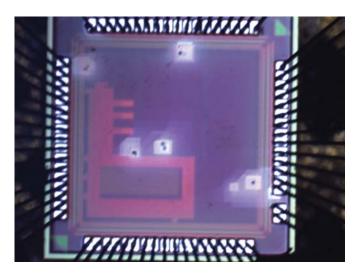

Other characteristics, especially the timing precision, are strongly affected by parasitics, which depend not only on the gate-level implementation of the circuit, but even on the actual layout, the process technology, temperature variations and supply voltage. As the delay of wires can be in the order of the TDC resolution, timing critical parts have to be designed in a full-custom way. Post-layout simulations can give an idea of the circuit properties. A prototype is required to fully characterise the timing performance. Disregarding side effects such as cross-talk, power supply and ground variations and increase of the ASIC temperature, synthesisable features such as large buffers don't influence the timing precision. They can be simulated with sufficient precision and can be generated using well established synthesis tools. The prototype contains the strict minimum of circuitry necessary for the evaluation of the timing part. It contains a Phase-Locked Loop (PLL) for multiplying the 40 MHz input reference clock up to 1.28 GHz as required by the following stage. A Delay-Locked Loop (DLL) provides 32 phase-shifted versions of the 1.28 GHz clock to the hit registers of the channels. The TDC bin size is defined by the delay corresponding to the phase shift between two successive DLL outputs. Using a newly developed delay element, a bin size of 24.4 ps has been achieved. Each channel consists of a bank of registers that store the state of all DLL outputs, called 'timestamp', at the arrival of a signal on the hit inputs. The timestamp stored in the hit registers is read out using a shift register. Another shift register is used for configuration purposes. Test outputs are used to analyse important signals. Possible sources of errors such as non-linearities, noise and jitter are identified (chapter 7).

Different tests for prototype evaluation are presented. Experiments carried out with the prototype confirm the simulations. A bin size of 19 ps has been reached, with an RMS integral non-linearity of 4 ps and an RMS integral non-linearity of 5 ps. A power dissipation of 8 mW per channel has been observed (chapter 8).

Chapter 1. Introduction

# 2 A Short Introduction to Time Measurements in HEP Experiments

#### 2.1 Introduction

The HPTDC, the previous version of a CERN-developed TDC, has been used in many different applications, including the LHC experiments ALICE [ALI02, BGG<sup>+</sup>05], ATLAS [AEF<sup>+</sup>04], CMS [Par08] and LHCb [LHC01]. The ALICE Time of Flight detector is described as case example, focussing on the timing measurement. NA62, also known as P326 and NA48/3, is a fixed target experiment at CERN's SPS accelerator. It contains the GigaTracker, for which a new front-end chip containing on-chip TDCs based on the TDC130 design is under development [Cec07].

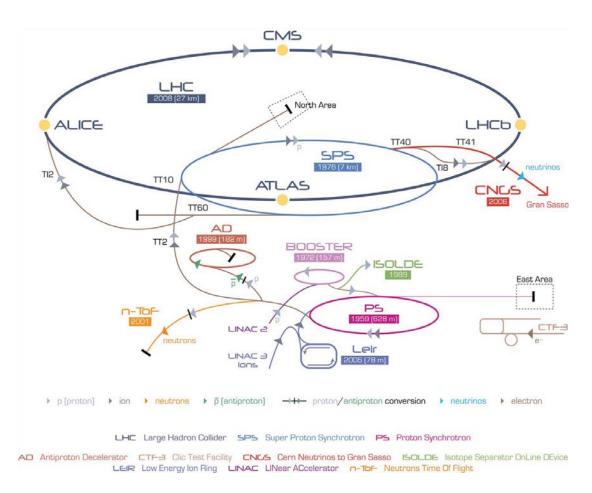

The LHC is the last accelerator of a chain (fig. 2.1) at CERN. Its centre of mass energy is 14 TeV for proton-proton collisions ([BCL<sup>+</sup>04], p. 21) and 1.15 PeV for  $^{208}$ Pb<sup>82+\_208</sup>Pb<sup>82+</sup> collisions ([BCL<sup>+</sup>04], p. 531).

### 2.2 Case Study: ALICE Time of Flight Detector

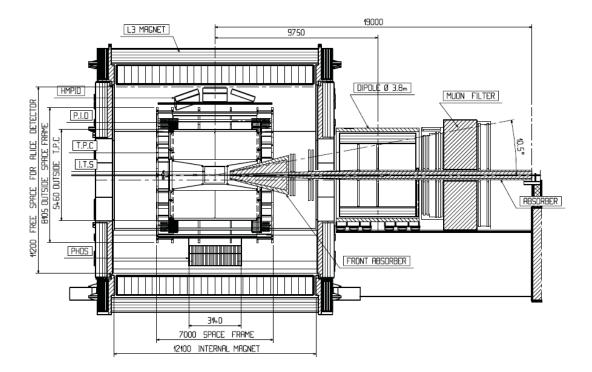

ALICE<sup> $\dagger$ </sup> (fig. 2.2) is an experiment at LHC. It is designed to observe heavy-ion collisions such as Pb-Pb, and study the plasma of deconfined quarks and gluons which

<sup>&</sup>lt;sup>†</sup>A Large Ion Collider Experiment

Figure 2.1: The CERN accelerator complex [Lef06]

is predicted by quantum chromodynamics [ALI95].

ALICE consists of different sub-detectors which are optimised for observing different particles emerging from the interaction point. The detectors are placed in a magnetic field that bends the trajectory of charged particles to simplify their identification. A Time Of Flight (TOF) detector for Particle Identification (PID) is installed in one of the outer layers. This detector uses a large number of HPTDCs in the 24.4 ps mode.

The TOF is used to distinguish pions, kaons and protons by measuring the time it takes them to reach the detector after emerging from the interaction point. For efficient

Figure 2.2: Longitudinal view of the ALICE detector [ALI95]

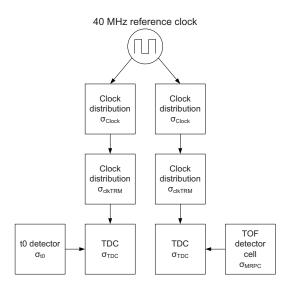

Figure 2.3: Signal paths of clock, TOF and t0 detector signal

separation of the signals of those particles, the time of flight needs to be measured with high precision to reveal the difference between the time a pion, kaon or proton takes. Studies have shown a relation between the efficiency of the identification and the resolution of the TOF time measurement [BKP<sup>+</sup>98]. In the higher momentum range of the expected particles, an overall resolution of 100 ps yields a considerably better result than e.g. 200 ps. An overall time resolution of 100 ps guarantees a  $3\sigma$  separation of kaons and pions for momenta up to 2.1  $\frac{\text{GeV}}{\text{c}}$ . With a resolution of 150 ps, momenta higher than 1.7  $\frac{\text{GeV}}{\text{c}}$  are not covered, for a resolution of 200 ps, the momentum limit is 1.4  $\frac{\text{GeV}}{c}$  [ALI95]. Several sub-systems of the detector contribute uncertainties to the overall resolution  $\sigma_{tot}$ . The particle's time of flight is calculated as the difference of the time the particle strikes the TOF detector and the time  $t_0$  of the interaction, as captured by the t0 detector. The TOF detector consists of several modules, placed at the surface of a cylinder with a radius of 3.5 m and a length of 7 m. These dimensions render the traditional solution of routing the  $t_0$  signal to all channels impractical. Therefore, the 40 MHz reference clock, which has to be distributed to all the system anyway, is used as a reference for the measurements. The time a particle arrives to a TOF detector channel is measured individually. Later on, after time to digital conversion,  $t_0$  is subtracted. Fig. 2.3 shows the described signal paths. Each step introduces an additional uncertainty. Due to the large volume the system is spread across, they are considered uncorrelated and can be added:

$$\sigma_{\text{tot}}^2 = \sigma_{\text{t0}}^2 + \sigma_{\text{MRPC}}^2 + 2 \cdot \sigma_{\text{TDC}}^2 + 2 \cdot \sigma_{\text{clkTRM}}^2 + \sigma_{\text{Clock}}^2$$

assuming for simplicity that the uncertainties of the TDCs and the clock distribution network in the TDC readout module (TRM) are the same in both of the independent signal paths.  $\sigma_{MRPC}$  represents the uncertainty of the Multi Resistive Plate Chamber that has been chosen as detector for the TOF.

Table 2.1 shows the estimated time resolution of the whole ALICE TOF system [ALI02]. An RMS resolution of 25 ps translates into a bin size of 87 ps, 50 ps into 173 ps (see appendix A.1 for the calculation).

|                       | Average time resolution | Maximum |

|-----------------------|-------------------------|---------|

|                       | in ps                   | in ps   |

| $\sigma_{t0}$         | 50                      | 50      |

| $\sigma_{\rm MRPC}$   | 50                      | 80      |

| $\sigma_{\text{TDC}}$ | 25                      | 50      |

| $\sigma_{\rm clkTRM}$ | 15                      | 15      |

| $\sigma_{ m Clock}$   | 10                      | 10      |

| $\sigma_{\rm tot}$    | 82                      | 120     |

Table 2.1: Time resolution estimations for the ALICE TOF system [ALI02]. Note that the values given here are RMS values. The TDC130's nominal RMS resolution is 7 ps on 32 channels. The smallest RMS resolution the HPTDC can reach in 32 channel mode is 28 ps.

## **3 Basic Principles of a TDC**

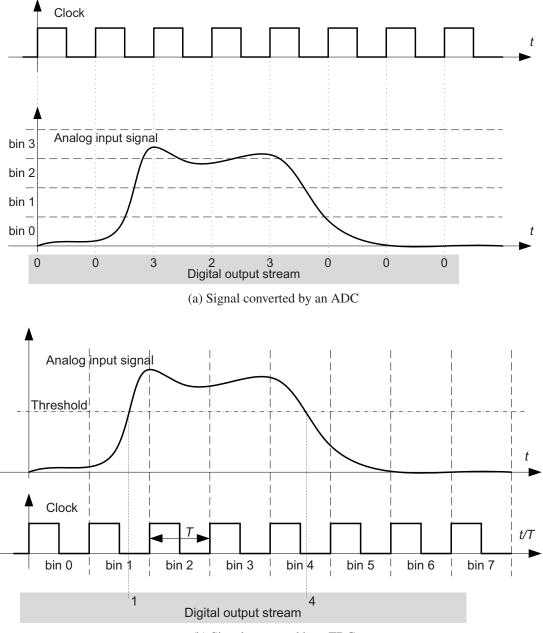

With increasing capabilities of digital data processing hardware such as FPGAs<sup>†</sup> and microprocessors, it has become common to analyse experimental data in the digital and discrete time domain. However, measurements of physical quantities usually take place in the analogue and continuous time domain. Conversion circuits are required to transform analogue signals such as a voltage into digital information and to perform a discretisation both of time and amplitude. Analogue-to-Digital Converters (ADCs) are used to sample analogue signals and convert the amplitude of the signal, most frequently an analogue voltage, into its discrete digital representation. Time-to-Digital Converters digitise the time their input signal crosses a given threshold (fig. 3.1). Since ADCs are more commonly known than TDCs, I will frequently use ADC related examples.

Unfortunately, conversion from continuous to discrete introduces a loss of information, even if an ideal converter is assumed. Imperfections of real converters introduce further errors. Therefore, only an approximation of the original signal can be reconstructed, based on some assumptions. An example is the Nyquist criterion: in order to perfectly reconstruct an analogue signal, the sampling frequency of an ADC has to be at least twice the bandwidth of the input signal. For a TDC, the spacing of two successive hits must not be smaller than a certain minimum, the double pulse resolution. If hits are closer, data loss occurs<sup>‡</sup>.

<sup>&</sup>lt;sup>†</sup>Field Programmable Gate Arrays

<sup>&</sup>lt;sup>‡</sup>There is however a fundamental difference between the Nyquist criterion and the double pulse resolution. The Nyquist criterion is a fundamental limit, independent of the ADC circuit, while the double pulse resolution is limited by the circuit.

(b) Signal converted by a TDC

Figure 3.1: Comparison of ADC and TDC output data

Figure 3.2: Transfer characteristic of an ideal TDC

### 3.1 Ideal TDC

A TDC converts a time interval into a digital number. The measured quantity can be a time relative to a reference, a delay with respect to another signal or between to edges of the same signal.

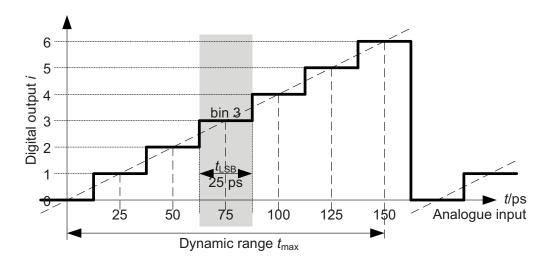

Fig. 3.2 shows the transfer function of an ideal TDC. The conversion consists of the discretisation of the continuous signal. It can be described by a piecewise linear equation:

$$i = (t \mod t_{\text{LSB}}) \dim \frac{t_{\max}}{N}$$

mod being the modulo and div the integer division operator. The real number *i* is the digital output of the infinite resolution TDC, when  $N \rightarrow \infty$ . As real TDCs cannot have infinite resolution, *i* belongs to a discrete set of numbers generating the bold solid staircase function that is only an approximation to the ideal straight line. Signals within an interval  $[t_i;t_{i+1})$  are rounded to the interval's mean value  $\frac{t_i+t_{i+1}}{2}$  and represented by the number *i*. One key figure describing a TDC is therefore the bin size, the width of the discretisation interval, which is called Least Significant Bit (LSB). The LSB represents the smallest time difference that can be resolved with the TDC. In physics applications, the required RMS<sup>†</sup> resolution or the required standard deviation of the measurement is

<sup>&</sup>lt;sup>†</sup>Root Mean Square

often specified, while in the domain of engineering, the bin size is frequently stated. These numbers can easily be converted:

$$\sigma_{\rm LSB} = t_{\rm LSB,RMS} = \frac{t_{\rm LSB}}{\sqrt{12}} \approx \frac{t_{\rm LSB}}{3.5}$$

as shown in appendix A.1.

Another key parameter is the dynamic range  $t_{max}$ , which gives the largest time difference that can be measured unambiguously. If the dynamic range is exceeded, an overflow occurs. The TDC output can represent either the measured time modulo the dynamic range, as assumed in this work if not otherwise stated and as shown in fig. 3.2, or, as it is the case for most ADCs, saturate to the maximum value.

Note that the number of digital output words, corresponding to the number of time bins, does not need to be a power of 2. Even though the output values are usually represented by a binary word, some words might not be used to represent a time. For example, the output words in fig. 3.2 can be encoded with 3 b. However, out of the  $2^3 = 8$  available symbols, only N = 7 are used.

### 3.2 Performance Metrics for TDCs

Some performance metrics for TDCs have been established under the same name as for ADCs [IEE01]. However, the definition may differ. Therefore, the definitions used in this thesis will be explained. Other ADCs metrics are not applicable to TDCs (e.g. sampling frequency) and vice-versa (e.g. double pulse resolution).

The most basic performance metrics that describe the properties of an ideal TDC as explained in section 3.1 are:

- The Bin Size  $t_{LSB}$  and RMS Resolution  $\sigma_{LSB}$

- The Dynamic Range  $t_{max}$

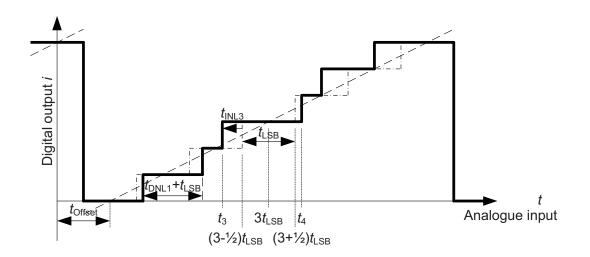

Static deviations from the ideal behaviour (fig. 3.3) are characterised by:

Figure 3.3: Transfer characteristic of a TDC. The thick solid line shows the characteristic of a real TDC, the dash-dotted line its approximation by an ideal TDC transfer function with an offset and the dashed line the piecewise-linear approximation.

• The Differential Non-Linearity (DNL) The differential non-linearity  $t_{\text{DNL},i}$  is the deviation of a particular bin size  $\Delta t_i = t_{i+1} - t_i$  of bin *i* from its ideal value  $t_{\text{LSB}}$ :

$$t_{\text{DNL},i} = \Delta t_i - t_{\text{LSB}} = t_{i+1} - t_i - t_{\text{LSB}}$$

with  $i = 0 \dots N - 1$  integer

Usually, the standard deviation  $\sigma_{\text{DNL}}$  is stated, sometimes with a graph showing the  $t_{\text{DNL},i}$  for all individual bins i = 0...N - 1. The DNL is commonly measured in units of LSB.

• The Integral Non-Linearity (INL) The integral non-linearity  $t_{INL,i}$  is the deviation of the total delay  $t_i$ , measured from the beginning of bin 0 to beginning of bin *i*, assuming the real offset  $t_{Offset}$ and ideal bin sizes  $t_{LSB}$ .

$$t_{\text{INL},i} = t_i - it_{\text{LSB}} + \frac{1}{2}t_{\text{LSB}} - t_{\text{Offset}} \text{ with } i = 0...N - 1 \text{ integer}$$

Usually, the standard deviation  $\sigma_{INL}$  is stated, sometimes with a graph showing the  $t_{INL,i}$  for all individual bins i = 0...N - 1. The INL is commonly measured in units of LSB, as it is the case for the DNL.

• The Gain Error

The gain error is the deviation of the slope of a linear approximation to the TDC transfer function from its ideal value. As the TDC time base consists of two parts, the fine time base and the dynamic range extension, a gain error translates into a large nonlinearity between the last and the first bin of the fine time base. Thus, it is more meaningful to include gain error effects in the INL, as it is the case for the definition of the INL used in this work.

• The Offset

For an event at time t = 0, a real TDC measures  $t_{\text{Offset}}$ . In every application, the offset of the TDC will add to differences in reference and signal paths. Practical applications have to be able to either cope with any offset, or include offset compensation. The offset does not depend on the time to be digitised. Any constant offset can be compensated for by adding a constant value to the measurement, regardless of the measurement itself. The transfer function of a real TDC can be approximated adding a constant to the approximation formula for ideal TDCs:

$$i = ((t + t_{\text{Offset}}) \mod t_{\text{LSB}}) \operatorname{div} t_{\text{LSB}}$$

The method of least squares is used to determine the offset, minimising the sum of the squared INLs for all bins:

$$\sum_{i=0}^{N-1} t_{\text{INL},i}^2 = \sum_{i=0}^{N-1} \left( t_i - i t_{\text{LSB}} + \frac{1}{2} t_{\text{LSB}} - t_{\text{Offset}} \right)^2 \longrightarrow \min$$

In practice, the offset of both the TDC and the input signal chain is expected to vary slowly during operation due to temperature changes. The offset can be minimised by careful layout, making sure the paths of both signal and reference are as similar as possible, the connected circuitry outside the chip will be very different in many applications. The off-chip contributions will be dominant and require periodic recalibrations at the system level.

• The Double Hit Resolution

The double hit resolution is the minimum delay between two subsequent time measurements in the same channel. It is limited by the time it takes to process the data in the first stage and could be called maximum hit frequency, as it is similar to the maximum sampling frequency of an ADC. However, the term 'frequency' is rather used for periodic signals, while the hit signal is random by definition.

In addition, the conversion can be affected by random effects and by other signals:

- Jitter or Phase Noise

- Noise

- Crosstalk

Those effects depend strongly on the implementation of the chip and the system.

At the system level, further properties are important. They do not characterise the quality of the time to digital conversion, but reflect the requirements of the system.

• Number of channels per chip

In HEP applications, a complete sub-detector can easily consist of many tens of thousands closely spaced channels. TDCs should have as many channels as possible, in order to minimise the number of chips required. In most other applications such as RADAR<sup>†</sup>, e.g. in cars, LIDAR<sup>‡</sup> and mass-spectroscopy, only a few channels are needed [RRRK00, PMK02] and the sensors are often meters

<sup>&</sup>lt;sup>†</sup>RAdio Detection And Ranging <sup>‡</sup>LIght Detection And Ranging

apart from each other. Sharing a common TDC requires all timing sensitive signals to be brought to the chip, while in a one-chip-per-channel approach, only digital signals need to be distributed.

• Calibration requirements

The implementation of the TDC time base also determines the calibration required to achieve precise measurements. While automatic calibration e.g. to the reference clock period is intrinsic to some time base architectures, others require special calibration procedures to be followed in regular intervals. If the signals to be measured are random, they can be used for a calibration using a code density test (section 8.2.2, p. 103). Otherwise, dedicated calibration signal generation can be required.

• Integrated System-level functionality

A TDC digitises a time, and all measurement data is expected to be read out. In HEP applications, the amount of data generated is far too high to be stored for off-line processing. Data reduction is required. The TDC ASIC can include a first level of data reduction. Avoiding the readout of data to be discarded as early as possible reduces also the power required to transfer those data.

The readout bandwidth is often limited by the availability of the data link or the receiver. In HEP applications, many events arrive within a small time window on different channels, followed by phases of no or low activity. In those cases, it is essential to derandomise the data. Storing data in a buffer memory until the next processing stage is ready converts data available at highly random times into a data flow with rather constant data rate [CAA57,Jai91]. If the link is shared among multiple TDCs, a readout buffer can be included on-chip to store any data that is ready for readout until the readout link is attributed to the specific chip.

• Maximum hit rate

The maximum hit rate is the maximum rate at which the TDC can accept hits, averaged over a given time. Once this rate is exceeded, data losses can occur due to buffer overflows. It must not be confused with the double pulse resolution, which specifies the minimum time between any two successive hits. • Power dissipation

Power dissipation translates into supply current and heat dissipation. In HEP applications, active cooling is often required [CMS00]. The larger the heat dissipation, the more material is needed for efficient cooling. In the ALICE inner tracking system, cooling and mechanics figure accounts for a large fraktion of the material budget [ALI95]. As little extra material as possible should be added inside a detector, as it can interact with the particles that are to be measured [Hal09]. Larger supply currents lead to thicker supply cables or larger resistive losses in the supply cables, causing heat dissipation. Thicker cables increase the material budget both by themselves and by their support structures.

Therefore, it is essential to minimise the power dissipation of all chips inside a detector. A chip with multiple channels can be designed such that some parts of the chip are used for all channels while only a few parts are duplicated for each channel. From a global detector point of view, it is advantageous to share one chip by all channels that are nearby and require only little signal routing.

Chapter 3. Basic Principles of a TDC

## **4 TDC Data Flow Architecture**

#### 4.1 Specifications

The new TDC needs to have 32 channels with a resolution of 25 ps or better. The time of arrival of a leading or a trailing edge will be measured depending on the configuration. To save readout bandwidth, in case both leading and trailing edge have to be digitised, the data can be converted into time of arrival of the leading edge and pulse width, as the latter requires a smaller dynamic range. In Time Over Threshold (TOT) measurements, the relevant information is the pulse width, not the time of arrival of the trailing edge. Often, the pulse width has to be known with a higher resolution than the time of arrival and the precision of the leading edge timestamp can be reduced prior to readout. The minimum dynamic range to be covered is in the order of 150 ns. One option for the CLIC RF bunch train length is 58.4 ns [BCdR<sup>+</sup>06]. A trigger feature allows to select hits for readout. Typically, the majority of data is discarded before leaving the TDC chip. This requires a buffer large enough to store all data during the trigger latency, i.e. until the trigger signal is available to the TDC chip. Overlapping triggers should be accepted. In triggered applications, it is often convenient to have the time scale relative to the trigger timestamp. The double pulse resolution, the time between to successive signals that can still be distinguished, has to be about 2 ns or smaller. For CLIC, bunch trains of 58 ns duration with a repetition rate of  $150 \text{ Hz} = (7 \text{ ms})^{-1}$  are being discussed [BCdR<sup>+</sup>06]. To save readout resources, multiple TDCs will share the readout link. Due to the trigger latency, readout will only take place after the high activity bursts. The last TDC to be read out will need to buffer the data during about 7 ms. Events may be lost, e.g. due to buffer overflows or single-event upsets, but the loss has to be signalled to the following data processing stage.

Figure 4.1: A clock driven TDC

The TDC130 has to be a highly configurable and multi-purpose, so that it can be used for most HEP applications without additional research, development and design effort, in order to reach production quantities that justify the development.

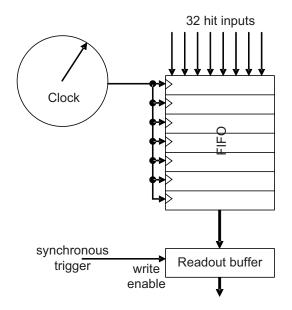

#### 4.2 Clock driven architecture

In clock driven TDCs, the state of the hit inputs is written into a FIFO<sup>†</sup> once every clock cycle (fig. 4.1). Therefore, the bin size and the double pulse resolution are equal to the clock period. The width of the FIFO is equal to the number of channels, 32. A bin size of 25 ps requires a clock frequency of 40 GHz. The FIFO has a fixed latency, which is equal to the trigger latency. As one data word is generated per clock cycle, the FIFO occupancy is independent of the activity of the channels. In ALICE TOF, this latency is about 1.2  $\mu$ s [AAea09], requiring a FIFO of 1.2  $\mu$ s × 40 GHz × 32 b ≈ 1.5 Mb operating at 40 GHz. This cannot be implemented in the chosen 130 nm-technology and, moreover, consumes a considerable amount of power. At the arrival of the trigger signal, the corresponding hit input state word is leaving the FIFO and transferred to

<sup>&</sup>lt;sup>†</sup>First In-First Out memory

the data input of the readout buffer. The readout buffer is write enabled if the TDC is triggered and disabled otherwise. Note that the trigger is not sensitive to the data in the FIFO, but to its position. Therefore, corrupted data in the FIFO doesn't influence the operation of the chip. The operating frequency of the data processing puts further limits on the double pulse resolution. In addition to the state of the hit inputs, a timestamp has to be stored in the readout buffer. The dynamic range of the time reference must be at least equal to the trigger latency if no timestamp is added in the FIFO. In HEP applications, very often a short period of activity is followed by a long break, as e.g. in the proposed CLIC system [BCdR<sup>+</sup>06]. In those cases, it is very inefficient that the input state has to be written into the FIFO even if there is no signal expected, in order to keep synchronisation.

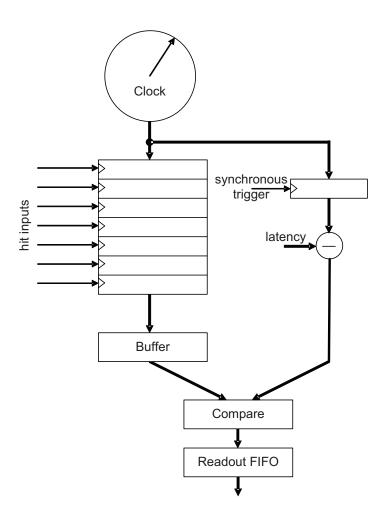

#### 4.3 Data driven architecture

In data driven architectures (fig. 4.2), the first memory, called hit register, is clocked by the hit inputs – whenever a hit signal arrives, and only then, the timestamp provided by a reference is stored. The operating frequency of the hit register is equal to the hit rate, the amount of data to be processed in a channel depends on the channel's activity. The maximum operation frequency fixes the double pulse resolution and does not influence the resolution. Each channel has its own hit register. The hit timestamps are transferred from the hit registers to a level-1 buffer. This buffer stores the timestamps during the trigger latency. The required buffer size depends on the number of hits during this period. Typically, in HEP experiments, the hit rate is in the order of 10 kHz to 1 MHz, which is considerably less than the inverse bin size of, in the hypothetical case being discussed, 40 GHz. Therefore, the level-1 buffer can be much smaller and consumes less power than the FIFO in clock driven architectures. However, if the actual hit rate exceeds the design value, buffer overflows can occur. Storing the data during the long breaks between the high activity periods, like in CLIC applications, has no implication on the buffer sizes.

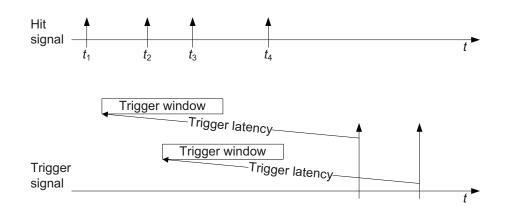

Once the trigger signal arrives, a trigger timestamp is generated which takes the trigger latency into consideration. The data in the level-1 buffer is compared with the trigger timestamp. If the hit timestamp is within a configurable neighbourhood, called

Figure 4.2: A data driven TDC

trigger window, of the trigger timestamp, it is transferred into the readout FIFO. While the trigger mechanism in clock driven architectures does not depend on the value stored in the buffer, in data driven architectures it does. Data corruption can consequently influence the operation of the trigger mechanism and thus, seen from the user's perspective, the complete TDC. In HEP applications, the loss of a single timestamp is often not a problem. It is sufficient to implement an error detection scheme and discard all corrupted data. The readout path is common for all channels. Therefore, the data coming from different channels need to be merged at some point between the hit registers and the readout buffer. This point can be chosen by the designer.

| ven Architecture           |

|----------------------------|

|                            |

| d clock period indepen-    |

|                            |

| n be much smaller than     |

| 1                          |

| double pulse resolution    |

| t                          |

| n be much smaller than     |

| e resolution               |

|                            |

|                            |

| low possible               |

| lepends on hit rate        |

|                            |

| ata in buffers can require |

| С                          |

|                            |

Table 4.1: Comparison of Data Flow Architectures

#### 4.4 Choice of Data Flow Architecture

Tab. 4.1 summarises the comparison. Overall, the data driven TDCs can fulfil the requirements for HEP experiments much better than clock driven TDCs at the price of a more complicated trigger mechanism. The main disadvantage, the sensitivity of the control to corrupted data, can be compensated for using error detection or even error correction schemes. Therefore, the TDC presented in this thesis is data driven. The following sections describe the chosen architecture in more detail. Chapter 4. TDC Data Flow Architecture

# 5 Time Base Architectures Overview

The time base provides a timing reference to the channels. Two different groups of TDC time bases are established. In time-tagging TDCs, the time is measured relative to a global reference, for example the 40 MHz LHC clock. This is similar to normal watches. In start-stop TDCs, there is typically one start channel and one or multiple stop channels. A signal on the start channel starts a circuit generating a time information, and a signal on a stop channel stops this circuit for the respective channel. This is comparable to stop watches in sport competitions.

Due to the high number of channels needed in an experiment and the availability of a very well defined reference clock that serves as a global reference for most systems in HEP experiments such as LHC, the TDC130 is a time-tagging TDC. Whenever a start-stop measurement in required, the time difference of two channels, which do not necessarily need to be connected to the same chip, can be calculated off-chip, e.g. in an FPGA.

There are many different options for the implementation of a time base, as shown in this chapter. To understand the global architecture, it is sufficient to know they all provide a digital timestamp that is distributed to the channels.

# 5.1 Time Base Architectures

Different methods have been proposed in the past for accurately measuring time [Por73, MRT<sup>+</sup>07, Kal]. To reduce power consumption, the TDC130 will have a single time base that provides the time information simultaneously to all channels. In this way, the power consumption of the time base is not duplicated for each channel.

The current integration method, for example, requires one time base per channel. In the simplest case, a constant current source is feeding a capacitor between the arrival of the start and the stop signal. The voltage across the capacitor is a measure for the time difference and can be converted using a standard ADC. This time base cannot be shared by all channels, which makes it unsuitable for the TDC130. Therefore, such techniques are not described in detail in the following sections.

#### 5.1.1 Counter based Architecture

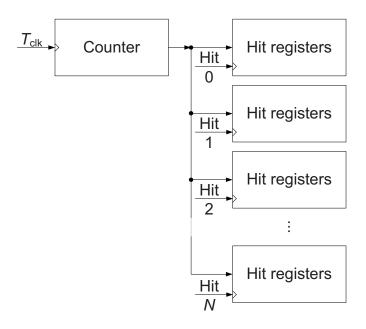

A common technique for timestamp measurements is based on a counter that is driven by a clock source. Whenever a hit arrives, the counter value is stored in the hit register of the corresponding channel while the counter continues running (fig. 5.1). The resolution is equal to the period of the reference clock,  $T_{clk}$ . The accuracy is given by the stability of the reference clock and the hit registers. The dynamic range is limited by the counting range and can easily be extended according to the application's needs. Counters are easy to implement in a digital design and could even be synthesised automatically, if no particular constraints, especially on speed, are to be respected.

A potential problem of the counter technique is the sensitivity to metastability [HEC89, Has97, Cyp97] in the hit registers. If a hit arrives while the counter is toggling, the timestamp stored in the hit registers is unpredictable. In a Gray code counter, only one bit toggles at a time. If this bit gets corrupted, the value of the timestamp can only shift by one bin size. Another method is to have two counters running on opposite phases of the same reference clock and sample both together at the arrival of a hit. While one counter might have toggled, the other counter is guaranteed to be stable. In a next step, one of the two timestamps will be discarded. The problem consists in determining which timestamp might have been affected by metastability.

A counter with a resolution of 25 ps requires a clock of  $(25 \text{ ps})^{-1} = 40 \text{ GHz}$ . In the chosen 130 nm-technology, such a clock cannot be provided, and neither can a counter running at that speed be built. In the following sections, other techniques are described. They all can give a higher resolution than a counter. Combining them with a counter extends their dynamic range to that of the counter while keeping the high resolution.

#### Figure 5.1: Counter based TDC

The hit registers are clocked by the respective channel's hit input signal.

They can also provide the information on which of the two counters has toggled more recently.

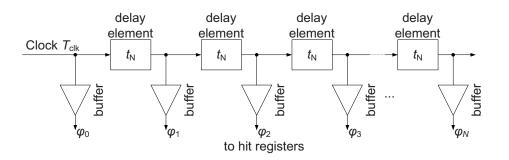

## 5.1.2 Delay line based Architecture

A conceptually simple way to obtain high resolution is phase interpolation using delay lines with multiple, equally spaced tap-outs (fig. 5.2). In this case, a low frequency clock signal is delayed in small steps. Let  $T_{clk}$  be the period of the reference clock and N the number of tap-outs. Assume the delays of all elements are equal and sum up to  $T_{clk}$ . The bin size is then  $t_N = \frac{1}{N} T_{clk}$ . The phase shifted versions  $\varphi_0 \dots \varphi_{N-1}$  of the clock signal are distributed to the hit registers. The position of the clock edge within the delay line at the time of the hit's arrival and thus within the hit registers gives the hit timestamp. It is irrelevant which clock edge is taken for this measurement. A hit may arrive at any time during a clock period. Therefore, the delay line must cover the full clock period. As the clock signal is periodic, even if the line delay was longer than

Figure 5.2: Delay line

a clock period, the dynamic range is limited to the clock period. However, it can be extended using a counter clocked by the same clock as the delay line.

#### Passive delay elements

Delay elements, RCs, LCs or transmission lines, can be implemented in sub-micron CMOS technologies. Resistors are easy to implement in a digital CMOS process, but the signal is attenuated along the line. Inductors can be built using standard metal wires and generate less attenuation, but take considerable space [SRGR03, DDTGG05]. In addition, coupling between multiple, closely spaced inductors is expected. Transmission lines are basically straight, shielded wires, as opposed to circular, not necessarily shielded inductors. Compensation of the process variations is necessary at least once per chip, if not once per start-up [Mot00] to obtain optimum linearity. Resistors that are not implemented using metal interconnects are subject to temperature variations and may require temperature compensation. Additional capacitors can be connected to increase the delay in all implementations. For LCs and transmission lines, the signal can be tapped out from different places within the inductors or the transmission lines to reduce the delay. Synthesisable digital logic can perform the calibration based on a code density test (ch. 8.2.2).

#### Gate delays

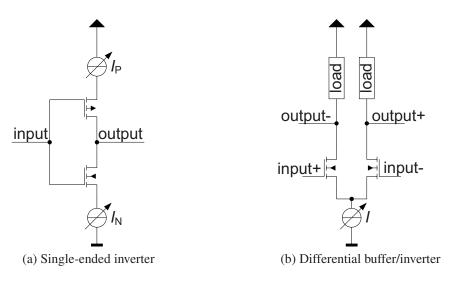

In 130 nm-technologies, the gate delay is in the order of tens of picoseconds. As the desired resolution is in the same order of magnitude, using gate delays as delay ele-

Figure 5.3: Adjustable delay gates

ments instead of the above-mentioned passive delay elements is an option. The gate delay can be adjusted limiting the current passing through its transistors (fig. 5.3). While this is trivial in differential buffers, single-ended inverters need two additional transistors for current limitation. The delay can be adjusted using a control voltage or a control current. The delay line is called Voltage Controlled Delay Line (VCDL) or Current Controlled Delay Line (CCDL). Alternatively, multiple current limiting transistors, typically with binary weighted sizes, can be used. The delay is adjusted by enabling or disabling current limiting transistors [DGLN95, WWCL05]. The adjustment can be performed by digital logic and the delay line is called a digitally controlled delay line.

The delay of a gate depends not only on the process, but also on temperature and even supply voltage variations. Therefore, the calibration needs to be performed more frequently.

Adjustable delay gates are slower than non-adjustable gates as the current control introduces additional parasitics and results in reduced current driving.

Figure 5.4: DLL (*k*=1 in nominal operation)

### 5.1.3 Delay Locked Loop based Architecture

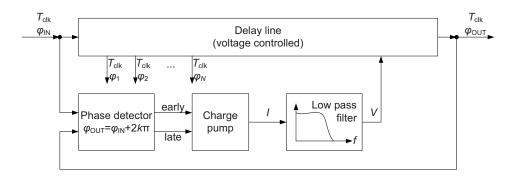

A VCDL or CCDL can be part of a control loop that automatically adjusts the delay of the full line to be equal to one clock cycle. Such a device (fig. 5.4) is called Delay Locked Loop (DLL).

An *N*-element DLL provides *N* phase shifted tap outputs to the hit registers, just as a delay line (5.1.2). It is always tuned so that the sum of all delays equals one reference clock cycle,  $T_{clk}$ . This cancels process, temperature and supply voltage variations, as long as they affect all elements equally.

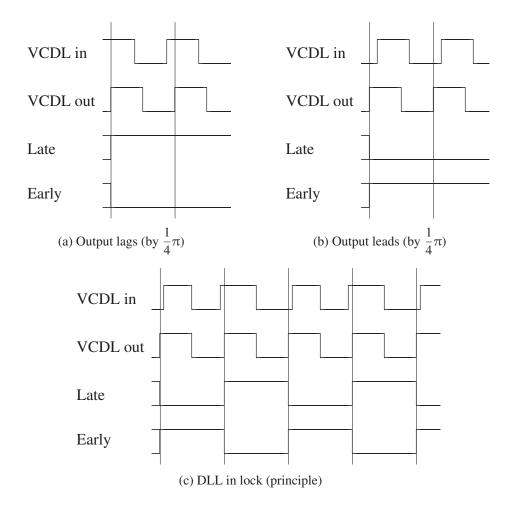

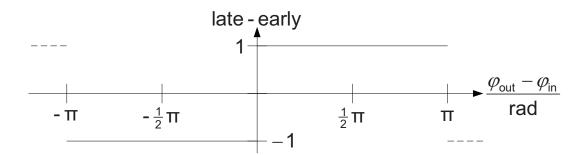

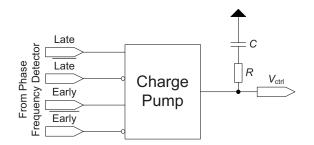

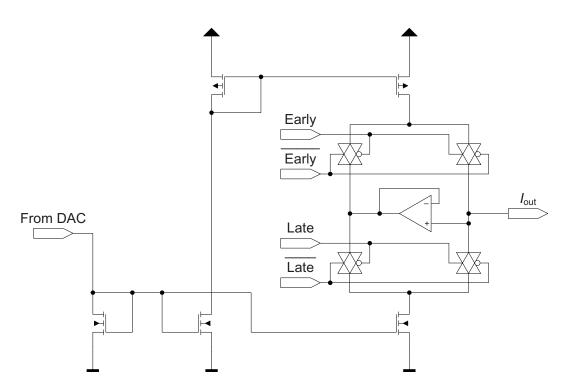

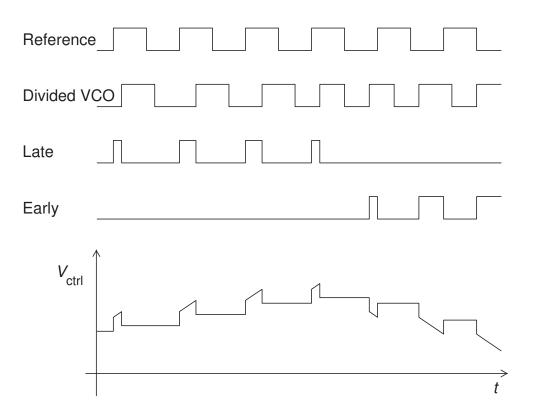

The control loop of a DLL consists of a phase detector, a charge pump, a loop filter and the delay line. The phase detector compares the phase at the delay line input to that at the output. The target phase difference between input and output is  $2\pi^{\dagger}$ . Depending on whether the phase difference is smaller or larger than the target value, it makes the charge pump sink or source a current for one clock cycle. The current is low-pass filtered by the loop filter, which consists of a capacitor. Every phase detector decision thus adds or removes a constant amount of charge to or from the loop filter capacitor, increasing or decreasing the voltage across it by a constant amount. This voltage is called control voltage, as it is used to control the current sources in fig. 5.3 and thus the delay of the delay line.

<sup>&</sup>lt;sup>†</sup>This is the nominal case. In principle, the phase detector can make the loop lock to a phase difference of  $2\pi k$  with  $k \ge 0$  integer. Additional circuitry assures that it always locks to  $2\pi$  (section 7.2.7, p. 71)

Figure 5.5: PLL (*k*=1 in nominal operation, *N* is the clock multiplication factor)

## 5.1.4 Phase Locked Loop based Architecture

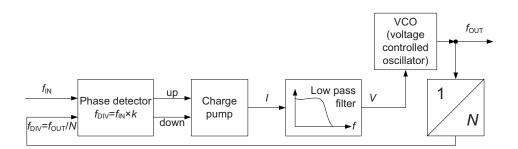

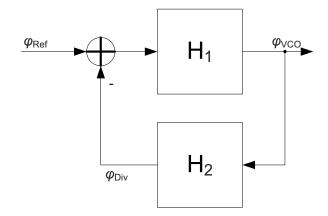

Alternatively, a Phase Locked Loop (PLL) can be used as time base. A PLL (fig. 5.5) consists of a Voltage Controlled Oscillator (VCO) that generates an output signal with a frequency  $f_{out}$  which depends on a control voltage. The loop assures that the output frequency is *N*-times higher than the frequency of a reference clock signal. Let's first consider the case with N = 1, when both reference input and VCO output have the same frequency.

Both the reference clock signal and the VCO output signal are fed to the phase detector. The phase detector compares these two signals. Depending on whether the VCO output phase is leading or lagging the reference clock phase<sup>†</sup>, it makes the charge pump sink or source a current for a duration of one reference clock cycle. If the frequencies are equal, the charge pump neither sinks nor sources any current. This current is converted into the VCO control voltage by a low-pass filter.

A major difference between PLL and DLL is that the PLL loop changes the frequency, not the phase, of the output signal in order to reach zero phase difference between reference input and VCO output. As the phase is the integral of the frequency, the phase detector introduces a new pole into the transfer function. The PLL is a second order system, which is not intrinsically stable.

If a frequency divided version of the VCO clock is fed to the phase detector, the phase detector compares the reference frequency to the divided VCO output frequency.

<sup>&</sup>lt;sup>†</sup>This is the nominal case. In general, a phase detector cannot distinguish phase differences that are integer multiples of  $2\pi$ . Depending on the phase detector implementation, additional circuitry may required to assure that the PLL always locks to the reference clock frequency.

The loop makes sure that the reference input and divided VCO output have the same frequency. The VCO frequency is *N*-times higher than the reference clock frequency.

Ring oscillators are commonly used as VCO. They consist of a chain of delay elements<sup>†</sup>, where the output of the last element is connected to the input of the first. The element delay is adjusted using a control voltage. The output of a delay element is phase-shifted, i.e. delayed, with respect to the preceding element. As for the delay line and the DLL, the delay elements of the PLL oscillator can provide phase-shifted signals that are sampled by the hit registers.

A fundamental difference between DLL and PLL is that the PLL generates its own signal, while the DLL delays the input signal without changing its frequency. A PLL can reduce the jitter of the reference clock signal if the VCO jitter is lower than the reference jitter. In this case, the jitter of the TDC timing measurement is lower than it would be if a DLL was to be used.

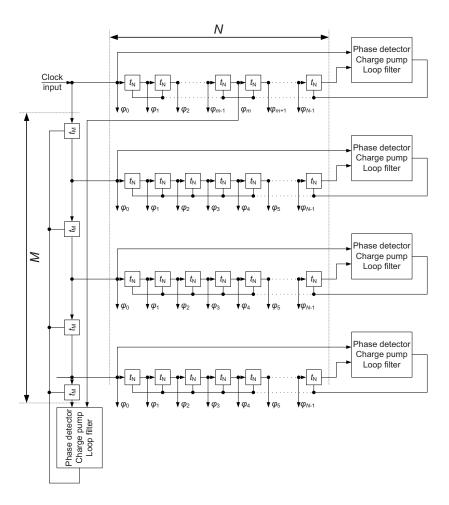

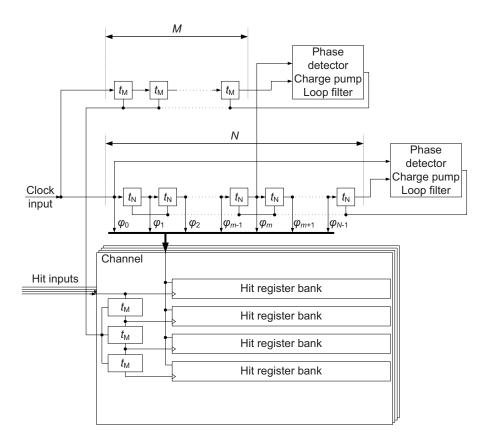

### 5.1.5 Array of DLLs based Architecture

As shown in chapter 5.1.3, DLLs can be used to generate multiple phase-shifted versions of the same, rather low frequency signal. The bin size is equal to the phase shift. The minimum delay of a single element is limited by the technology, but it is possible to have multiple DLLs with slightly shifted input phases. The shifted input phases can be generated using another DLL. Long delay lines lead to mismatch and consequently linearity problems, but in an array of DLLs, the individual lines are short and independently controlled. For the encoding and following data processing, it is convenient, but not necessary, to have a total bin number which is a power of 2. Fig. 5.6 shows the arrangement of DLLs, fig. 5.7 the bins.

Note that in fig. 5.6, the *M*-element DLL's phase detector takes the signals from the end of the delay line, as usual, and from the output of the  $m^{\text{th}}$  delay element of the first

<sup>&</sup>lt;sup>†</sup>To oscillate, the signal at the end of the chain needs to be inverted with respect to the input. If an odd number of inverters is used, this condition is fulfilled, but the number of bins is odd, in particular not a power of 2, and the delay of the chain covers only half a clock cycle. However, techniques to build ring oscillators with an even number of bins have been developed [AI96].

Figure 5.6: Array of DLLs

*N*-element DLL. Thus, in lock, the delay of the full *M*-element chain is equal to the delay of *m* elements in the *N*-element DLLs.

$$t_{\rm M} = \frac{m}{M} t_{\rm N}$$

The number of bins of the array into which a bin of an *N*-element DLL is divided into is called 'interpolation factor'. An interpolation factor F = 4 can be achieved with m = 5 and M = 4. The phase shift between two subsequent *N*-element DLLs is then  $t_{\rm M} = \frac{5}{4}t_{\rm N} = (1 + \frac{1}{4})t_{\rm N}$  instead of  $\frac{1}{4}t_{\rm N}$ . This is equivalent, as the subtraction of integer numbers of  $t_{\rm N}$  corresponds to fixed rotations of the corresponding part of the timestamp. As example, let's look at the outputs of the 4<sup>th</sup> element of each *N*-element DLL. For simplicity, let t = 0 be the time that the input clock signal toggles. In the DLL whose input is fed by the same signal as the *M*-element DLL, this signal toggles at  $t = 4t_N$ . In the second DLL, the same element toggles with an additional delay of  $t_M = \frac{5}{4}t_N$ , thus at  $t = 5\frac{1}{4}t_N$ , not at  $4\frac{1}{4}t_N$  as required. The difference is exactly  $1t_N$ , so a signal with the required timing can be found at the output of the 3<sup>rd</sup> element's output. The 2<sup>nd</sup> element of the third DLL toggles at  $t = 4\frac{2}{4}t_N$ , the 1<sup>st</sup> element of the fourth DLL at  $t = 4\frac{3}{4}t_N$ .

#### 1<sup>st</sup> DLL

| 0 4 8 12 16 20 24 28 32 36 40 44 48 52 56 60 64 68 72 76 80 84 88 92 96 100 104 10 | 8 112 116 120 124   |

|------------------------------------------------------------------------------------|---------------------|

| 2 <sup>nd</sup> DLL                                                                |                     |

| 1 5 9 13 17 21 25 29 33 37 41 45 49 53 57 61 65 69 73 77 81 85 89 93 97 101 105 1  | 09 113 117 121 125  |

| 3 <sup>rd</sup> DLL                                                                |                     |

| 2 6 10 14 18 22 26 30 34 38 42 46 50 54 58 62 66 70 74 78 82 86 90 94 98 102 106   | 110 114 118 122 126 |

| 4 <sup>th</sup> DLL                                                                |                     |

| 3 7 11 15 19 23 27 31 35 39 43 47 51 55 59 63 67 71 75 79 83 87 91 95 99 103 107   | 111 115 119 123 127 |

#### Figure 5.7: Bins in a $4 \times 32$ array of DLLs

The bins without number are bins 129...131 of the preceding clock cycle or bin 0...3 of the following cycle respectively.

This technique requires M DLLs with a constantly propagating clock signal, and one DLL with a clock signal that propagates only at the beginning of each clock cycle. The power dissipation is larger than that of a single DLL by a factor between 4 and 5. As the DLL array is shared among all channels, all MN tap-out signals need to be routed to all channels – the routing effort is non-negligible.

# 5.2 Fine Time Interpolation Techniques

The resolution of both DLL and PLL based techniques are limited by the delay of the gates used as delay elements, which is given be the technology. To further increase the resolution, different techniques can be used to provide sub-gate delay interpolation.

## 5.2.1 Dual-Slope Analogue Time Expansion

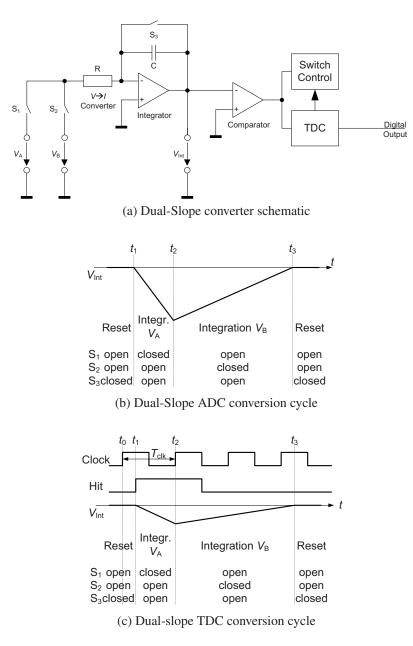

In the domain of voltage ADCs, the dual-slope conversion has been used for a long time. The input signal, a voltage, is converted into a time using an integrator, a reference, a comparator and some control logic (fig. 5.8a) [TS02].

Fig. 5.8b shows a voltage measurement cycle. The input voltage  $V_A > 0$  is converted into a current, which is integrated over a fixed time  $t_2 - t_1$ . Afterwards, the switch control replaces the input voltage by a reference voltage  $V_B < 0$ . When the integrator's output voltage  $V_{Int}$  reaches 0 at  $t_3$ , the switches are put into reset configuration, ready to take a new sample. The charge of the capacitor is zero at  $t_1$ , then decreased until  $t_2$ and increased to zero at  $t_3$ :

$$\frac{1}{R}V_{A}(t_{2}-t_{1}) + \frac{1}{R}V_{B}(t_{3}-t_{2}) = 0$$

$$\iff V_{A} = -V_{B}\frac{t_{3}-t_{2}}{t_{2}-t_{1}}$$

The durations of the charge and discharge cycle are measured and represent the input voltage as a function of the reference voltage.

This principle can be easily adapted to time measurements. The conversion circuitry may mainly remain unchanged; the only difference is the control of the current sources. Both  $V_A$  and  $V_B$  serve as reference voltages. Their sign is opposite, in fig. 5.8c  $V_A > 0$  and  $V_B < 0$ . The dual-slope TDC is used to provide only the fine part  $t_1 - t_0$  of a time stamp with high resolution and low dynamic range, while other circuitry gives the coarse part  $t_0$  with low resolution and high dynamic range. Therefore, the presence of a reference clock with a period  $T_{clk}$  provided for the coarse measurement must be assumed. Without loss of generality, assume the TDC is set to be sensitive to leading edges on the hit input. At the arrival of a hit, the current  $\frac{V_A}{R}$  is integrated until the e.g. next leading edge of the reference clock. Subsequently, the switches are changed and  $\frac{V_B}{R}$  is integrated until the integrator output voltage  $V_{Int}$  equals 0. A coarse timestamp at the moments  $t_1$ ,  $t_2$  and  $t_3$  is available.  $t_0 = t_2 - T_{clk}$  due to the implementation of the switch control. As before,

$$\frac{1}{R}V_{\rm A}(t_2 - t_1) + \frac{1}{R}V_{\rm B}(t_3 - t_2) = 0$$

Figure 5.8: Dual-slope converter

Now, the quantity to be measured is the fine timestamp,  $t_1 - t_0$ :

$$\iff t_2 - t_1 = \frac{-V_{\rm B}}{V_{\rm A}} (t_3 - t_2)$$

$$\iff t_1 - t_0 = t_1 - (t_2 - T_{\rm clk}) = \frac{V_{\rm B}}{V_{\rm A}} (t_3 - t_2) + T_{\rm clk}$$

Instead of  $t_1 - t_0$ ,  $t_2 - t_1$  can be used as fine part of the timestamp – in this case it is not referenced to the preceding rising edge of the reference clock, but to the following. As this difference is too small to be measured directly, it is stretched by a constant factor k and the larger value  $t_3 - t_2$  is measured instead. k is called stretch factor [Mot00]:

$$k = \frac{t_3 - t_2}{t_2 - t_1} = -\frac{V_{\rm A}}{V_{\rm B}}$$

To increase the resolution, k needs to be greater than 1, thus  $|V_A| > |V_B|$ .

This technique introduces a dead time that is increasing with the stretch factor, thus the desired resolution. k needs to be stable and known with precision. Therefore, good matching of the reference voltage sources and the switches  $S_1$  and  $S_2$  is required. Noise coupling into the integrator, capacitor non-linearities and the comparator stability further limit the accuracy.

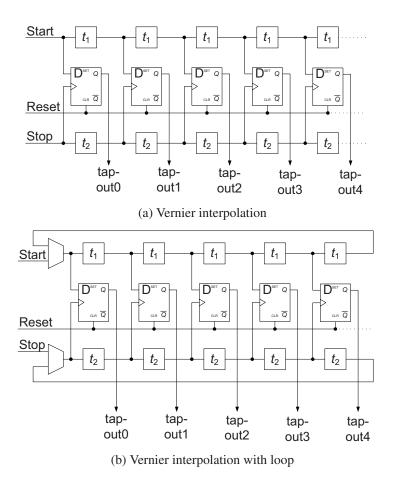

#### 5.2.2 Vernier Techniques

Vernier techniques are very much similar to a vernier calliper. They are based on D flip flops and delay elements with two different delays and perform start-stop measurement [Mot00]. In the simplest case (fig. 5.9a), the D flip flops are clocked with the stop signal and sample the start signal. Assume the hit is the rising edge of both signals. Between one flip flop and the next, the start signal is delayed by a time  $t_1$  and the stop signal by  $t_2 < t_1$ . Hence, the further the signals propagate through the lines, the smaller the difference between the arrival of the start and the stop signal. Eventually, if the line is long enough, the stop signal will overtake the start. The output of the following flip flops will be 0 instead of 1. Let 1-to-0 transition occur after the  $n^{\text{th}}$  flip flop. Assuming ideal D flip flops, the difference between start and stop signal to be measured is  $t_{\text{start}} - t_{\text{stop}} = nt_1 - nt_2 = n(t_1 - t_2)$ . A large dynamic range requires

Figure 5.9: Vernier interpolation schemes

long chains of delay elements and flip flops. It is possible to let the signal propagate though the same delay elements multiple times arranging the delay elements in a ring structure (fig. 5.9b). The dynamic range of such a circuit is infinite. However, already the straight line implementation is very sensitive to delay cell mismatch. In a ring, the signal propagates through the same elements multiple times, accumulating the error. Calibration has to be performed in absence of hits. The delay elements can be operated as a ring oscillator in order to measure their total delay. Modifications of this technique enable the use for timestamp measurements, but still suffer from very high sensitivity to delay cell mismatch.

## 5.2.3 Passive LC lines or RC lines

Figure 5.10: Passive delay line interpolation

```

\begin{array}{l} \text{Main register } (y=0) \\ \hline 0 \ 1 \ 2 \ 3 \ 4 \ 5 \ 6 \ 7 \ 8 \ 9 \ 10 \ 11 \ 12 \ 13 \ 14 \ 15 \ 16 \ 17 \ 18 \ 19 \ 20 \ 21 \ 22 \ 32 \ 4 \ 25 \ 26 \ 27 \ 28 \ 29 \ 30 \ 31 \ \end{array} \\ \hline \text{First interpolation register } (y=1) : \text{Delayed by } 1 \times \frac{t_{\text{N}}}{4} \\ \hline 0 \ 1 \ 2 \ 3 \ 4 \ 5 \ 6 \ 7 \ 8 \ 9 \ 10 \ 11 \ 12 \ 13 \ 14 \ 15 \ 16 \ 17 \ 18 \ 19 \ 20 \ 21 \ 22 \ 32 \ 4 \ 25 \ 26 \ 27 \ 28 \ 29 \ 30 \ 31 \ \end{array} \\ \hline \text{Second interpolation register } (y=2) : \text{Delayed by } 2 \times \frac{t_{\text{N}}}{4} \\ \hline \hline 0 \ 1 \ 2 \ 3 \ 4 \ 5 \ 6 \ 7 \ 8 \ 9 \ 10 \ 11 \ 12 \ 13 \ 14 \ 15 \ 16 \ 17 \ 18 \ 19 \ 20 \ 21 \ 22 \ 23 \ 24 \ 25 \ 26 \ 27 \ 28 \ 29 \ 30 \ 31 \ \end{array} \\ \hline \text{Third interpolation register } (y=3) : \text{Delayed by } 3 \times \frac{t_{\text{N}}}{4} \\ \hline \hline 0 \ 1 \ 2 \ 3 \ 4 \ 5 \ 6 \ 7 \ 8 \ 9 \ 10 \ 11 \ 12 \ 13 \ 14 \ 15 \ 16 \ 17 \ 18 \ 19 \ 20 \ 21 \ 22 \ 32 \ 42 \ 5 \ 26 \ 27 \ 28 \ 29 \ 30 \ 31 \ \end{array}

```

Figure 5.11: Local interpolation: Shifted bins.

The bins without number are bin 31 of the preceding clock cycle or bin 0 of the following cycle respectively.

Another possibility for fine interpolation, i.e. interpolation which is performed using the hit signal and thus cannot be shared among channels, is based on passive delay lines. The timestamp coming from the main time base, e.g. a DLL, is distributed to all channels. To divide the DLL time bins of size  $t_N$  into M sub-bins, the hit registers are replicated M times. The hit signal propagates through an M - 1-element delay line (fig. 5.10) with a unit delay  $t_M = \frac{1}{M}t_N$ . The tap-outs of this delay line are connected to the clock signal input of the hit register. Fig. 5.11 shows the shifted bins in such an arrangement. As delay elements, RC or LC elements can be used as well as transmission lines. The advantages and drawbacks of different delay elements are discussed in section 5.1.2. In the HPTDC, local fine interpolation has been implemented with RC delay lines.

Fig. 5.11 shows the shifted time bins for M = 4 and N = 32. For a given hit, the timestamps in the hit register blocks are either all the same or differ by 1. After binary encoding of the timestamps, thus with only  $\log_2(32) = 5$  b of data per hit register, the interpolation result can be computed. Let the transition from one timestamp value x to the next, x + 1 occur between block y and y + 1. The hit has then arrived in the (M - y)<sup>th</sup> quarter of the x<sup>th</sup> main DLL time bin. If all timestamps in the hit register banks are equal, the transition has occurred after the block with y = 3, i.e. the hit has occurred in the 1<sup>st</sup> quarter of the x<sup>th</sup> main DLL time bin.

#### 5.2.4 DLL adjusted delay lines

Resolutionwise, the array of DLLs is equivalent to one global *N*-element main DLL per chip and one local *M*-element secondary interpolation delay line per channel, reducing the amount of signals to be routed from the common time base to the individual channels. The secondary delay lines are fed by the hit input signal, not by the clock signal. This reduces the power consumption in idle mode considerably, as no signal is propagating along the line. The hit registers of each channel can be organised in *M* blocks of *N* elements. The first hit register block is triggered at the arrival of the hit, the second after a delay of  $t_M$ , the third after  $2t_M$  and so on. The secondary delay lines are not part of a control loop, but they need to be calibrated frequently. They cannot be implemented as DLLs, as DLLs require a periodic signal to propagate constantly, and the hit signal is random by definition.

The calibration problem can be avoided with a global, secondary DLL with M elements, fed by the clock signal as it is the case in the DLL array. The delay line is replicated once per channel, and the control voltage of the secondary DLL distributed to all delay lines (fig. 5.12). As delay lines in the channels are not part of a closed loop, only M - 1 elements are required. In this case, the local delay elements are auto-

Figure 5.12: DLL adjusted delay lines for fine interpolation

| Main register $(y = 0)$                                                        |

|--------------------------------------------------------------------------------|

| 0 1 2 3 4 5 6 7 8 9 1011121314151617181920212232425262728293031                |

| First interpolation register (y = 1): Delayed by $1 \times \frac{5t_N}{4}$     |

| 3101234567891011213141516171819202122324252627282930                           |

| Second interpolation register (y = 2): Delayed by $2 \times \frac{5t_N}{4}$    |

| 30310123456789101121314151617181920212223242526272829                          |

| Third interpolation register ( $y = 3$ ): Delayed by $3 \times \frac{5t_N}{4}$ |

| 2930310123456789101121314151617181920212232425262728                           |

Figure 5.13: Fine interpolation: Shifted bins.

The bins with numbers in italic belong to the preceding clock cycle.

calibrated, but do not consume power in absence of hits. The quality of the calibration depends on the mismatch between the delay line of the DLL and the delay lines in

the channels. Local fine adjustment needs to be implemented to limit the effects of mismatch. The control voltage distribution network is potentially prone to crosstalk.

Fig. 5.13 shows the shifted bins in the different hit register blocks for M = 4 and N = 32. The binary encoding of the individual blocks can be done independently, leading to the bin numbers given in the figure. It is advantageous for the decoding of the interpolation value if a rotation is performed before the encoding, resulting in bin numbers as given by fig. 5.11, because otherwise a subtraction has to be carried out. The interpolation decoding can be implemented as described in section 5.2.3.

## 5.3 Choice of Time Base Architecture

The most relevant characteristics of the different architectures are shown in table 5.1.

In the new TDC130, the main time base will consist of a DLL with a counter for dynamic range extension. Delay lines without feedback are discarded because they are not self-calibrating. Contrary to PLLs, DLLs are intrinsically first-order systems and thus stable. The advantage of the PLL, its capability of filtering jitter, would not be used, as a PLL is already needed to multiply the 40 MHz input clock up to 1.28 GHz, a value that leads to a useful bin size in a phase interpolating DLL or PLL. This clock-multiplying PLL can be used for jitter filtering.

The routing effort for an Array-DLL based TDC is judged to be excessive. Simulations show that the power required to distribute the DLL outputs to the hit registers is about the same as the power consumed by the DLL itself. In the prototype presented in chapter 7 the DLL output signals are routed at the pitch of the delay elements. Assuming the *N*-element DLLs of an array were placed in an  $N \times M$  array, M - 1 additional wires were to be routed in the space between two neighbouring wires. This space however does not allow for routing of more signals. Using different layers of metal is not possible either, as their number is limited. Spreading the DLLs in a  $1 \times (NM)$  row is not desirable. This would imply to spread the *M*-element secondary DLL across N(M-1)delay elements of the main DLL, making it very vulnerable to process variations and crosstalk.

To further increase the resolution, either passive or DLL-adjusted delay lines will be used. Those techniques offer a low channel dead time. Their power dissipation decreases with decreasing activity on the channels, which is not the case for an Array-DLL.

| Architecture                   | Resolution       | Dynamic          | Dead time | Calibration | Power dis- |  |

|--------------------------------|------------------|------------------|-----------|-------------|------------|--|

|                                |                  | range            |           |             | sipation   |  |

| Main time base architectures:  |                  |                  |           |             |            |  |

| Counter                        | T <sub>clk</sub> | $\infty$         | 0         | none        | high       |  |

| Passive delay                  | ∞                | T <sub>clk</sub> | 0         | offline     | low        |  |

| line                           |                  |                  |           |             |            |  |

| Active delay                   | gate delay       | T <sub>clk</sub> | 0         | offline     | low        |  |

| line                           |                  |                  |           |             |            |  |

| DLL                            | gate delay       | T <sub>clk</sub> | 0         | auto        | medium     |  |

| PLL                            | gate delay       | T <sub>clk</sub> | 0         | auto        | medium     |  |

| Array DLL                      | $\infty$         | T <sub>clk</sub> | 0         | auto        | very high  |  |

| Fine interpolation techniques: |                  |                  |           |             |            |  |

| Dual-slope                     | ∞                | OK               | yes       | offline     | high       |  |

| Vernier                        | ∞                | OK               | yes       | offline     | low        |  |

| Passive delay                  | ∞                | OK               | 0         | offline     | low        |  |

| line                           |                  |                  |           |             |            |  |

| DLL-adjusted                   | ∞                | OK               | 0         | auto        | low        |  |

| delay line                     |                  |                  |           |             |            |  |

Table 5.1: Comparison of time base architectures

$T_{\rm clk}$  is a clock cycle of the reference clock.

' $\infty$ ' and '0' mean the technique has no intrinsic limit. 'OK' means the dynamic range of the fine interpolation technique can reach the resolution of the main time base.

The power dissipation of an array of DLLs is high compared to other main time base architectures, but there is no need for a separate fine interpolation. However, the power consumption is higher than that of a DLL or PLL together with delay line base fine interpolation.

# 6 TDC130 Target Chip Architecture

# 6.1 Data Flow and Time Base Architecture

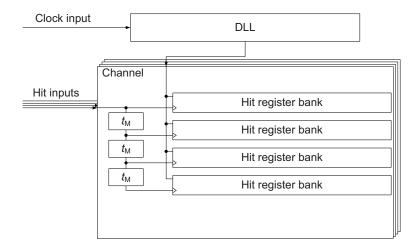

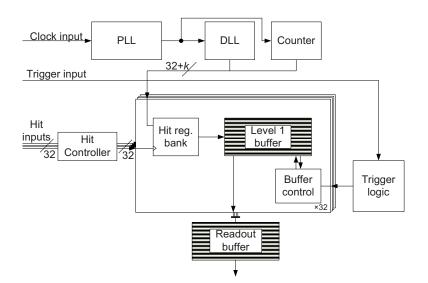

Based on the considerations stated above, it has been decided that the TDC130 (fig. 6.1) has a data driven architecture. The time base consists of a 32-element DLL with an element delay of 25 ps. The dynamic range is extended by a counter to comply with the ILC/CLIC requirements. Counter and DLL are clocked with a 1.28 GHz clock generated by an on-chip PLL. The external clock frequency is the LHC bunch crossing frequency, 40 MHz.

# 6.2 Channel Macro

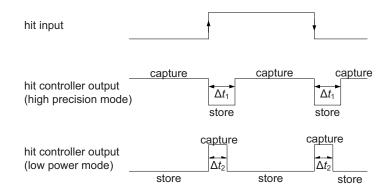

For every channel, there is a bank of hit registers, which, at the occurrence of a hit, store the timestamp provided by the time base. A hit controller converts the incoming hit signal into a control signal for the hit register bank. For every edge whose timing is to be measured, the hit controller generates a pulse in the control signal. The controller is highly configurable and can make the hit registers capture leading edge, trailing edge or either edge of the input signal. If required, the channel hit controller can be disabled for each channel individually, so that regardless of the input signal, the hit registers will not store a timestamp. This is useful if a channel is not connected or the corresponding channel in the detector itself is known to be damaged. A disabled channel dissipates minimum power and does not require bandwidth at the readout. The hit register banks constitute a pipeline and buffer the data for a short period until the following stage is ready. Furthermore, the hit controller can operate the channel in a high precision mode or in a low precision, low power consumption mode. In the high precision mode, the data in the first hit register stage is always updated. This guarantees

Figure 6.1: Target chip architecture

that the most recent timestamp is always available in the hit registers, at the price of additional power dissipation used to store data which might not be used. Once a hit arrives, the hit registers are switched from capture mode to store mode, the data is not updated anymore. If the hit arrives close to a change of timestamp, only those bits that have changed risk setup and hold problems. Only one bit of the data taken from the DLL changes at a time, as only one edge of the clock is used for the measurement. The resulting error is therefore limited to 25 ps. Once the stored hit timestamp is transferred to the next stage, the first hit register passes to capture mode again (fig. 6.2). This delay,

Figure 6.2: Hit controller output

$\Delta t_1$ , does not influence the time measurement. Therefore, there is no need to keep it constant. In the low precision/low power mode, the hit registers are not updated when in idle mode, minimising the power dissipation of the first hit register stage. Once a hit arrives, they are switched into the capture mode for a fixed time  $\Delta t_2$  before the data is stored. As it is the last timestamp captured which is stored, the hit seems delayed by  $\Delta t_2$ . Any variation of  $\Delta t_2$  directly affects the time measurement.

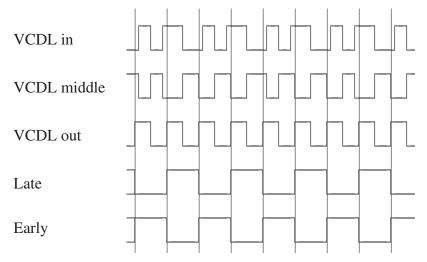

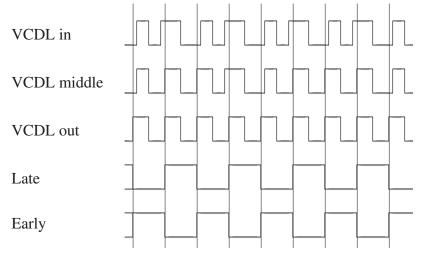

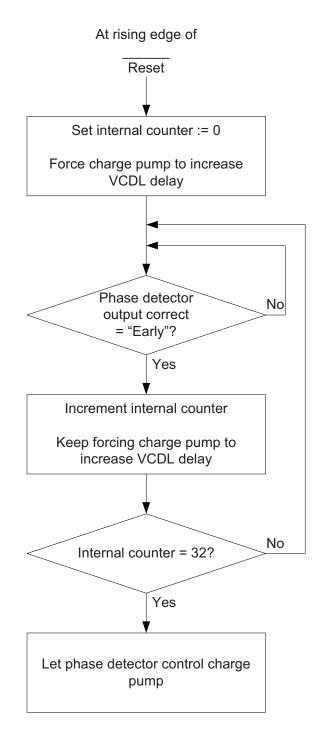

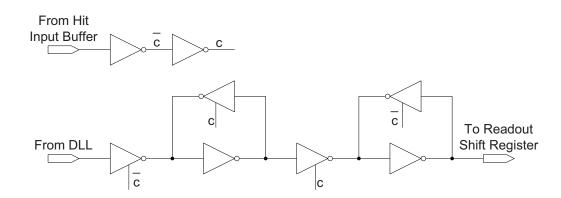

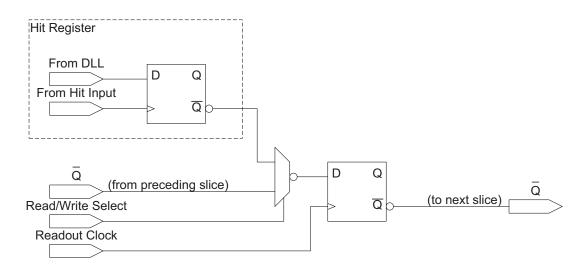

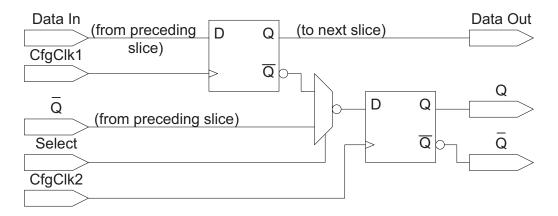

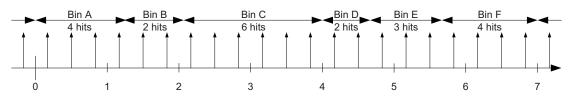

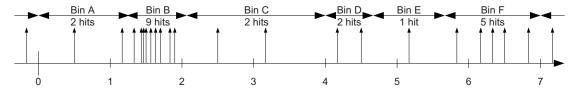

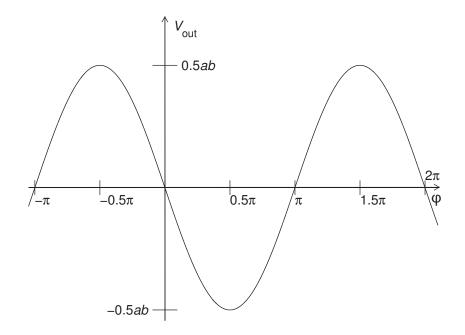

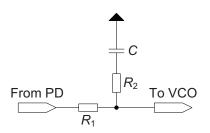

## 6.3 Level-1 Buffer Organisation