## High performance *n*-channel organic field-effect transistors and ring oscillators based on $C_{60}$ fullerene films

Thomas D. Anthopoulos<sup>a)</sup> Blackett Laboratory, Department of Physics, Imperial College London, London SW7 2BW, United Kingdom

Birendra Singh, Nenad Marjanovic, and Niyazi S. Sariciftci Linz Institute of Organic Solar Cells (LIOS), Physical Chemistry, Johannes Kepler University Linz, A-4040 Linz, Austria

Alberto Montaigne Ramil and Helmut Sitter

Institute of Semiconductors and Solid State Physics, Johannes Kepler University Linz, A-4040 Linz, Austria

Michael Cölle and Dago M. de Leeuw

Philips Research Laboratories, High Tech Campus 4, 5656 AE Eindhoven, The Netherlands

(Received 15 July 2006; accepted 26 September 2006; published online 20 November 2006)

We report on organic *n*-channel field-effect transistors and circuits based on  $C_{60}$  films grown by hot wall epitaxy. Electron mobility is found to be dependent strongly on the substrate temperature during film growth and on the type of the gate dielectric employed. Top-contact transistors employing LiF/Al electrodes and a polymer dielectric exhibit maximum electron mobility of  $6 \text{ cm}^2/\text{V}$  s. When the same films are employed in bottom-contact transistors, using SiO<sub>2</sub> as gate dielectric, mobility is reduced to  $0.2 \text{ cm}^2/\text{V}$  s. By integrating several transistors we are able to fabricate high performance unipolar (*n*-channel) ring oscillators with stage delay of 2.3  $\mu$ s. © 2006 American Institute of Physics. [DOI: 10.1063/1.2387892]

To date hole transporting (p-type) organic small molecules and polymers are by far the most widely used materials for the fabrication of functional organic circuits based on unipolar logic architectures<sup>1-9</sup>. Electron transporting (n-type) organic semiconductors on the other hand have received considerably less attention<sup>2,10</sup> with very few circuit demonstrations.<sup>11</sup> This is mainly due to the poor operating stability of the vast majority of electron transporting organic field-effect transistors (OFETs) under ambient conditions with only few exemptions.<sup>12-16</sup> Among the relatively few known electron transporting molecules is the C<sub>60</sub> fullerene with electron mobility, measured in oxygen and water free environment, on the order of 1 cm<sup>2</sup>/V s.<sup>17–19</sup> Despite the high performance, however,  $C_{60}$  based transistors degrade rapidly upon exposure to ambient air.<sup>11,18</sup> In an effort to overcome this problem Horiuchi et al.<sup>20</sup> have reported on an efficient oxygen passivation method using a top coating of alumina layer sputtered under Ar atmosphere. As a result the stability of C<sub>60</sub> transistors was considerably improved and showed no degradation upon exposure to air for a period of one month. This finding has renewed interest on fullerenes and use of C<sub>60</sub> can now be envisioned not only in organic unipolar circuits but also in the much needed complementary architectures.<sup>15,21,22</sup> To this end a primary challenge is the further improvement of the operating characteristics of  $C_{60}$ OFETs and the demonstration of functional integrated circuits.

Here we report on high mobility electron transporting (*n*-channel) organic transistors and circuits based on  $C_{60}$  films grown by hot wall epitaxy (HWE).<sup>17,23,24</sup> Making use of this technique and in combination with suitable gate dielectrics, we are able to fabricate discrete electron transport-

ing transistors and integrated ring oscillators with excellent performing characteristics.

Discrete top-contact transistors were fabricated on quartz glass substrates incorporating a predefined indium tin oxide (ITO) electrode acting as the gate terminal. Divinyltetramethyldisiloxane-bis(benzocyclobutene) (BCB), purchased from Dow Chemicals, was spin coated on the top of the quartz/ITO substrate as the gate dielectric. Following, a 300 nm thick film of  $C_{60}$  was grown by hot wall epitaxy<sup>1</sup> with the substrate maintained at different temperatures in the range of 100-250 °C. Finally, top-contact electrodes consisting of LiF/Al (0.6 and 60 nm, respectively) were evaporated under high vacuum (10<sup>-6</sup> mbar) through a shadow mask. The channel length (L) and width (W) of the transistor were 30  $\mu$ m and 1.5 mm, respectively. Bottom-contact fieldeffect transistors were made using heavily doped *n*-type Si wafers as the common gate electrode with a 200 nm thermally oxidized SiO<sub>2</sub> layer as the gate dielectric. Using conventional photolithography, gold source and drain electrodes were defined in a bottom-contact configuration with  $L=10 \ \mu m$  and  $W=10 \ mm$ . Due to the poor adhesion of evaporated gold on SiO<sub>2</sub>, a thin (10 nm) interlayer of titanium (Ti) was employed between Au and SiO<sub>2</sub>. The SiO<sub>2</sub> layer was treated with the primer hexamethyldisilazane (HMDS) prior to semiconductor deposition, in order to passivate its surface, followed by the growth of the  $C_{60}$  film by HWE. The detailed fabrication process of integrated circuits is described elsewhere.<sup>6,11,16</sup> Bottom-contact transistors and integrated circuits were annealed in vacuum  $(10^{-5} \text{ mbar})$  at 110 °C for 3 h prior to electrical characterization at room temperature.

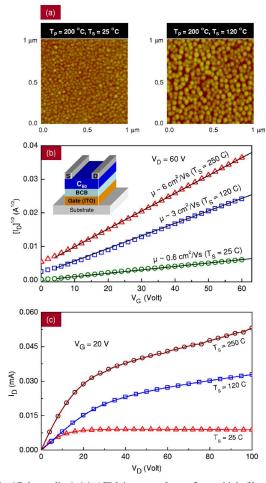

To study the effects of substrate temperature  $(T_S)$  on the crystallinity of the C<sub>60</sub>, films were characterized by means of atomic force microscopy (AFM) and x-ray diffraction (XRD) measurements. Figure 1(a) shows the AFM images for two 5 nm thick films of C<sub>60</sub> grown at different  $T_S$ . It is evident

89, 213504-1

Downloaded 25 Apr 2008 to 155.198.4.89. Redistribution subject to AIP license or copyright; see http://apl.aip.org/apl/copyright.jsp

<sup>&</sup>lt;sup>a)</sup>Author to whom correspondence should be addressed; electronic mail: thomas.anthopoulos@imperial.ac.uk

<sup>© 2006</sup> American Institute of Physics

FIG. 1. (Color online) (a) AFM images of two 5 nm thick films of  $C_{60}$  grown by HWE on BCB at  $T_S=25$  and 120 °C.  $T_P$  denotes the preheating temperature at which substrates were annealed prior to film deposition. (b) Square root of drain current  $(I_D^{1/2})$  vs gate bias  $(V_G)$  obtained from three different transistors based on  $C_{60}$  films grown by HWE at different  $T_S$ . Inset shows the schematic structure of the top-contact transistors employed. (c) Output characteristics obtained from transistors based on  $C_{60}$  films grown at different substrate temperatures:  $T_S=25$ , 120, and 250 °C.

from this images that grain size increases with increasing  $T_s$ . In particular, for films grown at  $T_s=25$  °C, the aerial density of crystallites is found to be in the order of ~500 crystallites/ $\mu$ m<sup>2</sup>, whereas for films grown at 250 °C, this figure is reduced to ~370 crystallites/ $\mu$ m<sup>2</sup>, indicating a larger grain size. Despite the morphological differences, however, both films exhibit the same highly crystalline structure, as determined by XRD measurements (data not shown), with the strongest  $2\theta$ -intensity diffraction peaks at 10.8°, 17.8°, and 20.9°  $2\theta$ , indexed as (111), (220), and (311), respectively. Our findings are in good agreement with previously published XRD data on thermally evaporated C<sub>60</sub> films.<sup>19,25</sup>

To investigate the effects of grain size on the performance characteristics of  $C_{60}$  transistors, we fabricated topcontact devices [Fig. 1(b), inset] incorporating films grown at different substrate temperatures. Figure 1(b) shows the square root of the drain current  $(I_D^{1/2})$  versus gate voltage  $(V_G)$  for three different devices at a drain voltage  $V_D=60$  V. From this figure it is evident that in all devices  $I_D^{1/2}$  depends linearly on  $V_G$ . From the linear fit in these plots, the saturated field-effect mobility was calculated employing the standard method<sup>26</sup> using a geometric capacitance value (as determined by capacitance-voltage measurements) of  $1.2 \times 10^{-9}$  F/cm<sup>2</sup>.

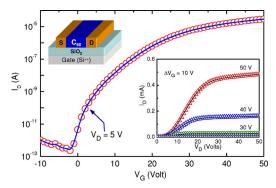

FIG. 2. (Color online) Room temperature transfer characteristic obtained from a bottom-contact  $C_{60}$  transistor ( $T_S$ =120 °C) employing SiO<sub>2</sub> as the gate dielectric. Inset diagram shows the device architecture employed. The inset figure displays the room temperature output characteristics of the transistor at different  $V_G$ .

It is evident that electron mobility increases from 0.6 cm<sup>2</sup>/V s, for films grown at  $T_S=25$  °C, to 3 cm<sup>2</sup>/V s and 6 cm<sup>2</sup>/Vs for films grown at  $T_S=120$  and 250 °C, respectively. These results are in contrast with the findings of Kobayashi *et al.*<sup>19</sup> where the electron mobility showed no correlation with  $T_S$ . We note, however, that in the latter work measurements were performed on films grown on SiO<sub>2</sub> rather than polymeric dielectrics. An additional difference in our devices is the use of low work function (LiF/Al) source and drain electrodes that results to excellent electron injecting characteristics. Experimental evidences for the latter are provided by the linear dependence of  $I_D$  on  $V_D$ , at low voltages, shown in Fig. 1(c).

The operating characteristics of bottom-contact  $C_{60}$  transistors, using SiO<sub>2</sub> as the gate dielectric (Fig. 2, inset), were also investigated. Here  $C_{60}$  layers were grown by HWE at relatively low substrate temperatures ( $T_S$ =120 °C) in order to prevent decomposition of the HMDS layer used for SiO<sub>2</sub> passivation. Figure 2 shows a typical transfer characteristic obtained from a  $C_{60}$  transistor (L=10  $\mu$ m, W=10 mm) measured at  $V_D$ =5 V. The inset figure shows the output characteristics at different  $V_G$  biases. The sigmoidal dependence of  $I_D$  on  $V_D$  at low drain voltages indicates the presence of a significant contact barrier. Despite that a high saturation mobility of 0.2 cm<sup>2</sup>/Vs is calculated. We only report the mobility values in saturation simply because in this operating regime contact effects are known to reduce significantly.<sup>11,27</sup>

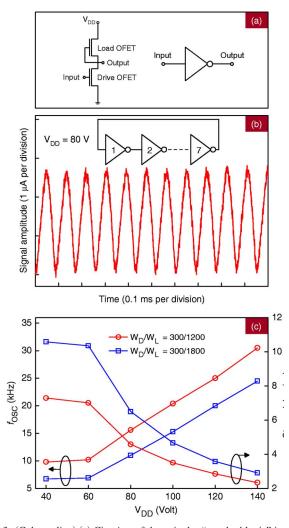

By integrating several bottom-contact transistors using the process flow chart for unipolar circuits,<sup>6</sup> we realized voltage inverters and ring oscillators. C<sub>60</sub> films were grown by HWE at  $T_s = 120 \text{ °C}$  using polyvinylphenol as the gate dielectric. We employ relatively low  $T_S$  in order to avoid possible circuit damage caused by high temperature. Figure 3(a)shows the inverter circuitry and its symbolic representation. Owed to the switching characteristics of  $C_{60}$  OFETs the logic design employed here is the  $V_{\rm G}=0$  or "standard logic."<sup>6</sup> By integrating several inverters we are able to fabricate ring oscillators [Fig. 3(b), inset]. Our fastest circuits are fabricated employing a design rule of 2.5  $\mu$ m with driver ( $W_D$ ), load  $(W_L)$ , and buffer  $(W_B)$  transistor widths of 300, 1200, and 5000  $\mu$ m, respectively. Frequency measurements were performed by measuring the current flowing through a buffer transistor, whose gate was driven by the oscillator output, using a digital oscilloscope. The output signal of a sevenstage ring oscillator, operating at a supply voltage

by capacitance-voltage measurements) of  $1.2 \times 10^{-9}$  F/cm<sup>2</sup>.  $V_{\text{DD}}$ =80 V at room temperature, is shown in Fig. 3(b). Os-Downloaded 25 Apr 2008 to 155.198.4.89. Redistribution subject to AIP license or copyright; see http://apl.aip.org/apl/copyright.jsp

FIG. 3. (Color online) (a) Circuitry of the unipolar "standard logic" inverter used and its symbolic representation. (b) Output signal of the ring oscillator measured at  $V_{\rm DD}$ =80 V in room temperature. Inset shows the schematic representation of the ring oscillator. (c) Oscillation frequency ( $f_{\rm osc}$ ) and calculated stage delay ( $\tau$ ) vs  $V_{\rm DD}$  for two ring oscillators fabricated employing a design rule of 2.5. Red circles represent data obtained from a ring oscillator with a  $W_D/W_L$ =300/1200 while blue squares represent the signal from a ring oscillator incorporating larger load transistors with  $W_D/W_L$ =300/1800.

cillation frequency  $(f_{osc})$  is found to depend strongly on  $V_{DD}$ as well as on the design rules employed. Figure 3(c) clearly demonstrates both effects. Here  $f_{osc}$  and calculated stage delay  $(\tau)$ ,<sup>16</sup> for two different ring oscillators, are plotted versus  $V_{\rm DD}$ . Red circles represent data obtained from a ring oscillator employing a design rule of  $L=2.5 \ \mu m$  with  $W_D/W_L$ =300/1200. For the second oscillator (blue squares) the same design rule applies but with  $W_D/W_L=300/1800$ . As can be seen the ring oscillator incorporating the small size load transistors ( $W_L$ =1200  $\mu$ m) operates at a higher frequency ( $f_{\rm osc} \sim 30.5$  kHz,  $\tau \sim 2.34 \ \mu s$ ) as compared with the oscillator employing load ring transistors with  $W_L$ =1800  $\mu$ m ( $f_{osc}$ ~24.5 kHz,  $\tau$ ~2.9  $\mu$ s). By increasing  $W_L$  to 3000  $\mu$ m, the operating frequency is reduced further, clearly demonstrating the importance of design principles.

In summary, we have demonstrated top-contact *n*-channel organic transistors based on films of  $C_{60}$  grown by HWE with electron mobility of 6 cm<sup>2</sup>/V s. A strong dependence of the electron mobility on the substrate temperature during film growth is observed. Increase of film grain size

with increasing substrate temperature is believed to be the main reason for the improved electron mobility obtained. By using OFETs based on  $C_{60}$ , we were able to fabricate *n*-channel ring oscillators with a maximum operating frequency  $f_{\rm osc} \sim 30.4$  kHz and a corresponding stage delay  $\tau \sim 2.34 \ \mu s$ .

The authors are grateful to the Engineering and Physical Sciences Research Council (EPSRC), EU (CT-2002-00327) and Austrian National Science Foundation (NFN No:P16891–N08, FWF No: S9706–N08) for financial support. One of the authors (T.D.A) is an EPSRC Advanced Research Fellow.

- <sup>1</sup>H. Sirringhaus, P. J. Brown, R. H. Friend, M. M. Nielsen, K. Bechgaard, B. M. W. Langeveld-Voss, A. J. H. Spiering, R. A. J. Janssen, E. W. Meijer, P. Herwig, and D. M. de Leeuw, Nature (London) **401**, 685 (1999).

- <sup>2</sup>C. D. Dimitrakopoulos and P. R. L. Malenfant, Adv. Mater. (Weinheim, Ger.) **14**, 99 (2002).

- <sup>3</sup>R. J. Kline, M. D. McGehee, and M. F. Toney, Nat. Mater. **5**, 222 (2006).

<sup>4</sup>I. Mcculloch, M. Heeney, C. Bailey1, K. Genevicius, I. Macdonald, M. Shkunov, D. Sparrowe, S. Tierney, R. Wagner, W. Zhang, M. L. Chabinyc, R. J. Kline, M. D. McGehee, and M. F. Toney, Nat. Mater. **5**, 328 (2006).

<sup>5</sup>M. Heeney, C. Bailey, K. Genevicius, M. Shkunov, D. Sparrowe, S. Tierney, and I. McCulloch, J. Am. Chem. Soc. **127**, 1078 (2005).

- <sup>6</sup>G. H. Gelinck, H. E. A. Huitema, E. van Veenendaal, E. Cantatore, L. Schrijnemakers, J. B. P. H. van der Putten, T. C. T. Geuns, M. Beenhakkers, J. B. Giesbers, B.-H. Huisman, E. J. Meijer, E. M. Benito, F. J. Touwslager, A. W. Marsman, B. J. E. van Rens, and D. M. de Leeuw, Nat. Mater. **3**, 106 (2004).

- <sup>7</sup>D. M. de Leeuw, U.S. Patent No. WO99/30432 (17 June 1999).

- <sup>8</sup>S. Steudel, K. Myny, V. Arkhipov, C. Deibel, S. de Vusser, J. Genoe, and P. Heremans, Nat. Mater. 4, 597 (2005).

- <sup>9</sup>L. Zhou, A. Wanga, S.-C. Wu, J. Sun, S. Park, and T. N. Jackson, Appl. Phys. Lett. **88**, 083502 (2005).

- <sup>10</sup>C. R. Newman, C. D. Frisbie, D. A. da Silva Filho, J.-L. Bredas, P. C. Ewbank, and K. R. Mann, Chem. Mater. **16**, 4436 (2004).

- <sup>11</sup>T. D. Anthopoulos, D. M. de Leeuw, E. Cantatore, P. van't Hof, J. Alma, and J. C. Hummelen, J. Appl. Phys. **98**, 054503 (2005).

- <sup>12</sup>H. E. Katz, A. J. Lovinger, J. Johnson, C. Kloc, T. Siegrist, W. Li, Y.-Y. Lin, and A. Dodabalapur, Nature (London) **404**, 478 (2000).

- <sup>13</sup>B. A. Jones, M. J. Ahrens, M.-H. Yoon, A. Facchetti, T. J. Marks, and M. R. Wasielewski, Angew. Chem., Int. Ed. **43**, 6363 (2004).

- <sup>14</sup>Z. Bao, A. J. Lovinger, and J. Brown, J. Am. Chem. Soc. **120**, 207 (1998).

- <sup>15</sup>T. D. Anthopoulos, F. B. Kooistra, H. J. Wondergem, D. Kronholm, J. C. Hummelen, and D. M. de Leeuw, Adv. Mater. (Weinheim, Ger.) **18**, 1679 (2006).

- <sup>16</sup>T. D. Anthopoulos, S. Setayesh, E. C. P. Smits, M. Cölle, E. Cantatore, B. de Boer, Paul W. M. Blom, and D. M. de Leeuw, Adv. Mater. (Weinheim, Ger.) 18, 1900 (2006).

- <sup>17</sup>Th. B. Singh, N. Marjanovic, G. J. Matt, S. Gunes, N. S. Sariciftci, A. M. Ramil, A. Andreev, H. Sitter, R. Schwodiauer, and S. Bauer, Org. Electron. 6, 105 (2005).

- <sup>18</sup>R. C. Haddon, A. S. Perel, R. C. Morris, T. T. M. Palstra, A. F. Hebard, and R. M. Fleming, Appl. Phys. Lett. **67**, 121 (1995).

- <sup>19</sup>S. Kobayashi, T. Takenobu, S. Mori, A. Fujiwara, and Y. Iwasa, Appl. Phys. Lett. **82**, 4581 (2003).

- <sup>20</sup>K. Horiuchi, K. Nakada, S. Uchino, S. Hashii, A. Hashimoto, N. Aoki, Y. Ochiai, and M. Shimizu, Appl. Phys. Lett. **81**, 1911 (2002).

- <sup>21</sup>B. Crone, A. Dodabalapur, Y.-Y. Lin, R. W. Fillas, Z. Bao, A. LaDuca, R. Sarpeshkar, H. E. Katz, and W. Li, Nature (London) **403**, 521 (2000).

- <sup>22</sup>D. J. Gundlach, K. P. Pernstich, G. Wilckens, M. Grüter, S. Haas, and B. Batlogg, J. Appl. Phys. **98**, 064502 (2005).

- <sup>23</sup>D. Stifter and H. Sitter, Appl. Phys. Lett. **66**, 679 (1995).

- <sup>24</sup>A. Montaigne Ramil, Th. B. Singh, N. T. Haber, N. Marjanovic, S. Gunes, A. Andreev, G. J. Matt, R. Resel, H. Sitter, and S. Sariciftci, J. Cryst. Growth **288**, 123 (2006).

- <sup>25</sup>H. Ohashi, K. Tanigaki, R. Kumashiro, S. Sugihara, S. Hiroshiba, S. Kimura, K. Kato, and M. Takata, Appl. Phys. Lett. **84**, 520 (2004).

- <sup>26</sup>S. M. Sze, *Physics of Semiconductor Devices* (Wiley, New York, 1981).

- <sup>27</sup>T. D. Anthopoulos, C. Tanase, S. Setayesh, E. J. Meijer, J. C. Hummelen, P. W. M. Blom, and D. M. de Leeuw, Adv. Mater. (Weinheim, Ger.) 16, 2174 (2004).

Downloaded 25 Apr 2008 to 155.198.4.89. Redistribution subject to AIP license or copyright; see http://apl.aip.org/apl/copyright.jsp