ISSN 0280-5316 ISRN LUTFD2/TFRT--5907--SE

# Modeling of Avionics Systems using JGrafchart and TrueTime

Anna Benktson Sofia Dahlberg

Lund University Department of Automatic Control November 2012

| Lund University<br>Department of Automatic Control | Document name<br>MASTER THESIS                                                                                         |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Box 118                                            | Date of issue<br>November 2012                                                                                         |

| SE-221 00 Lund Sweden                              | Document Number<br>ISRN LUTFD2/TFRT5907SE                                                                              |

| Author(s)<br>Anna Benktson<br>Sofia Dahlberg       | Supervisor<br>Eelco Scholte, UTC<br>Karl-Erik Årzén, Dept. of Automatic Control, Lund<br>University, Sweden (examiner) |

|                                                    | Sponsoring organization                                                                                                |

#### Title and subtitle

Modeling of Avionics Systems using JGrafchart and TrueTime (Modellering av flygsystem med JGrafchart och TrueTime)

#### Abstract

The first part of the thesis aims to investigate the applicability of JGrafchart and its associated Model of Computation (MoC) for describing sequential control in aircraft primary power distribution systems. The motivation behind this is the need for better modeling tools and in particular support for separation between nominal control and fault handling. Also, as system complexity increases, better structuring capabilities are required. The application for this part of the thesis is a typical primary power distribution system in a medium-sized aircraft, and JGrafchart is used as substitute for Stateflow for the sequential parts of the controller. Simulations were run to determine whether JGrafchart is suitable for these types of systems, and if it provided any additional value compared to Stateflow.

The second part focus around a different tool (TrueTime) to help assess the impact of embedded architecture on control performance. Today it is common for systems to be distributed over multi-tasking kernel nodes, which communicate on different networks. In these systems the nodes compete for the shared resources (The CPU and bandwidth) and the distribution of bandwidth is determined by the network protocol. Since the shared resources are limited in terms of bandwidth different kinds of delays arise, such as transmission delays and back-off times. The delays might lower the control performance significantly, which is why it is important to identify them early in the development process, preferably at the design stage. In the thesis, TrueTime is extended to support Avionics Full Duplex Switched Ehternet (AFDX) and applied to a typical aircraft electric power system.

| Key  | wor   | ds |

|------|-------|----|

| 1.09 | ** 01 | uu |

Classification system and/ or index terms (if any)

Supplementary bibliographical information

| ISSN and key title<br>0280-5316 |                         |                   | ISBN |

|---------------------------------|-------------------------|-------------------|------|

| Language<br>English             | Number of pages<br>1-88 | Recipient's notes |      |

| Security classification         |                         |                   |      |

http://www.control.lth.se/publications/

# Modeling of Avionics Systems using JGrafchart and TrueTime

Anna Benktson and Sofia Dahlberg

December 3, 2012

# Contents

| 1 | $1.1 \\ 1.2 \\ 1.3$                                       | Deduction         Background         Thesis Outline         Related Work         Individual Contributions                                                                                                                                                                | <b>10</b><br>10<br>10<br>11<br>11                                                                                                                                      |

|---|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ι | $\mathbf{Seq}$                                            | quential Control Systems                                                                                                                                                                                                                                                 | 12                                                                                                                                                                     |

| 2 | 2.1                                                       | hary Power Distribution SystemsBackground2.1.1Sources2.1.2Electrical Components2.1.3Control Algorithm                                                                                                                                                                    | <b>14</b><br>14<br>14<br>16<br>16                                                                                                                                      |

| 3 | <ul><li>3.1</li><li>3.2</li><li>3.3</li><li>3.4</li></ul> | lels of Computation for Sequential Control Systems         Finite State Machine                                                                                                                                                                                          | <ol> <li>18</li> <li>18</li> <li>18</li> <li>20</li> <li>20</li> <li>23</li> <li>23</li> <li>23</li> <li>25</li> <li>25</li> <li>25</li> <li>25</li> <li>27</li> </ol> |

|   | 3.5<br>3.6<br>3.7                                         | 3.4.4 History Junction       Grafcet         Grafcet                                                                                                                                                                                                                     | 27<br>27<br>27<br>29<br>29<br>29<br>29<br>30<br>30<br>30<br>30                                                                                                         |

|   |                                                           | 3.7.2       Step       Step       Step         3.7.3       Transition       Step       Step         3.7.4       Macro Step       Step       Step         3.7.5       Exception Transition       Step       Step         3.7.6       Procedure Step       Step       Step | 30<br>31<br>31<br>31<br>33                                                                                                                                             |

|          |                                         | 3.7.7 Process Step $\ldots$                                                                                                                                                                                                                                                                                                         | 33                                                                                                                                                                                 |

|----------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                                         | 3.7.8 Step Fusion Set (SFS) $\ldots$                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                    |

|          | <b>n</b> 0                              | 3.7.9 Object-Oriented Features                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                    |

|          | 3.8                                     | Choosing a Model of Computation                                                                                                                                                                                                                                                                                                                                                                                      | 34                                                                                                                                                                                 |

| 4        | App                                     | plication of JGrafchart                                                                                                                                                                                                                                                                                                                                                                                              | 36                                                                                                                                                                                 |

|          | 4.1                                     | Motivation                                                                                                                                                                                                                                                                                                                                                                                                           | 36                                                                                                                                                                                 |

|          | 4.2                                     | An Existing Control System                                                                                                                                                                                                                                                                                                                                                                                           | 36                                                                                                                                                                                 |

|          |                                         | 4.2.1 Stateflow blocks                                                                                                                                                                                                                                                                                                                                                                                               | 36                                                                                                                                                                                 |

|          |                                         | 4.2.2 Interfaces                                                                                                                                                                                                                                                                                                                                                                                                     | 37                                                                                                                                                                                 |

|          | 4.3                                     | JGrafchart Control System Architecture                                                                                                                                                                                                                                                                                                                                                                               | 37                                                                                                                                                                                 |

|          |                                         | 4.3.1 Sequential Control                                                                                                                                                                                                                                                                                                                                                                                             | 37                                                                                                                                                                                 |

|          |                                         | 4.3.2 Sequential Control Integrated With Fault Handling                                                                                                                                                                                                                                                                                                                                                              | 38                                                                                                                                                                                 |

|          |                                         | 4.3.3 Modifications Made to the JGrafchart Tool During Implementation                                                                                                                                                                                                                                                                                                                                                | 50                                                                                                                                                                                 |

|          | 4.4                                     | Results                                                                                                                                                                                                                                                                                                                                                                                                              | 53                                                                                                                                                                                 |

| <b>5</b> | Cor                                     | nclusion and Future Work                                                                                                                                                                                                                                                                                                                                                                                             | <b>54</b>                                                                                                                                                                          |

|          | 5.1                                     | General Discussion of Results                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                    |

|          | 5.2                                     | Future Work                                                                                                                                                                                                                                                                                                                                                                                                          | 55                                                                                                                                                                                 |

|          |                                         |                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                    |

|          | •                                       |                                                                                                                                                                                                                                                                                                                                                                                                                      | -                                                                                                                                                                                  |

| II       | $\mathbf{N}$                            | Iodeling of IMA Control Systems                                                                                                                                                                                                                                                                                                                                                                                      | 58                                                                                                                                                                                 |

| 11<br>6  |                                         | egrated Modular Avionics                                                                                                                                                                                                                                                                                                                                                                                             | 60                                                                                                                                                                                 |

|          |                                         | egrated Modular Avionics<br>Background and Introduction to IMA                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                    |

|          | Inte                                    | egrated Modular Avionics<br>Background and Introduction to IMA                                                                                                                                                                                                                                                                                                                                                       | <b>60</b><br>60<br>60                                                                                                                                                              |

|          | <b>Inte</b><br>6.1                      | egrated Modular Avionics<br>Background and Introduction to IMA                                                                                                                                                                                                                                                                                                                                                       | <b>60</b><br>60<br>60                                                                                                                                                              |

|          | <b>Inte</b><br>6.1<br>6.2               | egrated Modular Avionics         Background and Introduction to IMA         Theory         6.2.1                                                                                                                                                                                                                                                                                                                     | <b>60</b><br>60<br>60                                                                                                                                                              |

| 6        | <b>Inte</b><br>6.1<br>6.2               | egrated Modular Avionics<br>Background and Introduction to IMA                                                                                                                                                                                                                                                                                                                                                       | <b>60</b><br>60<br>60<br>60                                                                                                                                                        |

| 6        | <b>Inte</b><br>6.1<br>6.2<br><b>Tru</b> | egrated Modular Avionics Background and Introduction to IMA                                                                                                                                                                                                                                                                                                                                                          | <ul> <li>60</li> <li>60</li> <li>60</li> <li>60</li> <li>60</li> <li>64</li> </ul>                                                                                                 |

| 6<br>7   | <b>Inte</b><br>6.1<br>6.2<br><b>Tru</b> | egrated Modular Avionics         Background and Introduction to IMA         Theory         6.2.1         Network Protocols         Network Protocols         Time         7.0.2         TrueTime         Time Model of IMA Use Case                                                                                                                                                                                  | <b>60</b><br>60<br>60<br><b>60</b><br><b>64</b><br>64                                                                                                                              |

| 6<br>7   | Inte<br>6.1<br>6.2<br>Tru<br>Tru        | egrated Modular Avionics         Background and Introduction to IMA         Theory         6.2.1         Network Protocols         neTime         7.0.2         TrueTime         An Existing IMA System                                                                                                                                                                                                              | <ul> <li>60</li> <li>60</li> <li>60</li> <li>60</li> <li>60</li> <li>64</li> <li>64</li> <li>66</li> </ul>                                                                         |

| 6<br>7   | Inte<br>6.1<br>6.2<br>Tru<br>8.1        | egrated Modular Avionics         Background and Introduction to IMA         Theory         6.2.1         Network Protocols         Network Protocols         Time         7.0.2         TrueTime         Time Model of IMA Use Case                                                                                                                                                                                  | <ul> <li>60</li> <li>60</li> <li>60</li> <li>60</li> <li>60</li> <li>64</li> <li>64</li> <li>66</li> <li>66</li> </ul>                                                             |

| 6<br>7   | Inte<br>6.1<br>6.2<br>Tru<br>8.1        | egrated Modular Avionics         Background and Introduction to IMA         Theory         6.2.1         Network Protocols         neTime         7.0.2         TrueTime         An Existing IMA System         System modeled in TrueTime                                                                                                                                                                           | <ul> <li>60</li> <li>60</li> <li>60</li> <li>60</li> <li>60</li> <li>64</li> <li>64</li> <li>66</li> <li>66</li> <li>67</li> </ul>                                                 |

| 6<br>7   | Inte<br>6.1<br>6.2<br>Tru<br>8.1        | egrated Modular Avionics         Background and Introduction to IMA         Theory         Theory         6.2.1         Network Protocols         neTime         7.0.2         TrueTime         An Existing IMA Use Case         An Existing IMA System         System modeled in TrueTime         8.2.1         System Modeled With Full Duplex Switched Ethernet                                                   | <ul> <li>60</li> <li>60</li> <li>60</li> <li>60</li> <li>60</li> <li>64</li> <li>64</li> <li>64</li> <li>66</li> <li>67</li> <li>67</li> </ul>                                     |

| 6<br>7   | Inte<br>6.1<br>6.2<br>Tru<br>8.1<br>8.2 | egrated Modular Avionics         Background and Introduction to IMA         Theory         Theory         6.2.1 Network Protocols         neTime         7.0.2 TrueTime         Time Model of IMA Use Case         An Existing IMA System         System modeled in TrueTime         8.2.1 System Modeled With Full Duplex Switched Ethernet         8.2.2 Implementation of AFDX                                    | <ul> <li>60</li> <li>60</li> <li>60</li> <li>60</li> <li>60</li> <li>64</li> <li>64</li> <li>64</li> <li>66</li> <li>66</li> <li>67</li> <li>67</li> <li>67</li> <li>67</li> </ul> |

| 6<br>7   | Inte<br>6.1<br>6.2<br>Tru<br>8.1<br>8.2 | egrated Modular Avionics         Background and Introduction to IMA         Theory         6.2.1 Network Protocols         6.2.1 Network Protocols         meTime         7.0.2 TrueTime         meTime Model of IMA Use Case         An Existing IMA System         System modeled in TrueTime         8.2.1 System Modeled With Full Duplex Switched Ethernet         8.2.2 Implementation of AFDX         Results | <ul> <li>60</li> <li>60</li> <li>60</li> <li>60</li> <li>60</li> <li>64</li> <li>64</li> <li>66</li> <li>67</li> <li>67</li> <li>67</li> <li>70</li> </ul>                         |

3

# List of Figures

| $2.1 \\ 2.2$ |                                                                                             | .5<br>.6   |

|--------------|---------------------------------------------------------------------------------------------|------------|

| 3.1          |                                                                                             | 9          |

| 3.2          | Mealy machine                                                                               | 9          |

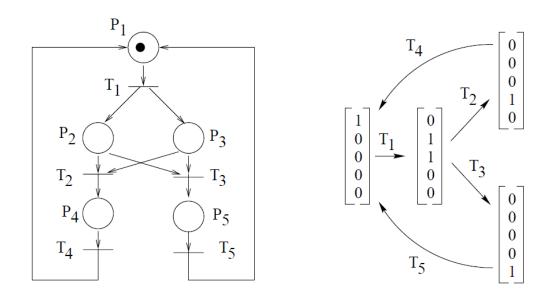

| 3.3          | A simple Petri net                                                                          | 21         |

| 3.4          |                                                                                             | 21         |

| 3.5          | A Petri net with coverability tree (upper) and coverability graph (lower)                   | 22         |

| 3.6          | Trucks and their corresponding Petri nets                                                   | 24         |

| 3.7          |                                                                                             | 24         |

| 3.8          | Stateflow                                                                                   | 26         |

| 3.9          | State machine without connective junction (Left) and state machine with connective junction |            |

|              | (Right)                                                                                     | 27         |

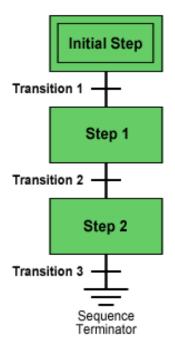

| 3.10         | A Grafcet chart                                                                             | 28         |

| 3.11         | Grafcet Macro Step                                                                          | 29         |

|              |                                                                                             | <b>B</b> 0 |

| 3.13         |                                                                                             | 81         |

| 3.14         | Transition                                                                                  | 81         |

| 3.15         | Macro Step                                                                                  | 32         |

|              |                                                                                             | 32         |

| 3.17         | Procedure step                                                                              | 33         |

|              |                                                                                             | 33         |

| 3.19         | State Machine Before Applying Step Fusion Set                                               | 34         |

|              |                                                                                             | 84         |

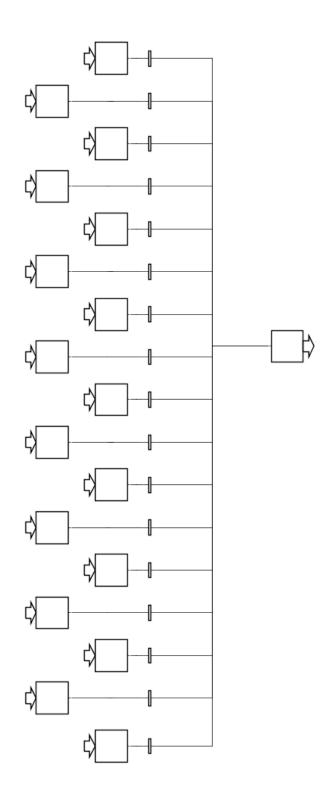

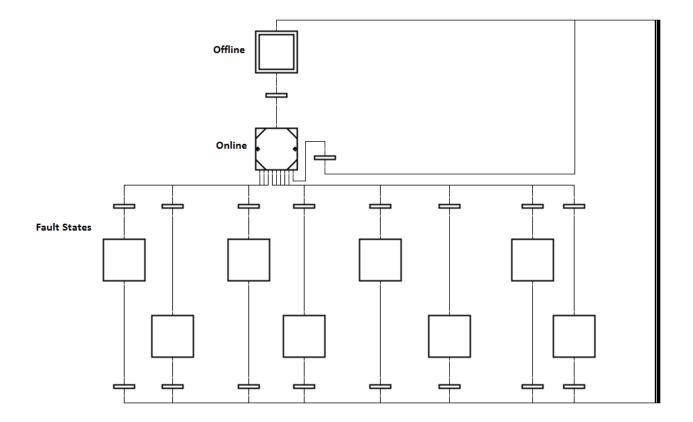

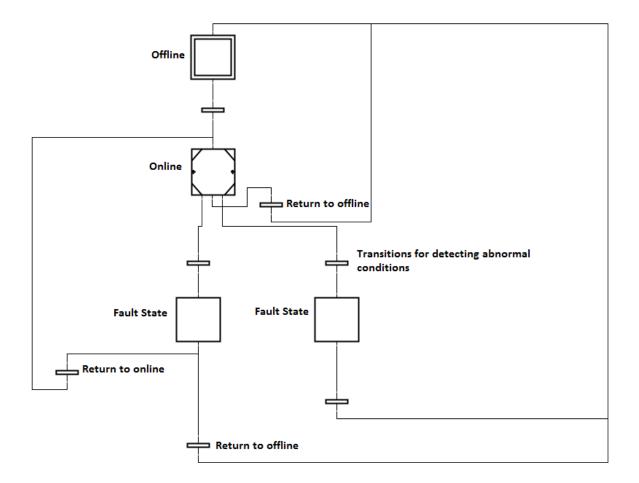

| 4.1          | Request Handler, top layer                                                                  | 39         |

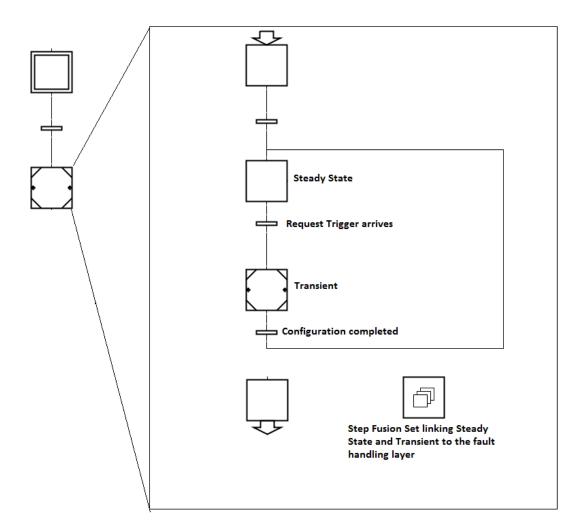

| 4.2          | Request Handler, internal states                                                            | 10         |

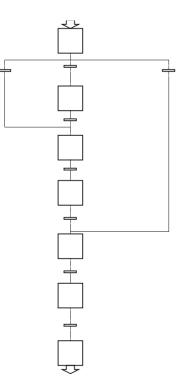

| 4.3          | Configuration of electric system, top layer 4                                               | 1          |

| 4.4          | Configuration of electric system, internal sequence 4                                       | 12         |

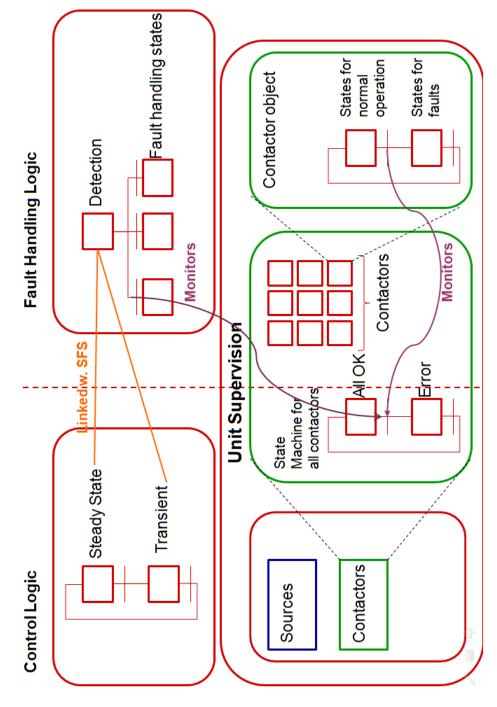

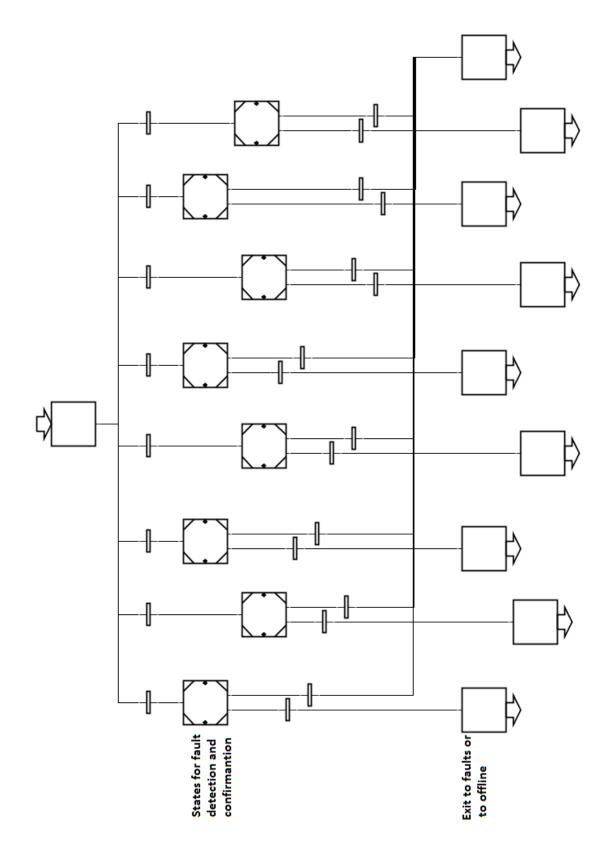

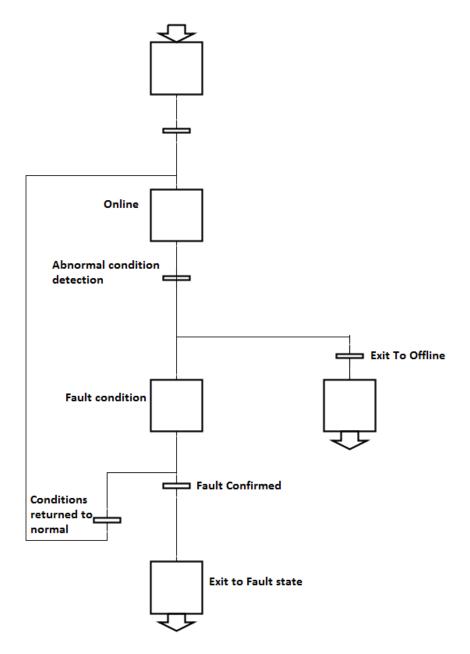

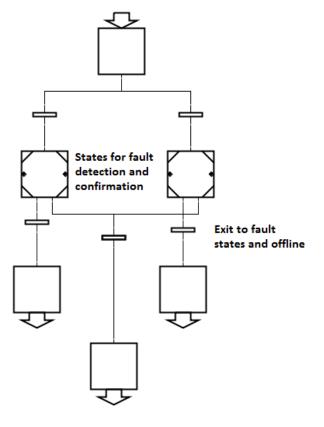

| 4.5          | JGrafchart Design Concept                                                                   | 13         |

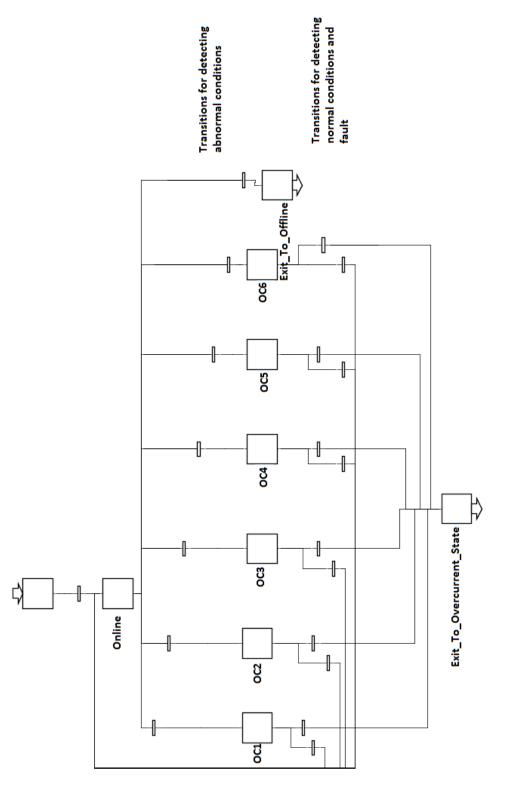

| 4.6          |                                                                                             | 14         |

| 4.7          |                                                                                             | 15         |

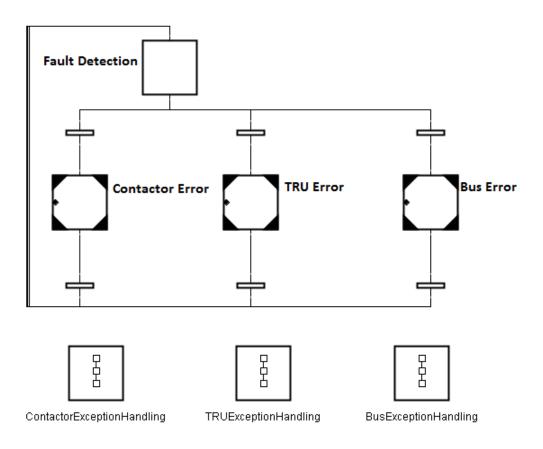

| 4.8          | Generator State Machine, Undervoltage Fault Detection Layer                                 | 16         |

| 4.9          | TRU State Machine, Top Level                                                                | 17         |

| 4.10         |                                                                                             | 18         |

|              |                                                                                             | 19         |

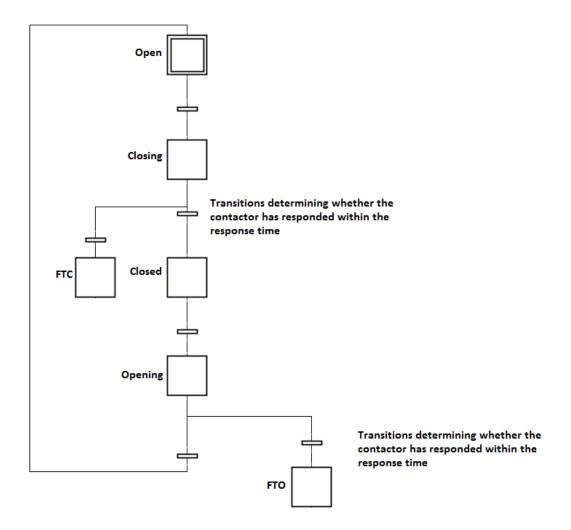

| 4.12         |                                                                                             | 50         |

|              |                                                                                             | 51         |

|              |                                                                                             | 52         |

| 5.1          | Concept Of Object Tokens In JGrafchart                                                      | 56         |

| 7.1          | Aircraft Electric Power System                                                              | 65         |

| 8.1  | Simplified Aircraft Electric Power System                                           | 67 |

|------|-------------------------------------------------------------------------------------|----|

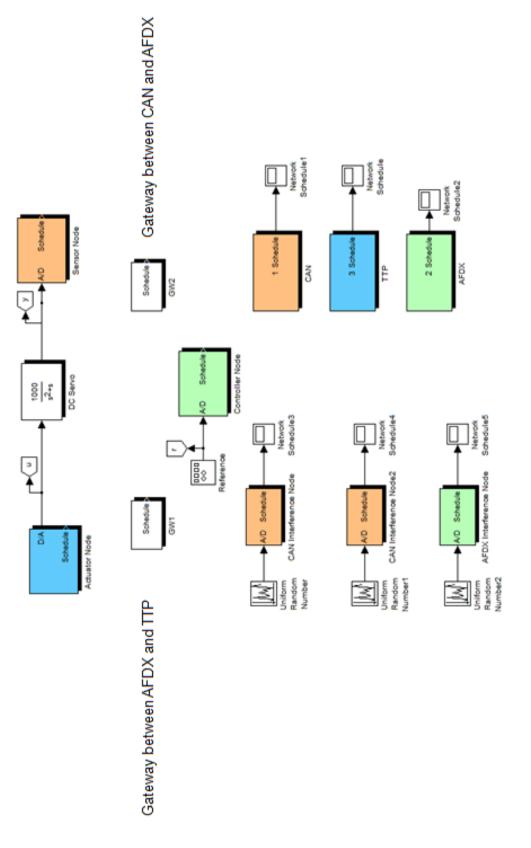

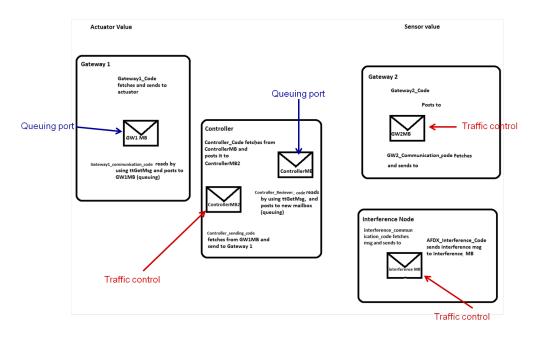

| 8.2  | Simplified Aircraft Electric Power System modeled in TrueTime                       | 68 |

| 8.3  | AFDX in TrueTime                                                                    | 69 |

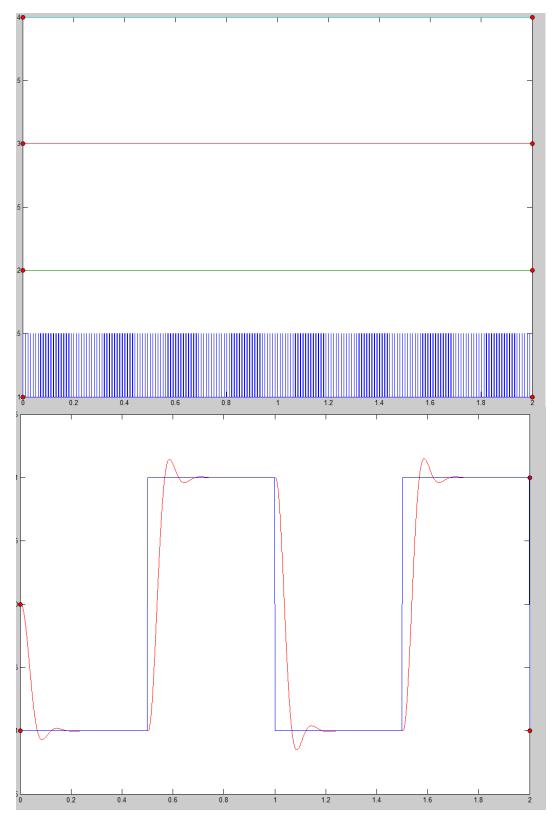

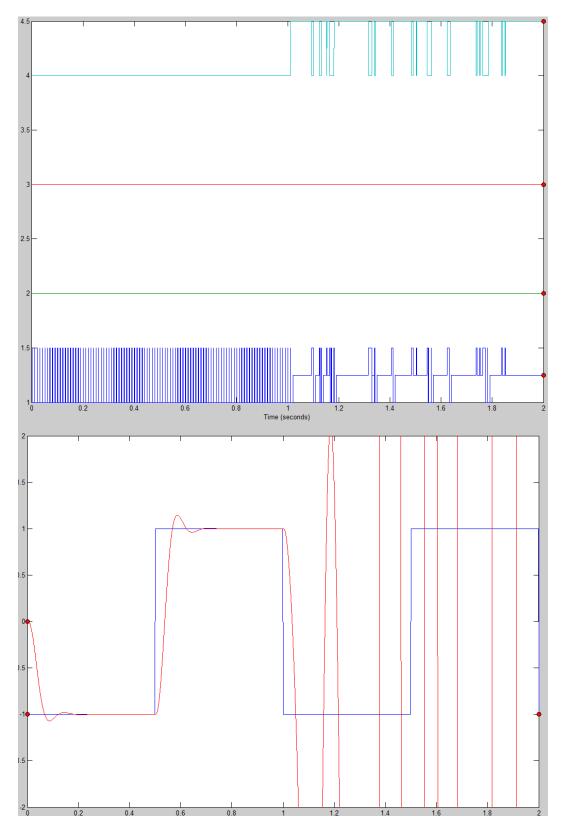

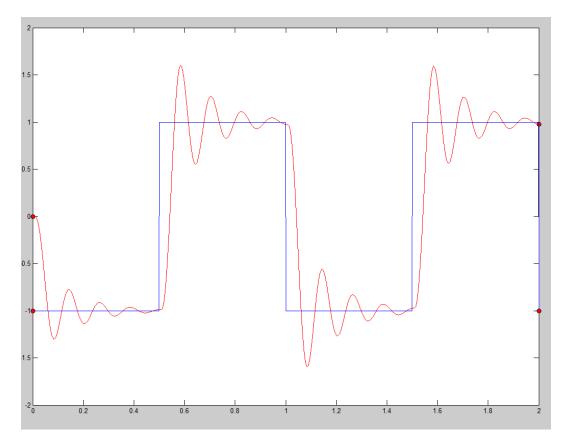

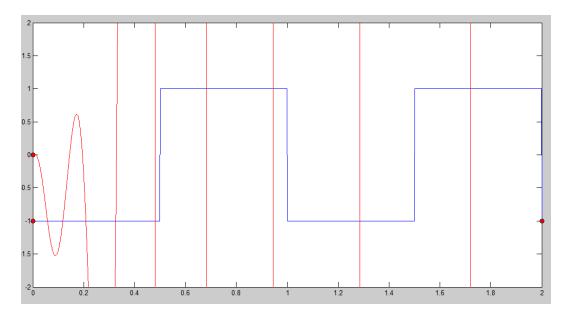

| 8.4  | Network Schedule and Corresponding Control Performance With 0 % Bandwidth Assigned  |    |

|      | To High Priority CAN Interference Node                                              | 71 |

| 8.5  | Network Schedule and Corresponding Control Performance With 5 % Bandwidth Assigned  |    |

|      | To High Priority CAN Interference Node                                              | 72 |

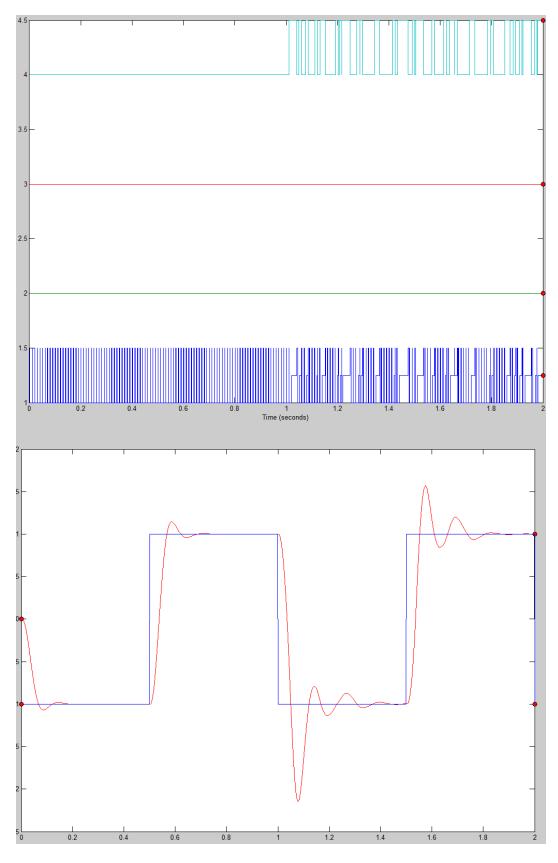

| 8.6  | Network Schedule and Corresponding Control Performance With 10 % Bandwidth Assigned |    |

|      | To High Priority CAN Interference Node                                              | 73 |

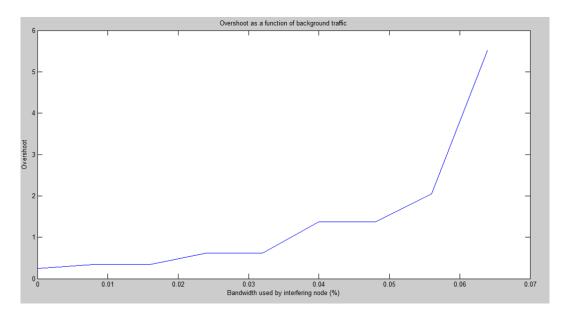

| 8.7  | Overshoot as A Function of Bandwidth Assigned To High Priority CAN Interference     | 74 |

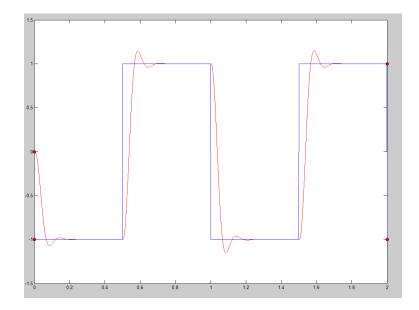

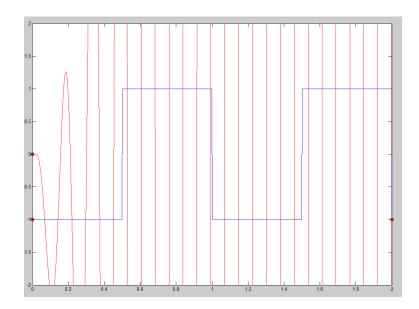

| 8.8  | Control Performance With 1 ms Gateway Delay                                         | 74 |

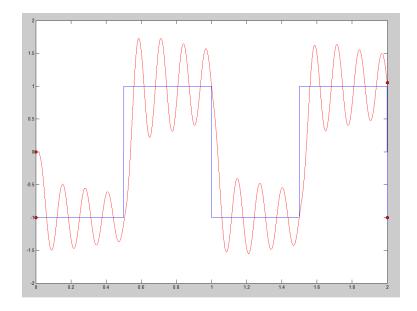

| 8.9  | Control Performance With 5 ms Gateway Delay                                         | 75 |

|      | Control Performance With 10 ms Gateway Delay                                        | 75 |

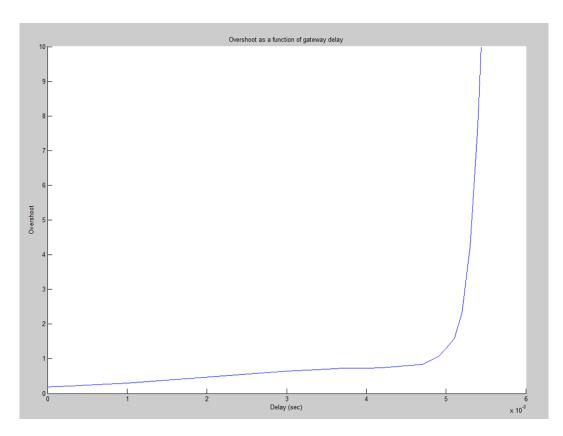

|      | Overshoot as a Function of Gateway Delay                                            | 76 |

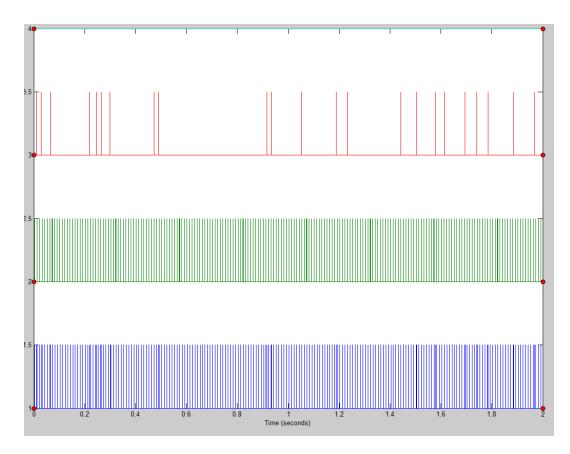

| 8.12 | Node 3 Executing Sporadic Task On Full Duplex Switched Ethernet                     | 77 |

| 8.13 | Node 3 Executing Sporadic Task on AFDX                                              | 78 |

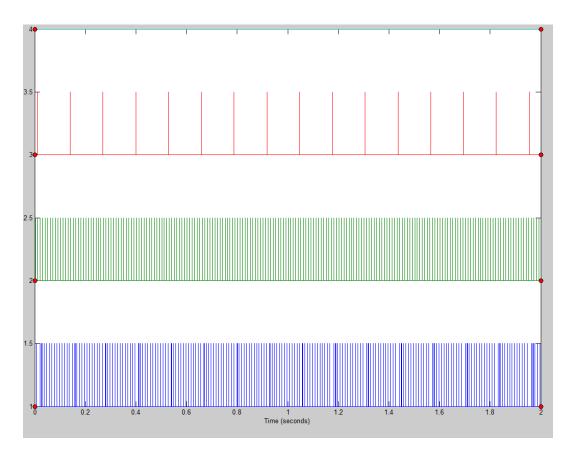

| 8.14 | Control Performance When Controller BAG is Equal to 1 ms                            | 79 |

| 8.15 | Control Performance When Controller BAG is Equal to 10 ms                           | 79 |

# List of Tables

| 4.1 | Components and Examp | les of Respective Faults | s |  |

|-----|----------------------|--------------------------|---|--|

|-----|----------------------|--------------------------|---|--|

# Acronyms

AFDX Avionics Full Duplex Switched Ethernet

CAN Controller Area Network

EPDS Electric Power Distribution System

FSM Finite State Machine

HS Hamilton Sundstrand

IMA Integrated Modular Avionics

MIMO Multiple Input Multiple Output

MOC Model Of Computation

PN Petri Net

PPDS Primary Power Distribution System

SLD Single Line Diagram

SSRPC Solid State Relay Power Contactor

TDMA Time Division Multiple Access

# Chapter 1

# Introduction

### 1.1 Background

Modern aircraft rely on the integration of several systems such as the Electrical System, the Air Management System, Avionics, Vehicle Management and others. Most recent aircraft have seen a drive towards increased integration and more reliance on system control to achieve system functionality. Most control systems are implemented using a combination of hardware and software systems and are designed to work under normal and fault conditions to ensure system performance and availability.

The control system often is distributed across several computational nodes and using communication networks to exchange data in real-time. In the past this was often done using point-to-point communication networks, however recent platforms have started to shift towards high speed bus based architectures. Developing control algorithms for these systems is particularly challenging due to the need for fault handling and degraded performance requirements. It is therefore desirable to have a methodology (and supporting modeling framework) that allows for the designer to approach the design in a modular fashion, rather than a fully integrated approach from the start.

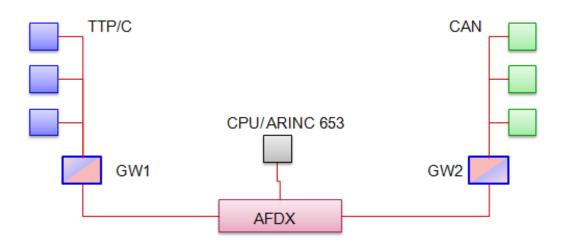

In addition, there is a need to predict the early impact of the embedded architecture on the control performance. The control performance in such Integrated Modular Avionics (IMA) based systems often is impacted by delay and jitter that are introduced by both the computational and communication elements.

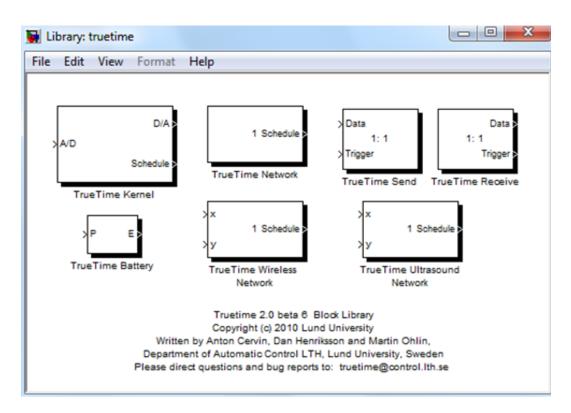

To support both types of analysis, two existing toolsets will be evaluated for the application to current and future aircraft systems. These two toolsets, JGrafchart and TrueTime have been developed at Lund University since 1991 and 1999 respectively.

The thesis has been done at UTC Aerospace Systems (legacy Hamilton Sundstrand) in Windsor Locks (CT, U.S) which is a business division within the United Technologies Corporation (UTC). UTC consists of six business divisions. The aerospace businesses are Sikorsky which is the largest helicopter manufacturer in the world, Pratt & Whitney which develops engines, industrial gas turbines and space propulsion systems and UTC Aerospace systems. UTC Aerospace system is a major supplier to aerospace and defense systems as well as to international space programs. The company is the result of the merging of Hamilton Sundstrand and Goodrich, which was completed in 2012. UTC also has commercial businesses which are Otis elevators and UTC Climate, Controls & Security.

#### **1.2** Thesis Outline

This thesis aims to address two applications of control and analysis tools to support development of aircraft control systems:

- 1. Investigate the applicability of JGrafchart and its associated Model of Computation (MoC) for describing the Primary Power Distribution Control System.

- 2. Extension of the TrueTime toolbox to typical aircraft control systems that employ Integrated Modular Avionics (IMA).

Within the first part a typical Electric Control System that forms the basis for the investigation of using JGrafchart is described. A brief comparison of different Models of Computation (MoC) is detailed in Chapter 3, and the application to Electric Systems is described in Chapter 4. Conclusions and future work for this part is summarized in Chapter 5.

A similar outline is followed for the second part of this thesis. The IMA concept is described in Chapter 6, followed by a description of the TrueTime background in Chapter 7 and a Use Case and the implementation of the necessary extensions in Chapter 8. The thesis is concluded with Chapter 9 for the second part of the thesis.

## 1.3 Related Work

Modeling of avionic systems has grown more difficult as system complexity has increased significantly over the past years. It becomes more and more important to construct models designed for verification, since these systems cannot be analyzed without the use of verification tools. Several large industry and government programs have developed methods for both design and verification of complex aircraft systems. Within the More Open Electrical Technologies (MOET) [1] program new modeling methodologies focused on the feasibility of more electric and integrated aircraft are investigated. In [2] the Modelica language is used as a common language for modeling aircraft systems in the different domains. An example of related work in the area of modeling and verification of avionic systems is provided in [3]. The authors propose an automated procedure for designing control protocols using Linear Temporal Logic to correctly describe the behavior of a system and its environment. The motivation behind this is to make the model amenable to formal analysis and create a hierarchical control structure.

## 1.4 Individual Contributions

The work behind this thesis has been done in close collaboration between the authors, and both have been working with both parts. However, Sofia had the main responsibility for the JGrafchart part whereas Anna had the main responsibility for the TrueTime part. Since the scope of the JGrafchart part exceeds the scope of the TrueTime part, Anna has also been responsible for the work done in Section 4.4.1.

# Part I

# Sequential Control Systems

# Chapter 2

# **Primary Power Distribution Systems**

### 2.1 Background

In today's aircraft powering is done dynamically by the Electric Power Distribution Systems (EPDS). Depending on which state the aircraft is in (take-off, landing etc) the routing will change accordingly by enabling/disabling a set of switches. In the physical system redundant paths are available for the controller to choose from. The controller has to choose a path and sequentialize the switches in a safe way, for example, it has to guarantee no electric power loss in the system. To describe the behavior of the sequentialized systems, different Models of Computation can be used [5]. Among them are Finite State Machines (FSM) and Petri Nets (PN), both of which have been used at Hamilton Sundstrand (HS) in the past for analysis purposes. The main objective of this part of the thesis is to model a PPDS control system in Simulink/JGrafchart and evaluate the expressiveness of the language, primarily to support fault handling.

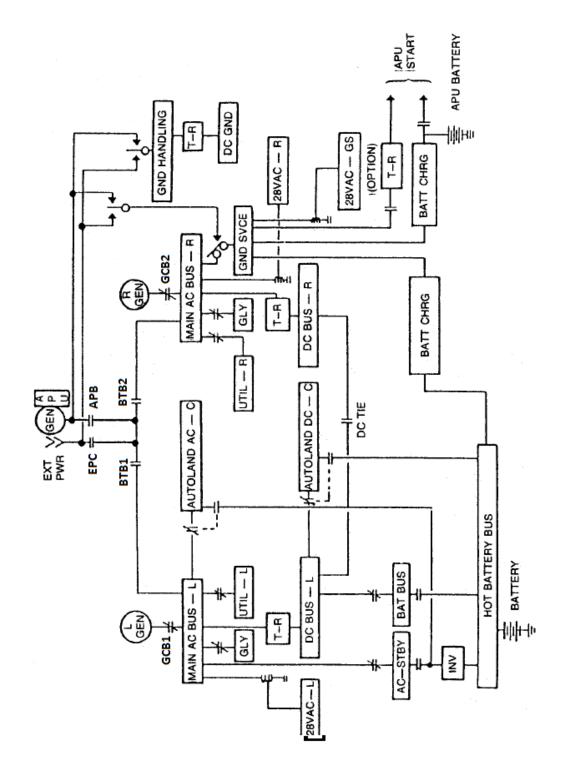

An Electric Power Distribution Systems (EPDS) is divided into Power generation, Protections and Primary and Secondary power distribution, PPDS and SPDS respectively. The PPDS is responsible for protections, input/output processing and supplying electric power to loads. The topology is shown in the single line diagram (SLD), which can be seen in Figure 2.1.

The electric system consists of two sides, the left side and the right side. AC power is generated on each side to power the AC loads. The AC power is converted to DC power to power the DC loads. The reason for using AC power is that it works at a higher voltage, which corresponds to a lower current. A low current is preferred since it reduces losses such as power losses (proportional to current squared) as well as lowers the weight since current conductors are heavy. As an added safety measure there is an independent system in the middle, which in case of major failure provides power to the most critical loads in the system.

Listed below is a description of all sources and components shown in the SLD.

#### 2.1.1 Sources

**Left/Right Generator** Since safety requirements on aircraft systems are rigid, redundancy in avionics systems is necessary to guarantee sufficient power supply. Therefore, two main generators are placed on each side of the aircraft. Under normal circumstances the generators power one side each, but depending on source availability one generator could power the entire system by itself. The generators are connected to two different main AC buses, from which power is distributed to the rest of the system [5].

Auxiliary Power Unit (APU) The APU is a gas turbine which primary function is to start the main engines. In case both the left and right generator break, the APU can be used to provide backup electricity to the system [5].

**External Power (EP)** As the name suggest, EP means providing the system with electricity from an external source. The difference between EP and the other sources is that EP can only be used while the airplane is on ground since electricity is supplied through a ground cart [5].

Figure 2.1: Typical Single Line Diagram

| Priority | Path             | Source          |

|----------|------------------|-----------------|

| 1        | GCB1             | Left Generator  |

| 2        | BTB1, APB        | APU             |

| 3        | GCB2, BTB1, BTB2 | Right Generator |

| 4        | UNPOWERED        |                 |

Figure 2.2: Priority Table

**Ram Air Turbine (RAT)** As one of the final protections the RAT exists to prevent power outage in the system and provide power to the hydraulics and electrical system. The RAT is used when most of all other power sources has broken down or are unavailable. It is an air-driven turbine connected to a small emergency generator. For a short period of time, the RAT is able to provide power to the most critical parts of the system and the most important flight instruments [5].

**Batteries** The batteries provide storage for electric power independent of the generators. They are used in system startup or emergency situations. In case of emergency, they supply short term powering (up to 30 minutes) while other sources are being prepared to take over [5].

#### 2.1.2 Electrical Components

**Transformer Rectifier Unit (TRU)** A TRU is a conversion unit which transforms AC power to DC power [5].

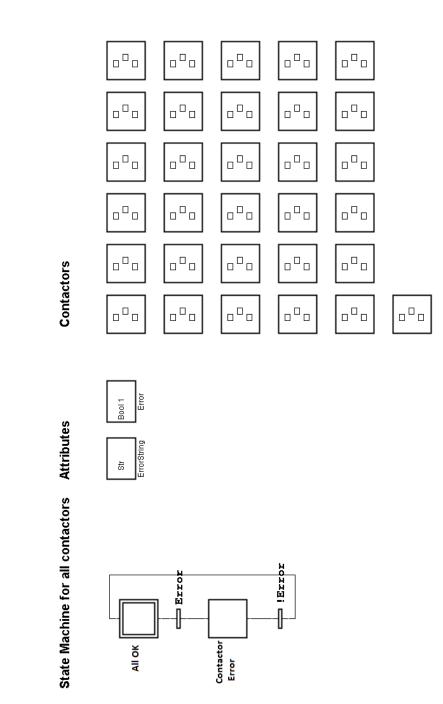

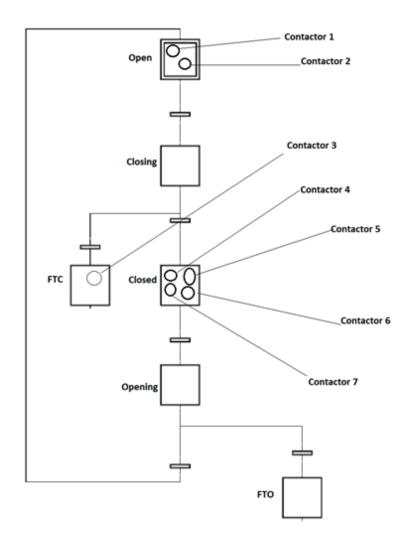

**Contactors** Contactors are devices that can be either open or closed. The state of the contactor indicates whether electric power may pass through it or not. The configuration of the contactors determines the routing of electric power in the system. A contactor has several failure modes, two of them are the Failed To Close (FTC) and Failed To Open (FTO) state. A contactor is determined to be in failure mode if it does not respond to a command within a certain amount of time [5].

**Buses** The electrical buses distribute power to the loads in the system [5].

### 2.1.3 Control Algorithm

The controller is responsible for the routing of electric power to the buses by opening and closing contactors. In the system, there are redundant paths for the controller to choose from. The set of paths are listed in priority tables and are ranked by optimality. Based on priority tables and available sources and contactors, the controller determines from which source the bus will be powered.

In Figure 2.2, an example priority table for the left AC bus is shown. The first row corresponds to the most optimal power configuration for powering left AC bus. However, if GCB1 or Left generator are not available, the controller chooses the second row which is the second most optimal configuration. The control algorithm continues in this way until a valid configuration is found or all redundant paths are exhausted. The second column indicates which contactors need to be closed in order for the source to power the bus.

# Chapter 3

# Models of Computation for Sequential Control Systems

A model of computation is a formal, abstract description of a system and its behavior, showing how the pieces in it relate to each other. The gain of describing a system formally is that it can then be transformed into an analyzable format which makes it amenable to analysis using standard methods. The sections in this chapter describe different MoCs and modeling tool for sequential logic.

### 3.1 Finite State Machine

A finite state machine is a mathematical model used to describe an event-driven system. It consists of a finite number of states and a set of triggering conditions which cause the system to change state. The triggering conditions are called events. A finite state machine is often summarized in a transition table, which specifies the input and output for each transition. The output from a FSM may differ depending on what type of FSM is used, a Moore machine or a Mealy machine. These are described in short below [6].

#### 3.1.1 Moore Machine

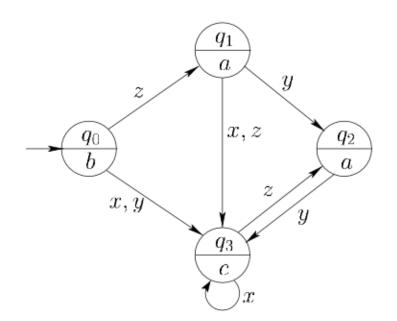

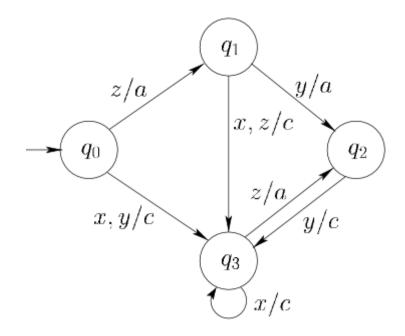

The output from a Moore Finite State Machine is only dependent on the state, not on the input. The actions are executed from inside a state. The advantage of the Moore machine is that its behavior is simple, but on the other hand the number of states are often larger [7]. In Figure 3.1, a Moore machine is displayed. The state machine has four states q0, q1, q2, q3 with actions a, b, c. The states are connected with transitions with conditions (events) x, y, z.

#### 3.1.2 Mealy Machine

A Mealy machine calculates its output based on both state and input. All actions are tied to transitions. This tends to require less states, but also leads to a more complicated output logic than a corresponding Moore Machine [7]. A Mealy machine is depicted in Figure 3.2. It has the same states, actions and transitions as for Figure 3.1 (The Moore machine). The only difference is that the actions are performed when a transition fires, and not from within a state.

Figure 3.1: Moore machine

Figure 3.2: Mealy machine

### 3.2 Petri Net

#### 3.2.1 Background

A Petri net is a mathematical and graphical modeling tool which can be used to model systems of concurrent, sequential, asynchronous, distributed, nondeterministic and/or stochastic character [9].

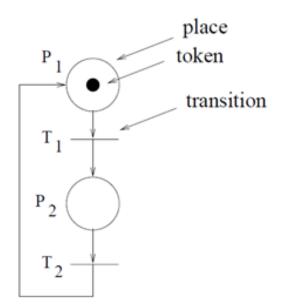

A Petri net is a bipartite directed graph, made up by three main components; places, transitions and arcs. A Bipartite graph is a graph where the nodes (places and transitions for this case) can be divided into two separate subsets such that each arc connects a node from one subset to a node in the other subset. If the arcs are directed it is called a bipartite directed graph [10].

The places, transitions and arcs, together with tokens, are used to simulate the flow of activities in the system. In the graph, places and transitions are called nodes which are connected with edges (arcs). An arc can only connect nodes of different types, i.e. a place with a transition or vice versa. Arcs are marked with a positive integer k which is called the weight of the arc. A k-weighted arc can transfer k tokens, and places can carry multiple tokens [9]. The flow is generated when a transition fires and tokens move from one place to another. A transition is enabled if all its input places carry at least as many tokens as the weight of the arc from the place to the transition. For a transition to fire, it first has to be enabled. When enabled, it may fire but does not have to. Both autonomous(untimed) and non-autonomous (timed) Petri nets exist. In the non-autonomous Petri net a condition from an external event and/or time may be assigned to the firing of a transition, when this condition becomes true the transition fires [11]. The tokens are removed from every input arc and added to every output arc when a transition fires [12].

In the informal definition the components of a Petri net are named as follows:

- *P* is the set of all places.

- T is the set of all transitions.

- *M* is the marking of the net.

- $M(P_i)$  or  $m_i$  is the number of tokens contained in one place

Each marking M is represented by a column vector with a row for each place. The element in the p:th row in the vector denotes the number of tokens in place p. With this said, the marking shows the state of the system [11]. When transitions fire the token distribution, also called the marking M, in the net is altered. A sequence of firing will cause a sequence of markings [9].

**Analyzability** Petri nets are of major use for analysis of concurrent systems, that is, to find out if different properties of the Petri net hold. There exist different types of analyzing methods which apply to Petri nets, where the main methods are reachability- and coverability graphs, linear algebra methods and reduction methods, which will be described in the following sections [11].

**Reachability** Reachability is used to examine the dynamical properties of a system. Mainly this is done by drawing a reachability graph. The graph can be used to see whether a given marking  $M_n$  can be reached from a different marking  $M_0$  by a sequence of firings which transforms  $M_0$  into  $M_n$ , if this holds  $M_n$  is said to be reachable from  $M_0$ . In the reachability graph (Figure 3.4) one is able to see in how many different ways this can be done [9].

**Boundedness** A Petri net is said to be bounded if the number of tokens in each place is less than a nonnegative number k for any marking reachable from a certain marking [9].

**Coverability** If the Petri net that is to be analyzed is unbounded the reachability graph becomes undefined and a coverability graph is used instead. This graph is obtained from the reachability graph by marking the places which carry an infinite number of tokens by  $\omega$  and then merging the nodes that correspond to the same marking, see Figure 3.2.1 [11].

**Deadlocks** A deadlock occurs if a marking is reached where no transitions are enabled [11].

Figure 3.3: A simple Petri net

Figure 3.4: A Petri net with corresponding reachability graph

Figure 3.5: A Petri net with coverability tree (upper) and coverability graph (lower)

**Linear algebra** The properties of a Petri net can be determined by the use of mathematical methods in order to find out about the invariants of the net. If no deadlocks exist there will be an infinite number of firings, however this is most often not the case, all markings cannot be reached and not all sequences of firing can be done. This kind of restrictions is represented by the invariants of the net[11].

**Reduction methods** The reachability and coverability graphs are good analysis methods for small Petri nets, however they are not applicable to large systems. Therefore system models are often reduced to simpler ones. There exist a lot of techniques which reduce large Petri nets into smaller ones without altering the properties of the original net[11].

## 3.3 Different types of Petri nets

There exist both Petri nets and high-level Petri nets. The main and more informal difference between the two is that in the high-level Petri net different tokens can be distinguished and calculated with, which they cannot be in Petri nets. The following two paragraphs give an overview of two important high-level Petri nets; the colored Petri net and the object Petri net.

### 3.3.1 Colored Petri nets

The colored Petri net is a high-level petri net developed during the 1980s. The main idea is to assign each token a color, which serves as an identifier for that token. Any Petri net can be transformed into a colored Petri net, an action which makes them more compact in structure and easier to read and comprehend.

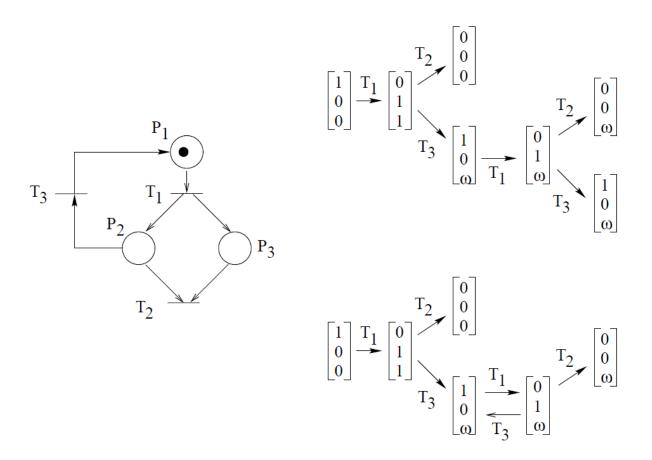

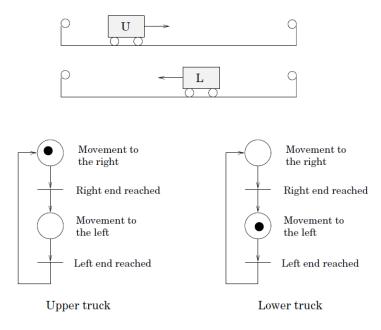

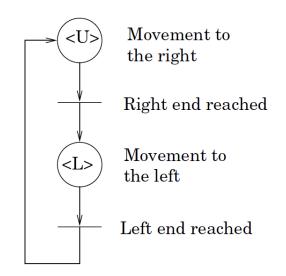

A simple example can be used to illustrate the benefits with colored Petri nets. Figure 3.6 describes two systems that are identical, except for the direction in which the trucks are moving, and their corresponding Petri nets. In this arrangement the system is modeled with separate nets each containing one token. The system could also be modeled with a colored Petri net. The Petri net would have two tokens whose label (or color) would mark the direction, see Fig 3.7. It is possible to transform a colored Petri net into a standard Petri net. This allows for analysis using the standard methods[11].

#### 3.3.2 Object Petri nets

The concept of object Petri nets are inspired by high-level object-oriented programming languages, although only two classes exist; one for tokens and one for modules/subnets. The main idea is to give the token itself a Petri net structure which results in a net within a net structure. The layered approach is better suited for modeling of real system since they are not often "flat", but have internal structures that are of interest for the modeler[13].

Figure 3.6: Trucks and their corresponding Petri nets

Figure 3.7: Two identical systems modeled with a colored Petri net

#### 3.4 Stateflow

Stateflow is an extension of Simulink, which supports sequential control through the use of flow diagrams and state charts. In Stateflow it is possible to have both Moore and Mealy FSM, which in combination with its integration with Simulink and Matlab makes it a powerful tool for modeling of sequential control applications. Stateflow also has built-in C-code generation.

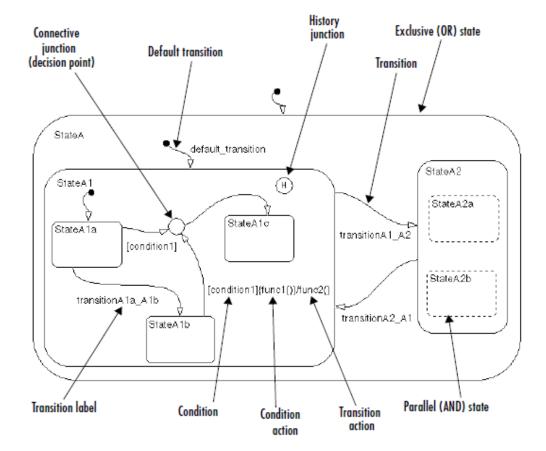

Stateflow is made up by a set of graphical components which are shown in Figure 3.8 and described in short in the following sections.

#### 3.4.1 State

As the name suggest, a Stateflow state models a state and is graphically represented as a rectangle. The current state is marked with a thicker border which implies that the state is active. Stateflow supports two types of states, exclusive (OR) states and parallel (AND) states. Exclusive states are used to represent states that are mutually exclusive, which can be seen in Figure 3.8. *StateA1a*, *StateA1b* and *StateA1c* are exclusive, which implies that the system cannot be in more than one of them at a time. Exclusive states are marked with a solid border line. The parallel state, on the other hand, is used to model system behavior where the system can be in multiple states at the same time. Parallel states are marked with a dashed line and can be seen in the picture as *StateA2a* and *StateA2b*. As a structuring mechanism, states can have internal states. A state which contains other states is called a superstate, and the inner states are called substates [8]. Superstates and substates can be seen in Figure 3.8, where for example *StateA1* is superstate to *StateA1a*, *StateA1b* and *StateA1c* as well as a substate to *StateA*.

For each state, it is possible to specify actions. There are different types of actions and the type determines when the action will be executed. The types are; entry actions, during actions, exit actions, on event\_name actions and bind actions. Entry and exit actions are executed once when a state is entered or exited respectively. During actions are executed periodically while the state is active. On event\_name actions are bound to an event in the system and are performed when the active state receives that event, that is, events occurring in the system can trigger events in states. Bind actions ties data and events to the state where it is declared, meaning only that state and its substates are allowed to change the tied data and broadcast the events. Other states can only read the data and listen to the events[8].

#### 3.4.2 Transition

Transitions mark the changing of state in the system. They are directed arcs that link one state to another. It is possible to prioritize transitions, meaning that if a state has more than one transition connected and two or more of them become true simultaneously, the one with the highest priority will fire. To mark where execution starts, default transitions exist. They can be connected to states and connective junctions. If connected to a state, they have no source state, only a destination state. The default transition is shown in Figure 3.8.

Transitions are defined by a label with the following syntax *event*[condition]conditionaction/transitionaction. Thus, a transition label is made up of four parts, each of which is optional.

**Event** The event part refers to a specified event in the system. If this event occurs and the condition, if any, is true the transition is taken. If no event is specified, the transition will be taken at any event.

**Condition** Conditions are simply boolean expressions which must be true in order for a transition to be taken. If both event and condition are specified, the condition must be true and the event must occur simultaneously for the transition to be valid.

**Condition Action** Condition actions are performed immediately if the condition is true. In absence of a condition, it will be assumed to be true (Implied condition). A condition action is performed before knowing whether the destination state is valid or not. A destination is valid if the preceding state is active and the transition connecting them is true.

Figure 3.8: Stateflow

Figure 3.9: State machine without connective junction (Left) and state machine with connective junction (Right)

**Transition Action** The difference between a condition action and a transition action is that a transition action is not executed before the destination state is proven to be valid [8].

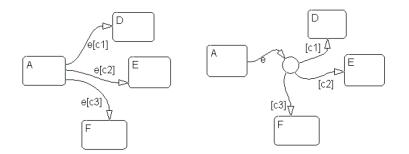

#### 3.4.3 Connective Junction

A connective junction is a way of representing multiple transition paths originating from a single transition, i.e. a source state can have several destination states even though it only has one outgoing transition. In Figure 3.9 the concept of the connective junction can be seen. The two state machines are equivalent, but the state machine on the right hand side uses a connective junction instead of having three outgoing transitions. Upon the occurrence of event e, the state machine moves to the connective junction and evaluates the conditions c1, c2 and c3. If none of them are true, state A continues to be active[8].

#### 3.4.4 History Junction

A history junction is used in a superstate to remember which substate was last active. When exiting the superstate, the history port registers the currently active substate and once it becomes active again, execution is resumed from that substate[8].

## 3.5 Grafcet

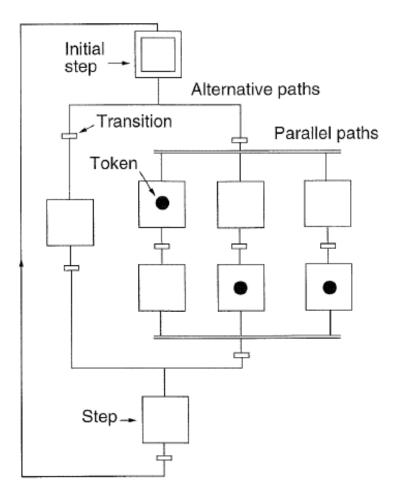

Originally developed in France 1977, Grafcet is a formal method for graphically describing logical controllers as state machines. Grafcet is based on Petri Nets and supports both Moore and Mealy state machines[14]. Figure 3.10 shows a simple Grafcet application. The components are described in short below.

#### 3.5.1 Step

The states in Grafcet are called steps and are drawn as squares. A step can be either active or inactive depending on whether there is a token present or not. Initial steps are a special kind of step which are activated when execution starts, and are graphically represented as a double square.

It is possible to tie actions to a step, which are executed when the step is active. The actions can be one of two types, level actions or impulse actions. Level actions are continuous actions which are performed while the step they are tied to is active. A level action can be either conditional or unconditional. Impulse actions are executed immediately when the step becomes active, and are only performed once[11].

#### 3.5.2 Transition

Transitions are represented as horizontal bars and connect steps. When the step(s) preceding the transition is/are active, the transition is said to be enabled. To a transition, a condition, an event or both can be tied. When an enabled transition becomes enabled, it is also fireable. It will fire instantly and tokens are moved

Figure 3.10: A Grafcet chart

Figure 3.11: Grafcet Macro Step

to the succeeding step(s). In Grafcet, there is no support for prioritizing transitions. If a step has more than one outgoing transition and several of them are fireable at the same time, all fireable transitions will fire simultaneously. If, when a step is entered, its outgoing transition fires immediately the situation is said to be unstable. In this case, only the impulse actions are performed[11].

### 3.5.3 Branching

In Grafcet, both alternative and parallel branches can be used. If an ingoing transition which connects more than one step through the use of a parallel path fires, all steps succeeding it will become active. Furthermore, for outgoing transitions connected to more than one preceding step, all steps preceding the transition must be active for the transition to enable[11]. The concept of branching is visualized in Figure 3.10.

### 3.5.4 Macro Step

Macro steps is a way of structuring large applications in Grafcet. A macro step contains an internal sequence of steps and has one input and one output step. The transition following the macro step is not enabled until the output step is reached[11]. The macro step architecture can be seen in Figure 3.11.

## 3.6 Sequential Function Charts

Sequential Function Charts (SFC) is a programming language used to graphically model sequential systems and is standardized in IEC 61131-3. The language was derived from, and is essentially the same as, Grafcet. The Grafcet/SFC standard is well accepted in the industry due to its graphical interface. SFC consists of steps connected to transitions via directed arcs. It is possible to tie three types of actions to steps, set actions, reset actions and continuous actions. A continuous action is executed periodically while the step is active. A step becomes active if the transition(s) connected to it is/are fireable, i.e. its/their condition(s) is/are true, and the preceding step(s) is/are active [11]. A simple SFC example is shown in Figure 3.12.

Figure 3.12: Sequential Function Chart example

### 3.7 JGrafchart

#### 3.7.1 Background

Grafchart is a mathematical modeling tool based on Grafcet/SFC and Petri nets. It also features concepts from object-oriented programming languages. The aim of Grafchart is to provide a high-level language for control applications.

Originally there existed two versions of Grafchart, one low level version derived from Grafcet, as well as a high level version which resembles colored Petri nets. When the implementation platform was switched from G2 to Java, only support for the low level version was implemented. This version was called JGrafchart and is the version that is currently in use. This means that JGrafchart runs on every platform supporting Java. One feature of JGrafchart is the ability to create extensive graphical user interfaces, including for example animated icons, plotters and message browsers [15]. JGrafchart features several graphical elements which together form the system one wish to model. These components are briefly described in the following paragraphs.

#### 3.7.2 Step

A step represents one of the states in the system. It is possible to tie actions to a step, which will be executed when the step is active, i.e. when it contains a token. The actions can be one out of four types; initially, finally, always or abortive. Final and initial actions are performed only once when a step is entered or exited respectively. Always actions are executed periodically while the step is active. Abortive actions are executed once when an exception transition fires.

In order to find out for how long a step has been active, two methods exist. The call syntax is either  $\langle step - name \rangle .s$ , which returns the number of seconds the step has been active, or  $\langle step - name \rangle .t$ , which returns the number of periods. Periods in JGrafchart are called Scan Cycles and can be set manually for each chart.

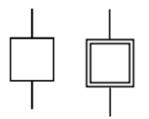

Figure 3.13: Step and initial step

Figure 3.14: Transition

To mark where execution starts, initial steps are used. These are marked graphically by a double square, see Figure 3.13[15].

#### 3.7.3 Transition

A transition models the changing of system state. They are controlled by Boolean expressions and are enabled once the expression becomes true. If there are tokens in the preceding step(s) connected to the transition and the transition is enabled, it will fire and tokens will move to the succeeding step(s)[15]. If a step has more than one outgoing transition, it is possible to prioritize them. Consequently, if several of the outgoing transitions are fireable at the same time, only the transition with the highest priority will fire. Priorities range from one, which corresponds to the highest priority, and up. If no priority is set, the transition automatically receives the lowest priority.

The JGrafchart transition can be seen in Figure 3.14.

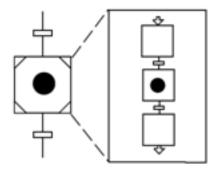

#### 3.7.4 Macro Step

A macro step is used to mark an internal sequence of steps and transitions. The macro step architecture provides the option of having a layered structure, which enhances readability of the model. It is possible to have multiple entries and exits to and from a macro step. In addition to steps and transitions, the body of the macro step also contains enter and exit steps. The number of enter and exit steps are equal to the number of transitions connected to the macro step, meaning that each transition corresponds to a certain enter or exit step. The transition(s) following the macro step cannot fire until its exit step is active.

The macro step has two additional ports, the exception transition port and the history port. The exception port has priority over the transitions in the body and aborts the macro step execution if it becomes true. The history port makes it possible to continue to execute from the state the system was in before abortion[15].

The macro step architecture is shown in Figure 3.15.

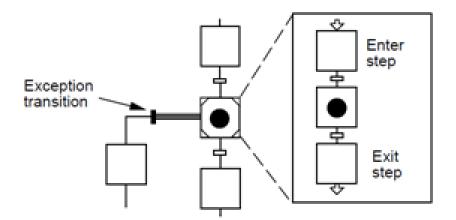

#### 3.7.5 Exception Transition

The exception transition is a high priority transition which can only be connected to a macro step or procedure step. It is only active during the execution of the step it is connected to. If the exception condition becomes true, the transition fires and forces abortion of the current step. It is possible to add abortive actions that should be executed in case of exception[17]. The exception transition is depicted in Figure 3.16.

Figure 3.15: Macro Step

Figure 3.16: Exception transition

Figure 3.17: Procedure step

Figure 3.18: Process step

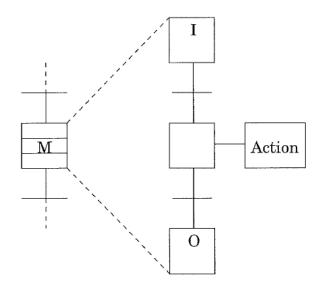

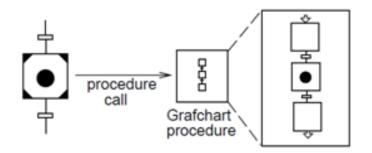

### 3.7.6 Procedure Step

If the same sequence of steps and transitions are repeated in the model, they can be extracted to a procedure. Procedures in JGrafchart are similar to methods in object-oriented programming. When a procedure step is entered, it calls a certain procedure. Similar to the macro step, procedures start with an enter step and end with an exit step. However, the procedure step does not allow multiple entries and exits. It is also possible to connect an exception transition to a procedure, but there is no history port. The transition following a procedure will not enable until the exit step is reached[15].

It is possible to pass values to and from a procedure. Parameters are assigned values either by call by value or call by reference, for which the syntax is V < internalvariable >=< expression > and R < internalvariable >=< variable > respectively[15]. The procedure step and its internal structure (body) can be seen in Figure 3.17.

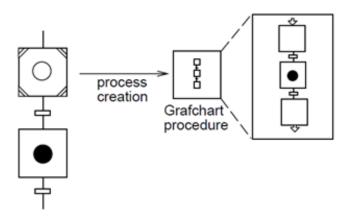

### 3.7.7 Process Step

The process step is basically a procedure step except that the procedure is started in a separate execution thread, meaning that the transition following the process step may fire even if the process step has not reached its exit step[15]. The process step is shown in Figure 3.18.

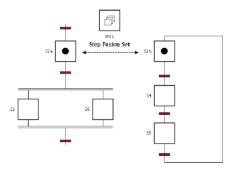

### 3.7.8 Step Fusion Set (SFS)

The step fusion set is a way of representing different views of the same step. This means that if several steps are linked by a step fusion set, whenever one of them becomes active, the other ones activate as well. Step fusion sets can be either abortive or non-abortive. In an abortive step fusion set, for the transition connected

Figure 3.19: State Machine Before Applying Step Fusion Set

Figure 3.20: State Machine After Applying Step Fusion Set

to the output of the step fusion set to fire, it is only required that one of the views is in its last step. When an abortive step fusion set is exited, abortive actions, if any, are executed in the views that did not reach their last step. Non-abortive fusion sets however, require all of the views to have reached their last step before the transition connected to the output may fire [16]. The concept of the step fusion set is shown in Figures 3.19 and 3.20. In Figure 3.19, the state S2 is connected to states S3, S6 via one transition and to state S4 via a different transition. However, in Figure 3.20 state S2 is divided into S2a and S2b, where state S2a is connected to S3 and S6 and state S2b is connected to S4. In that way, S2a and S2b represents the two views of the same state S2, and the state machine in Figure 3.19 has been separated into two different state machines in Figure 3.20. However, the two figures are equivalent in terms of functionality.

### 3.7.9 Object-Oriented Features

As mentioned, JGrafchart resembles object-oriented programming languages in the sense that objects and methods can be modeled. To represent objects, the workspace component can be used. A workspace contains a subworkspace and can be used in different ways, e.g. as a way to structure large JGrafchart applications or to model objects. If a workspace is used to model objects, its subworkspace contains only attributes represented as JGrafchart variables and methods represented as JGrafchart procedures.

However, the object-orientation in JGrafchart is limited since there is no support for classes, inheritance etc[15].

## 3.8 Choosing a Model of Computation

In the previous section, several MoCs and tools suitable for sequential control systems have been presented. When choosing a MoC, its applicability to the domain as well as its formality have to be taken into account. For example, the Finite State Machine is very good for sequential logic, but not very expressive and the number of states grow large even for trivial systems. The structuring capabilities in JGrafchart, where each state recursively can contain a whole state machine, together with the object oriented concepts and the fact that it is transformable to a Petri net and can therefore be analyzed using standard methods makes it an interesting tool to investigate.

# **Application of JGrafchart**

### 4.1 Motivation

One of the main reasons for giving a system a model-based design is to increase traceability and analyzability. JGrafchart combines ideas from Finite State Machines and object-oriented programming languages to provide a more powerful structuring mechanism for designing complex systems. The motivation for using JGrafchart instead of Stateflow can be compared to the motivation for using a high-level programming language such as Java instead of a low-level language. It enables the designers to easier build larger and more complex systems.

## 4.2 An Existing Control System

In this chapter the implementation process is described. Due to proprietary reasons, specific details are removed and replaced with generic substitutes. The investigated control system models the Primary Power Distribution System (PPDS) in a medium sized jet airliner. The PPDS is divided into several subsystems, among which are the Power Transfer system which handles the routing of power from the sources to the loads, and the Protection system which exists to isolate faulty components.

The main control objectives are to make sure that the system operates safely both during normal operation and faults, as well as maximize the bus availability for all system states. This means that the most fundamental safety requirements always shall be met and that the system should utilize the available power in the best possible way.

The following paragraphs describe the Stateflow implementation of the sequential parts of the controller, followed by a brief description of the interfaces necessary for communication between Simulink and JGrafchart as well as the implementation of the sequential control in JGrafchart.

### 4.2.1 Stateflow blocks

In the Power Transfer subsystem the configuration of the contactors takes place. Part of this is sequential control, represented in the system as Stateflow charts. The rest of the subsystem is mainly logical expressions, which for obvious reasons are left in Simulink since it is better suited to handle that kind of computations.

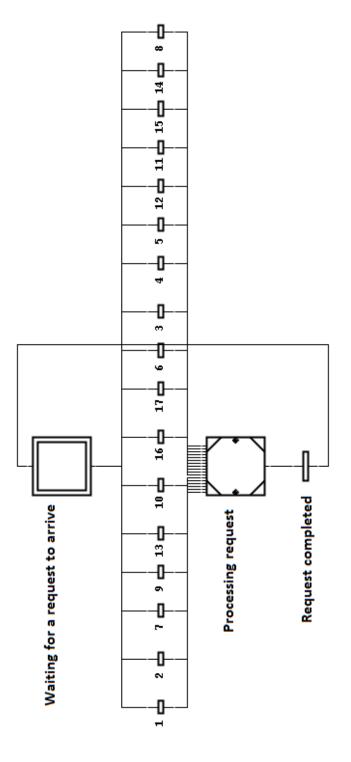

The first part of the sequential control determines which part of the electrical system to configure based on requests. The requests are generated based on the status of sources and contactors. The requests can be either to turn a source on, turn a source off or to reconfigure the system. In the first Stateflow block, all of the requests have priorities as they can be triggered simultaneously and only one request can be processed at a time.

The second Stateflow block handles the sequence of steps taken when a request is triggered. The sequence is executed sequentially to reach a new target AC and DC configuration, and may differ slightly depending on which request is triggered and what state the system was in before the request. If the target configuration cannot be achieved due to unavailable contactors, the controller will re-execute the second Stateflow chart to find an alternative path.

### 4.2.2 Interfaces

#### Communicator between Simulink and JGrafchart