ISSN 0280-5316 ISRN LUTFD2/TFRT--5684--SE

# Porting the Ericsson Bluetooth Stack A Real-Time Analysis

Mats Attnäs Ulrik Laurén

Department of Automatic Control Lund Institute of Technology April 2002

| Department of Au                                            |                                                           | Document name MASTER THESIS                                     |       |

|-------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------|-------|

| Lund Institute of Technology<br>Box 118                     |                                                           | Date of issue April 2002                                        |       |

| SE-221 00 Lund Sv                                           | veden                                                     | Document Number ISRN LUTFD2/TFRT5684                            | SE    |

| Author(s) Mats Attnäs and Ulrik La                          | urén                                                      | Supervisor<br>Karl-Erik Årzén. LTH<br>Pär-Gunnar Hjälmdahl, Eri | csson |

|                                                             |                                                           | Sponsoring organization                                         |       |

|                                                             | ooth Stack – A Real-Time A<br>uetooth stack – En realtids |                                                                 |       |

| stack and the effects of rep<br>The practical part consists | olacing this operating syste                              | system for the Ericsson Blue                                    |       |

|                                                             |                                                           |                                                                 |       |

|                                                             |                                                           |                                                                 |       |

|                                                             |                                                           |                                                                 |       |

|                                                             |                                                           |                                                                 |       |

|                                                             |                                                           |                                                                 |       |

|                                                             |                                                           |                                                                 |       |

|                                                             |                                                           |                                                                 |       |

|                                                             |                                                           |                                                                 |       |

|                                                             |                                                           |                                                                 |       |

|                                                             |                                                           |                                                                 |       |

| Keywords                                                    |                                                           |                                                                 |       |

| Classification system and/or inde                           | ex terms (if any)                                         |                                                                 |       |

|                                                             |                                                           |                                                                 |       |

| Supplementary bibliographical in                            | nformation                                                |                                                                 |       |

| ISSN and key title 0280-5316                                |                                                           |                                                                 | ISBN  |

| Language<br>English                                         | Number of pages 104                                       | Recipient's notes                                               |       |

| Security classification                                     |                                                           | i                                                               |       |

# Porting the Ericsson Bluetooth stack

- A real-time analysis

Master's thesis by

Mats Attnäs and Ulrik Laurén

Lunds tekniska högskola

April 2002

# 1 Contents

| 1 | Contents                                                         | 1                |

|---|------------------------------------------------------------------|------------------|

| 2 | Introduction                                                     | 5                |

|   | 2.1 Goal and purpose                                             | 5                |

|   | 2.2 What we have done                                            |                  |

|   | 2.3 What we have learned                                         |                  |

|   | 2.4 Requirements and constraints                                 |                  |

|   | 2.5 Investigated operating systems                               |                  |

|   | 2.5.1 OSE Epsilon                                                |                  |

|   | 2.5.2 µC/OS-II                                                   |                  |

|   | 2.5.3 eCos                                                       |                  |

|   | 2.5.4 Nucleus PLUS                                               |                  |

|   | 2.5.5 VxWorks                                                    |                  |

|   | 2.6 Outline of the thesis                                        |                  |

| 3 | Background                                                       | 11               |

|   | 3.1 Real-time operating systems                                  | 11               |

|   | 3.1.1 Introduction                                               |                  |

|   | 3.1.2 Classification of a real-time operating system             | 11               |

|   | 3.1.3 Scheduling                                                 |                  |

|   | 3.1.4 Internal components                                        | 12               |

|   | 3.1.4.1 Scheduling mechanism                                     | 13               |

|   | 3.1.4.2 Memory handler                                           | 13               |

|   | 3.1.4.3 Interrupt handler                                        |                  |

|   | 3.1.4.4 Clock                                                    |                  |

|   | 3.1.4.5 Error Handler                                            |                  |

|   | 3.2 Embedded system                                              |                  |

|   | 3.3 Bluetooth                                                    |                  |

|   | 3.4 Bluetooth specification and the Ericsson solution            | 14<br>1 <i>5</i> |

|   | 3.4.1 Link Manager                                               |                  |

|   | 3.4.2 Host Control Interface                                     |                  |

|   | 3.4.3 Higher layers                                              |                  |

|   | 3.5 Communication links                                          |                  |

|   | 3.5.1 SCO link                                                   |                  |

|   | 3.5.2 ACL link                                                   |                  |

|   |                                                                  |                  |

| 4 |                                                                  |                  |

|   | 4.1 Introduction                                                 | 19               |

|   | 4.2 Timing requirements                                          |                  |

|   | 4.2.1 Timing requirements in the general Bluetooth specification | 19               |

|   | 4.2.2 Timing requirements in the Ericsson solution               | 20               |

|   | 4.3 Memory requirements                                          |                  |

|   | 4.3.1 Memory requirements in the general Bluetooth specification | 20               |

|   | 4.3.2 Memory requirements in the Ericsson solution               | 20               |

|   | 4.4 Core                                                         |                  |

|   | 4.4.1 Introduction                                               | 21               |

|   | 4.4.2 VOS                                                        | 21               |

|   | 4.4.3 IRQ                                                        | 21               |

|   | 4.4.4 Handler Control                                            | 22               |

|   | 4.4.5 Power Management                                           | 22               |

|   | 4.4.6                                                                                                                                                                    | Timer                                                                                                                                                                                                                                                                                                                                                                                                                 | 22                                                                                                             |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

|   | 4.4.7                                                                                                                                                                    | Clock                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                |

|   | 4.4.8                                                                                                                                                                    | Cache                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                |

|   | 4.5 R                                                                                                                                                                    | TOS                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                |

| _ |                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                |

| 5 | OSE E                                                                                                                                                                    | psilon for ARM                                                                                                                                                                                                                                                                                                                                                                                                        | 25                                                                                                             |

|   | 5.1 Pr                                                                                                                                                                   | oblems                                                                                                                                                                                                                                                                                                                                                                                                                | 25                                                                                                             |

|   |                                                                                                                                                                          | terrupt handling                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                |

|   |                                                                                                                                                                          | emory handling                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                |

|   |                                                                                                                                                                          | ming                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                |

|   | 5.4.1                                                                                                                                                                    | Interrupt service times                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                |

|   | 5.4.2                                                                                                                                                                    | Scheduling                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                |

|   | -                                                                                                                                                                        | •                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                |

| 6 | eCos.                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                       | 29                                                                                                             |

|   | 6.1 In                                                                                                                                                                   | troduction                                                                                                                                                                                                                                                                                                                                                                                                            | 20                                                                                                             |

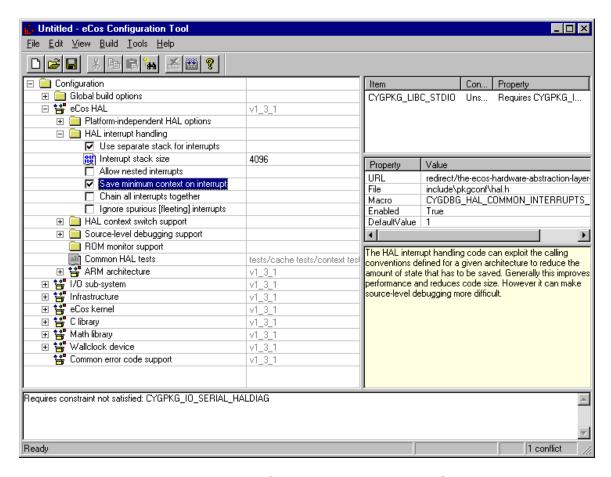

|   | 6.1.1                                                                                                                                                                    | Configuration layout                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                |

|   |                                                                                                                                                                          | oblems encountered                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                |

|   | 6.2.1                                                                                                                                                                    | Compilation                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                |

|   |                                                                                                                                                                          | Configuration                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                |

|   |                                                                                                                                                                          | -                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                |

| 7 | μC/OS                                                                                                                                                                    | S-II                                                                                                                                                                                                                                                                                                                                                                                                                  | 33                                                                                                             |

|   | 7.1 ln                                                                                                                                                                   | troduction                                                                                                                                                                                                                                                                                                                                                                                                            | 22                                                                                                             |

|   |                                                                                                                                                                          | oblems                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                |

|   |                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                |

|   | 7.2.1                                                                                                                                                                    | Priorities                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                |

|   | 7.2.2                                                                                                                                                                    | Messaging                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                |

|   | 7.2.3                                                                                                                                                                    | Memory allocation                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                |

|   | 7.2.4<br>7.2.5                                                                                                                                                           | Stack handling                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                |

|   |                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                       | ₹4                                                                                                             |

|   | 7.2.5                                                                                                                                                                    | Interrupt handling                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                |

| 8 |                                                                                                                                                                          | g VOS to μC/OS-II                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                |

| 8 | Portin                                                                                                                                                                   | g VOS to μC/OS-II                                                                                                                                                                                                                                                                                                                                                                                                     | 35                                                                                                             |

| 8 | Portin<br>8.1 In                                                                                                                                                         | g VOS to μC/OS-IItroduction                                                                                                                                                                                                                                                                                                                                                                                           | 3 <b>5</b>                                                                                                     |

| 8 | <b>Portin</b> 8.1 In <i>8.1.1</i>                                                                                                                                        | g VOS to µC/OS-IItroduction  Code organisation                                                                                                                                                                                                                                                                                                                                                                        | 35<br>35                                                                                                       |

| 8 | Portin<br>8.1 In<br>8.1.1<br>8.1.2                                                                                                                                       | g VOS to µC/OS-IItroduction                                                                                                                                                                                                                                                                                                                                                                                           | 35<br>35<br>35                                                                                                 |

| 8 | Portin<br>8.1 In<br>8.1.1<br>8.1.2<br>8.1.3                                                                                                                              | g VOS to µC/OS-II                                                                                                                                                                                                                                                                                                                                                                                                     | 35<br>35<br>35<br>35                                                                                           |

| 8 | Portin<br>8.1 In<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4                                                                                                                     | g VOS to µC/OS-II                                                                                                                                                                                                                                                                                                                                                                                                     | 35<br>35<br>35<br>37                                                                                           |

| 8 | Portin<br>8.1 In<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>8.1.5                                                                                                            | g VOS to µC/OS-II                                                                                                                                                                                                                                                                                                                                                                                                     | 35<br>35<br>35<br>37<br>37                                                                                     |

| 8 | Portin<br>8.1 In<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>8.1.5<br>8.1.6                                                                                                   | g VOS to µC/OS-II  troduction  Code organisation  Memory Allocation  Configuration  Message handling  Synchronisation  Limitations                                                                                                                                                                                                                                                                                    | 35<br>35<br>35<br>37<br>37<br>38                                                                               |

| 8 | Portin<br>8.1 In<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>8.1.5<br>8.1.6<br>8.2 M                                                                                          | g VOS to µC/OS-II                                                                                                                                                                                                                                                                                                                                                                                                     | 35<br>35<br>35<br>37<br>37<br>38<br>38                                                                         |

| 8 | Portin<br>8.1 In<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>8.1.5<br>8.1.6<br>8.2 M<br>8.2.1                                                                                 | g VOS to µC/OS-II                                                                                                                                                                                                                                                                                                                                                                                                     | 35<br>35<br>35<br>37<br>38<br>38<br>39                                                                         |

| 8 | Portin 8.1 In 8.1.1 8.1.2 8.1.3 8.1.4 8.1.5 8.1.6 8.2 M 8.2.1 8.2.1                                                                                                      | g VOS to µC/OS-II                                                                                                                                                                                                                                                                                                                                                                                                     | 35<br>35<br>35<br>37<br>38<br>38<br>39<br>39                                                                   |

| 8 | Portin 8.1 In 8.1.1 8.1.2 8.1.3 8.1.4 8.1.5 8.1.6 8.2 M 8.2.1 8.2.1 8.2.1                                                                                                | troduction                                                                                                                                                                                                                                                                                                                                                                                                            | 35<br>35<br>35<br>37<br>38<br>38<br>39<br>39                                                                   |

| 8 | Portin 8.1 In 8.1.1 8.1.2 8.1.3 8.1.4 8.1.5 8.1.6 8.2 M 8.2.1 8.2.1 8.2.1 8.2.2                                                                                          | troduction                                                                                                                                                                                                                                                                                                                                                                                                            | 35<br>35<br>35<br>37<br>38<br>39<br>39<br>39                                                                   |

| 8 | Portin 8.1 In 8.1.1 8.1.2 8.1.3 8.1.4 8.1.5 8.1.6 8.2 M 8.2.1 8.2.1 8.2.1 8.2.2 8.2.3                                                                                    | g VOS to µC/OS-II  troduction  Code organisation  Memory Allocation.  Configuration  Message handling  Synchronisation  Limitations  odifications made to VOS.  Memory allocation and deallocation  1 VOS_Alloc  2 VOS_Free  Time management  Process information                                                                                                                                                     | 35<br>35<br>35<br>37<br>38<br>38<br>39<br>39<br>40<br>40                                                       |

| 8 | Portin  8.1 In  8.1.1  8.1.2  8.1.3  8.1.4  8.1.5  8.1.6  8.2 M  8.2.1  8.2.1  8.2.1  8.2.2  8.2.3  8.2.3                                                                | g VOS to µC/OS-II  troduction  Code organisation  Memory Allocation.  Configuration  Message handling  Synchronisation  Limitations  odifications made to VOS.  Memory allocation and deallocation  1 VOS_Alloc  2 VOS_Free  Time management  Process information  3.1 VOS_CurrentProcess                                                                                                                             | 3535353737383939404041                                                                                         |

| 8 | Portin  8.1 In  8.1.1  8.1.2  8.1.3  8.1.4  8.1.5  8.1.6  8.2 M  8.2.1  8.2.1  8.2.2  8.2.3  8.2.3  8.2.4                                                                | g VOS to µC/OS-II                                                                                                                                                                                                                                                                                                                                                                                                     | 3535353737383939404141                                                                                         |

| 8 | Portin  8.1 In  8.1.1  8.1.2  8.1.3  8.1.4  8.1.5  8.1.6  8.2 M  8.2.1  8.2.1  8.2.2  8.2.3  8.2.3  8.2.4  8.2.4                                                         | g VOS to µC/OS-II  troduction  Code organisation  Memory Allocation.  Configuration  Message handling  Synchronisation.  Limitations  odifications made to VOS.  Memory allocation and deallocation.  1 VOS_Alloc.  2 VOS_Free  Time management  Process information  3.1 VOS_CurrentProcess  Message transfer.  1 VOS_Send                                                                                           | 353535373738393940414141                                                                                       |

| 8 | Portin  8.1 In  8.1.1  8.1.2  8.1.3  8.1.4  8.1.5  8.1.6  8.2 M  8.2.1  8.2.1  8.2.2  8.2.3  8.2.3  8.2.4                                                                | troduction Code organisation Memory Allocation Configuration Message handling Synchronisation Limitations odifications made to VOS Memory allocation and deallocation 1 VOS_Alloc 2 VOS_Free Time management Process information 3.1 VOS_CurrentProcess Message transfer 4.1 VOS_Send 4.2 VOS_Receive                                                                                                                 | 35353537373839394041414141                                                                                     |

| 8 | Portin  8.1 In  8.1.1  8.1.2  8.1.3  8.1.4  8.1.5  8.1.6  8.2 M  8.2.1  8.2.1  8.2.2  8.2.3  8.2.4  8.2.4  8.2.4  8.2.4                                                  | g VOS to μC/OS-II  troduction  Code organisation  Memory Allocation  Configuration  Message handling  Synchronisation  Limitations  odifications made to VOS  Memory allocation and deallocation  1 VOS_Alloc  2 VOS_Free  Time management  Process information  3.1 VOS_CurrentProcess  Message transfer  1.1 VOS_Send  2 VOS_Receive  3 VOS_Receive  3 VOS_ReceiveList                                              | 3535353737383939404141414242                                                                                   |

| 8 | Portin  8.1 In  8.1.1  8.1.2  8.1.3  8.1.4  8.1.5  8.1.6  8.2 M  8.2.1  8.2.1  8.2.2  8.2.3  8.2.4  8.2.4  8.2.4  8.2.4  8.2.4  8.2.4  8.2.4                             | g VOS to µC/OS-II  troduction  Code organisation  Memory Allocation  Configuration  Message handling  Synchronisation  Limitations  odifications made to VOS  Memory allocation and deallocation  1 VOS_Alloc  2 VOS_Free  Time management  Process information  3.1 VOS_CurrentProcess  Message transfer  1.1 VOS_Send  2 VOS_Receive  3 VOS_Receive  3 VOS_ReceiveList  4 VOS_Sender                                | 3535353737383939404141414242                                                                                   |

| 8 | Portin  8.1 In  8.1.1  8.1.2  8.1.3  8.1.4  8.1.5  8.1.6  8.2 M  8.2.1  8.2.1  8.2.2  8.2.3  8.2.4  8.2.4  8.2.4  8.2.4  8.2.4  8.2.4  8.2.4                             | g VOS to μC/OS-II                                                                                                                                                                                                                                                                                                                                                                                                     | 35353537373839394041414141424242                                                                               |

| 8 | Portin  8.1 In  8.1.1  8.1.2  8.1.3  8.1.4  8.1.5  8.1.6  8.2 M  8.2.1  8.2.1  8.2.2  8.2.3  8.2.4  8.2.4  8.2.4  8.2.4  8.2.4  8.2.4  8.2.5                             | troduction  Code organisation  Memory Allocation  Configuration  Message handling  Synchronisation  Limitations  odifications made to VOS  Memory allocation and deallocation  1 VOS_Alloc  2 VOS_Free  Time management  Process information  3.1 VOS_CurrentProcess  Message transfer  1.1 VOS_Send  1.2 VOS_Receive  1.3 VOS_Receive  1.3 VOS_ReceiveList  1.4 VOS_Sender  Critical sections  5.1 VOS_EnterCritical | 3535353737383939404141414142424243                                                                             |

| 8 | Portin  8.1 In  8.1.1  8.1.2  8.1.3  8.1.4  8.1.5  8.1.6  8.2 M  8.2.1  8.2.1  8.2.2  8.2.3  8.2.4  8.2.4  8.2.4  8.2.4  8.2.4  8.2.5  8.2.5  8.2.5                      | troduction  Code organisation  Memory Allocation  Configuration  Message handling  Synchronisation  Limitations  odifications made to VOS  Memory allocation and deallocation  1 VOS_Alloc  2 VOS_Free  Time management  Process information  3.1 VOS_CurrentProcess  Message transfer  1.1 VOS_Send  1.2 VOS_Receive  1.3 VOS_Receive  1.3 VOS_ReceiveList  1.4 VOS_Sender  Critical sections  5.1 VOS_EnterCritical | 35<br>35<br>35<br>37<br>37<br>38<br>38<br>39<br>40<br>40<br>41<br>41<br>41<br>42<br>42<br>42<br>43<br>43       |

| 8 | Portin  8.1 In  8.1.1  8.1.2  8.1.3  8.1.4  8.1.5  8.1.6  8.2 M  8.2.1  8.2.1  8.2.2  8.2.3  8.2.4  8.2.4  8.2.4  8.2.4  8.2.5  8.2.5  8.2.5  8.2.6  8.2.6  8.2.6        | g VOS to µC/OS-II                                                                                                                                                                                                                                                                                                                                                                                                     | 35<br>35<br>35<br>37<br>37<br>38<br>38<br>39<br>40<br>40<br>41<br>41<br>41<br>42<br>42<br>42<br>43<br>43<br>43 |

| 8 | Portin  8.1 In  8.1.1  8.1.2  8.1.3  8.1.4  8.1.5  8.1.6  8.2 M  8.2.1  8.2.1  8.2.2  8.2.3  8.2.4  8.2.4  8.2.4  8.2.4  8.2.5  8.2.5  8.2.5  8.2.6  8.2.6  8.2.6        | g VOS to µC/OS-II                                                                                                                                                                                                                                                                                                                                                                                                     | 35353537373838393940414141424242434343                                                                         |

| 8 | Portin  8.1 In  8.1.1  8.1.2  8.1.3  8.1.4  8.1.5  8.1.6  8.2 M  8.2.1  8.2.1  8.2.2  8.2.3  8.2.4  8.2.4  8.2.4  8.2.4  8.2.5  8.2.5  8.2.5  8.2.6  8.2.6  8.2.7  8.2.7 | g VOS to μC/OS-II                                                                                                                                                                                                                                                                                                                                                                                                     | 35 35 35 37 37 38 38 39 40 41 41 41 42 42 42 43 43 43 43 44 44                                                 |

| 8.3.1          | I Interrupt handling                                               | 44 |

|----------------|--------------------------------------------------------------------|----|

| 8.3.2          |                                                                    |    |

| 8.3            | 3.2.1 Stack initialisation                                         | 45 |

| 9 Perf         | ormance tests                                                      | 47 |

| 9.1            | Execution time                                                     | 47 |

| 9.1.1          |                                                                    |    |

| 9.1.2          |                                                                    |    |

| 9.1.3          |                                                                    |    |

| 9.1            | 1.3.1 Critical regions                                             |    |

|                | 1.3.2 Memory allocation                                            |    |

|                | 1.3.3 Message passing                                              |    |

|                | 1.3.4 Interrupt handling                                           |    |

|                | Conclusion                                                         |    |

|                | Pre-scheduling performance                                         |    |

| 9.2.1<br>9.2.2 |                                                                    |    |

| 9.2.2          |                                                                    |    |

|                | Memory usage                                                       |    |

| 9.3<br>9.3.1   |                                                                    |    |

| 9.3.2          |                                                                    |    |

| 9.3.3          |                                                                    |    |

| 9.3.4          |                                                                    |    |

|                |                                                                    |    |

| 10 Too         | ls used                                                            | 57 |

| 10.1           | Trace32                                                            | 57 |

|                | ARM Software Development Tool                                      |    |

|                | Config                                                             |    |

|                | -                                                                  |    |

| 11 Con         | ıclusion                                                           | 59 |

| 11.1           | The choice of operating system                                     | 59 |

| 11.2           | The portability of the Ericsson Bluetooth stack                    | 59 |

| 11.3           | VOS requirements and limitations                                   | 59 |

| 11.4           | Time requirements                                                  | 60 |

| 11.5           | General implementation experiences                                 | 61 |

| 12 Ack         | nowledgements                                                      | 63 |

|                | · ·                                                                |    |

| 13 Refe        | erences                                                            | 65 |

| 14 Glos        | ssary                                                              | 67 |

|                | Abbreviations                                                      |    |

|                |                                                                    |    |

| Appendi        | x I The IRQ mask                                                   | 69 |

| Appendi        | x II General information about task and interrupt handling         | 71 |

|                | • •                                                                |    |

|                | nsk switches                                                       |    |

|                | terrupt Service Routines                                           |    |

|                | e task                                                             |    |

|                | ne stack                                                           |    |

|                | cenario: A normal task switch                                      |    |

| 6 Sc           | enario: Interrupt handling                                         |    |

| <b>Appendi</b> | x III Implementation issues concerning task and interrupt handling | 77 |

|                |                                                                    |    |

| 1 Ne           | ested interrupts                                                   | 77 |

| Appendix IV How CORE_IrqHandler() works.   | 81    |

|--------------------------------------------|-------|

| Appendix V Configuring the μC/OS-II VOS pe | ort87 |

| Appendix VI Error codes from μC/OS-II      | 89    |

|                                            | 89    |

|                                            | 89    |

|                                            | 89    |

|                                            | 90    |

|                                            | 90    |

|                                            | 90    |

|                                            | 90    |

|                                            | 91    |

| <b>2.7</b> OSTaskCreate()                  | 91    |

| Appendix VII The ARM architecture          | 93    |

| 1 Introduction                             | 93    |

|                                            | 93    |

| •                                          | 93    |

|                                            | 94    |

|                                            | 95    |

|                                            | 95    |

|                                            | 95    |

|                                            | 96    |

|                                            | 96    |

|                                            | 96    |

|                                            | 96    |

| 5.7 System mode (SYS)                      | 96    |

| Appendix VIII Files                        | 97    |

### 2 Introduction

# 2.1 Goal and purpose

The main goal of this master thesis was to switch the current real-time operating system that powers the *Ericsson Bluetooth embedded platform* (BEP).

It is recommended that the reader of this master thesis have at least a basic understanding of real-time operating systems and embedded platforms to fully comprehend and profit from the contents.

The reason for this was to evaluate if and how it could be done, and what problems one may encounter. Also, it would show if the intention of making the platform portable had been successful or not. This could be useful for future applications in other hardware or software environments, allowing a greater flexibility and possibility to integrate the system with existing client products.

The thesis was done in co-operation with *Ericsson Technology Licensing*.

### 2.2 What we have done

The work has mainly consisted of three parts:

- Preparatory investigation of suitable operating systems for porting.

- Adaptation of the system to interface with the new operating system.

- Analysis of the performance differences of the two ports, and their implications.

### 2.3 What we have learned

- The principles of the Bluetooth protocol.

- How an embedded application is designed and what its limitations are.

- How real-time operating systems work, and differences between design principles of such.

- How to debug and examine an embedded application.

# 2.4 Requirements and constraints

There are quite a few constraints placed on the work performed in the master thesis since it deals with an already existing technology that should be modified, not rebuilt. The main requirement is that the system has to be able to function in such a tightly planned hard real-time environment that BEP offers. But since it is designed for an embedded environment there is also a strict limit for how much memory that could be used by the system.

Both of these requirements are dealt with by most real-time operating systems but there are other limitations placed on the system. It is necessary for the RTOS to function with the ARM7 processor architecture both in ARM and Thumb mode (see Appendix VII for details on the ARM architecture). The reason for this is that BEP has parts of it developed in assembly language that utilise both of these modes and the test environment use the ARM7 processor.

The final requirements were that no changes should be made to the current development environment and that the new operating system had to fit into the model of the system. The reason behind these requirements was that this master thesis should also try to discern any problems that could arise when working with a new real-time operating system. This meant that it was necessary to develop systems that support the existing functionality implemented in the *virtual operating system* (VOS) using the functions available in the new operating system. This requirement also prevented any changes to the programs used in the original development environment.

# 2.5 Investigated operating systems

To implement the port, a target operating system had to be found first. Three factors were especially important: Real-time performance, compactness and availability.

It was also necessary to gain basic knowledge of the existing operating system, OSE Epsilon, to know how to adapt the new operating system. The principle of the VOS is to require only very basic functionality from the operating system, thereby allowing many different operating systems.

Our choice of target operating system finally fell on  $\mu$ C/OS-II, because of its simplistic and efficient design and its royalty free license.

# 2.5.1 OSE Epsilon

| Supported target processors            | Siemens C166/167, ARM7/Thumb, NEC V85X, Atmel AVR, Mitsubishi M16, 8051, 68HC11, Z80, 64180    |

|----------------------------------------|------------------------------------------------------------------------------------------------|

| Supported compilers                    | Distributed as target specific assembly code                                                   |

| Supported standards                    | None                                                                                           |

| Supplied as                            | Assembly code                                                                                  |

| Guaranteed maximum interrupt latency   | Hard real-time                                                                                 |

| Scheduling policies                    | Fixed priority preemptive scheduling (priority processes) + Round robin (background processes) |

| Priority inversion avoidance mechanism | None                                                                                           |

| Nested interrupts                      | Yes                                                                                            |

OSE Epsilon is a real-time operating system developed by Enea OSE AB. They also have a couple of other versions of their operating system but Epsilon is the smallest version. It is the main real-time operating system used by Ericsson and the platform currently used for the Ericsson Bluetooth stack.

# 2.5.2 μC/OS-II

| Supported target processors               | x86, PowerPC, ARM, MIPS, StrongARM, NEC V850, Hitachi SH, and many more |

|-------------------------------------------|-------------------------------------------------------------------------|

| Supported compilers                       | ANSI-C                                                                  |

| Supported standards                       | None                                                                    |

| Supplied as                               | Source                                                                  |

| Guaranteed maximum inter-<br>rupt latency | Hard real-time                                                          |

| Scheduling policies                       | Fixed priority preemptive scheduling                                    |

| Priority inversion avoidance mechanism    | None                                                                    |

| Nested interrupts                         | No                                                                      |

$\mu$ C/OS-II is a very small real-time operating system developed by Jean J. Labrosse of Micriµm Incorporated. Its source code is openly available, and the terms of use are very advantageous.

### 2.5.3 eCos

|                                        | <b>T</b>                                                                        |

|----------------------------------------|---------------------------------------------------------------------------------|

| Supported target processors            | x86, PowerPC, ARM, MIPS, StrongARM, NEC V850, Hitachi SH, Panasonic AM3x, SPARC |

| Supported compilers                    | GCC (GNU)                                                                       |

| Supported standards                    | EL/IX, ISO C, POSIX.1, μITRON                                                   |

| Supplied as                            | Object, source                                                                  |

| Guaranteed maximum interrupt latency   | Soft real-time                                                                  |

| Scheduling policies                    | Prioritised FIFO, bitmap                                                        |

| Priority inversion avoidance mechanism | Priority inheritance, priority ceilings                                         |

| Nested interrupts                      | Yes                                                                             |

eCos is a highly configurable real-time operating system for deeply embedded applications, maintained by Red Hat. It is not an embedded Linux, though it offers POSIX.11 compatibility, as well as an optional µITRON2 compatibility layer.

eCos is also an open source initiative, and therefore free of charge.

### 2.5.4 Nucleus PLUS

| Supported target processors            | x86, PowerPC, ARM, MIPS |

|----------------------------------------|-------------------------|

| Supported compilers                    | ANSI-C                  |

| Supported Standards                    | μITRON, OSEK            |

| Supplied as                            | Source                  |

| Guaranteed maximum interrupt latency   | Hard real-time          |

| Scheduling policies                    | Prioritised FIFO        |

| Priority inversion avoidance mechanism | Yes                     |

| Nested interrupts                      | Yes                     |

Nucleus PLUS is a royalty free, small and powerful RTOS from Accelerated Technology, optionally supporting µITRON or OSEK<sup>3</sup>.

8

<sup>1</sup> Set of standards designed to provide application portability between Unix variants 2 Application interface for real-time systems, widely used in the Japanese embedded market 3 An RTOS interface standard used mainly in the vehicle manufacturing industry

### 2.5.5 VxWorks

| Supported target processors            | x86, PowerPC, ARM, MIPS, 68K, i960, SH, SPARC, NEC V8xx, M32 R/D, RAD6000, ST 20 |

|----------------------------------------|----------------------------------------------------------------------------------|

| Supported compilers                    | ANSI-C/C++                                                                       |

| Supported Standards                    | POSIX 1003.1b                                                                    |

| Supplied as                            | Object                                                                           |

| Guaranteed maximum interrupt latency   | Hard real-time                                                                   |

| Scheduling policies                    | Prioritised FIFO, round robin                                                    |

| Priority inversion avoidance mechanism | Yes                                                                              |

| Nested interrupts                      | Yes                                                                              |

VxWorks from Wind River Systems is the most widely used RTOS in the world, and is both scalable and efficient.

### 2.6 Outline of the thesis

A short description of the information presented in the chapters:

In chapter 3 there is an introduction to the more important concepts necessary for understanding the contents of this report. The chapter is followed by an analysis of the Bluetooth specification and the Ericsson solution, focusing on either real-time or memory constraints. This is followed by a short introduction and analysis of the three operating systems that were examined thoroughly, namely OSE Epsilon, eCos and  $\mu$ C/OS-II. After this introduction and analysis, a detailed description of the modifications that were necessary for the Ericsson solution to function with its new operating system,  $\mu$ C/OS-II, follows. The performance tests and their implications are presented and discussed in the next chapter, followed by a short description of the programs used. This is followed by the conclusions of the master thesis and finally there are the acknowledgements and references followed by a short glossary of important abbreviations.

Following all these chapters are a number of appendices that are referenced from various parts of the report.

# 3 Background

# 3.1 Real-time operating systems

### 3.1.1 Introduction

An operating system is basically the software needed to run applications, programs, on a computer system. This software includes process handling, hardware drivers and memory handling, all those things that often are taken for granted when using modern computers.

When real-world interaction becomes an issue, so do real-world time constraints. These constraints are most often of a temporal nature, it is necessary to complete certain tasks within a certain time. When working with humans these interactions often have constraints in the range of a few seconds, but when interacting with other computer devices these timing constraints are reduced to very small units.

For this reason, real-time operating systems contain certain basic primitives:

- Prioritised processes/threads

- Multileveled interrupts

- Mutexes and semaphores

### 3.1.2 Classification of a real-time operating system

There are two basic types of real-time operating systems, *hard* and *soft* ones. The hard real-time systems are predictable; it is possible to guarantee maximum and minimum execution time for system calls, procedures, and interrupt latencies. Hard real-time operating systems therefore have very high demands in terms of scheduling and interrupt handling.

In soft real-time systems, the system only needs to behave in a consistent manner, being allowed to fail to fulfil the time constraints from time to time. This leeway allows the system to employ somewhat less strict interrupt handling, and the scheduling can be done in a not so strict and predictable manner.

Real-time operating systems can alternatively be grouped according to their interaction with their surroundings. They can be either time or event driven, or in rare cases both.

An event driven real-time operating system reacts to events that occur during execution, and can modify the order of execution, while a time driven real-time operating system has a fixed execution schedule that is calculated before execution starts.

### 3.1.3 Scheduling

The scheduler plans the execution to ensure that the processes can fulfil their deadlines. However, the running process may be interrupted by a more important process, in which case the operating system has to be able to do a context switch, letting the more important process run. This is allowed only if at least one of the following conditions are met:

- A clock tick interrupt has occurred. Clock tick interrupts occur when the system updates the time, and checks if any other task with a higher priority wants to run.

- A running task performs a system call.

- The interrupt handler orders a switch due to an external interrupt.

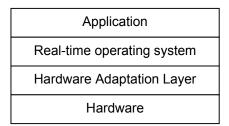

The system can be divided into four distinct layers, see Figure 1. The bottom layer is the hardware that contains CPU, physical memory, a clock, and communication hardware. On top of this layer is the hardware adaptation layer, containing functionality for registers and interrupt handling. The real-time operating system layer consists of functionality for scheduling, synchronisation and interprocess communication. The highest layer consists of applications that run on the platform.

Figure 1. The structure of an embedded solution

### 3.1.4 Internal components

This section describes the internal components of a typical real-time operating system. Many of these components can also be found in standard operating systems.

### 3.1.4.1 Scheduling mechanism

The scheduling mechanism plans the order in which the active processes are to execute. This planning can be done according to a variety of principles. The basic concept for all of them is that processes have a deadline to uphold. The two most common algorithms are rate monotonic scheduling and earliest deadline scheduling. Both of them have pros and cons. Rate monotonic scheduling has a stabile, predictable behaviour, but assumes that all tasks are independent. Earliest deadline scheduling is easy to implement and uses the CPU very efficiently, but may result in unpredictable behaviour if a task fails to meet its deadline. Both algorithms are designed to be used in an event driven operating system, where new processes are activated due to external events, and not according to a predefined plan.

### 3.1.4.2 Memory handler

The memory handling system is responsible for the handling of dynamic memory, with the use of a central memory pool. When a process has finished using a memory portion, it returns it to the memory pool. To prevent memory fragmentation it is important to have a good algorithm for memory allocation, especially in small, embedded systems, where often the amount of available memory is very limited.

### 3.1.4.3 Interrupt handler

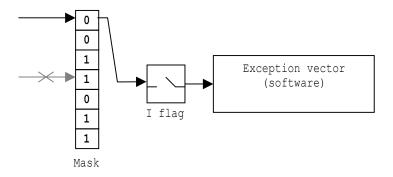

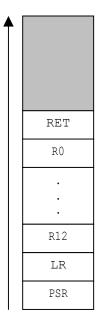

Interrupts can be activated from either hardware or software, and both have to be handled. This is taken care of by the interrupt handler, which can force context switches. If the priority of an interrupt is not high enough it will be discarded, and the running process will continue running. A discarded interrupt is dealt with either by ignoring it, hoping that if the problem remains a new interrupt will occur, or delaying it until the executing processes has finished. When an interrupt is called, there is a short delay before the interrupt can start executing. This delay is called interrupt latency, and during this period the executing process is stored away and the new process, activated by the interrupt, is placed into memory ready to start executing.

### 3.1.4.4 Clock

An external clock generates ticks through hardware interrupts to the operating system, allowing it to update the internal clock. Processes used to measure time intervals and to set timers to activate after a certain amount of ticks can then use the internal clock. This is necessary if the operating system is designed to support periodical and sleeping processes. The precision of the clock has to be very good to prevent drift over long periods.

#### 3.1.4.5 Error Handler

The error handling consists of a central system that can handle exceptions from running processes and activate a suitable response. This response varies according to the severity of the error encountered. Serious errors can cause the error handler to terminate the executing process or even freeze the entire system.

### 3.1.4.6 Data access synchronisation

Access to shared resources, such as memory areas or devices, can be controlled using some kind of signalling device that prevents other processes from using that resource. This can be implemented in many different ways, but it is often implemented with semaphores or mutexes.

It is necessary for a real-time operating system to prevent simultaneous access to resources because this might result in corrupted data.

# 3.2 Embedded system

An embedded system is a computer system that is integrated into a device, performing a certain task. The size and complexity of both the computer system and its task may vary substantially, though generally it is a matter of small devices with very limited processing and memory capabilities. Furthermore, embedded systems often act in co-ordinance with external events and conditions, such as sensors and timers, rather than actual user interaction.

### 3.3 Bluetooth

Bluetooth is a wireless communications standard developed by the Bluetooth Special Interest Group (SIG). Its main focus is to provide wireless connectivity between any kind of electronic device, at a low price and easy access. To put it simple, Bluetooth reduces the need for cables and specific communication protocols between devices, allowing everything to communicate with anything.

Bluetooth powered units can communicate and send data or voice over the connections. The existing standard is designed to support a multitude of different devices including everything from headsets for mobile telephones to connecting computers to networks.

In Bluetooth, there are *masters* and *slaves*. A master can have many slaves, and may also be the slave of another master. A master with slaves is called a *piconet*. Several inter-connected piconets form a *scatternet*.

# 3.4 Bluetooth specification and the Ericsson solution

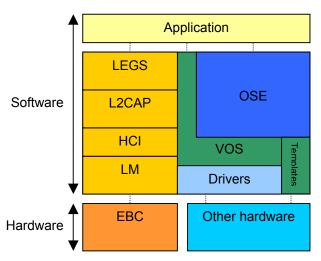

The Ericsson Bluetooth solution for embedded systems is a hardware and software platform, see Figure 2. The hardware contains the baseband controller block (EBC), a CPU, some RAM, some ROM, some flash memory and input/output ports (UART and USB). Apart from the application, the software mainly consists of two parts: the Bluetooth stack and the operating system. To make a port of the stack as easy as possible, an interface layer (VOS and templates) is put between the two. All operating system calls from the stack are consequently done through this layer.

Figure 2. Schematics of the Ericsson Bluetooth platform, and its surrounding components, both hardware and software

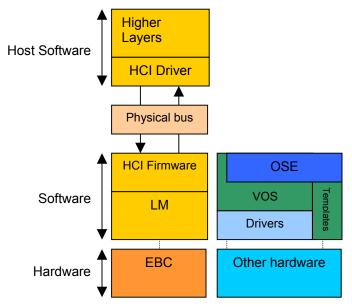

In a host solution where the Bluetooth device is not planned to run everything on its own processor the layout of the components is a bit different as shown in Figure 3.

Figure 3. Shows a schematic describing the host version of the Ericsson Bluetooth platform.

### 3.4.1 Link Manager

The link manager is the lowest software layer in the stack. It controls the usage of the common channel, connections of new slaves and searches for available units. It also implements security for the data transferred through encryption and controls how to portion packets between the master and the slaves on the common channel.

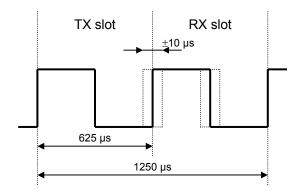

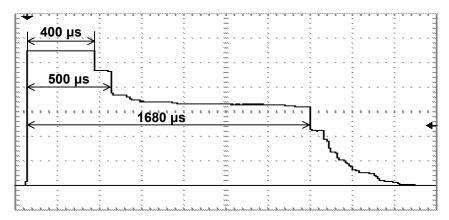

The physical channel is divided into equally sized time frames of 1,250  $\mu$ s each. Each frame is divided into two slots, which hence are 625  $\mu$ s each. The master in a connection uses the first slot in each frame to send data and the second slot to receive data from the slaves.