# PROGNOSTICS AND DIAGNOSIS OF CATASTROPHIC FAULTS IN PHOTOVOLTAIC ARRAY AND RELIABILITY CENTERED MAINTENANCE (RCM) FOR POWER CONVERTERS USING SPREAD SPECTRUM TIME DOMAIN REFLECTOMETRY (SSTDR)

by

Mohammed Khorshed Alam

A dissertation submitted to the faculty of

The University of Utah

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Department of Electrical and Computer Engineering

The University of Utah

May 2015

Copyright © Mohammed Khorshed Alam 2015

All Rights Reserved

## The University of Utah Graduate School

# STATEMENT OF DISSERTATION APPROVAL

| The dissertation of                    | Mohammed Khorshed           | Alam                     |

|----------------------------------------|-----------------------------|--------------------------|

| has been approved by the following sup | ervisory committee members: |                          |

| Marc Bodson                            | , Chair                     | 11/07/2014 Date Approved |

| Rajesh Menon                           | , Member                    | 11/03/2014 Date Approved |

| Jeffrey Walling                        | , Member                    | 11/03/2014 Date Approved |

| Thomas Schmid                          | , Member                    | Date Approved            |

| Sanford G. Meek                        | , Member                    | 11/04/2014 Date Approved |

| Michael Scarpulla                      | , Member                    | 11/04/2014               |

| and by Gian                            | nluca Lazzi                 | _ , Chair/Dean of        |

| the Department/College/School of       | Electrical and Computer     | Engineering              |

| and by David B. Kieda, Dean of The Gr  | raduate School.             |                          |

### **ABSTRACT**

Three major catastrophic failures in photovoltaic (PV) arrays are ground-faults, line-to-line faults, and arc faults. Although the number of such failures is few, recent fire events on April 5, 2009, in Bakersfield, California, and April 16, 2011, in Mount Holly, North Carolina suggest the need for improvements in present fault detection and mitigation techniques, as well as amendments to existing codes and standards to avoid such accidents. A fault prediction and detection technique for PV arrays based on spread spectrum time domain reflectometry (SSTDR) has been proposed and was successfully implemented. Unlike other conventional techniques, SSTDR does not depend on the amplitude of the fault-current. Therefore, SSTDR can be used in the absence of solar irradiation as well. However, wide variation in impedance throughout different materials and interconnections makes fault locating more challenging than prediction/detection of faults.

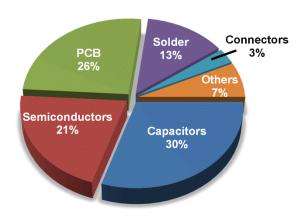

Another application of SSTDR in PV systems is the measurement of characteristic impedance of power components for condition monitoring purposes. Any characteristic variations in one component will simultaneously alter the operating conditions of other components in a closed-loop system, resulting in a shift in overall reliability profile. This interdependence makes the reliability of a converter a complex function of time and operating conditions. Details of this failure mode, mechanism, and effect analysis

(FMMEA) have been developed. By knowing the present state of health and the remaining useful life (RUL) of a power converter, it is possible to reduce the maintenance cost for expensive high-power converters by facilitating a reliability centered maintenance (RCM) scheme. This research is a step forward toward power converter reliability analysis since the cumulative effect of multiple degraded components has been considered here for the first time in order to estimate reliability of a power converter.

### TABLE OF CONTENTS

| ABSTRACTi                                                                                                                                                              | iii                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| LIST OF TABLES                                                                                                                                                         | ix                         |

| ACKNOWLEDGEMENTS                                                                                                                                                       | X                          |

| Chapters                                                                                                                                                               |                            |

| 1. INTRODUCTION.                                                                                                                                                       | 1                          |

| 1.1 References.                                                                                                                                                        | 4                          |

| 2. CATASTROPHIC FAULTS IN PV ARRAYS: TYPES, DETECTION AND MITIGATION TECHNIQUES                                                                                        | 7                          |

| 2.1.1 Grounded and Ungrounded PV Systems12.1.2 Reasons for Ground Fault12.1.3 Ground Fault Detection Techniques12.1.3.1 GFDI Fuse12.1.3.2 Monitoring Residual Current1 | 8<br>9<br>10<br>11<br>12   |

| 2.1.4 Blind Spot and Double Ground Fault                                                                                                                               | 13<br>14<br>15             |

| 2.3.1 Physics of Arc                                                                                                                                                   | 18<br>20<br>20             |

| 2.3.2.3 Differentiating Between Series and Parallel Arc Faults 2 2.3.2.4 Effect on PV Operation                                                                        | 21<br>22<br>24<br>28<br>32 |

|    | 2.6 Conclusions 2.7 References                                     |     |

|----|--------------------------------------------------------------------|-----|

| 3. |                                                                    |     |

|    | DOMAIN REFLECTOMETRY (SSTDR)                                       | 57  |

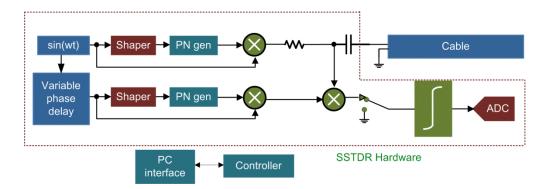

|    | 3.1 Spread Spectrum Time Domain Reflectometry (SSTDR)              | 58  |

|    | 3.1.1 Basic Concepts of Reflectometry                              | 58  |

|    | 3.1.2 SSTDR Theory                                                 | 61  |

|    | 3.2 Ground Fault Detection Using SSTDR                             | 63  |

|    | 3.2.1 Creating Baseline                                            | 64  |

|    | 3.2.2 Estimating System Noise                                      | 65  |

|    | 3.2.3 Fault Detection                                              | 65  |

|    | 3.3 Influence of Different Parameters on Fault Detection Algorithm | 66  |

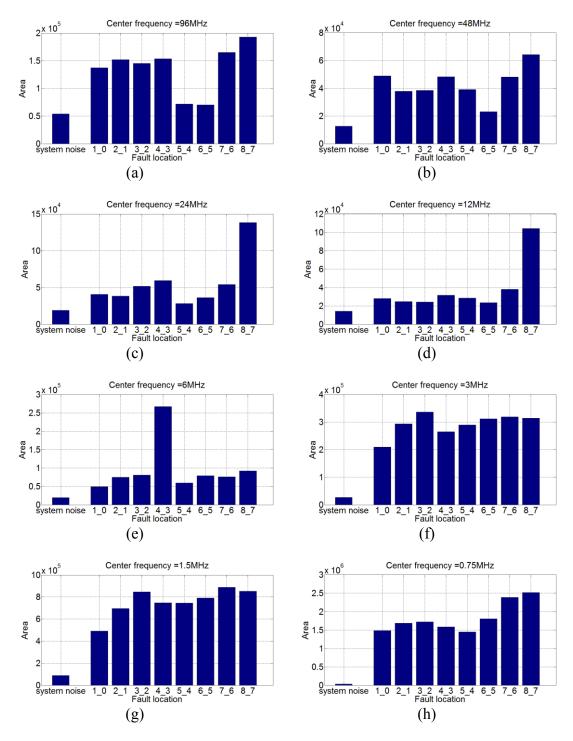

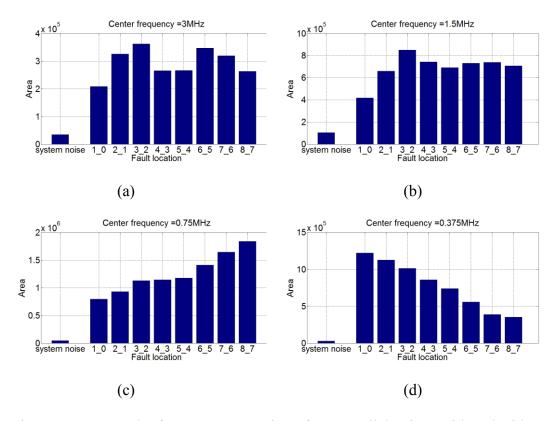

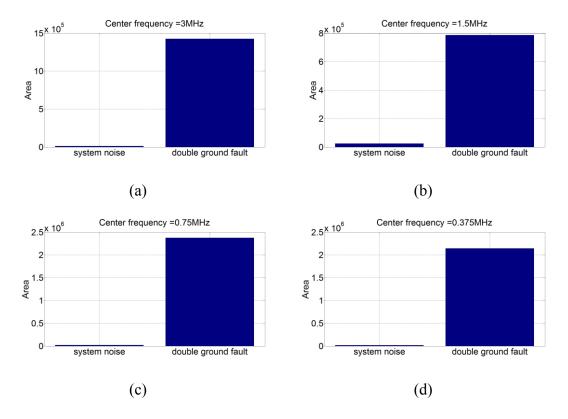

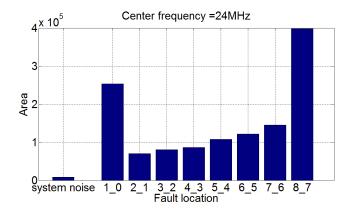

|    | 3.3.1 Impact of Carrier frequency                                  | 66  |

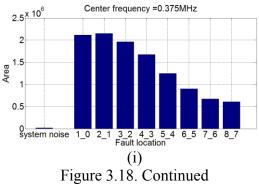

|    | 3.3.2 Impact of Fault Resistance                                   | 67  |

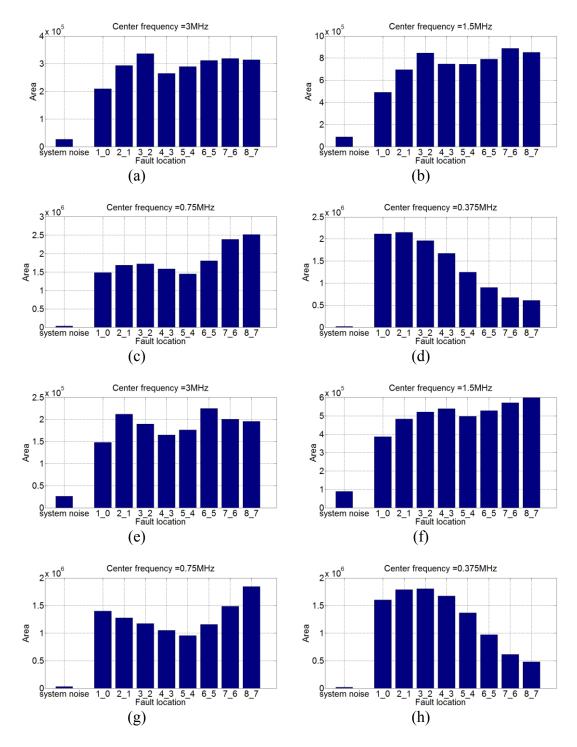

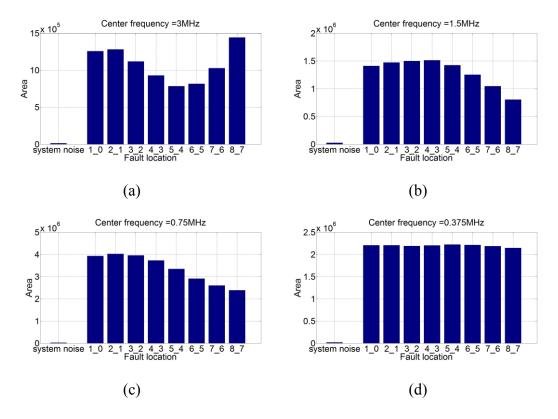

|    | 3.3.3 Impact of Parallel Connected Strings                         |     |

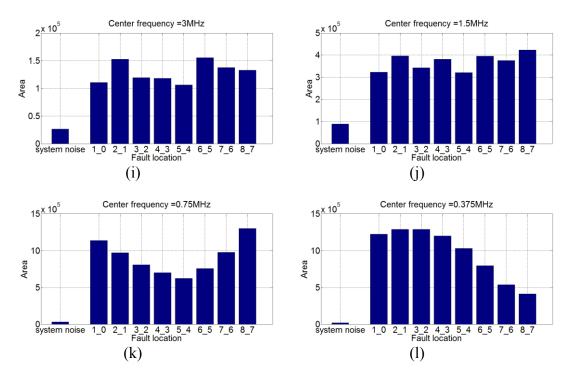

|    | 3.3.4 Impact of Solar Irradiance                                   | 69  |

|    | 3.3.5 Double Ground Fault                                          |     |

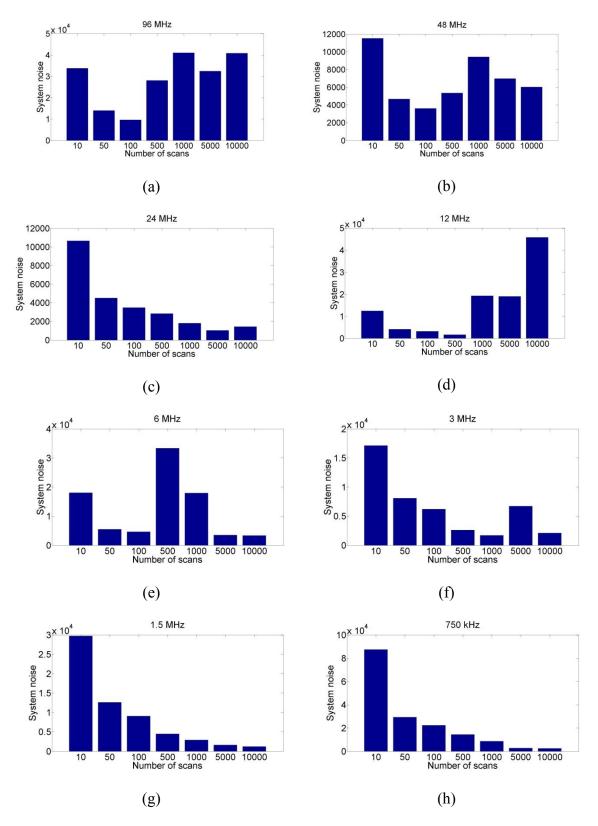

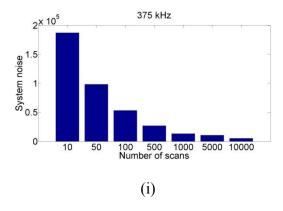

|    | 3.3.6 Impact of Number of Scans on the Estimation of System Noise  |     |

|    | 3.4 Limitations of the Proposed Technique                          |     |

|    | 3.5 Conclusions                                                    |     |

|    | 3.6 References                                                     | 72  |

| 4  | OPEN (ARC) FAULT DETECTION USING SPREAD SPECTRUM TIME              |     |

| •• | DOMAIN REFLECTOMETRY (SSTDR)                                       | 97  |

|    |                                                                    |     |

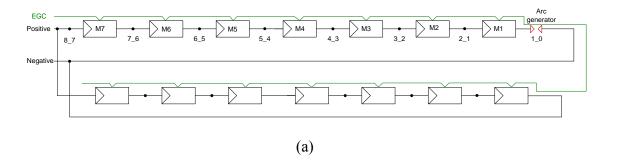

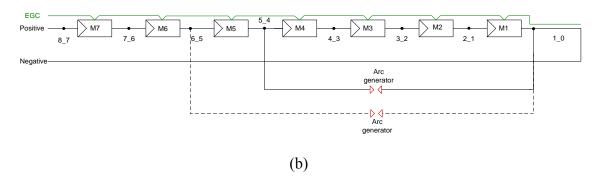

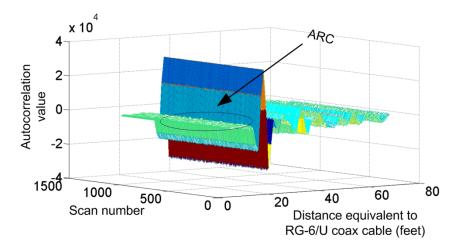

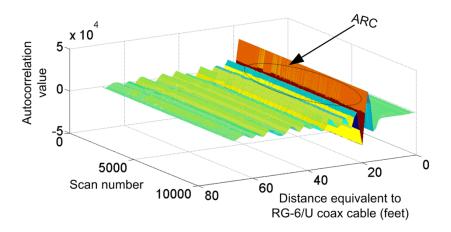

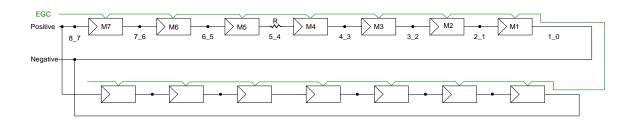

|    | 4.1 ARC Fault Detection: Intermittent Scan                         | 98  |

|    | 4.2 Open Fault Detection                                           | 100 |

|    | 4.3 Impact of Fault Resistance                                     | 101 |

|    | 4.4 Conclusions                                                    | 102 |

|    | 4.5 References.                                                    | 102 |

| _  |                                                                    |     |

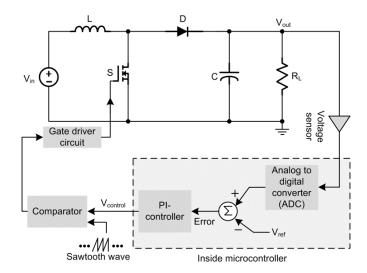

| 5. | RELIABILITY ANALYSIS AND PERFORMANCE DEGRADATION OF A              |     |

|    | BOOST CONVERTER                                                    | 108 |

|    | 5.1 Reliability Estimation of a Boost Converter                    | 111 |

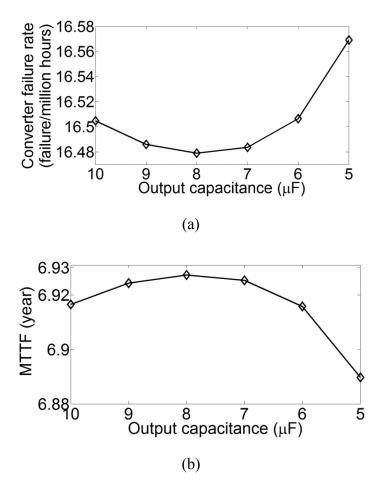

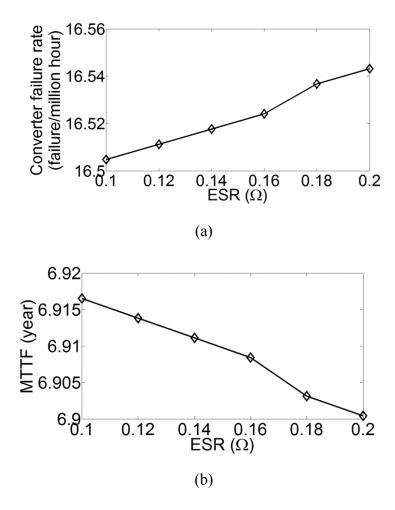

|    | 5.2 Effect of Variation in Different Component Parameters          | 111 |

|    | 5.2.1 Effect of Variation in $R_{DS(ON)}$                          | 114 |

|    | 5.2.2 Change in Capacitance (C) and ESR                            |     |

|    | 5.3 Sample Reliability Model: A Test Case                          |     |

|    | 5.3.1 Change in MOSFET ON-resistance $(R_{DS(ON)})$                | 117 |

|    | 5.3.2 Change in Capacitance $(C)$                                  | 118 |

|    | 5.3.3 Change in ESR of the Output Capacitor                        | 119 |

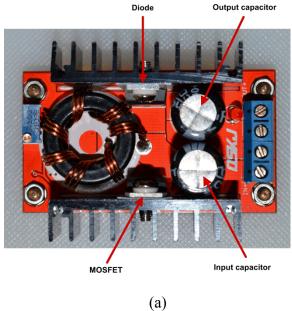

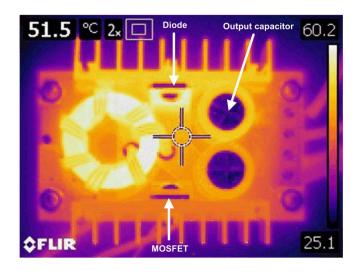

|    | 5.4 Experimental Analysis                                          |     |

|    | 5.5 Conclusions and Future Work                                    |     |

| 5.6 References | 122 |

|----------------|-----|

| 6 CONCLUSIONS  | 139 |

### LIST OF TABLES

| 2.1 | Different types of ground fault detection methods                                                | 4(  |

|-----|--------------------------------------------------------------------------------------------------|-----|

| 2.2 | DC rating of PV inverter versus maximum GFDI fuses rating                                        | 40  |

| 2.3 | Summary of different PV faults detection techniques                                              | 41  |

| 2.4 | Summary of different PV fault locating techniques.                                               | 43  |

| 3.1 | Specification of a PV module used in the test setup (at 1000W/m², 25°C cell temperature)         | 75  |

| 3.2 | Specification of a 100W PV module used inside the lab setup (at 1000W/m², 25°C cell temperature) | 75  |

| 4.1 | Area under absolute autocorrelation difference plot for different fault resistances              | 104 |

| 5.1 | Circuit parameters of the boost converter                                                        | 126 |

| 5.2 | Different parameters of the experimental tests with the commercial boost converter.              | 127 |

| 5.3 | System failure rate for characteristics variation of $R_{DS(ON)}$ , $C$ and $ESR$                | 128 |

### **ACKNOWLEDGEMENTS**

This dissertation presents a significant portion of my graduate school research and it is a pleasure to me to mention the contribution of all my mentors, collaborators, friends and family members that have made this journey possible.

First and foremost, I wish to thank my advisor, Dr. Faisal Khan. He has been extremely supportive since the days I started working at the Power Engineering and Automation Research Laboraory (PEARL). He helped me to come up with the thesis topic and helped me during the most difficult times during my research. He always gave me the moral support and the freedom I needed to move on. I am grateful to him for allowing me to present our research work to different research groups and organizations such as Siemens, Sandia National Laboratories and so on.

My thesis committee guided me through all these years. Thank you to Dr. Marc Bodson, Dr. Rajesh Menon, Dr. Jeffrey Walling, Dr. Thomas Schmid and Dr. Sanford Meek for being on the committee. Professor Marc Bodson has been very helpful, not only in my research but also in providing various academic supports. I would like to thank Professor Rajesh Menon and Professor Cynthia Furse for their advice and suggestions in my research in the field of photovoltaic systems.

I would like to acknowledge Sandia National Laboratories (SNL) for the support of my research through the Department of Energy (DOE). Jay Johnson and Jack Flicker from SNL have always been very helpful in reviewing my work and suggesting to me future developments.

I have always been blessed with many true friends and relatives. I would like to thank all of them, especially all my group members in PEARL who have always been helpful to me.

Finally, I would like to acknowledge immense inspiration from my mother and my father throughout my life. They have taught me the true meaning of education and advised me to be a good person in life irrespective of all successes and failures. I would like to thank my beloved wife for all the supports and inspiration she gave me during my PhD. I believe that this journey would have been incomplete without her.

### CHAPTER 1

### INTRODUCTION

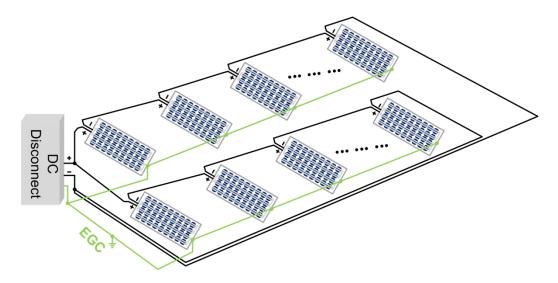

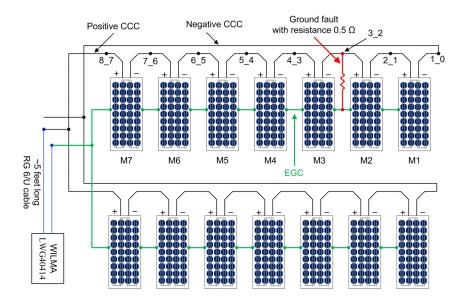

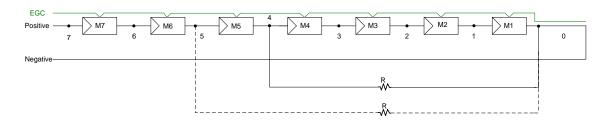

Photovoltaic (PV) installation throughout the world has been increasing exponentially, and the total installed capacity of PV power globally was exceeded 136 GW. At least 37 GW has added in the year of 2013, which represents an increase of about 35% in total capacity [1]. This source of renewable energy will ensure a more sustainable environment in the future, and many larger PV plants (50 MW) are under construction in different countries. Grounding of PV plants is an important safety issue for both the maintenance workers and the power plant itself. Besides the current carrying conductors (CCCs), a PV array has several noncurrent carrying conductors (NCCs) such as module frames, mounting racks, metal enclosures, distribution panels, the chassis of end-use appliances and power converters, etc. All these NCCs are connected through a grounding cable called "equipment grounding conductor (EGC)," and the use of EGC is mandated by National Electrical Code 690.43 regardless of the nominal voltage of the PV system to avoid any potential electric shock to any living beings [2] - [6].

One of the CCCs can be connected to the EGC using ground fault detection and interruption fuse (GFDI) to detect the presence of any accidental circulating current path, and this is termed as system grounding. PV arrays can be divided into two types based on the type of grounding implemented: grounded and ungrounded PV systems [4] [5]. PV

systems with system grounding are known as grounded, and these are more common in the USA. A ground fault occurs if there is any accidental low impedance current path established between a CCC and the EGC/earth. Ground faults may result in a high current flow through the EGC that may exceed the rating of the EGC and initiate a fire [7] - [20].

A similar situation arises when two points on the PV array are connected together through a finite impedance by accident and this type of fault is known as a line-to-line fault. In addition to establishing unintentional solid contacts in PV array, there might be some arc created inside the PV array due to insulation damage. This is called an arc fault and arc faults are one of the major reasons that fires are initiated. Detail of the ground, line-to-line and arc faults, limitations of the existing fault detection and mitigation techniques, together with a review of other analytical and instrument-based techniques proposed in the literature are discussed in Chapter 2.

A PV ground fault detection and locating technique based on spread spectrum time domain reflectometry (SSTDR) is presented in Chapter 3. This chapter covers the basic concepts of SSTDR, the proposed algorithm, advantages and limitations of the proposed fault detection and locating algorithm, the impact of different parameters such as center frequency of the SSTDR, fault resistance, number of parallel strings, operation under different light intensity and double ground fault. Chapter 4 describes the applications of SSTDR in line-to-line and arc fault detection in PV array. These results are so far the most comprehensive investigation of fault detection in PV arrays using SSTDR.

In addition to fault detection in PV arrays, SSTDR can be used for condition monitoring of PV converters. It has been demonstrated in [21] [22] that SSTDR can be used for determining the level of degradation of power metal oxide semiconductor field

effect transistors (MOSFETs), insulated gate bipolar transistors (IGBTs) and electrolytic capacitors in live power converters. Moreover, several real-time methods to estimate the state of health of power converters have been proposed in [23] – [30]. Reference [23] proposed a real-time monitoring of capacitor's equivalent series resistance (ESR) based on the power dissipation across the capacitor and the capacitor current. Capacitor voltages and currents are continuously monitored to determine the power dissipation. Junction temperature of power devices is directly related to the operating states of the inverter. An online monitoring method was presented in [24] using the junction temperature of power devices in a voltage source inverter. Online fault diagnosis methods in power electronic drives were described in [25] by measuring the capacitor *ESR*, MOSFET  $R_{DS}$  and  $V_{CE(sat)}$  of IGBT. *ESR* was calculated from the capacitor's voltage and current.  $R_{DS}$  was calculated from the corresponding ripple voltage and ripple current of the MOSFET.

Other online approaches for system health monitoring include data from the current sensors and relays of the protection system, monitoring power loss in different components of the power converter and frequency response [26]. Monitoring solder joint fatigue in power modules using the "case above ambient temperature" (CAAT) was proposed in [27]. The CAAT was measured using a two channel thermometer, and the module power loss was calculated using CAAT. Power loss is directly related to thermal resistance, which is an indicator of aging. An online fault diagnosis technique in DC-DC converters was proposed in [28] by calculating the *ESR* of the DC bus capacitor. *ESR* was calculated from the input current and the output voltage ripple of the converter. In reference [29],  $R_{DS}$  of power MOSFETs was calculated as the ratio of drain-source

voltage ( $V_{DS}$ ) and drain current ( $I_D$ ) during the on-state. Reference [30] proposed an online diagnosis method considering the variation in parasitic/internal resistors of components in a DC-DC converter. However, this diagnosis method is applicable to diagnose the entire system, not individual components.

A reliability centered maintenance (RCM) scheme that uses data of device degradation or characteristics parameter variation is proposed in Chapter 5. In addition to the proposed time-dependent reliability analysis, the complex interdependence of characteristic parameters, ambient condition, and operating point in closed loop converters is investigated in detail.

### 1.1 References

- [1] Gaëtan Masson *et al.*, "Global market outlook for photovoltaics 2014-2018," European Photovoltaic Industry Association, Onehemisphere, Sweden, March 2014.

- [2] National Electrical Code(R) (NEC(R)) Handbook, 2011 Edition, National Fire Protection Association, Inc., Quincy, MA.

- [3] National Electrical Code(R) (NEC) and Handbook Set, 2014 Edition, National Fire Protection Association, Inc., Quincy, MA.

- [4] W. Bower and J. Wiles, "Investigation of ground-fault protection devices for photovoltaic power system applications," in *Proc. Twenty-Eighth IEEE Photovoltaic Specialists Conference*, 2000, pp.1378-1383.

- [5] W. I. Bower and J. C. Wiles, "Analysis of grounded and ungrounded photovoltaic systems," in *Proc. IEEE First World Conference on Photovoltaic Energy Conversion*, Dec 1994, pp. 809-812.

- [6] Tom Markvart and Luis CastaÑer, "*Practical Handbook of Photovoltaics*," Elsevier Science, Amsterdam, 2003, ISBN 9781856173902.

- [7] M. K. Alam *et al.*, "A Comprehensive Review of Catastrophic Faults in PV Arrays: Types, Detection and Mitigation Techniques," submitted for publication.

- [8] M. K. Alam et al., "PV ground-fault detection using spread spectrum time domain

- reflectometry (SSTDR)," in *Proc. IEEE Energy Conversion Congress and Exposition (ECCE)*, Sept. 2013, pp. 1015-102.

- [9] Ye Zhao and Robert Lyons Jr., "Ground-Fault Analysis and Protection in PV Arrays", in *Photovoltaic Protection*, note 1, issue 1, 2011, pp. 1-4.

- [10] Ye Zhao, "Fault Analysis in Solar Photovoltaic Arrays", M.S. thesis, Dept. of Electrical and Computer Engineering, Northeastern University, Bostton, MA, 2010.

- [11] M. K. Alam *et al.*, "PV faults: Overview, modeling, prevention and detection techniques," in *Proc. IEEE Workshop on Control and Modeling for Power Electronics (COMPEL)*, June 2013, pp.1-7.

- [12] Ye Zhao *et al.*, "Fault analysis in solar PV arrays under: Low irradiance conditions and reverse connections," in *Proc. 37th IEEE Photovoltaic Specialists Conference* (*PVSC*), pp. 2000-2005, June 2011.

- [13] Ye Zhao *et al.*, "Fault evolution in photovoltaic array during night-to-day transition," in *Proc. IEEE 12th Workshop on Control and Modeling for Power Electronics (COMPEL*), pp.1-6, June 2010.

- [14] Ye Zhao *et al.*, "Line–line fault analysis and protection challenges in solar photovoltaic arrays," *IEEE Transactions on Industrial Electronics*, vol. 60, no.9, pp. 3784-3795, Sept. 2013.

- [15] Neelkanth G. Dhere and Narendra S. Shiradkar, "Fire hazard and other safety concerns of photovoltaic systems" in *Proc. SPIE 8112, Reliability of Photovoltaic Cells, Modules, Components, and Systems IV, 81120Q*, September 21, 2011.

- [16] Neelkanth G. Dhere and Narendra S. Shiradkar, "Fire hazard and other safety concerns of photovoltaic systems", *J. Photon. Energy*, 2(1), pp. 022006-022006, Dec. 2012.

- [17] J. Flicker and J. Johnson, "Analysis of fuses for 'blind spot' ground fault detection in photovoltaic power systems," Solar America Board for Codes and Standards Report, June 2013.

- [18] J. Flicker and J. Johnson, "Photovoltaic ground fault and blind spot electrical simulations," Sandia National Laboratories, Albuquerque, NM, Technical Report SAND2013-3459, June 2013.

- [19] B. Brooks (Feb/Mar 2011). *The Bakersfield Fire: A Lesson in Ground-Fault Protection*. SolarPro., Issue 4.2. Available: http://solarprofessional.com/articles/design-installation/the-bakersfield-fire-a-lesson-in-ground-fault-protection.

- [20] B. Brooks, "The Ground-Fault Protection Blind Spot: Safety Concern for Larger PV Systems in the U.S.," Solar American Board for Codes and Standards, January 2012.

- [21] M. S. Nasrin, F. H. Khan and M. K. Alam, "Real time monitoring of device degradation in power converters using SSTDR assisted impedance matrix," *IEEE Transactions on Power Electronics*, vol.29, no.6, June 2014.

- [22] M. S. Nasrin and F. H. Khan, "Characterization of aging process in power converters using spread spectrum time domain reflectometry," in *Proc. IEEE Energy Conversion Congress and Exposition (ECCE)*, pp. 2142-2148, Sept. 2012.

- [23] T. Wiesinger and H. Ertl, "A novel real time monitoring unit for PWM converter electrolytic capacitors," in *Proc. IEEE Power Electronics Specialists Conference*, pp. 523-528, June 2008.

- [24] U. Franke *et al.*, "Online diagnostics and condition monitoring in voltage source inverters," in *Proc. European Conference on Power Electronics and Applications*, pp. P.1 P.6, 2005.

- [25] J. M. Anderson et al., "An on-line fault diagnosis method for power electronic drives," in Proc. IEEE Electric Ship Technologies Symposium (ESTS), pp. 492-497, April 2011.

- [26] J. Morroni *et al.*, "Online health monitoring in digitally controlled power converters," in *Proc. IEEE Power Electronics Specialists Conference*, pp.112-118, June 2007.

- [27] Dawei Xiang *et al.*, "Monitoring solder fatigue in a power module using the rise of case-above-ambient temperature," in *Proc. IEEE Energy Conversion Congress and Exposition (ECCE)*, pp. 955-962, Sept. 2010.

- [28] A. M. R. Amaral, and A. J. M. Cardoso, "Using input current and output voltage ripple to estimate the output filter condition of switch mode DC/DC converters," in *Proc. IEEE International Symposium on Diagnostics for Electric Machines, Power Electronics and Drives*, pp. 1-6, Sept. 2009.

- [29] J. R. Celaya *et al.*, "Prognostics approach for power MOSFET under thermal-stress aging," in *Proc. Annual on Reliability and Maintainability Symposium (RAMS)*, pp. 1-6, Jan. 2012.

- [30] Tae-Jin Kim *et al.* "A diagnosis method of DC/DC converter aging based on the variation of parasitic resister," in *Proc. International Telecommunications Energy Conference (INTELEC)*, pp. 18-22, Oct. 2009.

### **CHAPTER 2**

# CATASTROPHIC FAULTS IN PV ARRAYS: TYPES, DETECTION AND MITIGATION TECHNIQUES

Recent fire events initiated by PV arrays suggest the necessity of understanding catastrophic failures in PV systems [1] - [3]. Shutting down the PV generation system under different fault conditions requires different mitigation techniques and, in most cases, requires prior knowledge of the type of the fault. This chapter discusses the major faults that may result in damage to a PV array (catastrophic faults), possible causes and detection schemes of these faults and protection techniques.

Among the numerous possible faults such as ground fault, line-to-line fault, hot spot formation, polarity mismatch, arc fault, open fault, bypass diode failure, dust/soil formation, etc. in a PV array, ground fault, line-to-line and arc fault are reported to be the major reasons behind catastrophic failures resulting in electrical fires. This chapter studies the electrical behavior of the PV system during those faults, possible causes for any failure, and the state-of-the-art detection and mitigation techniques for each type. In each fault case, there are specific technical challenges to detection and mitigation. Standards are reviewed and recommendations are provided to ensure more reliable PV arrays. This chapter does not cover faults in the rest of the components of a PV system (AC isolation failure, inverter failure, DC signal injection to the AC side of the inverter,

faults inside battery modules, etc.).

### 2.1 PV Ground Faults

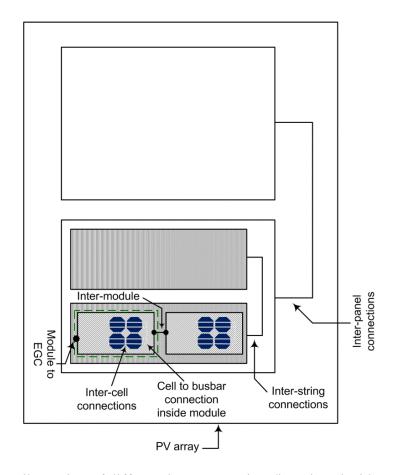

Typically, a PV array has several exposed noncurrent carrying (NCC) metals/conducting parts (module frames, mounting racks, metal enclosures, distribution panels, the chassis of end-use appliances and power converters, etc.) [4]. These conductors do not carry any current during normal operation. However, there is a potential risk of electric shock hazard from these exposed NCC conductors when an electrical connection is established between the current carrying conductors (CCCs) and NCC conductors due to a fault (e.g., corrosion, loss or melting of insulation, wire cut-off, wrong wiring, etc.). Therefore, all these NCC conductors are connected together to the ground or earth through a current carrying conductor termed a "equipment grounding conductor" (EGC). This is illustrated in Figure 2.1 as green lines.

Equipment grounding is required by National Electrical Code Article 690.43 to protect people and other living animals from being electrocuted [5]. Similarly, any accidental connection between a CCC and EGC/earth can cause significant current flow to the ground circuit, known as a "ground fault". Therefore, proper grounding is required for any electrical system to provide adequate personnel and system safety in the case of one or multiple ground faults. The voltage and current limit for a living being to be electrocuted is proposed as 75 V and 100 mA [6], and to avoiding a potential electric shock, equation (2.1) should be met:

$$R_A I \le U_L \quad for \quad I < I_d$$

(2.1)

where  $R_A$  is the resistance of the living being exposed to potential electrical shock with a current I from the point of contact at higher potential to the ground. The maximum and average estimated resistances for the human body are approximately 1000  $\Omega$  and 650  $\Omega$  [4] [6].  $I_d$  and  $U_L$  are 100 mA and 75 V, respectively.

### 2.1.1. Grounded and Ungrounded PV Systems

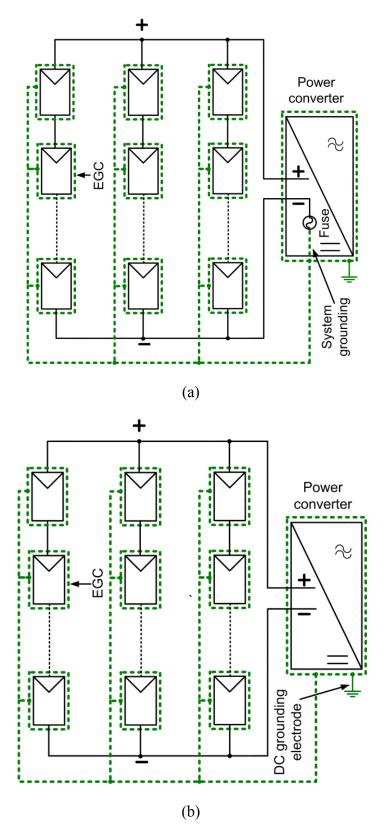

Grounding practices in PV systems vary depending on the operating voltage, size of the plant, type of installation (ground-mount, roof-top, building mounted etc.), and geographic location. Any PV system with system voltage higher than 50 V requires ground fault protection according to US National Electrical Code (NEC) Art. 690.5. Typically, U.S. PV arrays have an electric connection between ground and one of the CCCs through a ground-fault detection and interruption (GFDI) fuse, known as "system grounding." However, there are alternative ground fault protection schemes, which are more common outside the U.S. including residual current monitoring devices (RCD) and DC insulation resistance (Riso) measurements. These ground fault protection systems often are used on ungrounded ("floating") PV systems which do not have a connection between a CCC and ground. Differences in grounded and ungrounded systems are illustrated in Figure 2.2.

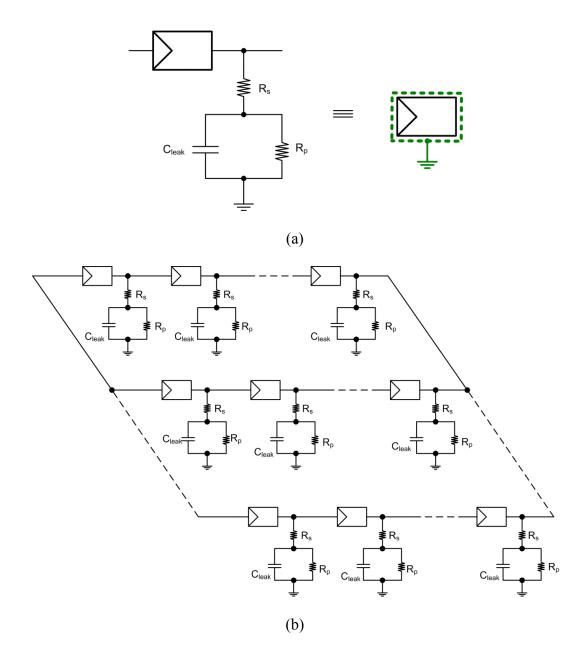

In order to analyze different ground faults, a complete electrical model of a PV array is necessary. Unfortunately, electrical parameters vary between PV systems due to variations in the construction of PV modules (e.g., dimension, material, and ground connection), site (grounded, roof-top, building mounted, etc.), physical layout, etc. Therefore, a generic RC model for a PV array from CCCs to ground is proposed in [7], as

shown in Figure 2.3.  $R_s$ ,  $R_p$  and  $C_{leak}$  are series insulation resistance, parallel insulation resistance and leakage capacitance of each module. In addition, long connecting wires may be required in large PV arrays to connect PV panels to the central inverter. These connecting wires add additional impedances [8].

An unintended effect of GFDI protection schemes is that it provides an electrical path for the leakage current to return to the PV conduction path through the ground fault detection fuse. The leakage current is highly dependent on relative humidity, temperature, array voltage, and size of the array [6] - [8]. Moreover, impedance from a CCC to ground in an ungrounded system varies with different meteorological variables (temperature, humidity, etc.), and the design of fault detection devices for both ungrounded and grounded systems requires a safe estimation of detection parameters to avoid system shutdown under normal operating conditions.

### 2.1.2. Reasons for Ground Fault

A ground fault establishes an unintentional low impedance path between one of the CCCs and the ground/earth, and a large fire in a PV array often destroys the origin of the fault. Several potential reasons for ground faults have been discussed in [4] [9] - [11], and summarized here:

- 1) Cable insulation damage during the installation, due to aging, impact damage, water leakage, and corrosion

- 2) Ground fault within the PV modules (e.g., degraded sealant, water ingress)

- 3) Insulation damage of cables due to chewing done by rodents

- 4) Accidental short circuit inside the PV combiner box, often at the time of

### maintenance

If a ground fault remains undetected, it may generate a DC arc within the fault and cause a fire hazard.

### 2.1.3. Ground Fault Detection Techniques

Depending on whether a PV system is ungrounded or grounded, and considering the geographic location, several ground fault detection devices are commercially available to be used with PV installations. They are listed in Table 2.1.

### 2.1.3.1 GFDI Fuse

System grounding provides an intentional circulating path for the ground current during a fault condition and the fuse melts if the current is higher than a safe threshold current limit. If the fuse is cleared (opened), the inverter needs to be turned OFF immediately to isolate the PV array from the rest of the power system, and fault inspection becomes possible. In most grounded PV systems, a fuse with 1-5 A rating is installed inside the PV inverter. UL 1741 sets the upper limits for the ground fault fuse ratings as depicted in Table 2.2. A sensor inside the inverter checks the fuse continuity and shuts down the system in the presence of any ground fault.

The fuse rating needs to be high enough to avoid nuisance tripping due to leakage current, and it should be low enough to trip during actual ground faults. An estimation of leakage current for modules operating at 600V that meet the standard UL 170 [12], IEC 61646 [13] or IEC 61215 [14] has been provided in [8]. It has been estimated that the maximum leakage current for 1.2 m2 crystalline Si modules is 11 μA/kW for a 7-module

string, which can result in 56 mA of leakage current from a 500kW array. Compounding this challenge, the sensitivity of the GFDI fuse is influenced by the leakage current of the PV array, and several papers have investigated the effect of different parameters such as ambient temperature, relative humidity, salt mist, electromagnetic interference (EMI), and resistance of the grounding conductor on the leakage current [6]-[8] [15]-[19].

An ungrounded PV array poses shock hazard in the form of capacitive discharge, and such shock hazards can be avoided by using resistive grounding. Distributed capacitances in a grounded PV array do not pose such danger due to the system grounding.

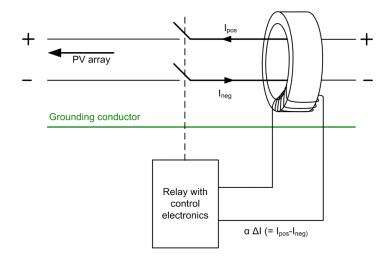

### 2.1.3.2 Monitoring Residual Current

Residual current monitoring devices (RCDs) can sense the difference between the current entering and leaving PV system through the positive and negative CCCs. A simple schematic diagram of an RCD is shown in Figure 2.4. RCDs, in general, sense the presence of an alternate current path through the presence of any residual magnetic field and can open the current carrying conductors using switching relays. RCDs can be installed for each string or for the entire array [1]. However, the sensitivity of an RCD should be set by considering the leakage current of the PV modules. In [6], it is recommended that the set point of differential current (\(\Delta I\)) at which an RCD signals a ground fault should be chosen according to equation (2.2).

$$\Delta I \ge C_{sl} \times I_{leakmax} \tag{2.2}$$

In Figure 2.4,  $I_{leak,max}$  is the maximum leakage current that may result from the PV

modules covered by the RCD channel, and the multiplier  $C_{sl}$  (>1) is used to avoid the nuisance tripping that may result from external noise, measurement error, etc. RCDs can be installed in both grounded and ungrounded PV systems to protect them against ground and other line-to-line faults.

### 2.1.3.3 Insulation Monitoring Device

An insulation monitoring device (IMD) measures the resistance between both CCCs and ground and can alarm the system if the resistance falls below a preset value  $(R_{fault\_threshold})$  [6] [8]. IMDs can be implemented for detecting ground fault in a grounded system by disconnecting the GFDI fuse at the time of taking measurements, generally at the beginning of the day before the inverter is connected to the array.

Since the insulation resistance is influenced by the ambient conditions, a nuisance trip threshold  $R_{fault\_threshold}$  is recommended in [6] and shown in (2.3).

$$R_{fault\_thre\,shold} \le C_{sr} \times R_{iso\_min} \tag{2.3}$$

$R_{iso\_min}$  is the minimum insulation resistance that may result in the PV array under any climatic condition,  $C_{sr}$  (<1) is another safety factor.

### 2.1.4 Blind Spot and Double Ground Fault

A fuse has a threshold current for detecting a ground fault, and the fault may remain undetected if the resultant ground fault current is less than this threshold limit. If a ground fault occurs on a grounded current carrying conductor or at a location in the array where

the potential to ground is small, the fault current is very small. In those cases, a fault can occur that does not trip the GFDI. This gap in traditional ground fault detection fuses is known as the "blind spot" [1] [2] [8] [18] [19]. Any ground fault that results in a blind spot poses a significant risk, because the ground fault in the array remains undetected for an indefinite time, unless otherwise deactivated. A blind spot is extremely important for the safety of the PV array, since any subsequent ground fault will result in a fault current that may bypass the GFDI fuse. The entire array current may flow through the grounding wire, resulting in the possibility of severe damage to the array.

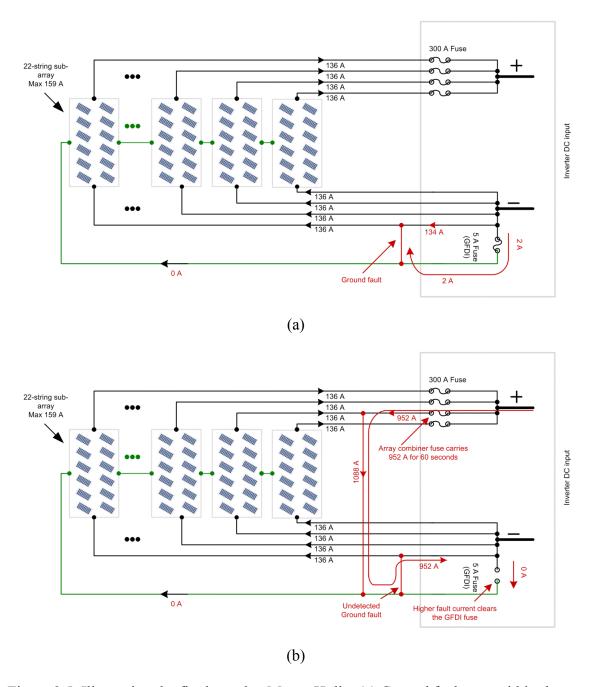

Two well-investigated ground fault events, on April 5, 2009, in Bakersfield, California, and April 16, 2011, in Mount Holly, North Carolina resulted from undetected ground faults within a blind spot range, followed by another ground fault that allowed a large amount of current to flow through the grounding wire [1] [21]. The example of Mount Holly fire, as depicted here in Figure 2.5, is an illustration of double ground fault. A similar incident occurred in the Bakersfield fire. The first ground fault produced a current through the GFDI fuse which had fault current amplitude below the threshold limit and the fault remained undetected for an undetermined period of time. The next ground fault resulted in a flow of an estimated 952 A through the EGC, which ignited a fire before it was cleared by the over current protection fuse.

### 2.1.5. Limitations of Ground Fault

### **Detection Techniques**

In general, ground fault detection devices are based on passive fuses, isolation impedance measurements, or differential current measurement methods, and these

devices suffer from several limitations as discussed here [2] [22]:

- 1) Ground-fault may result within the blind spot range due to low insolation e.g., during the night, on a cloudy day, at the time of partial shading, etc. and remain undetected.

- 2) A double ground fault may be established during the night and may result in high fault current and arcing inside the array during daytime.

- 3) Residual current monitoring devices may be affected by external electrical noise and may result in nuisance tripping of the system [23].

- 4) If not designed properly, leakage current can deceive the GFDI and IMD devices, especially during the presence of high relative humidity in large PV systems [16].

- 5) The leakage current may flow in the opposite direction of the ground fault current, reducing the magnitude of the current through the GFDI fuse [1] [18]. This may lead to an undetected ground fault.

### 2.1.6. I-V Curve Analysis and Effect of

### MPPT on Ground Fault

Electrical characteristics of a PV array are a nonlinear function of several parameters, i.e., insolation, temperature, humidity, module mismatch, etc., and a change in any of these several factors may result in a change to the array I-V characteristics similar to that caused by a ground fault. In some cases, the maximum power point tracker (MPPT) responds to the ground fault in such a way that it may diminish the onset fault current or the back fed current, making fault detection more challenging.

Effects of the ground fault on the I-V curve of the PV array has been discussed

extensively in [10] [20] [24]-[26], and a summary is presented here.

- 1) The fault current amplitude through the GFDI fuse depends on the location of the ground fault in the PV string. The higher the voltage at the fault location, the higher the ground fault current that results.

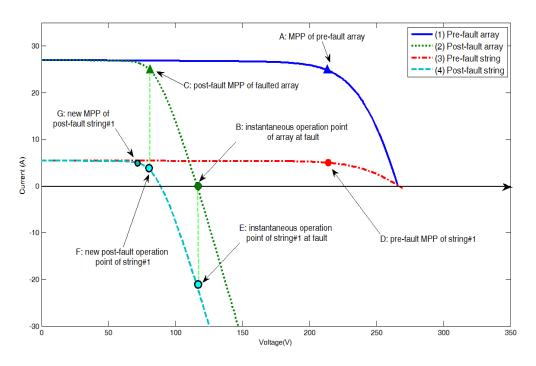

- 2) If the fault is uninterrupted in a grounded array, the maximum power point tracker (MPPT) will set the new operating power point lower than the level before fault (if the fault is not on the grounded CCC) with a small reduction in operating current (Figure 2.6). Therefore, a permanent reduction in output power can be a sign of a ground fault [10].

### 2.2. Line-to-Line Faults

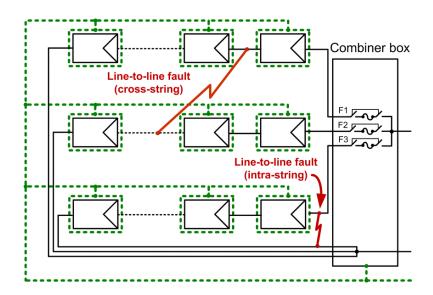

An unintentional low impedance current path between two points in a PV array is referred to as a line-to-line fault. This fault may occur within the same string or between two strings, as depicted in Figure 2.7 [10] [24] - [26]. A line-to-line fault may reverse the current flow through the faulty strings. The maximum current that can flow through the faulty string of a PV array with n number of strings connected in parallel is (n-1) × (short circuit current of each string). However, the amplitude of this fault current depends on the potential difference between the points establishing the fault before the fault occurs. The higher the potential difference, the higher the fault current that results. Line-to-line faults are, in general, cleared by over current protection devices (OCPDs), i.e., string fuses, if the fault current is higher than the rated current of the OCPD which is mandated to be at least 56% greater than the string short circuit current by the NEC.

The effects of MPPT, irradiance, and series blocking diodes on PV arrays with

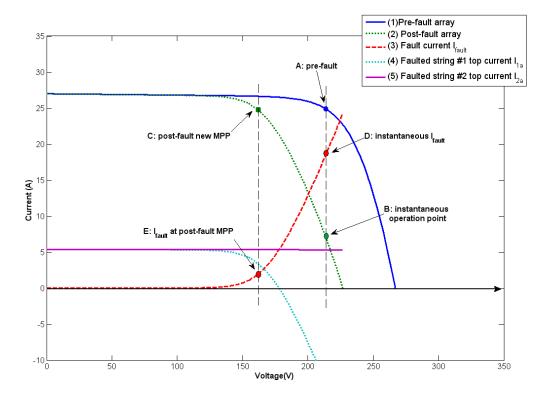

different line-to-line faults have been explained in [26]. In most cases, a line-to-line fault under full illumination results in an open circuit due to melting of the OCPD and the fault can be located through inspection of the affected strings. However, if the line-to-line fault occurs under low illumination (e.g., during the night, night-to-day transition, during morning, day-to-night transition), the current through the affected string/strings is not large enough to melt the OCPD, and the fault may remain undetected until sufficient illumination is present to clear the OCPD. Moreover, the MPPT operation of the inverter may move the operating point to a new position on the I-V curve such that the fault current amplitude decreases over time and remains undetected.

This is illustrated in Figure 2.8 [10]. In this figure, if a line-to-line fault occurs while the PV array is operating at point A and the resultant fault current is less than the melting current of the OCPF ( $I_{melt\_OCPF}$ ), the fault remains undetected, and the MPPT moves the operating point to C where the array seems to be operating at normal condition with lower output power. These types of line-to-line faults will remain undetected for an indefinite time, and thereby any degradation in power output from a PV generator for a long duration requires thorough investigation of the PV array for a line-to-line fault. The use of blocking diodes makes the fault detection more challenging since it prevents the current flow through the affected modules in the reverse direction [10], and any short failure of diodes in absence of an OCPD can be dangerous and may cause a fire due to a high fault current through the PV modules.

### 2.3. PV Arc Faults

A PV array consists of numerous connections/junctions throughout the array, as depicted in Figure 2.9. A current path may be established through the air via arcing due to a discontinuity in the current carrying conductors or insulation breakdown in adjacent current carrying conductors. A series arc fault occurs when there is an arc fault due to a discontinuity in any of the CCCs resulting from solder disjoint, cell damage, corrosion of connectors, rodent damage, abrasion from different sources, etc. Parallel arc faults in adjacent CCCs occur mostly due to insulation breakdown. Any form of arc fault is harmful and potentially dangerous to the PV array since it may initiate a fire, especially in the presence of any flammable substance present in close proximity of the PV arc [27]-[32]. Unlike AC systems, the current through the DC arc does not possess a periodic zero crossing and, therefore, it is much more likely that an arc in a PV system will result in a sustained arc compared to an AC generation system [33] [35]. The National Electrical Code® (NEC)-2011 requires a series arc-fault protection device, known as an arc-fault circuit interrupter (AFCI), in any rooftop PV array with DC operating voltage equal to or higher than 80 V [33] [34]. The 2014 NEC expands this requirement to all PV systems above 80 V [36].

### 2.3.1. Physics of Arc

The dielectric constant of an insulating material defines the maximum electric field that the material can withstand before breakdown occurs. A sustained arc results if the energy produced inside the arc is higher than the energy lost due to thermal radiation, light, sound, etc. The dielectric constant of air is approximately 3 V/µm, and it depends

on surrounding pressure, humidity, presence of impurities, etc. [28] [37]. In addition, the initiation/sustainability of an arc also depends on the size/shape of the electrodes, air gap between the electrodes, and presence of chemical products from the arc (melted metals from electrodes, melted/vaporized polymers from glass, wire insulation, etc). An arc is initiated across an air gap when high electric fields ionize air molecules and accelerate the ion towards the opposite electrode. This results in high-velocity particle collisions, which generate additional charged particles. This runaway ion generation converts the normally insulating air medium into a conductive medium.

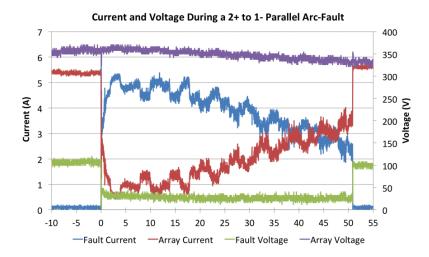

The voltage-current relationship of an arc is highly nonlinear. The transient behavior of a DC parallel arc in a PV array connected to an inverter undergoing MPPT suggests a decrease in voltage and increase of current during the onset of an electric arc, as depicted in Figure 2.10. An arc can be modeled as simple resistor at steady-state with the resistance being a function of the arc current, voltage, and length [38]. Different V-I characteristics and model equations for a DC arc have been summarized in [39]. Yao *et al.* has proposed a modified Paukert form for describing the V-I relationship of arc in PV system, as shown in equation (2.4) [38]:

$$V_{arc} = \frac{a + bL}{I_{arc}^{c + dL}} \tag{2.4}$$

Here, a,b,c,d are constants while  $V_{arc}$ ,  $I_{arc}$ , L are arc voltage, current, and length.

Two other significant aspects of PV arc faults are arc temperature and burn-through time of CCC insulation. Burn-through time depends on the temperature, power density, and type of the material considered. Arc temperatures of 6000° K and above can vaporize

most metals and adjacent materials, and radiative heating can ignite flammable materials near the arc fault. Therefore, use of fire-retardant materials may help extinguish the arc and abate subsequent fire hazards in a PV array [28].

### 2.3.2. Types and Reasons for Arc Faults

As shown in Figure 2.9, there are numerous interconnection/junction that exist in a PV array (cell to cell, cell to bus bar, module to module, bypass diode parallel to solar cells, string to string, panel to panel, etc.). In addition, there are several interconnections that exist for mounting safety devices (OCPDs, DC disconnect switches, etc.). These connections are created through soldering, MC4 connectors, or screw terminals inside junction boxes. Any of these connections are potential places for arc fault initiation. Any insulation damage in the CCCs poses a risk of arc fault as well.

Arc faults are categorized as series and parallel categories depending on whether the current through the arc creates a new conduction branch in the existing PV array.

### 2.3.2.1. Series Arc Faults

Series arc faults are caused by any discontinuity in the existing current path of a PV array and may result from corrosion, thermal cycling, damage from rodents, extreme weather, etc. [28]. Degradation in solder joints, wiring or connections inside the junction box, loosening of screws, or incorrect crimping may increase the connection resistance. Increased operating temperature may result in thermal stress leading to accelerated aging or complete disconnection [33] [40].

It has been shown in [37] that a 5 µm separation of interconnect ribbon to busbar

connection inside a solar module can experience dielectric breakdown from the module's voltage. Only 0.4 mm<sup>2</sup> of arc region may produce enough heat within 2 seconds to shatter the glass and burn off the metal coating and other materials. As PV modules are considered to be very reliable and scheduled maintenance is not performed frequently, small signatures (discoloration of busbar, ribbons, edge of solar cells, small cracked region of glass, etc.) of arc faults may go unnoticed for some time [37] [41]. A well-reported product recall occurred for BP solar modules due to arc hazards from faulty cold soldering [40].

### 2.3.2.2. Parallel Arc Fault

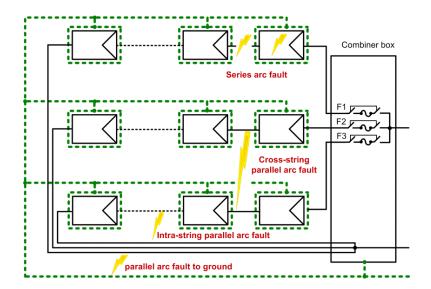

Parallel arc faults result in a current branch that does not exist under normal operation of a PV array, as depicted in Figure 2.11. Examples of such parallel arc faults are [33]:

- a) Intrastring parallel arc-fault: Parallel arc fault between two points on the CCCs of the same string.

- b) Cross-string parallel arc-fault: Parallel arc fault between two points on the CCCs of the two different strings.

- c) Parallel arc fault to ground: Parallel arc fault between one point on a CCC and another point at ground potential.

Parallel arc faults can result from insulation damage due to mechanical damage, aging, or wildlife [41], as well as previous series arc fault events [40].

### 2.3.2.3. Differentiating Between Series and Parallel Arc Faults

Series arc faults can be de-energized by opening the inverter terminals to stop the current flow, but this method will not be able to extinguish parallel arc faults. In parallel arc cases, opening the inverter terminals increases the electric field across the arc column, since the operating voltage is moved toward a higher voltage (open circuit voltage of the array), increasing the amount of current circulating through the parallel current. Therefore, it is extremely important to differentiate between the series and parallel arc fault for safe operation of a PV array [27] [33] [41] [42]. Different methods have been proposed in [27] [43] to distinguish series and parallel arc faults in a PV array:

- a) Parallel arc faults often result in a drop of array current and voltage, which does not occur in the case of series arc fault or usual irradiance changes. Therefore, a combination of arcing noise and change in current/voltage magnitude can be used as a method for differentiating between series and parallel arc faults.

- b) Forcing the operating point of a PV array close to the open circuit voltage will allow extinguishing the series arc fault, and any arc-induced noise at that point ensures the presence of a parallel arc fault.

- c) Installing arc-fault detectors (AFDs) at the string level and disconnecting the inverter without disconnecting the parallel strings can be used to select the presence of a parallel arc fault by observation of arc-induced noise.

- d) Opening the conduction path, thereby extinguishing all series arc-faults and rechecking for arc-fault noise to determine if the fault is a parallel fault [43].

Moreover, parallel arc faults can be detected similar to other line-to-line faults by comparing the differential string input/return current. The presence of differential current

along with arc-induced noise suggests the existence of a parallel arc fault [45].

### 2.3.2.4. Effect on PV Operation

The voltage drop across an arc can be subdivided into two components: voltage drop across the positive and negative electrodes and across the ionized/plasma medium. The sum of voltage drops across copper electrodes is 20 V to 30 V, and the voltage drop across the plasma depends on the gap length between the electrodes. Therefore, if the voltage across two copper plates is higher than 30V, there is a chance of arc initiation [40]. However, it is reported in [42] that the voltage and current across an arc in a PV string connected to an inverter changes rapidly due to the transient nature of the arc and the maximum power point tracking (MPPT) operation of the inverter.

One general trend to study the impact of steady-arc on PV is to model the arc as a resistance that may vary from near zero to 45  $\Omega$  [34] [38] [42]. Modeling series arc fault as a series resistance suggests a decrease in the fill factor and efficiency of the PV array. Moreover, it introduces mismatch losses among the parallel connected strings in an array. In general, the voltage drop across the arc increases with the increase in arc length, and thereby results in a substantial drop in efficiency [38].

Although the formation of parallel arc faults is unlikely compared to series arc faults, it poses significant threat to the safety of a PV array [40]. Parallel arc faults affect the PV array similarly to other line-to-line faults discussed in the previous section, although the presence of the arc fault adds additional high frequency components to the voltage and current signals.

### 2.3.2.5. Detection and Mitigation Methods

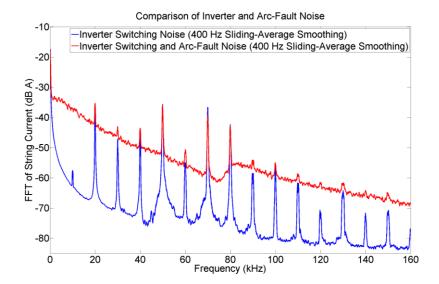

Arc in both DC and AC systems manifest similar frequency characteristics except the line frequency components in an AC arc [41] [44]. Solar arrays show more dynamic variation than conventional battery backed DC systems installed in automotive systems, due to the variation in solar irradiance, temperature, etc. Although arcs in a PV system are characterized by signatures in both the time and frequency domains, most arc detection techniques already developed for PV systems use frequency spectrum analysis of the voltage or current waveforms, and other complex analytical methods (e.g., wavelet transformation, neural network analysis, etc.) to avoid any nuisance tripping and unwanted down time [29] [38].

The frequency content of an arc is similar to pink noise and shows a 1/f relation (i.e., the amplitude of frequency content decreases with frequency) [34] [41]. The fast fourier transform (FFT) of the current signal of a PV string connected to an inverter with and without arc fault is shown in Figure 2.12. The switching frequency of the converter was 10 kHz. It is expected that analyzing the lower frequency content can be used for detecting arcs. However, frequencies below 1000 Hz are not recommended to avoid nuisance tripping due to signal variations from solar irradiance, partial shadows, movement of humans or vehicles, 50-120 Hz noise from the inverter, etc. [29].

Arcing frequency content above 500 kHz interacts with external RF noise sources and frequencies above 100 kHz contain less arcing energy, so these frequencies are generally not used in AFCIs. Unfortunately, most inverters, charge controllers and DC/DC converters have switching frequencies within the range of 10 kHz to 50 kHz [41] [45], and generate other harmonics and subharmonics. Therefore, it is not possible to develop a

detection technique based on one frequency component. The range of 1-100 kHz is considered to be the most suitable range for designing arc fault detectors and arc fault circuit interrupters (AFCIs) for PV plants irrespective of arc fault type (series or parallel) [29] [32] [34] [35] [45].

Another important aspect of designing an arc-safe PV system is the location and number of arc fault detectors (AFD) and circuit interrupters (AFCI). In general, AFD and AFCI are installed in the inverter in small PV systems and in the combiner box in large systems. However, this method suffers from the following limitations [34] [46] [52]:

- 1) The arc signal needs to propagate from the location of the arc to the location of the detector. The signal can be attenuated throughout the propagation path at numerous interconnections of the array. Moreover, some high frequency signals may be filtered out by the components of solar cells and other parasitics.

- 2) Long wiring runs present in a PV plant may work as an RF receiver and may capture signals from other sources to create false tripping of the AFCI.

- 3) Irrespective of the location of the arc in a string or adjacent strings, AFCIs installed inside the inverter/combiner box disconnects the entire array.

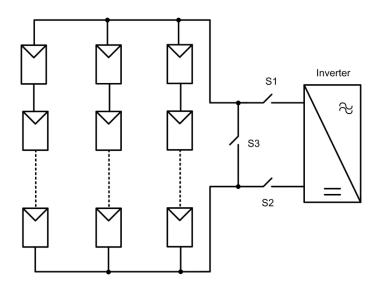

A possible switching scheme for extinguishing parallel arc fault is shown in Figure 2.13 [40]. Here, switches S1 and S2 are used for disconnecting the PV array from the inverter whenever the AFD detects a fault. This will extinguish all the series arc faults, while sustaining any parallel arc faults. If the arc noise still exists, the parallel arc fault can be extinguished by short-circuiting the positive and negative terminals using the switch S3. However, this might not be possible in large PV systems where multiple arrays are connected in parallel.

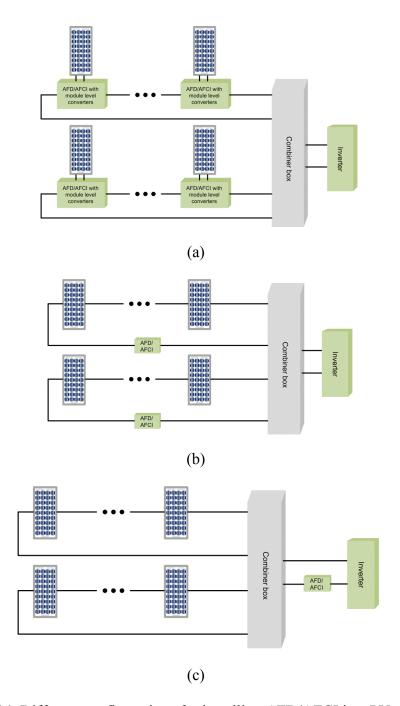

In order to optimize the accuracy, cost and annual production from a PV generation unit, the possibility of installing AFDs at three different locations: module-level, string-level, array-level are discussed in [31], as illustrated in Figure 2.14. In [47], it is reported that AFDs are able to detect faults irrespective of whether they are located at the string, between the combiner and recombiner, or at the central inverter of a 5 kW system. However, in larger PV systems, installing AFDs in recombiners might be affected by a serious attenuation issue. Therefore, AFDs can be installed in the combiner boxes and AFCI can be installed at the inverter or recombiner.

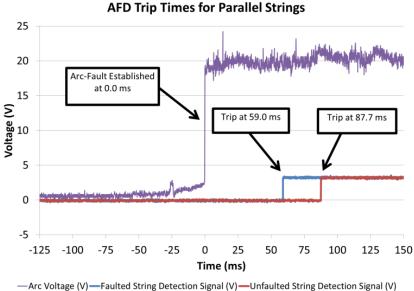

String level utilization of AFDs can disconnect the affected string or strings while the rest of the strings may operate uninterrupted. However, this is a more expensive option compared to array level protection and may suffer from "crosstalk" noise, where are noise from one string propagates to unaffected strings (Figure 2.15) [31]. An AFCI needs to be fast enough to de-energize the arc before any fire ignites and be robust enough to avoid nuisance tripping. In [31], it is reported that, in a two-string array, a false arc signature was detected in a nonarced string due to noise from a parallel faulty string within an average delay of 19.5 ms. However, it is expected that the performance of string level detection would be better with a large number of parallel strings since the arc energy will be lower in each healthy parallel string. Also, faster detection schemes might be effective for avoiding crosstalk noise [31].

Module level AFD/AFCIs seem to be more reliable (an expensive option) among all these mounting options and more appropriate for PV modules with DC/DC converters or micro-inverters [31] [40]. Moreover, it is possible to adapt hybrid structures where the AFDs are located at module/string/combiner and AFCIs are located at string/combiner/re-

combiner/central converter. A detailed comparison among all these structures in terms of cost and reliability require further investigation.

Parallel arcs to ground are most common, and it is expected that such faults might involve GFDI or OCPDs to operate. Moreover, the improved ground fault detection capabilities required by 2014 NEC will address the vast majority of parallel arc fault risks in large systems.

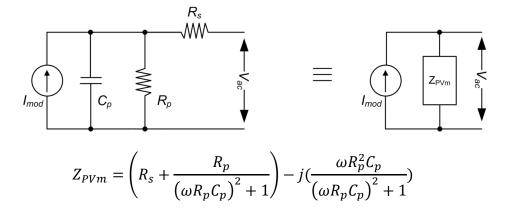

Understanding the propagation of arc noise through a PV array requires high frequency models for PV modules as described in [30] [48] [49], and a simplified equivalent AC circuit model for a PV module is shown in Figure 2.16.

We define,

$I_{mod}$  = photo-generated current of the PV module.

$R_s$  = series resistance

$R_p = R_{sh} \parallel R_d$

$R_{sh}$  = shunt resistance

$R_d(V)$  = dynamic resistance of diode

$C_p = C_D \parallel C_T$

$C_D$  ( $V,\omega$ ) = diffusion capacitance

$C_T(V)$  = transition capacitance

$V_{ac}$  = dynamic voltage

$\omega$  = signal frequency

The attenuation characteristics of a PV panel vary with solar irradiance and cell voltage. Therefore, the arc noise will be affected by a wide variation in solar irradiance/cell voltage during PV operation [29] [30] [48] [49]. Some arcing dangers are

inherent to regular operation of a PV plant, such as inverter operation during the morning or in the evening, low voltage shutdown resulting from clouds or partial shading, or contact arcing at junction boxes during maintenance operations. An intelligent AFCI should be able to avoid nuisance tripping in the above mentioned cases.

Other arc fault detection and mitigation techniques based on more complex signal processing techniques are discussed in section 2.4.

## 2.4. Other Analytical Solutions for Detection

## of PV Faults

This section summarizes methods proposed in the literature for detection, mitigation, and differentiation of different fault types besides the general techniques described in section 2.1-2.3. Most methods use different on-site measurement data such as recorded voltage/current, maximum power point, temperature, irradiance, power loss, fill factor, etc. to detect and classify faults using different numerical and data processing techniques [53]- [63].

A multilayer artificial neural network (ANN) based algorithm has been proposed in [53], where irradiance, cell temperature, voltage and current at maximum power point are used as inputs to estimate the voltage across each module of a two string array, which is used for detection and location of a short line-to-line fault. However, performance of the algorithm with other types of faults (ground or arc faults) has not been reported. Based on the PV array voltage, current, operating temperature and irradiance, a decision tree-based supervised technique is proposed in [54] to detect and classify four fault conditions: line-to-line fault with short circuit, line-to-line fault with 20  $\Omega$  resistance, open circuit fault

and partially shaded condition. Similar to other supervised learning algorithms, this method requires suitable training data for each faulty condition along with data from the PV array at normal operating conditions. Accuracy of this algorithm depends on the size of the tree and number of leaves used in the algorithm. In order to overcome the drawback of large training data, a graph-based semisupervised learning technique has been used in [55], with similar accuracy and less of a training data set due the self-training capability of the algorithm.

Less computation intensive fault detection techniques based on the variation in string currents of a PV array only are proposed in [56] [57]. Three different outlier detection rules, 3-sigma, Hampel identifier, and Boxplot are described in [56]. These methods do not require previous training data to detect line-to-line faults (short circuit and 20  $\Omega$  resistance), open faults, series resistance faults, and partial shading. However, it was concluded that the Boxplot rule performs best in identifying faults while the 3-sigma method failed to detect any faults. The ratio of string current to the maximum string current operating in parallel is used for identifying faulty string/strings in [57], although this method cannot differentiate the type of fault.

Some inverters are designed to shut down automatically whenever the primary current becomes negative at the onset of a parallel line-to-line or arc fault [64]. In large systems, reverse current detection at the feeder inputs to a recombiner box or inverter is a good method of detecting parallel line-to-line or arc faults because of the contribution to the fault from parallel circuits. Authors in [45] proposed connecting all positive and negative CCCs to ground to extinguish parallel arc faults. Fault detection analysis based on comparing maximum current, voltage, and power from simulation and field data over

a long duration to avoid the effects of partial shading has been described in [58]. A minimum covariance determinant (MCD) estimator based method considering PV fault detection as a clustering problem was described in [59] [60]. This method provides the probability of detection along with the probability of false alarms to determine the presence of a fault. Based on simulation results, it was claimed that the algorithm could detect PV series are faults and ground faults in a single module. In [61], differences in power losses between simulated and real-world data are used for detecting PV faults. However, no conclusive study has been conducted to determine the comparative performance indices of the proposed techniques describe above. In [62], fuzzy rule-based power estimation from temperature and irradiance data is used for detecting faults in a PV by comparing the real power measurement data and the estimated power from the algorithm.

In addition to the arc detection techniques based on frequency content of current and voltage signals described in section 2.4, several other arc fault detection methods based on time domain signature have been proposed. In [40], the voltage signal of a PV module passes through a finite impulse response band pass filter (FIR filter) and the randomness of the output from the FIR filter is measured in terms of variance. If the variance is higher than a predefined threshold, an arc fault is assumed present. Arc detection using two resonant circuits tuned at a few hundred kilohertz is proposed in [3], based on the assumption that there will be no strong signal in the PV array at those frequencies except in the case of an arc. In addition, discrete wavelet transformation (DWT) of current-based arc fault detection has been proposed in [63] and [38]. DWT is more computationally efficient compared to Fourier transformation since DWT analyzes both time and

frequency signatures in the arc signal.

Fault detection using reflectometry has long been used for detecting faults in extended transmission lines and several reflectometry methods were adapted for use in fault detection of PV arrays. A critical comparison among different reflectometry methods used to detect and locate different wire faults can be found in [65]. In time-domain reflectometry (TDR) detection methods, a step/pulsed voltage signal is sent through the two CCCs (or one CCC and EGC) to observe any deviation of the reflected voltage signal due to short or open faults [66] - [70]. Any high impedance (open fault) compared to the normal characteristic impedance provides positive reflection and the amplitude of the voltage signal at the receiving terminal increases. The opposite effect is observed in the case of decreased impedance compared to characteristic impedance (short circuit fault).

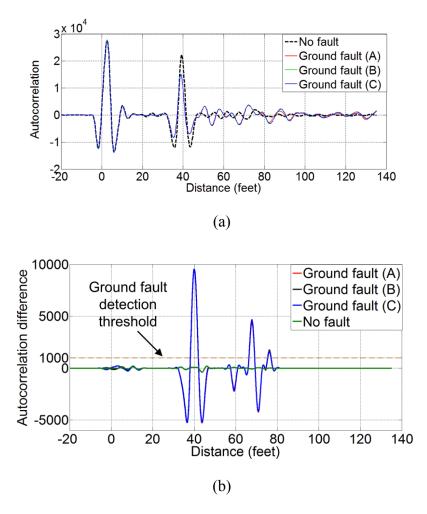

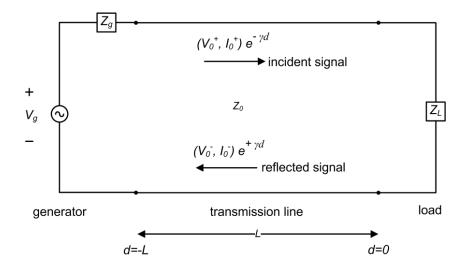

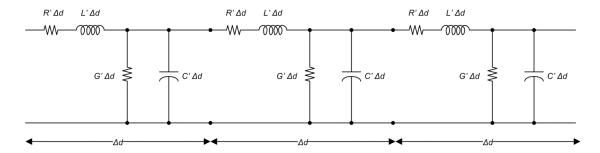

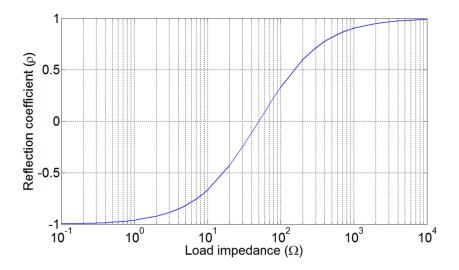

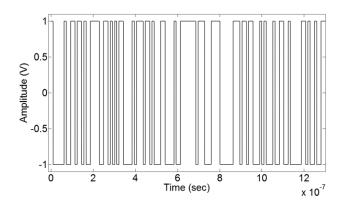

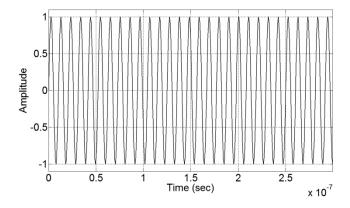

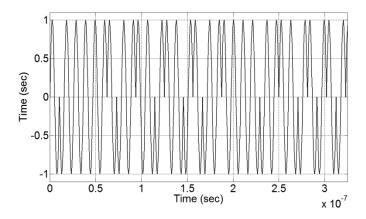

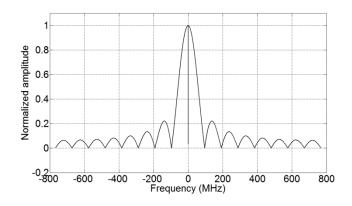

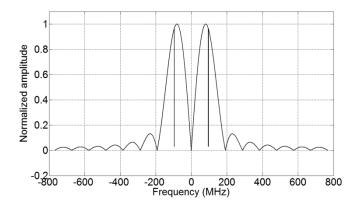

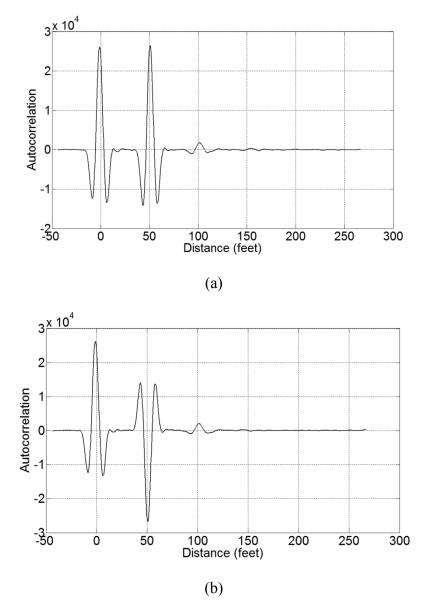

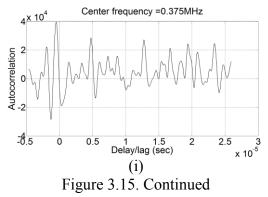

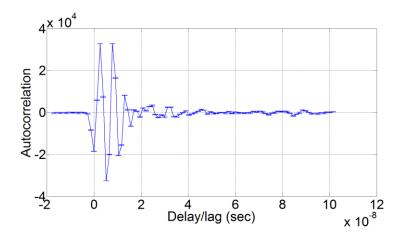

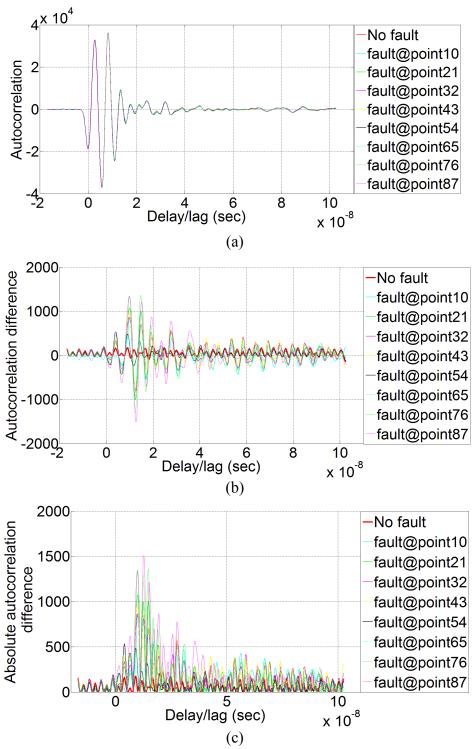

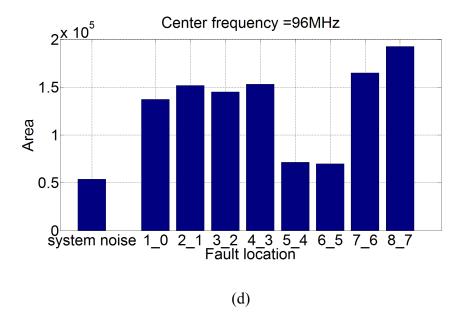

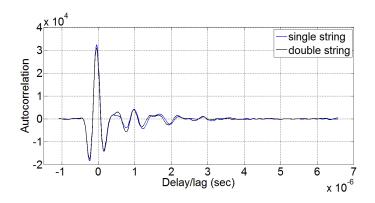

Spread spectrum time domain reflectometry (SSTDR) uses a pseudo-random binary noise (PRBN) modulated, high frequency sine wave to generate an autocorrelation plot using the incident and reflected signals. The autocorrelation plot can be used to detect the presence of a fault. SSTDR is advantageous over TDR since SSTDR can be used without disconnecting the inverter. However, both reflectometry based fault detection techniques require a baseline for comparison to detect the presence of faults. Autocorrelation plots generated by the SSTDR hardware before ground fault and after ground faults at separate locations are shown in Figure 2.17 (a). The presence of a ground fault is detected if the autocorrelation plot of the PV string deviates from the autocorrelation plot generated by the PV string without any fault by a certain threshold, as depicted in Figure 2.17 (b).

All the possible faults in the PV systems discussed in this paper along with the detection techniques are summarized in Table 2.3.

# 2.5. Fault Locating Technologies

Once the fault has been detected, the system operator must determine the location of the line-to-line fault, ground fault, or arc fault in order to repair or replace the faulty component. This process can be very difficult and time consuming with large PV installations.

Faults will present themselves differently after the fault has been de-energized:

- Ground faults will be low impedance paths from the conduction path to the ground.

- Line-to-line faults will establish a new conduction path in the PV array.

- Series arc-faults will be open connections in the PV conduction path because the arc gap will still exist

- Parallel arc-faults will not contain any changes to the conduction path, but there

may be damage to the conductors (e.g., increased resistance) that could be

detectable by fault locating devices.

There are existing challenges to determine intermittent connections and faults. If the fault is not persistent, it will be even more challenging to locate the faulty component. Table 2.4 investigates different technologies and commercially available products that could be used to locate faults in PV systems.

#### 2.6. Conclusions

Ground faults, line-to-line faults, and arc faults have been discussed in detail in this chapter. Both grounded and ungrounded PV arrays use different commercial fault detection and mitigation techniques to prevent fires. However, due to some limitations in the conventional detection techniques, ground faults may remain undetected and cause severe damage to the PV array and surrounding environment. Similar situations may arise in the case of line-to-line faults.

Depending on the type of arc fault, different mitigation techniques must be implemented. Therefore, it is imperative to detect both the presence and type of arc. This chapter has presented an overview of different state-of-the-art detection and mitigation techniques along with a literature survey of other proposed methods and recommendations for further improvements in PV fault detection, location, and mitigation.

# 2.7 References

- [1] B. Brooks, "The Ground-Fault Protection Blind Spot: Safety Concern for Larger PV Systems in the U.S.," Solar American Board for Codes and Standards, January 2012.

- [2] M. K. Alam, F.H. Khan, J. Johnson, J. Flicker, "PV faults: Overview, modeling, prevention and detection techniques," in *Proc. IEEE Workshop on Control and Modeling for Power Electronics (COMPEL)*, pp.1,7, June 2013.

- [3] H. Haberlin and M. Real, "Arc detector for remote detection of dangerous arcs on the DC side of PV plants," presented at *The 22nd European Photovoltaic Solar Energy Conference*, Milano, Italy, Sept. 2007.

- [4] W. I. Bower and J. C. Wiles, "Analysis of grounded and ungrounded photovoltaic systems," in *Proc. IEEE First World Conference on Photovoltaic Energy Conversion*, pp. 809-812, 5-9 Dec 1994.

- [5] *National Electrical Code(R) (NEC(R)) Handbook*, 2011 Edition, National Fire Protection Association, Inc., Quincy, MA.

- [6] J. C. Hernandez and P. G. Vidal, "Guidelines for protection against electric shock in PV generators," *IEEE Transactions on Energy Conversion*, vol.24, no.1, pp. 274-282, March 2009.

- [7] J. C. Hernandez, P.G. Vidal and A. Medina, "Characterization of the insulation and leakage currents of PV generators: Relevance for human safety," *Renewable Energy*, Vol. 35, Issue 3, Pages 593-601, March 2010.

- [8] G. Ball, B. Brooks, J. Johnson, J. Flicker, A. Rosenthal, J. Wiles, L. Sherwood, M. Albers, and T. Zgonena, "Inverter ground-fault detection 'blind spot' and mitigation methods," Solar America Board for Codes and Standards Report, June 2013.

- [9] Ye Zhao, Robert Lyons Jr., "Ground-fault analysis and protection in PV arrays," *Photovoltaic Protection*, note 1, issue 1, pp. 1-4, 2011.

- [10] Ye Zhao, "Fault analysis in solar photovoltaic arrays," M.S. thesis, Department of Electrical and Computer Engineering, Northeastern University, Boston, MA, 2010.

- [11] Tom Markvart and Luis CastaÑer, "*Practical Handbook of Photovoltaics*," Elsevier Science, Amsterdam, 2003, ISBN 9781856173902.

- [12] *UL Standard for flat-plate photovoltaic modules and panels, UL 1703*, Underwriter Laboratories Inc., Northbrook, IL, 2002.

- [13] Thin-film terrestrial photovoltaic (PV) modules Design qualification and type approval, IEC 61646, Edition 2.0, International Electrotechnical Commission, Geneva, Switzerland, 2008.

- [14] Crystalline silicon terrestrial photovoltaic (PV) modules Design qualification and type approval, IEC 61215, Edition 2.0, International Electrotechnical Commission, Geneva, Switzerland, 2005.

- [15] J. A. del Cueto and T. J. McMahon, "Analysis of leakage currents in photovoltaic modules under high-voltage bias in the field," *Progress in Photovoltaics: Research and Applications*, vol. 10 (1), pp. 15-28, 2002.

- [16] W. Bower and J. Wiles, "Investigation of ground-fault protection devices for photovoltaic power system applications," in *Proc. IEEE Photovoltaic Specialists Conference*, pp.1378-1383, 2000.

- [17] E. Wang *et al.*, "Accelerated aging tests on PV grounding connections," in *Proc. IEEE Photovoltaic Specialists Conference (PVSC)*, pp. 3241-3246, 19-24 June 2011.

- [18] J. Flicker and J. Johnson, "Analysis of fuses for 'blind spot' ground fault detection in photovoltaic power systems," Solar America Board for Codes and Standards Report, June 2013.

- [19] J. Flicker and J. Johnson, "Photovoltaic ground fault and blind spot electrical simulations," Sandia National Laboratories, Albuquerque, NM, Technical Report SAND2013-3459, June 2013.

- [20] J. C. Wiles and D.L. King, "Blocking diodes and fuses in low-voltage PV systems," in *Proc. IEEE Photovoltaic Specialists Conference*, pp.1105-1108, 29 Sep-3 Oct 1997.

- [21] B. Brooks (Feb/Mar 2011). *The Bakersfield Fire: A Lesson in Ground-Fault Protection*. SolarPro., Issue 4.2. Available: http://solarprofessional.com/articles/design-installation/the-bakersfield-fire-a-lesson-in-ground-fault-protection.

- [22] M. K Alam *et al.*, "PV ground-fault detection using spread spectrum time domain reflectometry (SSTDR)," in *Proc. IEEE Energy Conversion Congress and Exposition (ECCE)*, pp. 1015-1020, 15-19 Sept. 2013.

- [23] S. Czapp, "The effect of earth fault current harmonics on tripping of residual current devices," in *Proc. International School on Nonsinusoidal Currents and Compensation*, pp.1-6, 10-13 June 2008.

- [24] Ye Zhao *et al.*, "Fault analysis in solar PV arrays under: Low irradiance conditions and reverse connections," in *Proc. IEEE Photovoltaic Specialists Conference* (*PVSC*), pp. 2000-2005, 19-24 June 2011.

- [25] Ye Zhao *et al.*, "Fault evolution in photovoltaic array during night-to-day transition," in Proc. *IEEE 12th Workshop on Control and Modeling for Power Electronics (COMPEL)*, pp. 1-6, 28-30 June 2010.

- [26] Ye Zhao *et al.*, "Line–line fault analysis and protection challenges in solar photovoltaic arrays," *IEEE Transactions on Industrial Electronics*, vol.60, no.9, pp. 3784-3795, Sept. 2013.

- [27] J. Johnson *et al.*, "Differentiating series and parallel photovoltaic arc-faults," in *Proc. IEEE Photovoltaic Specialists Conference (PVSC)*, pp. 720-726, 4 June, 2012.

- [28] J. Johnson *et al.*, "Electrical and thermal finite element modeling of arc faults in photovoltaic bypass diodes," Sandia National Laboratories, Albuquerque, NM, Technical Report SAND2012-0743, Jan. 2012.

- [29] J. Johnson et al., "Using PV module and line frequency response data to create robust arc fault," in Proc. European Photovoltaic Solar Energy Conference and

- Exhibition, pp. 3745 3750, 2011.

- [30] J. Johnson *et al.*, "Creating dynamic equivalent PV circuit models with impedance spectroscopy for arc fault modeling," in *Proc. IEEE Photovoltaic Specialists Conference (PVSC)*, pp. 2328-2333,19-24 June 2011.

- [31] J. Johnson *et al.*, "Crosstalk nuisance trip testing of photovoltaic DC arc-fault detectors," in *Proc. IEEE Photovoltaic Specialists Conference (PVSC)*, pp. 1383-1387, 3-8 June 2012.

- [32] J. Johnson and J. Kang, "Arc-fault detector algorithm evaluation method utilizing prerecorded arcing signatures," in *Proc. IEEE Photovoltaic Specialists Conference (PVSC)*, pp. 1378 1382, 3-8 June 2012.

- [33] Jack D. Flicker and Jay Johnson, "Electrical simulations of series and parallel PV arc-faults," in *Proc. IEEE Photovoltaic Specialists Conference (PVSC)*, pp. 3165-3172, 16-21 June 2013.

- [34] J. Johnson *et al.*, "Photovoltaic DC arc fault detector testing at Sandia National Laboratories," in *Proc. IEEE Photovoltaic Specialists Conference (PVSC)*, pp. 3614-3619, 19-24 June 2011.

- [35] Gab-Su Seo *et al.*, "Arc protection scheme for DC distribution systems with photovoltaic generation," in *Proc. International Conference on Renewable Energy Research and Applications (ICRERA*), pp. 1-5, 11-14, Nov. 2012.

- [36] National Electrical Code(R)(NEC) and Handbook Set (NFPA 70), 2014 Edition, National Fire Protection Association, Inc., Quincy, MA.

- [37] J. Strauch *et al.*, "Solar module arc fault modeling at Sandia National Laboratories," Sandia National Laboratories, Albuquerque, NM, SAND2010-5881C, Aug. 2010.

- [38] X. Yao *et al.*, "Characteristic study and time domain discrete wavelet transform based hybrid detection of series DC arc faults," *IEEE Transactions on Power Electronics*, vol. 29, no.6, pp. 3103-3115, June 2014.

- [39] R. Ammerman *et al.*, "DC-arc models and incident-energy calculations," *IEEE Trans. Ind. Appl.*,vol. 46, no. 5, pp. 1810-1819, 2010.

- [40] F. Schimpf and L.E. Norum, "Recognition of electric arcing in the DC-wiring of photovoltaic systems," in *Proc. 31st International Telecommunications Energy Conference*, pp.1-6, 18-22 Oct. 2009.

- [41] D.A. Dini *et al.*, "Development of arc-fault circuit-interrupter requirements for photovoltaic systems," in *Proc. 37th IEEE Photovoltaic Specialists Conference (PVSC)*, pp. 1790-1794, 19-24 June 2011.

- [42] J.K. Hastings *et al.*, "A study of ignition time for materials exposed to DC arcing in PV systems," in *Proc. 37th IEEE Photovoltaic Specialists Conference (PVSC)*, pp. 3724-3729, 19-24 June 2011.

- [43] J. Johnson *et al.*, "Series and parallel arc-fault circuit interrupter tests," Sandia National Laboratories, Albuquerque, NM, SAND2013-5916, July 2013.

- [44] John J. Shea *et al.*, "RF current produced from DC electrical arcing," in *Proc. 26th International Conference on Electrical Contacts (ICEC 2012)*, pp.1-6, 14-17 May 2012.

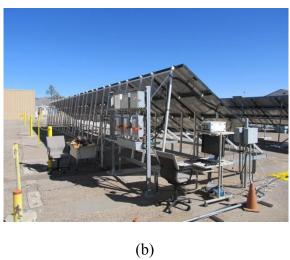

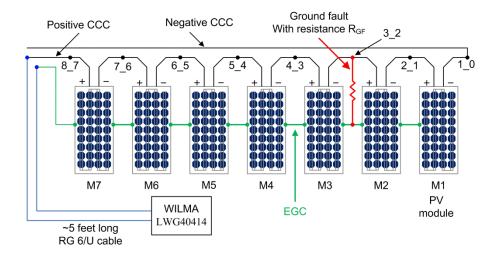

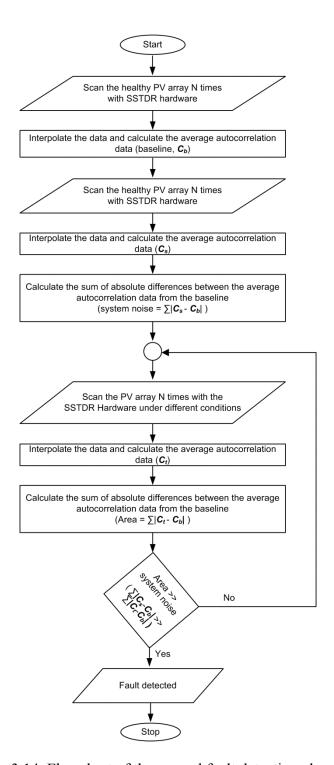

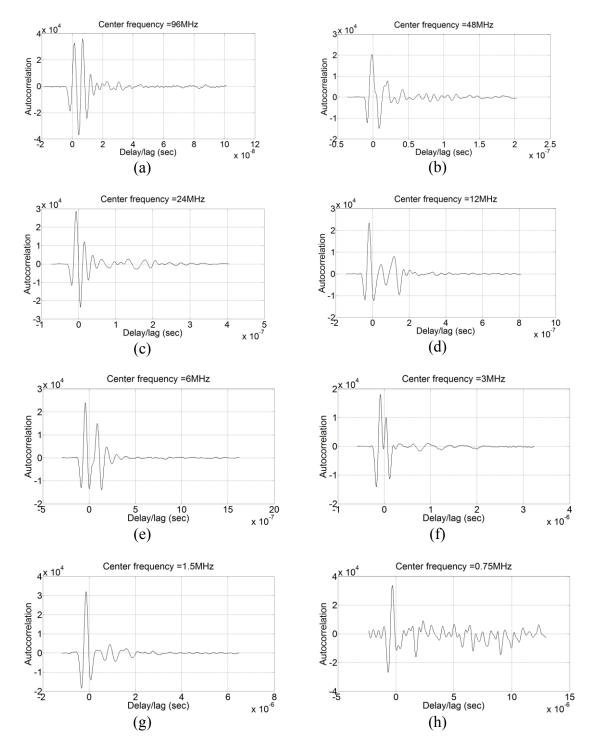

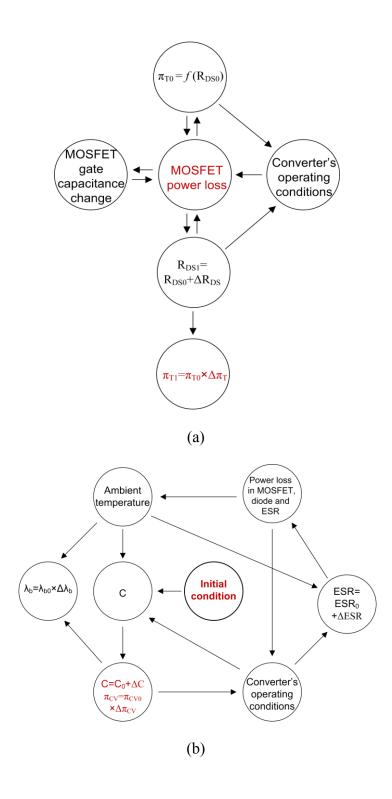

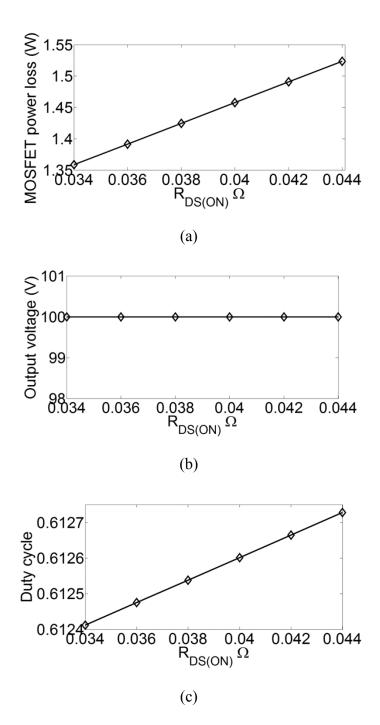

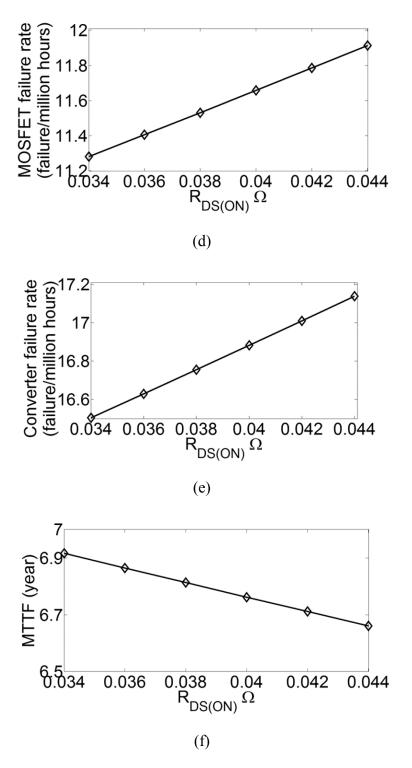

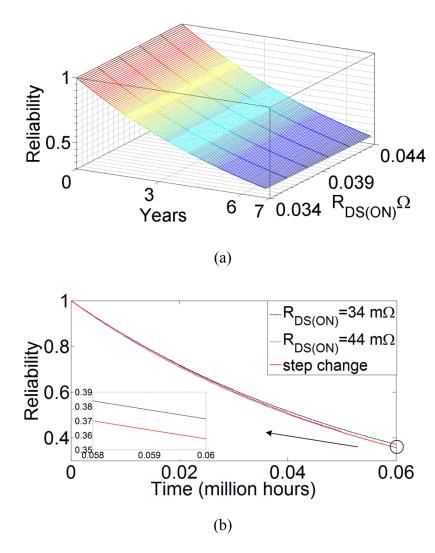

- [45] Texas instruments, "AN-2154 RD-195 DC Arc Detection Evaluation Board," Application report, SNOA564F–June 2011–Revised December 2012. Online [http://www.ti.com/lit/ug/snoa564f/snoa564f.pdf].