### ITERATIVE HEURISTICS FOR CMOL HYBRID CMOS/NANODEVICES CELLS MAPPING

ABDALRAHMAN M. ARAFEH

**Computer Engineering**

May 2012

### ITERATIVE HEURISTICS FOR CMOL HYBRID CMOS/NANODEVICES CELLS MAPPING

by

### ABDALRAHMAN M. ARAFEH

A Thesis Presented to the DEANSHIP OF GRADUATE STUDIES

In Partial Fulfillment of the Requirements for the Degree of

### MASTER OF SCIENCE

IN

### COMPUTER ENGINEERING

KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

Dhahran, Saudi Arabia

May 2012

# KING FAHD UNIVERSITY OF PETROLEUM & MINERALS DHAHRAN 31261, SAUDI ARABIA DEANSHIP OF GRADUATE STUDIES

This thesis, written by

#### ABDALRAHMAN M. ARAFEH

under the direction of his Thesis Advisor and approved by his Thesis Committee, has been presented to and accepted by the Dean of Graduate Studies, in partial fulfillment of the requirements for the degree of

#### MASTER OF SCIENCE IN COMPUTER ENGINEERING

Thesis Committee

Dr. Sadiq M. Sait (Chairman)

Dr. Alaaeldin Amin (Member)

Dr. Zubair Baig (Member)

Dr. Basem Almadani Department Chairman

Dr. Salam Zummo Dean of Graduate Studies

30/12/12 Date Dedicated to

My Parents, beloved Brothers and Sister

$\mathscr{E}$

The undaunted Syrian People

### Acknowledgements

All sincere praises and thanks are due to Allah (SWT), for His limitless blessings on us. May Allah bestow his peace and blessings upon our leader Prophet Muhammad (P.B.U.H), his family, his companions, and those that follow his guidance until the last day. Acknowledgements are due to King Fahd University of Petroleum & Minerals for providing the computing resources for this research.

I would like to express my profound gratitude and appreciation to my thesis advisor Dr. Sadiq M. Sait for his guidance and patience throughout this thesis. His continuous support, advise and encouragement can never be forgotten. I would also like to express my appreciation to my thesis committee members, Dr. Alaaeldin Amin and Dr. Zubair Baig for their constructive comments. Also, I would like to express my deepest thanks to faculty and staff members of Computer Engineering Department for their cooperation. Thanks are due also to my fellow graduate students, and brothers who supported me with help and encouragement during the work. Especially, Feras Chikh Oughali, Abdulrahman Idlbi, Mouheddin Alhaffar and Abdulnaser Alsharaa.

I also thank my beloved parents, my brothers and sister for their moral support throughout my academic career. Their assistant and sacrifices are truly appreciated and will be remembered. Finally, thanks to everybody who contributed to this achievement in a direct or an indirect way.

# Contents

|                 | Ack                 | knowledgements          | iv  |

|-----------------|---------------------|-------------------------|-----|

| List of Tables  |                     |                         | ix  |

| List of Figures |                     |                         | xi  |

|                 | Abstract (English)  |                         | xv  |

|                 | Abstract (Arabic) x |                         | xvi |

| 1               | Intr                | roduction               | 1   |

|                 | 1.1                 | Iterative Heuristics    | 3   |

|                 | 1.2                 | CMOS/nanodevices Hybrid | 4   |

|                 | 1.3                 | Thesis Objectives       | 6   |

|                 | 1.4                 | Thesis Contributions    | 6   |

|                 | 1.5                 | Thesis Organization     | 7   |

| <b>2</b>        | Lite                | erature Review          | 9   |

| 2.1 | Nanof                                                                       | abric Crossbars                                                                                                                                                                                                                                               | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | 2.1.1                                                                       | Fault Diagnosis in Nanofabric Crossbars                                                                                                                                                                                                                       | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | 2.1.2                                                                       | Reconfiguration/Repair of Nanofabric Crossbars                                                                                                                                                                                                                | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.2 | CMO                                                                         | L Hybrid CMOS/Nanodevices Circuits                                                                                                                                                                                                                            | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | 2.2.1                                                                       | Cell-based FPGA-like CMOL Architecture                                                                                                                                                                                                                        | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | 2.2.2                                                                       | Tile-based FPGA-like CMOL Architecture                                                                                                                                                                                                                        | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | 2.2.3                                                                       | CMOL Cells Design                                                                                                                                                                                                                                             | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | 2.2.4                                                                       | Two-Terminal Latching Nanodevices                                                                                                                                                                                                                             | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.3 | Other                                                                       | CMOS/nanodevices Architectures                                                                                                                                                                                                                                | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | 2.3.1                                                                       | Field-Programmable Nanowire Interconnect (FPNI)                                                                                                                                                                                                               | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | 2.3.2                                                                       | 3-D CMOL Architecture                                                                                                                                                                                                                                         | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.4 | Cell P                                                                      | Placement in CMOL Architecture                                                                                                                                                                                                                                | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | 2.4.1                                                                       | Theoretical Principles of CMOL Cell Placement                                                                                                                                                                                                                 | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | 2.4.2                                                                       | Cell Placement in Cell-based CMOL Architecture                                                                                                                                                                                                                | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | 2.4.3                                                                       | Cell Placement in Tile-based CMOL Architecture                                                                                                                                                                                                                | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.5 | Non-d                                                                       | leterministic Iterative Heuristics                                                                                                                                                                                                                            | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | 2.5.1                                                                       | Simulated Evolution                                                                                                                                                                                                                                           | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | 2.5.2                                                                       | Tabu Search    .    .    .    .    .                                                                                                                                                                                                                          | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Pro | blem l                                                                      | Description and Design Automation                                                                                                                                                                                                                             | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.1 | Proble                                                                      | em Statement                                                                                                                                                                                                                                                  | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | <ul> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>Pro</li> </ul> | $\begin{array}{c} 2.1.1 \\ 2.1.2 \\ 2.1.2 \\ 2.1.2 \\ 2.1.2 \\ 2.2.1 \\ 2.2.1 \\ 2.2.2 \\ 2.2.3 \\ 2.2.4 \\ 2.3 \\ 2.2.4 \\ 2.3.1 \\ 2.3.1 \\ 2.3.2 \\ 2.4.1 \\ 2.3.2 \\ 2.4.1 \\ 2.4.2 \\ 2.4.1 \\ 2.4.2 \\ 2.4.3 \\ 2.5.1 \\ 2.5.1 \\ 2.5.2 \\ \end{array}$ | 2.1.1       Fault Diagnosis in Nanofabric Crossbars         2.1.2       Reconfiguration/Repair of Nanofabric Crossbars         2.1.2       Reconfiguration/Repair of Nanofabric Crossbars         2.2       CMOL Hybrid CMOS/Nanodevices Circuits         2.2.1       Cell-based FPGA-like CMOL Architecture         2.2.2       Tile-based FPGA-like CMOL Architecture         2.2.3       CMOL Cells Design         2.2.4       Two-Terminal Latching Nanodevices         2.3       Other CMOS/nanodevices Architectures         2.3.1       Field-Programmable Nanowire Interconnect (FPNI)         2.3.2       3-D CMOL Architecture         2.3.1       Field-Programmable Nanowire Interconnect (FPNI)         2.3.2       3-D CMOL Architecture         2.4.1       Theoretical Principles of CMOL Cell Placement         2.4.2       Cell Placement in Cell-based CMOL Architecture         2.4.3       Cell Placement in Tile-based CMOL Architecture         2.5       Non-deterministic Iterative Heuristics         2.5.1       Simulated Evolution         2.5.2       Tabu Search |

|   | 3.2  | Proble  | em Formulation                                      | 47        |

|---|------|---------|-----------------------------------------------------|-----------|

|   |      | 3.2.1   | Placement                                           | 47        |

|   |      | 3.2.2   | Reconfiguration                                     | 49        |

|   | 3.3  | Cost I  | Functions                                           | 52        |

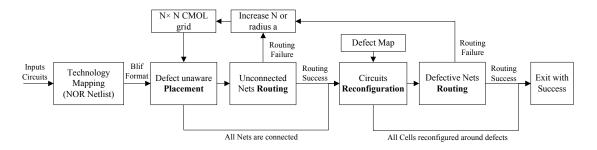

|   | 3.4  | Defect  | Maps                                                | 54        |

|   | 3.5  | Desigr  | n Flow                                              | 56        |

| 4 | Nor  | n-deter | ministic Evolutionary Heuristics for CMOL Cell Map- |           |

|   | ping | S       |                                                     | <b>58</b> |

|   | 4.1  | Soluti  | on Representation                                   | 59        |

|   | 4.2  | Simula  | ated Evolution                                      | 59        |

|   |      | 4.2.1   | Initialization                                      | 60        |

|   |      | 4.2.2   | Goodness Function                                   | 61        |

|   |      | 4.2.3   | Selection Function                                  | 63        |

|   |      | 4.2.4   | Allocation Function                                 | 64        |

|   |      | 4.2.5   | Routing                                             | 65        |

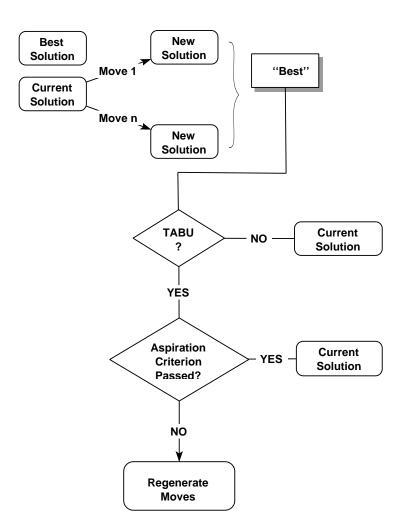

|   | 4.3  | Tabu    | Search                                              | 66        |

|   |      | 4.3.1   | Initialization                                      | 66        |

|   |      | 4.3.2   | Neighborhood Solutions Generation                   | 67        |

|   |      | 4.3.3   | Tabu List and Move Attributes                       | 68        |

|   |      | 4.3.4   | Aspiration Criterion                                | 69        |

|   |      | 4.3.5  | Routing                     |   | 70  |

|---|------|--------|-----------------------------|---|-----|

| 5 | Exp  | erime  | ntal Results and Comparison |   | 71  |

|   | 5.1  | Simula | ation Environment           |   | 72  |

|   |      | 5.1.1  | Benchmarks                  |   | 72  |

|   |      | 5.1.2  | Defect Maps and CMOL Grids  |   | 74  |

|   | 5.2  | Placer | nent                        |   | 76  |

|   |      | 5.2.1  | Simulated Evolution         |   | 77  |

|   |      | 5.2.2  | Tabu Search   .             |   | 79  |

|   |      | 5.2.3  | Results Comparison          |   | 81  |

|   | 5.3  | Recon  | figuration                  |   | 87  |

|   |      | 5.3.1  | Simulated Evolution         |   | 87  |

|   |      | 5.3.2  | Tabu Search   .             |   | 87  |

|   |      | 5.3.3  | Results                     |   | 90  |

|   | 5.4  | Soluti | ons Verification            |   | 101 |

| 6 | Cor  | clusio | n & Future Work             | 1 | 103 |

|   | 6.1  | Conclu | usion                       |   | 103 |

|   | 6.2  | Future | e Work                      |   | 104 |

|   | BIE  | BLIOG  | RAPHY                       | 1 | 105 |

|   | Vita | a      |                             | 1 | 116 |

# List of Tables

| 5.1  | ISCAS'89 Benchmarks                                                                                                                                                           | 73 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.2  | Defect Scenarios.                                                                                                                                                             | 74 |

| 5.3  | CMOL 2-D grid sizes                                                                                                                                                           | 75 |

| 5.4  | CMOL area utilization                                                                                                                                                         | 76 |

| 5.5  | SimE Comparison With CMOL CAD, GA, MA and LRMA - $(a = 12)$ .                                                                                                                 | 83 |

| 5.6  | TS Comparison With CMOL CAD, GA, MA and LRMA - $(a=12).$ .                                                                                                                    | 84 |

| 5.7  | SimE and TS Comparison With CMOL CAD, MA and LRMA - $(a = 9)$ .                                                                                                               | 86 |

| 5.8  | Circuits reconfiguration using SimE and random defect map $R1$ , $(q_{wire} =$                                                                                                |    |

|      | $20\% - q_{cell} = 0\%$ )                                                                                                                                                     | 92 |

| 5.9  | Circuits reconfiguration using SimE and clustered defect map $C1$ -                                                                                                           |    |

|      | $\sigma = \frac{2a}{3}, (q_{wire} = 20\% - q_{cell} = 0\%) \dots \dots$ | 93 |

| 5.10 | Circuits reconfiguration using SimE and clustered defect map $C2$ -                                                                                                           |    |

|      | $\sigma = \frac{4a}{3}, (q_{wire} = 20\% - q_{cell} = 0\%)  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                  | 94 |

| 5.11 | Circuit s820 reconfiguration around cut wires using SimE, ( $q_{nano} =$                                                                                                      |    |

|      | $20\% - q_{cell} = 0\%$ )                                                                                                                                                     | 94 |

| 5.12 Circuit s1238 reconfiguration around cut wires using SimE, ( $q_{nano} =$                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $20\% - q_{cell} = 0\%$ )                                                                                                                                            |

| 5.13 Implementation of SimE for defect scenario (iii), $(q_{nano}~=~20\%$ -                                                                                          |

| $q_{wire} = 20\%).$ 95                                                                                                                                               |

| 5.14 Circuits reconfiguration using TS and random defect map $R1$ , $(q_{wire} =$                                                                                    |

| $20\% - q_{cell} = 0\%$ )                                                                                                                                            |

| 5.15 Circuits reconfiguration using TS and clustered defect map $C1$ - $\sigma =$                                                                                    |

| $\frac{2a}{3}, (q_{wire} = 20\% - q_{cell} = 0\%) \dots 99$                                  |

| 5.16 Circuits reconfiguration using TS and clustered defect map $C2$ - $\sigma =$                                                                                    |

| $\frac{4a}{3}, (q_{wire} = 20\% - q_{cell} = 0\%) \dots \dots$ |

| 5.17 Circuit s820 reconfiguration around cut wires using TS, $(q_{nano} = 20\%)$                                                                                     |

| $-q_{cell} = 0\%$ )                                                                                                                                                  |

| 5.18 Circuit s1238 reconfiguration around cut wires using TS, $(q_{nano} = 20\%)$                                                                                    |

| - $q_{cell} = 0\%$ )                                                                                                                                                 |

# List of Figures

| 1.1 | Levels of abstraction and corresponding design steps                  | 2  |

|-----|-----------------------------------------------------------------------|----|

| 2.1 | Low-level structure of CMOL architecture                              | 16 |

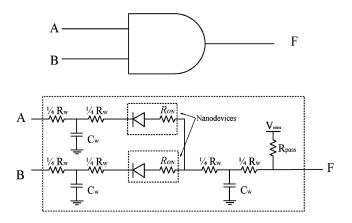

| 2.2 | The equivalent circuit of a CMOL logic stage                          | 17 |

| 2.3 | CMOL FPGA-like Architecture: Connectivity Domain                      | 19 |

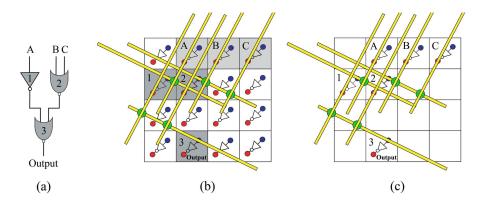

| 2.4 | Fan-in-two NOR gate: (a) equivalent circuit and (b) physical imple-   |    |

|     | mentation in CMOL                                                     | 20 |

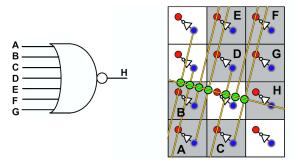

| 2.5 | Example of CMOL implementation of a 7-input NOR gate                  | 20 |

| 2.6 | Example of CMOL circuit: (a) NOR/INV logical circuit; (b) CMOL        |    |

|     | impl<br>mentaion of (a), (c) showing only used cells                  | 21 |

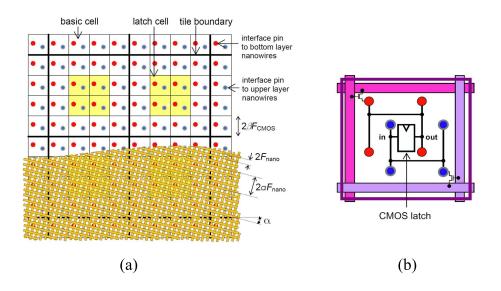

| 2.7 | CMOL FPGA: (a) Tiles configuration, (b) Latch cell                    | 22 |

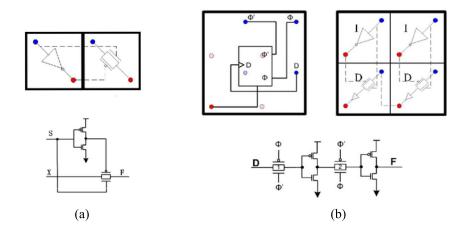

| 2.8 | (a) T-Cell: Transmission gate and inverter (b) D-Cell: D flip-flop is |    |

|     | formed using two D-Cells and two inverter cells                       | 23 |

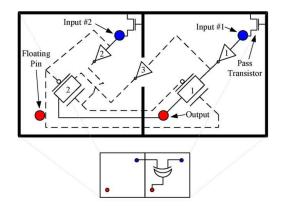

| 2.9 | XOR cell design based on resistive-based nanodevices                  | 24 |

| 2.10 | AND cell based on diode-like nanodevices and its equivalent circuit.    |    |

|------|-------------------------------------------------------------------------|----|

|      | Rw and $Cw$ represent the nanowires                                     | 25 |

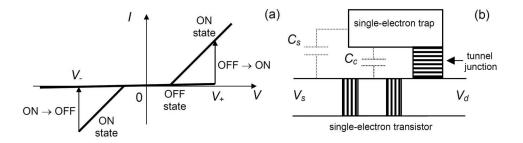

| 2.11 | Single-Electron two terminal nanodevice: (a) The I - V curves, and      |    |

|      | (b) A possible implementation of the device                             | 26 |

| 2.12 | FPNI architecture [1]: (a) large pads connecting CMOS and nanowires,    |    |

|      | (b) nanofabric overlay in FPNI                                          | 28 |

| 2.13 | 3D CMOL architecture [2]                                                | 30 |

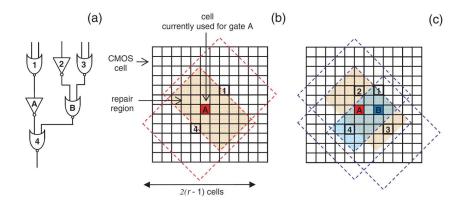

| 2.14 | Example of a circuit fragment reconfiguration. (a) Circuit whose gate   |    |

|      | A is to be relocated. (b) The repair region of gate A. (c) intersection |    |

|      | of the repair region of cells $[3]$                                     | 33 |

| 2.15 | Example of global routing for a single net                              | 36 |

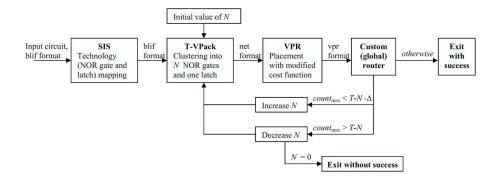

| 2.16 | CMOL FPGA CAD 1.0 design flow                                           | 37 |

| 2.17 | Structure of the Simulated Evolution algorithm [4]                      | 41 |

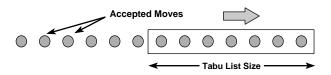

| 2.18 | Tabu List visualized as window over accepted moves [4]. $\ldots$ .      | 42 |

| 2.19 | Flow-Chart of Tabu Search algorithm [4]                                 | 44 |

| 2.20 | Algorithmic description of short-term Tabu Search (TS) [4]. $\ldots$    | 45 |

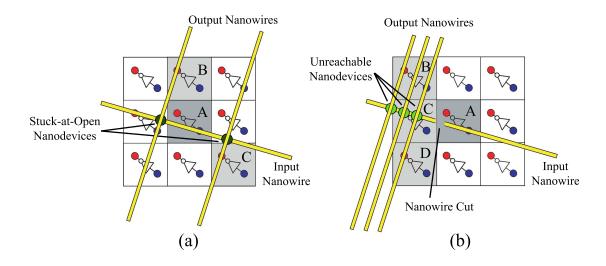

| 3.1  | Defects in CMOL circuits: (a) Stuck-at-Open defect (b) Broken nanowire  |    |

|      | defect. The cells shown in light gray are not reachable by the cell in  |    |

|      | dark gray                                                               | 51 |

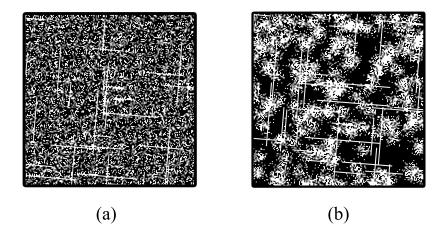

| 3.2  | Defect maps: (a) Random defects (b) Clustered defects                   | 55 |

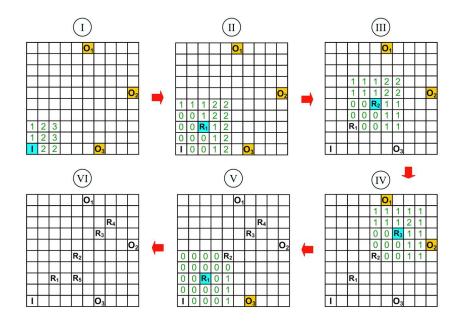

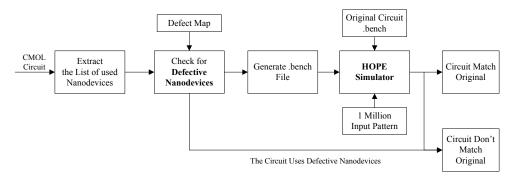

| 3.3 | Design flow of CMOL cells mapping                                                      | 56 |

|-----|----------------------------------------------------------------------------------------|----|

| 4.1 | 2-D grid layout of CMOL placement for $s27.blif$ . 19 cells; 8 gates, 7                |    |

|     | inputs and 4 outputs                                                                   | 59 |

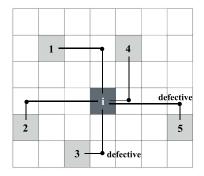

| 4.2 | Evaluation of gate <i>i</i> 's goodness; for $r = 3$ cells 1, 2 and 3 are inside       |    |

|     | <i>i</i> 's connectivity domain (i.e., $dist \leq r$ ), while cells 4 and 5 are out of |    |

|     | it (i.e., $dist > r$ ), $goodness_i = 3/5 = 0.6.$                                      | 62 |

| 4.3 | Evaluation of gate $i$ 's goodness; connection between cell $i$ and cells 4            |    |

|     | and 5 use defective nanodevices, $goodness_i = 3/5 = 0.6$ . Nanodevices                |    |

|     | are shown as black dots.                                                               | 63 |

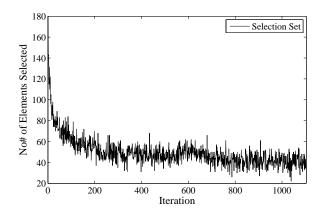

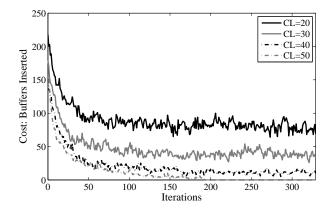

| 5.1 | Evaluation of SimE performance: selected elements Vs. iterations                       |    |

|     | (a = 12 - s1238.blif).                                                                 | 77 |

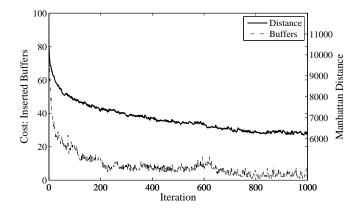

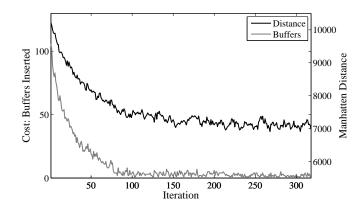

| 5.2 | Correlation between distance minimization and buffers insertion in                     |    |

|     | SimE iterations ( $a = 12$ - s1238.blif)                                               | 78 |

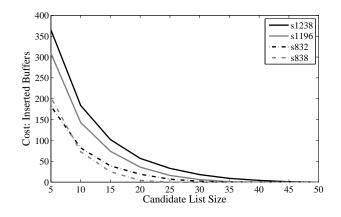

| 5.3 | Final cost yielded by TS in four circuits vs. candidate list size $(a = 12)$ .         | 79 |

| 5.4 | Change in cost per iteration of s1238.blif for different candidate list                |    |

|     | sizes $(a = 12)$                                                                       | 80 |

| 5.5 | Change of problem cost and Manhattan distance in TS iterations                         |    |

|     | (a = 12 - s1238.blif).                                                                 | 80 |

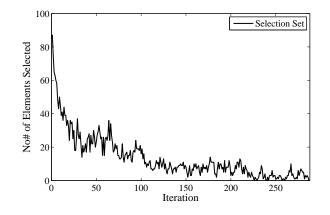

| 5.6 | SimE reconfiguration heuristic: selection set size Vs. iterations -                    |    |

|     | s1238.blif                                                                             | 88 |

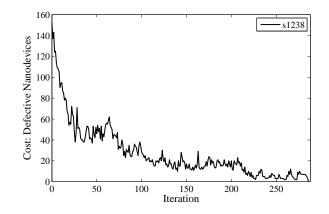

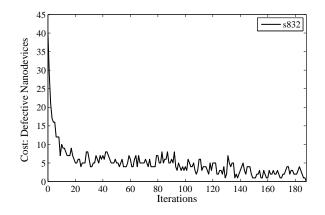

| 5.7  | Change of reconfiguration cost per iteration in Simulated Evolution      |     |

|------|--------------------------------------------------------------------------|-----|

|      | - s1238.blif                                                             | 88  |

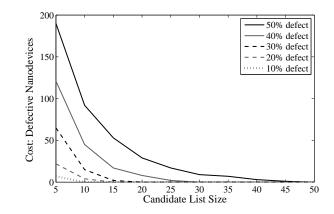

| 5.8  | Change of reconfiguration cost per iteration in Tabu Search - s832.blif. | 88  |

| 5.9  | Cost yielded by TS for $q_{nano}$ between 10% and 50% vs. candidate list |     |

|      | size - s1196.blif                                                        | 89  |

| 5.10 | Verification steps.                                                      | L01 |

#### THESIS ABSTRACT

| Name:           | ABDALRAHMAN M. ARAFEH                |

|-----------------|--------------------------------------|

| Title:          | ITERATIVE HEURISTICS FOR CMOL HYBRID |

|                 | CMOS/NANODEVICES CELLS MAPPING       |

| Major Field:    | COMPUTER ENGINEERING                 |

| Date of Degree: | May 2012                             |

Recently, many CMOS/nanodevices hybrid architectures have been proposed; the new architectures combine the flexibility and high fabrication yield advantages of CMOS technology with nanometer scale latching devices. CMOL (CMOS/Molecular hybrid) is a novel architecture that consists of an overlay of a nanofabric over a CMOS stack. Combinational logic in CMOL is implemented from a netlist of NOR gates and Inverters, by programming nanodevices placed between overlapping nanowires. The length of the nanowires is restricted, and therefore connectivity of the circuit elements is constrained to only cells that are located within proximity square-like connectivity domain. The confined connectivity reduces the flexibility of VLSI design automation and further complicates cells mapping. Furthermore, misassembly of the two-terminals bistable nanodevices will lead to non-programmable crosspoints (i.e., stuck-at defects). The defect rate in nanofabric architectures is expected to be higher than that of conventional CMOS technology. In this work, we solve the problems of cell placement and reconfiguration in CMOL circuits. Simulated Evolution (SimE) and Tabu Search (TS) are employed to find an arrangement of cells that adhere to connectivity constraints and rely on non defective nanodevices. Circuits of various sizes from ISCAS'89 benchmarks are used to evaluate the designed heuristics. Results show that SimE and TS are able to find placement solutions that are better than previously published ones, and in less computation time. Moreover, they yield successful reconfigurations when the defect rate is as high as 50%.

**Keywords:** CMOL, Nanofabrics, Placement, Reconfiguration, Simulated Evolution, Tabu Search, Evolutionary Tabu Search, Search Heuristics, Defects, VLSI.

#### ملخص الرسالة

الإسم: عبد الرحمن محمد عرفان عرفة

**العنوان:** توزيع العناصر الإلكترونية ضمن الدارات الهجينة بإستخدام الخوارزميات التكرارية غير الحتمية

الإختصاص: هندسة الحاسب الآلى

تاريخ المنح: أيار ٢٠١٢

شهدت الأونة الأخيرة عدة إقتر احات لدارات هجينة تجمع بين عناصر الدارات المتكاملة التقليدية CMOS وعناصر نانوية ذات خواص كهربائية. تجمع هذه الدارات الهجينة بين سهولة التصميم ومردود التصنيع العالي لتكنولوجيا CMOS، وبين مواسك نانوية ثنائية الإستقرار ذات كثافة عالية وقدرة على العمل عند ترددات مرتفعة. إحدى هذه البنى الجديدة هي بنية المحالي وهي بنية مكونة من طبقة أسلاك نانوية متقاطعة تتوضع فوق طبقات CMOS التقليدية. يتم تحقيق المنطق التركيبي في بنية للمحرفة من طبقة أسلاك نانوية متقاطعة تتوضع فوق طبقات CMOS التقليدية. يتم تحقيق المنطق التركيبي في بنية للمحرفة من طبقة أسلاك نانوية متقاطعة تتوضع فوق طبقات CMOS التقليدية. يتم تحقيق المنطق التركيبي في بنية للمحرفة من طبقة أسلاك نانوية ما للمكل شبكة من بوابات NOR وعواكس. يتم تحقيق التركيبي في بنية للمحوفة العناصر النانوية المتوضعة بين الأسلاك النانوية على شكل شبكة من بوابات NOR وعواكس. يتم الدارة من خلال برمجة العناصر النانوية المتوضعة بين الأسلاك النانوية المتداخلة. تسبب الصعوبات التصنيعية محدودية في أطوال الأسلاك النانوية، مما يجعل التوصيل بين عناصر الدارة مقيداً بالخلايا الموجودة ضمن مجال محدد للتوصيل. يسبب الدارة. كما تعاني العناصر النانوية ثانائية الإستقرار الموجودة عند تقاطعات الأسلاك النانوية على الخلايا المتوفرة في أطوال من خلال برمجة أو الإستخدام، ويتوقع بأن تكون نسبة العيوب في هذه التجهيزات النانوية من عيوب ضمنية، أي أنها الدارة. كما تعاني العناصر النانوية ثنائية الإستقرار الموجودة عند تقاطعات الأسلاك النانوية من عيوب ضمنية، أي أنها العيوب الموجودة في دارات كلامية.

في هذه الرسالة سنقدم حلاً لمشكلة توزيع عناصر الدارات الإلكترونية على الخلايا المتاحة في بنية CMOL، كما سنقوم بإعادة توزيع هذه العناصر لتلافي إستخدام أي من التجهيزات النانوية المعيبة. سيتم ذلك بإستخدام خوارزميتين غير حتميتين هما Simulated Evolution و Tabu Search واللتان تقومان بإيجاد توزيع معين للعناصر، بحيث يتم احترام قيود التوصيل واستخدام عناصر نانوية غير معيبة. استخدمنا في عملية تقييم فعالية الخوارزميات المقترحة مجموعة من الدارات القياسية ذات الأحجام المختلفة والمعروفة بإسم ISCAS8 لقد أظهرت النتائج أن كلاً من الخوارزميتين قادرتان على إعطاء حلول أفضل من مثيلاتهما وبزمن حساب أقل. علاوة على ذلك، فإنهما تسفران عن عملية إعادة توزيع ناجحة عند نسب عالية من العيوب تصل إلى خمسين في المئة.

# Chapter 1

# Introduction

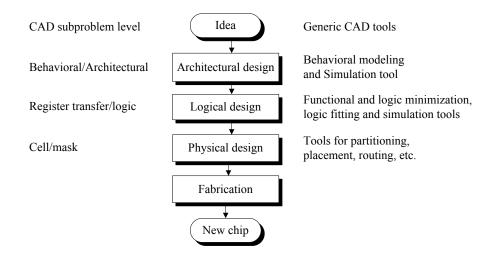

The recent advances in Very Large Scale Integration (VLSI) have led to the fabrication of circuits with millions of transistors. Conventionally, VLSI design process is divided into several intermediate levels of abstraction. More details about the new design are introduced as the design progresses from highest to lowest levels of abstraction. The design is taken from specification to fabrication step by step with the help of various Computer Aided Design (CAD) tools that automate the design flow and manage design information at all levels of VLSI design process. Typical levels of abstraction, together with their corresponding design steps, are illustrated in Figure 1.1.

Feature size scaling in CMOS technology has led to difficulties in manufacturing due to short channel effects, doping fluctuations and expensive lithography process. Meanwhile, advances in nanoelectronics are expected to achieve high density of

Figure 1.1: Levels of abstraction and corresponding design steps.

devices and to operate at THz frequencies [5]. Many effective applications have been proposed that use molecular nanodevices, nanowires, and nano-crossbar fabrics [3, 1, 6, 7]. A new trend is emerging for combining the flexibility and high fabrication yield advantages of CMOS technology with nanometer-scale molecular devices. A self-assembly of two-terminal nanodevices, with nanowire crossbar fabrics, enables high functional density and sustains acceptable fabrication costs.

Assigning cells to slots is an important step in the process of electronic design automation. The assignment problem has been proven to be NP-hard problem for which iterative heuristics have been employed successfully to reach acceptable solutions. Overtime, the objective of placement has changed from reducing the overall wirelength to reducing the area, to improving timing performance, and then to reducing the overall power dissipation. With new advances in technology come new issues; the CMOS/nanodevices hybrid architectures require combinational logic cells to be placed in slots that are connected by programmable nanodevices placed between overlapping nano-wires. The length of the nanowires is restricted, and therefore connectivity of the circuit elements is constrained.

### **1.1** Iterative Heuristics

Many of the significant optimization problems are NP-Hard. For relatively large instances of such problems, it is not possible to resort to optimal enumerative techniques; instead, we must resort to *approximation algorithms*. Approximation algorithms, also known as heuristic methods, do not guarantee finding an optimal solution, yet they exploit domain specific heuristic knowledge to bias the search toward "good" solution subspace to quickly find an "acceptable" solution which satisfies design constraints. Therefore, the time requirement of a heuristic is small compared to that of full enumerative algorithms.

A number of heuristics have been developed for various problems. Examples of approximation algorithms are the modern general iterative algorithms such as *Simulated Annealing*, *Tabu Search*, and *Simulated Evolution*. All mentioned iterative heuristics constitute very general (i.e., can be applied to solve any combinatorial optimization problem) and effective optimization techniques. Most iterative heuristics are easy to implement; all that is required is to have suitable solution representation, a cost function, and a mechanism to traverse the search space. Although they asymptotically converge to an optimal solution, the rate of convergence is heavily dependent on the adequate choice of several parameters and the utilization of "hill climbing" property.

### 1.2 CMOS/nanodevices Hybrid

Semiconductors have been largely dominated by CMOS (Complementary Metal-Oxide-Silicon), however, the current VLSI paradigm, based on a combination of lithographic patterning, CMOS circuits, and Boolean logic; can hardly be extended into a-few-nm region [8, 9]. The main reason is that at gate length below 10 nm, the sensitivity of parameters (most importantly, the gate threshold voltage) of silicon field-effect transistors (MOSFETs) grows exponentially. As a result, the gate length should be controlled with a few-angstrom accuracy, far beyond even the long-term projections of the semiconductor industry [10]. Even if such accuracy can be technically implemented using sophisticated patterning technologies, this will send the fabrication facilities costs to unprecedented high values, and will lead to annulment of Moore's Law some time during the next decade.

There is a growing consensus that the impending crisis of the microelectronics progress may be resolved only by a radical paradigm shift from the *lithography-based* fabrication to the so-called *bottom-up* approach [11]. In this approach, the smallest active devices of integrated circuits are not defined lithographically but assembled from parts with fundamentally reproducible size and structure, (e.g., few-nm-scale molecules). The most straightforward example of such devices is a specially designed two-terminal single-electron nanodevice [9, 12].

Unfortunately, integrated circuits consisting of molecular devices alone are hardly viable because of limited device functionality. For example, the voltage gain of a 1-nm-scale transistor, based on any known physical effect (e.g., the field effect, quantum interference, or single-electron charging), can hardly exceed one, i.e., the level necessary for sustaining the operation of virtually any active analog or digital circuit [13]. This is why the only plausible way toward high-performance nanoelectronic circuits is to integrate molecular devices, and the connecting nanowires, with CMOS circuits whose (relatively large) field-effect transistors would provide the necessary additional functionality, in particular high voltage gain. Thus, most efforts in the development of high-performance nanoelectronic circuits are focused on hybrid CMOS/nanodevices [3, 14, 15, 16, 17, 18]. Recent reviews of CMOS/nanodevices circuits can be found in [19, 20, 21, 22]. CMOS/nanodevices circuits with feature size below 10 nm have the potential to provide huge density improvement over the current CMOS technology [10, 23]. However, at such a small scale, fabricated chips will exhibit a high percentage of defects, probably as much as 20%-50%.

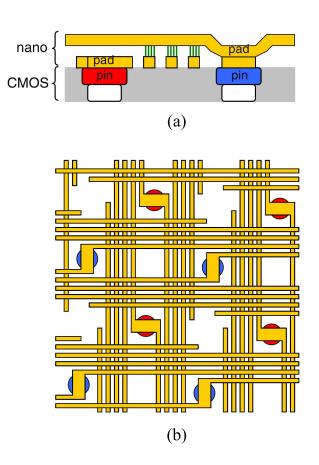

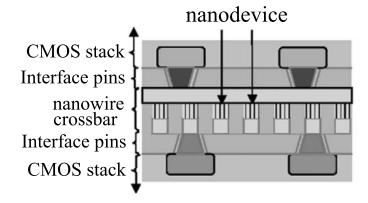

It is important to note that even though the recent demonstrations of CMOS/nanodevices hybrid architectures are promising, building a practical hybrid circuit is still challenging. One of the major challenges is the interfacing with CMOS environment (necessary for I/O functions). If a crossbar is small (much smaller than the chip it is fabricated on), each nanowire may be gradually widened to eventually fit a broader CMOS wire. Moreover, the requirement of special pins with different heights to connect to the top or bottom crossbar nanowires may render nanowires unreachable, causing circuits to become defective.

### **1.3** Thesis Objectives

The main objective of this work is to investigate the new constraints imposed on cells mapping in CMOL hybrid CMOS/nanodevices architecture. The mapped circuits should adhere to the architecture's constrained connectivity and should avoid to use any defective component. The mapping process will be divided to two main steps; *placement* on defect-free layout, and defect-aware *reconfiguration*.

Simulated Evolution (SimE), and Tabu Search (TS) are the search heuristics to be employed for search space exploration. The work will focus on the design of the search heuristics and their various operators and parameters given the new connectivity and defect constraints.

#### **1.4** Thesis Contributions

This thesis presents the results of the investigations related to the objectives discussed in the previous section. The main contributions can be summarized as follows:

- The work illustrates the design of iterative heuristics to address the new constraint related to cells placement in the emerging CMOS/nanodevices circuits.

- The work demonstrates the use of iterative heuristics for fault tolerance in CMOL nanofabric architecture through reconfiguration.

- Implement Simulated Evolution (SimE) and Tabu Search (TS) heuristics for CMOL placement and reconfiguration problems.

- Propose new goodness, allocation and neighborhood generation functions for better exploration of search space and evolutionary enhancement of cells assignments.

- Generate defect maps with three types of defects part of which are based on stuck-at-open model.

- Successfully place circuits without requiring any additional buffers and preserving the circuits timing delay.

- Tolerate up to 50% of Stuck-at-open defects and broken nanowires rate up to 70% by reconfiguring circuits using SimE and TS Heuristics.

### 1.5 Thesis Organization

This thesis is organized as follows: In chapter 2, theoretical aspects of CMOL CMOS/nanodevices hybrid FPGA-like architecture are discussed along with a review of related literature on nanofabric design, iterative heuristics and proposed

techniques for cell placement in CMOL. Problem formulation is dealt with in chapter 3. Chapter 4 discusses the parameters and operators of non-deterministic iterative heuristics employed for CMOL placement and reconfiguration problems. Heuristics evaluation and final results are reported in chapter 5, including comparison with previous techniques. The thesis concludes with conclusion and future work in chapter 6.

# Chapter 2

### Literature Review

### 2.1 Nanofabric Crossbars

A considerable amount of research has been done on developing nanoscale devices and devising nanofabric architectures to replace conventional lithographybased CMOS technology. Recently, many nanofabric logic designs have been proposed based on nanoscale componenets such as carbon nanotubes (CNTs) [24, 25, 26, 27], silicon nanowires (SiNWs) [28, 29], single electron devices [30, 31], and quantum dot cells [32]. Crossbar-based architecture is a promising computational nanotechnology, a 2D array formed by the intersection of two orthogonal sets of parallel and uniformly-spaced nanometer-sized wires. Nanoscale wires can be aligned to construct an array with nanometer-scale spacing using a form of directed selfassembly, the formed crosspoints of nanoscale wires can be used as programmable diodes. The nanoscale crossbar systems offers ultra-high density, however, the nanodevics are likely to have many imperfections and defect rates as high as 20% to 50%.

Nanoscale crossbar structures are very regular and can be implemented in a similar manner to the conventional filed programable gate arrays (FPGAs). Goldstein et al [7] proposed chemically assembled electronic nanotechnology FPGA-like architecture called NanoFabric. The architecture consists of an array of connected logic blocks, called Nanoblocks. A 2D molecular array inside each Nanoblock provides reprogrammable resistor-diode logic. DeHone et al. [6] presented another nanofabric architecture where the main building block of the design, called the nano programmable logic array nanoPLA, is based on self-assembled crossbar arrays of nanowires with non-volatile diode-based switches at the intersections. The individual nanowires can be addressed by a lithographic scale address decoder. Most importantly, Likharev el al [3] proposed *CMOL*, the CMOS/nanodevices circuits. CMOL uses diode-based nano crossbar arrays on top of CMOS cells. The main difference of CMOL compared to previous proposed architectures is how the CMOS/nanodevices are interfaced. Pins are distributed over the circuit on top of the CMOS stack to connect to either lower or upper nanowire levels. Nanowires in CMOL do not need to be precisely aligned with each other and the underlying CMOS layer in order to be able to uniquely access a nanodevice.

Generally, defects can be divided into two classes: permanent defects caused by

inherent physics uncertainties in the manufacturing process, and transient faults due to lower noise tolerance. The methods used to cope with the aforementioned defects can be classified into two categories. The first one is based on redundancy, e.g. Rfold Module Redundancy (RMR). Such approach can handle both permanent defects and transient faults, however, it suffers from low reliability. The second category is based on reconfiguration techniques during post-manufacturing design to avoid the defects. It is reported that reconfiguration is the most effective technique, however, it does not effectively handle transient faults.

Defects are a major issue for devices with few atoms in diameter. The small cross-section and contact areas can render nanodevices fragile and defect prone. The order of defects in nanofabric architectures surpass the conventional CMOS devices since the inherent non-determinism in bottom-up self-assembly chemical processes at molecular scale, result in more defects compared to highly controlled lithography-based manufacturing process. Thus, an effective fault tolerance schemes are required, along with test and diagnostic techniques to identify and locate the defects and then reconfigure the circuit to bypass defective elements.

#### 2.1.1 Fault Diagnosis in Nanofabric Crossbars

Reconfigurable devices are fault tolerant such that faults can be detected, and their locations can be stored in a defect map. The defect map is a database that stores defect information that can be used during reconfiguration. The faulty devices can be avoided with the help of a defect map which can be constructed by testing and diagnosis techniques. High resolution diagnosis is required to identify defective resources such as programmable switches, wires, or logic cells. A survey of different approaches for fault detection and diagnosis in molecular computing can be found in [33].

The Teramac project at HP-labs [34] applies thorough testing and diagnosis to identify defective unusable resources and maps an entire design to the usable resources. Build-in self-test (BIST) techniques make use of the reconfigurability of nanofabric FPGA-like architectures to provide a complete test and diagnosis of defects. In the built-in self-test approache, the fabric is divided into mainly three groups; a test pattern generator (TPG), blocks under test (BUTs), and output response analyzers (ORAs). The TPG applies test patterns to the BUTs, which send output responses to the ORA, and ORAs compare the responses to determine if there is a defect. Different variations and enhancement to BIST have been proposed in literature, among those the designs reported in [35, 36, 37].

The size of defect map for the entire fabric can be prohibitively large with almost  $10^{12}$  nanodevices per chip. The authors in [38] show that Bloom filters can be used as a data structure for defect maps. They develop a defect tolerant nanoscale memory architecture that allow manufacturers to embed defect information within the delivered nanosystem.

#### 2.1.2 Reconfiguration/Repair of Nanofabric Crossbars

In the presence of defects, it is still possible to utilize the non defective nanodevices, by reconfiguring circuits around defective ones. Huang et al [39] presented a solution for defect tolerance in two-dimensional crossbars by utilizing defective architecture and determining the expected size of functional (defect-free) crossbar, based on defect density information obtained from the fabrication process. Another attempt to reconfigure nanowire crossbar systems was reported by Yellambalase et al [40]. They presented three different logic mapping algorithms to circumvent defective crossbars. The algorithms namely; Row-wise matching, Column-matching-first, and Redundant column-matching first, are based on matching of two bipartite graphs, one of them represents the defective crossbar and the other represents the circuit to be mapped.

Tahoori has presented a defect tolerant design flow that includes a greedy mapping algorithm [41]. The algorithm finds and locates the maximum defect free  $k \times k$ crossbar within the defective crossbar by finding the maximum biclique in a bipartite graph that represents the nanofabric crossbar. Further, a variation tolerant logic mapping for molecular (diode-based) crossbar using heuristic algorithms has been presented by Tahoori [42, 43]. His approach is mainly based on swapping rows (columns) of a crossbar to reduce the output dependency and delay variation.

Although, many heuristic algorithms have been presented in the literature for the

reconfiguration or logic mapping in defective nanofabric crossbars, many are only applicable for small size nanofabrics. Moreover, The devised greedy algorithms are expected to have degraded results and to consume considerable computation time in case of high defects rate.

### 2.2 CMOL Hybrid CMOS/Nanodevices Circuits

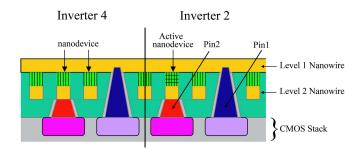

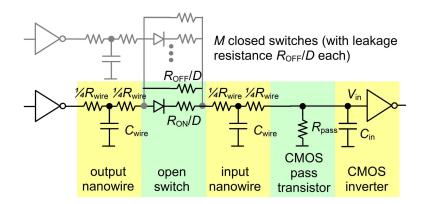

CMOL (CMOS/nanowire/MOLecular hybrid) is a hybrid circuit architecture which combines a semiconductor MOSFET transistors with uniform reconfigurable nanowires fabric. It was originally developed by Likharev and his colleagues [3], to overcome the CMOS/nanodevices interface problems pertinent to earlier proposals. In CMOL circuits, interfacing between transistors and nanowires is provided by sharp-tip pins that are distributed all over the circuit area on top of the CMOS stack. Two-terminal molecular-scale nanodevices "latching switches", that have two metastable internal states, are self-assembled at each crosspoint of the nanofabric. Nanodevices work as switches that are programmable to connect the two levels of nanowires. The generic CMOL cell shown in Figure 2.1(a), consists of conventional CMOS stack, two perpendicular nanowires, and two-terminal nanodevices sandwiched between nanowires to form points of contact. The output of inverter 2 (Pin 2) is connected to the input of inverter 4 (Pin 1) by pin-nanowire-nanodevicenanowire-pin connection. The overlay nanofabric serves as a connection and wiring logic medium with the help of molecular nanodevices.

#### 2.2.1 Cell-based FPGA-like CMOL Architecture

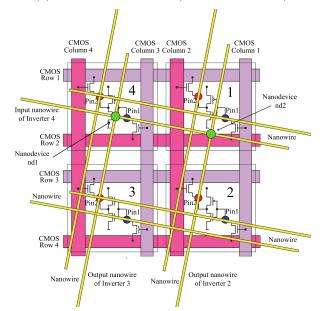

CMOL cell-based, field programmable gate array (FPGA)-like architecture is based on a uniform, reconfigurable CMOL fabric, with four transistor CMOS cells and two-terminal nanodevices [3]. Each generic CMOS cell (Four cells are shown in Figure 2.1(b) consists of an inverter and two pass transistors that serve two pins as the cell input and output, respectively. During the configuration process the inverters are turned off, and the pass transistors are used for setting the binary state of each molecular device. By turning programmable diodes "ON" or "OFF", the nanowires, nanodevice and CMOS inverters can implement a basic wired NOR with multiple fan-ins. As shown in Figure 2.1(b), Inverter 1 has two pins; pin1 connects the input of the CMOS inverter to one of the nanowires levels, while pin2 connects the CMOS inverter's output to the second level of nanowires. The lower left cell (Inverter 3) is connected to the upper left cell (Inverter 4) by activating the appropriate nanodevice (nd1) in the crosspoint between the nanowire connected to the output of inverter 3 and nanowire connected to the input of inverter 4. When two or more nanodevices in the input nanowire of inverter 4 are activated (nd1 and nd2) the output of cell 4 will be equivalent to NOR gate whose inputs are cell 2 and cell 3.

The equivalent electrical circuit of the aforementioned configuration is shown

(a) Schematic side view (A-A cross-section)

(b) Four CMOL cells and corresponding nanowires

(c) Nanowires crossbar and pins connectivity

Figure 2.1: Low-level structure of CMOL architecture.

in Figure 2.2. The figure shows five logic stages that the electrical signals should traverse to connect two cells. The first stage is output nanowire; which is equivalent to resistance  $R_{wire}$  and the capacitance of the full nanowire fragment  $C_{wire}$ . Then, comes the nanodeivce which is represented as an open diode with resistance  $R_{ON}/D$ in the ON state and as a high resistance  $R_{OFF}/D$  in OFF state, where D is the number of parallel molecular-scale devices each with  $R_{ON}$  resistance. Then, the connection passes through input nanowire to reach CMOL cell which has a CMOS pass transistor with  $R_{pass}$  resistance and a CMOS inverter. Those stages comprise the pin-nanowire-nanodevice-nanowire-pin connection mentioned earlier.

Figure 2.2: The equivalent circuit of a CMOL logic stage.

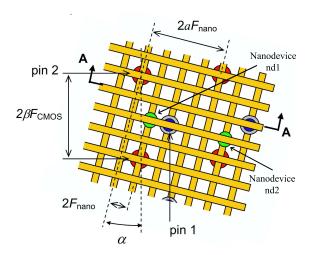

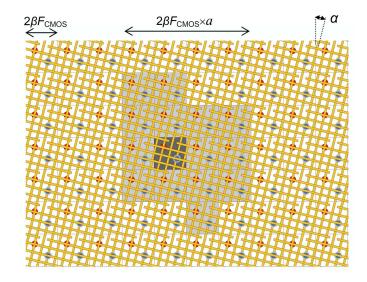

Figure 2.1(c) shows CMOS pins reaching to the lower and upper nanowire levels. CMOL fabric is arranged into a square array with side  $2\beta F_{CMOS}$ , where  $F_{CMOS}$  is the half-pitch of the CMOS subsystem, while  $\beta$  is a dimensionless factor greater than 1 and depends on the CMOS cell complexity [21]. Because nanodevices are non-volatile switches, they can be programmed to route the signals from CMOS to the nanowires and nanodevices, and back to CMOS again. For FPGA applications, the nanowire crossbar is turned by almost  $\alpha = 45$  relative to CMOS cells array, though that is not absolutely necessary [3, 21]. More exactly, the requirements for the angle  $\alpha$  and the dimensionless factor  $\beta$  that determines the CMOS cell area  $A = (2\beta F_{CMOS})^2$  is:

$$\alpha = \arcsin\left(\frac{F_{nano}}{\beta F_{CMOS}}\right) \tag{2.1}$$

Where  $F_{nano}$  is the nanowiring half-pitch. Also, Figure 2.1(c) shows that any nanodevice may be addressed via the appropriate pin pair (e.g., input pin of Inverter 4 and output pins of Inverters 2 and 3), only two devices are shown but in reality, similar nanodevices are formed at all nanowire crosspoints. Like in the case of most programmable devices, the length of the nanowires is restricted and therefore each CMOL cell can be connected to  $M = a^2 - 2$  other cells located within a squareshaped *Connectivity Domain* shown in Figure 2.3. Where *a* is a positive integer number that constitute CMOL radius. In Case a = 4 output pins of cells painted in light-gray may be connected to the input pin of the specified dark-gray cell.

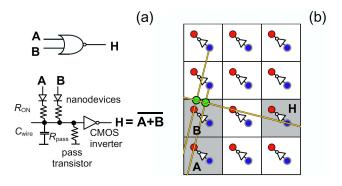

An example of implementing NOR gate using CMOL cells is given in Figure 2.4, if only the two nanodevices shown in Figure 2.4(b) are in the "ON" state, while all other nanodevice connected to the input nanowire of cell 'H' are in the "OFF"

Figure 2.3: CMOL FPGA-like Architecture: Connectivity Domain.

(high resistance) state, then cell 'H' calculates the NOR function of signals 'A' and 'B', and for the sake of clarity only the nanowires used are shown. The advantage of such architecture that gates with high fan-in (Figure 2.5) and fan-out may be readily formed as well by turning "ON" the corresponding latching switches. CMOL architecture is inherently defect-tolerant, since it has  $M \approx a^2 >> 1$  nanodevices per CMOS cell, and few of them are required for either logic or routing functionality.

If the nanowires and nanodevices shown in Figure 2.6(b) are all activated, the CMOL circuit will be equivalent to circuit shown in Figure 2.6(a). Shaded cells are connected through combination of nanowires, nanodevices and CMOS pins. The first NOR gate of the circuit can be implemented by connecting inputs 'A' and 'B' with inverter '2' to satisfy both connectivity and logic wiring for the desired gate.

Figure 2.4: Fan-in-two NOR gate: (a) equivalent circuit and (b) physical implementation in CMOL.

Figure 2.5: Example of CMOL implementation of a 7-input NOR gate.

The abundance of available nanodevices and nanowires provide a variety of different possible configurations for the implementation of one circuitry. Among those there could be only certain configurations that satisfy connectivity domain constraint and do not require additional routing resources.

Figure 2.6: Example of CMOL circuit: (a) NOR/INV logical circuit; (b) CMOL implementation of (a), (c) showing only used cells.

#### 2.2.2 Tile-based FPGA-like CMOL Architecture

Likharev and Strukov extended CMOL architecture into fabric of "tiles" [21, 44]. The fabric is a uniform mesh of square-shaped "tiles" as shown in Figure 2.7(a). Each tile consists of a shell of T basic inverter-based cells surrounding a single "latch" cell shown in Figure 2.7(b). The latter cell is a level-sensitive latch implemented in CMOS subsystem and connected to eight interface pins, plus two pass transistors used for circuit configuration. All four pins of each of the input or the output group are always connected, so nanowires they contact always carry the same signal. The latch cell is assumed to be four times larger than the size of the basic cell. Thus, the total tile area is equal to  $T = 12+4 = 16 = 4 \times 4$  basic cells. That provide latch/logic resource ratio comparable to conventional FPGAs. For worst case 4-input Boolean function (i.e., 4-input parity function); the function can be implemented using 14 four-input NOR gates, while an average 4-input Boolean function requires much less

Figure 2.7: CMOL FPGA: (a) Tiles configuration, (b) Latch cell

gates. Hence, each CMOL tile is crudely similar in functionality to the basic logic element consisting of a four-input LUT and one latch.