# SYNTHESIS OF SOFT ERROR TOLERANT **COMBINATIONAL CIRCUITS**

BY

## **KHALED ABDEL-KARIM DAUD**

A Thesis Presented to the DEANSHIP OF GRADUATE STUDIES

#### KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the Requirements for the Degree of

## MASTER OF SCIENCE

In

COMPUTER ENGINEERING

January, 2012

## KING FAHD UNIVERSITY OF PETROLEUM AND MINERALS DHAHRAN 31261, SAUDI ARABIA

#### **DEANSHIP OF GRADUATE STUDIES**

This thesis, written by **KHALED DAUD** under the direction of his thesis advisor and approved by his thesis committee, has been presented to and accepted by the Dean of Graduate Studies, in partial fulfillment of the requirements for the degree of **MASTER OF SCIENCE in COMPUTER ENGINEERING**.

#### **Thesis Committee**

with

Dr. Aiman El-Maleh (Advisor)

Dr. Sadiq M. Sait (Member)

Dr. Alaaeldin Amin (Member)

Dr. Basem AL-Madani (Department Chairman)

Dr. Salam A. Zummo (Dean of Graduate Studies)

1/4/12

Date

# Dedicated to My Beloved Parents and Brothers

## ACKNOWLEDGMENT

All praise and thanks are due to Almighty Allah, Most Gracious and Most Merciful, for his immense beneficence and blessings. He bestowed upon me health, knowledge and patience to complete this work. May peace and blessings be upon prophet Muhammad (PBUH), his family and his companions.

Thereafter, acknowledgement is due to the support and facilities provided by the Computer Engineering Department of King Fahd University of Petroleum & Minerals for the completion of this work.

I acknowledge, with deep gratitude and appreciation, the inspiration, encouragement, valuable time and continuous guidance given to me by my thesis advisor, **Dr. Aiman El-Maleh**. I am also grateful to my committee members, **Dr. Sadiq M. Sait**, and **Dr. Alaaeldin Amin** for their constructive guidance and support.

My heartfelt thanks are due to my parents and brothers for their prayers, guidance, and moral support throughout my academic life. My parents' advice, to strive for excellence has made all this work possible.

Last, but not least, thanks to all my colleagues and friends who encourage me a lot in my way to the achievement of this work.

## TABLE OF CONTENTS

| ACK  | NOW    | LEDGMENT                                                 | iv   |

|------|--------|----------------------------------------------------------|------|

| LIST | OF 1   | TABLES                                                   | viii |

| LIST | OF F   | FIGURES                                                  | x    |

| THE  | SIS A  | BSTRACT (ENGLISH)                                        | xii  |

| THE  | SIS A  | BSTRACT (ARABIC)                                         | xiv  |

|      |        |                                                          |      |

| СНА  | PTEF   | R 1 INTRODUCTION                                         | 1    |

| 1.1  | Cor    | nbinational Circuits                                     | 3    |

| 1.2  | Soft   | t Errors in Nano-Scale Circuits                          | 3    |

| 1.3  | Res    | earch Motivation                                         |      |

| 1.4  | Pro    | blem Statement and Thesis Objectives                     |      |

| 1.   | 4.1    | Problem Statement                                        |      |

| 1.   | 4.2    | Thesis Objectives                                        | 13   |

| 1.5  | The    | sis Contributions                                        | 14   |

| 1.6  | The    | sis Organization                                         | 15   |

|      |        |                                                          |      |

| CHA  | PTEF   | R 2 LITERATURE REVIEW                                    | 16   |

| 2.1  | Def    | initions                                                 | 16   |

| 2.   | 1.1    | Defects, Faults and Errors                               | 16   |

| 2.   | 1.2    | Defect (or Fault) Models                                 | 17   |

| 2.   | 1.3    | Failure Rate                                             |      |

| 2.   | 1.4    | Reliability                                              |      |

| 2.   | 1.5    | Fault Tolerance                                          | 19   |

| 2.2  | Cur    | rent Fault Tolerance Methods                             | 19   |

| 2.   | 2.1 H  | ardware Redundancy Techniques                            |      |

| 2.   | 2.2 Sy | ynthesis-Based Fault Tolerance Techniques                |      |

| 2.   | 2.3 Pł | nysical Characteristics Based Fault Tolerance Techniques |      |

| <b>FOLERANCE</b>  | •••••                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                          | •••••                                                                                                                                                                                                                                                                                                                                                                    | •••••                                                                                                                                                                                                                                                                                                                                                                    |                                                               |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| 1 Extracting Sub- | Circuits                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                          |                                                               |

| 2 Adding Control  | llability Don'                                                                                                                                                                                                            | t Care Cor                                                                                                                                                                                                                                                                                                                                      | nditions                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                          |                                                               |

| .3 Proposed Desig | gn Level Appr                                                                                                                                                                                                             | oach                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                          | •••••                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                          |                                                               |

| 3.3.1 Finding Ca  | re Minterms'                                                                                                                                                                                                              | Probabilit                                                                                                                                                                                                                                                                                                                                      | ies                                                                                                                                                                                                                                                                                                                                                      | •••••                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                          |                                                               |

| 3.3.2 Two-Level   | Fail Rate Est                                                                                                                                                                                                             | imator                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                          | •••••                                                                                                                                                                                                                                                                                                                                                                    | •••••                                                                                                                                                                                                                                                                                                                                                                    | 39                                                            |

| 3.3.3 Finding Co  | vering Cubes                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                          | •••••                                                                                                                                                                                                                                                                                                                                                                    | •••••                                                                                                                                                                                                                                                                                                                                                                    | 44                                                            |

| 3.3.4 Adding Red  | dundant Cube                                                                                                                                                                                                              | s                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                          | •••••                                                                                                                                                                                                                                                                                                                                                                    | •••••                                                                                                                                                                                                                                                                                                                                                                    | 51                                                            |

| 3.3.5 Duplicate   | One Cube Pha                                                                                                                                                                                                              | ase                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                          | •••••                                                                                                                                                                                                                                                                                                                                                                    | •••••                                                                                                                                                                                                                                                                                                                                                                    | 52                                                            |

| 3.3.6 Algorithm   | 1: Two-Level                                                                                                                                                                                                              | Circuit Sy                                                                                                                                                                                                                                                                                                                                      | ynthesis                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                          | •••••                                                                                                                                                                                                                                                                                                                                                                    | 53                                                            |

| 3.3.7 Complexity  | of Algorithn                                                                                                                                                                                                              | n 1                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                          | 55                                                            |

| 4 Conclusion      |                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                          |                                                               |

|                   |                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                          |                                                               |

|                   | <b>TOLERANCE</b><br>1 Extracting Sub-<br>2 Adding Control<br>3 Proposed Desig<br>3.3.1 Finding Ca<br>3.3.2 Two-Level<br>3.3.3 Finding Co<br>3.3.4 Adding Rec<br>3.3.5 Duplicate of<br>3.3.6 Algorithm<br>3.3.7 Complexity | <b>TOLERANCE</b><br>1 Extracting Sub-Circuits<br>2 Adding Controllability Don'<br>3 Proposed Design Level Appr<br>3.3.1 Finding Care Minterms'<br>3.3.2 Two-Level Fail Rate Est<br>3.3.3 Finding Covering Cubes<br>3.3.4 Adding Redundant Cube<br>3.3.5 Duplicate One Cube Pha<br>3.3.6 Algorithm 1: Two-Level<br>3.3.7 Complexity of Algorithm | <b>TOLERANCE</b> 1 Extracting Sub-Circuits2 Adding Controllability Don't Care Cor3 Proposed Design Level Approach3.3.1 Finding Care Minterms' Probabilit3.3.2 Two-Level Fail Rate Estimator3.3.3 Finding Covering Cubes3.3.4 Adding Redundant Cubes3.3.5 Duplicate One Cube Phase3.3.6 Algorithm 1: Two-Level Circuit Sy3.3.7 Complexity of Algorithm 1. | <b>TOLERANCE</b> 1 Extracting Sub-Circuits2 Adding Controllability Don't Care Conditions3 Proposed Design Level Approach3.3.1 Finding Care Minterms' Probabilities3.3.2 Two-Level Fail Rate Estimator3.3.3 Finding Covering Cubes3.3.4 Adding Redundant Cubes3.3.5 Duplicate One Cube Phase3.3.6 Algorithm 1: Two-Level Circuit Synthesis3.3.7 Complexity of Algorithm 1 | <b>TOLERANCE</b> 1 Extracting Sub-Circuits2 Adding Controllability Don't Care Conditions3 Proposed Design Level Approach3.3.1 Finding Care Minterms' Probabilities3.3.2 Two-Level Fail Rate Estimator3.3.3 Finding Covering Cubes3.3.4 Adding Redundant Cubes3.3.5 Duplicate One Cube Phase3.3.6 Algorithm 1: Two-Level Circuit Synthesis3.3.7 Complexity of Algorithm 1 | IAPTER 3 TWO-LEVEL LOGIC SYNTHESIS FOR SOFT         FOLERANCE |

#### CHAPTER 4 MULTI-LEVEL LOGIC SYNTHESIS FOR SOFT ERROR TOLRANCE 58

| TOLRANCE                                                                     | 58 |

|------------------------------------------------------------------------------|----|

| 4.1 Fast Extraction for Area Optimization                                    | 59 |

| 4.2 Fast Extraction for Reliability                                          | 61 |

| 4.3 Algorithm 2: Enhancing Area for Reliability Optimized Two-Level Circuits | 69 |

| 4.4 Framework of Enhancing Fault Tolerance Using Algorithms 1 and 2          | 70 |

| 4.5 Conclusion                                                               | 72 |

####

| 5.1 | Measuring Combinational Circuit Reliability       | 74 |

|-----|---------------------------------------------------|----|

| 5.2 | The Simulation Framework of Reliability Evaluator | 74 |

| 5.3 | Assumptions                                       | 76 |

| 5.4 | Fault Model and Fault Injection Mechanism         | 76 |

| CHAPTER 6 RESULTS, DISCUSSION AND FINDINGS | 78 |

|--------------------------------------------|----|

| 6.1 Experiments                            | 78 |

| -                                |     |    |

|----------------------------------|-----|----|

|                                  |     |    |

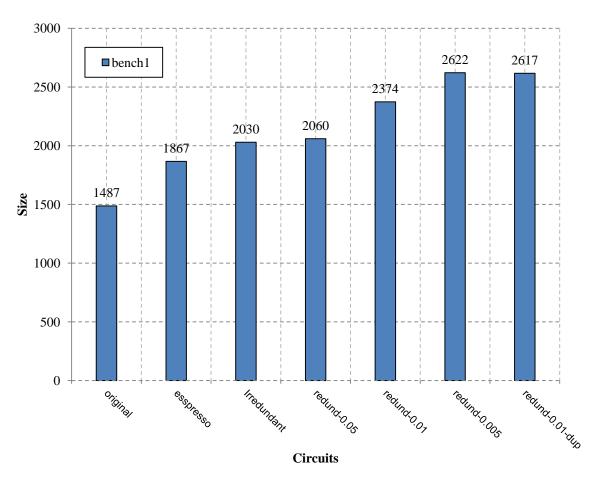

| 6.2 Calculating the Area Overhea | d 8 | 33 |

|                                  |     |    |

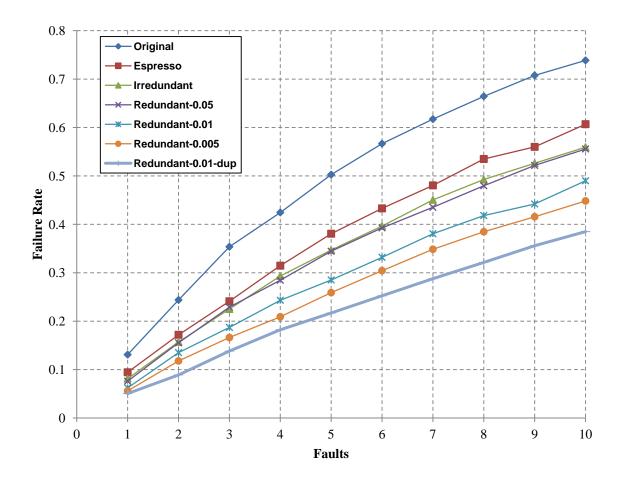

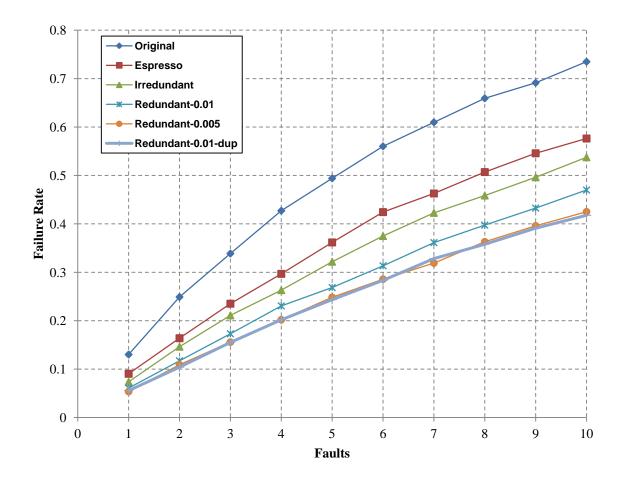

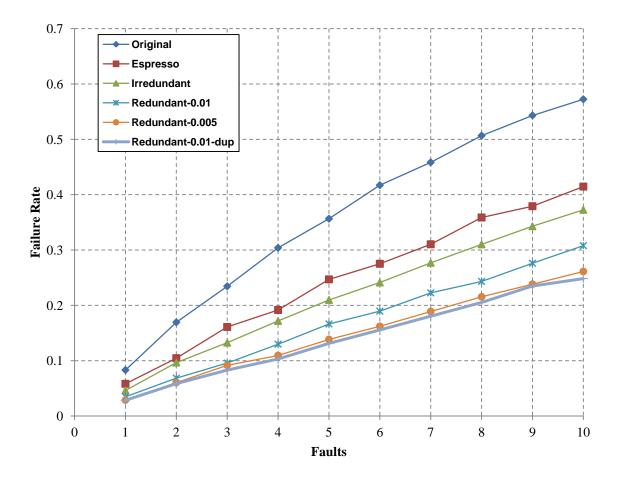

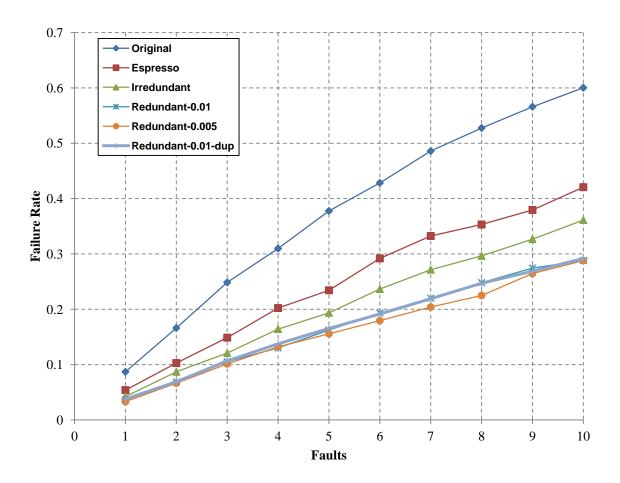

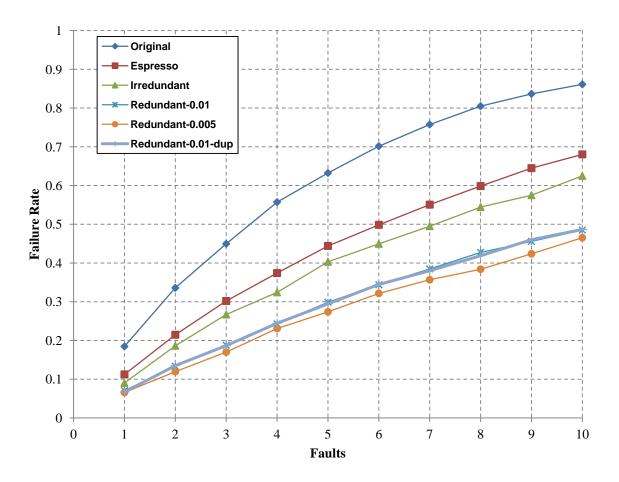

| 6.3 Algorithm 1 Results                               | 83  |

|-------------------------------------------------------|-----|

| 6.3.1 Case Study: Bench1 Benchmark                    | 84  |

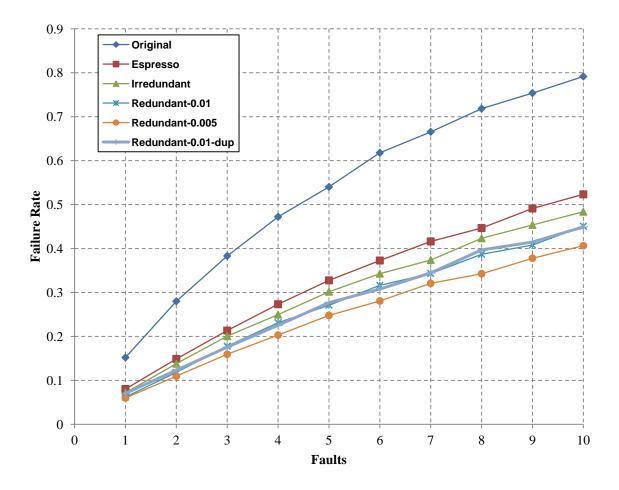

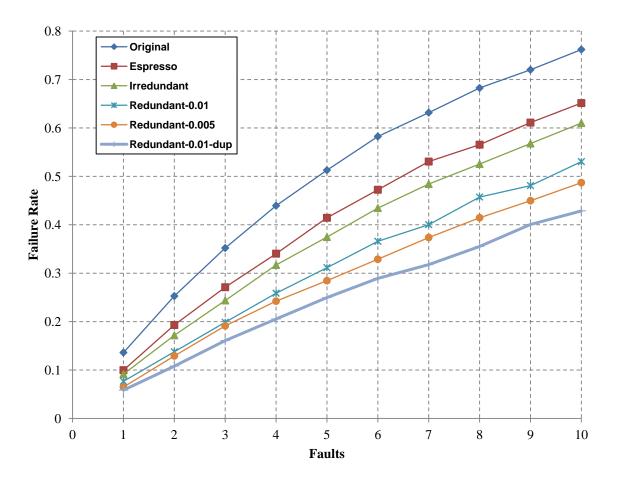

| 6.3.2 Other Benchmarks Results                        | 88  |

| 6.3.3 Aggregated Results and Conclusions              | 101 |

| 6.4 Algorithm 2 Results                               | 108 |

| 6.5 Overall Results Using Algorithm 1 and Algorithm 2 | 114 |

| 6.6 Comparison Results                                | 118 |

| 6.7 Proposed Technique with TMR                       | 121 |

## CHAPTER 7 CONCLUSION AND FUTURE WORK...... 123

| 7.1 Summary of the Contributions | 125 |

|----------------------------------|-----|

| 7.2 Future Work                  | 126 |

| REFERENCES | 127 |

|------------|-----|

| VITA       | 133 |

## LIST OF TABLES

| Table 3.1: Summary of failure rate estimator example                                  |

|---------------------------------------------------------------------------------------|

| Table 3.2: Selected cubes covering for example 1.    45                               |

| Table 3.3: Cubes covering for example 2.    50                                        |

| Table 4.1: Double-cube divisors along with their bases for $f = ade + ag + bcde +$    |

| bcg                                                                                   |

| Table 4.2: Failure rate for two implementations of $f_2 = ab + ac + de$ for different |

| minterms probabilities                                                                |

| Table 4.3: Failure rate for two implementations of $x = abf + adef + cde$ for         |

| different minterms probabilities                                                      |

| Table 6.1: primary inputs, primary outputs and area for benchmark circuits            |

| Table 6.2: Size of gates.    83                                                       |

| Table 6.3: Failure rate results for MCNC combinational benchmark circuits -           |

| Injecting 1 fault104                                                                  |

| Table 6.4: Failure rate results for MCNC combinational benchmark circuits -           |

| Injecting 5 faults 105                                                                |

| Table 6.5: Failure rate results for MCNC combinational benchmark circuits -           |

| Injecting 10 faults 106                                                               |

| Table 6.6: Area overhead for combinational benchmark circuits                         |

| Table 6.7: Overall averaged failure rate results for benchmark circuits               |

| Table 6.8: Failure rate results for combinational benchmark circuits using            |

| Algorithm 2 - Injecting 1 fault110                                                    |

| Table 6.9: Failure rate results for combinational benchmark circuits using            |

| Algorithm 2 - Injecting 5 faults 111                                                  |

| Table 6.10: Failure rate results for combinational benchmark circuits using           |

| Algorithm 2 - Injecting 10 faults 112                                                 |

| Table 6.11: Area reduction for combinational benchmark circuits using Algorithm       |

| 2                                                                                     |

| Table 6.12: Overall averaged failure rate overhead for benchmark circuits using       |

| Algorithm 2114                                                                        |

| Table 6.13: Overall results of failure rate for benchmark circuits using fixed |    |

|--------------------------------------------------------------------------------|----|

| number of faults 1, 5 and 10 11                                                | .6 |

| Table 6.14: Overall results of failure rate for benchmark circuits using fixed |    |

| number of faults 1, 5 and 10 at the original version                           | .7 |

| Table 6.15: Area overhead for combinational benchmark circuits using proposed  |    |

| technique compared to original circuits11                                      | .8 |

| Table 6.16: Failure rate results for Ranking-based Don't Care comparison 12    | 20 |

| Table 6.17: Area overhead of Ranking-based DC compared to Algorithm 1          |    |

| versions12                                                                     | 20 |

| Table 6.18: Failure rate results for TMR experiments                           | 22 |

| Table 6.19: Area overhead for TMR experiments.    12                           | 22 |

## LIST OF FIGURES

| Figure 1.1: Upsets hitting combinational and sequential logic                          | 4  |

|----------------------------------------------------------------------------------------|----|

| Figure 1.2: Single Event Upset (SEU) effect in an SRAM memory cell                     | 5  |

| Figure 1.3: NMOS transistor hit by ion particle.                                       | 6  |

| Figure 1.4: Soft error generation due to alpha particle strike.                        | 8  |

| Figure 1.5: Logical masking.                                                           | 9  |

| Figure 1.6: Electrical masking [9].                                                    | 10 |

| Figure 1.7: Latching window masking [9]                                                | 11 |

| Figure 2.1: Von Neumann's logic for 2-input NAND gate with N = 4                       | 22 |

| Figure 2.2: A Triple Modular Redundant (TMR) structure                                 | 23 |

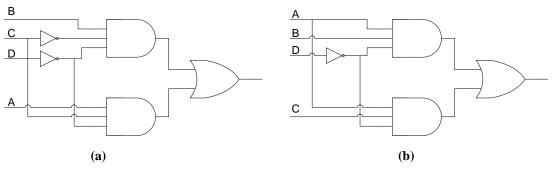

| Figure 2.3: Quadded logic example: (a) original circuit, (b) quadded logic circuit     | 25 |

| Figure 2.4: Partial error masking scheme as proposed in [33].                          | 26 |

| Figure 2.5: HICC module [34]                                                           | 28 |

| Figure 3.1: Extracting sub-circuits' algorithm                                         | 35 |

| Figure 3.2: Example of 1-level window.                                                 | 37 |

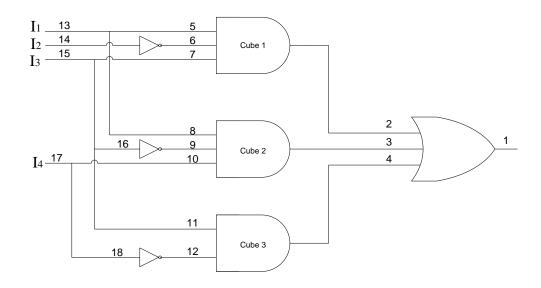

| Figure 3.3: Failure rate estimator example.                                            | 40 |

| Figure 3.4: Two-level failure rate estimator algorithm                                 | 43 |

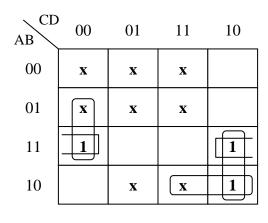

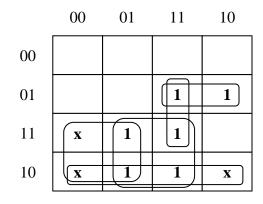

| Figure 3.5: K-map for example 1                                                        | 45 |

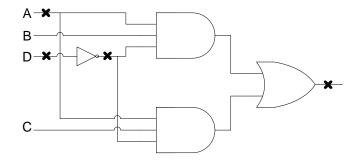

| Figure 3.6: Different implementations for example 1.                                   | 47 |

| Figure 3.7: Faulty wires in example 1 for minterm 1110 for second implementation       | 47 |

| Figure 3.8: K-map for example 2                                                        | 50 |

| Figure 3.9: Duplication of one cube off-phase.                                         | 52 |

| Figure 3.10: Duplication of one cube on-phase.                                         | 53 |

| Figure 3.11: Algorithm 1- Two-level tool to enhance fault tolerance                    | 54 |

| Figure 4.1: Fast Extraction algorithm for area optimization [50]                       | 61 |

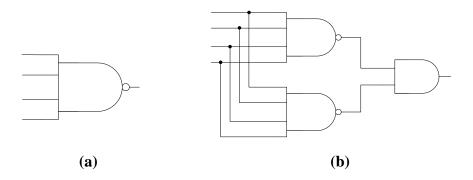

| Figure 4.2: Single-cube extraction example: (a) $fl = abc + abd + abe + kg$ , (b) t    |    |

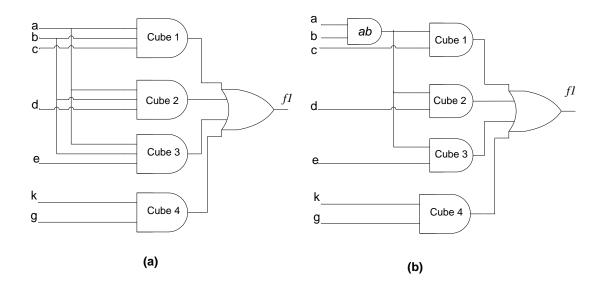

| = ab, $fl = tc + td + te + kg$                                                         | 62 |

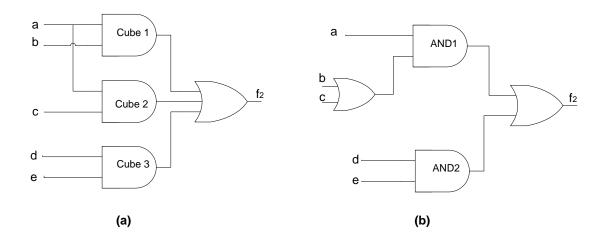

| Figure 4.3: Double-cube extraction example: (a) $f_2 = ab + ac + de$ , (b) $t = b+c$ , |    |

| $f_2 = a t + d e$                                                                      | 65 |

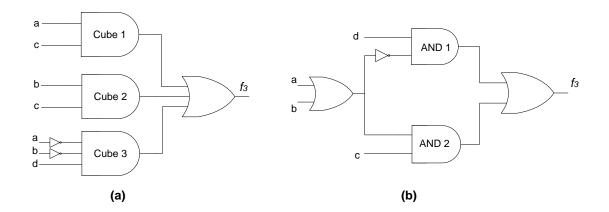

#### Figure 4.4: Double-cube extraction with complement example: (a) $f_3 = ac + bc + bc$

## **THESIS ABSTRACT (ENGLISH)**

| NAME:           | KHALED ABDEL-KARIM DAUD |    |      |       |          |

|-----------------|-------------------------|----|------|-------|----------|

| TITLE:          | SYNTHESIS               | OF | SOFT | ERROR | TOLERANT |

|                 | COMBINATIONAL CIRCUITS  |    |      |       |          |

| MAJOR FIELD:    | COMPUTER ENGINEERING    |    |      |       |          |

| DATE OF DEGREE: | JANUARY 201             | 11 |      |       |          |

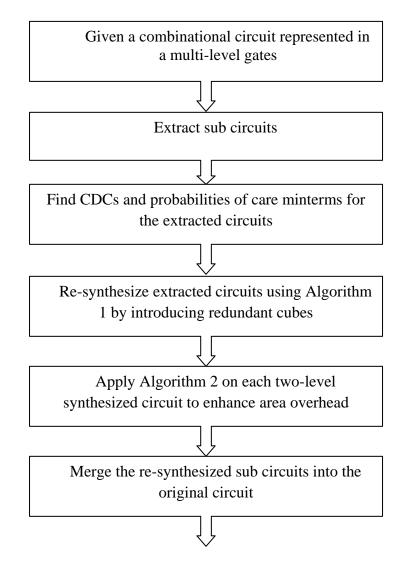

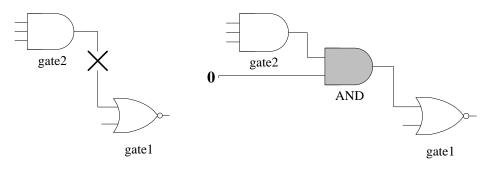

Due to current technology scaling trends, digital designs are becoming more sensitive to radiation-induced particle hits resulting from radioactivity decay and cosmic rays. A low-energy particle can flip the output of a gate, resulting in a soft error if it's propagated to a circuit output. Thus, soft error tolerance has become an important criterion in digital system design. This work is directed to analyze, model and design combinational circuits for soft error tolerance. A simulation based method to reduce the soft error failure rate in combinational logic circuits is proposed. This method maximizes the probability of logical masking when a soft error occurs. This is done by extracting sub-circuits from the original multi-level circuit and then re-synthesizing each extracted sub-circuit to increase fault masking. After that, the re-synthesized sub-circuits are merged back to the original circuit. Therefore, the overall reliability of the original circuit will be enhanced as well. We present a two-level synthesis scheme to maximize soft error masking that is applied on each extracted sub-circuit. This scheme provides a heuristic that first finds the best irredundant set of cubes to cover an extracted sub-circuit minterms. This cover maximizes fault masking against single fault especially for minterms with high

probability of occurrence. Then, an extra number of cubes can be added as redundant cubes to the cover such that they have a significant effect on maximizing error masking. Reliability driven fast extraction is also proposed to enhance area overhead of synthesized two-level circuits. Experimental results on some MCNC combinational benchmarks show that on average, a failure rate reduction of 52% is achieved compared to the original circuits. The area overhead on average is found to be 61% of the original circuit.

**Keywords**: fault tolerance, soft errors, transient faults, single event upset (SEU), single event transients (SET), nano technology, robust system design, circuit reliability, combinational circuits, soft error rate.

### **THESIS ABSTRACT (ARABIC)**

ملخص الرسالة

| خالد عبد الكريم داود                             | الاسم:         |

|--------------------------------------------------|----------------|

| تصميم دوائر توافقية ذات وقاية من الاخطاء اللحظية | عنوان الرسالة: |

| هندسة الحاسب الآلي                               | التخصص:        |

| يناير 2012 م                                     | تاريخ التخرج:  |

مع تقدم تقنية النانو، أصبحت الانظمة الرقمية أكثر قابلية للأخطاء المستحثة بواسطة الذرات الأيونية. حيث أنه يمكن لجسيم ذو طاقة منخفضة أن يغير قيمة بوابة منطقية معينة، فينتج عن ذلك ما يسمى الخطأ اللحظي إذا انتقل هذا التغيير إلى مخارج الدائرة. وبالتالي، أصبحت الوقاية من الأخطاء اللحظية معيارا مهما في تصميم الأنظمة الرقمية. هذا التغيير إلى مخارج الدائرة. وبالتالي، أصبحت الوقاية من الأخطاء اللحظية معيارا مهما في تصميم الأنظمة الرقمية. هذا التغيير إلى مخارج الدائرة. وبالتالي، أصبحت الوقاية من الأخطاء اللحظية معيارا مهما في تصميم الأنظمة الرقمية. هذا التغيير إلى مخارج الدائرة. وبالتالي، أصبحت الوقاية من الأخطاء اللحظية معيارا مهما في تصميم الأنظمة الرقمية. هذا البحث موجه لتحليل وتمثيل وتصميم الدوائر التوافقية وذلك لزيادة وقايتها من الأخطاء اللحظية، هذه الطريقة بالطبع المستحدث أيونيا. اقترحنا طريقة تقلل نسبة الخطأ في الدوائر التوافقية بالنسبة للأخطاء اللحظية، هذه الطريقة يتم مبنية على زيادة احتمالية إلغاء أثر الخطأ اللحظي بالاعتماد على التركيب المنطقي للدائرة. في هذه الطريقة يتم استخراج دوائر أصغر من الدائرة الأصلية، و اعادة تصميم هذه الدوائر المستخرجة بحيث تكون اكثر وقاية من الأخطاء اللحظية. ومن ثم يتم إرجاع الدوائر المعاد تصميمها إلى الدائرة الأصلية. التقنية المقترحة لإعادة تصميم الدوائر المعاد تصميمها إلى الدائرة الأصلية. التقنية المقترحة لإعادة تصميم الدوائر المستخرجة يون ألكم وقاية من الدوائر المستخرجة. هذه الدوائر المستخرجة يون أقصى قدر ممكن من الحماية ضد خطأ لحظي واحد خاصة بالنسبة للمدخلات ادائرة المستخرجة. هذه الدوائر المعادة الخبي واحد في من الحماية الدوئر. المعاد واخر ألمجموعة بحيث يكون هناك تحسين معتبر في الحماية. اقترحنا العالية أخرى مبنية على خاورزمية الاستخراج السريع التي يمكن استخدا واحد الغيل المساحة الزائذة الناتجة عن تطبي في تقلي أفر أقصى قدر ألمانة حدود مكررة للمجموعة بحيث يكون هناك تحسين معتبر في الحماية. العالية أخرى مبنية على خوارزمية الاستخراج السريع التي يمكن استخدامها لتقليل المساحة الزائذة الناتجة عن تطبيق تقلي في تقنية أخرى مبنية على الدوائر المستخرجة. نتائج التجارب على الدوائر التوافقية MCNC مساحة الإضافية ما يقارب أ6% معد ما الحواي الخرية الحافية مدوا الأصلية. ما ساحة المابعة ما يمربق الأمري

الكلمات الرئيسة: التسامح في الأخطاء أو العيوب، الأخطاء اللينة، العيوب اللحظية، الحدث الأحادي القالب، الحدث الأحادي اللحظي، تقنية النانو، تصميم الأنظمة القوية، اعتمادية الدوائر، الدوائر التوافقية، معدل الأخطاء اللحظية.

## Chapter 1

## **INTRODUCTION**

Reliability with respect to soft errors has become a critical issue in digital circuits. In the past few decades, CMOS technology has reached high scaling advancement. This advancement is consistent with Moore's law [1] which states that the number of transistors that can be placed in a chip doubles every 18 months. As CMOS technology is improving and reaching the nanometer scale, quantum mechanical effects come into the picture generating many challenges for additional scaling of CMOS devices. This has motivated researchers to investigate new technologies for circuit design. Circuits and devices based on nanotechnology-based fabrication are expected to offer extra density and performance that takes electronic circuits to next higher integration level. According to [2], nanoelectronics can operate at very high frequencies (of the order of THz) and achieve very high densities (10<sup>12</sup> devices per cm<sup>2</sup>). Several researchers have presented novel successful nanoelectronic devices. These devices include carbon nano-tubes(CNT) [3], silicon nano-wires (NW) [4-5], and quantum dot cells [6].

Nanoscale devices are limited by several characteristics. The most dominant characteristics are the devices' higher defect rates and increased susceptibility to soft errors. These limiting characteristics are due to two sources [7]:

- One source is the inherent randomness and imprecision in the bottom-up manufacturing process, which results in a large number of defective devices during the fabrication process.

- The second source is the reduced noise tolerance of these devices which is responsible for inducting device malfunctions by external influences like EMI (electromagnetic interference), thermal perturbations and cosmic radiations.

In general, errors can be categorized as either permanent or transient errors. Permanent (hard) errors may occur during manufacturing process or during the lifetime of a device. Transient (soft) errors can arise due to multiple sources like high-energy particles, coupling, power supply noise, leakage and temporal circuit variations. The transient error can last for one or many clock cycles. Both types of errors affect the circuit reliability if they aren't tolerated. Reliability of a circuit can be defined as the ability to function properly despite the existence of such errors. It's required to improve the tolerance against permanent and transient errors in order to enhance circuit reliability.

In this work, we address the fault tolerance of transient (soft) errors for combinational circuits. In the following sections, we will introduce the combinational circuit model as well as the nature of transient faults. After that, a glance will be given about this work motivation, objectives and contributions. Then we will finish by thesis organization.

#### **1.1 Combinational Circuits**

Logic circuits for digital systems may be combinational or sequential. A combinational circuit consists of logic gates (AND, OR, NOR, NAND... etc) whose outputs at any time are determined by combining the values of the applied inputs using logic operations. A combinational circuit performs an operation that can be specified logically by a set of Boolean expressions. Sequential circuits employ storage elements in addition to using logic gates. In combinational circuits, the output is a pure function of the present input only. This is in contrast to sequential logic, where the output depends not only on present input but on the history of the input as well.

A combinational circuit consists of input variables, output variables, logic gates and interconnections. The interconnected logic gates accept signals from the inputs and generate signals at the output. The n input variables come from the environment of the circuit, and the m output variables are available for use by the environment. Each input and output variable exists physically as a binary signal that represents logic 1 or logic 0.

#### **1.2** Soft Errors in Nano-Scale Circuits

Transient faults (SET/SEU) are mainly caused by cosmic-ray neutrons or alpha particles through the materials of ICs. They can hit either in the combinational logic or flip flops of a sequential circuit block. If it happens in the combinational logic, it will result in a Single Event Transient (SET) fault. On the other hand, if it happens in the memory cell itself, it will result in a Single Event Upset (SEU) fault. Both of SET and SEU faults cause a major implication and should be treated properly.

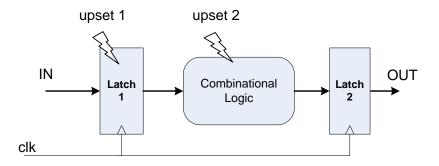

Figure 1.1 shows a typical structure for most sequential circuits. In this figure, the first latch releases data to combinational logic at the rising or falling clock edge, and then combinational logic performs operation. Latch 2 stores result outputs at rising or falling clock edge.

Figure 1.1: Upsets hitting combinational and sequential logic.

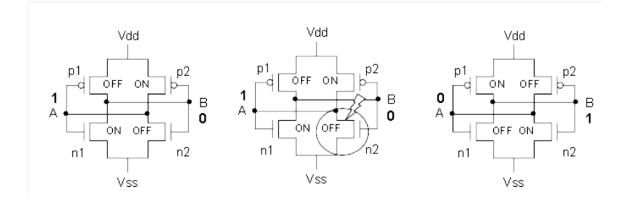

When a charged particle strikes a sensitive region in a memory cell, such as a drain in an OFF transistor, a transient current pulse is generated that can cause a bit flip in the memory cell. A memory cell stores two states either logic 0 or 1 values. In each state, two transistors are ON and two are OFF. Figure 1.2 illustrates how an energetic particle can reverse the state of transistors in the circuit, which results in a bit-flipping.

Figure 1.2: Single Event Upset (SEU) effect in an SRAM memory cell.

A single event transient (SET) occurs when a charged particle hits the combinational logic, resulting in a transient current pulse. This can change the logic level of a gate. If this transient has enough width and magnitude, it can result in an erroneous value to be latched. Once it is latched, a single event transient becomes a single event upset (SEU). However, there are certain conditions that are to be met for this transient to propagate and be latched by the memory element. These conditions are discussed later.

It is worth to mention that a single SET can produce multiple transient current pulses at the output. This is due to the logic fan-out in the circuit. Hence, SETs can produce multiple SEUs in the memory elements.

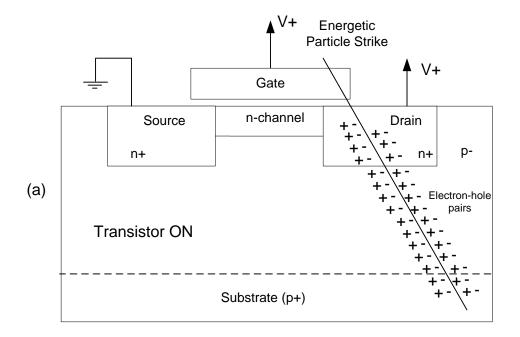

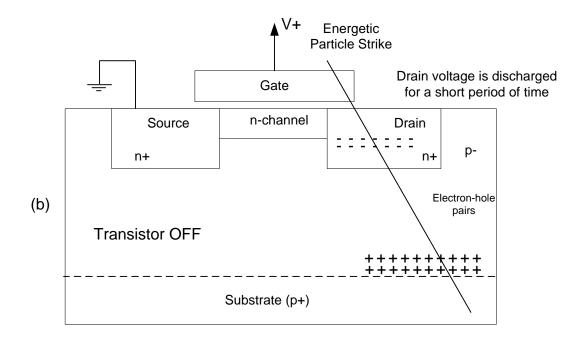

For more details on how a transient soft error can change the state of transistor, consider the NMOS transistor shown in Figure 1.3 (a). The transistor is assumed to be in the ON state. During normal operation, a current will flow from the drain to the source that makes the transistor ON. If an alpha particle strikes the drain of the NMOS transistor, it loses its energy as it travels along the path inside the semiconductor material.

Figure 1.3: NMOS transistor hit by ion particle.

In this period, the particle ionizes the material around it, which results in the generation of electron-hole pairs. If there is no voltage applied to the drain of transistor, electrons and holes are recombined. However, since the transistor is in the ON state, electrons and holes are separated by the voltage applied on the drain. Consequently, the holes are collected by the (p+) substrate and the electrons are collected by the drain. This results in a prompt component of current at the drain in shape of negative pulse; this is shown in Figure 1.3 (b). If this prompt current has a high enough charge, this will lead to discharging the voltage at the drain for a very short period of time in order of 100 to 200 picoseconds [8]. Hence, the state of transistor is changed to OFF in that period of time.

In the previous generations of CMOS technologies, the sizes of CMOS transistors were large enough to neglect the effect of the resulting prompted current. However, with device dimensions shrinking to nanometer scale, SET and SEU faults are no longer considered a small attenuation. Instead, they will be considered as normal circuit signals. Therefore, tolerance of soft and transient errors is no longer limited to specific applications like aerospace applications, and they can no longer be ignored.

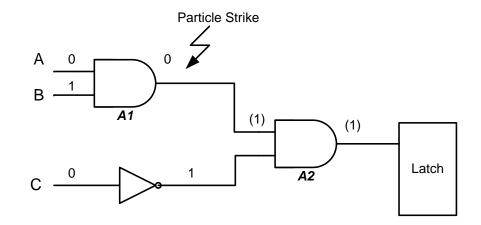

In order to give insight into how a particle strike hits in the combinational logic can generate wrong values stored in latches, consider the circuit in Figure 1.4. Assume that the inputs of the AND gate Al are A = '0' and B = '1'. During normal conditions, the output of Al is '0'. Also the output of gate A2 is '0'. Therefore, the memory element latches a logic value of '0' during normal operation. Let us consider a particle strike at the output node of gate Al which results in the change of logic level at the output of Al. The particle strike in this case is assumed to have sufficient pulse width and magnitude so that it propagates through the gate A2 and gets latched by the memory element. Now we have

a wrong value of '1' latched by the memory element instead of '0'. This type of error is called soft error.

Figure 1.4: Soft error generation due to alpha particle strike.

Although the incident alpha particles cause voltage transients, these transients must propagate through a certain path to get latched and result in soft errors. This path is called critical path. The following are three types of masking that shield the SEUs from propagating.

- Logical Masking

- Electrical Masking

- Latching window masking

#### Logical Masking

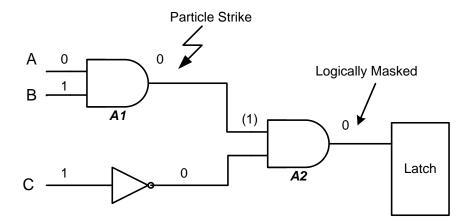

Logical masking prevents the SET from propagation from fault location to primary outputs of circuit because of path gate inputs that stop logical transition of the gate's output. As shown in Figure 1.5, there is a particle strike at the output of the A1 gate which results in a wrong logic of '1' instead of logic '0'. This wrong value is one of the inputs of the A2 gate.

Figure 1.5: Logical masking.

When one of the inputs of A2 gate is tied to logic '0', the output of A2 gate is always logic '0' irrespective of the other input. Therefore, this input of A2 gate is called controlling input. The transient caused by the alpha particle strike is logically masked. Hence a correct value is latched by the following memory element.

#### **Electrical Masking**

Electrical masking attenuates or completely masks the SET signal due to electrical properties of gates. The voltage transient caused by the particle strike is attenuated as it propagates through a series of gates. The transient gets attenuated to an extent where it is ignored by the following memory element.

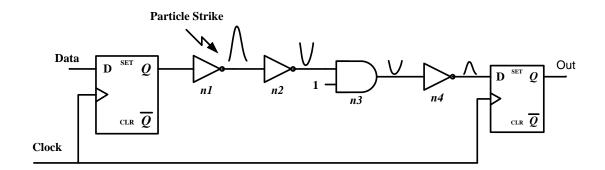

Figure 1.6: Electrical masking [9].

As shown in Figure 1.6, the voltage pulse generated at the output of the gate n1 attenuates as it passes through gates n2, n3 and n4. The attenuation is due to the parasitic capacitance of succeeding gates. The pulse with duration more than the gate delay attenuates as it propagates [9].

#### Latching Window Masking

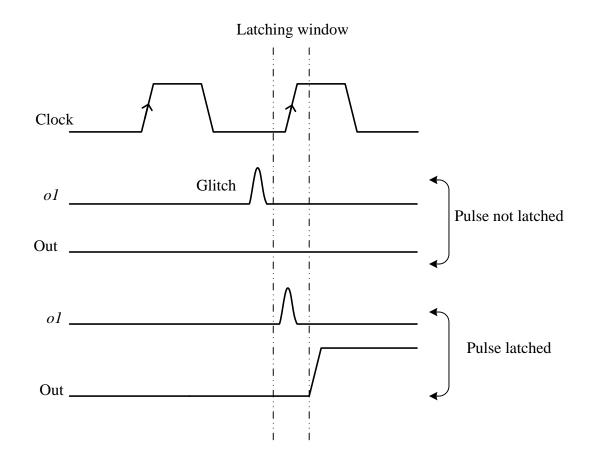

In latching window masking, if a SET doesn't arrive "on time" then it will be masked; this depends on hold and setup times of the target memory element. This is a timing related masking technique. For a voltage transient to get latched by a memory element, the pulse should be available exactly at the latching window. The transient is masked if it arrives before or after the latching window. As shown in Figure 1.7, the value of 'out' changes only when the glitch is available at the latching window. In all the other cases, the output is error free.

Figure 1.7: Latching window masking [9].

These three mechanisms can prevent some SETs from being latched. However, the continuous scaling trends limit the effectiveness of the electrical and latching window masking properties.

#### **1.3 Research Motivation**

With the advancement in technology reaching 0.35 microns and below, systems became more susceptible to soft errors. Soft errors induced by ion particles are no longer considered a small attenuation and can no longer be neglected. Therefore, techniques are needed to tackle soft faults in both combinational and sequential circuits. Many techniques were proposed by researchers to enhance circuit reliability against soft errors. In this work, a method is proposed to enhance combinational circuits' reliability. This is achieved by synthesizing the circuit in order to maximize the probability of logical masking when a soft error occurs.

#### **1.4 Problem Statement and Thesis Objectives**

Problem statement is specified as well as the thesis main contributions in the following sub-sections.

#### **1.4.1 Problem Statement**

The general problem statement is: *Given a combinational circuit, we would like to increase its reliability against transient errors with minimum area overhead.*

#### 1.4.2 Thesis Objectives

The objective of this work is to investigate the design of soft error tolerant combinational circuits based on maximizing the probability of logical masking when a soft error occurs. This is done by extracting small sub-circuits from the original circuit. Then for each extracted sub-circuit, the probabilities of its input vectors to occur are computed. Next, developed tool is applied on each extracted sub-circuit to produce a new two-level sub-circuit. Logical masking for one fault is maximized in the new two-level sub-circuit. Finally, the new synthesized sub-circuits are merged back to the original circuit. The main work objectives can be summarized as:

- Design a two-level tool that maximizes fault masking against the occurrence of a single fault in a circuit. Maximizing masking is based on the probabilities of sub-circuit input vectors to occur.

- Design a multi-level tool that reduces the area overhead result after applying the two-level tool. Applying this multi-level tool is supposed to have low impact on the reliability enhancement achieved.

- Design a framework to be used in order to apply the previous two techniques on the original circuit.

#### **1.5** Thesis Contributions

To achieve the thesis objectives, the contributions of this thesis can be summarized as follows:

- Implement a tool for extracting sub-circuits from an original multi-level circuit, finding inputs don't cares, and the probability of care minterms for each extracted sub-circuit.

- Implement a tool for computing soft error reliability for combinational circuits based on Monte Carlo simulation [10]. The objective of this tool is to find the failure rate of a combinational circuit as more faults are observed in the circuit.

- Develop and implement an algorithm to enhance reliability of combinational circuits based on enhancing reliability of each individual sub-circuit. A two-level synthesis heuristic is proposed and applied on each extracted sub-circuit that attempts to find the best cover that maximizes fault masking while keeping area overhead minimum.

- Develop and implement a multi-level tool that reduces the area overhead resulting after applying the two-level tool. This should have a low impact on fault masking achieved by the two-level tool.

- Evaluate the proposed approaches in terms of failure rate and area overhead.

#### **1.6 Thesis Organization**

The thesis is organized into the following chapters. Chapter 2 starts with a background about the current fault tolerance methods. An exploration of different approaches to solve this problem at different levels of abstraction will be presented.

Chapter 3 discusses in detail the proposed two-level technique, namely Algorithm 1, which enhances the logical masking of a circuit against a single fault. In Chapter 4, detailed discussion is presented on the proposed multi-level technique, namely Algorithm 2. Chapter 5 describes the simulation framework used to evaluate algorithms proposed in Chapter 3 and Chapter 4. Chapter 6 presents the experimental results along with discussion. The thesis finally concludes in Chapter 7, where the proposed solutions are summarized, with a list of some potential improvements as a future work.

## Chapter 2

## LITERATURE REVIEW

In this chapter, definitions regarding fault tolerance are reviewed. Then, a survey of the current methods to tolerate faults in combinational circuits is presented.

#### 2.1 Definitions

In the next few subsections, some terms are defined. Those terms are used to describe when electronic systems fail. Throughout the thesis, many of those terms are used.

#### 2.1.1 Defects, Faults and Errors

The definitions of defects, errors and faults terms as defined in [11] are presented.

#### Defects

A defect in the electronic system is the unintended difference between the implemented hardware and its intended design. Some typical defects in VLSI chips are:

- Process Defects missing contact windows, parasitic transistors, oxide breakdown.

- Material Defects bulk defects (cracks, crystal imperfections), surface impurities.

- Age Defects dielectric breakdown, electro-migration etc.

- Package Defects contact degradation, seal leaks.

Defects occur either during manufacturing or during the use of devices. Repeated occurrence of the same defect indicates the need for improvement in the manufacturing process or the design of the device.

#### Faults

A representation of a "defect" at the abstracted function level is called a fault. The difference between a defect and a fault is rather subtle. They are the imperfections in the hardware and function respectively.

#### **Errors**

A wrong output signal produced by a defective system (or circuit) is called an error. An error is an effect whose cause is some "defect". Fabrication defects, fabrication errors and physical failures are collectively termed as physical faults [11]. According to their stability in time, physical faults can be classified as:

- *Permanent faults*: They are those which are always present after their occurrence.

- Intermittent faults: They are those which exist only during some intervals.

- *Transient faults*: They are one-time occurrence (also known as Single Event Upsets (SEUs) or Single-Event Transients (SETs)) which are caused by a temporary change in some environment factor e.g., due to α-particle radiation etc.

#### **2.1.2 Defect (or Fault) Models**

In order to simulate the effect of faults in the circuit, many fault models have been proposed. Those models are presented in different levels of abstraction. Examples of such models are: stuck-at defect (or fault) model, *stuck open and stuck-short defect (or fault) model, bridging defect (or fault) model* and *crosspoint defect (or fault) model*. In this work, a single stuck-at fault model is used. The interested reader can refer to [11] for other fault models. In the stuck-at fault model, a fixed value of 0 or 1 is assigned to a single line in the circuit. A single line can be an output or an input of a gate. Single stuck -at faults are the most famous because they are simple and model many types of defects. They are also known as stuck-at-1 and stuck-at-0 faults.

#### 2.1.3 Failure Rate

Failure rate of a system represents the regularity at which a system fails. It can be defined as the total number of failures within an item population, divided by the total time expended by that population, during a particular measurements interval under stated conditions [12]. In this study, failure rate is redefined as: the total number of experiments in which a circuit fails divided by the total number of performed experiments.

Mainly, in semiconductor industry, the Failures In Time (FIT) rate is used to represent the failure rate of a system. It represents the expected number of failures in one billion  $(10^9)$  hours of device operation. In other words, 1000 devices for 1 million hours, or 1 million devices for 1000 hours each, or some other combination [13-15].

#### 2.1.4 Reliability

The reliability of a system can be defined as the ability to perform specified function under stated conditions [16]. For hardware systems, the most common way of evaluating reliability is to apply a probabilistic reliability function R(t) that gives the probability that a system is working correctly between time 0 and time t, given certain conditions and correct behavior at time 0.

#### **2.1.5 Fault Tolerance**

A system is fault-tolerant if its programs can be properly executed despite the occurrence of faults [17]. The objective of fault-tolerance is either to mask, or to recover from, faults once they have been detected [18].

#### 2.2 Current Fault Tolerance Methods

In general, two types of techniques are used to reduce soft error failure rate. The first one, *fault avoidance*, in which the defective modules are identified and are replaced by other redundant modules through configuration. The second one, *fault tolerance*, faulttolerant techniques are based on the concept of adding redundancy in order to mask faulty behavior due to faults, defects or errors. Fault-tolerant techniques attempt to maximize the probabilities of the three masking mechanisms, namely, logical, electrical and latching window masking.

Avoidance mechanisms presented in the literature generally exploit fabrication process (device-level) to reduce charge collection [19-23]. Error detection circuits[24-25] can be used to monitor the outputs of the circuit when an error occurs. If it detects an error, the system recovers through rollback and retry to prevent the failures.

The fault-tolerant techniques work on circuit-level or higher levels of abstractions to achieve soft error rate (SER) improvement. Fault-tolerant techniques for combinational circuits can be classified into three major categories: *hardware redundancy*, *synthesis-based*, and *physical characteristics based* techniques.

Hardware redundancy methods are based on adding redundant hardware. Multiple modules are used to represent the same function in order to maximize masking of errors. Multiple copies of either the entire circuit or part of the circuit are used as redundant hardware.

In the synthesis-based techniques, the combinational circuit is restructured in order to maximize masking properties of the circuit. Logical masking is the main masking property to be maximized.

The physical characteristics based techniques attempt to reduce SER based on the physical characteristics to maximize the electrical masking.

In this section, a survey of the current fault-tolerant methods to tolerate SEU/SET in combinational circuits are discussed.

#### 2.2.1 Hardware Redundancy Techniques

#### Von Neumann's Multiplexing

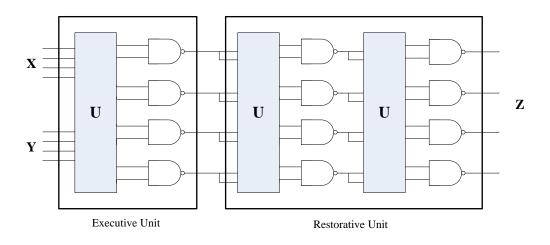

Designing of reliable systems by using redundant unreliable components was initiated by John von Neumann in the 1950s [26]. He proposed a multiplexing technique in which a processing unit is replaced by multiplexed units. Two stages are used to implement a unit: the *executive* stage and the *restorative* stage. The *executive* stage represents the basic function of the unit, while the *restorative* stage is used to correct some of the faulty values of the gates caused by errors in the *executive* stage. In the *executive* stage, unit is replaced by N multiplexed units which have N copies of every input and output of the unit. The inputs randomly pair to feed the N units. Consider the case when the processing unit is a single 2-input NAND gate, with N=4, Von Neumann multiplexing is shown in Figure 2.1. The unit *U* represents a random permutation of the input signals. The two inputs of each NAND gate are selected randomly from the first and second inputs *X* and *Y* respectively. The restorative stage is made using the same technique as in the executive stage. However, the outputs of the executive stage are duplicated and used as inputs for the restorative stage. Note that, this approach will invert the result if it's used only once, thus, two steps are required. By defining some critical level  $\Delta$  such that  $0 < \Delta < 1/2$ , if the number of lines carrying a positive state (logic 1) is larger than  $(1- \Delta)$ .N, he considers it as a positive state of the bundle, if it was less than  $\Delta$ , he interprets it as negative state (logic 0). In cases where the number of positive state lines does not meet either of these criteria, then the output is not decided, and so a fault will occur.

Giving a probability of failure  $\varepsilon$  for each gate, Von Neumann's structure requires a large amount of redundancy and a low error rate for individual gates. For deep logic with a gate failure probability  $\varepsilon = 0.01$  and N = 100, it is shown in [27] that a circuit failure probability in the order of 10<sup>-6</sup> can be obtained. This required amount of redundancy is huge and is considered impractical. In order to reduce this large amount of redundancy, the works in [28-29] combine NAND multiplexing with reconfiguration.

Figure 2.1: Von Neumann's logic for 2-input NAND gate with N = 4.

#### **Triple Modular Redundancy (TMR)**

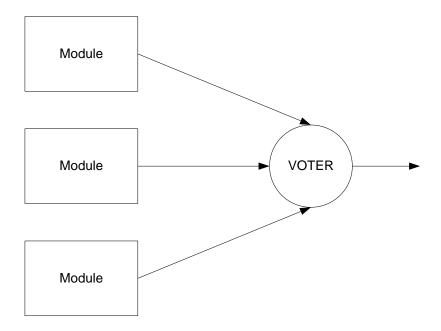

Triple Modular Redundancy is one of the most well-known techniques to tolerate soft/hard errors in combinational circuits [16]. It's a special case of the NMR system. An NMR system (also known as M-of-N system) is a system that consists of N modules and needs at least M of them for proper operation. TMR is a system where M=2 and N=3, which consists of three functionally identical copies of the original circuit that feed a 2-out-of-3 majority voter as shown in Figure 2.2. If 2 modules out of 3 produce expected correct results, then the majority of the modules produces correct results, and so the error in the third module will be masked. However, TMR suffers from high overhead in terms of area and power (more than 200%).

In such a structure, M=2 and N=3 and voter selects the majority vote. If a single voter is used, that voter becomes a critical point of failure and the reliability of the TMR structure is limited by that of the final arbitration unit (i.e., voter), which makes the approach difficult in the context of highly integrated nano-systems [20]. Despite this limitation, TMR is heavily used in practice especially when single faults are needed to be protected. Even in the case of multiple faults, some of these faults could be masked due to electrical and logical masking in each module.

Figure 2.2: A Triple Modular Redundant (TMR) structure.

# **Intervowen Redundant Logic and Quadded Logic**

Pierce[30] suggested another scheme called intervowen redundant logic. This scheme considers two types of faults  $0 \rightarrow 1$  and  $1 \rightarrow 0$  faults. The error correction mechanism in interwoven redundant logic depends on asymmetries in the effects of these two types of binary errors. The effect of a fault depends on the value of the input and the type of gate. Consider a NAND gate, for an instance. If the value of one of the inputs is 0 while it should be 1, the output of NAND gate will be 1 regardless of the values of other inputs. In this case the output will be stuck at 1. On the other hand, if an input value is 1 while it

should be 0, the output will depend on other inputs and the output will not be stuck. The type of faults that cause the output to be stuck is considered as critical; the other type is subcritical in the sense that its occurrence alone does not cause an output error. Hence, alternating layers of NAND (or NOR) gates can correct errors by switching them from critical to subcritical.

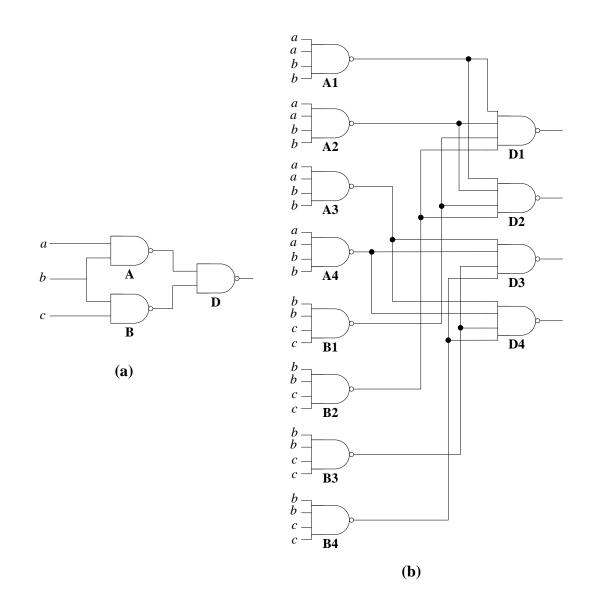

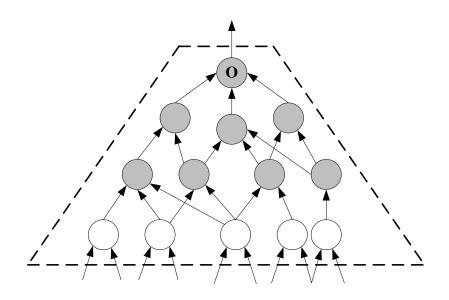

Quadded logic [31-32] is an ad hoc configuration of the interwoven redundant logic. It requires four times as many circuits, interconnected in a systematic way, and it corrects errors and performs the desired computation at the same time. A quadded circuit implementation based on NAND gates replaces each NAND gate with a group of four NAND gates, each of which has twice as many inputs as the one it replaces. The four outputs of each group are divided into two sets of outputs, each providing inputs to two gates in a succeeding stage. The interconnections in a quadded circuit, a single critical error  $(1 \rightarrow 0)$  is correctable after passing through two stages of logic and a single sub-critical error  $(0 \rightarrow 1)$  will be corrected after passing a single stage. In quadded logic, it must be guaranteed that the interconnect pattern at the output of a stage differ from the interconnect patterns of any of its input variables. While quadded logic guarantees tolerance of most single errors, errors occurring at the last two stages of logic may not be corrected. Figure 2.3 shows an example of a quadded logic circuit.

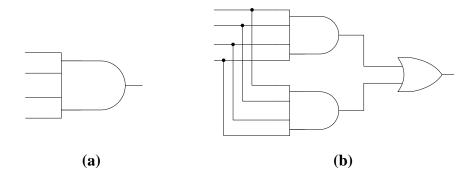

Figure 2.3: Quadded logic example: (a) original circuit, (b) quadded logic circuit.

#### Partial Error Masking Scheme Based on TMR

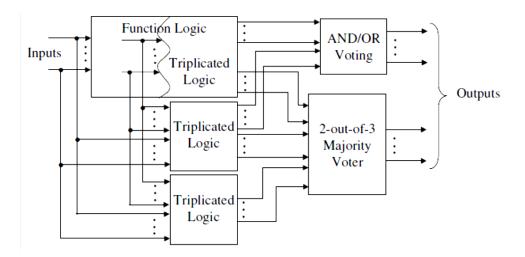

In [33], a partial error masking scheme is proposed based on TMR shown in Figure 2.4. It targets the nodes with the highest soft error susceptibility. Two reduction heuristics are used to reduce soft error failure rate, namely, cluster sharing reduction and dominant value reduction. Instead of triplicating the whole logic as in TMR, only the nodes with highest soft error susceptibility are triplicated, the rest of nodes are clustered and are shared among the triplicated logic. The dominant value reduction heuristic exploits the fact that the logic 0 and logic 1 soft error susceptibility of certain primary outputs is highly skewed. Such outputs are identified and the triplication is replaced by duplication. The 2-out-of-3 majority is replaced by AND (OR) logic.

Figure 2.4: Partial error masking scheme as proposed in [33].

#### Fault Tolerant Based on History Index of Correct Computation

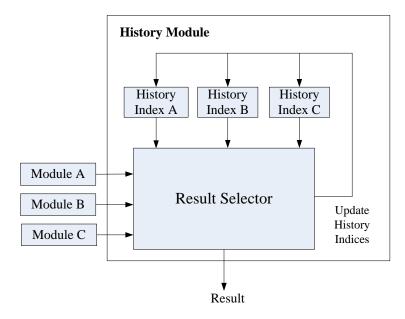

A more recent technique based on TMR is proposed in [34]. A history index of correct computation (HICC) module is used to select the correct result. Instead of using merely majority voting to transmit results, HICC module uses the history indices of redundant units to transmit the correct computation. It represents a measure of a hardware unit's reliability. The most reliable unit is the unit with the highest history index. The computations of other redundant units that implement the same function are ignored.

Figure 2.5 shows an example that demonstrates the concept of the HICC module. In the figure, an ALU module is triplicated as units *A*, *B*, and *C*. The *result selector* decides the unit with the correct result based on stored history index of each unit. The unit with the highest index is considered to be the most reliable unit, and its result is transmitted. When all units have the same history index value, a bitwise majority voting is used to decide the result. After that, the history index of each unit is incremented by 1 if its result is identical to the result of majority; otherwise it's decremented by 1. The HICC logic is distributed within the modules themselves. Hence, unreliable modules are identified simultaneously in real time and are ignored.

Figure 2.5: HICC module [34].

# **Defect-Tolerant** N<sup>2</sup> **Transistor Structure**

In [35], a defect tolerant technique that adds redundancy at the transistor level of the circuit is proposed. The  $N^2$  structure is a generalization of the quadded-transistor structure. In the quadded-transistor structure, each transistor, A, is replaced by a structure that implements either the logic function (AA) + (AA) or the logic function (A+A)(A+A). In such structure, any single transistor defect is tolerated. However, in the  $N^2$  structure, N blocks are connected in series such that each block contains N parallel transistors. If number of defects is less than or equal to (N-1),  $N^2$  structure guarantees the tolerance of all those defects. It was shown that this technique achieves higher defect tolerance compared to gate level based techniques such like quadded logic and TMR.

# **2.2.2 Synthesis-Based Fault Tolerance Techniques**

#### **Localized Circuit Restructuring Tolerant Technique**

In [36], logic masking of errors is increased by taking the advantage of conditions already present in the circuit, such as observability don't cares. Two techniques are used to improve reliability: don't care-based resynthesis and local rewriting. In the first method, high-impact nodes are identified. A node has high impact if many observable faults flow through it. High-impact nodes are used to select areas of the circuit for restructuring, in which a vulnerable node is replicated by adding a single gate. Local rewriting is also used to optimize small sub-circuits to obtain overall area improvements.

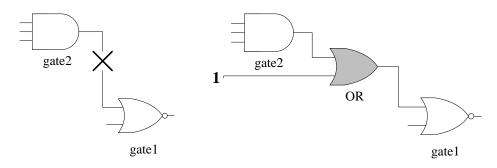

In the first method, logic masking is increased by getting benefit from redundancy already present in the circuit. Covering relationships are identified among existing nodes. Given two nodes x and y, x covers y if and only if x is 1 or a don't-care whenever y is 1. Node x is defined to be an *anti-cover* of node y if y is 1 or a don't-care whenever x is 1. An *impact* measure is defined and calculated for each node. High impact nodes are selected to be redesigned. For a high-impact node x, other nodes which node x covers or anti-covers are found. Given a node y covered by x, redundant logic is added by transforming node x into OR(x,y). Similarly, if x is an anti-cover of y, node x is transformed into AND(x,y). When x is replaced by AND(x,y) all errors that flip x from 0 to 1 will be masked. Likewise, all 1 to 0 errors will be masked by OR(x,y). Covering relation can be implied from nodes' signatures. For a node n, a signature is defined as the sequence of logic values observed at n due to a sequence of K input vectors. Thus, the signature partially specifies the Boolean function of n. For example, suppose x has a

signature sig(x) = 11000 and sig(y) = 11001. By definition, x is an anti-cover of y, because y is 1 whenever x is 1. Therefore, x can be replaced by AND(x,y). And so, all 0-to-1 flips at the third and fourth inputs will be masked. However, if y is replaced by OR(x,y) then all 1-to-0 flips of the first two bits will be masked. Since signatures do not fully capture Boolean functions, SAT solver is used to verify replication of nodes.

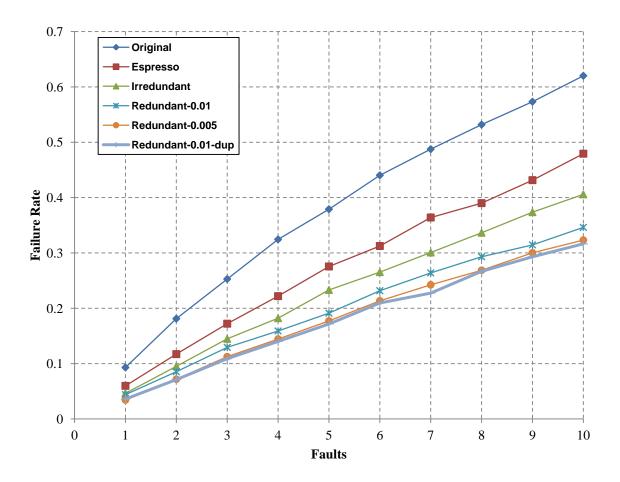

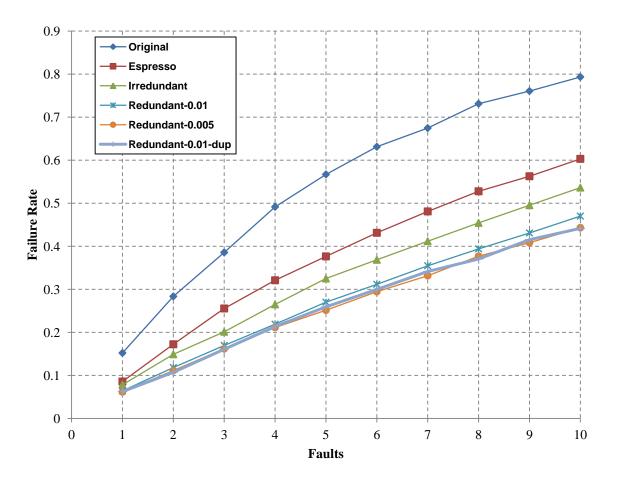

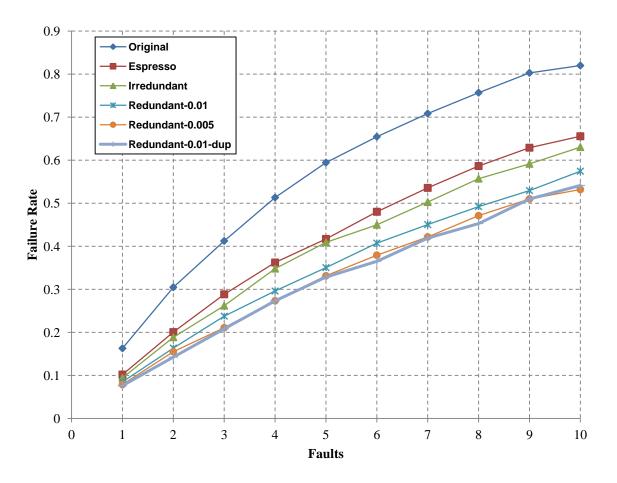

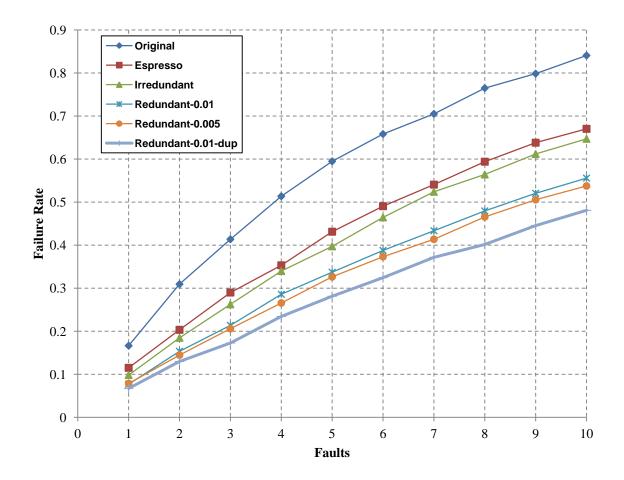

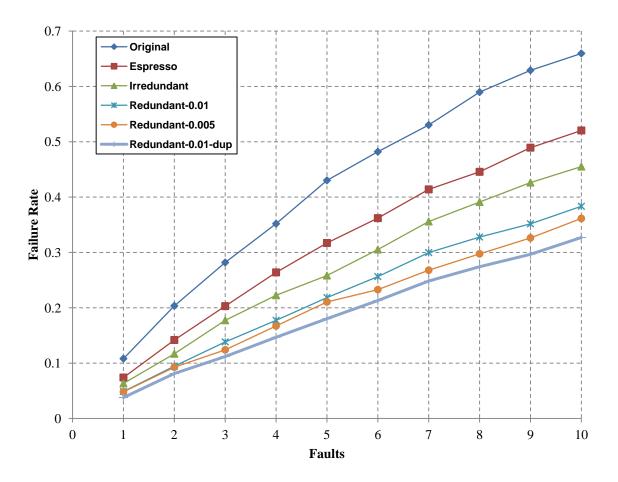

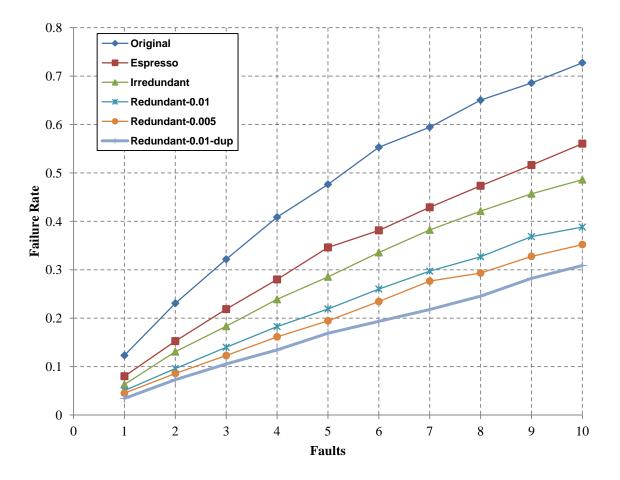

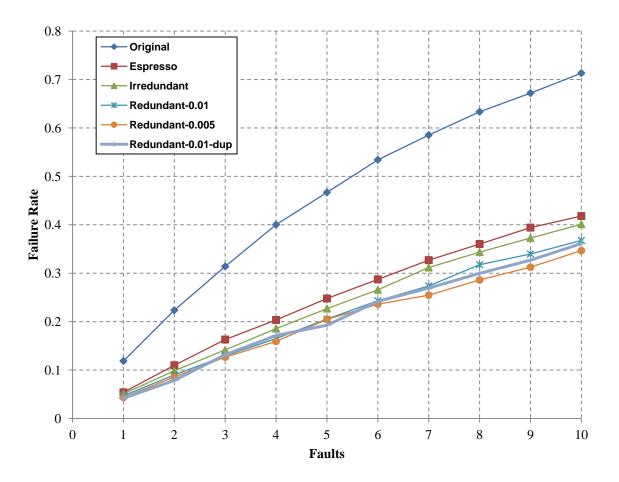

#### **Reliability-Driven Don't Care Assignment Method**