## Parallelization of Rete-Match Algorithm for Distributed Memory Architectures

by

Mohammed A. Tayyib

A Thesis Presented to the

FACULTY OF THE COLLEGE OF GRADUATE STUDIES

KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the Requirements for the Degree of

MASTER OF SCIENCE

In

INFORMATION AND COMPUTER SCIENCE

July, 1996

**INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI

films the text directly from the original or copy submitted. Thus, some

thesis and dissertation copies are in typewriter face, while others may be

from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the

copy submitted. Broken or indistinct print, colored or poor quality

illustrations and photographs, print bleedthrough, substandard margins,

and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete

manuscript and there are missing pages, these will be noted. Also, if

unauthorized copyright material had to be removed, a note will indicate

the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by

sectioning the original, beginning at the upper left-hand corner and

continuing from left to right in equal sections with small overlaps. Each

original is also photographed in one exposure and is included in reduced

form at the back of the book.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white

photographic prints are available for any photographs or illustrations

appearing in this copy for an additional charge. Contact UMI directly to

order.

UMI

BY

Mohammed A. Tayyib

A Thesis Presented to the

FACULTY OF THE COLLEGE OF GRADUATE STUDIES

KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the Requirements for the Degree of

MASTER OF SCIENCE In

Information and Computer Science

JULY 1996

# Parallelizing the Rete-Match Algorithm for Distributed Memory Architectures

## BY Mohammed A. Tayyib

A Thesis Presented to the FACULTY OF COLLEGE OF GRADUATE STUDIES

In Partial Fulfillment of the Requirements for the degree

MASTER OF SCIENCE

King Fahd University of Petroleum and Minerals Dhahran, Saudi Arabia January 1997 UMI Number: 1385298

UMI Microform 1385298 Copyright 1997, by UMI Company. All rights reserved.

This microform edition is protected against unauthorized copying under Title 17, United States Code.

300 North Zeeb Road Ann Arbor, MI 48103

#### KING FAHD UNIVERSITY OF PETROLEUM AND MINERALS DHAHRAN-31261, SAUDI ARABIA

#### **COLLEGE OF GRADUATE STUDIES**

This thesis, written by Mohammed Abdui-Aziz Hassan Tayyib under the direction of his thesis Advisor and approved by his Thesis committee, has been presented to and accepted by the Dean of the College of Graduate Studies, in partial fulfillment of the requirement for the degree of MASTER OF SCIENCE.

**Thesis Committee**

Chairman

Dr. Subbarao Ghanta

Member

Member

ICS Department Chairman

Dean, College of Graduate Studies

13 January 1997

#### ACKNOWLEDGMENT

Acknowledgment is due to King Fahd University of Petroleum and Minerals for support of this research. Acknowledgment is also due to the Exploration and Petroleum Engineering Computer Center (EXPEC) of Saudi Aramco for providing me with all the needed computing facilities to carry out this research.

I wish to express my appreciation to Dr. Mostafa M. Aref who served as my major advisor and the committee chairman who also played a major role in organizing this thesis. I also wish to thank Dr. Subbarao Ghanta for the excellent and interesting five graduate courses he taught me and the fruitful discussions we had over the past five years. These discussions had a major impact on my academic and professional life. Special thanks are also due to Dr. Muslim Bozyigit for his contribution as a thesis committee member.

Last but not least, I would like to express my thanks to all of my family and friends who gave me all the encouragement and support that I needed to carry out this research.

#### **TABLE OF CONTENTS**

| PAGE                                                           |

|----------------------------------------------------------------|

| LIST OF TABLESvi                                               |

| LIST OF FIGURESvii                                             |

| THESIS ABSTRACTix                                              |

| CHAPTER 1: INTRODUCTION1                                       |

| CHAPTER 2: BACKGROUND5                                         |

| 2.1 Production Systems5                                        |

| 2.2 The Rete-Match Algorithm7                                  |

| 2.3 Parallelism                                                |

| 2.4 Serializability & Concurrency Control                      |

| 2.5 Previous work on Parallelizing of the Rete-Match Algorithm |

| CHAPTER 3: THE LANA-MATCH MODEL24                              |

| 3.1 The Lana-Match Computational Model Architecture24          |

| 3.2 The Correctness of the Lana-Match Model                    |

| 3.3 The Lana-Match Model Complexity Analysis                   |

| 3.4 Implementing the Lana-Match Model using PVM and CLIPS39    |

| 3.5 Advantages of the Lana-Match Model42                       |

| 3.6 Disadvantages of the Lana-Match Model                      |

| CHAPTER 4: RESULTS AND ANALYSIS                                       | 46 |

|-----------------------------------------------------------------------|----|

| 4.1 Case-1: Totally Independent Light Action Instantiations           | 48 |

| 4.2 Case-2: Totally Independent Heavy Action Instantiations           | 53 |

| 4.3 Case-3: Enabling Dependent Rules with Additions                   | 58 |

| 4.4 Case-4: Enabling Dependent Rules with Few Additions and Deletion  | 63 |

| 4.5 Case-5: Enabling Dependent Rules with Many Additions and Deletion | 68 |

| CHAPTER 5: CONCLUSION AND FUTURE WORK                                 | 73 |

| 5.1 Conclusion                                                        | 73 |

| 5.2 Directions for Future Research                                    | 74 |

| APPENDIX A: THE RETE-MATCH DETAILS                                    | 77 |

| APPENDIX B: CHARACTERISTICS OF PARALLEL AND DISTRIBUTED               |    |

| PROCESSING                                                            | 82 |

| APPENDIX C: PARALLEL PRODUCTION SYSTEMS CORRECTNESS                   | 85 |

| APPENDIX D: THE LANA-MATCH MODEL IMPLEMENTATION                       |    |

| ALTERNATIVES                                                          | 89 |

| REFERENCES                                                            | 95 |

#### LIST OF TABLES

|                                              | PAGE |

|----------------------------------------------|------|

| TABLE 1: ACTUAL TIME MEASURED IN CASE 1      | 52   |

| TABLE 2: SPEEDUP DATA CALCULATED FOR CASE 2  | 52   |

| TABLE 3: ACTUAL TIME MEASURED IN CASE 2.     | 57   |

| TABLE 4: SPEEDUP DATA CALCULATED FOR CASE 2. | 57   |

| TABLE 5: ACTUAL TIME MEASURED IN CASE 3.     | 62   |

| TABLE 6: SPEEDUP DATA CALCULATED FOR CASE 3. | 62   |

| TABLE 7: ACTUAL TIME MEASURED IN CASE 4.     | 67   |

| TABLE 8: SPEEDUP DATA CALCULATED FOR CASE 4. | 67   |

| TABLE 9: ACTUAL TIME MEASURED IN CASE 5.     | 72   |

| TABLE 10: SPEEDUP DATA CALCULATED FOR CASE 5 | 72   |

#### LIST OF FIGURES

|                                                                   | PAGE |

|-------------------------------------------------------------------|------|

| FIGURE 1: AN EXAMPLE OF A RETE-MATCH NETWORK                      | 9    |

| FIGURE 2: A MORE COMPLEX RETE MATCH NETWORK                       | 10   |

| FIGURE 3: THE RETE-MATCH ALGORITHM OUTLINE                        | 11   |

| FIGURE 4: THE LANA-MATCH MODEL ARCHITECTURE                       | 25   |

| FIGURE 5: THE LANA-MATCH MODEL DATA STRUCTURES                    | 29   |

| FIGURE 6: THE LANA-MATCH MODEL OUTLINES (PART 1)                  | 33   |

| FIGURE 7: THE LANA-MATCH MODEL OUTLINES (PART 2)                  | 34   |

| FIGURE 8: THE LANA-MATCH MODEL OUTLINES (PART 3)                  | 35   |

| FIGURE 9: EXAMPLE OF CASE 1                                       | 49   |

| FIGURE 10: TOTALLY INDEPENDENT LIGHT ACTION RULES, ACTUAL MEASURE | Ð    |

| TIME                                                              | 50   |

| FIGURE 11: TOTALLY INDEPENDENT LIGHT ACTION RULES, SPEEDUP        | 51   |

| FIGURE 12: EXAMPLE OF CASE 2                                      | 54   |

| FIGURE 13: TOTALLY INDEPENDENT HEAVY ACTION RULES, ACTUAL MEASUR  | ŒD   |

| TIME                                                              | 55   |

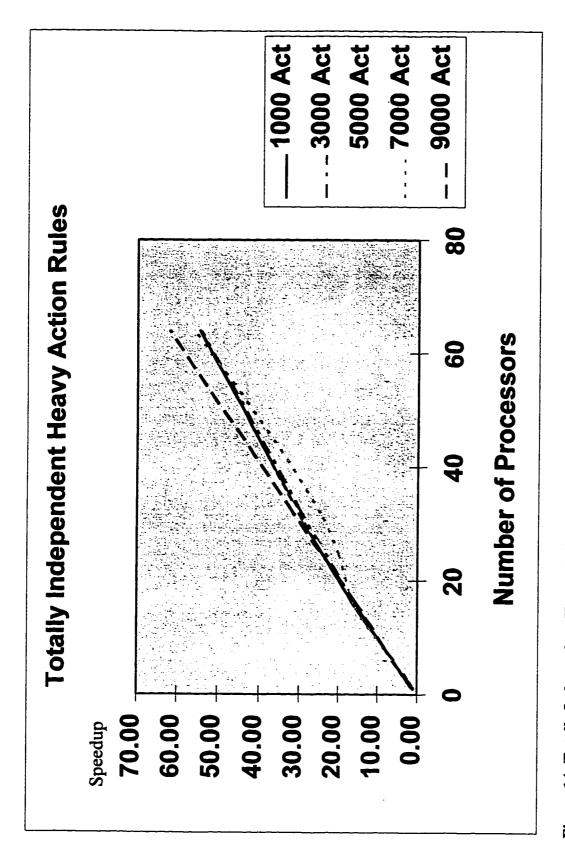

| FIGURE 14: TOTALLY INDEPENDENT HEAVY ACTION RULES, SPEEDUP        | 56   |

| FIGURE 15: EXAMPLE OF CASE 3                                      | 59   |

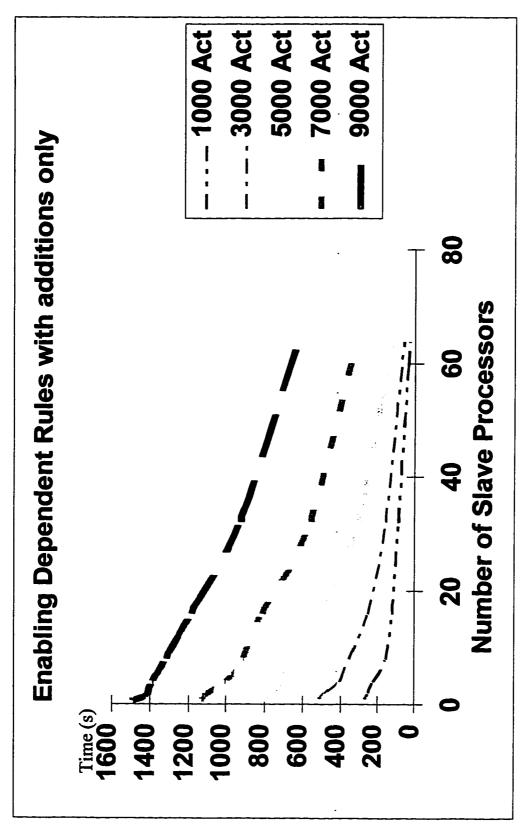

| FIGURE 16: ENABLING DEPENDENT RULES WITH ADDITIONS ONLY, ACTUAL   |      |

| Management That                                                   | 60   |

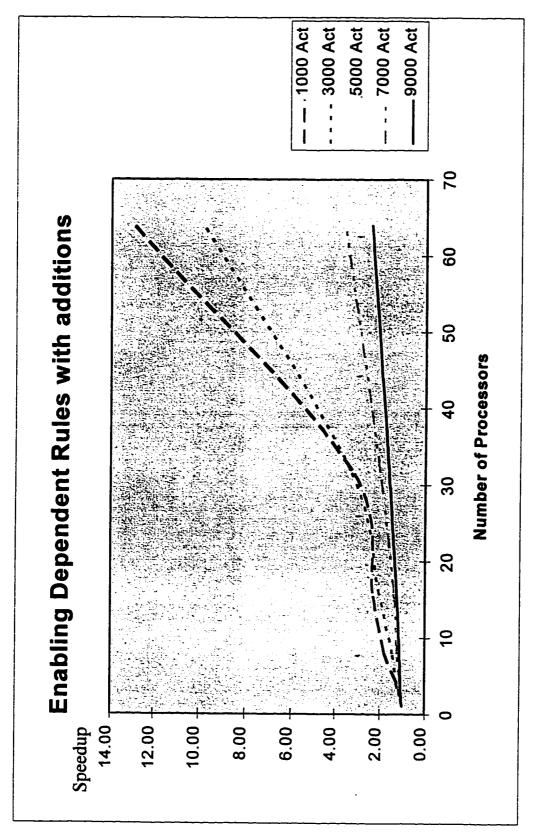

| FIGURE 17: ENABLING DEPENDENT RULES WITH ADDITIONS ONLY, SPEEDUP      |  |

|-----------------------------------------------------------------------|--|

| FIGURE 18: EXAMPLE OF CASE 4                                          |  |

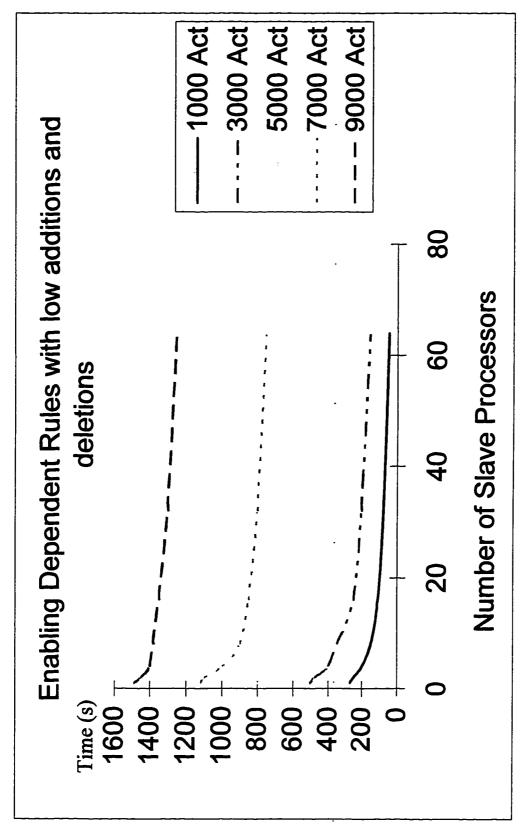

| FIGURE 19: ENABLING DEPENDENT RULES WITH LOW ADDITIONS AND DELETION,  |  |

| ACTUAL MEASURED TIME                                                  |  |

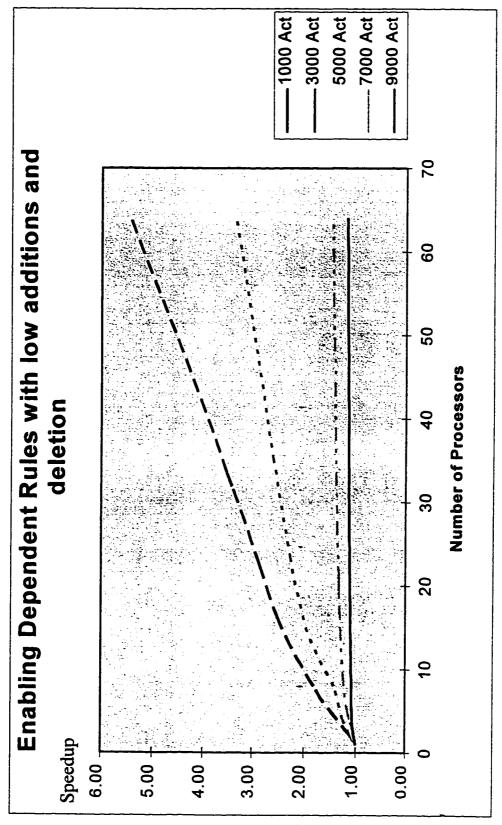

| FIGURE 20: ENABLING DEPENDENT RULES WITH LOW ADDITIONS AND DELETION,  |  |

| SPEEDUP                                                               |  |

| FIGURE 21: EXAMPLE OF CASE 5                                          |  |

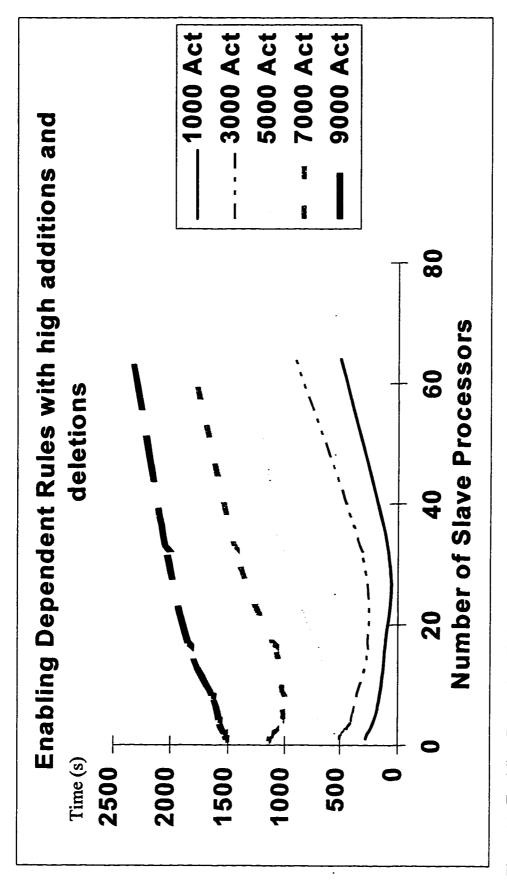

| FIGURE 22: ENABLING DEPENDENT RULES WITH HIGH ADDITIONS AND DELETION, |  |

| ACTUAL MEASURED TIME70                                                |  |

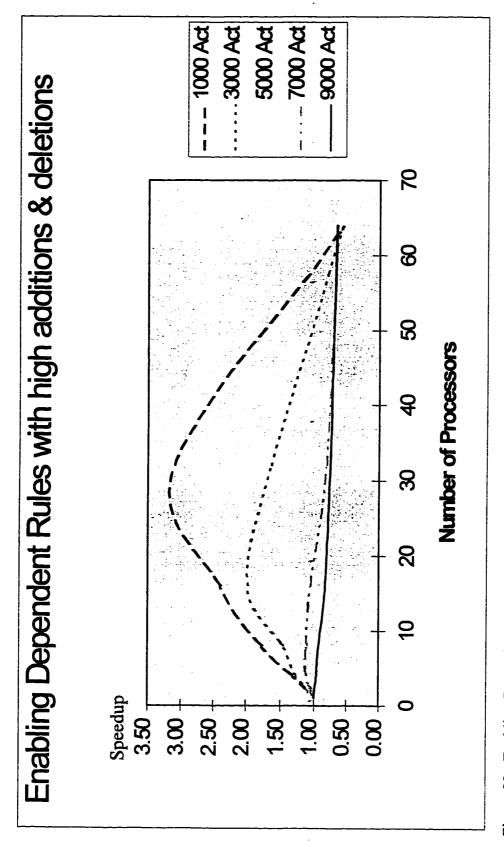

| FIGURE 23: ENABLING DEPENDENT RULES WITH HIGH ADDITIONS AND DELETION, |  |

| SPEEDUP71                                                             |  |

THESIS ABSTRACT

NAME: MOHAMMED ABDUL-AZIZ HASSAN TAYYIB

TITLE: PARALLELIZING THE RETE-MATCH ALGORITHM

FOR DISTRIBUTED MEMORY ARCHITECTURES

MAJOR FIELD: COMPUTER SCIENCE

**DATE:** January 1997

The Rete-Match algorithm is the main algorithm that is used to develop Production

Systems. A Production System is a knowledge representation scheme in the Artificial

Intelligence. Although this algorithm is the fastest known algorithm, for many patterns

and many objects matching, it still suffers from considerable amount of time needed

due to the recursive nature of the problem. In this thesis, a parallel version of the Rete-

Match algorithm for distributed memory architectures is designed, implemented, and

analyzed. The implementation of this parallel version accomplished considerable speed

up with respect to the number of processors over the sequential execution of the Rete-

Match algorithm.

MASTER OF SCIENCE DEGREE

King Fahd University of Petroleum and Minerals

Dhahran, Saudi Arabia

January 1997

ix

### خلاصة الرسالة

إسم الطالب : محمد عبدالعزيز حسن طيب

عنوان الدراسة : تسريع الخوارزم مطابق ريتا بإستخدام

العديد من الحواسيب ذات الذاكرة المنفصلة

التخصص : علوم الحاسب الآلي.

تاريخ الشهادة : رمضان ١٤١٧هـ - يناير ١٩٩٧م.

يلعب الخوارزم مطابق—ريتا دوراً بارزاً في مجال النظم المنتجة والتي تعتبر فرعاً من فروع الذكاء الإصطناعي، وبالرغم من كون الخوارزم مطابق—ريتا أسرع وسيلة معروفة ومستخدمة للبحث ومطابقة عناصر متعدد، إلا أن تنفيذ هذا الخوارزم على الحاسبات الآلية التقليدية يستغرق وقتاً ليس بالقليل نظراً لطبيعة المشكلة. وفي هذه الرسالة، نقدم نمونجاً مطوراً من هذا الخوارزم والذي يعتمد على إستخدام العديد من الحواسيب الآلية ذات الذاكرة المنفصلة. ومن ثم تصميم، تنفيذ وتحليل النتائج. ولقد أثبتت جميع الدراسات والتحليل في هذه الرسالة إن هذا النموذج الجديد من مطابق—ريتا يؤدي أداءً متميزاً في حالة كون النظم المنتجة تتألف من قواعد تحتاج إلى وقت أكثر من الحواسيب لتنفيذها وكذلك كونها غير معتمدة على بعضها في التنفيذ، هذه الخاصية تجعل هذا النموذج المطور أكثر كفاءة وفاعلية من معظم المحاولات السابقة لتسريع الخوارزم مطابق—ريتا.

درجة الماجستير في العلوم جامعة الملك فهد للبترول والمعادن الظهران - المملكة العربية السعودية رمضان ١٤١٧هـ - يناير ١٩٩٧م

#### CHAPTER 1

#### INTRODUCTION

The Rete-Match algorithm is one of the main algorithms in the Production Systems field that belongs to the Artificial Intelligence. Although this algorithm is the fastest known algorithm for many patterns and many objects matching, it still suffers from considerable amount of time needed due to the recursive nature of the problem.

In this thesis, a parallel version of the Rete-Match algorithm for distributed memory architectures is designed, implemented, and analyzed. This study is targeted to be a practical approach to design and implement a reliable, heterogeneous, an adaptive and efficient message passing version of the Rete-Match algorithm. This new design is also targeted to utilize run time chances for to exploit higher degree of parallelism. Moreover, the correctness of the new model is guaranteed by the system rather than leaving it to the user that was the common practice for most of the previous attempts to parallelize this algorithm.

The new parallel version of the Rete-Match algorithm for distributed memory architectures that is presented in this thesis is being referred to as the Lana-Match model. The Lana-Match Model is an optimistic, message passing, parallel version of the Rete-Match algorithm that was specially designed to utilize the power of the parallel distributed memory architecture machines and to address the following shortcoming that was found with most of the current research:

- 1. Most of the work that has been reported toward parallelizing the Rete-Match algorithm can be classified as pessimistic parallel match and/or parallel-rule firing models. This means, that the concurrency control mechanisms (CCM) that they use to control the concurrent matching or concurrent rule firing are based on the assumptions that these rules or matches will most of the time conflict with each other. Such a very strict pessimistic CCM prevented most of these approaches from exploiting very high degree of parallelism and also prevented them from achieving major speed up.

- 2. Most of these approaches were either based on shared memory architectures or were based on special topologies (i.e. tree). That is why most of the reported results (nine out of twelve) were based on simulated solutions. How well these simulated ideas perform in practice remains to be seen.

The main idea behind the Lana-Match model is to make one or more copies of the Rete-Match network and engines running as Slave Processors for a Controller Processor that maintains a Master Agenda and a Master Fact List. The Controller assigns every activated rule of its Agenda to different slaves by sending all the facts that are activating that particular rule to the corresponding slave. This will activate the rule at the slave, execute the action part and send all the facts that either to be added or deleted from the Master Fact List back to the Controller. The Controller buffers the slaves responses and applies them, based on the time stamp of the activation they were generated from. If an activation was deleted then its generated action commands

will not be added to the Master Fact List. The final conclusion will be found at the Master Fact List.

The Lana-Match model was implemented using the C Language Integrated Production System (CLIPS) and the Parallel Virtual Machine (PVM). This implementation shows a proportional speedup with respect to the number of processors. This speed up and the adaptive feature of the Lana-Match represent major improvement for the performance of the Rete-Match algorithm. Moreover, the parallel version of this algorithm that is presented in this thesis could be used as a good starting point to build real cooperating expert systems which are gaining wide acceptance and interest from major Artificial Intelligence researchers.

Chapter-2 of this thesis covers the basic concepts and the key terminology that would be needed to follow the rest of this thesis. It starts with a brief description of the production system model. This is followed by a detailed description of the Rete-Match algorithm. Next, the main key concepts and terminology for parallel computing are described followed by a summary of the main concurrency control mechanisms. Finally, this chapter is concluded with a comprehensive survey of all the previous approaches that were reported toward parallelizing the Rete-Match algorithm.

Chapter-3 contains detailed description of the architecture of the Lana-Match model followed by a comprehensive analysis of its correctness and complexity.

Finally, the advantages and the disadvantages of the Lana-Match model are summarized.

Chapter-4 summarizes comprehensive analysis for the performance of our implementation of the Lana-Match model. Chapter-5 contains the major contributions followed by a list of suggested future research topics on this subject.

#### **CHAPTER 2**

#### BACKGROUND

This chapter starts with a brief description of production system followed by a detailed description of the Rete-Match algorithm. Next, the main key concepts and terminology for parallel computation and Concurrency Control Mechanisms (CCM) are described. This chapter is concluded with a comprehensive survey of the previous approaches that were reported toward parallelizing the Rete-Match algorithm.

#### 2.1 Production Systems

The term "Production System" is a heavily used term in Artificial Intelligence. Unfortunately this term may mean different things to different people. For example, Production System is a knowledge representation scheme to knowledge engineers while it is a programming language (like OPS-2 & OPS-5) for AI programmers. On the other side of the spectrum, theoreticians define production system as an abstract computation model. In this thesis, we use the term production system as a programming paradigm that is being adapted by many contemporary AI programming languages (i.e. OPS-5, CLIPS,...). This paradigm is based on the original model that

have been proposed first time by Post [5] and have undergone theoretical and application-oriented developments [5,18]. It consists of three major parts:-

- A Rule Base is composed of a set of production rules where every rule has the form "IF (conditions) THEN (actions)" construct. The conditions part of the rule generally referred to as the Left Hand Side (LHS).

- 2. A Working Memory is a special buffer-like data structure holding the data operated on by the program. Both the working memory and the LHS of the production rule contains lists of condition elements which are symbolic patterns.

- 3. An Interpreter is a program that repeatedly executes the following steps:-

- [Recognize] Determine which production rules evaluate to TRUE conditions for the current state of the working memory.

- [Select] If there are no such rules STOP; else select one of these rules.

- [Act] Perform the action specified by the chosen rule. This will modify the

working memory by adding or deleting some data which could require

another match.

- [Repeat] GOTO step (a).

This sequence of operations is called the Recognize-Act cycle. The first step of this cycle is called the Matching step. The second step is called the Conflict Resolution step. The third step is called the Act step. The match step tries to find instance of a class defined by the LHS among patterns in the working memory. This process is also called *instantiating* the pattern. The main function of the match step is

to find the set of all legal instantiations of conditions which is called the conflict set. The conflict resolution step decides whether the execution of the production system should halt, and then if not, it chooses one rule to be executed in the act step. There are several conflict resolution strategies. These include Depth, Breadth, Simplicity, Complexity, LEX, MEA, and Random strategies [19].

#### 2.2 The Rete-Match Algorithm

Matching is the most time consuming step in the execution of a production system. It consumes around 90% of the total execution time for each cycle [24]. To get a feeling for the complexity of the matching processor, imagine a production system consists of 2000 productions and 4000 facts, where each production has 5 condition elements. This production system will perform (4000 X 2000 X 5) matching operations at each execution cycle. The Rete-Match algorithm was first described in [19]. A complex version of this algorithm that includes an interpreter which delays evaluation of pattern as long as possible is presented in a similar report [24]. An efficient implementation of the algorithm is presented in [18-19]. The Rete-Match algorithm utilizes the following facts:-

- At each execution cycle a small fraction of the working memory could be changed.

- 2. There are a lot of structural similarities between most of the productions that can be found in most of the production systems.

By storing results of matching from previous cycle and using them in subsequent cycles combined with performing common tests only once, the matching process can be reduced by %90 [19].

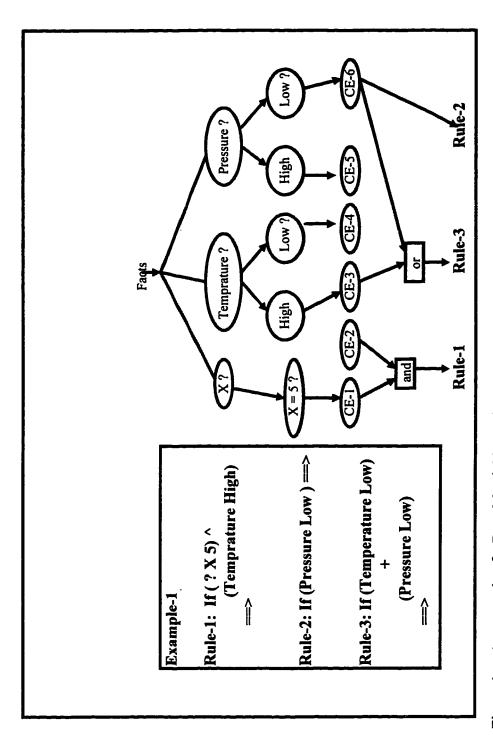

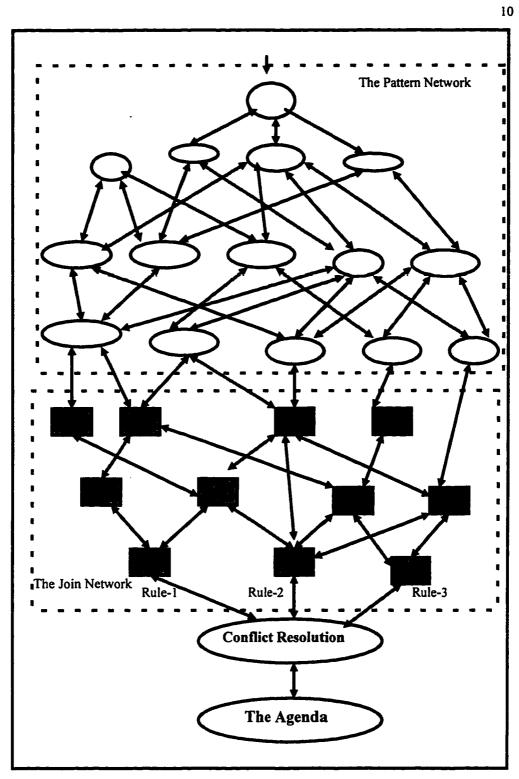

As in Figure 1, the Rete-Match algorithm compiles the condition elements of the production rules into a tree like network. This network is referred to as the Pattern Network. Every leaf of this tree has a list of pointers that points to the facts that matches that pattern. This list of pointers is referred to as the Alpha-Memory. The other network that joins the leaves of the pattern network to form productions is referred to as the Join Network. Every node of the join network has a list of pointers that point to the facts that match the pattern at that stage of the matching. This list is referred to as the Beta-Memory. The Rete-Match builds these two networks only once from the LHS of all the productions as these productions are being loaded into the system. All the LHSs of all the productions will be discarded after the networks are built. A more complex example network is given in Figure 2.

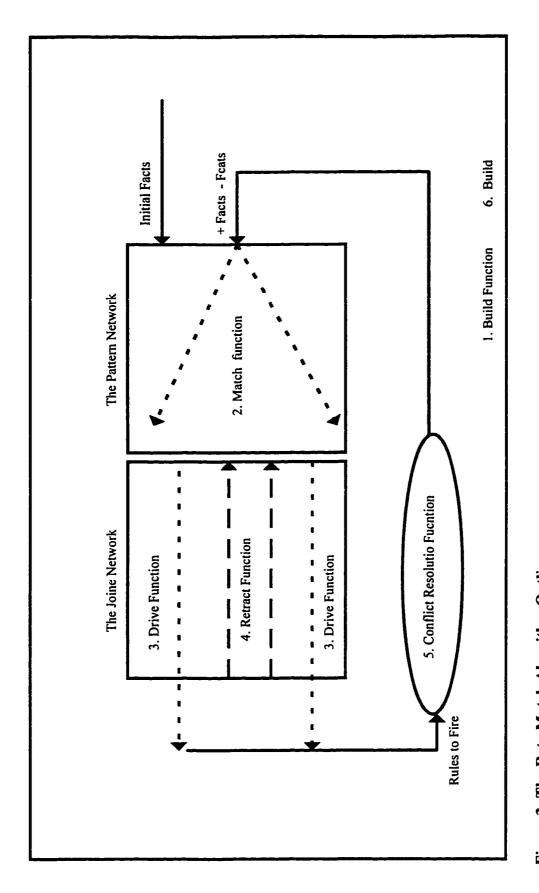

As in Figure 3, the pattern network and the join network form what can be described as a black-box system where all changes to the working memory pass to this black-box in the form of adding and deleting facts instructions from one side of the box which produce some more facts to be added or deleted from the system from the other side of the box. The system will be ignited by initial facts entering the system. Facts will be coming in and out of this box till the system reaches the equilibrium state in which there is no fact entering in or out of this box [60]. The

Figure 1: An example of a Rete-Match Network

Figure 2: A More Complex Rete Match Network.

Figure 3: The Rete-Match Algorithm Outline

behavior of these functions make what is being referred to as the Rete-Match algorithm. Appendix A contains detailed English like description of the Rete-Match Algorithm in terms of description for the Build, Match, Drive, Retract, Conflict resolution and the Engine functions.

#### 2.3 Parallelism

Dramatic increase in computing power were achieved over the past forty years. Most of it was largely due to the use of inherently faster electronic components. Unfortunately, it is evident that this trend will soon come to end because sequential computers may be approaching a fundamental physical limit on their potential computational power [3]. The limiting factor is speed of light in the vacuum. It appears that the only way around this limit (upper-bound) is to use parallelism. The idea here is that several operations are performed simultaneously, then the time taken by a computation can be significantly reduced. This is a fairly intuitive concept, and one to which we are accustomed in any organized society. We know that several people of comparable skills can usually finish a job in a fraction of the time taken by one individual. From mail distribution to harvesting and from office to factory work, our every day live offers numerous examples of parallelism through task sharing During 1979 to 1996, parallelism has become truly attractive and a viable approach for the attainment of very high computational speeds. The arguments over single von Neumann computers versus multiprocessors, not long ago, were settled. Parallel computing has always been criticized by referring to Grosch's law, Minsky's conjecture, and Amdahls's law [9]. Grosch's law states that the computing power of a single processor increases in proportion to the square of the cost. But this law is no longer applies to computer systems built with many inexpensive VLSI processors. Minsky's conjecture claims that because of the communications overhead between n processors, the actual performance of the parallel computer should be approximated by  $\log_2 n$  instead of n. But this conjecture was formulated in the late 1960s based on experience with systems containing few processors. Only present experience overwhelmingly indicates that the actual loss in performance is much less than the loss predicted by Minsky's conjecture.

Amdahl's law states that the improvement in performance of a parallel algorithm over a corresponding sequential algorithm is limited by the fraction of algorithm that can not be parallelized. But Sandia National Laboratories has recently confirmed that almost linear speed-up has been achieved on 1024 processors hypercube for a number of practical problems. That's why, in recent years, parallel computing has grown to the point where computers of various types are both commercially available and potentially cost effective tools in a number of application areas. Appendix B contains some of the main characteristics of parallel and distributed processing.

#### 2.4 Serializability & Concurrency Control

At the moment we think of having more than one agents to accomplish a task by sharing resources, a series of issues will start showing up to be addressed. No matter what subject domain we are talking about these issues will be similar in nature but may have different flavor at each domain. Serializability and concurrency control are the main two issues that have been studied extensively in the operating system and database subfields of the computer science discipline. In this section, we will approach this topic from the database point of view only. This is mainly due the natural similarity between knowledge and database systems. The following are definitions for few terms that will help us clarify this topic [61].

- Transaction: A single executing program that would read and write data to and

from the database, into a private work space, where the computation is performed.

These computations will not effect the database until new values are written in to

the database.

- Atomicity: An atomic operation either occurs in its entirety or does not occur at all, and if it has occurred, no other operation went on during the time of its occurrence.

- 3. Item: The unit of data to which access is controlled. A relation, a tuple or a field are examples of such units.

- 4. Schedule: A schedule is the interleaved order of execution of transactions.

- 5. Serialization: The scheduling mechanism which forces transactions to run concurrently in a way that makes it appear as if they ran one at a time (serially).

- 6. Serializability: A schedule S is said to be serializable if the state of the database after the successful completion of all of its interleaved transactions will always be the same as if these interleaved transaction were executed in some serial fashion. Serializability is the most widely accepted correctness criterion for concurrency control mechanisms.

- 7. Concurrency Control Mechanisms: There is a large number of concurrency control algorithms and proposals in the literature. These mechanisms can be classified as:

- Pessimistic Concurrency Control: it is based on the assumption that many (if not all) transaction will conflict with each other. Thus it will not permit a transaction to access a data item if there will be a conflicting. Which means that the execution of any operation of a transaction follows the sequence phases: validate, read, compute and write. (only update operation is considered here because its the one that causes inconsistency problems).

- Optimistic Concurrency Control: it is based on the assumption that not too

many transaction will conflict with one another. Thus it will permit a

transaction to access a data item even if there is a conflicting transaction.

Which means that the execution of any operation of a transaction follows

the sequence phases: read, compute, validate and write. Although the

pessimistic approach is the safest which guarantee Serializability

- conditions, the optimistic approach has great potential to allow a higher level of concurrency.

- Locking based Concurrency Control: the main idea of locking-based concurrency control is to ensure that a shared item is accessible only by one operation at a time. This is a accomplished by associating a "lock" with each item. This lock will be set by one of the transactions to prevent any other transaction from accessing it and will be reset by one of the transactions at the end of its use. There are two types of lock, Read locks and Write locks. Two Locks are said to be compatible if and only if both of them are Read locks. Only compatible locks will be allowed to be executed concurrently. Although, the basic locking mechanism guarantee mutual exclusion of accessing the shared item by conflicting transaction, it does not guarantee Serializability. With some modifications to the basic locking mechanism, Serializability conditions can be achieved. Two Phase Locking (2PL) rule is one of the modifications. This rule requires that the transaction should not release any of its locks until it is certain that it will not require any other lock. Any schedule generated by 2PL concurrency control mechanism is serializable [61].

- Time stamp based concurrency Control: Time stamp concurrency

mechanisms do not maintain Serializability by mutual exclusion. Instead

they select a prior serialization order and execute transactions accordingly.

This is established by assigning each transaction a unique time stamp at its

initiation. Uniqueness and monotonicity are the two main properties of time stamp generation.

Hybrid Concurrency Control: It is a combination of the Lock and time stamp based concurrency control mechanisms.

#### 2.5 Previous work on Parallelizing of the Rete-Match Algorithm

The research efforts toward parallelizing the Rete-Match algorithm can be classified into the following three main categories [32].

#### 2.5.1 Speeding up the match phase by faster sequential algorithm

Charles Forgy [18], encouraged researchers to work on Parallelizing this algorithm as he was concluding his PHD. thesis "On the Efficient Implementation of Production System" where he first introduced the Rete-Match algorithm. He also pointed that since the Rete-Match algorithm is a memory limited, this algorithm is not amenable to uniprocessoror techniques like putting more data paths in the machine, pipelining the processors, or using special functional unit. His one page conclusion on Parallelizing this algorithm was the first road sign.

Miranker, D.P. [42] proposed a new version of the Rete-Match algorithm that he called TREAT. This algorithm resolves the ineffective network updates procedure that is used by Rete. In TREAT, a modify action is still implemented as a deletion and an addition, but the state of the network is stored differently. In TREAT network, the

memory nodes are eliminated. When a new fact is added, an exhaustive search through the network is made to determine the new rule binding. Minker showed that in many cases the speed-up obtained in deletion is greater than the loss in addition. Thus he concluded that TREAT obtain better performance than Rete. Minker and his group at the University of Texas at Ausin have completed a new, highly optimized, C-based version of OPS-5 compiler. They reported 4-15-Fold speed-up over the Rete-Match algorithm.

Highland proposed a new version of Rete-Match algorithm that he called YES/RETE [32]. The modify action is no longer implemented as deletion followed by an addition. Instead, a new update-in-place operation is used. The update-in-place operation directly changes the attributes of a fact. For the instantiation that continue to exist after a modify action, it does not cause a network update. Only those instantiation that are affected by the modify action are updated. The YES/RETE algorithm has been implemented in KnowldgeTool and HiPER both from IBM [32]. The main difference between KnowldgeTool and HiPER is in how the program is compiled. HiPER achieve 3-11-fold speed-up over KnowldgeTool and regular Rete-Match algorithm.

#### 2.5.2 Speeding up the match phase by parallel algorithm

Carles Forgy [24] presented a parallel version of the Rete-Match algorithm on a SIMD machine (Illiac-IV). The idea of this algorithm can be outlined as follows. First, divide the set of rules into 64 partitions, corresponding to the number of

processors in Illiac-IV. Second, for each partition, construct the Rete-Network.

Third, execute the Rete-Match code sequentially on each node.

Annop Gupta [24] (a student of Charles Forgy), presented a paper on Parallelizing the Rete-Match algorithm on the DADO machine. DADO [57] is a highly parallel tree-structured architecture designed to execute production system at Colombia University by Salvatore J. Stolfo and his colleagues. It consists of a very large number (tens of thousands) of processing elements, interconnected to form a complete binary tree. Annop Gupta extended Charles Forgy parallel version of the Rete-Match to the DADO prototype machine and predicted to be able to processor 125 facts/seconds. The DADO machine was just a prototype. Reports on its performance was given by Stolfo [57, 58]. Speed up of 2-31-fold has been reported.

Researchers at Honeywell CSC proposed a parallel version of Rete-Match algorithm that is based on translating the Rete-Network into a data-flow graph that explicitly shows the data dependencies. Similarly, operations performed in the Rete algorithm are encapsulated into appropriate activities or tasks in the data-flow model which can then be executed on the available physical processing resources [24]. No performance evaluation is available.

Kemal Oflazer [24] in his thesis showed that the task of partitioning production system so that work is uniformly distributed is an NP-complete problem. He also presented a more complex heuristic method for partitioning that relies on data obtained from actual production system runs. The second part of his thesis proposes a

new parallel algorithm for performing match for production system and proposed a parallel architecture to execute it.

The Rete-Network was implemented using a similar kind of dataflow architecture PESA-I which consists of 32 special purpose processor. The simulator was built using Pascal. Only small production systems programs had been simulated. The simulated results showed that PESA-I obtained a rate of 8000 rule firing per seconds [51].

Anoop Gupta [24] explored parallelizing Rete-Match based production system programs on a simulated 32-64 shared-memory multiprocessor machine and reported the following results:-

- 1. The Rete-Match algorithm is highly suitable for parallel implementation.

- 2. The amount of speed-up available from parallelism is quite limited, about 10-fold.

- 3. To obtain the limited speed-up, it is necessary to exploit parallelism at a very fine granularity.

- 4. To exploit the suggested source of parallelism, a multiprocessor architecture with 36-64 high performance processors and special hardware support for scheduling the fine-grain task is desirable.

He concluded his thesis with the following points. His results are based on the analysis of existing programs (1980-1987) that were written with sequential implementation in mind which did not reflect the true parallelism which is to be found in programs written with parallel implementation in mind. However, he does not expect that this would have a major impact on his results.

Gupta [25] and his colleague implemented a parallel version of the Rete-Match on the Encore Multimax shared-memory multiprocessors with 16 CPUs. This approach exploits very fine grained parallelism and speed-up of 2-11-fold was achieved using 13 processor. The Rete-network was partitioned at the node level to obtain fine grain parallelism.

A simulated version of the Rete-match suitable for message-passing computing have been proposed by Acharya, Gupta, and Tambe [1], It has been simulated on the Nectar simulator, which is a message-passing computer with low message overhead. The simulation results indicated that speed 2-12-fold were achieved for three programs.

Kelly and Seseviora [30,31] have proposed a distributed version of the Rete-Match algorithm that they called Drete on a special machine CUPID that was designed to maximize the performance of Drete. The CUPID has not been implemented. It was only simulated on the CUPID simulator. The simulation indicated speed-up similar to Gupta's thesis.

#### 2.5.3 Speeding up Production Systems by Multiple Rules Firing

Pakis [47] simulated a new programming methodology called IRIS to reduce the software complexity and to improve the parallelism in production system. IRIS reduces the software complexity by eliminating the explicit control. The simulations show that 6-90-fold speedup is possible to be achieved using the IRIS methodology.

Ishida [28] has proposed a simulated parallel programming environment consisting of analyzer that will determine the inter-instantiation data dependencies and a set of parallel language construct (i.e. rule-set and focusing mechanism). These constructs enable the programmer to group production rules into different rule sets and specify the desired conflict resolution strategy. The simulation indicated that 5.11 to 7.57 fold speedup. However this environment does not provide a mechanism for determining whether a rule set is a parallel or sequential rule-set. Instead, it is the programmer's sole responsibility to ensure that the rule instantiations in a parallel rule-set do not interfere with each other.

Schmloze [52,53] has proposed a simulated asynchronous distributed production system called PARS with the following advantages:-

- 1. It obtains speed up over parallel match systems by executing multiple rule instantiations simultaneously.

- 2. It obtains speed-up over synchronous production systems by eliminating synchronization bottlenecks.

- 3. It is an inexpensive solution for large-scale production system.

For a 32-processor system, PARS is almost as fast as four times. For 8-processor system, PARS is two times as fast. However the over all speed-ups are not spectacular.

Miranker et al [40,41] developed a parallel production language CREL which is syntactically identical to OPS5. A CERL program is correct if and only if all eligible serial execution paths reach correct terminal state. It is the programmer's sole

responsibility to write correct a CERL code. As the program increases in size the programmer's job becomes unmanageable.

Gamble proposed (not implemented and not simulated) a non deterministic parallel language called SWARM [21]. SWARN is a parallel language that provides formal methods for specifying production system for coding and verifying production system. No information is available yet on its performance and capability.

Kuo [35] implemented a Multiple Context Multiple Rule (MCMR) firing model. The performance of this model was measured on the RUBIC simulator and the Intel IPSC/2 Hypercube. The RUBIC is a simulator that was written in Common Lisp and currently running on a Sparc Sun workstation. Speed up of 3.35 to 19.45 fold have been obtained.

Stolfo et al. [56] implemented a prototype of the PARULEL language using Common Lisp. PARULEL capture the inherent parallelism in production programs using parallel production languages. It allows the programmer to develop parallel solutions and also enjoy actual efficient, parallel execution of the resultant code. However, it is the programmer's responsibility to write correct code which is hard to do.

### **CHAPTER 3**

### THE LANA-MATCH MODEL

In this chapter, detailed description of the architecture of the Lana-Match Model, a parallel version of the Rete-Match algorithm for distributed memory architecture, is presented followed by a comprehensive analysis of its correctness and complexity. Finally, the chapter is concluded with a summary of our implementation followed with the advantages and the disadvantages of the Lana-Match model.

# 3.1 The Lana-Match Computational Model Architecture

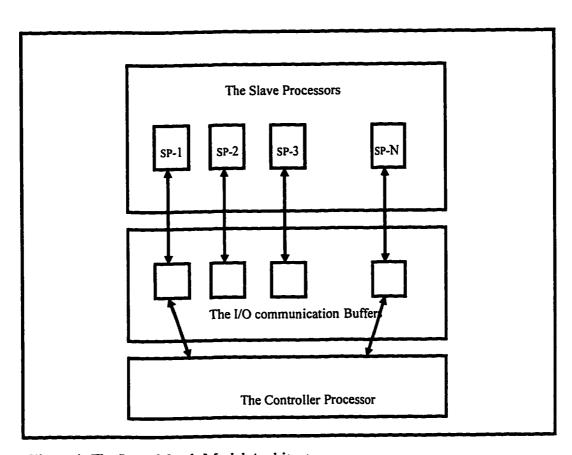

The Lana-Match Model is asynchronous master-slave parallel computational model that consists of one Controller Processor (CP) and a one or more Slave Processors (SP). Every SP communicates with the CP through two communication buffers. One of these buffers is for input and the other is for output. Figure 4 outlines the Lana-Match model architecture.

Figure 4: The Lana-Match Model Architecture

#### 3.1.1 The Controller Processor

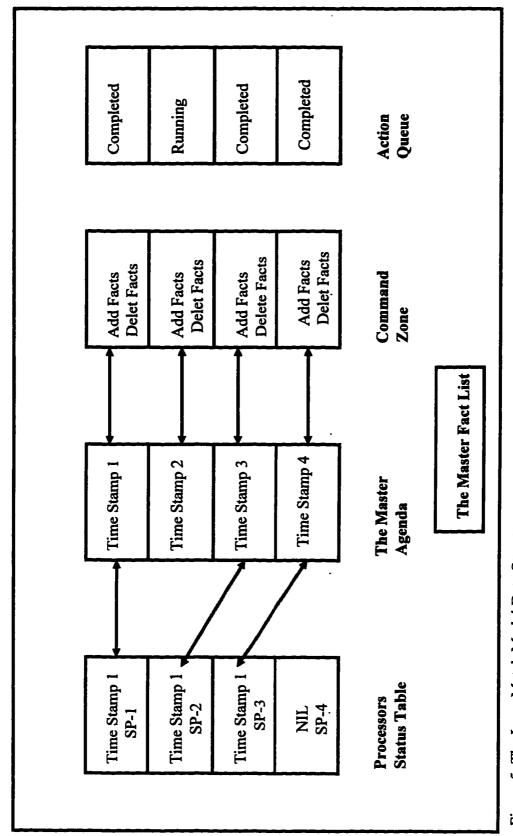

The Controller Processor (CP) is a production system that consists of a Master Rete Network (MRN), a Master Facts List (MFL), a Master Agenda (MA), an Action Queue and a Master Engine (ME). The Controller Processor is the main console through which the user can interface with the model. Through this console, the user can load the rule set, insert initial facts and receive the final facts or conclusions.

- a) The Master Rete-Network is the pattern and join networks generated at the Controller Processor by compiling the rules set. These two networks are created by the Build function of the Rete-Match algorithm at the CP. At the start-up time, these two networks are also duplicated on every one of the Slave Processors by compiling the same rules set on each SP.

- b) The Master Facts List. All the facts are maintained in the Master Facts List. Apart from the initial facts that are inserted directly by the user through the Controller Processor at the start-up time, all the facts that are inserted or deleted from the Master Facts List are generated at the Slave Processors. The SP receives a message from the Controller Processor that contains the facts that activate an activation. The SP executes the activation and sends back the facts that are need to be added to (or deleted form) the MFL as a set of action commands. These action commands are queued at the Action Queue based on their time stamp. Asserting-facts-to or deleting-facts-from the Master Facts List activates or deactivates rules at

the Controller Processor, which are then translated to addition (or deletion) of one or more activation to/from the Master Agenda.

- c) The Master Agenda is a set of activations where every one of these activations represents a rule instantiation and contains a set of pointers to the rule that it represents and all of its activating facts. Each activation maintains the following information:-

- A time stamp represents the time that this activation was added to the agenda. It

is stamped by the Controller Processor at the creation time.

- 2) A pointer to the Slave Processor that is currently processing this activation. When the scheduler assigns this activation to an SP, this pointer is set to point to that SP.

Otherwise it will be set to null.

- 3) A Pointer to the Action Commands Zone which has all the activation commands that were generated by executing this activation at the SP.

The Action Commands Zone is just a buffer that is used by the Control Processor to temporarily store all the additions and deletions to the MFL. In another words, the Action Commands Zone is nothing more than a waiting zone for the results of executing an activation at a Slave Processor (SP). The reason to buffer the changes and not to apply them directly to the Master Fact List is mainly because assertion of facts can deactivate and remove some or all the of its younger activation. Since activations are executed in parallel, some of the younger activations can be completed before their elder activations. If an activation is removed from the agenda by one of its elder activation, this will remove all of the queued changes that were buffered for

that activation. Allowing activations to execute in parallel and committing the changes to the Master Agenda based on their time stamps is the Lana-Match model concurrency control mechanism.

- d) The Action Queue guarantees serializability. It is a circular list of slots where every one of these slots is assigned to a slave processors every time an SP is assigned to an activation. Each one of these slots has a pointer to the activation that it represents and its status. The status is set to "ON" while the activation is running on the SP and it is set to "OFF" whenever the SP completes the execution of that activation.

- e) The Slave Processor Status Table. Every one of the SP has an entry in the Slave Processor Status Table (SPST) at the CP. This entry is set to null if the SP is idle, otherwise it contains the status of the corresponding Slave Processor. The status of an SP is described by three entities; a pointer to the activation that is currently executing, the time stamp of that activation, the Slave Processor identification number.

- f) The Master Engine. As in Figure 5, the Master Rete Network, the Master Facts List, the Master Agenda, the Slave Processor Status Table and the Action Queue are different data structures that are used by the Master Engine of the model to carry out the parallel execution of the system. The Master Engine consists of the Main Loop and different control functions such as finding a free Slave Processor, scheduling an activation to a Slave Processor, rescheduling a Slave Processor and examining and committing the action commands in the same sequence as they were created.

Figure 5: The Lana-Match Model Data Structures

- 1. Get a Free Slave Processor Function examines the Slave Processor Status Table and returns the first Slave Processor identification number that points to a null activation. If there is not any free Slave Processor, this function executes the Rescheduler repeatedly to search the SPTS and return the first available free SP.

- 2. Schedule an activation to a Slave Processor: Given an activation and a free Slave Processor, do the following:-

- Set the corresponding entry for this Slave Processor at the Slave Processor

Status Table to point to the given activation.

- b) Set the time stamp field for this SPTS entry to the time stamp of the given activation.

- c) Make the activation points to the Slave Processor.

- d) Buffer all the facts that activated this activation along with its time stamp at the input buffer of the Slave Processor.

- e) Change the status of the Action Queue entry for that activation to "Running'.

- 3. The Rescheduler. At completion, every Slave Processor buffers all the facts additions and deletions that were generated while its executions along with the assigned activation time stamp at its output buffer. Every one of these facts additions and deletion is referred to as an action command. The Rescheduler examines the output buffer of every SP and matches the time stamp of the coming action command with the current time stamp that this Slave Processor is pointing to at the Slave Processors Status Table.

If these two times match, it means that this message is a correct message and should be buffered in the action zone of the activation that is being executed at that particular Slave Processor. Then, the Rescheduler buffers this action command at the action zone of the activation that is being executed at that particular Slave Processor; makes this Slave Processor pointing to null to make it free again and marks this activation as a completed activation. On the other hand, if these two times do not match, this means that while this Slave Processor is executing the activation, that activation was deactivated by its elder activations. In this case, the Rescheduler ignores the message and all other message that are coming from this Slave Processor with that mismatched time stamp. However, if all the SP output buffers are empty, the Rescheduler consider that as a free time and tries to utilize this time to examine the Action Queue and commit completed action commands based on the their time stamps.

4. Examine & Commit Action Commands Function: This function examines the Action Queue starting from the beginning. If the first action on the queue is completed, execute all the action commands that are stored at the Action Zone that is pointed to by the activation that owns this slot. Next, move forward in the queue and do the same thing but stop at the first non completed action even if all the activations that are queued after it were completed. This guarantees that action commands are committed in the same sequence as they were created.

5. The Main Loop: The Master engine executes this loop repeatedly until the end of the Master Agenda.

LOOP until the end of the Master Agenda.

Get a free Control Processor and schedule the top activation of the agenda to it.

Remove this activation from the Master agenda.

#### END LOOP

### 3.1.2 The Slave Processors

The Slave Processors are the set of processors that are available for the Rescheduler to choose from. This set is sometimes referred to as the Slave Processors pool. Slave processors communicate with the Controller Processor through asynchronous message passing mechanisms. Every one of these processors has the full Rete-Match network MRN. It waits for messages from the CP asking to insert facts into its local agenda. When the CP finished sending all the facts that activates the activation that was assigned to this SP, these facts instantiate a rule at the Slave Processor. Then, the Slave Processor fires this rule and buffers all the new generated facts additions or deletions of facts to/from the MFL. Figure 6,7 and 8 outline the Lana-Match computational model in an English like description.

```

/* THE MASTER ENGINE */

Function Get a free Slave Processor;

Function Schedule an Activation(p,a);

Function The Rescheduler;

Function Examine and Commit;

Function Remove an Activation (a);

/* MAIN */

LOOP Until the end of the Master Agenda

1. Get_a free_Slave Processor(p);

2. Schedule an Activation(a,p);

3. Remove an Activation(a);

ENDLOOP

End

Function Get a free Slave Processor;

1. Examine the Slave Processors Status Table and

returns the first SP that points to Nil;

2. If there is not any, then execute the Reschedular;

End

Function Remove an Activation (a)

1. Set Agenda(a) = Nil;

2. Set Command Zone(a) = Nil;

End

Function Schedule an activation(p,a)

1. Set PST(p).proc --> Agenda(a);

2. Set PST(p).time = Agenda(a).timestamp;

3. Send all the facts that activated Agenda(a) to

the Input buffer of the Slave processes p along wit the

Timestamp of a (Agenda(a).timestamp);

4. Set Action_Queue(a) = Running;

End

```

Figure 6: The Lana-Match Model Outlines (Part 1)

```

Function The Reschedular

1. Examine the output buffer of each Slave Processor;

2. FOR each processor p which completed its

Activation (i):

2.1 Read the fact additions and deletions;

2.2 Read the timestamp;

2.3 IF the timestamp = PST(p).timestamp;

- Write all the facts addition and deletions

that is generated by i to the Command Zone(a);

- Set PST(i) -> Nil;

- Set Action Que(a) = Completed;

ENDIF

END FOR

3. Return if at least one Slave Processor was freed;

Otherwise

3.1 Call Examine and Commit;

3.2 Call the reschedular;

End

THE SLAVE PROCESS

1. Examine the Input buffer repeatedly when an activation is assigned:-

1.1 Read the facts from the buffer;

1.2 Read the timestamp;

1.3 Insert these facts into its local fact list;

2. FOR each generated Activation

2.1 Execute the Action of the Activation;

2.2 Write all generated facts additions and deletion to the output buffer

of the Slave Processor;

2.3 Write the timestamp of the activation

to the output buffer;

END FOR

End

```

Figure 7: The Lana-Match Model Outlines (Part 2)

```

Function Examine_and_Commit

1. Start from the top of the Action Queue;

2. LOOP UNTIL Action_Queue(i+)=Runing;

2.1 Apply Command_zone(i) to the master agenda;

2.2 For each rule activation that is generated;

- Add that activation to the bottom of the master

Agenda with the current timestamp+;

2.3 For each activation that is deleted from the

Agenda;

- Set PST(a) = Nil;

- Remove_activation(a);

- Command_Zone(a) = Nil;

END LOOP

```

Figure 8: The Lana-Match Model Outlines (Part 3)

### 3.2 The Correctness of the Lana-Match Model

The correctness of the Lana-Match Model is based on a centralized time stamp Optimistic Concurrency Control mechanism which is a full proven database technique [61]. In this thesis, this technique is extended to guarantee the correctness of parallel execution of production systems. This extension is part of the contribution of the thesis as an improvement that fills in the gap between database and production system techniques. This mechanism was implemented as follows: at the creation time, the CP stamps every activation that it adds to the MA with an increment integer. This integer number is stored as part of the activation and will be used to identify this activation and all the results that is generated from it.

In the Lana-Match model, correctness is accomplished by distributing the Master Agenda to the Slave Processors simultaneously and letting every SP executes its activation and passes all of its results back to the CP. These results which are either addition or deletion actions of facts to/from the Master Fact list will not be committed as the CP receives them. But instead, they will be queued in the Action Queue. As the Controller Processor (CP) is free (or needs to get a free Slave Processor), the CP executes the Examine-and-Commit function which examines and executes the action commands that are queued at the Action Queue starting from the top of the queue. Then, it executes the completed activations in the same sequence as they were queued in to the AQ. This sequence is FIFO to reflect the incremental nature of the time stamp of the activations. The Examine\_and\_Committ function

continues in the same fashion and stops at the first non completed activation. This makes sure that although the results of younger activations were obtained at the SP, these results will not be committed until all its elder activations were completed. This guarantees that the final effect to the Master Fact List is done exactly the same as if the activation were executed sequentially.

## 3.3 The Lana-Match Model Complexity Analysis.

The expected speed-up (SP) is equal to the sequential execution costs over the parallel execution costs. In another words, the SP is the ratio between the number of time units that are required for the sequential execution of all the activations of the Master Agenda on a single node and the number of time units that are required for parallel execution of all activations on more than one node. To calculate the sequential execution costs, let:

- N<sub>a</sub> the number of activations that were actually fired.

- N<sub>f</sub> the average number of facts per a rule instantiation.

- T<sub>m</sub> the average time that is needed to match a fact through the pattern network

and to drive it through the join network.

• T<sub>f</sub> the average time that is required to fire a rule.

Thus, the total time that is needed to evaluate the Left-Hand-Side of a rule T<sub>LHS</sub>

$$T_{LHS} = N_f * T_m \tag{1}$$

Then, the time that is needed to fire a rule equals to the total time that is needed to evaluate the Left-Hand-Side  $T_{LHS}$  and the Right-Hand-Side  $T_f$ . Thus, the total execution time for a rule  $T_{Rule}$  would be calculated as follows.

$$T_{Rule} = N_f^* T_m + T_f \tag{2}$$

This makes the total execution time on a single node (Tseq) equals to the total execution time of all the activations that are fired during the exaction of the production system.

$$Tseq = N_a \left[ N_f * T_m + T_f \right] \tag{3}$$

On the other hand, to calculate the parallel execution cost Tparallel let,

T1 the time that is needed to evaluate the Left-Hand-Side for each rule once at the Controller Processor.

$$T1 = Na* T_{LHS}$$

(4)

• T<sub>2</sub> the time that is needed to re-evaluate the Left-Hand-Side for each rule that is assigned to all the SPs and let Ns be the number of Slave Processors.

$$T_2 = T_1 / Ns \tag{5}$$

T3 the time that is needed to fire all the rules in parallel. Firing all the rules in parallel.

$$T3 = N_a * T_s / Ns \tag{6}$$

T<sub>c</sub> the average time that the CP needs to send all the facts for one activations to

an SP and to receive all the generated results from executing that activation.

Comunication Cost =

$$N_a * T_c$$

(7)

This makes the parallel execution costs as follows

$$T_{parallel} = T_1 + T_2 + T_3 + Comunication Cost$$

(8)

Performance speedup is achieved when the sequential execution costs is greater than the parallel execution costs. In another words  $T_{parallel} < T_{seq}$ . This relation could be expanded as follows:-

$$N_a * T_m + N_a * T_m / N_s + N_a * T_f / N_s + N_a * T_c < N_a * (T_m + T_f)$$

(9)

This relation can be simplified as follows:

$$T_{\rm m}/(N_{\rm s}-1) + N_{\rm s}/(N_{\rm s}-1) T_{\rm c} < T_{\rm f}$$

(10)

However,  $T_m$  is almost constant and  $(N_s/N_s-1)$  is almost one. Thus, from this relation we can conclude that the Lana Match model performs its best speed up when the average time that is required to fire a rule  $T_f$  is much greater than the average time that the CP needs to send all the facts for one activations to an SP and to receive all the generated results from executing that activation.

## 3.4 Implementing the Lana-Match Model using PVM and CLIPS

The two main ingredients to implement the Lana-Match model are a Rete-Match based production system package and a message passing communication mechanism. Appendix C, of this thesis summarize possible implementation alternatives for this model. In this thesis, we decided to implement the Lana-Match Model using CLIPS and PVM.

The C Language Integrated Production System (CLIPS) [59-60] that was developed at NASA's Johnson Space Center during 1985-1993 started receiving a widespread acceptance throughout the public and private sectors to be one of the most powerful Rete-Match based production system packages. It has more than 5000 users including NASA sites and branches, numerous federal bureaus, government contractors, more than 200 universities and many companies. Because of its portability, extensibility, capabilities and low-cost for both the executable and the source code, it was decided to implement the Lana-Match Model using the C Language Integrated Production System (CLIPS). The Parallel Virtual Machine (PVM) [8,10] permit a network of heterogeneous UNIX computers to be used as a single large parallel computers while handling all communications and reliability details. It provides a more efficient, powerful, reliable, popular parallel programming environment. The development of PVM started 1989 at Oak Ridge National Laboratory (ORNL). It was ported to almost every known UNIX machine. The PVM system is composed of two parts; a demon that resides on all the computers of the virtual machine and a library of PVM interface routines. These routines are user callable routines for message passing, spawning processors, coordinating tasks, and modifying the virtual machine. For its portability and popularity, it was decided to use PVM to implement the Lana-Match Model in this thesis. To implement the Lana-Match model using CLIPS & PVM on a UNIX based environment, the following three steps were taken:

- 1. Creating the Controller Processor: XCLIPS which is an Xwindow version of CLIPS was modified to become the Controller Processor. This is accomplished by creating all the data structures that are needed by the CP such as the SPST, AQ, ME, etc. and modifying its agenda to become the Master Agenda, the fact list to become the Master Fact List and the engine to become the Master Engine. Modifying the engine is accomplished by transforming the firing mechanism to make it schedule the activations to the SPs and copy every activation to the assigned SP input buffer. Finally, the ME was made to repeatedly check the output buffers of all of its slaves and take the passed action commands and queue them in the Action Queue to be processed in the same sequence that their activations were originally created on.

- 2. Creating the Slave Processor Code: A copy of CLIPS was modified to become the Controller Processor. This was accomplished by changing the behavior of the Line Command procedure of the package from waiting for a user response to make it check repeatedly its local input buffer for messages from the CP. Moreover, this copy was modified to write the final results to its output buffer as Action Commands rather than applying it to its local fact list.

- 3. Creating the communication infrastructure: Both of these copies need to be modified to make the CP run as a PVM master and the SP to run as a slave or (worker using PVM terminology). This modification includes defining and building all the needed buffers and the necessary communication mechanisms.

# 3.5 Advantages of the Lana-Match Model

The Lana-Match model enjoys the following main advantages:-

- 1. The Lana-Match model is Adaptive. The Lana-Match model is a very adaptive approach in which adding a Slave Processor is accomplished easily just by copying the Rete-Match network on that node and declaring that node to be ready for the CP.

- 2. Heterogeneity. The Lana Match Model was designed to be a very heterogeneous model. It was designed to allow heterogeneity at three levels. First, at the network level since the Slave Processors and the Control Processors can be executed on any network as long as they can communicate via message passing. Second, at the production system level since the Slave Processor and the Control Processor can be implemented using any production system as long as it can be modified to communicate with the Controller Processor. However, the Controller Processor needs to be developed using a production system package that is based on the Rete Match algorithm. Third, at the node (or the processor) level, heterogeneous nodes that can communicate through message passing mechanism.

- 3. Practicality. The main motivation for developing the Lana-Match model is to take a practical approach to develop a parallel version of the Rete-Match algorithm that can lead to a real implementation. This need raised as we noticed that most of the research that was reported in this area was either based on a shared memory architecture or was based on a special architecture. Moreover, it

was also noticed that nine out of twelve of the previous approaches to this study were based on simulation rather than real implementation [24-26, 28-35, 40-45]. Therefore, we thought a practical real implementation approach is highly needed for this algorithm.

- 4. Exploits Run Time Parallelism. The Lana-Match Model was designed to exploit run time parallelism opportunities which are more fruitful than compile time analysis that was taken by ten out of the twelve reported studies in this area. Compilation time analysis does not utilize many of the parallelism opportunity that can be utilized at the run time. As an example, let us say that we have only one rule to fire and 10000 run time instantiations for that rule. In this case, compilation time analysis does not foresee any chance for parallelism while it is obvious that there are, at least, 10000 chances for parallelism (assuming the instantiations are independent).

- 5. Reliability. The Lana-Match model was designed to have a great immunity form losing a node on the network. This is mainly true because the Slave Processors do not store any status. They are only created to be assigned tasks to execute and at the end, they are destroyed. It is perfectly true, that the system can start with N processors and end with less processors without effecting the final results. However, the model is not immune from the death of the CP (i.e. if the CP crush the model will be dead and will leave all the SPs behind it).

- 6. No Interaction From the Programmer. The Lana-Match model does not leave any responsibility on the programmer to develop parallel production systems that

are as correct as their sequential versions. But instead, the Lana-Match model asks the programmer to write only a set of rules and leave all the rest to be addressed by the system.

7. Filled In the Gap Between Database and Knowledge Base Concurrency Control Mechanism. In this thesis, we demonstrated this by showing the applicability of some of the techniques of distributed database serializability theory and concurrency control mechanisms to solve the parallel rule firing production systems.

## 3.6 Disadvantages of the Lana-Match Model.

The Lana-Match Model could be criticized with the following concerns:-

- 1. The Controller Processor Can be a Memory Intensive Processor. Since the Lana-Match Model utilizes the optimistic concurrency control mechanism, it requires high memory to store intermediate results before committing changes. However, this cost is well justified at the database area and we think it is also well justified in our approach by the speed up that it delivers.

- 2. The Controller Processor Can Be a Bottle-neck. For extremely large production systems where the Controller Processor can not keep up with the Slave Processors, some of the Slave Processors can be kept waiting. One approach to address this issue is to utilize the heterogeneity feature of the model that allows

different computers and networks to be used for implementation by executing the Controller Processor on a more powerful node while executing the Slave Processors on less powerful nodes. Another approach is to execute more than one Slave Processors at one node.

3. Redundant Execution of the Rules. Since the CP sends facts to the SPs to activate rules, some facts may activate more than the targeted rule. This mean we activated the same rule more than once. This contributes to the redundant execution of the rules and increases the execution time.

### **CHAPTER 4**

### **RESULTS AND ANALYSIS**

This chapter contains a comprehensive analysis of the performance of our implantation of the Lana-Match model. It was measured in an environment that consists of more than 500 Sun workstations that are connected through FDDI (i.e has around 100MB/Second throughput). Clusters of 2, 4, 8, 16, 32 and 64 workstations were used to measure the Lana-Match performance. Most of these workstations were Sun SPARCstation 10 model with few SPARC stations LX model. Although this network was not dedicated for these tests, all of the measurements were taken when the network was almost dedicated during weekends and after working hours. The total elapse time for the sequential execution of the Rete-Match algorithm was measured by running the rules on the original implementation of CLIPS on a SPARC station 10 workstation. This time is measured as the difference between the system time when CLIPS start processing the agenda and the system time when it complete it. The total elapsed time of the Lana-Match model was measured as the difference between the system time when the CP starts scheduling the first activation of the Master Agenda and the system time when the CP commit all the Action Commands of the last activation of the Master Agenda. The CP was running on a SPARC station 20

workstation while the SP's were running mostly on Sun SPARC stations 10 workstation.

In section 3.3, the thoratical analysis of the Lana Matching model conclude that the average time that is required to fire a rule  $T_f$  and the average time that is required by the CP to send all the facts for one activations to a SP and to receive all the generated results from executing that activation  $T_c$ , were identified as the two mauin parameters that influence the performance of the Lana-Match model. The Lana Matching Model perform its best when  $T_f$  is much larger than  $T_c$ . (i.e  $T_f >> T_c$ ). The following five test cases were designed to study the impact of these parameters on the over all performance of this implementation of the Lana-Match model and to identify the best conditions at which the Lana-Match performs the best.

- Case-1: Totally Independent Light Action Instantiations, T<sub>f</sub> is much greater than

T<sub>c</sub>.

- Case-2: Totally Independent Heavy Action Rules, T<sub>f</sub> is much smaller than T<sub>c</sub>.

- Case-3: Enabling Dependent Rules with Additions, T<sub>f</sub> is larger than T<sub>c</sub>.

- Case-4: Enabling Dependent Rules with few Additions and Deletions, this is similar to case-3, T<sub>f</sub> larger than T<sub>c</sub>.

- Case-5: Enabling Dependent Rules with many Additions and Deletions, this is similar to case 3 and case 4, except that T<sub>f</sub> larger than T<sub>c</sub>.

# 4.1 Case 1: Totally Independent Light Action Instantiations

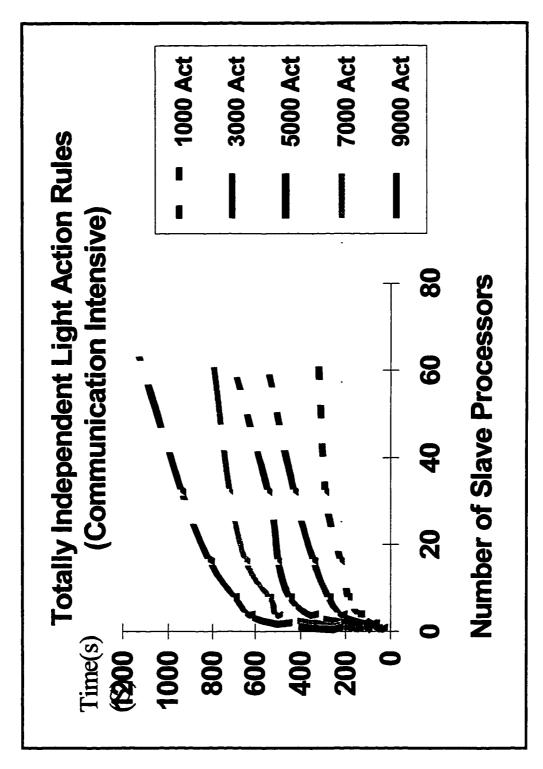

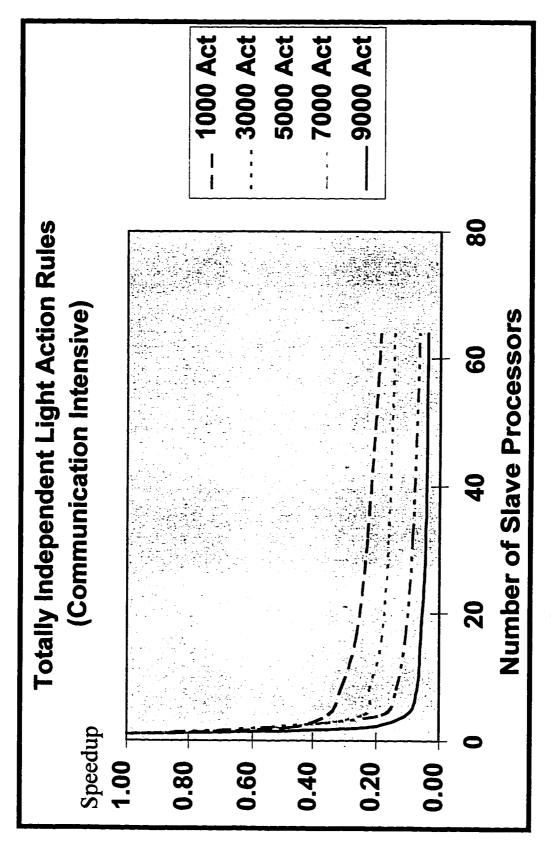

Light Actions instantiations are rules that the majority of their actions (i.e. RHS) requires very little CPU time. In another words, Light Action Instantiations are those ones with the average number of time units that are required to fire a rule  $T_f$  is very small. Five tests were designed with 1000, 3000, 5000, 7000 and 9000 of totally independent Light Action instantiations.

This case is demonstrated by Example 1 in Figure 9. It consists of one rule which requires a pair of facts to instantiate it and performs a simple action that consists of a simple PRINT statement that prints "Hello World". The performance of the Lana-Match model was measured for this case by instantiating the given rule 1000, 3000, 5000, 7000 and 9000 times by inserting 1000, 3000, 5000, 7000 and 9000 pairs of facts at the start-up time respectively. Figure 10 shows that the time that is required to execute these instantiations on clusters of 2, 4, 8, 16, 32 and 64 processors.

Figure 11 concludes that the Lana-Match model requires more time than the sequential version of the Rete-Match algorithm if the majority of the actions of the rules has light action as its RHS. This result is mainly due to big difference between the communication costs and the saving of parallelization. In another words,  $T_f$  <<  $T_c$ . Table 1 and Table 2 show the actual measured data for this case.

Figure 9 : Example of case 1

Figure 10: Totally Independent Light Action Rules, Actual Measured Time

Figure 11: Totally Independent Light Action Rules, Speedup

Table 1: Actual time measured in Case 1.

|    | 1000 | 3000 | 5000   | 7000 | 9000 |

|----|------|------|--------|------|------|

| 4- | 12   |      | ACL 82 | 114  |      |

| 2  | 49   | 61   | 101    | 217  | 435  |

| 4  | 115  |      | 319    |      |      |

| 8  | 170  |      |        |      |      |

| 16 | 203  | 321  |        |      |      |

| 32 |      |      | 523    |      | 919  |

| 64 | 608  | 623  | 869    | 786  |      |

Table 2 : Speedup data calculated for Case 2.

|    | 1000 | 3000 |      | 7000 | 0006 |

|----|------|------|------|------|------|

|    | Act  | Act  | Act  | _    | Act  |

| 1  | 1.00 | 1.00 | 1.00 | 1.00 | 1.00 |

| 2  | 0.24 | 0.57 | 0.81 | 0.53 | 0.48 |

| 4  | 0.10 | 0.18 | 0.26 | 0.24 | 0.35 |

| 8  | 0.07 | 0.14 | 0.19 | 0.22 | 0.31 |

| 16 | 0.06 | 0.11 | 0.17 | 0.18 | 0.27 |

| 32 | 0.04 | 0.09 | 0.16 | 0.16 | 0.23 |

| 64 | 0.04 | 90'0 | 0.12 | 0.15 | 0.19 |

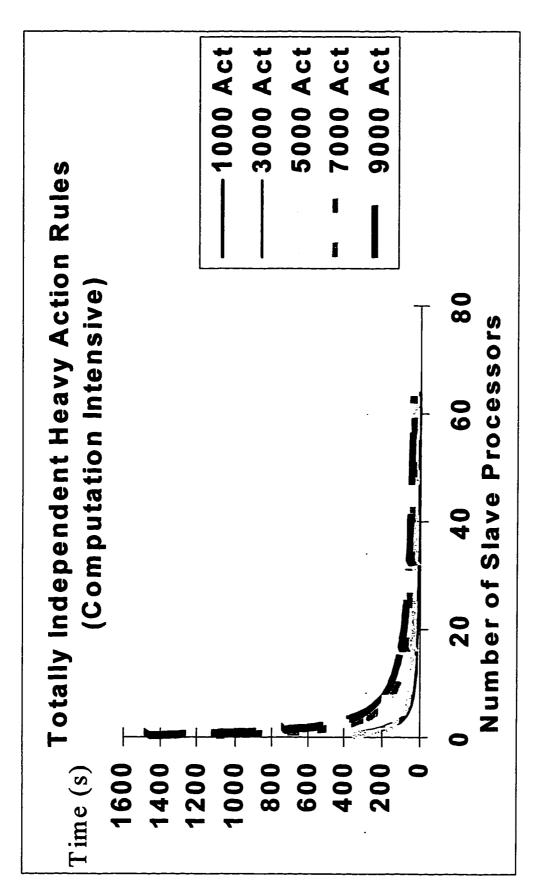

## 4.2 Case 2: Totally Independent Heavy Action Instantiations

Heavy Actions instantiations are rules that the majority of their actions (i.e. RHS) requires a lot of CPU time. In another words, Light Action Instantiations are those one with the average number of time units that are required to fire a rule  $T_f$  is very large. Five tests were designed with 1000, 3000, 5000, 7000 and 9000 of totally independent Light Action instantiations.

This case is demonstrated by Example 2 in Figure 12. It consists of one rule which requires a pair of facts to instantiate it and performs a heavy action on its RHS that consists of busy waiting of a WHILE loop statement. This WHILE statement rule makes the firing of the rule uses more CPU time. The performance of the Lana-Match model was measured for this case by conducting five different tests. These tests instantiated the given rule 1000, 3000, 5000, 7000 and 9000 times by inserting 1000, 3000, 5000, 7000 and 9000 pairs of facts at the start-up time respectively. Figure 13 shows that the time that is required to execute these instantiations on clusters 2, 4, 8, 16, 32 and 64 processors.

Figure 14 concludes that the Lana-Match model does achieve a significant speed up with respect to the number of processors in situations where the rule set consists of a very large number of independent rules were every rule has a heavy action to perform. Table 3 and Table 4 show the actual measured data for this case.

```

(defrule R1 " This is the only rule for case-2 !!!! "

(point1 ?x ?y)

(point2 ?y ?x)

=>

(printout t "Hello world !!!!!" crlf)

(while (> (* ?y ?x) 0)(+ ?x ?y)(bind ?y (- ?y 1)))

)

(deffacts startup "Initially insert 1000, 3000, 5000, 7000 and 9000

Paris facts for Test-1, Test-2, Test-3, Test-4 and Test-5"

(point1 1 2) (point2 2 1)

(point1 1 3) (point2 3 1)

(point1 1 4) (point2 4 1))

```

Figure 12 : Example of case 2

Figure 13: Totally Independent Heavy Action Rules, Actual Measured Time

Figure 14: Totally Independent Heavy Action Rules, Speedup

Table 3: Actual time measured in Case 2.

|    | 1000 | 3000 | 2000 | 2000 | 0006 |

|----|------|------|------|------|------|

|    | Act  | Act  | Act  | Act  | Act  |

| 1  | 272  | 328  |      | 1113 | 1489 |

| 2  | 151  | 190  | 185  | 999  | 746  |

| 4  | 74   | 98   | 66   | 279  | 370  |

| 8  | 34   | 14   | 25   | 138  | 185  |

| 16 | 17   | 21   | 78   | 0/   | 86   |

| 32 | 6    | 11   | 12   | 45   | 47   |

| 64 | 9    | 9    | 6.5  | 70   | 24   |

Table 4: Speedup data calculated for Case 2.

|    | 1000  | 3000  | 2000  | 7000  | 0006  |

|----|-------|-------|-------|-------|-------|

|    | Act   | Act   | Act   | Act   | Act   |

| 1  | 1.00  | 1.00  | 1.00  | 1.00  | 1.00  |

| 2  | 1.80  | 1.71  | 1.97  | 2.00  | 2.00  |

| 4  | 3.68  | 3.78  | 3.68  | 3.99  | 4.02  |

| 8  | 8.00  | 7.93  | 7.00  | 8.07  | 8.05  |

| 16 | 16.00 | 15.48 | 13.00 | 15.90 | 15.19 |

| 32 | 30.22 | 29.55 | 30.33 | 24.73 | 31.68 |

| 64 | 54.40 | 54.17 | 26.00 | 55.65 | 62.04 |

## 4.3 Case 3: Enabling Dependent Rules with Additions

Enabling Dependent Instantiations are rules that activates each others in a chained fashion in which executing an activation generates additions of facts that instantiate more activation on the agenda.

This case is demonstrated by Example 3 in Figure 15. It consists of four rules where the execution of these rules forms a chain of four consecutive instantiation sequence. The first rule requires a pair of facts to instantiate it which then inserts a pair of facts that instantiates the second rule (i.e. R2). Next, the execution of the second rule inserts a pair of facts that instantiates the third rule (i.e. R3) and so forth. The performance of the Lana-Match model was measured for this case by conducting five tests. These tests instantiate these four rules 1000, 3000, 5000, 7000 and 9000 times by inserting 1000, 3000, 5000, 7000 and 9000 pairs of facts respectively. Figure 16 shows that the time that is required to execute these instantiations on clusters 2, 4, 8, 16, 32 and 64 processors.

Figure 17 concludes that the Lana-Match model does achieve a significant speed up with respect to the number of processors. However, this speed up is not as big as the speed up in Case 2 which is manly due to the increase on the communication costs and the increased work for the CP. Table 5 and Table 6 show the actual measured data for this case.

```

EXAMPLE-3

(defrule R1 " This is the first rule" (point1 ?x ?y) (point2 ?y ?x)

=> (assert (point3 ?x ?y) (Point4 ?y ?x) )

(while (> (*?y?x) 0)(+?x?y)(bind?y(-?y 1))))

(defrule R2 "This is the second rule" (point3 ?x ?y)(point4 ?y ?x

\Rightarrow (assert (point5 ?x ?y) (Point6 ?y ?x))

(while (> (* ?y ?x) 0)(+ ?x ?y)(bind ?y (- ?y 1)))