### POLITECNICO DI TORINO Repository ISTITUZIONALE

Advancement on the Susceptibility of Analog Front-Ends to EMI

Original Advancement on the Susceptibility of Analog Front-Ends to EMI / BRIGNONE AIMONETTO, Marco. - (2019 Mar 25), pp. 1-145.

Availability: This version is available at: 11583/2730889 since: 2019-04-15T09:18:53Z

*Publisher:* Politecnico di Torino

Published DOI:10.6092/polito/porto/2730889

Terms of use: openAccess

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

Publisher copyright

(Article begins on next page)

### POLITECNICO DI TORINO

### SCUOLA DI DOTTORATO

Doctoral Program in Electronic Engineering – XXX cycle

Doctoral Thesis

## Advancement on the Susceptibility of Analog Front-Ends to EMI

Marco Brignone Aimonetto

Supervisor Franco Fiori Coordinator Ajmone Marsan Marco Giuseppe

Gennaio 2019

A Morgana Bianca, nata dalle acque inondate di sole. Coraggiosa scimmia e leone ruggente, gattina affettuosa e fedele cane. A te, che sei fatta d'universo, dono tutto ciò che realmente ho e sono: le mie parole e i miei pensieri.

### Summary

This thesis deals with the EMC characterization of analog front-ends, in particular the operational amplifier and the 2.4 GHz RF receiver. The former is largely used in electronic systems for its low-cost and versatility; it can be found almost in any front-end for signal conditioning, for example to accommodate the output of a sensor to the input of an analog to digital converter. The latter grows in importance for the Internet of Things applications being the 2.4 GHz Industrial, Scientific and Medical radio band licence free and widely used for wireless networking.

An initial objective of this study was to analyze the response of operational amplifiers to continuous wave interference referring in particular to the Direct RF Power Injection method. The upset induced by disturbance has been discussed by theoretical analysis, simulations and measurements. It has been found that smallsignal models have limited validity in predicting the susceptibility of amplifiers.

The natural progression of this work was to analyze the response of amplifiers subjected to multi-tone disturbance. The upset of such interference has been found to be not only the generation of a DC offset but also the appearance of a lowfrequency beat component in the case of intermodulation distortion.

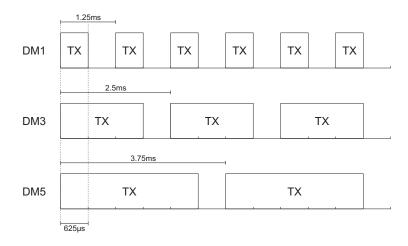

This is an important issue for future research. On one hand, actual disturbance, intentional or unintentional RF emissions, are poorly described by the CW approach. It is sufficient to think about the wireless data transmissions. The RF emission for equipment based on the time division multiple access is mostly a high-frequency burst with a slow repetition rate. On the other hand, the interference injection test set-up can be modified by using an arbitrary waveform generator to measure and evaluate the response of both analog and digital circuits when subjected to actual interference.

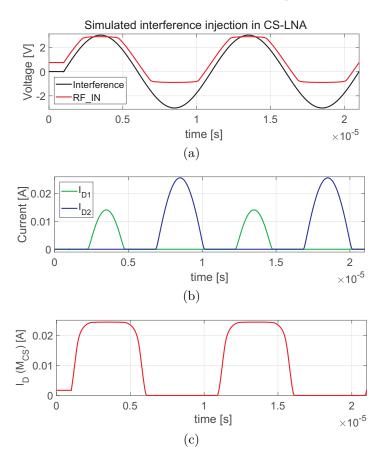

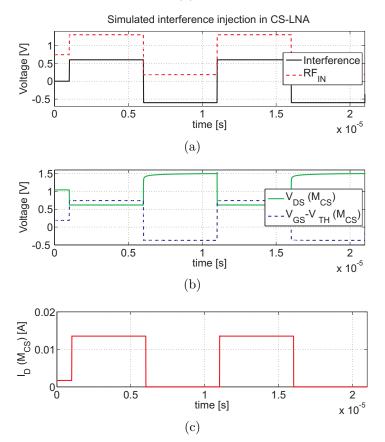

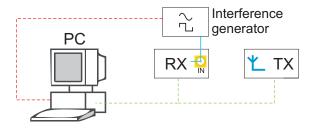

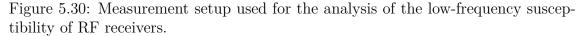

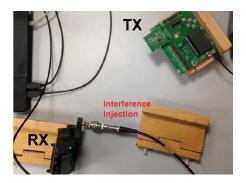

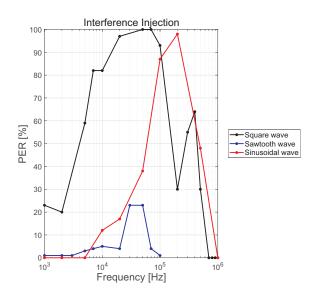

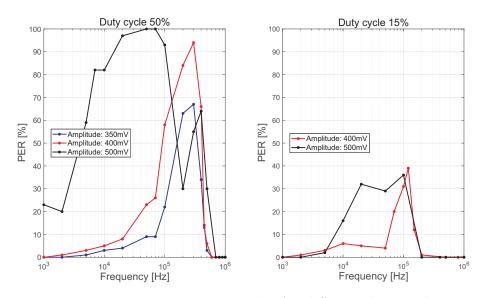

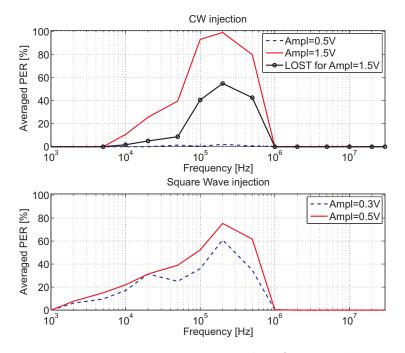

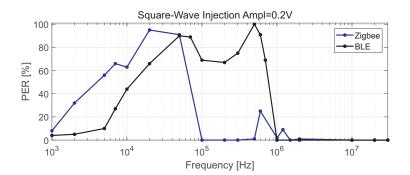

Another important finding in this study was that 2.4 GHz transceivers were susceptible to low-frequency disturbance. Several interfering waveforms, not only the continuous wave, were injected directly in the receiver front-end once the wireless communication has been set. The measurement set-up was similar to the DPI method and results showed relevant errors for the square wave injection, even the interruption of the communication. The errors induced by the low-frequency interference were related to the time in which the input transistors of the LNA were switched-off. If the LNA does not provide an useful signal for a time that is equal or greater than the symbol period, then the stages that follows in the receiver chain can't successfully decode the information.

## Contents

| Sι | imm                    | ary                                                                | V  |

|----|------------------------|--------------------------------------------------------------------|----|

| In | trod                   | uction                                                             | 1  |

| 1  | The                    | e problem of interference                                          | 5  |

|    | 1.1                    | Sources of interference                                            | 6  |

|    | 1.2                    | Coupling path                                                      | 8  |

|    |                        | 1.2.1 Electromagnetic coupling                                     | 9  |

|    |                        | 1.2.2 Low-frequency lumped-element approximation                   | 12 |

|    | 1.3                    | Receptor circuit                                                   | 14 |

| 2  | $\mathbf{E}\mathbf{M}$ | C of Operational Amplifier                                         | 15 |

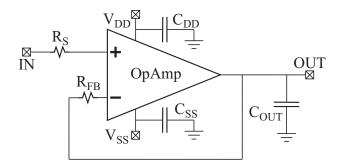

|    | 2.1                    | OpAmp model                                                        | 18 |

|    | 2.2                    | Offset induced by RF interference                                  | 21 |

|    |                        | 2.2.1 Model for the offset prediction                              | 22 |

|    | 2.3                    | Measurement and evaluation of the EMI susceptibility               | 27 |

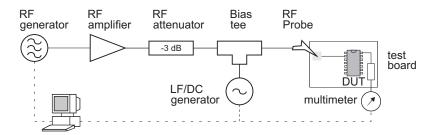

|    |                        | 2.3.1 DPI set-up                                                   | 28 |

|    |                        | 2.3.2 Model for DPI analysis                                       | 29 |

| 3  | Inve                   | estigation on the EMIRR to qualify OpAmps                          | 37 |

|    | 3.1                    | EMI Rejection Ratio                                                | 37 |

|    |                        | 3.1.1 Quadratic relationship between offset and RFI peak amplitude | 39 |

|    | 3.2                    | EMIRR evaluation on commercially available OpAmps                  | 41 |

|    |                        | 3.2.1 Comparison between EMIRR prediction and actual measured      |    |

|    |                        | offset                                                             | 45 |

|    | 3.3                    | Discussion                                                         | 54 |

| 4  | Sus                    | ceptibility of OpAmps to Multi-Tone Interference                   | 57 |

|    | 4.1                    | Multi-tone analysis                                                | 59 |

|    |                        | 4.1.1 Offset induced by multi-tone injection                       | 61 |

|    |                        | 4.1.2 Intermodulation distortion                                   | 63 |

|         |                                                 | 4.1.3 Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 67                                                                                                                 |

|---------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

|         | 4.2                                             | Susceptibility measurements with two-tone interference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 68                                                                                                                 |

| 5       | Sus                                             | ceptibility of 2.4 GHz Receivers to Low-Frequency Interference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 73                                                                                                                 |

|         | 5.1                                             | ETSI EN 300 328 and EMC Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 75                                                                                                                 |

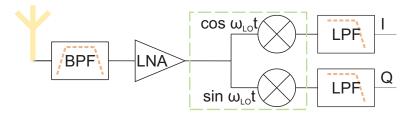

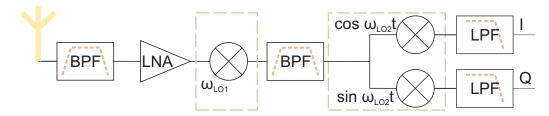

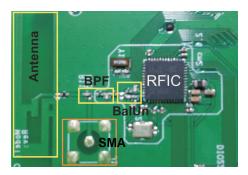

|         | 5.2                                             | 2.4 GHz Receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 77                                                                                                                 |

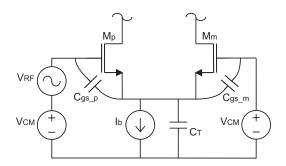

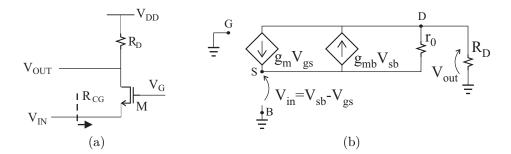

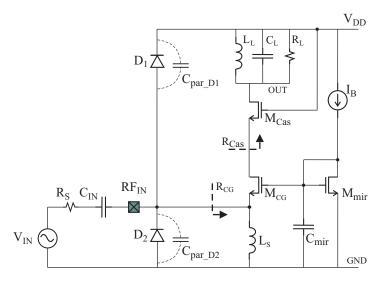

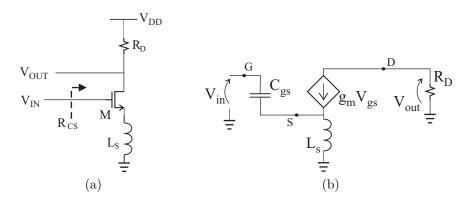

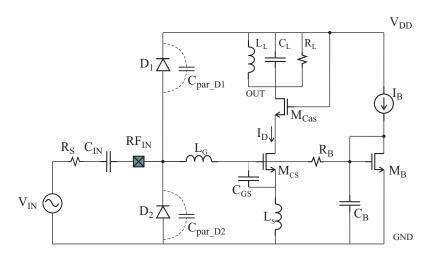

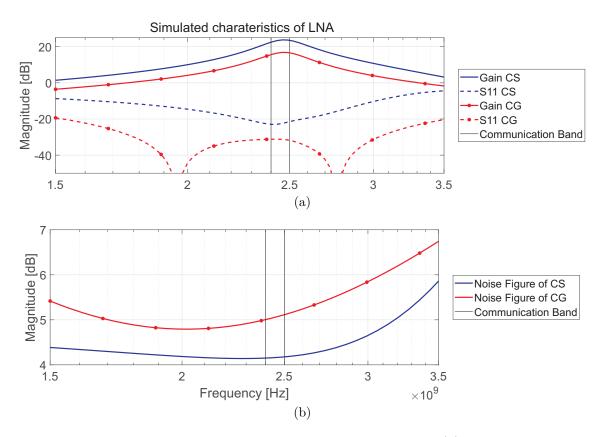

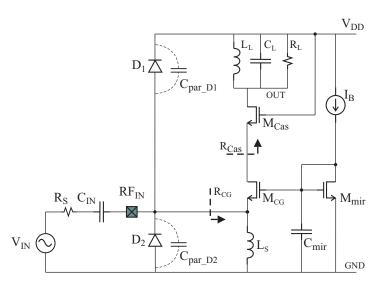

|         |                                                 | 5.2.1 Low Noise Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 79                                                                                                                 |

|         |                                                 | 5.2.2 Susceptibility to Low-Frequency EMI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 83                                                                                                                 |

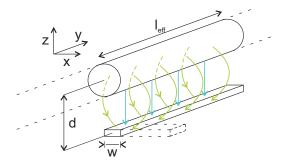

|         | 5.3                                             | EMI coupling and propagation to the receiver input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 87                                                                                                                 |

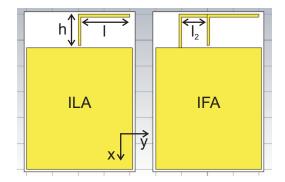

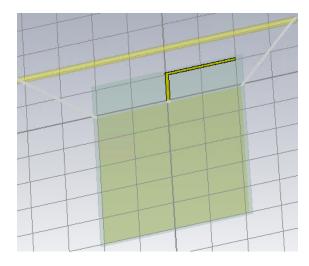

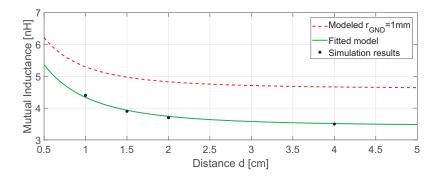

|         |                                                 | 5.3.1 Coupling with PCB printed antennas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 87                                                                                                                 |

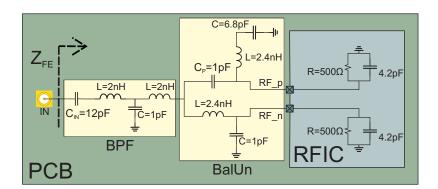

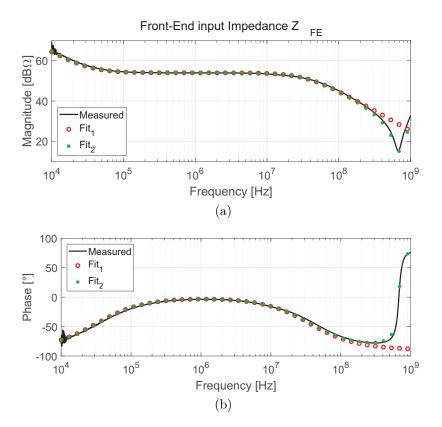

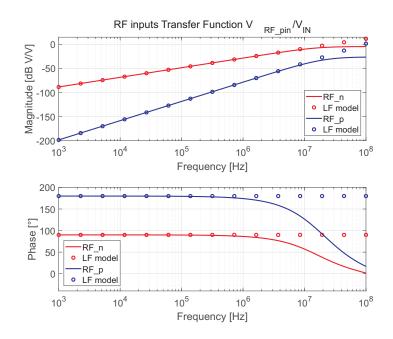

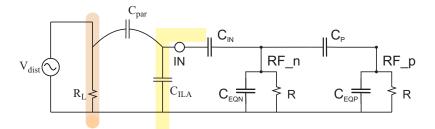

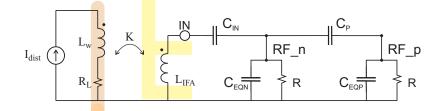

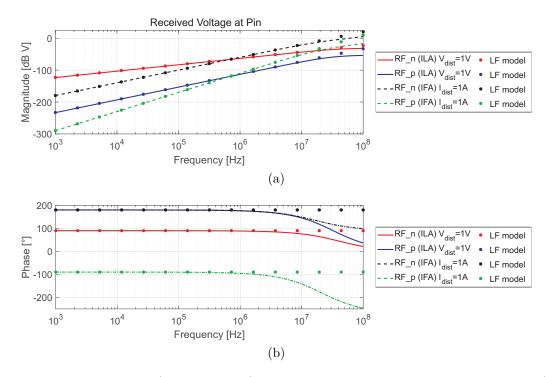

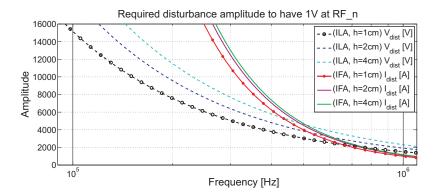

|         |                                                 | 5.3.2 Propagation in the Front End                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 92                                                                                                                 |

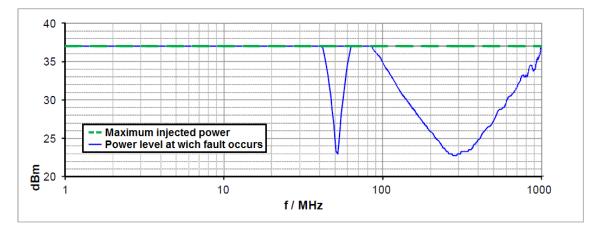

|         | 5.4                                             | Low-Frequency susceptibility measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 98                                                                                                                 |

|         |                                                 | 5.4.1 Differential receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 102                                                                                                                |

|         |                                                 | 5.4.2 Single-ended receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 104                                                                                                                |

|         |                                                 | 5.4.3 Comparison between BLE and Zigbee                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 105                                                                                                                |

|         | 5.5                                             | Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 107                                                                                                                |

|         |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                    |

| Co      | onclu                                           | sion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 109                                                                                                                |

|         |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 109<br>111                                                                                                         |

| Bi      | bliog                                           | raphy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                    |

| Bi      | bliog                                           | raphy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 111 $115$                                                                                                          |

| Bi      | bliog<br>Sma                                    | raphy III signal analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $111 \\ 115 \\ 115 \\ 115$                                                                                         |

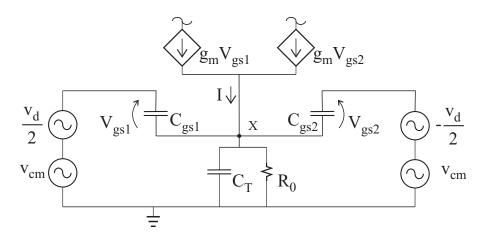

| Bi      | bliog<br>Sma<br>A.1                             | graphy<br>all signal analysis<br>Fluctuation of the bias current of the differential pair                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 111<br>115<br>115<br>116                                                                                           |

| Bi      | bliog<br>Sma<br>A.1<br>A.2                      | graphy       I         all signal analysis       I         Fluctuation of the bias current of the differential pair       I         Gate to source voltage of the differential pair transistors       I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 111<br>115<br>115<br>116<br>117                                                                                    |

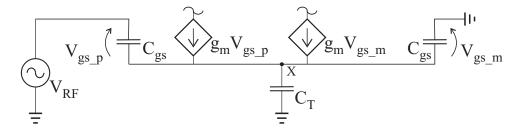

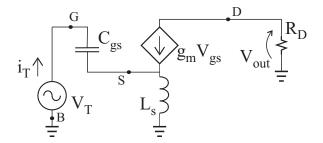

| Bi      | <b>bliog</b><br><b>Sma</b><br>A.1<br>A.2<br>A.3 | graphy       I         all signal analysis       I         Fluctuation of the bias current of the differential pair       I         Gate to source voltage of the differential pair transistors       I         Input impedance of the Common Gate LNA       I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 111<br>115<br>115<br>116<br>117<br>118                                                                             |

| Bi      | <b>Sma</b><br>A.1<br>A.2<br>A.3<br>A.4          | graphy       I         all signal analysis       I         Fluctuation of the bias current of the differential pair       I         Gate to source voltage of the differential pair transistors       I         Input impedance of the Common Gate LNA       I         Voltage gain of the Common Gate LNA       I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 111<br>115<br>115<br>116<br>117<br>118<br>119                                                                      |

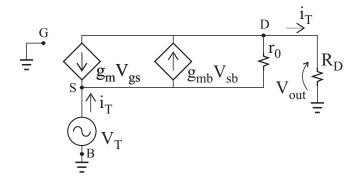

| Bi      | bliog<br>A.1<br>A.2<br>A.3<br>A.4<br>A.5<br>A.6 | graphy       Il signal analysis       Image: Second | 111<br>115<br>115<br>116<br>117<br>118<br>119                                                                      |

| Bi<br>A | bliog<br>A.1<br>A.2<br>A.3<br>A.4<br>A.5<br>A.6 | graphy       Il signal analysis       Image: Second | <ol> <li>111</li> <li>115</li> <li>116</li> <li>117</li> <li>118</li> <li>119</li> <li>120</li> <li>123</li> </ol> |

# List of Figures

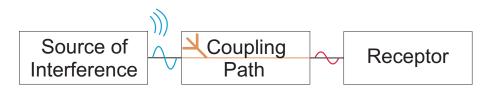

| 1.1  | Block diagram representing the interference problem.                                                                                 | 6  |

|------|--------------------------------------------------------------------------------------------------------------------------------------|----|

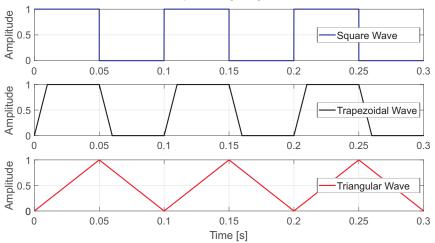

| 1.2  | Representation of digital pulses in time domain.                                                                                     | 7  |

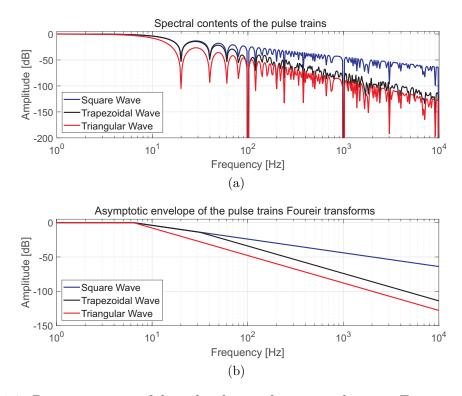

| 1.3  | Representation of digital pulses in frequency domain. Fourier trans-                                                                 |    |

|      | form (a) and asymptotic envelope (b).                                                                                                | 7  |

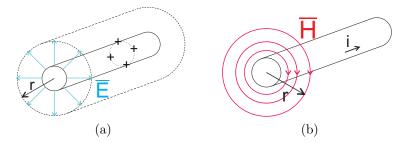

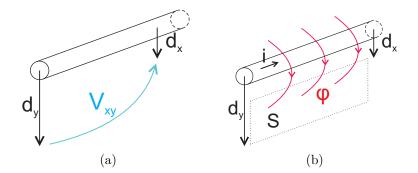

| 1.4  | Representation of electric field (a) and magnetic field (b) around a                                                                 |    |

|      | wire                                                                                                                                 | 9  |

| 1.5  | Representation of basic problems: voltage difference between two<br>points near a charged wire (a) and magnetic flux density through |    |

|      | a surface near a wire carrying current (b)                                                                                           | 10 |

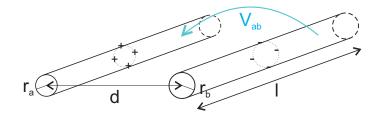

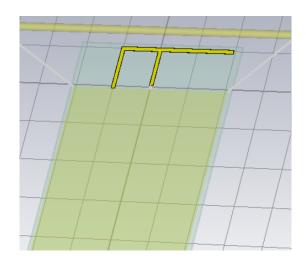

| 1.6  | Geometry for the mutual capacitance evaluation.                                                                                      | 11 |

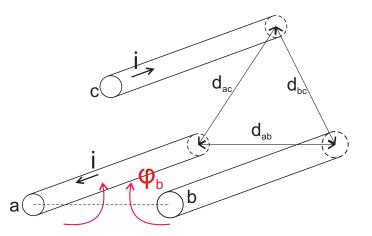

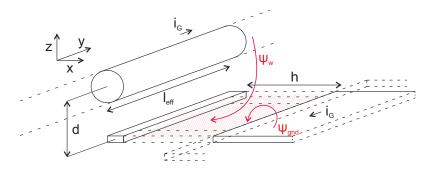

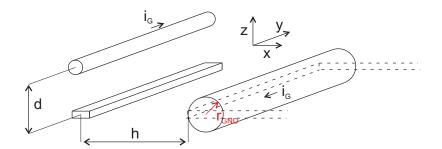

| 1.7  | Geometry for the mutual inductance evaluation                                                                                        | 12 |

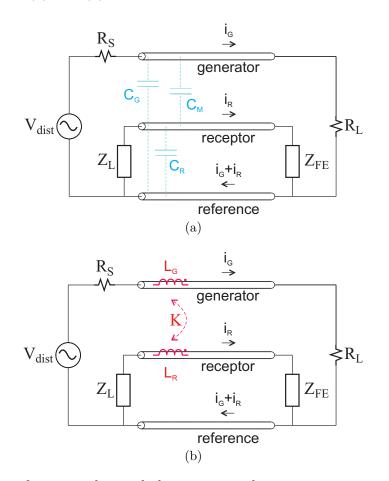

| 1.8  | Low-frequency lumped-element equivalent circuit representing the elec-                                                               |    |

|      | tromagnetic coupling between wires. Capacitive coupling (a) and in-                                                                  |    |

|      | ductive coupling (b) simplifications.                                                                                                | 13 |

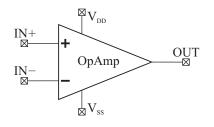

| 2.1  | Symbol of the Operational Amplifier                                                                                                  | 15 |

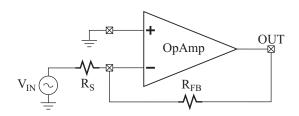

| 2.2  | Schematic of the inverting amplifier.                                                                                                | 16 |

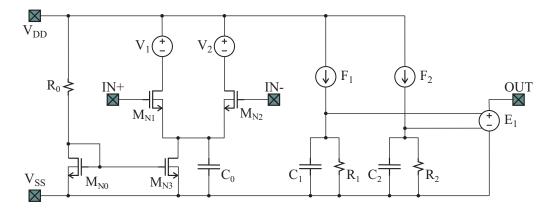

| 2.3  | Schematic of the modeled Operational Amplifier.                                                                                      | 18 |

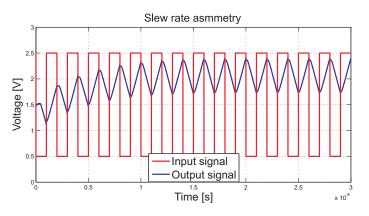

| 2.4  | Simulation results highlighting the DC offset shift caused by the SR                                                                 |    |

|      | asymmetry.                                                                                                                           | 22 |

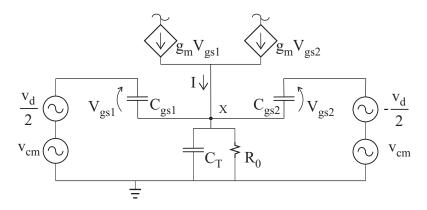

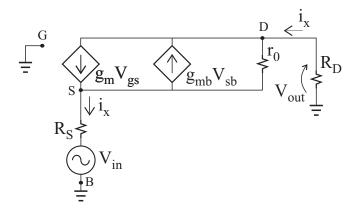

| 2.5  | Differential pair small-signal equivalent circuit                                                                                    | 23 |

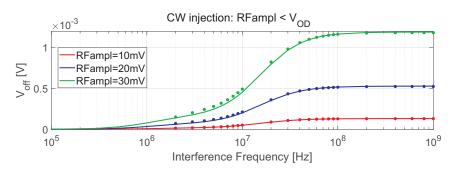

| 2.6  | Simulation of EMI induced offset due to CW injection (RF amplitude                                                                   |    |

|      | lower than the overdrive voltage)                                                                                                    | 26 |

| 2.7  | Simulation of EMI induced offset due to CW injection (RF amplitude                                                                   |    |

|      | near the overdrive voltage).                                                                                                         | 26 |

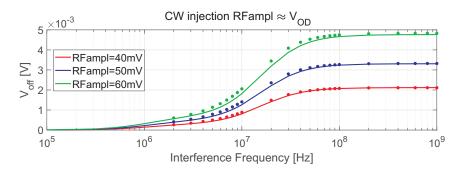

| 2.8  | Simulation of EMI induced offset due to CW injection (RF amplitude                                                                   |    |

|      | higher than the overdrive voltage).                                                                                                  | 27 |

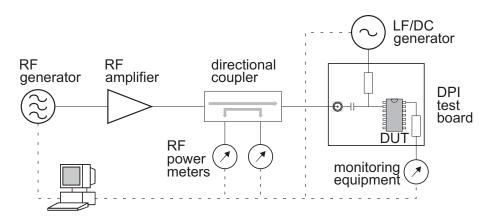

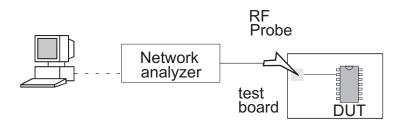

| 2.9  | DPI test set-up.                                                                                                                     | 28 |

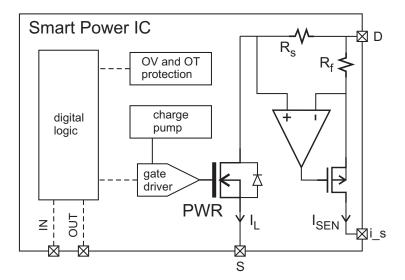

| 2.10 | Block diagram of the Smart Power IC.                                                                                                 | 29 |

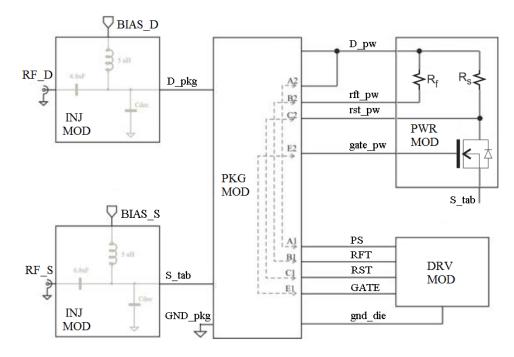

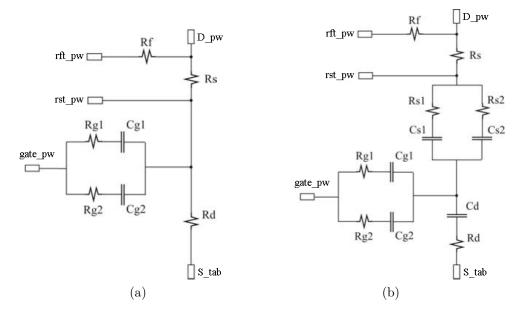

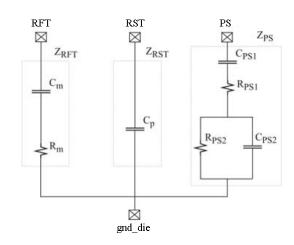

| 2.11 | Macromodel of the Smart Power IC used for the DPI analysis                                                                           | 31 |

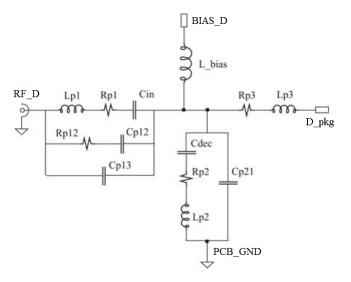

| 2.12 |                                                                                                                                      |    |

|      | tracted from measurements)                                                                                                           | 31 |

| 2.13 | Equivalent circuit of the power MOS switched ON (a) and OFF (b)      |      |

|------|----------------------------------------------------------------------|------|

|      | extracted from measurements                                          | . 32 |

| 2.14 | Equivalent circuit of the top chip extracted from measurements       | . 33 |

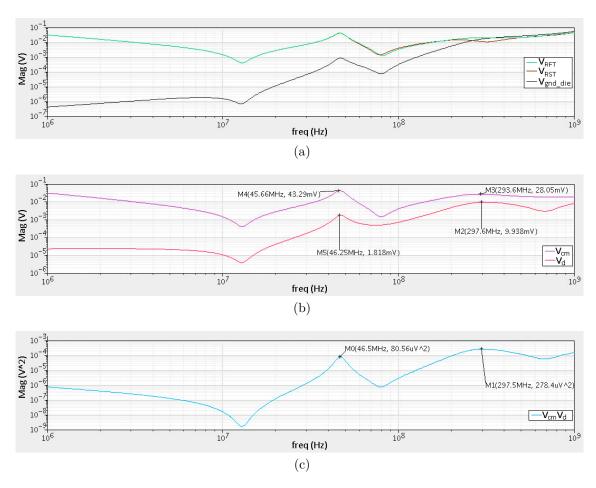

| 2.15 | Macromodel AC simulation for the amplifier susceptibility analysis   |      |

|      | (PWR switched OFF). Probed voltages (a), common mode and dif-        |      |

|      | ferential mode (b) and their product (c).                            | . 34 |

| 2.16 | DPI test results (PWR switched OFF).                                 |      |

| 3.1  | Measurement test set-up for the EMIRR and the offset evaluations.    |      |

| 3.2  | Differential pair schematic.                                         |      |

| 3.3  | Schematic of the Devices under test (OpAmp connected as voltage      |      |

|      | follower).                                                           | . 42 |

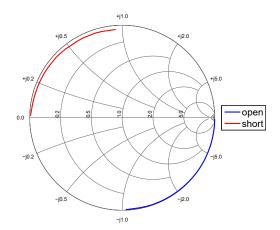

| 3.4  | Test set-up for the measurement of the DUTs input impedance.         |      |

| 3.5  | Z Probe reflection coefficient.                                      |      |

| 3.6  | DUTs reflection coefficients before and after de-embedding.          |      |

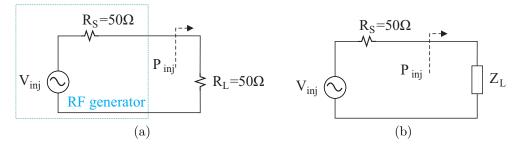

| 3.7  | Circuits for the peak amplitude calculation. Matched load (a) and    |      |

|      | arbitrary load (b).                                                  | . 44 |

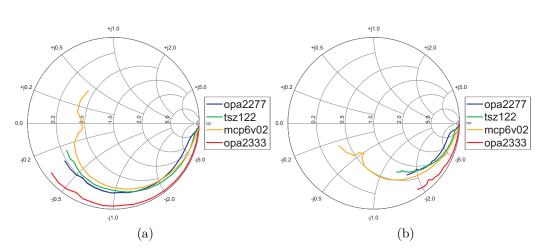

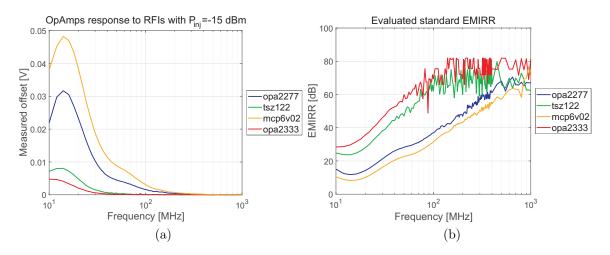

| 3.8  | Measured RFIs induced offset (a) and standard EMIRR evaluated        |      |

|      | from measurement results (b).                                        | . 46 |

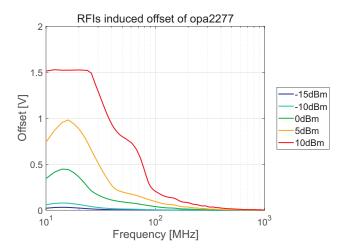

| 3.9  | Measured RFIs induced offset of OPA2277 for all the injected RF      |      |

|      | power levels.                                                        | . 46 |

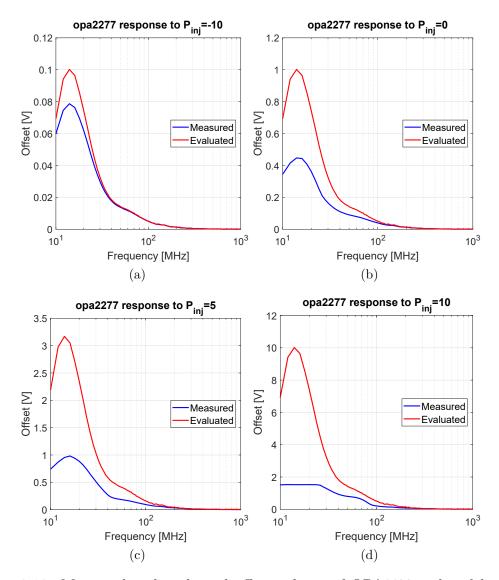

| 3.10 | Measured and evaluated offset voltage of OPA2277 induced by RFIs     |      |

|      | injected at constant power of -10dBm (a), 0dBm (b), 5dBm (c) and     |      |

|      | 10dBm (d)                                                            | . 47 |

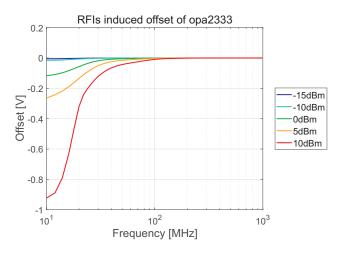

| 3.11 | Measured RFIs induced offset of OPA2333 for all the injected RF      |      |

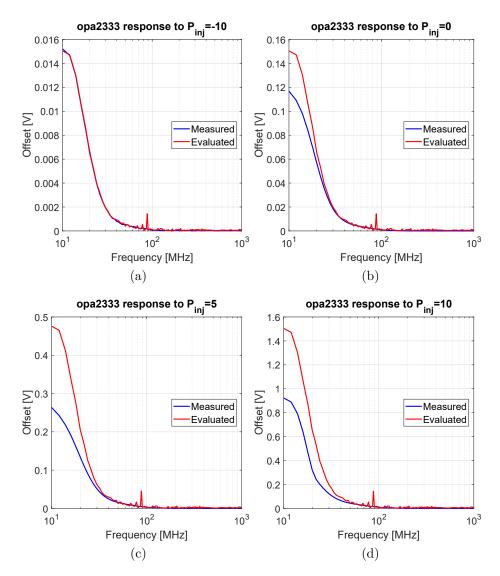

|      | power levels                                                         | . 48 |

| 3.12 | Measured and evaluated offset voltage of OPA2333 induced by RFIs     |      |

|      | injected at constant power of -10dBm (a), 0dBm (b), 5dBm (c) and     |      |

|      | 10dBm (d)                                                            | . 49 |

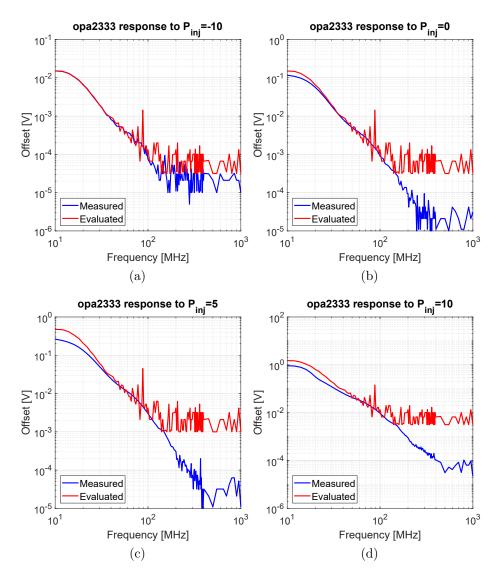

| 3.13 | Measured and evaluated offset voltage of OPA2333 induced by RFIs     |      |

|      | injected at constant power of -10dBm (a), 0dBm (b), 5dBm (c) and     |      |

|      | 10dBm (d) in double logarithmic scale.                               | . 50 |

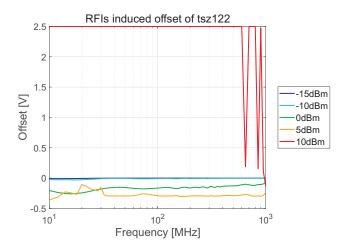

| 3.14 | Measured RFIs induced offset of TSZ122 for all the injected RF power |      |

|      | levels.                                                              | . 51 |

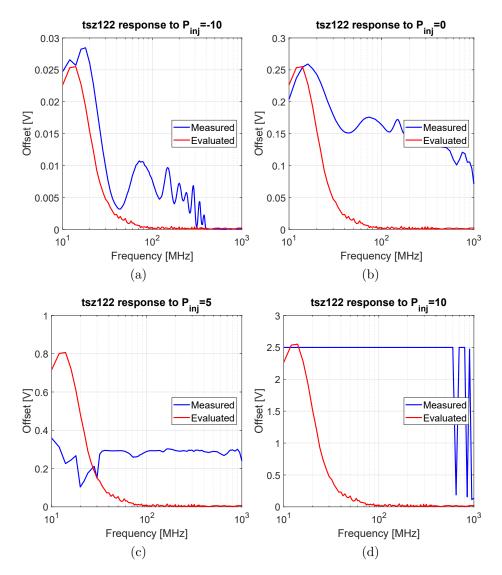

| 3.15 | Measured and evaluated offset voltage of TSZ122 induced by RFIs      |      |

|      | injected at constant power of -10dBm (a), 0dBm (b), 5dBm (c) and     | •    |

| 0.10 | 10dBm (d)                                                            | . 52 |

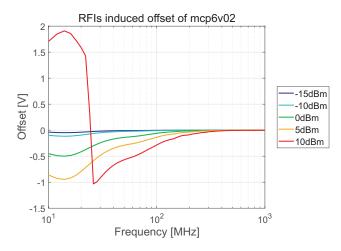

| 3.16 | Measured RFIs induced offset of MCP6V02 for all the injected RF      | 50   |

| 0.15 | power levels                                                         | . 53 |

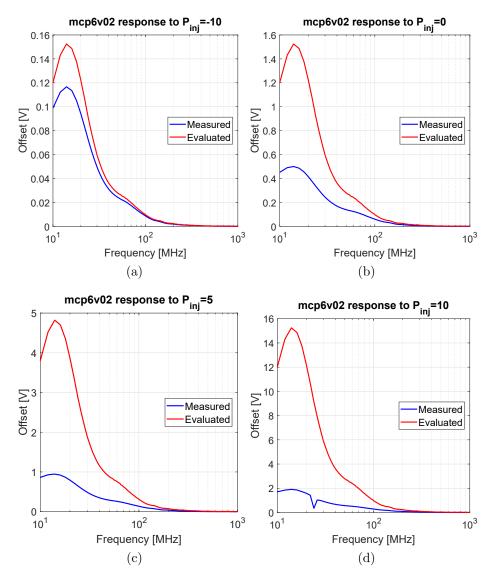

| 3.17 | Measured and evaluated offset voltage induced by RFIs injected at    | ۳.4  |

|      | constant power of -10dBm (a), 0dBm (b), 5dBm (c) and 10dBm (d).      | . 54 |

|      |                                                                      |      |

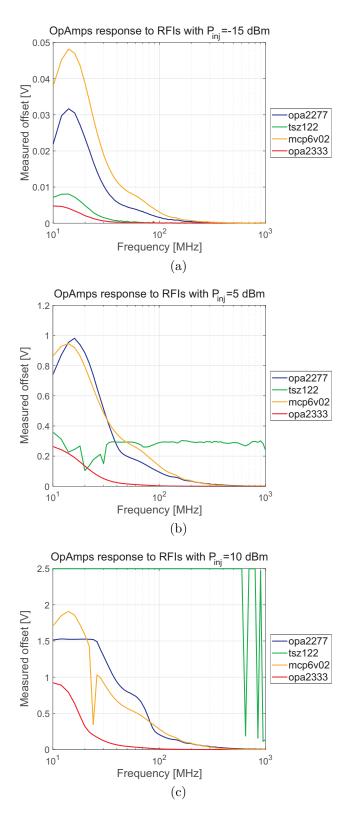

| 3.18  | Measured offset induced by RFIs injected at constant power of -<br>15dBm (a), 5dBm (b) and 10dBm (c).                                                            | 56 |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.1   | Example of channel occupation (Standard Bluetooth communication).                                                                                                | 58 |

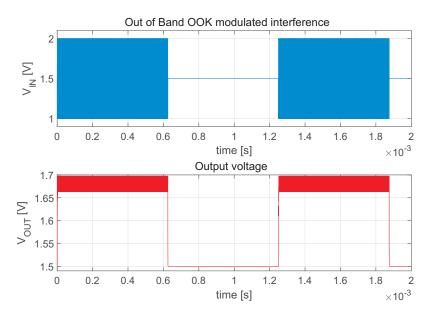

| 4.2   | Simulated upset induced by OOK modulated interference.                                                                                                           | 59 |

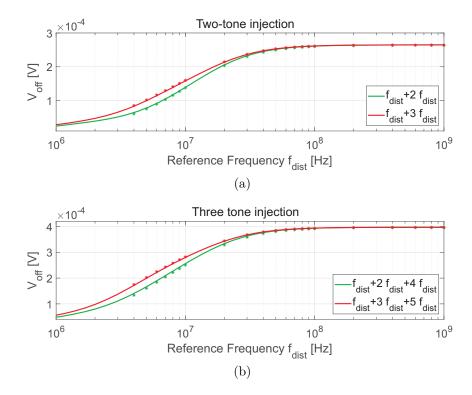

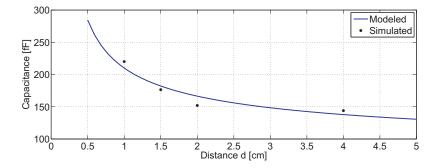

| 4.3   | Simulated (stars) and modeled (line) offset induced by the injection                                                                                             |    |

|       | of the multi-tone disturbance. Two-tones (a) and three-tones (b)                                                                                                 |    |

|       | injection. Each tone has an amplitude of 10 mV.                                                                                                                  | 61 |

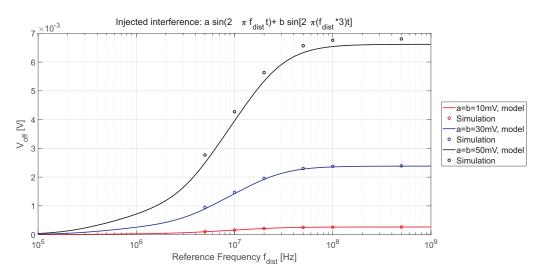

| 4.4   | Simulated and modeled offset induced by the injection of a two-tone                                                                                              |    |

|       | disturbance for the model validity analysis                                                                                                                      | 62 |

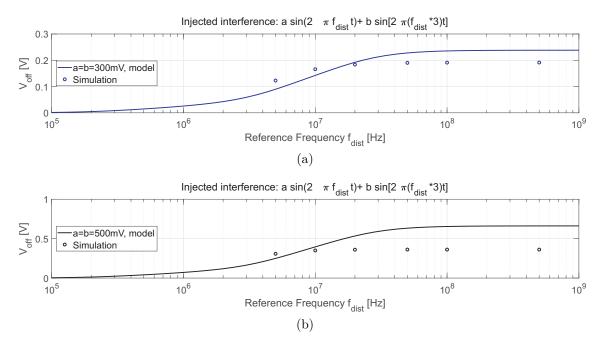

| 4.5   | Simulated and modeled offset induced by the injection of a two-tone                                                                                              |    |

|       | disturbance for the model validity analysis. (RF amplitudes $\gg V_{OD}$ ).                                                                                      | 62 |

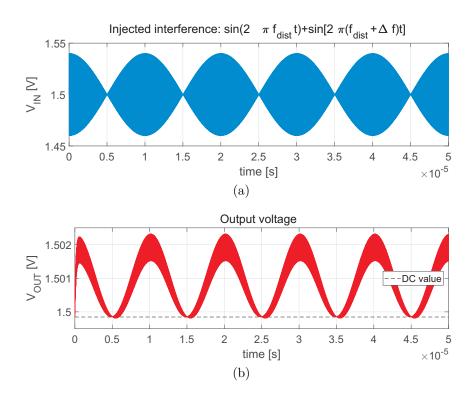

| 4.6   | Transient simulation highlighting the intermodulation distortion effect.                                                                                         | 63 |

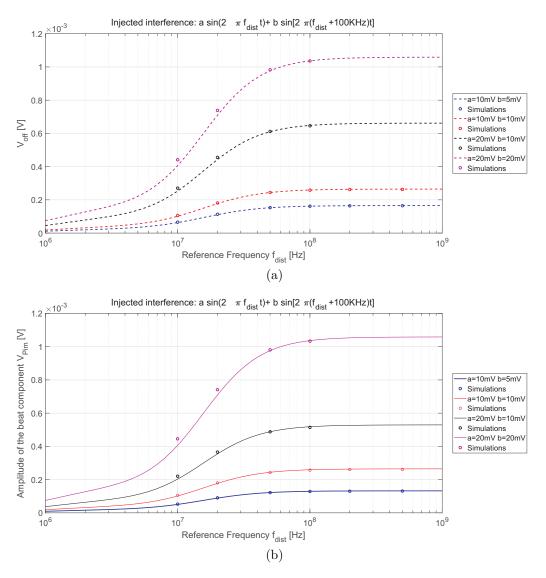

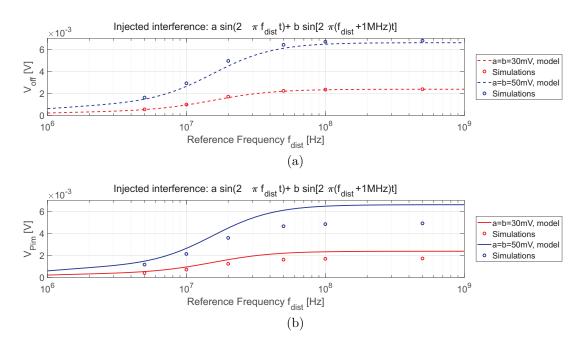

| 4.7   | Comparison between model prediction and simulation results for the                                                                                               |    |

|       | intermodulation analysis. Offset voltage (a) and beat component am-                                                                                              |    |

| 4.0   | plitude (b).                                                                                                                                                     | 64 |

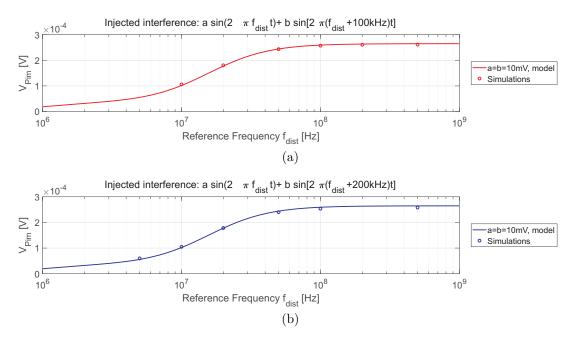

| 4.8   | Comparison between model prediction and simulation results for the interval lattice and $f = 100 \text{ MH}$ (1)                                                 | 05 |

| 4.0   | intermodulation analysis. $\Delta f = 100$ KHz (a) and $\Delta f = 200$ KHz (b).                                                                                 | 65 |

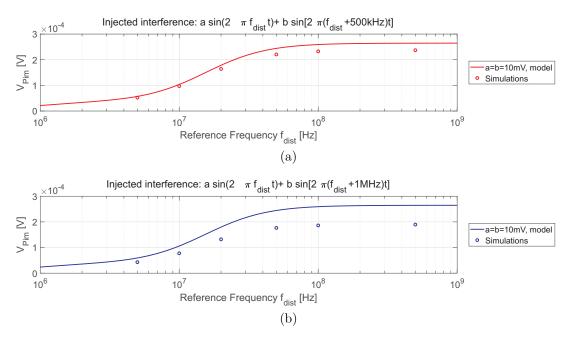

| 4.9   | Comparison between model prediction and simulation results for the intermodulation analysis. $\Delta f = 500 \text{ kHz}$ (a) and $\Delta f = 1 \text{ MHz}$ (b) | 66 |

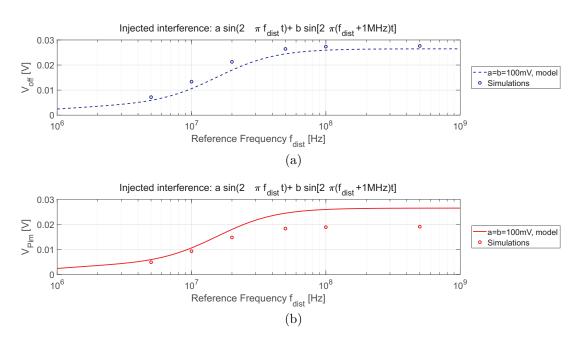

| 4.10  |                                                                                                                                                                  | 00 |

| 4.10  | intermodulation analysis $\Delta f = 1 \text{ MHz}$ . Offset voltage (a) and beat                                                                                |    |

|       | component amplitude (b). $\ldots$                                                                                                                                | 67 |

| 4.11  | Comparison between model prediction and simulation results for the                                                                                               | 01 |

|       | intermodulation analysis $\Delta f = 1 \text{ MHz}$ . Offset voltage (a) and beat                                                                                |    |

|       | component amplitude (b).                                                                                                                                         | 68 |

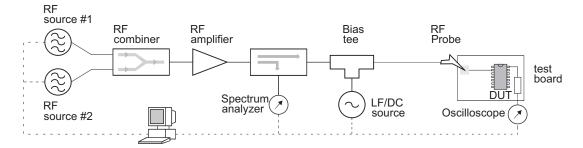

| 4.12  | Test setup for the two-tone susceptibility measurements.                                                                                                         | 69 |

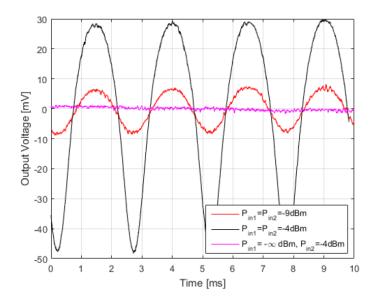

| 4.13  | Measurement results comparing the effects induced by the CW and                                                                                                  |    |

|       | the two-tone injection.                                                                                                                                          | 69 |

| 4.14  | Measurements of the OpAmp output voltage offset induced by inter-                                                                                                |    |

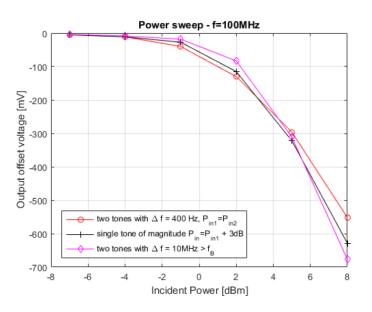

|       | ference injection at 100 MHz.                                                                                                                                    | 70 |

| 4.15  | Measurements of the OpAmp output voltage offset induced by inter-                                                                                                | 70 |

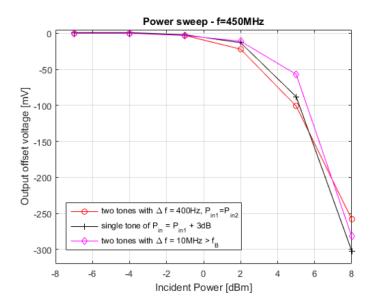

| 4 1 6 | ference injection at 450 MHz.                                                                                                                                    | 70 |

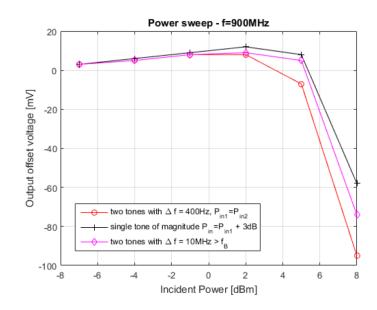

| 4.10  | Measurements of the OpAmp output voltage offset induced by inter-<br>ference injection at 900 MHz.                                                               | 71 |

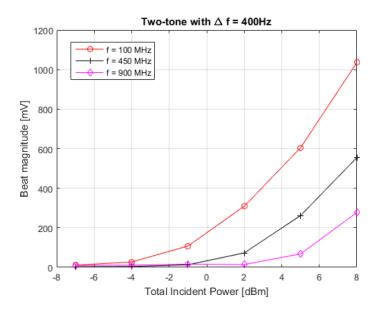

| 1 17  | Measurements of the magnitude of the beat component induced by                                                                                                   | 11 |

| 7.17  | intermodulation distortion ( $\Delta f = 400  \text{Hz}$ ).                                                                                                      | 72 |

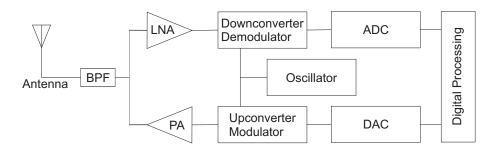

| 5.1   | Block diagram of a generic RF transceiver.                                                                                                                       | 74 |

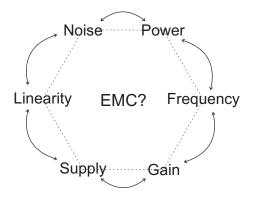

| 5.2   | RF design trade-offs.                                                                                                                                            | 74 |

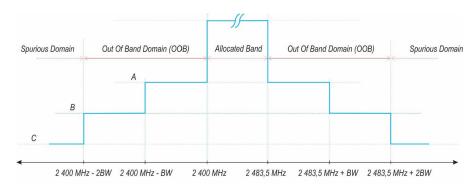

| 5.3   | ETSI EN 300 328: TX emission in out-of-band domain.                                                                                                              | 75 |

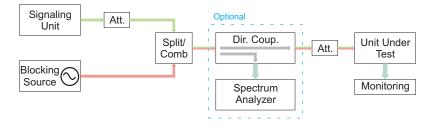

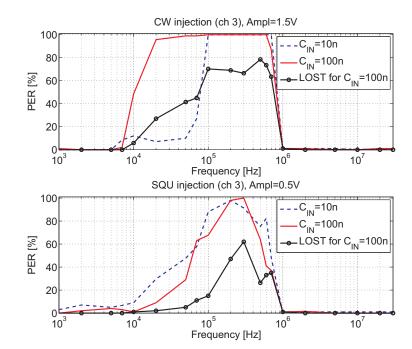

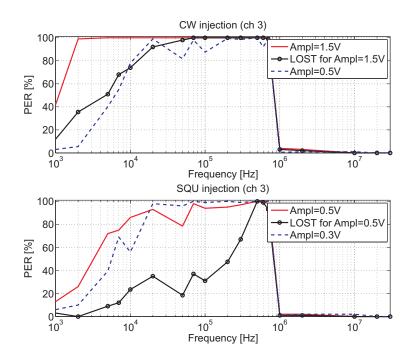

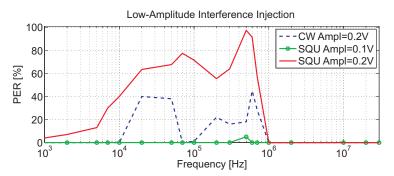

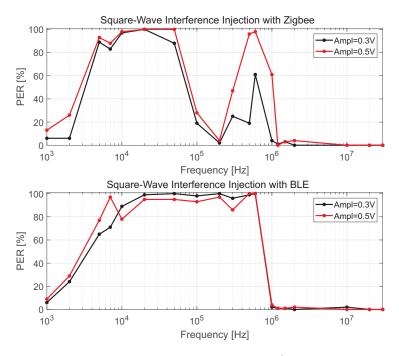

| 5.4   | ETSI EN 300 328: set-up arrangement for testing the receiver blocking.                                                                                           | 76 |