### POLITECNICO DI TORINO Repository ISTITUZIONALE

Infrastructures and Algorithms for Testable and Dependable Systems-on-a-Chip

*Original* Infrastructures and Algorithms for Testable and Dependable Systems-on-a-Chip / Di Carlo, S. - ELETTRONICO. - (2003), pp. 1-106.

*Availability:* This version is available at: 11583/2709266 since: 2018-07-17T08:31:44Z

*Publisher:* Politecnico di Torino

Published DOI:10.6092/polito/porto/2709266

Terms of use: openAccess

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

Publisher copyright

(Article begins on next page)

### POLITECNICO DI TORINO DOCTORAL SCHOOL

PhD Course in Computer and Control Engineering – XV cycle

PhD Dissertation

## Infrastructures and Algorithms for Testable and Dependable Systems-on-a-Chip

Stefano Di Carlo

**Tutor** Prof. Paolo Prinetto **Coordinator of the PhD** prof. Pietro Laface

2003

This work is subject to the Creative Commons Licence

## Contents

| Li | st of Tables                                                                                                                                                  | VI                                         |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| Li | st of Figures                                                                                                                                                 | VII                                        |

| 1  | Infrastructures and Algorithms for Testable and Dependable SoC1.1High Performance SoC Test Diagnosis and Failure Analysis1.2Memory Dominance                  | $\begin{array}{c} 1 \\ 2 \\ 3 \end{array}$ |

| Ι  | High Performance SoCs Test, Diagnosis and Failure Analysis                                                                                                    | <b>5</b>                                   |

| 2  | Introduction                                                                                                                                                  | 9                                          |

| 3  | State-of-the-Art                                                                                                                                              | 11                                         |

| 4  | Architecture Overview                                                                                                                                         | 13                                         |

| 5  | HD <sup>2</sup> BIST hierarchy configuration and scheduling                                                                                                   | 19                                         |

| 6  | RT-level Implementation6.1Test Block Architecture6.2Test Processor Architecture6.3IEEE 1149.1 interface6.4Scan Chain Router6.5Test Control Bus6.6Token Format | 25                                         |

| 7  | Using HD <sup>2</sup> BIST in SoC Testing7.1Testing BISTed and BIST-Ready Cores7.2Testing Scan Cores7.3Testing glue logic                                     | 29<br>29<br>30<br>30                       |

| 8  | Case study8.1DacTOPplus Architecture8.2DacTOP Test Structure                                                                                                  |                                            |

|    | 8.3  | DacTOPplus Test Structure                                                       |    |

|----|------|---------------------------------------------------------------------------------|----|

| 9  | Con  | iclusions                                                                       | 41 |

|    |      |                                                                                 |    |

| п  | M    | emory Dominance                                                                 | 43 |

| 10 | Intr | roduction                                                                       | 47 |

| 11 | An   | introduction to memory Test                                                     | 49 |

|    | 11.1 | The fault model                                                                 | 49 |

|    |      | 11.1.1 Memory Cell Faults                                                       | 49 |

|    |      | 11.1.2 Address decoder fault                                                    | 50 |

|    |      | 11.1.3 Read/Write logic faults                                                  | 50 |

|    | 11.2 | Memory test Algorithms                                                          | 50 |

| 12 | Mer  | mory BIST                                                                       | 51 |

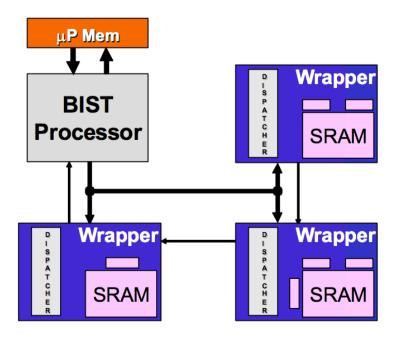

|    | 12.1 | The BIST Processor                                                              | 52 |

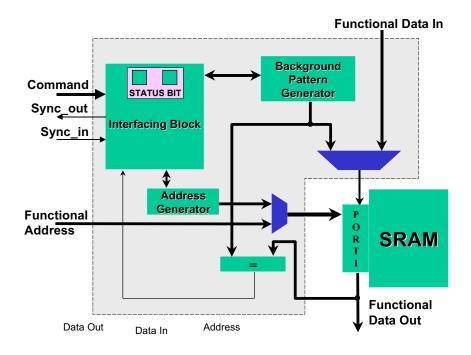

|    | 12.2 | Wrapper Structure                                                               | 54 |

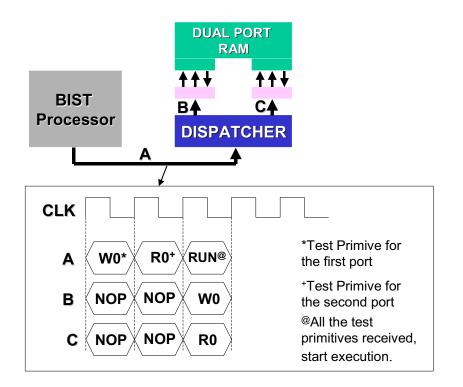

|    |      | 12.2.1 Dispatcher                                                               | 55 |

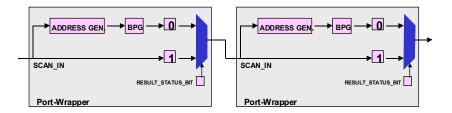

|    |      | 12.2.2 Port Wrapper                                                             | 55 |

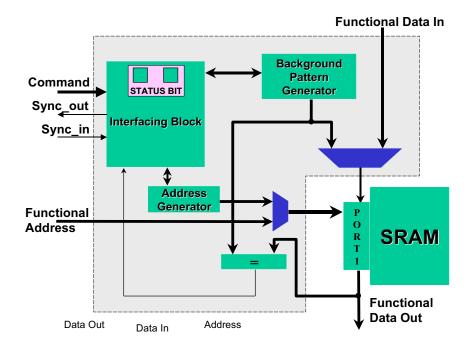

|    |      | 12.2.3 Multiplexing                                                             | 56 |

|    | 12.3 | Diagnosis                                                                       | 57 |

|    | 12.4 | Further optimizations                                                           | 57 |

|    |      | 12.4.1 Sharing Wrappers among SRAMs clusters                                    | 57 |

|    |      | 12.4.2 Using a Topological approach for complex coupling fault testing $\ldots$ | 58 |

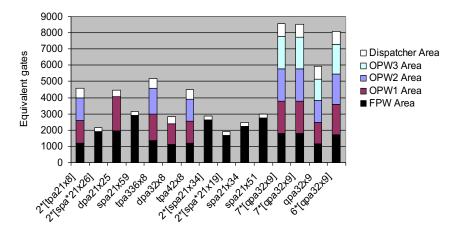

|    | 12.5 | Case study                                                                      | 58 |

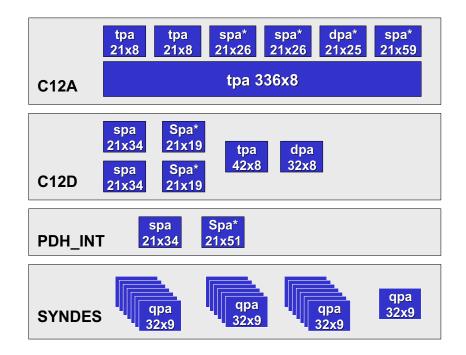

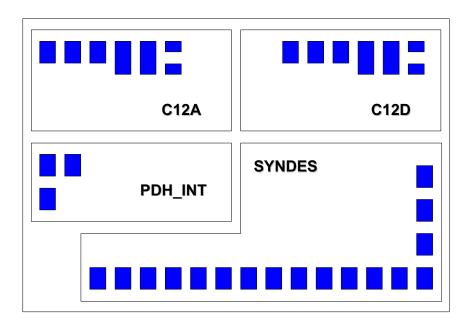

|    |      | 12.5.1 Case Study Architecture                                                  | 59 |

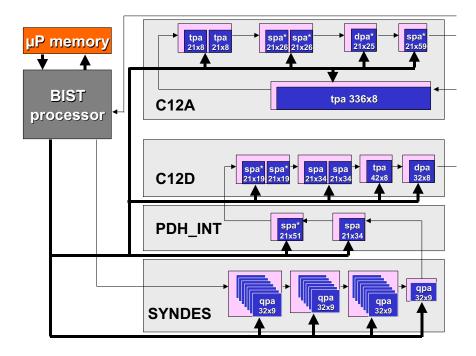

|    |      | 12.5.2 Case Study BISTArchitecture                                              | 60 |

|    |      | 12.5.3 Case Study BIST Scheduling                                               | 61 |

|    |      | 12.5.4 Experimental results                                                     | 62 |

| 13 | Aut  | comatic Test Generation                                                         | 67 |

|    | 13.1 | State of the Art                                                                | 67 |

|    | 13.2 | Memory Model                                                                    | 68 |

|    | 13.3 | March Test Generation Algorithm                                                 | 71 |

|    |      | 13.3.1 GTS Reordering                                                           | 74 |

|    |      | 13.3.2 GTS minimization                                                         | 74 |

|    |      | 13.3.3 March Test Generation                                                    | 75 |

|    | 13.4 | BFEs equivalence                                                                | 75 |

|    |      | 13.4.1 Experimental Results                                                     | 76 |

| 14 Memory Test Algorithms Verification | 77 |

|----------------------------------------|----|

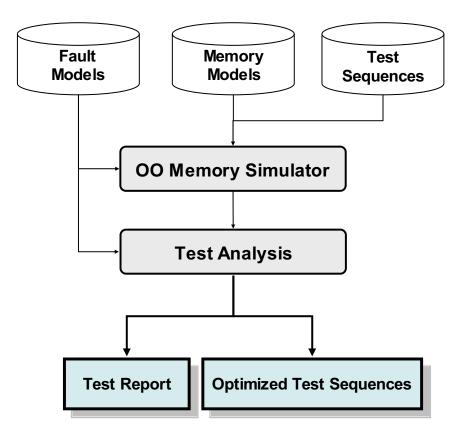

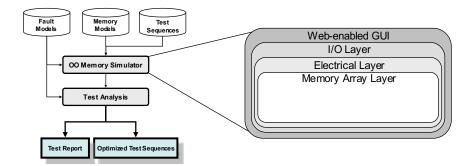

| 14.1 The Fault Simulator Architecture  | 77 |

| 14.2 The Electrical and Physical Model | 79 |

| 14.3 Input Test Sequences              | 79 |

| 14.4 Simulator Engine                  | 80 |

| 14.4.1 Test Analysis Module            | 81 |

| 15 Self Repair                         | 83 |

| 15.1 State of the art $\ldots$         | 84 |

| 15.2 The conceptual architecture       | 85 |

| 15.2.1 Memory Built In Self Repairing  | 86 |

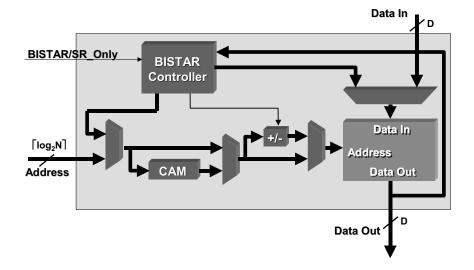

| 15.2.2 Memory Built In Self Testing    | 87 |

| 15.3 Actual Implementation             | 89 |

| 15.4 BISTAR validation                 | 91 |

| 15.5 Experimental results              | 91 |

| 15.5.1 Area overhead                   | 91 |

| 15.5.2 BISR Logic Fault Coverage       | 93 |

| 16 Conclusions                         | 95 |

| A Publication list                     | 97 |

| A.1 International journals             | 97 |

| A.1.1 Year 2003                        | 97 |

| A.2 International conferences          | 97 |

| A.2.1 Year 2002                        | 97 |

| A.2.2 Year 2001                        | 98 |

| A.2.3 Year 2000                        | 98 |

|                                        |    |

### Bibliography

# List of Tables

| 8.1  | DacTOPplus dimensions in Synopsys <sup>®</sup> equivalent gates     | <br>34 |

|------|---------------------------------------------------------------------|--------|

| 8.2  | DacTOP area with wrapped modules                                    | <br>36 |

| 8.3  | $HD^{2}BISTed DacTOP$ area occupation                               | <br>36 |

| 8.4  | Area result of DacTOPplus                                           | <br>38 |

| 12.1 | March Algorithm Test Primitives                                     | <br>53 |

| 12.2 | 8 bits Background patterns BP <sub>j</sub> for CFsts                | <br>54 |

| 12.3 | March Algorithm Representation                                      | <br>63 |

| 12.4 | Meanings of the Output Synchronization signal                       | <br>64 |

| 12.5 | Memory Wrapper overhead                                             | <br>65 |

| 12.6 | Total area overhead                                                 | <br>65 |

| 13.1 | Reordering Rewrite Rules                                            | <br>74 |

| 13.2 | Reordering Rewrite Rules                                            | <br>75 |

| 13.3 | Experimental Results                                                | <br>76 |

| 15.1 | Percentage of Area overhead introduced by the BISTAR Architecture . | <br>92 |

| 15.2 | BISR Logic Fault Coverage                                           | <br>93 |

# List of Figures

| 4.1  | $HD^2BIST$ Ring                                                                                          | 14 |

|------|----------------------------------------------------------------------------------------------------------|----|

| 4.2  | TCB (token bus) and TDB (scan bus)                                                                       | 15 |

| 4.3  | Test Block and core wrapper                                                                              | 15 |

| 4.4  | Test Processor architecture                                                                              | 16 |

| 4.5  | Connecting two rings                                                                                     | 17 |

| 5.1  | TDB connections                                                                                          | 20 |

| 6.1  | Test Block General Architecture                                                                          | 24 |

| 7.1  | Using of TDB to test different types of cores                                                            | 30 |

| 7.2  | Pseudo TDB lines for testing the glue logic                                                              | 31 |

| 8.1  | DacTOPplus schema                                                                                        | 34 |

| 8.2  | DacTOP HD <sup>2</sup> BIST schema $\ldots$                                                              | 35 |

| 8.3  | DacTOPplus with $HD^2BIST$                                                                               | 37 |

| 8.4  | Test program PROG[1] of the Top Level TP                                                                 | 38 |

| 8.5  | Test program PROG[2] of the TLTP                                                                         | 39 |

| 8.6  | Test program PROG[1] of the DacTOP macro                                                                 | 39 |

| 8.7  | Test program PROG[4] of the Top Level TP                                                                 | 40 |

| 8.8  | Test program PROG[3] of the DacTOP macro                                                                 | 40 |

| 12.1 | Basic memory-BIST Architecture                                                                           | 52 |

| 12.2 | Wrapper architecture                                                                                     | 55 |

|      | Test Instruction execution diagram                                                                       | 56 |

| 12.4 | Wrapper structure                                                                                        | 57 |

| 12.5 | Results_Scan_Chain                                                                                       | 58 |

| 12.6 | VC12AD memories organization                                                                             | 59 |

|      | VC12AD floorplan                                                                                         | 60 |

|      | VC12AD BIST Architecture                                                                                 | 61 |

| 12.9 | Wrappers area                                                                                            | 62 |

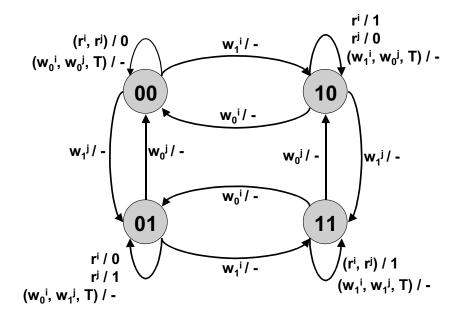

| 13.1 | $M_0$ FSM representing a fault free RAM $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 69 |

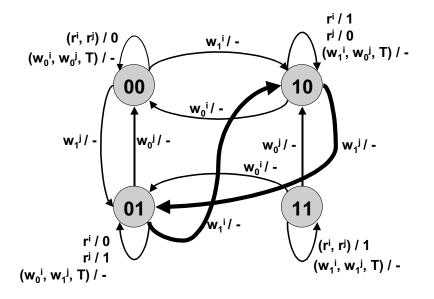

|      | $M_1: \langle \uparrow, 0 \rangle$ Idempotent Coupling Fault Representation                              | 70 |

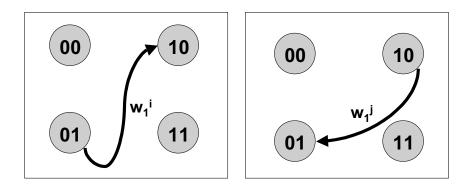

|      | BFE model for $\langle \uparrow, 0 \rangle$ Coupling Fault                                               | 70 |

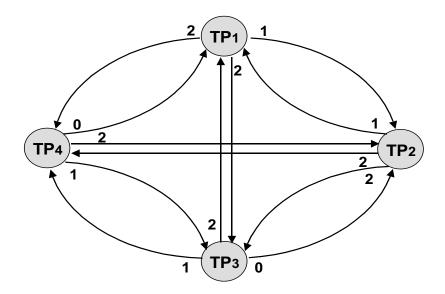

|      | TPG for $\{\langle \uparrow, 1 \rangle \langle \uparrow, 0 \rangle\}$                                    | 72 |

|      | Simulator architecture                                                                                   | 78 |

| 14.2 | Example of test algorithm including Neighborhood cells and a cycle state-                                |    |

|      | ment                                                                                                     | 80 |

| 14.3 | The simulator engine layered structure                                                                   | 80 |

| 15.1 | BISTAR conceptual architecture            | 85 |

|------|-------------------------------------------|----|

| 15.2 | Memory layout                             | 87 |

| 15.3 | Minimization of the address critical path | 90 |

#### "The Silicon Infrastructure Opportunity"

"Economists have long argued that the key factor for the boom in interstate automobile travel was not the mass production of the car as in Ford's Model T in the 1920s, but rather the highway infrastructure built near the end of World War II and into the postwar growth era. Market analysts have argued that the key factor for the adoption of semiconductor Intellectual Property (IP) was the realization that no System-on-a-Chip (SoC) semiconductor design team could develop every block of IP from scratch in a viable time-to-market window.

Despite all the announcements over SoCs in the trade press during the past few years, the widespread deployment of SoCs has still not occurred (with the exception of a few general-purpose, graphics, and game processor designs). However, SoCs will come into their own at the 0.13-micron technology node, a confluence of integrated complexity (Moore's law) and process fungibles (having memory and analog devices on a base-line digital process). Although both trends are necessary, they will not be sufficient to drive widespread SoC adoption.

Unlike prior process generations, the nanometer era will need more than just hardware-based tooling to realize production volumes. The mass production of 130-nm SoCs will require the commercial availability of Infrastructures (softwareassisted technologies that span the ramp from design tape-out to manufacturing). Examples of software-assisted tooling include mask synthesis, embedded test, process-yield simulation, automatic test generation and built-in reliability. By 2005, SoC component revenues will grow to \$35 billion (nearly 20%) of overall chip revenues, not including microprocessor units). The semiconductor IP component market (licensing and royalties) will be at \$2.6 billion. The silicon infrastructure market will catapult to \$3.4 billion. These bold predictions impinge on the ability of the emerging silicon infrastructure vendors to extract fair value for value added, that is a business model predicated on Time-To-Volume (TTV) royalty versus selling software seats as in the traditional electronic-design-automation model. The silicon infrastructure market has already seen some early success stories on this front. Hindsight will decisively prove that the most significant driver for the adoption of SoCs was the emergence of the silicon infrastructure market. Only history will tell which forward-looking innovators will have made the most of this opportunity, and which will have been left behind in the dust of antiquated business models."

[Erach Desai, DESAIsive Technology Research IEEE Design & Test of Computer Systems Guest Editor's Introduction May-June2002]

## Chapter 1

## Infrastructures and Algorithms for Testable and Dependable SoC

Every new node of semiconductor technologies provides further miniaturization and higher performances, increasing the number of advanced functions that electronic products can offer. Silicon area is now so cheap that industries can integrate in a single chip usually referred to as System-on-Chip (SoC), all the components and functions that historically were placed on a hardware board. Although adding such advanced functionality can benefit users, the manufacturing process is becoming finer and denser, making chips more susceptible to defects. Today's very deep-submicron semiconductor technologies (0.13 micron and below) have reached susceptibility levels that put conventional semiconductor manufacturing at an impasse. Being able to rapidly develop, manufacture, test, diagnose and verify such complex new chips and products is crucial for the continued success of our economy at-large. This trend is expected to continue at least for the next ten years making possible the design and production of 100 million transistor chips [83] [86].

To speed up the research, the National Technology Roadmap for Semiconductors identified in 1997 a number of major hurdles to be overcome. Some of these hurdles are related to test and dependability [37].

Test is one of the most critical tasks in the semiconductor production process where Integrated Circuits (ICs) are tested several times starting from the wafer probing to the end of production test. Test is not only necessary to assure fault free devices but it also plays a key role in analyzing defects in the manufacturing process [84]. This last point has high relevance since increasing time-to-market pressure on semiconductor fabrication often forces foundries to start volume production on a given semiconductor technology node before reaching the defect densities, and hence yield levels, traditionally obtained at that stage. The feedback derived from test is the only way to analyze and isolate many of the defects in today's processes and to increase process's yield.

With the increasing need of high quality electronic products, at each new physical assembly level, such as board and system assembly, test is used for debugging, diagnosing and repairing the sub-assemblies in their new environment. Similarly, the increasing reliability, availability and serviceability requirements, lead the users of high-end products performing periodic tests in the field throughout the full life cycle. To allow advancements in each one of the above scaling trends, fundamental changes are expected to emerge in different Integrated Circuits (ICs) realization disciplines such as IC design, packaging and silicon process. These changes have a direct impact on test methods, tools and equipment. Conventional test equipment and methodologies will be inadequate to assure high quality levels. On chip specialized block dedicated to test, usually referred to as Infrastructure IP (*Intellectual Property*), need to be developed and included in the new complex designs to assure that new chips will be adequately tested, diagnosed, measured, debugged and even sometimes repaired [85].

In the following of this introduction, some of the scaling trends in designing new complex SoCs will be analyzed one at a time, observing their implications on test and identifying the key hurdles/challenges to be addressed. The goal of the remaining of the thesis is the presentation of possible solutions. It is not sufficient to address just one of the challenges; all must be met at the same time to fulfill the market requirements.

### 1.1 High Performance SoC Test Diagnosis and Failure Analysis

The design of high performance SoCs requires increased performances of test equipments. While semiconductor off-chips speeds have improved at 20% per year, tester speed has improved at rate of 12% per year. Tester timing errors are approaching the cycle time of the fastest devices. Furthermore the so called bandwidth-gap between external pin and internal parts of a complex SoC denies the possibility of testing at operating speed modern devices. It has been demonstrated that, most of the new types of defects can only be detected if the device is tested at operating speed. The solution today is the use of Built-In-Self-Test (BIST), which means the integration of test capability directly on-chip [1]. Many solutions have been proposed in literature but the complexity of new designs makes them difficult to implement. Usually, each component or function in a SoC is now available as a pre-designed functional block, or *embedded core*, whose internal structure is usually hidden to the core integrator. Moreover, cores may embed different test architectures, like Full-Scan [1], Partial-Scan [1], or BIST, and may be *reused* in different designs and integrated with other cores coming from different vendors. In addition, when a certain combination of cores is often used together, the system integrator or the core provider may decide to create a new core from that combination. Hence, today's SoCs may become tomorrow's cores in more complex SoCs. This new design philosophy based on a hierarchical reuse of cores, leads to a radical change in the test engineering process, requiring the adoption of IP test infrastructure able to fully support core reuse, hierarchical design, and multiple test strategies integration.

In addition, failure analysis and diagnosis in faulty chips is becoming a key problem. The traditional failure analysis comprises fault localization, silicon reprocessing and physical characterization and inspection steps. The migration towards smaller geometries severely challenges this analysis process. The only solution is gathering failure data by using embedded diagnosis infrastructure IP, such as signature analyzers, dedicated test vehicles or on-chip test processors, and then analyzing the obtained data by off-chip fault localization methodologies and tools.

### **1.2** Memory Dominance

There is a clear trend to integrate large quantities of memories on a chip. Memories are designed with aggressive design rules and tend to be more prone to manufacturing defects. Memories in complex SoC are deeply embedded in the circuits and are not easily accessible from the outside to apply test program. New IP Infrastructures to embed the test programs and to allow diagnosis and debug operation are required.

Furthermore the increasing scale of integration and the introduction of new manufacturing processes introduce new classes of defects not present in the previous technologies. To efficiently deal with them, designers need to automate the process of memory test program generation. This goal involves the realization of algorithms able to address the problem of: (i) describing new fault models (ii) generating tests able to cover these new fault models, (iii) verifying the effectiveness of the generated test programs.

Finally, embedded memories were traditionally testable but not reparable. Many applications today need to keep on working in case of fault. This is addressed in today's memories by introducing redundancy, i.e. spare elements. However, having redundancy only does not solve the problem, it is necessary to find optimal solutions to detect the defects and to allocate the redundant elements. This involves the realization of dedicate infrastructure IPs to realize Self-Repairable Memories.

## Part I

# High Performance SoCs Test, Diagnosis and Failure Analysis

### Related publications

Portions of the material described in this part of the thesis has been subject of following scientific publications: [6],[19], [18].

# Chapter 2 Introduction

As mentioned in chapter 1 the new SoC design philosophy based on a hierarchical reuse of already made cores, requires the adoption of IP test infrastructures able to fully support core reuse, hierarchical design, and multiple test strategies integration.

The problem of testing already-made components bought from different vendors is a well-known problem in the field of discrete components. Specifically, the test of boards is based on the direct access to the component's pins using bed-of-nails whose probes contact the pads and the wire of the board under test. In SoC design, direct accessibility to interconnections and cores' boundaries is not possible, but test patterns have still to be carried from their source, either a BIST-controller or an external Automatic Test Equipment (ATE) [1], to the core and vice versa. The problem has to be solved by designing an access-architecture, usually referred to as *Test Access Mechanism* (TAM), to activate the test functions, possibly delivering test patterns, and gathering the results of the test of any core in the overall SoC hierarchy. In general, a TAM has to guarantee three main properties:

- *Core accessibility*: the test of the core has to be controllable by a limited set of SoC boundary signals;

- *Reusability*: the access mechanism should be easily reconfigurable to allow the reuse of cores with different test architectures;

- Lowest overhead: area, routing, and performance overheads must be kept at a minimum.

To worsen the situation, test execution in general, and BIST in particular, typically result in a circuit activation-rate and power consumption higher than the one of the normal operation mode, thus limiting the possibility of testing concurrently all the cores embedded in a SoC. A SoC test strategy has therefore to be organized in several sessions, each carefully planned to fulfill the required power dissipation constraints.

It is now clear how the SoC integration task would be simpler if core designs were more test-friendly, and SoC designers would have more flexibility in choosing the best overall test methodologies for their chips. For this purpose, the IEEE P1500 standard for embedded-core test is under development. The P1500 standard strives to provide a "plugand-play" methodology of integrating core testability into a SoC. Its goal is to ensure testfriendliness and interoperability of cores coming from diverse sources. P1500 concentrates on a standardized, but configurable and scalable core interface or *wrapper* that allows easy *access* to the internal test methods of the core. The *Test Access Mechanism* (TAM), which has the task of managing the execution of the test of the overall chip, is out of the current scope of P1500 and therefore must still be designed by the test engineer.

This part of the thesis proposes a possible solution to this problem. An innovative TAM named *Hierarchical-Distributed-Data BIST* (HD<sup>2</sup>BIST), able to address several of the most critical issues in SoC testing, will be presented. HD<sup>2</sup>BIST allows a smooth integration and management of cores with different test strategies (e.g., Full Scan [1], Partial Scan [1], BIST-ready [1], or BISTed cores [1]) and built-in test access protocols, either user-defined or automatically inserted using commercial BIST and Design-for-Testability insertion tools. It is fully compatible with a hierarchical design methodology, allowing accessing any core of the system independently from its hierarchical depth.

Being already addressed by the IEEE P1500 task force,  $HD^2BIST$  does not focus on the problem of *core isolation*. Nevertheless, although  $HD^2BIST$  does not require the cores of the system to be P1500 compliant, it assumes at least a simple wrapper to be placed around each core in order to guarantee its *isolation* during the test execution. Obviously, in the scenario of a P1500 compliant design, a significant part of the  $HD^2BIST$  structures would be merged with the P1500 wrapper to optimize performances and minimize the area overhead.

To reduce the power consumption and therefore to overcome one of the main drawbacks of the BIST methodology in SoCs, the HD<sup>2</sup>BIST approach allows defining the test scheduling of the cores using sophisticated control flow mechanisms. A very low area overhead is guaranteed by the fact that the HD<sup>2</sup>BIST architecture is fully customizable and adaptable to the test requirements of the cores integrated in the system, and thus provides a trade-off capability among routing, area, and test length.

# Chapter 3 State-of-the-Art

As introduced in chapter 2 the two main issues to be targeted in SoC testing are *core isolation* and *core accessibility*. [87] gives an overview on the current solutions to create testable and diagnosable embedded core-based SoCs, and presents a generic conceptual architecture consisting of three structural elements. It introduces the basic concepts of test pattern *source*, test pattern *sink*, and the *test access mechanism* (TAM).

Several TAM architectures have been proposed in literature. *Macro Test* in [56] separates tests into protocols and test patterns. It introduces a dedicated test access mechanism but also takes advantage of existing on chip functionalities. [39] and [38] use the functional transparent mode of the cores to propagate the test data through the system. The approach requires low-test area but quite high-test application time since the test data need to be propagated trough the cores. In [47] the core under test is directly and parallel accessed from the IC pins, inserting additional wires connected to the core terminal and *multiplexed* into the existing IC pins. As a main drawback, the approach is not scalable and introduces high area costs and long test time. [75] and [76] access the core under test from the IC pins using multiple *test buses* of different width shared by multiple cores. Each test bus allows testing one single core at the time. In [41] a new architecture template has been proposed for system level connection based on switching networks.

Alternative solutions reuse the approaches developed for board level interconnects testing, through the JTAG IEEE 1149.1 Boundary Scan Architecture [61]. Some aspects however limit the effectiveness of the approach: the Boundary Scan is optimized for testing interconnections between components in a board and it does not allow at-speed testing. In [65] the authors present a variation of the IEEE 1149.1 standard based on a partial boundary scan ring around the core, whereas in [77] they suggest to provide each core of an addressable Test Access Port (TAP) in order to directly address the core to be tested, and to introduce a special hierarchical TAP to manage group of cores as a single one. To test interconnections among cores, the method proposed in [24] requires the insertion of test collar cells on the virtual core input and output pins, to create different connections between the cells and the system data bus. In [55], the cores are wrapped by an ad-hoc interface (*TestShell*), and connected by a proper test bus (*TestRail*), that delivers the test data patterns and control signals.

To allow flexibility in test scheduling, [5] and [42] proposed a centralized controller

to activate the BIST sessions one at a time, whereas [81] suggests distributing the test management on different *BIST Resource Controllers* (*BRCs*).

The area overhead reduction was addressed in [62]: a local test controller is associated to each core, and a dedicated bus inserted to connect the controllers, deliver data patterns, and link the controllers to the Unit Under Tests (UUT). More UUTs can share the same controller, properly configuring the local test controller. A modular, generic and re-configurable TAM architecture has been proposed in [58], based on a packet switching communication network. Finally, the concept of hierarchical distribution of the test management is introduced in [22][21] and [23] with the *Hierarchical* and *Distributed BIST* architecture, able to manage different hierarchical levels of BISTed blocks.

Concurrently with the development of proper testing architectures, some initiatives started to standardize the cores embedding process. The Virtual Socket Interface Alliance (VSIA) and the P1500 IEEE Standard Working Group are the most relevant ones. The VSI Alliance intends to define, develop, ratify, test and promote open specifications relating to data formats, test methodologies and interfaces, to help the reuse of intellectual property blocks from different sources in the design and development of SoCs [67]. The P1500 IEEE Standard Working Group aims at defining a uniform but flexible hardware interface between an embedded core and its environment, capable of delivering predefined test patterns to and from the embedded cores [2][82][49].

Despite the novelty of the approaches, none of the proposed solutions efficiently fulfills all the test requirement of new generation SoCs.

## Chapter 4

## Architecture Overview

This chapter presents the general architecture of the  $HD^2BIST$  test access mechanism. For the sake of clarity,  $HD^2BIST$  is here introduced as a flat architecture, but the reader should keep in mind that it is a hierarchical structure, fully adaptable to the hierarchical architecture of complex SoCs.

The main actor in the HD<sup>2</sup>BIST is a bus-based communication link, named *Test BUS* (*TBUS*), which implements an effective solution to the problem of *core access* and *reuse*. From a conceptual point of view, the data exchanged on the TBUS can be clustered into two categories:

- Control Data, used to configure and control the HD<sup>2</sup>BIST test structures.

- *Test Data*, used to carry the test vectors needed to test the cores embedded into the system. Test vectors can be generated on-chip by BIST controllers, or be applied from the outside to the SoC Input/Output signals using Automatic Test Equipments (ATE).

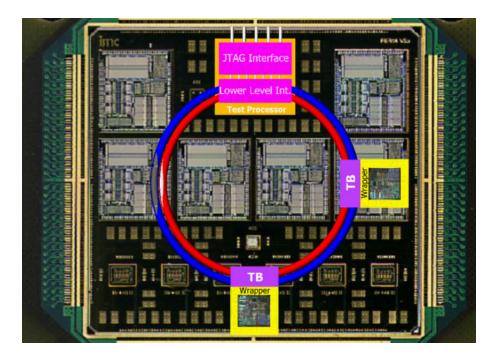

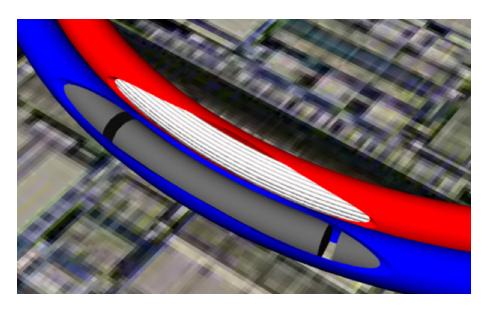

To reflect this logical classification, the TBUS is split into two sub-buses named *Test* Control Bus (TCB) and Test Data Bus (TDB), respectively. Both test busses have a ring structure (Figure 4.1), to guarantee a simple and technology independent approach, and to offer a high degree of flexibility and dependability.

The difference of information exchanged on the two busses imposes the use of different *Communication Protocols*. The amount of information exchanged over the TCB is usually very low and it can be easily coded as a predefined set of commands, thereinafter referred to as *Test Primitives*. A *Token Based Protocol* has been chosen as the most effective solution for the TCB. On the contrary, data exchanged on the TDB is mainly composed of a large amount of test patterns and test responses. This characteristic makes a *Scan Chain Based Protocol* [1] the most suitable solution for data transmitted on the TDB (Figure 4.2).

As detailed later, the scan chain approach allows a very flexible *sharing mechanism* of the TDB to concurrently test different cores, or to reuse the same lines of the TDB to test different cores in different times, thus minimizing the routing overhead.

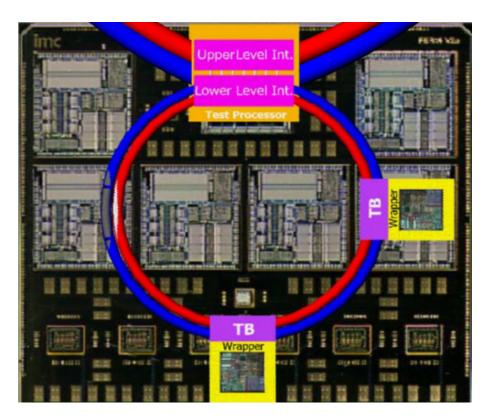

Figure 4.1. HD<sup>2</sup>BIST Ring

The TBUS structure implemented by  $HD^2BIST$  provides a high degree of reliability. Thanks to the Scan Chain protocol, the TDB itself can be easily tested using a standard scan test approach [1]. The dependability of the TCB is guaranteed by implementing it as a bi-directional link. The same information transmitted on a *forward link* is then sent back on a *backward link* to verify its correctness. In case of a transmission error, a diagnosis procedure can be executed to locate the fault.

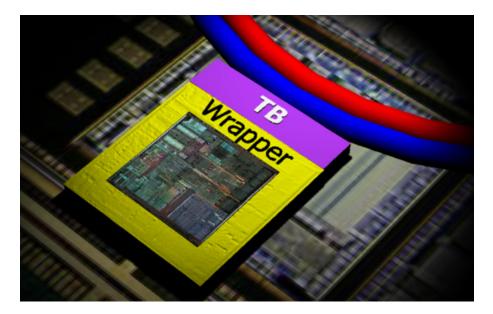

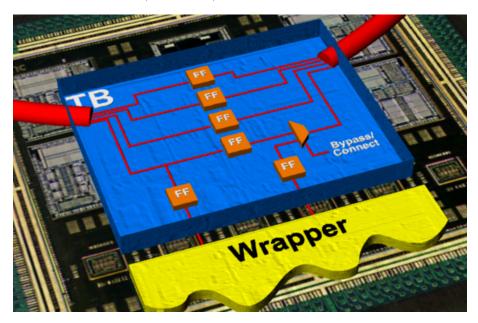

The TBUS proves to be an efficient TAM only if an appropriate *bus interface* with the cores under test and a *bus manager* are properly defined and implemented. In the HD<sup>2</sup>BIST these rules are played by two special blocks named *Test Block* (TB) and *Test Processor* (TP), respectively. Each TB/TP connected to the TBUS is identified by a unique address defined at design time.

The Test Block (Figure 4.3) can be easily customized to support the specific test solution implemented in the core. In particular, its internal structure is optimized for (1) *full and partial scan cores* [1], using the TDB to apply test vectors and to gathered test results, (2) *BISTed cores* [1], using the TCB to send BIST commands and to read BIST results, and (3) *BIST-ready cores* [1], using the TDB to exchange test vectors between the core under test and its BIST controller.

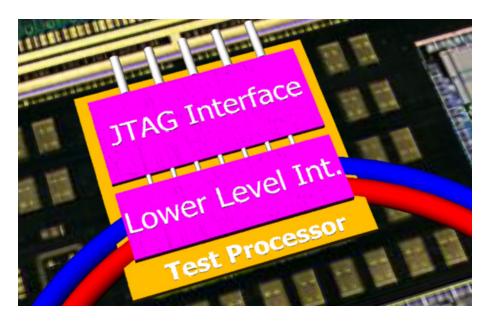

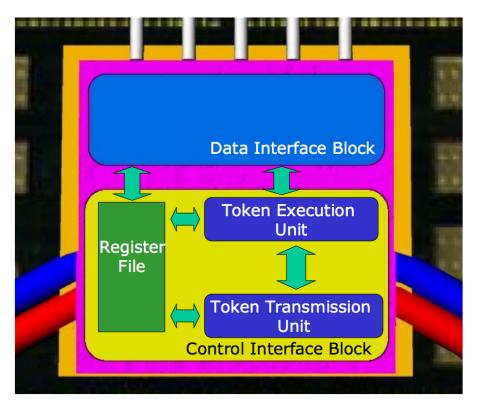

The Test Processor controls, through the TBUS, the HD<sup>2</sup>BIST structures inserted in the chip, and schedules the execution of the test of each core in the chip itself. It is interfaced to the TBUS through a *Lower Level Interface* (Figure 4.4) implemented either as a Finite State Machine (FSM) or as a micro-programmed machine, and able to execute a sequence of *Test Primitives* implementing a set of *Test Programs* defined by the core 4 – Architecture Overview

Figure 4.2. TCB (token bus) and TDB (scan bus)

Figure 4.3. Test Block and core wrapper

integrator. Each test primitive corresponds to one (or more) token(s) exchanged over the TCB, and it can be either generated by the TP itself, or applied from the outside of the SoC through a *IEEE 1149.1 JTAG* interface [61]. The JTAG defines a standard Test Access Port (TAP) for board components. The use of a JTAG interface allows having a standardized protocol to access the TP and the HD<sup>2</sup>BIST structure in general and to control the execution of the Test Programs from an external ATE.

Figure 4.4. Test Processor architecture

As explained in the Section 1, the design of a complex SoC usually follows a hierarchical approach. To be compatible with this design philosophy, HD<sup>2</sup>BIST allows connecting different TBUS to achieve a hierarchical structure. The element that allows the connection of different busses is the TP. In this case, instead of being controlled by a JTAG interface, the TP is interfaced to the second TBUS through a TB-like interface named *Upper Level Interface* (Figure 4.5). Each TP manages the test of the cores connected to its TBUS, only. The Upper Level Interface allows viewing each TP as a complex TB and therefore managing it as a single Unit Under Test: a TP placed at the i<sup>th</sup> level<sup>1</sup> will be considered by the TP of level (i-1)<sup>th</sup> as a standard TB, and therefore dealt with as any other core under test. Nevertheless, its task is to translate the test primitives coming from the (i-1)<sup>th</sup> level in the execution of the appropriate Test Program for the blocks belonging to its TBUS. Using this approach, TPs support a distributed approach in the execution of the system test. The general idea is that each TP is able to resolve the commands coming from the upper bus in all the operations needed on the lower bus (Figure 4.5).

As mentioned before each TB and TP is identified by a unique address defined at design time. To extend this concept when the SoC is reused as an embedded core in a more complex system, each TBUS is considered as a distinct address domain. In this way, two cores belonging to different TBUS can share the same address without any conflict. Using this approach, when a SoC is reused as an embedded core, the only part that has to be modified is the Upper Level Interface of the most external TP, which, in the case of a stand-alone SoC, is a JTAG interface, whereas in the case of a SoC used as a core it is

<sup>&</sup>lt;sup>1</sup>i=0 is associated to the highest level, i.e. the chip level.

#### 4 – Architecture Overview

Figure 4.5. Connecting two rings

a TB-like interface connecting the TP to the upper level TBUS.

## Chapter 5

# HD<sup>2</sup>BIST hierarchy configuration and scheduling

The hardware architecture described in chapter 4 can be easily configured in different operative modes to create a connection in the SoC hierarchy between a core and its test patterns source/sink, to test or to perform diagnosis on faulty components and to accurately schedule the test execution of the overall SoC.

Both the Test Structure Configuration and the Test Scheduling are possible thanks to a set of Test Primitives implementing Test Programs. This mechanism defines a software level that, to some extent, allows separating the task of designing the  $HD^2BIST$  hardware from the task of programming and configuring it.

A Test Programs is a set of Test Primitives issued as tokens to the blocks (TBs and TPs) connected to the TCB. Conceptually, there are *atomic* and *macro* primitives. There is no semantic difference between them, but the result of their execution depends on the target block. *Atomic primitives* are commands received by a TB and used to configure the wrapper of a core or to change the status of some signals at the core boundaries; *macro primitives* are sent to those TPs that connect different hierarchical levels in the TBUS tree. In this case, the execution of the test primitive results in the activation of another test program used to manage the test of the lower hierarchical levels.

Using this software level, it is therefore possible to describe the test of a SoC as a collection of Test Programs. The order in which the test programs are executed does not necessarily have to be chosen at design time. In fact, HD<sup>2</sup>BIST provides two ways of delivering a Test Primitive to the blocks under test. In *external mode*, the test instructions are sent from the outside of the system through the top-level TP, possibly using an ATE connected to the TP JTAG interface. In *internal mode*, the tokens are generated on-chip by each TP and the JTAG interface is used only to select the desired test program. The two modes are not mutually exclusive and can be integrated to add flexibility to the overall test strategy. In particular, the internal mode is mostly used to activate BIST procedures and to read their results. The external mode is instead exploited to create a direct data path form the outside to the core under test to perform diagnosis or to apply test patterns using an external ATE.

In order to exploit the external mode, the SETENV and UNSETENV macro primitives

are used to configure the TCB and TDB lines to directly access, from the outside, any core of the system, regardless its hierarchical depth. SETENV is sent to the TP blocks to create a *bypass connection* between two adjacent hierarchical levels. After a SETENV primitive, all the test instructions sent to level i<sup>th</sup> are directly forwarded to the (i+1)<sup>th</sup> level. Resorting to a sequence of SETENV primitives it is therefore possible to reach, from the outside, any level of the hierarchy. This operation is usually referred to as *Environment Setup*. The UNSETENV primitive is used to restore the normal functionality of the TBUS.

In general, each Test Program requires a different *configuration* of the HD<sup>2</sup>BIST. In this context, a configuration is defined as a connection scheme between the cores under test and the TDB lines used to transmit test vectors; each connection scheme is referred to as *Configuration Mode*. The set of Configuration Modes is fully customizable by the test engineer, the only constraints being that each TB has to implement at least a *Bypass Mode*, where each TDB line is not used and all the data coming into a TB is forwarded to the next block on the bus (Figure 5.1).

Figure 5.1. TDB connections

From the user point of view, the configuration mode can be set using the Test Primitive *CONF*. The possibility of setting different Configuration Modes allows sharing the TDB lines between different blocks in a single test session ("*Width*" sharing) or reusing the same data line to test different cores in different test sessions ("*Time*" sharing) thus obtaining the maximum efficiency from the available test resources.

The last issue solved by the bus-based approach is the Test Scheduling problem. Despite some scheduling mechanisms are already addressed solving the Test Structure Configuration problem where the "Width" and "Time" sharing are intrinsic scheduling facilities, four Test Primitives have been defined to manage the test session of BISTed and BISTready blocks. The definition of a scheduling algorithm for BISTed and BIST-ready cores can be translated into an appropriate sequence of configurations, activations and collections of test results of the BIST routines. The following test primitives can efficiently code these commands:

- *START*: starts the execution of a BIST routine;

- COLLECT: collects the results of a BIST routine.

The two primitives are useful to define simple sequential tests, but do not allow complex scheduling algorithms where decisions should be taken depending on some test results. To overcome this problem two additional test primitives have been defined:

- *WAIT*: suspends the execution of a Test Program until the BIST procedure or the execution of the Test Program of one or more blocks is completed. This instruction allows the test engineer to address possible power consumption issues raised by the concurrent test of multiple blocks in the system.

- *JUMP*: depending on the result of the BIST (or Test Program) of one or more blocks, the Test Program execution jumps to a certain label. This command improves the flexibility in the test scheduling, allowing the test engineer to take decisions on-the-fly as, for example, to skip testing additional parts of an already revealed faulty component.

## Chapter 6

## **RT-level Implementation**

After introducing the main features of the HD<sup>2</sup>BIST architecture, this paragraph details how the test structures actually may appear at the RT level. The proposed implementation can be seen as a sort of guideline for the test engineer, who can obviously customize it to his target application, implementing the needed features, only.

### 6.1 Test Block Architecture

As explained in chapter 4, the TBUS is split in two busses: the TCB and TDB. Consequently, each TB includes a *Control Interface Block* and a *Data Interface Block* (Figure 6.1).

The Control Interface Block is in charge of managing the information coming from the TCB. Inside a Control Interface Block it is possible to identify a *Token Transmission Unit*, which sends and receives tokens on the TCB using the transmission protocol described in the sequel of this paragraph, and a *Token Execution Unit*. The execution of a token is implemented as one or more read/write operations on a register file. The primitives presented in chapter 5 are translated into elementary register operations.

The register file is organized in three different sections:

- 1. *Test Control Registers:* each bit of a Test Control Register is used to directly drive one of the control pins of the core like a start BIST signal;

- 2. *Test Status Registers:* each bit of a Test Status Register is connected to a core output and is used to read the core status during the test;

- 3. Test Mode Registers: they are usually used to set up configuration modes (see chapter 5). The content of the Test Mode Registers therefore codes the connection schema between the TDB lines and the core pins.

The number of registers and their size are customizable by the user depending on the target application.

The Data Interface Block is in charge of correctly routing the information transmitted on the TDB. Inside a Data Interface Block, each TDB line can assume two different states:

- 1. *Bypass*: the data received on the line is directly forwarded to the next block of the TBUS;

- 1. *Connect*: the data received on the line is forwarded to a core input and on the same line a core output is forwarded to the next block.

Each Configuration Mode corresponds to a different TDB routing configuration. The state of each line is obtained by properly decoding the contents of one of the Test Mode Registers.

Figure 6.1. Test Block General Architecture

### 6.2 Test Processor Architecture

The main role of the TP is to execute Test Programs, each implemented as a sequence of tokens. Tokens and Test Patterns are sent on the TBUS through the Lower Level Interface (see chapter 4) using the same Control and Data Interface Blocks described in section 6.1. Each TP can be implemented as either an FSM statically executing the test programs, or a  $\mu$ -programmed machine executing the test programs stored in a local memory.

The interface changes accordingly to the hierarchical level the TP belongs to. In particular we can distinguish between the top level and all the other hierarchical levels. At the top level, the TP is interfaced to the SoC boundaries through an IEEE 1149.1 compliant Test Access Port (TAP), which makes possible to access all the SoC test structures via an external ATE using a standard protocol. In all the other cases, when the TP is used to connect two different hierarchical levels, the interface to the upper TBUS is implemented as in a normal TB, and a Routing Unit is used to directly connect the lines of the two TDBs (if this is required by any of the Configuration Modes). The Test Control, Data, and Configuration Registers are used to configure, control and read the test results form the Lower Level Interface.

### 6.3 IEEE 1149.1 interface

Providing the HD<sup>2</sup>BIST with a JTAG IEEE 1149.1 Test Access Port (TAP) interface is necessary to control the top level TP using a standard protocol and to simplify the use of an external ATE to test full or partial scan cores. Mainly and IEEE 1149.1 compliant TAP defines two signal named TDI and TDO used to access in a serial way a set of user defined JTAG registers.

As mentioned in chapter 5, from the external user point of view, an HD<sup>2</sup>BIST SoC can be used in two different functional modes:

- Internal Mode: tokens and test data in general are generated on-chip. The IEEE 1149.1 interface is only used to start the execution of the Test Programs and to read out the test results. The test program can be selected by loading an appropriate value in a JTAG register. At the end of the test, the results are loaded into a JTAG Register in the form of a status word that can be scanned out through the TDO pin.

- *External Mode*: in this configuration mode the TCB is controlled using the TDI and TDO signals. The tokens to be transmitted on the TCB are loaded into a JTAG Register. In this situation the TDB is controlled using a set of dedicated input lines usually referred to as scan-in and scan-out pins. Directly controlling the TBUS, the Top Level TP is conceptually substituted by the external ATE. This configuration mode is particularly useful for diagnosis and debugging phases.

The two functional modes are not mutually exclusive. They can be combined together to improve flexibility.

### 6.4 Scan Chain Router

When the number of data lines needed to test a core is not compatible with the number of lines of the TDB, a *Scan Chain Router* can be placed between each TB and the corresponding core. This block is able to merge a set of core lines into a single one, thus reducing the number of TDB lines needed during the test. This block is particularly useful to test full-scan cores [1]. Introducing a Scan Chain Router, the test engineer can trade off between the routing, area overhead (number of TDB lines) and test time (long scan chain). The Scan Chain Router configuration can be set using a dedicated Test Mode Register. The same approach can be adopted inside a TP connecting two hierarchical levels with different TDB width.

#### 6.5 Test Control Bus

While the data is transmitted on the TDB using a simple scan protocol, tokens exchanged on the TCB require a more complex transmission protocol.

The Token Transmission Protocol is designed to make the transmission more tolerant to hardware faults. The protocol is based on the implementation of the TCB as a bidirectional link named *Forward Bus* and *Backward Bus*, respectively. The Forward Bus is used to actually transmit the token, whereas the Backward Bus is used to send the received data back to the sender in order to check its correctness and detect a wide range of transmission errors. In case of inconsistency, the block enters an *Error State* and blocks all future transmission. Using an appropriate diagnostic routine, the TP connected to the faulty bus can locate the fault, save this information into an appropriate Test Status Register, and make it accessible from the upper level of the hierarchy. In addition, an optional CRC can be inserted in each token to improve the token transmission reliability. On both the forward and the backward bus, tokens are transmitted in a serial way using a start/stop bit protocol. Each sender can transmit only one token at a time and, after the transmission, it has to wait for the token to come back before removing it form the bus and sending a new one.

#### 6.6 Token Format

The  $HD^2BIST$  does not define a fixed token format, the only requirement being the implementation of a set of token fields needed to support the  $HD^2BIST$  basic functionalities. The required fields are listed below:

- *OP\_CODE* (Operative Code): it specifies the operation to be performed. The number of possible operations is customizable. At least a Read and a Write operation must be defined.

- *DEST\_ADDR* (Destination Address): it specifies the address of the destination block. It can specify also a broadcast or a group address.

- SOURCE\_ADDR (Source Address): it specifies the address of the sender.

- *REG\_ADDR* (Register Address): it identifies the register addressed by the op-code (see Section 5.1).

- *MASK*: It is a bit mask. In the case of a WRITE operation, it specifies the value to be written in the register; for a READ operation it carries the result of the read operation. The length of this field depends on the maximum size of the registers present in the TBs.

• *CRC* (Circular Redundancy Code): It is an additional optional field for inserting a CRC code (often a simple parity code) to improve the token transmission reliability.

# Chapter 7 Using HD<sup>2</sup>BIST in SoC Testing

The HD<sup>2</sup>BIST architecture allows testing SoCs, which integrate IP cores characterized by different test strategies. For each IP the HD<sup>2</sup>BIST architecture has to provide a way to transport test patterns to the core, and test responses from the core itself to the pattern sink. The solution offered by HD<sup>2</sup>BIST relies on the configuration features of the TBUS. As explained before, the *SETENV* test primitive allows configuring the TDB lines in order to create a direct path between any pair of blocks connected to a TBUS, even not necessarily belonging to the same hierarchical level. The path configuration is executed using the token-based protocol of the TCB.

In general, testing a complex SoC usually requires facing four different test scenarios: BISTed or BIST-Ready cores, Scan-cores, and glue logic. The following sections explain how each of them can be addressed using the HD<sup>2</sup>BIST architecture.

#### 7.1 Testing BISTed and BIST-Ready Cores

The situation of a BISTed core, i.e., a core embedding all the logic needed to execute its test and provide the test results can be addressed using the TCB only. The TP configures the core wrapper to isolate the core under test, and write the proper values in the TB registers to directly control the test pins of the core able to activate the BIST procedure.

In the simple case of a system embedding BISTed cores only, the HD<sup>2</sup>BIST may be limited to a TCB, a TP and a TB for each core. Nevertheless, at the end of the test session, BISTed cores often release not only a Boolean result, but in case of failure they allow downloading a set of diagnosis data. In this case the TDB can be used to route this information outside the SoC.

In a different way, a BIST-Ready core is not entirely self-testable; it requires an external BIST Controller to generate and apply the test patterns and to verify the correctness of the core responses. Typical examples of BIST-Ready cores are RAM memories, whose BIST logic is usually implemented in a separate BIST Controller executing a March test [69]. In this scenario, HD<sup>2</sup>BIST has to enable a direct path from the BIST Controller outputs to the memory inputs and from the memory outputs to the BIST Controller inputs (Figure 7.1-a). This task is achieved by defining a Test Program able to configure

a direct connection over the TDB between the BIST Controller and the core I/Os. At this point, the test can be executed at-speed without any modification in the test protocol, the only test time overhead being the initial and final latency due to the bypass TBs on the path.

When the SoC integrates more than one copy of the same core, it is possible to exploit the HD<sup>2</sup>BIST to reuse the same BIST controller to test all the identical cores. With two different Test Programs it is possible to configure the connection between the BIST Controller and, one after the other, the different instances of the core.

#### 7.2 Testing Scan Cores

Full scan cores need test patterns applied from external test equipment. They represent the most difficult situation, especially when they are deeply inserted in the hierarchy of the SoC. This is the scenario in which the hierarchical structure of the HD<sup>2</sup>BIST is efficient to create a direct connection between the SoC boundaries and the cores I/O (Figure 7.1-b). The Top Level TP is set in External Mode and acts as a TDB line router, allowing the connection between TDB lines belonging to different hierarchical levels. After a configuration phase, it is possible to test the core applying the patterns directly from the SoC boundaries.

The original test patterns for the core do not need to be significantly modified, and the only test time overhead introduced is caused by the latency required to traverse the HD<sup>2</sup>BIST hierarchy.

Figure 7.1. Using of TDB to test different types of cores

#### 7.3 Testing glue logic

It is not unusual that the chip integrator adds glue logic around the cores embedded in the system. This logic is usually not localized and cannot be wrapped or considered as a core. Glue logic is usually tested using a full-scan approach. If it is possible to split the glue logic into different domains, each referring to a certain TBUS hierarchical level, the glue logic scan chains can be directly connected to a TP and considered as pseudo TDB lines. In this way it is possible to test the glue logic with the same approach used to test full-scan cores (Figure 7.2).

Figure 7.2. Pseudo TDB lines for testing the glue logic

## Chapter 8

### Case study

To demonstrate the effectiveness of the proposed TAM, the  $HD^2BIST$  architecture has been implemented on an industrial case study. The example has been chosen to underline the flexibility of the proposed approach in terms of *reusability* of the test structures in a hierarchical architecture, *test patterns delivering* for full-scan cores, *scheduling* of BIST-ready blocks, and *integration* of the HD<sup>2</sup>BIST architecture with BIST structures automatically generated using commercial tools.

The following sections analyze the case study, providing experimental results in terms of area and test time overhead.

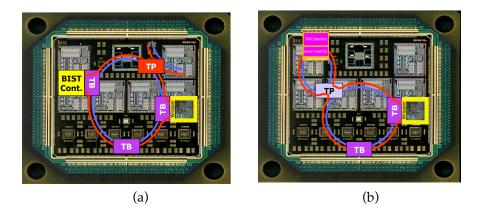

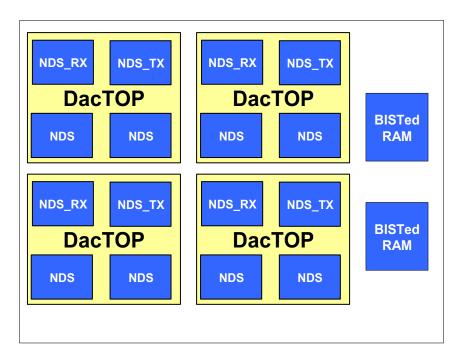

#### 8.1 DacTOPplus Architecture

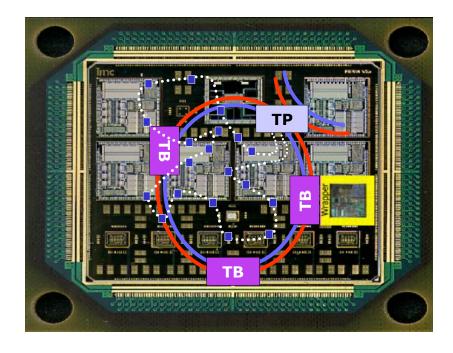

The case study, named DacTOPplus, is a LSI Logic<sup>®</sup> circuit used in transmission devices. DacTOPplus is composed of four identical macro-cores (DacTOP) and two BISTed RAMs (8192x8) (Figure 8.1).

Each DacTOP macro is composed of four sub-modules: one transmission macro-cell NDS\_TX, one receiving macro-cell NDS\_RX and two identical NDS macro-cells.

The NDS\_RX, NDS\_TX macro-cells are full-scan modules with seven scan chains, whereas the two NDS modules have been considered as glue-logic, and all their flip-flops are connected through a single scan chain. The circuit is realized using the G11 LSI Logic<sup>®</sup> library. Table 8.1 reports the area occupied by the test case in Synopsys<sup>®</sup> Equivalent Gates [69].

In the sequel, we will focus first on the test structure implemented in the DacTOP macros, and then on the complete test case, including the four DacTOP macros as well as the two BISTed memory modules.

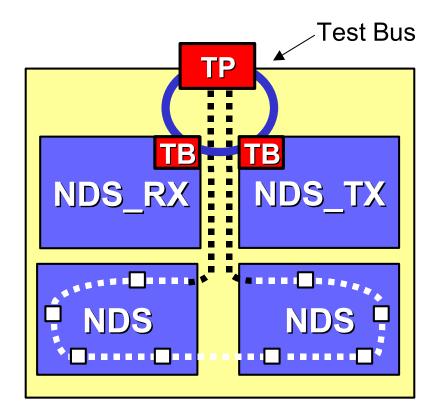

#### 8.2 DacTOP Test Structure

The test structure implemented in each DacTOP macro is composed of a single HD<sup>2</sup>BIST chain controlled by a TP. The NDS\_TX and the NDS\_RX macros, packaged by a P1500-like wrapper, are controlled by two TBs, whereas the NDS modules are treated as glue

| CORE       | Equivalent Gates |

|------------|------------------|

| NDS        | 99,801           |

| NDS_RX     | 102,688          |

| NDS_TX     | 102,802          |

| DacTOP     | $430,\!356$      |

| BISTed RAM | 163,694          |

| DacTOPplus | 2,048,814        |

Table 8.1. DacTOPplus dimensions in Synopsys<sup>®</sup> equivalent gates

Figure 8.1. DacTOPplus schema

logic, and therefore directly controlled (or tested) by the TP. The  $HD^2BIST$  structure inserted in each DacTOP macro is therefore composed of (Figure 8.2):

- One Test Bus split into:

- One Test Control Bus 1-bit wide.

- One Test Data Bus. Since each module has 7 scan chains and the TDB has to transmit the Scan Enable and the Reset signals, the TDB should be composed of nine lines.

- Two *Test Blocks (TBs)*. Each *Test Block* is able to implement three connection modes:

- Bypass mode, where the TDB is in bypass mode;

- *Connect mode*, where the TDB is connected to the scan chains and the scan patterns can be delivered to the module;

- Glue mode, where the core wrapper is set to isolate the core and used trough the TDB to apply test patterns to the glue logic placed at the core boundary.

- One *Test Processor (TP)* implementing three test programs PROG[1-3], used to connect the NDS\_RX, NDS\_TX, and the two NDS macros respectively, to the *Test Data Bus*. Each program sets a different target block in Connect mode and the others in Bypass mode. The Test Processor implements three connection modes:

- Bypass mode where the upper TDB controlled by the TP is in bypass mode (see chapter 5);

- Connect mode where the upper level TDB is connected with the lower one;

- *Glue* mode, where the TP creates a direct path from the outside to the scan chain connecting the glue logic;

Figure 8.2. DacTOP HD<sup>2</sup>BIST schema

Tables 8.2 and 8.3 report the area obtained synthesizing the DacTOP test case and the HD<sup>2</sup>BIST architecture using the G11 LSI Logic<sup>®</sup> library.

Table 8.2. DacTOP area with wrapped modules

| CORE                 | Equivalent Gates |

|----------------------|------------------|

| Glue Logic           | 199,602          |

| Wrapped NDS_RX       | 112,049          |

| Wrapped NDS_TX       | $110,\!976$      |

| DacTOP with wrappers | 447,891          |

Table 8.3. HD<sup>2</sup>BISTed DacTOP area occupation

| CORE                          | Equivalent Gates |

|-------------------------------|------------------|

| TB of NDS_RX                  | 3,695            |

| TB of NDS_TX                  | 3,701            |

| TP                            | $6,\!145$        |

| HD <sup>2</sup> BISTed DacTOP | 461,434          |

The area overhead of the HD<sup>2</sup>BIST structure w.r.t. the original DacTOP area is the 7.03%, whereas the overhead w.r.t. the DacTOP area including the wrappers is 2.97%. We included the wrapped version of the DacTOPplus since we consider the wrappers a test requirement independent from the HD<sup>2</sup>BIST structure.

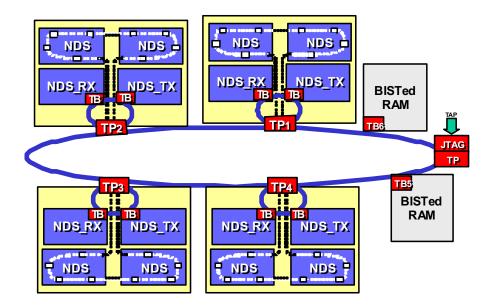

#### 8.3 DacTOPplus Test Structure

The test structure inserted in the DacTOPplus test case is composed of one  $HD^2BIST$  chain at the top level, and one  $HD^2BIST$  chain for each DacTOP module. No modifications are necessary to reuse the test architecture implemented in each DacTOP macro at the top-level. The top level chain is built of the following blocks (Figure 8.3):

- One *Test Bus* split into:

- One Test Control Bus one line wide;

- One Test Data Bus 9 lines wide (each DacTOP module needs nine lines, whereas the BISTed RAMs do not need any data line);

- One *Test Block* for each RAM;

- Four *Test Processors*, one for each DacTOP macro, as described in the previous section;

- One *Top Level Test Processor* with a IEEE 1149.1 interface. In the Test Processor we implemented 13 different test programs, which can be executed in any desired order:

- PROG[1]: it starts the BIST of the two RAMs, waits for the BIST to end, and reads the test results;

- PROG[2-4]: they start respectively PROG[1-3] of the first DacTOP and they wait for their end. They then connect the Scan In of the TAP interface with the first DacTOP in order to scan out the test results;

- PROG[5-7]: the same as PROG[2-4] but with the second DacTOP module;

- PROG[8-10]: the same as PROG[2-4] but with the third DacTOP module;

- PROG[11-13]: the same as PROG[2-4] but with the fourth DacTOP module;

Figure 8.3. DacTOPplus with HD<sup>2</sup>BIST

Table 8.4 reports the area obtained synthesizing the DacTOP plus using the G11 LSI  $\mathrm{Logic}^{\circledast}$  library.

The area overhead of the  $HD^2BIST$  structure w.r.t. the original DacTOPplus area is 6.61%, whereas the overhead w.r.t. the DacTOPplus area including the wrappers is 3.06%.

#### 8.3.1 Running a test program

To show how it is possible to actually exploit the HD<sup>2</sup>BIST architecture to run the system test, we detail three different test programs that target the BISTed RAMs, one DacTOP

| CORE                              | Equivalent Gates |

|-----------------------------------|------------------|

| HD <sup>2</sup> BISTed DacTOP     | 461,434          |

| TB of RAM                         | 2,956            |

| TP_TAP                            | 5,958            |

| HD <sup>2</sup> BISTed DacTOPplus | $2,\!184,\!997$  |

Table 8.4.

Area result of DacTOPplus

NDS\_RX module, and the glue logic. Each program can be run loading the corresponding code into a dedicated JTAG register.

Figure 8.4 presents PROG[1] of the top-level DacTOP, which activates the test of the two BISTed RAMs. The program activates the BIST procedures of the two BISTed RAMs and then starts polling the two Test Blocks waiting for the end of the test. Test programs allows a very flexible implementation of any test scheduling: PROG[1] executes the BIST of the two memories in parallel, but, by simply exchanging instruction #3 and #4, it is possible to test the two memories sequentially.

Program PROG[1]

| <b>Conf</b> ALL, BYPASS /* Configure all the TP/TB in BYPASS       |

|--------------------------------------------------------------------|

| mode since the TDB is not used during BIST                         |

| phase */                                                           |

| <b>Start</b> TB5 /* Start the first RAM BIST by sending a          |

| start primitive to TB1*/                                           |

| <b>Start</b> TB6 /* Start the second RAM BIST */                   |

| <b>Wait</b> ALL $/*$ Wait for the end of all the BIST.             |

| This primitive is Implemented using a                              |

| polling mechanism */                                               |

| <b>Collect</b> ALL $/*$ Read the BIST results contained in the RAM |

| TBs and store them in The Top Level TP.                            |

| In case of fault the faulty Block can                              |

| be located using the external mode to                              |

| have Direct access to the TBs and BIST                             |

| controllers. */                                                    |

| }                                                                  |

Figure 8.4. Test program PROG[1] of the Top Level TP

The second example is PROG[2] of the top-level TP (Figure 8.5), which creates a path on the TDB to directly connect the top-level TP to the NDS\_RX module of the first DacTOP. After properly configuring the top-level chain, the TDB of the first DacTOP module is connected to the top-level TDB to allow the top-level TP to start the execution of PROG[1] in the first DacTOP (Figure 8.6). PROG[1] of the DacTOP macro, creates a path from the scan chains of NDS\_RX to the Test Data Bus lines. As soon as PROG[1] is completed a path has been set from the top-level to the addressed block in the hierarchy, and the test patterns can be applied using the scan signals.

Program PROG[2]

{

Conf ALL,BYPASS /\* Configure all the TB/TP in BYPASS mode \*/

Conf TP1,Connect /\* The TP of the first DacTOP macro is set

in Connect mode, to connect its TDBus to

the top level TDB \*/

Start TP1,PROG[1]/\* Start the execution of PROG[1] of TP1 \*/

Wait TP1 /\* Wait for the end of PROG[1] of TP1.

From this moment the NDS\_RX block of the

first DactTop is accessible from the top

level.\*/

}

Figure 8.5. Test program PROG[2] of the TLTP

Program PROG[2]

{

Conf ALL,BYPASS /\* Configure all the TB/TP in BYPASS mode \*/

Conf TB1\_1,Connect /\* The first TB of the chain is set in

Connect mode, to connect the scan chains of

NDS\_RX to the TDB \*/

}

Figure 8.6. Test program PROG[1] of the DacTOP macro

In the last example we detail PROG[4] of the top-level TP (Figure 8.7), which enable the test of the first DacTOP glue logic (the two NDS macros) and interconnections. After configuring the top-level chain, the TP of the first DacTOP macro is configured to directly control the scan-chain connecting the glue-logic of the module. Moreover, PROG[3] of the DacTOP macro (Figure 8.8) is executed to set all the wrappers of the macro in ExtTest mode, so that the values scanned in their scan chains can be applied to the input of he glue logic.

**Program** PROG[4] { Conf ALL, BYPASS /\* Configure all the TB/TP in BYPASS mode \*/ Conf TP1,glue /\* TP1 is set in Glue mode, i.e., it is configured to directly control the glue logic scan chain. In particular, the first two lines of the top-level TDB are connected to the Scan In/Scan Out signals of the glue logic chain, and the third line is connected to the first line of the lower Test Data Bus to create a scan path through the wrappers, necessary to apply test patterns to the glue logic boundaries \*/ Start TP1,PROG[3]/\* Start the execution of PROG[3] of TP1 \*/ Wait TP1 /\* Wait for the end of PROG[3] of TP1. From this moment the patterns to test glue logic can be applied.\*/ }

Figure 8.7. Test program PROG[4] of the Top Level TP

Program PROG[3]

{

Conf ALL,Glue /\* Configure all the TB in glue mode

allowing to apply test patterns trough

the core wrappers\*/

}

Figure 8.8. Test program PROG[3] of the DacTOP macro

# Chapter 9 Conclusions

In this part of the thesis the problem of test and diagnosis of complex SoC designed using embedded cores has been addressed. The proposed solution HD<sup>2</sup>BIST, is a complete hierarchical framework to support the definition of the scheduling strategies and data patterns delivering mechanisms of the embedded cores of a complex system. The main goal of the HD<sup>2</sup>BIST architecture is to maximize and simplify the reuse of the built-in test architectures giving the chip designer the highest flexibility in planning the overall SoC test strategy. HD<sup>2</sup>BIST defines a TAM able to provide a direct "virtual" access to each core of the system, and can be conceptually considered on a higher level w.r.t. the P1500 standard, whose main target is to make the test interface of each core independent from the vendor. A complex case study has been presented to demonstrate the effectiveness of the approach in terms of complexity and area overhead.

# Part II Memory Dominance

### Related publications

Portions of the material described in this part of the thesis has been subject of following scientific publications: [14],[27],[7],[10], [9], [20], [13].

# Chapter 10 Introduction

SRAMs are nowadays widely used as embedded memories in a plenty of SoCs. As an example, Mlti-port SRAMs are basic elements of telecommunications or multiprocessor systems. They allow to speed-up the system, in particular when the memory has to serve many concurrent requests. Today's technologies allow the design and manufacturing of memory chips up to 11 ports, and Multi-port RAM generators are commonly available in many vendor libraries as LSI-Logic, Texas Instruments and ST Microelectronics.

Memory-BIST is today a pressing issue. The test engineer has to define test strategies for complex SoCs including several multi-port SRAMs of different size (number of bits, number of words), access protocol (asynchronous, synchronous), and timing. Apart from the required design time, there are several issues to be solved, including minimizing BIST area and routing overhead, selecting the proper number of BIST controllers, fulfilling power budget constraints, supporting diagnostic capabilities and defining the best test algorithm with respect to the target technology and application. Among the different types of algorithms proposed to test random access memories (RAM), March Tests have proven to be faster, simpler, regularly structured and linear in complexity [69]. March Tests are able to cover a wide range of memory faults, but due to the technology advance, new types of faults arise and should be tested. Different March Tests of variable complexity have been proposed in literature, each optimally covering a different set of memory faults. All of them have been manually generated, a task that requires a lot of time, expertise, that does not always allow to obtain an optimal solution, and that sometimes does not succeed in covering particularly complex memory faults. An automatic approach to generate test algorithms to be used in memory-BIST architectures is a pressing issue in complex SoC design and test. These new algorithms have to be always validated. Memory fault simulation is therefore necessary to compute the Fault Coverage of a test sequence every time a new defect is discovered and the corresponding fault model defined. Computing and limiting the test application power consumption is also another important issue, especially when the memory test is implemented as a BIST procedure.

An emerging trend in memory design is to have not only testable memory but also repairable memories. The emerging field of Self-Repair Computing is expected to have a major impact on deployable systems for space missions and defense applications, where high reliability, availability, and serviceability are needed; but also on new commercial applications were high level of availability is a must.

In the following of this chapter, each of the proposed issues will be analyzed and a set of solutions will be presented.

### Chapter 11

## An introduction to memory Test

This chapter introduces the basic concepts and background on memory testing. It is a short overview to help the reader understanding the following chapters.

#### 11.1 The fault model

Memories are usually tested using a functional approach. The functional model of a simple SRAM is made of the following units: (i) the memory cell array, (ii) the address decoder and (iii) the read/write logic. Memory faults can be classified depending on their location.

#### 11.1.1 Memory Cell Faults

Memory cell faults can be split in two categories: *single cell faults* and *multiple cell faults*. Single cell faults are restricted to a single cell of the memory array and are classified as follow:

- *Stuck-at faults (SAF)*: the logic value of a cell is always fixed to a certain value. It can be a stuck-at zero (SAF-0) if the fixed value is '0' or stuck-at one (SAF-1) if the fixed value is '1';

- Transition faults (TF): a cell fails to perform a transition from '0' to '1' or vice versa.

In multiple cell faults the logic value of one or more cells is influenced by the logic value of one or more others cells. The former is called the coupled cell(s) whereas the latter is called the coupling cell(s). Coupling faults occur due to capacitive linkage of storage cells. It should be noted that these faults are not bi-directional. Some of the commonly occurring coupling faults are:

- *Idempotent coupling faults (CFid)*: they occur when a transition in one cell forces the logic value of the coupled cell to a fixed value;

- Inversion coupling fault (CFin): a transition in the coupling cell inverts the logic value of the coupled cell.

#### 11.1.2 Address decoder fault

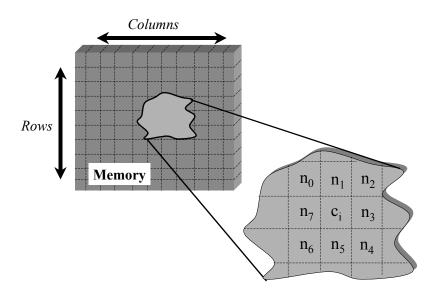

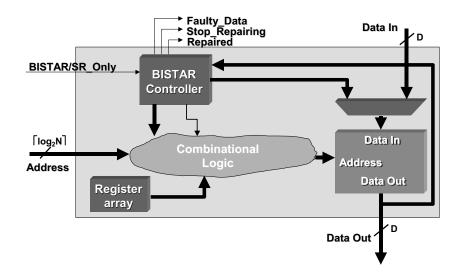

Faults in the decoder circuitry of a memory chip manifest as follows: