## POLITECNICO DI TORINO Repository ISTITUZIONALE

Enhancing Real-time Embedded Image Processing Robustness on Reconfigurable Devices for Critical Applications

Enhancing Real-time Embedded Image Processing Robustness on Reconfigurable Devices for Critical Applications /

This version is available at: 11583/2641174 since: 2016-04-30T20:58:59Z

| Publisher: Politecnico di Torino                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| Published DOI:10.6092/polito/porto/2641174                                                                                              |

| Terms of use: Altro tipo di accesso                                                                                                     |

| This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository |

|                                                                                                                                         |

| Publisher copyright                                                                                                                     |

|                                                                                                                                         |

|                                                                                                                                         |

(Article begins on next page)

Original

Availability:

Trotta, Pascal. - (2016).

### POLITECNICO DI TORINO

#### SCUOLA INTERPOLITECNICA DI DOTTORATO

Doctoral Program in Computer and Control Engineering

Final Dissertation

# Enhancing Real-time Embedded Image Processing Robustness on Reconfigurable Devices for Critical Applications

Pascal TROTTA

Tutor prof. Paolo PRINETTO

Co-ordinator of the Research Doctorate Course prof. Matteo SONZA REORDA

#### **ACKNOWLEDGEMENTS**

his thesis represents the result of three years of work. Throughout this period I had the opportunity to interact with many people that gave me suggestions and encouraged me.

First of all, it is a great pleasure to thank my advisor Prof. Paolo Prinetto, from Politecnico di Torino, that guided me during these three years (and more) with his always precious hints and guidelines. His suggestions led me to grow both from the technical and, most important, personal point of views. I also wish to thank Prof. Stefano Di Carlo, from Politecnico di Torino, that helped me with his valuable experience.

The work that has been carried out during the last three years relied on the collaboration with industrial partners. In particular, I would like to thank Ing. Andrea Martelli, Ing. Antonio Tramutola, and Ing. Piergiorgio Lanza from Thales Alenia Space Italy for our fruitful meetings and their very helpful guidelines. Moreover, during the PhD period I had the opportunity to spend one year in Sweden, working in Cobham Gaisler AB. It is a pleasure to thank the whole Cobham Gaisler team, and in particular Jan Andersson for his immense patience in tutoring me during the entire visiting period, in which I had the opportunity to greatly improve my technical knowledge.

Also, I would like to thank all my colleagues that have worked, or are still working, with me in the laboratory of the Control and Computer Engineering Department at Politecnico di Torino. They made this research period much more enjoyable. In particular, many thanks go to Giulio and Daniele (or Daniele and Giulio) for the great working and non-working time spent together.

Last, but not least, I would like to thank my family that supported and tolerated me during these years.

# **CONTENTS**

| Lis | st of F | igures                                                                                                              | vi        |

|-----|---------|---------------------------------------------------------------------------------------------------------------------|-----------|

| Li  | st of T | ables                                                                                                               | x         |

| 1   | Intr    | oduction                                                                                                            | 1         |

|     | 1.1     | Thesis Organization                                                                                                 | 3         |

| 2   | Digi    | al Image Processing for Mission-critical Applications                                                               | 7         |

|     | 2.1     | History of Digital Image Processing                                                                                 | 9         |

|     | 2.2     | $\label{thm:processing} Image\ Processing\ in\ mission-critical\ applications \ \ldots \ldots \ldots \ldots \ldots$ | 10        |

|     | 2.3     | Imaging sensors and related issues                                                                                  | 17        |

|     |         | 2.3.1 Mathematical model                                                                                            | 22        |

| 3   | Reco    | nfigurable Devices for Mission-critical Applications: architectures and issues                                      | 25        |

|     | 3.1     | History and Evolution of Programmable Logic Devices: from Programmable Logic                                        |           |

|     |         | Arrays to modern FPGAs                                                                                              | 29        |

|     | 3.2     | Field Programmable Gate Arrays architectures                                                                        | 33        |

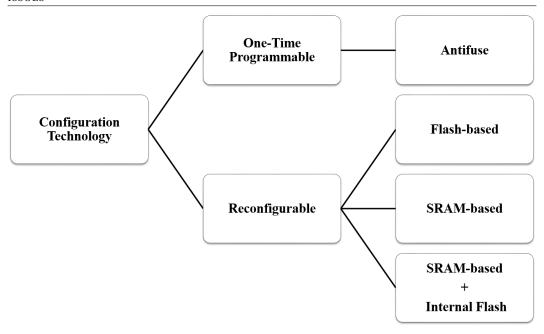

|     |         | 3.2.1 One-time programmable FPGAs                                                                                   | 34        |

|     |         | 3.2.2 Reconfigurable FPGAs                                                                                          | 36        |

|     |         | 3.2.2.1 Flash-based FPGAs                                                                                           | 36        |

|     |         | 3.2.2.2 SRAM-based FPGAs                                                                                            | 37        |

|     | 3.3     | FPGAs for mission-critical applications                                                                             | 41        |

|     | 3.4     | Dynamic Partial Reconfiguration                                                                                     | 45        |

|     |         | $3.4.1  \text{Configuration Details and Bitstream Composition}  \dots \dots \dots \dots$                            | 48        |

|     | 3.5     | Dependability issues in modern reconfigurable FPGAs $\ \ldots \ \ldots \ \ldots \ \ldots$                           | 50        |

|     |         | 3.5.1 Dependability issues in dynamically reconfigurable systems                                                    | 54        |

| 4   | Buil    | ling Robust Hardware Accelerators and systems for real-time embedded image                                          |           |

|     | proc    | essing on reconfigurable FPGAs                                                                                      | <b>59</b> |

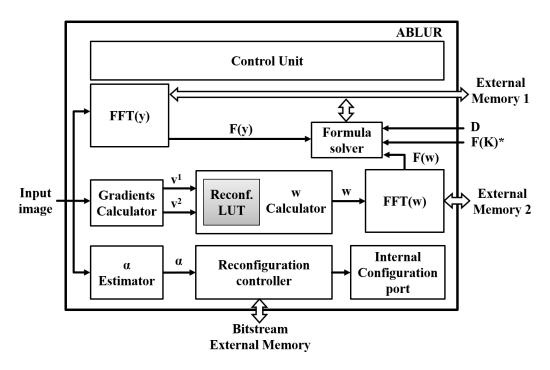

|     | 4.1     | ABLUR: an FPGA-based adaptive deblurring core for real-time applications                                            | 60        |

|     |         | 4.1.1 Deblurring Algorithms Overview                                                                                | 61        |

|     |         | 4.1.2 <i>ABLUR</i> Architecture                                                                                     | 62        |

|     |         | 4.1.2.1 Input Image Fast Fourier Transform module (FFT(y)) $\dots \dots$                                            | 64        |

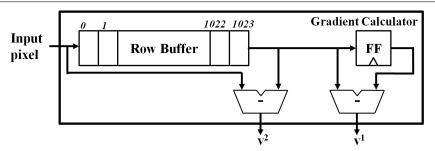

|     |         | 4.1.2.2 Gradient calculator                                                                                         | 65        |

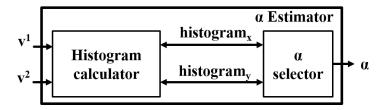

|   |      |              | 4.1.2.3                                                                     | $\alpha$ estimator                                                                                                                                                                                                                                                                    | 66                                            |

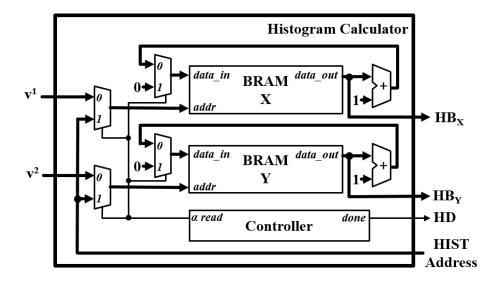

|---|------|--------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|   |      |              | 4.1.2.4                                                                     | Reconfiguration Manager                                                                                                                                                                                                                                                               | 68                                            |

|   |      |              | 4.1.2.5                                                                     | w calculator                                                                                                                                                                                                                                                                          | 68                                            |

|   |      |              | 4.1.2.6                                                                     | w Fast Fourier Transform module (FFT( $w$ ))                                                                                                                                                                                                                                          | 69                                            |

|   |      |              | 4.1.2.7                                                                     | Formula Solver                                                                                                                                                                                                                                                                        | 70                                            |

|   |      |              | 4.1.2.8                                                                     | Control Unit                                                                                                                                                                                                                                                                          | 70                                            |

|   |      | 4.1.3        | Experim                                                                     | nental results                                                                                                                                                                                                                                                                        | 70                                            |

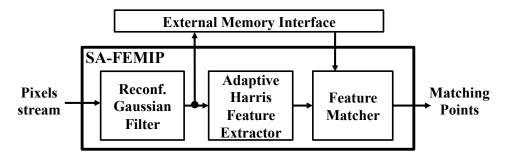

|   | 4.2  | SA-FE        | MIP: a Sel                                                                  | f-Adaptive Features Extractor and Matcher IP-core based on Par-                                                                                                                                                                                                                       |                                               |

|   |      | tially I     | Reconfigui                                                                  | rable FPGAs for Space Applications                                                                                                                                                                                                                                                    | 76                                            |

|   |      | 4.2.1        | Related                                                                     | Works                                                                                                                                                                                                                                                                                 | 76                                            |

|   |      | 4.2.2        | SA-FEM                                                                      | IP Architecture                                                                                                                                                                                                                                                                       | 77                                            |

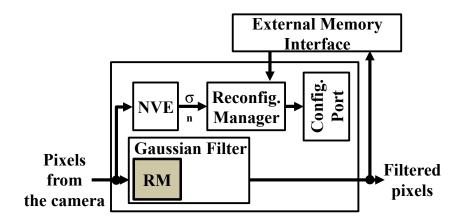

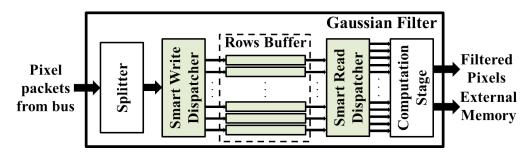

|   |      |              | 4.2.2.1                                                                     | Reconfigurable Gaussian Filter                                                                                                                                                                                                                                                        | 78                                            |

|   |      |              | 4.2.2.2                                                                     | Adaptive Harris Feature Extractor                                                                                                                                                                                                                                                     | 84                                            |

|   |      |              | 4.2.2.3                                                                     | Features Matcher                                                                                                                                                                                                                                                                      | 89                                            |

|   |      |              | 4.2.2.4                                                                     | SA-FEMIP timing diagram                                                                                                                                                                                                                                                               | 92                                            |

|   |      |              | 4.2.2.5                                                                     | Experimental Results                                                                                                                                                                                                                                                                  | 93                                            |

| 5 | On I | Enhanc       | ing Depen                                                                   | ndability of Dynamic Partial Reconfiguration                                                                                                                                                                                                                                          | 101                                           |

|   | 5.1  | Deper        | ndability is                                                                | ssues in Dynamic Partial Reconfiguration (DPR)                                                                                                                                                                                                                                        | 101                                           |

|   | 5.2  | Deper        | ndable DP                                                                   | R with minimal area and time overheads                                                                                                                                                                                                                                                | 102                                           |

|   |      | 5.2.1        | Propose                                                                     | d Methodology and Design Rules                                                                                                                                                                                                                                                        | 104                                           |

|   |      |              | 5.2.1.1                                                                     | Partial bitstream file splitting                                                                                                                                                                                                                                                      | 105                                           |

|   |      |              | 5.2.1.2                                                                     | Critical links protection                                                                                                                                                                                                                                                             | 107                                           |

|   |      |              | 5.2.1.3                                                                     | Critical modules protection                                                                                                                                                                                                                                                           | 108                                           |

|   |      | 5.2.2        | Experim                                                                     | ental results                                                                                                                                                                                                                                                                         | 108                                           |

|   |      |              |                                                                             | Defense a colution in along autotion                                                                                                                                                                                                                                                  | 109                                           |

|   |      |              | 5.2.2.1                                                                     | Reference solution implementation                                                                                                                                                                                                                                                     | 100                                           |

|   |      |              | 5.2.2.1<br>5.2.2.2                                                          | Proposed approach implementation                                                                                                                                                                                                                                                      |                                               |

|   |      |              |                                                                             | -                                                                                                                                                                                                                                                                                     | 109                                           |

|   | 5.3  | A port       | 5.2.2.2<br>5.2.2.3                                                          | Proposed approach implementation                                                                                                                                                                                                                                                      | 109<br>109                                    |

|   | 5.3  | A port 5.3.1 | 5.2.2.2<br>5.2.2.3<br>able open                                             | Proposed approach implementation                                                                                                                                                                                                                                                      | 109<br>109<br>113                             |

|   | 5.3  | -            | 5.2.2.2<br>5.2.2.3<br>able open<br>Related                                  | Proposed approach implementation                                                                                                                                                                                                                                                      | 109<br>109<br>113<br>114                      |

|   | 5.3  | 5.3.1        | 5.2.2.2<br>5.2.2.3<br>able open<br>Related                                  | Proposed approach implementation                                                                                                                                                                                                                                                      | 109<br>109<br>113<br>114<br>115               |

|   | 5.3  | 5.3.1        | 5.2.2.2<br>5.2.2.3<br>able open<br>Related                                  | Proposed approach implementation                                                                                                                                                                                                                                                      | 109<br>109<br>113<br>114<br>115               |

|   | 5.3  | 5.3.1        | 5.2.2.2<br>5.2.2.3<br>able open<br>Related<br>Propose<br>5.3.2.1            | Proposed approach implementation                                                                                                                                                                                                                                                      | 109<br>113<br>114<br>115<br>115               |

|   | 5.3  | 5.3.1        | 5.2.2.2<br>5.2.2.3<br>able open<br>Related<br>Propose<br>5.3.2.1<br>5.3.2.2 | Proposed approach implementation       1         Comparison       1         -source controller for safe Dynamic Partial Reconfiguration       1         Works       1         d architecture       1         Synchronous/Asynchronous DPR       1         Dependable DPR $(D^2 PR)$ 1 | 109<br>109<br>113<br>114<br>115<br>115<br>119 |

| 6  | Evaluating system's robustness through error injection 1 |         |                                              |       |

|----|----------------------------------------------------------|---------|----------------------------------------------|-------|

|    | 6.1                                                      | Relate  | d Works                                      | . 130 |

|    | 6.2                                                      | Propo   | sed Methodology and Infrastructure           | . 132 |

|    |                                                          | 6.2.1   | Fault Generator                              | . 133 |

|    |                                                          | 6.2.2   | System Input Controller                      | . 137 |

|    |                                                          | 6.2.3   | System Clock Controller                      | . 137 |

|    |                                                          | 6.2.4   | System Output Collector and Fault Classifier | . 137 |

|    | 6.3                                                      | Experi  | imental Results                              | . 138 |

| A  | List                                                     | of syml | pols and acronyms                            | 145   |

| Bi | bliog                                                    | raphy   |                                              | 149   |

# LIST OF FIGURES

| 2.1  | Representation of a generic image processing flow                                     | 8  |

|------|---------------------------------------------------------------------------------------|----|

| 2.2  | Digital image processing pyramid [14]                                                 | 9  |

| 2.3  | First image of the Moon taken by <i>Ranger 7</i> [158]                                | 10 |

| 2.4  | Examples of vehicle camera-based systems tasks [222]                                  | 11 |

| 2.5  | Block diagram of an automotive Advanced Driver Assistance Systems (ADAS) system       |    |

|      | [222]                                                                                 | 11 |

| 2.6  | Curiosity rover                                                                       | 12 |

| 2.7  | Picture of the <i>Curiosity</i> 's heatshield taken by <i>MARDI</i> [164]             | 13 |

| 2.8  | Representation of the <i>Curiosity</i> 's landing ellipse on the Martian surface[201] | 14 |

| 2.9  | Representation of the <i>Curiosity</i> 's EDL [159]                                   | 15 |

| 2.10 | Representation of the <i>Curiosity</i> 's EDL [122]                                   | 15 |

| 2.11 | DIMES descent scenario [109]                                                          | 16 |

| 2.12 | Charge-Coupled Device (CCD) imaging sensor high level block diagram [130]             | 17 |

| 2.13 | CMOS imaging sensor high level block diagram [130]                                    | 18 |

| 2.14 | CMOS passive pixel sensor [80]                                                        | 18 |

| 2.15 | CMOS active pixel sensor [80]                                                         | 19 |

| 2.16 | Example of an image affected by noise                                                 | 20 |

| 2.17 | Example of the blur effect                                                            | 20 |

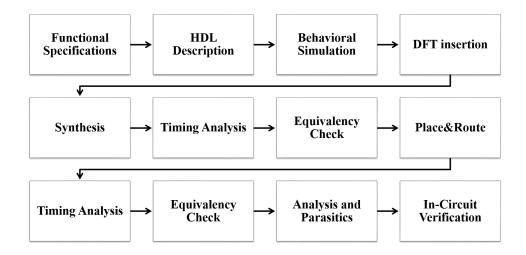

| 3.1  | Simplified FPGA design flow                                                           | 26 |

| 3.2  | Simplified ASIC design flow                                                           | 27 |

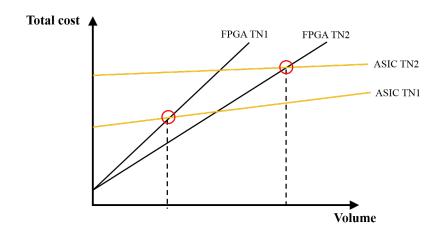

| 3.3  | FPGAs versus ASICs project cost analysis                                              | 28 |

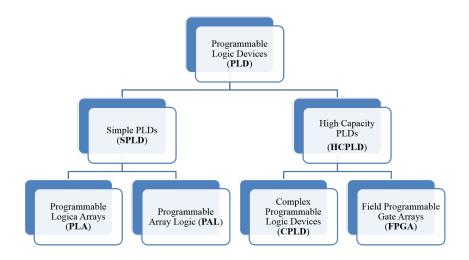

| 3.4  | Programmable Logic Devices taxonomy                                                   | 29 |

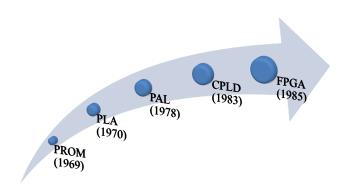

| 3.5  | Programmable Logic Devices history roadmap                                            | 30 |

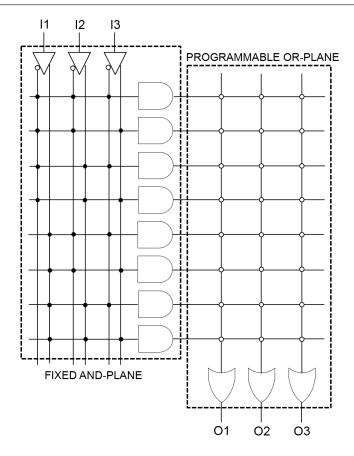

| 3.6  | Programmable Read Only Memory (PROM) internal architecture                            | 31 |

| 3.7  | CPLD internal architecture [220]                                                      | 31 |

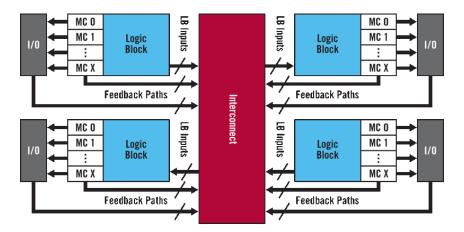

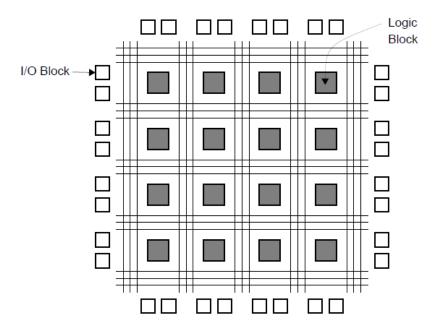

| 3.8  | FPGA internal architecture [30]                                                       | 32 |

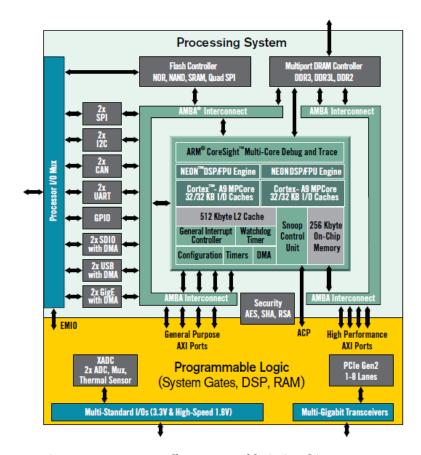

| 3.9  | Zynq-7000 All Programmable SoC architecture [245]                                     | 33 |

| 3.10 | Field Programmable Gate Arrays (FPGAs) taxonomy                                       | 34 |

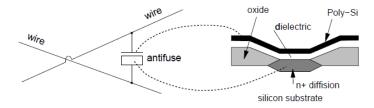

| 3.11 | Antifuse example [30]                                                                 | 34 |

| 3.12 | <i>Microsemi RTAX-DSP</i> device architecture [148]                                   | 35 |

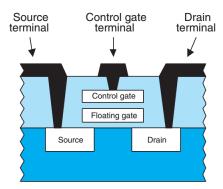

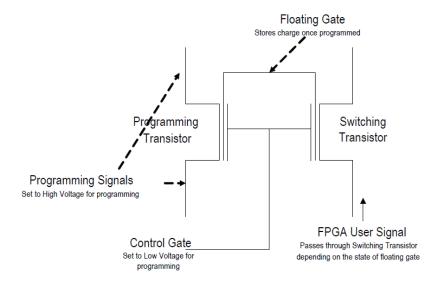

| 3.13 | Floating Gate transistor [139]                                                        | 36 |

| 3.14 | FLASH-based FPGAs programming technology [119]                                        | 37 |

| 3.15 | Microsemi RTG4 device architecture [149]                                                               | 38 |

|------|--------------------------------------------------------------------------------------------------------|----|

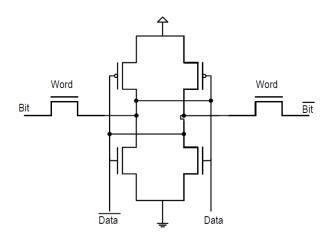

| 3.16 | Static Random Access Memory (SRAM) memory cell [119]                                                   | 38 |

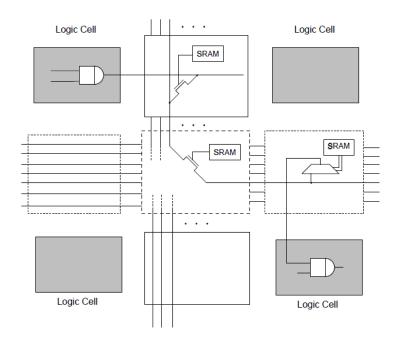

| 3.17 | SRAM-based FPGAs programming technology [30]                                                           | 39 |

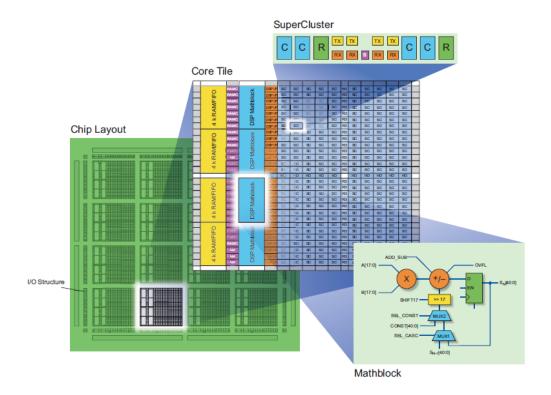

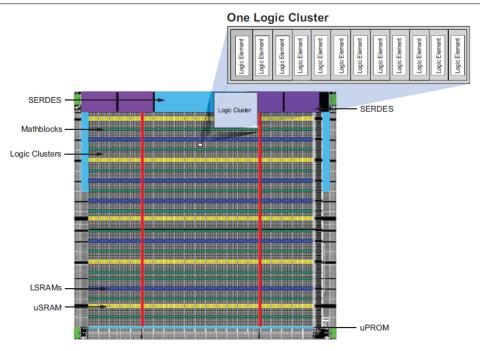

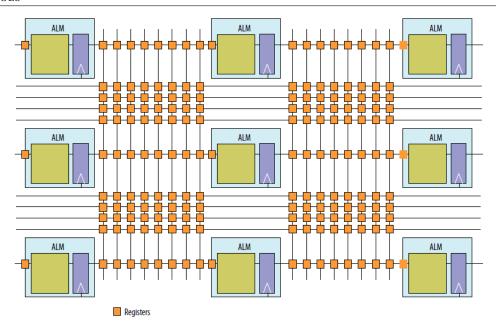

| 3.18 | Core Logic Fabric for <i>Altera Stratix 10</i> devices [9]                                             | 40 |

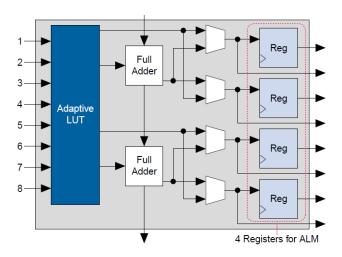

| 3.19 | Altera Stratix 10 FPGA ALM Block Diagram [9]                                                           | 40 |

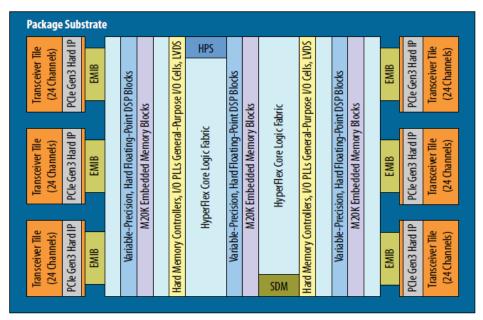

| 3.20 | Altera Stratix 10 FPGA Architecture Block Diagram [9]                                                  | 41 |

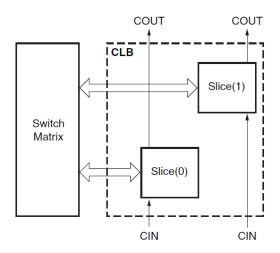

|      | <i>Xilinx</i> FPGAs Configurable Logic Block (CLB) architecture[242]                                   |    |

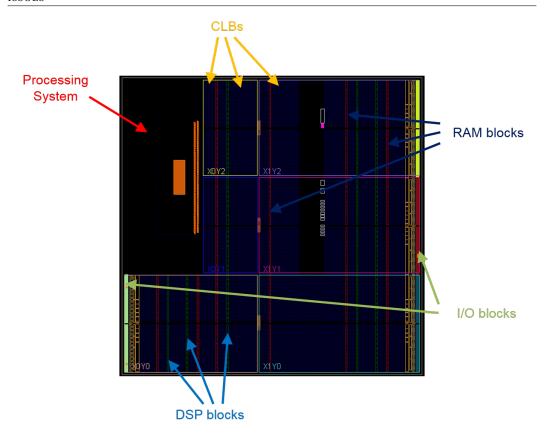

| 3.22 | Layout of a Xilinx Zynq-7000 FPGA                                                                      | 42 |

| 3.23 | Space missions employing <i>Microsemi RTSX-SU</i> FPGAs [144]                                          | 43 |

| 3.24 | Space missions employing <i>Microsemi RTAX</i> FPGAs [144]                                             | 43 |

| 3.25 | Space missions employing <i>Microsemi RTAX</i> FPGAs [144]                                             | 44 |

| 3.26 | Past and planned Space missions employing <i>Microsemi RTAX</i> FPGAs [144]                            | 44 |

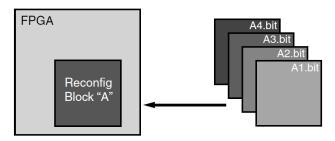

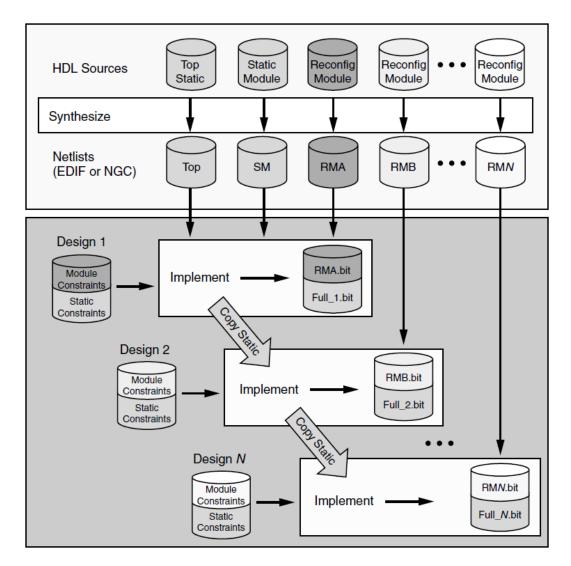

| 3.27 | Partial Reconfiguration concept [239]                                                                  | 46 |

| 3.28 | Partial Reconfiguration Design Flow [239]                                                              | 47 |

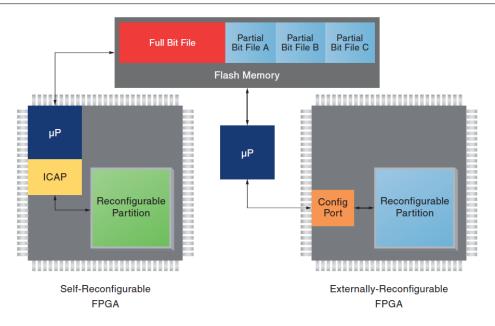

| 3.29 | Methods for delivering partial bitfiles [230]                                                          | 48 |

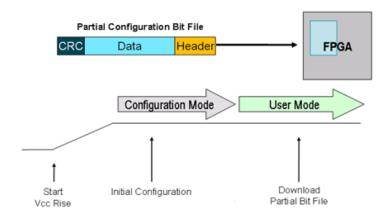

| 3.30 | Partial Bitstream composition and loading process [241]                                                | 49 |

| 3.31 | Chain of dependability threats                                                                         | 50 |

| 3.32 | Effect of a ionizing particle on a MOS transistor [110]                                                | 51 |

| 3.33 | Single-Event Effects classification [252]                                                              | 52 |

| 3.34 | Example of the effect of a Single Event Upset (SEU) on the configuration of a pro-                     |    |

|      | grammable routing matrix [37]                                                                          | 55 |

| 4.1  | ABLUR block diagram                                                                                    |    |

| 4.2  | Gradient calculator architecture                                                                       |    |

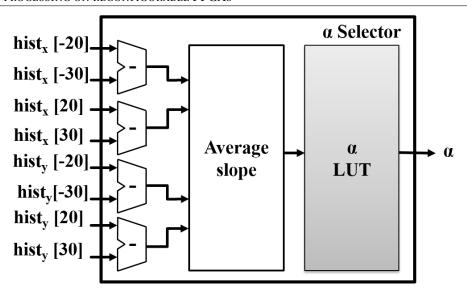

| 4.3  | lpha estimator architecture                                                                            |    |

| 4.4  | Histogram calculator architecture                                                                      |    |

| 4.5  | $lpha$ selector internal architecture $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$ | 68 |

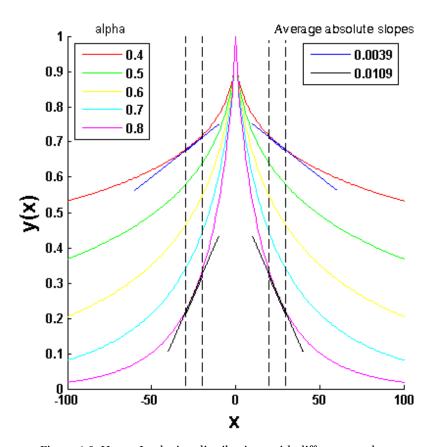

| 4.6  | Hyper-Laplacian distributions with different $lpha$ values                                             | 69 |

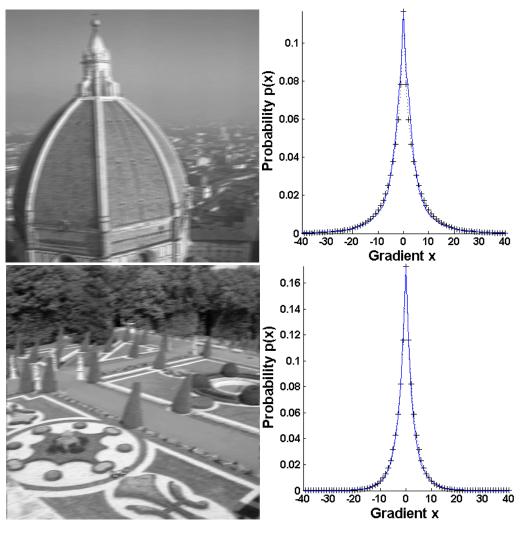

| 4.7  | Real-world scene images affected by blur and their gradients distribution, together                    |    |

|      | with the Hyper-Laplacian that better fits them (represented with black crosses) $\ \ \ldots \ \ .$     | 72 |

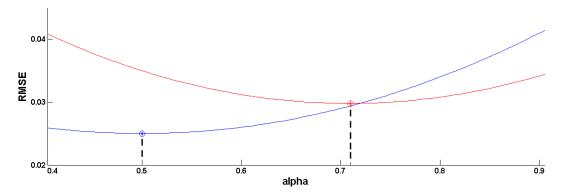

| 4.8  | RMSE of the recovered latent images w.r.t. the original ones, varying the input $\alpha$ value,        |    |

|      | for the two examples in Figure 4.7 (the minimum RMSE is highlighted with a circled                     |    |

|      | star)                                                                                                  | 73 |

| 4.9  | Example from Figure 4.7 deblurred by <i>ABLUR</i> (RMSE=0.044) and by software imple-                  |    |

|      | mented double precision version of the same algorithm (RMSE=0.039)                                     | 74 |

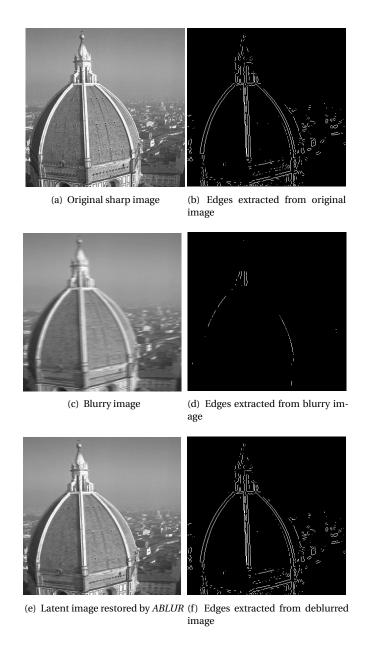

| 4.10 | Example from Figure 4.7 deblurred by <i>ABLUR</i> and edges extracted from blurry and                  |    |

|      | Example from Figure 4.7 debiurred by AbLOR and edges extracted from blurry and                         |    |

|      | deblurred image                                                                                        | 75 |

| 4.12 | Reconfigurable Gaussian Filter hardware architecture                                     | 79 |

|------|------------------------------------------------------------------------------------------|----|

| 4.13 | Gaussian Filter internal architecture                                                    | 79 |

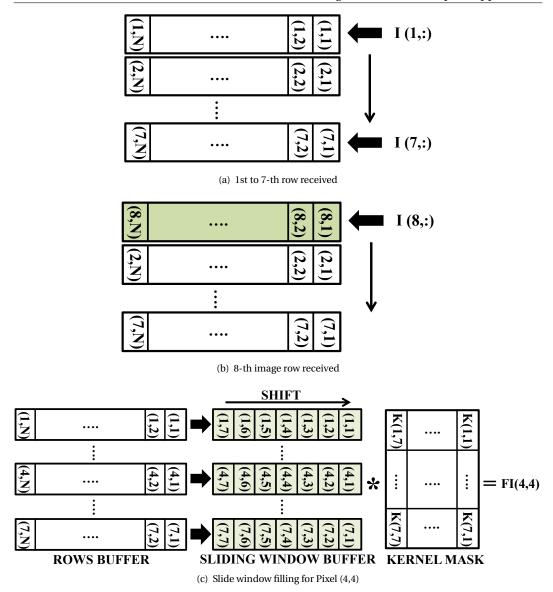

| 4.14 | Gaussian Filter internal buffers architecture. (i,j) indicates the pixel coordinates 8   | 81 |

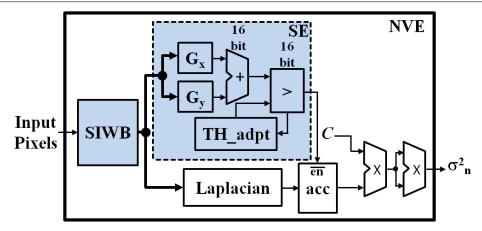

| 4.15 | NVE internal architecture                                                                | 82 |

| 4.16 | Adaptive Harris Features Extractor internal architecture                                 | 85 |

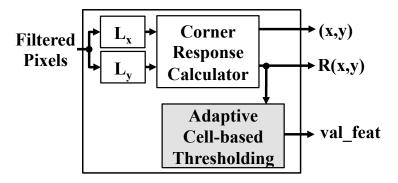

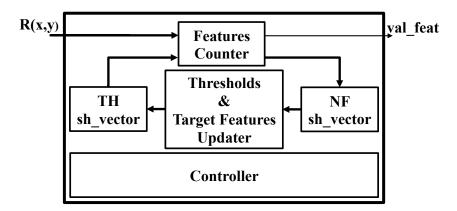

| 4.17 | Adaptive Cell-based Thresholding hardware architecture                                   | 88 |

| 4.18 | TH and NF shifter vector hardware architecture                                           | 89 |

| 4.19 | Features Matcher internal architecture                                                   | 90 |

| 4.20 | Fake matches on test images ranging different Cross-Correlation window size 9            | 92 |

| 4.21 | Timing diagram of SA-FEMIP                                                               | 93 |

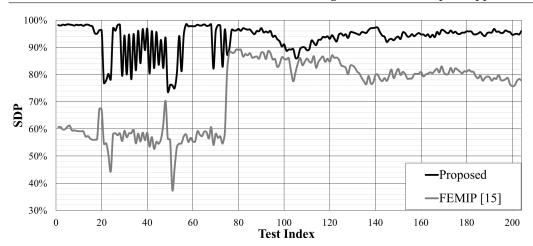

| 4.22 | SDP results for FEMIP and the proposed architecture                                      | 97 |

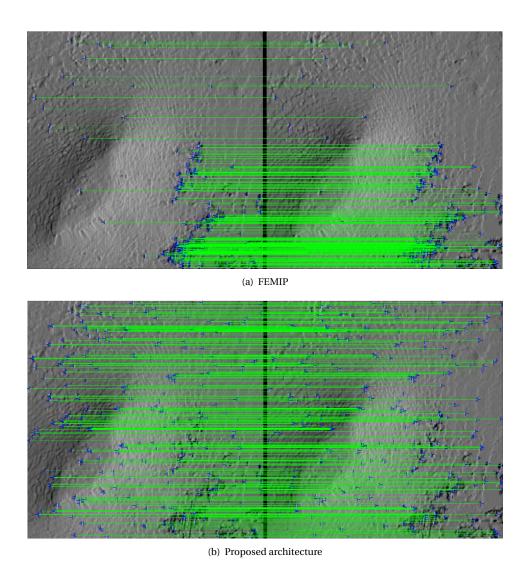

| 4.23 | Example of extracted matches                                                             | 98 |

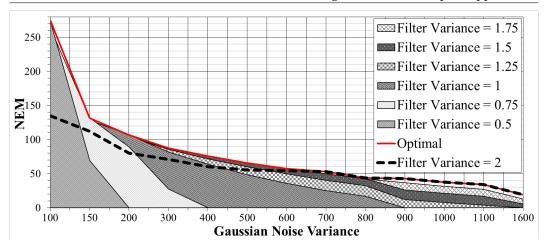

| 4.24 | NEM results for different levels of injected Gaussian noise, varying the Gaussian Filter |    |

|      | variance                                                                                 | 99 |

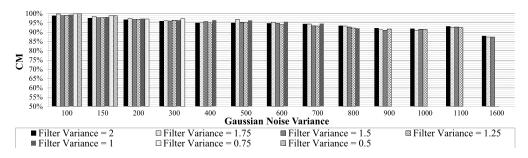

| 4.25 | Correct Matches (CM) results for different levels of injected Gaussian noise, varying    |    |

|      | the Gaussian Filter variance                                                             | 99 |

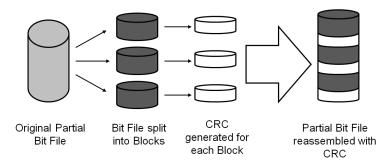

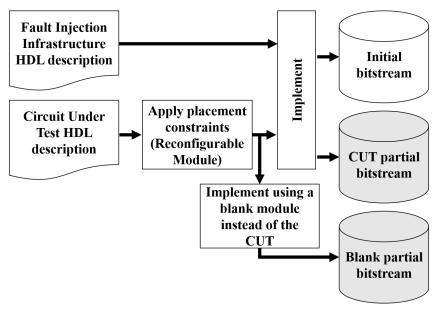

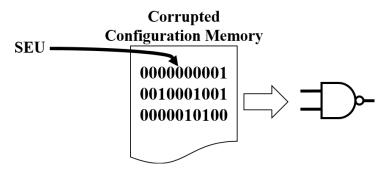

| 5.1  | Bitstream generation [229]                                                               | 03 |

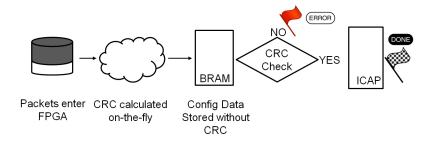

| 5.2  | Bitstream Loading process [229].                                                         |    |

| 5.3  | Reconfiguration time of Xilinx solution                                                  |    |

| 5.4  | Bitstream generation with the proposed solution.                                         |    |

| 5.5  | Bitstream loading process with the proposed solution.                                    |    |

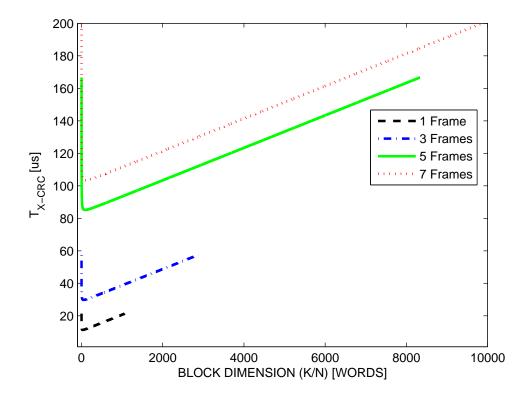

| 5.6  | Comparison between proposed solution and Xilinx solution                                 |    |

| 5.7  | Critical connections and cores                                                           |    |

| 5.8  | Reconfiguration time with 2 Frames                                                       |    |

| 5.9  | Xilinx PlanAhead tool device view                                                        |    |

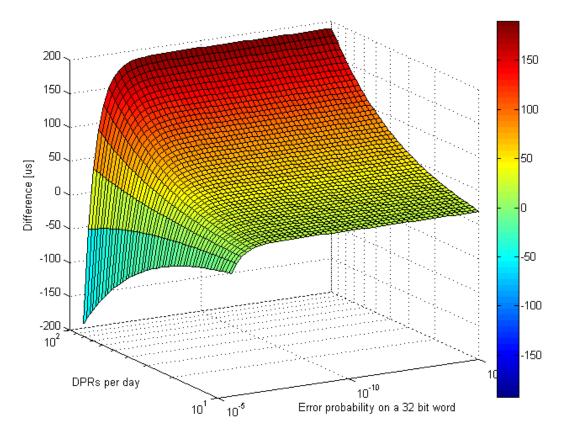

|      | Difference of DPRs time in 1 day - Bitstream size equal to 1,969 32-bit words            |    |

|      | Difference of DPRs time in 1 day - Bitstream size equal to 11,040 32-bit words 1         |    |

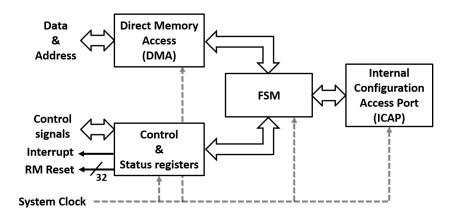

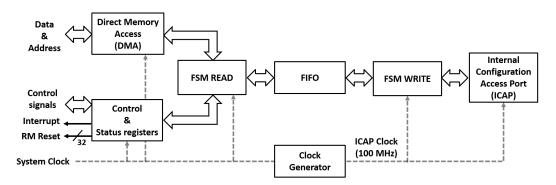

|      | DPR controller architecture for Synchronous DPR mode                                     |    |

|      | · · · · · · · · · · · · · · · · · · ·                                                    | 17 |

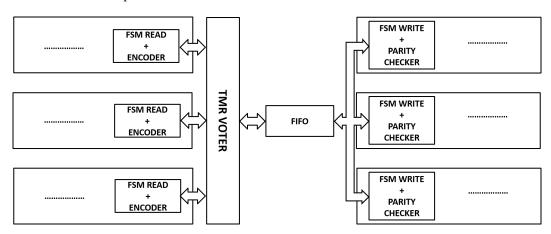

|      | Proposed TMR approach applied to the Asynchronous DPR mode architecture 1                | 18 |

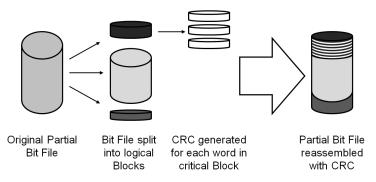

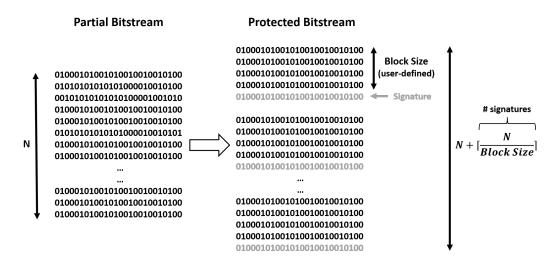

|      | Protected bitstream generation                                                           |    |

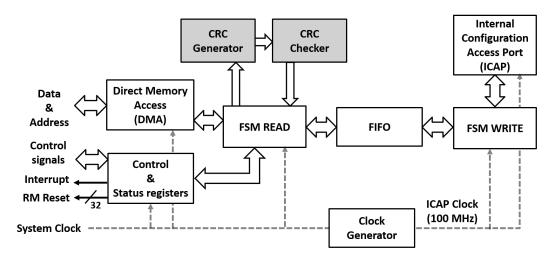

|      | DPR controller architecture for D <sup>2</sup> PR-CRC mode                               |    |

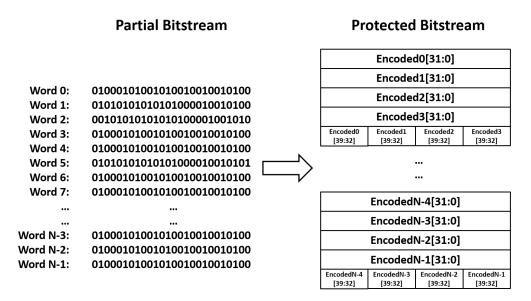

|      | Protected bitstream generation                                                           |    |

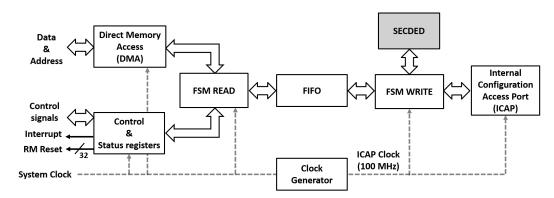

|      | DPR controller architecture for D <sup>2</sup> PR-EDAC mode                              |    |

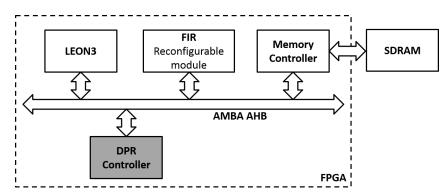

|      | Proposed controller instantiated in a LEON3-based system                                 |    |

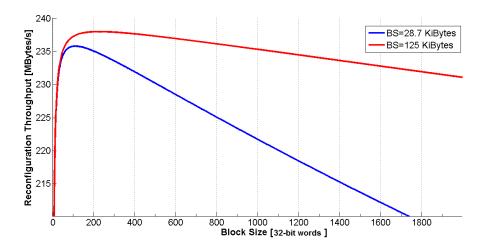

|      | Reconfiguration throughput w.r.t. data block size for the proposed DPR controller        | _5 |

| 0    |                                                                                          | 25 |

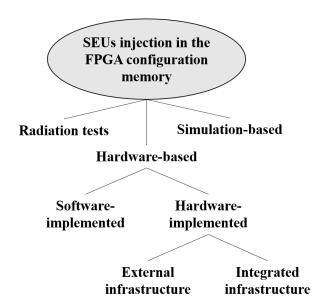

| 6.1 | FPGA configuration memory SEUs fault injection approaches classification 131                                         |

|-----|----------------------------------------------------------------------------------------------------------------------|

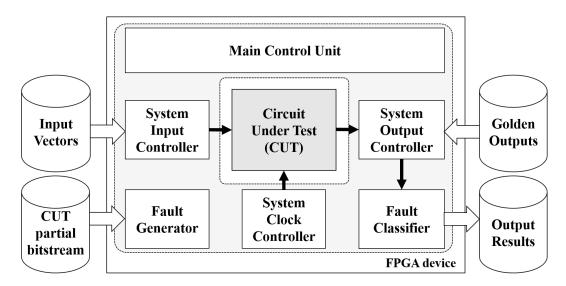

| 6.2 | Proposed fault injection infrastructure architecture                                                                 |

| 6.3 | Fault locations generation flow                                                                                      |

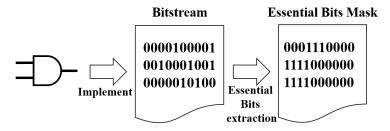

| 6.4 | Essential bits meaning                                                                                               |

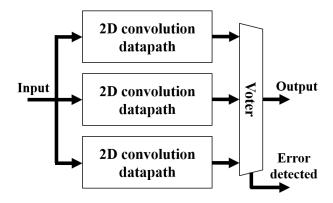

| 6.5 | Two-dimensional convolution datapath, with Triple Modular Redundancy 139                                             |

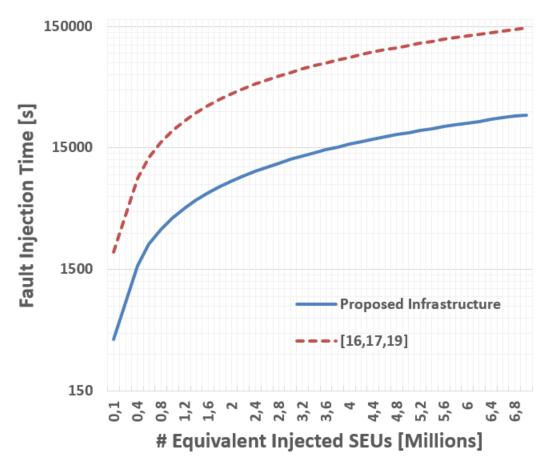

| 6.6 | Fault injection time vs number of equivalent injected SEUs trends comparison, in the case of the LEON3 running CRC32 |

# LIST OF TABLES

| 3.1 | Characteristics of <i>Xilinx</i> FPGAs configuration ports [239]                         |

|-----|------------------------------------------------------------------------------------------|

| 4.1 | Resource Usage for Xilinx Virtex 7 VX485T FPGA device                                    |

| 4.2 | Comparison among deblurring approaches in terms of execution time and RMSE 73            |

| 4.3 | Resources usage and power consumption of FEMIP and SA-FEMIP, implemented on              |

|     | a Xilinx XQR4VLX200 Virtex 4 FPGA device                                                 |

| 4.4 | Resource usage and throughput of FEIC and SA-FEMIP for a Xilinx XQR4VLX200 Vir-          |

|     | tex 4 FPGA device                                                                        |

| 5.1 | Area occupation and reconfiguration time of different implementations                    |

| 5.2 | Hardware resources and throughput for the proposed controller operating in a LEON3-      |

|     | based system implemented on a Virtex4-VLX100 FPGA                                        |

| 5.3 | Hardware resources and throughput for the proposed controller implemented on an          |

|     | <i>Artix7-xc7a100t</i> FPGA                                                              |

| 5.4 | Comparison of the proposed DPR controller with state of the art and vendor solutions.    |

|     | The target device is a <i>Virtex6-vlx240t</i> FPGA                                       |

| 6.1 | LEON3 CUT + associated fault injection infrastructure                                    |

| 6.2 | 2D convolution datapath CUT + associated fault injection infrastructure                  |

| 6.3 | 2D convolution datapath with TMR CUT + associated fault injection infrastructure 140     |

| 6.4 | CUTs Bitstream size, percentage of Essential Bits, application execution time, and total |

|     | injection time                                                                           |

| 6.5 | Fault Injection classification results                                                   |

CHAPTER

#### Introduction

owadays, computer vision is one of the most evolving areas of Information Technology (IT). Digital image processing, i.e., the use of algorithms to process and/or extract information from digital images, is being increasingly adopted in multiple application fields.

In general, digital image processing applications fall in two macro-fields: the former includes those applications in which it is used to improve visual information that must be subsequently interpreted by a human actor. Two examples are represented by consumer electronics, such as digital video or photo-cameras, and medical applications. The latter macro-field includes applications in which image processing is employed to extract information that must be stored, transmitted, or used for autonomous machine interpretation. Unmanned Aerial Vehicles (UAVs) navigation, autonomous surveillance and reconnaissance, military situational awareness, and other particular defense, aerospace, and automotive applications, fall in this class [93].

Within the aforementioned fields, image processing is used to serve both non-critical and critical tasks. As example, in automotive, cameras are becoming key sensors for increasing car safety and driving comfort, and for building high-reliable Advanced Driver Assistance Systems (ADAS) [209]. They have been employed for infotainment (non-critical), as well as for some mission-critical driver assistance tasks, such as Forward Collision Warning and Avoidance, Intelligent Speed Control, or Pedestrian Detection.

Also in the aerospace field cameras are likely to become reference sensors. Since decades, cameras are being used for Earth or deep-space observation through in-orbit satellites or powerful space telescopes (e.g., Hubble), and remote rovers navigation. Nonetheless, during the last years, several additional studies and projects carried out by space agencies have also demonstrated suitability of cameras and digital image processing in innovative space-mission contexts. For instance, they can be employed for object recognition during active space debris removal processes [62], or to assist the entry, descent and landing phase of spacecrafts employed in fu-

ture space exploration missions, thus enabling an autonomous video-based navigation of such objects [60].

In these application fields, real-time behaviors are often required in order to allow the system to quickly react to external dangerous events. However, the complexity of the applied algorithms brings a challenge when trying to build real-time embedded image processing systems, requiring high computing capacity, usually not available in modern processors for embedded systems. *Hardware acceleration* is therefore crucial and devices such as Field Programmable Gate Arrays (FPGAs) best fit the growing demand of computational capabilities.

FPGAs are digital integrated circuits which functionality can be programmed, once or multiple times, by the user or the designer after manufacturing, i.e., in the field [100]. They provide logic gates, memories and Digital Signal Processors (DSPs) blocks, thus enabling the implementation of complex digital functions and custom hardware accelerators. Due to their flexibility and continuously growing computing capacity, FPGAs often represent the preferred platform for the final deployment of embedded image processing systems. These devices can assist and offload embedded processors by significantly speeding-up computationally intensive software algorithms, thereby acting as efficient dedicated co-processors.

However, critical applications impose strict requirements in terms of both device dependability and algorithm robustness. Technology shrinking is highlighting reliability problems related to both aging phenomena and to the increasing sensitivity of electronic devices to external radiation events, that can cause transient or even permanent faults, leading to wrong information processed or, in the worst case, to a dangerous system failure.

In addition, even if the circuit which implements the chosen image processing algorithm is working correctly, sensor noise, illumination conditions variation, and other transitory environmental factors can impact the quality of the images acquired by cameras, consequently decreasing the trustworthiness of the algorithm's output results.

The research work presented in this thesis focuses on the development of techniques for implementing efficient and robust real-time embedded image processing hardware accelerators and systems for mission-critical applications. FPGAs have been chosen has target technology, following the current trend that is replacing custom and expensive Application Specific Integrated Circuits (ASICs) with more flexible FPGA devices also in such applications [97].

According to the aforementioned issues, three main challenges have been faced and will be discussed, along with proposed solutions, throughout the thesis: (i) achieving real-time performances, (ii) enhancing algorithm robustness, and (iii) increasing overall system's dependability.

In order to ensure real-time performances, efficient FPGA-based hardware accelerators implementing selected image processing algorithms have been developed. Functionalities offered by the target technology, and algorithm's characteristics have been constantly taken into account while designing such accelerators, in order to efficiently tailor algorithm's operations to available hardware resources. Moreover, efficient design, verification and validation methodologies have

been developed and adopted throughout the research work.

On the other hand, the key idea for increasing image processing algorithms' robustness is to introduce self-adaptivity features at algorithm level, in order to maintain constant, or improve, the quality of results for a wide range of input conditions, that are not always fully predictable at design-time (e.g., noise level variations). This has been accomplished by measuring at runtime some characteristics of the input images, and then tuning the algorithm parameters based on such estimations. Dynamic reconfiguration features of modern reconfigurable FPGAs have been extensively exploited in order to integrate run-time adaptivity into the designed hardware accelerators.

*Dynamic Reconfiguration* is the ability of modern FPGAs to be reconfigured at run-time without interrupting system's operations. The entire device or, in some cases, portions of it can be reconfigured in order to run-time change implemented hardware functionality, to correct design bugs, or to on-line recover from hardware faults.

However, the usage of dynamic reconfiguration exposes the system to new dependability threats that can cause mis-reconfigurations and consequently severely impact reconfigured device's operations. For this reasons, tools and methodologies have been also developed in order to increase the overall system dependability during reconfiguration processes, thus providing safe run-time adaptation mechanisms.

In addition, taking into account the target technology and the environments in which the developed hardware accelerators and systems may be employed, dependability issues have been analyzed and relevant fault models have been defined and adopted. This led to the development of a platform for quickly assessing the reliability and characterizing the behavior of hardware accelerators implemented on reconfigurable FPGAs when they are affected by such faults. The proposed platform can help designers to identify the weaknesses of the circuit and consequently apply the most suitable fault mitigation or protection techniques.

Finally, it is worth to mention that the entire thesis work relies on a strong collaboration with two companies operating in the aerospace market, i.e., *Thales Alenia Space Italy* and *Cobham Gaisler AB* (Sweden). Several target applications in the aerospace field have been selected during the research period and will be considered as main reference case-studies for the proposed solutions. Nonetheless, the concepts behind the contributions of this thesis can be generalized and applied when dealing with the development of embedded image processing, or more in general signal processing, systems for mission-critical applications.

#### 1.1 Thesis Organization

The thesis has been split in two main parts in order to allow the reader to easily understand the concepts and contributions of the presented research work. The first part includes two introductory chapters:

- Chapter 2 provides an overview on image processing concepts and applications. The chapter starts with a brief history of digital image processing. Then, several applications are presented focusing on those ones in which image processing is employed in mission-critical contexts, and highlighting issues, challenges and limitations of modern systems. Several reference use-cases and issues are discussed more in detail since they will be deeply analyzed in the following chapters. Image processing algorithm's classes are introduced and some mathematical background provided;

- Chapter 3, provides an overview of modern FPGAs, focusing on reconfigurable ones, and discussing the reasons behind their popularity and adoption in mission-critical applications. After a brief summary of the history that led from the first programmable device to modern reconfigurable FPGAs, the chapter details modern device types and architectures. Dynamic Partial Reconfiguration (DPR) is then introduced along with some technical details about the run-time reconfiguration process. Finally, dependability threats related to the usage of FPGAs in critical environments will be presented, analyzed and discussed.

The second part of the thesis presents the actual contributions of the research work. According to the points and challenges highlighted in the previous section, the rest of the thesis is organized as follows:

- Chapter 4 provides details on proposed approaches to enhance image processing algorithm robustness [59, 60, 61, 63, 77, 121, 122]. The implementation of associated hardware accelerators and systems on FPGAs is also detailed. Several case-studies are presented. For each of them, algorithms, issues, and advancements with respect to the state of the art are discussed;

- Chapter 5 discusses the proposed solutions for enhancing dynamic reconfiguration process dependability [58, 65]. In particular, this chapter details the issues related to run-time dynamic reconfiguration and the effect of mis-reconfigurations. Then, it presents two alternative ways to safely enhance reconfiguration process dependability. The former is essentially based on a set of rules to be applied at design-time [58], while the latter relies on the usage of a flexible hardware reconfiguration manager that must be instantiated in the target system [65]. Both approaches can be employed to safely enable self-adaptivity mechanisms in the designed image processing hardware systems without decreasing the dependability levels required by the target applications;

- Chapter 6 introduces the problem of evaluating system's robustness with respect to target fault models. It provides an overview of the state-of-the-art methods for emulating or injecting faults in FPGA-based systems, highlighting their limitations. Finally, it presents a methodology, along with an associated hardware platform, for emulating the effects of

selected soft errors types on modern FPGAs. The presented methodology provides designers a powerful tool to quickly evaluate the behaviour of the developed systems in harsh environments [64].

# DIGITAL IMAGE PROCESSING FOR MISSION-CRITICAL APPLICATIONS

ccording to the literature, *Digital Image Processing* represents a sub-field of the more general *Digital Signal Processing*, and refers to the usage of computer algorithms to process and/or extract useful information from digital images [93].

In general, an *image* can be defined as a "spatial representation of an object or a scene" [14], represented trough a continuous function:

$$f(x,y), \quad x,y \in \Re \tag{2.1}$$

where f denotes the value of the analog image at the coordinate (x, y).

In contrast to *Analog Image Processing*, which operates on analog representations of the object or scene, *Digital Image Processing* acts on a spatially-sampled and quantized representation of it, i.e., a *digital image*, which can be represented through a discretized function:

$$\bar{f}[x, y], \quad x, y \in \mathbb{N}$$

(2.2)

where f represents the quantized intensity value of the digital image at the sampled coordinate (x, y). Equivalently to Equation 2.2, a digital image can be represented through a two-dimensional array:

$$\bar{f}[x,y] = \begin{bmatrix} f[0,0] & f[0,1] & \dots & f[0,C-1] \\ f[1,0] & f[1,1] & \dots & f[1,C-1] \\ \dots & \dots & \dots & \dots \\ f[R-1,0] & f[R-1,1] & \dots & f[R-1,C-1] \end{bmatrix}$$

(2.3)

composed of *R* rows and *C* columns of picture elements, called *pixels*. The value of each *pixel* stores the quantized *intensity* level of that point in the scene. For digital images, pixels store one

or more integer values, represented trough bit arrays, that result from a quantization process carried out by the adopted imaging sensor circuitry. Common bit-widths for the representation of a pixel are 8 or 24 for grey-scale and colors images, respectively [14].

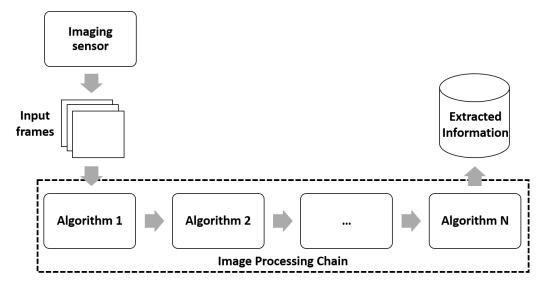

Usually, digital image processing is carried out by applying one or more image processing algorithms to the frames acquired trough an imaging sensor. As shown in Figure 2.1, algorithms are applied sequentially in order to extract high level information that can be easily handled by the user of the image processing system.

Figure 2.1: Representation of a generic image processing flow.

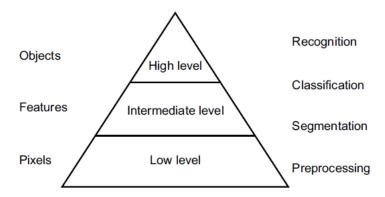

According to [14], image processing algorithms can be grouped depending on the type of data they have to handle and process. This concept is also illustred in Figure 2.2, which depicts the so called *Image Processing Pyramid*.

- Image Pre-processing: this category includes all the algorithms used to enhance the quality of the input frames, and more in general enhance the relevant information. Examples of pre-processing operations are distortion correction, histogram equalization, and noise filtering [93]. Pre-processing techniques act on every pixel composing the image, in order to change their values;

- **Image Segmentation**: the purpose of segmentation is to detect objects or regions in an image, characterized by some specific properties. They essentially extract features from the pixels information, providing a higher-level description of the input frame.

- Image Classification: starting from a set of features, classification algorithms identify objects, and eventually classify them into categories;

Figure 2.2: Digital image processing pyramid [14].

• **Image Recognition**: recognition algorithms work on objects extracted from the image and aim at deriving high level descriptions or interpretation of the scene.

#### 2.1 History of Digital Image Processing

The first applications of digital images date back to the early 1920s, when newspaper pictures were sent through the Bartlane cable transmission system across the Atlantic. At that time, a picture can be trasmitted in less than three hours using a telegraph and reproduced at the receiving part exploiting a special telegraph printer [93, 140].

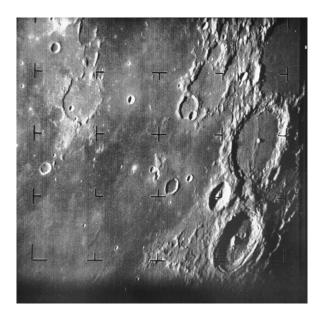

Although in the following years the systems and underlying technology were improved, we can start talking about "true" digital image processing with the introduction and development of digital computers with sufficient computational capabilities. Actually, the first computers powerful enough to process digital images were introduced in the 1960s [93]. In that period, due to the high activity of the space programs, the NASA Jet Propulsion Laboratory developed and used image processing techniques to enhance the quality of the Moon images taken from the *Ranger* 7 space probe [158], therefore demonstrating the effectiveness and potentialities of digital image processing. In fact, the imaging system was the unique scientific instrumentation equipped on the *Ranger* 7 probe, that in 1964 was able to capture, for the first time (for the US), 4,316 images of the Moon (Figure 2.3) and transmit them to the Earth in the 15 minutes before its impact on the lunar surface [158].

In the late 1960s and early 1970s, digital image processing started to be employed also in medical applications, with the introduction of the computerized axial tomography [87].

Due to the technology advance and the decrease of modern computers cost-to-performance ratio, digital image processing has expanded its application domains. Nowadays it is heavily employed in numerous fields, including, but not limited to, aerospace, automotive, medicine, biology, and defense [93].

Figure 2.3: First image of the Moon taken by Ranger 7 [158].

#### 2.2 Image Processing in mission-critical applications

Nowadays digital image processing is being increasingly adopted in numerous application fields, to serve both critical and non-critical tasks. Two examples are represented by the usage of digital image processing techniques for building innovative automotive Advanced Driver Assistance Systems (ADAS) or autonomous Video-based Navigation Video-based Navigation (VBN) systems for future space exploration missions.

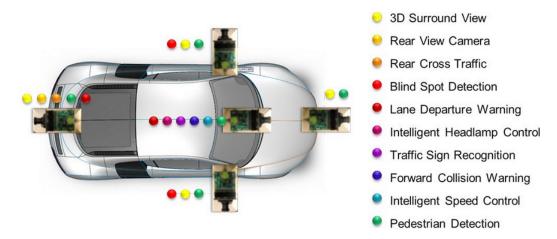

As stated in [7], "one of the major goals of the automotive industry is to reduce the number of traffic fatalities and severity of accidents". Although standard safety (e.g., airbag or ABS) systems are heavily employed in modern vehicles, due to the large and continuously increasing number of vehicles in on the road, new innovative technologies have been introduced to increase car safety and to assist drivers to avoid dangerous situations. In this context, vehicles are being equipped with multiple smart camera-based systems, that can carry out different tasks, as depicted in Figure 2.4.

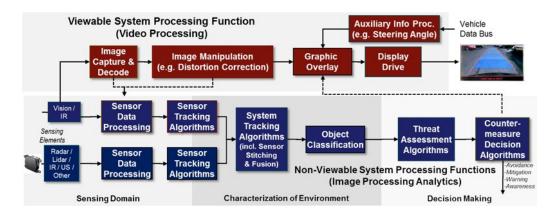

During the last years, vehicle-based camera systems for ADAS have become more and more complex, being able to perform real-time tasks such as traffic sign recognition, pedestrian detection, forward collision avoidance and road lane detection [167]. An example ADAS system high-level block diagram is illustrated in Figure 2.5.

As reported in [222], an ADAS system may be based on several subsystems that can share some portions of the digital image processing pipeline:

• Viewable system: images are captured through one or more imaging sensors and decoded

Figure 2.4: Examples of vehicle camera-based systems tasks [222].

Figure 2.5: Block diagram of an automotive ADAS system [222].

for further video processing (e.g., for image enhancement and distortion correction) in order to provide graphical information that can be displayed to the driver;

Non-viewable system: includes all those hardware and software systems needed to implment digital image processing algorithms for extracting useful information from the acquired frames and for interpreting them to characterize the vehicle environment and support continuous threat assessment and drive countermeasures (e.g., to identifying lane markings, road signs, pedestrians and other vehicles) [222].

On the other hand, in the aerospace domain, digital image processing has been used in the last decades for many purposes [176], such as *Earth Observation* [23, 161], *Space Cartography* [160], *Satellites and Spacecrafts Attitute Control* [129], and *Rovers Navigation* [165].

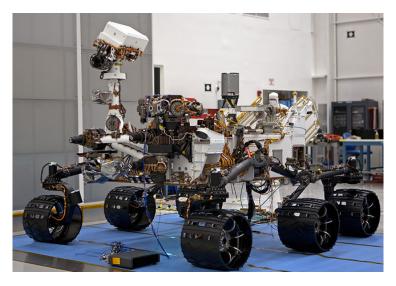

A recent example of the usage of digital image processing techniques requiring high computational capabilities in the space domain is represented by the *NASA Curiosity* mission [163].

*Curiosity* is a car-sized rover (see Figure 2.6), that is exploring the Martian surface since August 2012.

Figure 2.6: Curiosity rover.

As reported in [165], the *Curiosity* rover has been equipped with 17 "eyes", for a total of 10 cameras. 6 cameras are devoted to the rover navigation, while the other 4 are used to perform science investigations on the Mars surface:

- **Hazcams**: four pairs of cameras are employed for hazard avoidance. *Hazcams* are black and white cameras mounted on the lower portion of the front and rear of the rover to capture three-dimensional images. Hazard detection is essential to protect the rover from crashing into unexpected obstacles. These cameras work in tandem with the software that allows the rover to autonomously react and avoid dangerous situations [165];

- **Navcams**: two pairs of cameras are used to help rover ground navigation providing a panoramic view of the terrain. These cameras also work in cooperation with *Hazcams*;

- **MastCam**: two *Mast* cameras are used to take three-dimensional color images and videos of the Martian terrain;

- MAHLI: the *Mars Hand Lens Imager* provides close views of the minerals, textures, and structures in the martian surface. It takes color images of features as small as 12.5 micrometers.

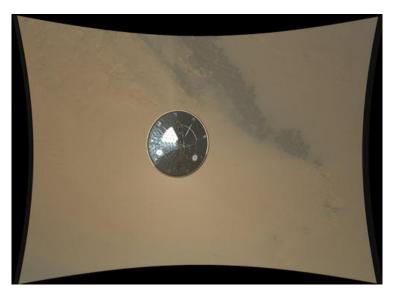

In addition to the aforementioned cameras, the *Curiosity* mission employs an additional camera that has been used to acquire frames during the rover landing phase. The *Mars Descent Imager* (MARDI) acquired 1600x1200 pixel images (Figure 2.7) at roughly 5 frames per second throughout the entire landing period, i.e., from the landing module heatshield separation until surface touchdown.

Figure 2.7: Picture of the *Curiosity*'s heatshield taken by *MARDI* [164].

During the landing phase, the acquired frames were written into flash memory in real-time and transmitted later to the Earth.

Although vision-based approaches have been heavily employed to allow autonomous rover ground navigation, during the Entry, Descent and Landing phase, cameras are usually employed as passive components, not included in the spacecraft landing control loop (e.g., *MARDI* in *Curiosity* mission).

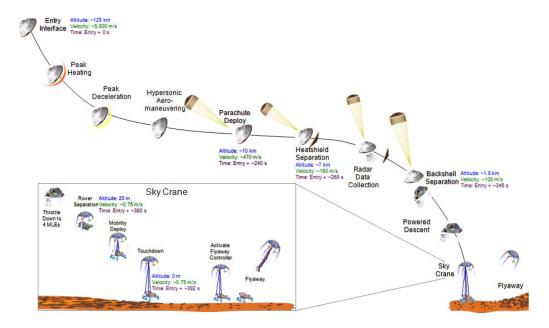

In a space exploration mission, the Entry, Descent and Landing (EDL) represents one of the most dangerous phases, since all the expensive on-board electronic and mechanical instruments are subject to strong mechanical vibrations that can damage them. Moreover, a high accuracy of the landing point must be guaranteed in order to be able to reach predefined and safe portions of the target planet surface. For these reasons, during the last years, there was an increasing interest of space agencies in developing innovative EDL systems that try to minimize the probability of mission failures, while at the same time providing an increased precision of the landing point. The landing accuracy is usually measured resorting to the size of the so called *landing ellipse*, which identifies the predicted landing zone. The size of the landing zone is essentially determined by the uncertainty of numerous environmental factors, that can impact the descending

trajectory during the actual landing phase. Figure 2.8 illustrates the predicted landing ellipse of the *Curiosity* rover. The size of the landing ellipse was 20x7 kilometers.

Figure 2.8: Representation of the *Curiosity*'s landing ellipse on the Martian surface[201].

The high precision of the state-of-the-art *Curiosity*'s landing system is due to the adoption of a combinations of different sensors and approaches that enable a guided landing phase. Figure 2.9 summarizes the *Curiosity*'s EDL phases.

When the parachute is completely deployed, the heat shield is released, and the radar begins collecting data about velocity and altitude. The information gathered from the radar instruments are then used by the Guidance Navigation and Control (GNC) system to correct, if necessary, the spacecraft descending trajectory through the usage of thrusters.

During the last years, space agencies have increased the effort for the development of novel EDL systems. In particular, VBN approaches have been preferred, as demonstrated by several funded studies [69, 79] due to the potentialities offered by digital image processing and the limited weight of vision instruments and associated processing systems. VBN systems aim at computing the speed and attitude of the spacecraft by processing consecutive frames acquired through an imaging sensor. This approach is also called *Relative Navigation*, which aims at computing speed and relative position of the spacecraft by processing images in real-time.

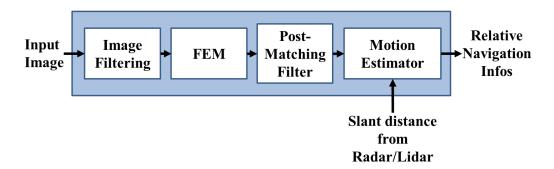

A typical relative navigation image processing chain is depicted in Figure 2.10 [122]. *Relative Navigation* is carried out by performing two main activities:

• **Features Extraction and Matching** FEM: each frame is processed to detect those pixels or regions that represent features of interest in the image (e.g., corners or edges on the surfaces). The detected features are then compared to extract those that can be recognized in two consecutive images (*matching points*);

Figure 2.9: Representation of the Curiosity's EDL [159].

Figure 2.10: Representation of the *Curiosity*'s EDL [122].

• **Motion Estimation**: the output results of *FEM* are analyzed by the motion estimation algorithms that extract the relative position, speed and attitude of the camera by fusing matching points information with those extracted by additional sensor, such as radars or lidars.

A first approach to an autonomous VBN system in space exploration missions has been accomplished during the *Mars Exploration Rovers* mission [162], in which two rovers, i.e., *Spirit* and

Opportunity landed on the Martian surface.

The EDL approach adopted in such mission was parachute-assisted and almost entirely ballistic. Moreover, due to the limited knowledge of the Martian environment (e.g., wind speeds and atmosphere composition), the predicted trajectory presented a large uncertainty, leading to an estimated landing ellipse of 15x160 kilometers.

However, during the *EDL* phase, the so-called Descent Image Motion Estimation System (DIMES) has been employed. DIMES represents the first autonomous machine vision system used to safely land a robotics payload on another planet. It consists of a camera and a software algorithm for estimating horizontal velocity using images, inertial and altitude measurements [40, 109].

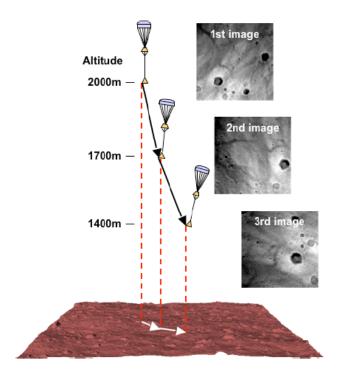

Figure 2.11 illustrates the DIMES descent scenario.

Figure 2.11: DIMES descent scenario [109].

Three images are taken by the camera, at roughly 2000m, 1700m, and 1400m above the Martian surface, and processed by a software algorithm that first extracts features between the first and the second image, and other two features between the second and the third image. The three images are scaled and rotated depending on the actual attitude, that has been measured through an inertial measurement unit. Finally, two features for each image pair are tracked using a two-dimensional correlator in order to compute and estimate the average velocity between two acquired frames. The resulting value is also checked with respect to the outputs of the inertial measurement unit data that eventually propagates a control command to thrusters to correct

the horizontal velocity of the spacecraft [40, 109].

It is worth to mention that this system has been successfully employed during landing of both *Spirit* and *Opportunity* rovers, and played an important role in the first case. In fact, during *Spirit* landing, the total velocity was at the limit of the landing airbag capability. Airbags were used to limit the impact forces of the rover with the Martian surface. However, tests highlighted that, if the velocity at impact instant had been too large, the airbags would be ripped [40]. Anyway, DIMES was able to compute the correct values and activate thrusters to reduce the risky horizontal velocity [109] and provide a safe landing of the *Spirit* rover on the planet terrain.

#### 2.3 Imaging sensors and related issues

The image sensor represents the fundamental part of a camera. In its basic form, an image sensor can be defined as a sensor that converts light information into electrons, and subsequently electrons into a voltage.

Two main sensor technologies are adopted to generate digital images that can be digitally processed, i.e., Charge-Coupled Device (CCD) and *CMOS*.

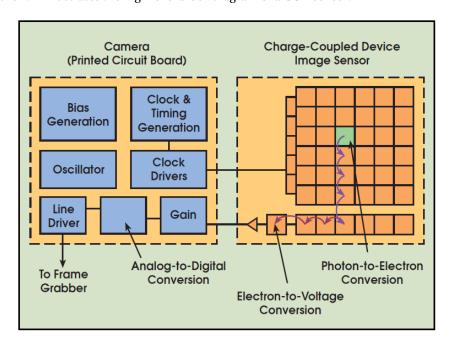

Figure 2.12 illustrates the high level block diagram of a CCD sensor.

Figure 2.12: CCD imaging sensor high level block diagram [130].

A CCD is a solid-state image sensor composed of a two-dimensional array of pixels. A pixel is a MOS capacitor that stores charges whenever a photon is absorbed [120, 137] (*Photon-to-Electron Convesion* phase). When exposure is complete, pixels' charges are sequentially transferred to the

read-out circuitry that generates a buffered output voltage proportional to the amount of charge trapped by a single pixel. Afterwards, an off-chip Analog-to-Digital Converter (ADC) converts the analog voltage value generated by each pixel into a binary representation.

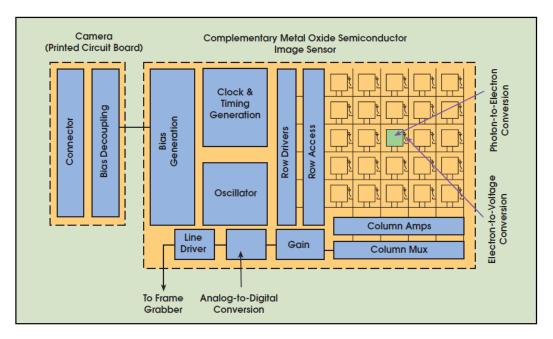

On the other hand, as depicted in Figure 2.13, in a *CMOS* sensor most of the operations are performed on-chip.

Figure 2.13: CMOS imaging sensor high level block diagram [130].

A *CMOS* sensor is composed of a two-dimensional array of pixels elements that, depending on the adopted technology, can be either *passive* (Figure 2.14) or *active* (Figure 2.15).

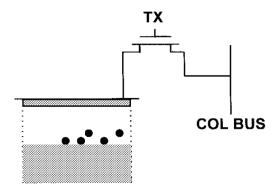

Figure 2.14: *CMOS* passive pixel sensor [80].

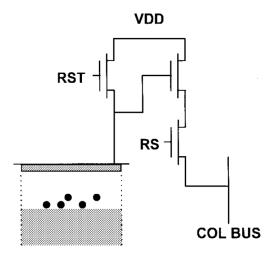

Figure 2.15: CMOS active pixel sensor [80].

As shown in Figure 2.14, a *CMOS* passive pixel element consists of a photo-diode and a pass transistor. When the pass transistor is activated, the photo-diode is connected to the *column* bus and the charge accumulated in the photodiode is converted into a proportional voltage by the read-out circuitry [80].

On the other hand, Figure 2.15 illustrates a *CMOS* active pixel, composed of a photo-diode and three transistors [80]. When the *reset* transistor (i.e., the one driven by the *RST* signal) is turned-on, the photo-diode looses the accumulated charge because of the direct connection to the power supply (i.e., *VDD*). An amplifier transistor is used to read the pixel voltage without removing the actual accumulated charge, while a selection transistor (i.e., the one driven by the *RS* signal) is used guarantee the access of the read-out circuitry to the target pixel voltage. The main difference of such pixel architecture over a CCD sensor relies on the fact that (i) the entire charge-to-voltage conversion takes place in each pixel [130], and (ii) CMOS pixels do not require special manufacturing techniques since they can be fabricated resorting to the same silicon technology process of the surrounding logic.

Either acquired trough a CCD or a *CMOS* sensor, digital images may not accurately reproduce the target scene due to the presence of several phenomena, such as temperature or sensor manufacturing process variations, or sensor mechanical vibrations during the exposure time, that can induce errors in the output pixels values.

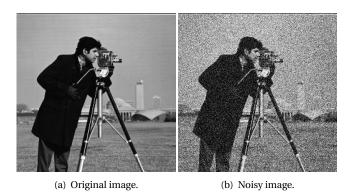

In particular, two main effects are usually considered as unwanted sources of digital image degradation, i.e., *noise* and *blur* [93]. Figure 2.16 and Figure 2.17 illustrate two examples of digital images affected by noise and blur, respectively.

Several types of image noise and blur exists, and they are briefly discussed in the sequel.

Noise can be defined as a stochastic undesired variation of the pixels values that leads to a

Figure 2.16: Example of an image affected by noise.

Figure 2.17: Example of the blur effect.

deviation from the correct representation of the target scene [255].

As stated in [93], "the principal sources of noise in digital images arise during image acquisition and/or transmission. The performance of imaging sensors is affected by a variety of factors, such as environmental conditions during image acquisition (e.g., light levels and sensor temperature), and by the quality of the sensing element themselves". Some examples of noise sources are:

• **Shot noise**: this type of noise, also called *Photon noise*, is caused by the non-deterministic arrival of photons during the image acquisition process. Basically, during the digital image acquisition interval, photons hit the sensor's sensing elements. However, it is not guaranteed that, if we carry-out two independent acquisitions of the same target scene (with the same light conditions and for the same interval), the number of charges acquired by the

sensor elements will be the same, due to the random arrival of photons. Since the charge accumulated is inherently discretized, this leads to a stochastic variation of the pixel value. This effect is highlighted when the image is acquired with very narrow acquisition periods, since the number of accumulated photo-electrons can be very low. Therefore, the impact of this effect can be limited with the adoption of longer exposure periods;

- Dark current: also called *Thermal noise*, it represents the noise contribution given by the thermally-generated electrons in the sensor's pixels. It is proportional to the sensor temperature and to the exposure time. As reported in [255], to partially suppress this type of noise, the average dark current for a given acquisition period can be estimated and substracted just before the ADC conversion. Nonetheless, since the thermal noise contribution is also stochastic, even if the average value is removed, the contribution related to the standard deviation is still present [255];

- **Read noise**: it represents the noise generated by the read-out circuitry during the pixel voltage extraction;

- Amplifier noise: it is well known that all analog amplifiers introduce noise. In an imaging sensor, the extracted pixel voltage is amplified before the actual *Analog-to-Digital* conversion. This amplification is necessary to extend the range of the voltages generated by the sensor sensing element to be compliant with the adopted ADC;

- **Quantization noise**: it is mainly introduced during the *Analog-to-Digital* conversion process because of the sampling of the input analog voltage and subsequent conversion into a discretized binary representation. It essentially depends on the adopted ADC levels, or equivalently, on the number bits used to represent the pixel value.

On the other hand, according to [28], blur can be classified in:

- **Motion blur**: it is introduced when there is a relative translation, rotation, zoom, or a combination of them, between the camera and the objects in the target scene;

- De-focus blur: this kind of image blur is introduced when the target scene presents objects

that have different distances with respect to the camera. It mainly depends on the focal

length, on the adopted lens, and on the distance between the camera and the objects;

- Atmospheric blur: this type of blur mainly affects remote sensing applications (e.g., Earth

observation from space satellites). This effects depends on several environmental factors,

such as temperature and atmospheric turbulence, that can lead to unpredictable light refraction phenomena.

The aforementioned blur effects are accentuated when the target scene is poorly lighted and so a greater exposure time is required. However, in many situations there is simply not enough light to avoid using a long shutter speed, leading to an acquired images that is inevitably blurry.

#### 2.3.1 Mathematical model

The presence of noise or blur effects in images can severely impact the performances of digital image processing and computer vision algorithms, since image details (such as edges) and, more in general, image information, may be partially lost.

Consequently, one of the aims of digital image processing is to try to restore the information affected by unwanted effects, and therefore provide images that can be well processed by the subsequent algorithms in order to extract "reliable" information.

A simplified model of a digital image g[x, y], composed of a two-dimensional array of R rows and C columns of pixels, and affected by blur and noise, can be formalized as follows [28]:

$$g[x,y] = \sum_{a=0}^{R-1} \sum_{b=0}^{C-1} h[a,b] f[x-a,y-b] + n[x,y]$$

(2.4)

where f[x, y] denotes the ideal image not affected by any unwanted effect, n[x, y] represents the additive noise that corrupt the image, while h[a, b] is the so-called Point Spread Function (PSF).

Equation 2.4 can be re-written as:

$$g[x, y] = h[a, b] * f[x, y] + n[x, y]$$

(2.5)

where \* denotes the two-dimensional convolution operator.

Equation 2.4 and Equation 2.5 model the effect of blur through a two-dimensional convolution operation between the PSF and f[x, y]. Assuming the absence of noise, the PSF represents the transfer function of the imaging system. As stated in [28], "if the ideal image", i.e., f[x, y] in Equation 2.5, "would consist of a single intensity point or point source, this point would be recorded as a spread-out intensity pattern", i.e., h[x, y] in Equation 2.5. Basically, the PSF represents the system response to a point source, and describes how each point source is "spreaded" in the output image. From a system theory point of view, assuming that the considered imaging system is linear, the PSF represents the system impulse response.

Despite its simplicity, this model is often adopted in practice because it provides a good approximation level of the real effects, and low-complexity.

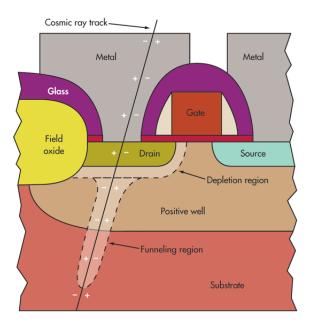

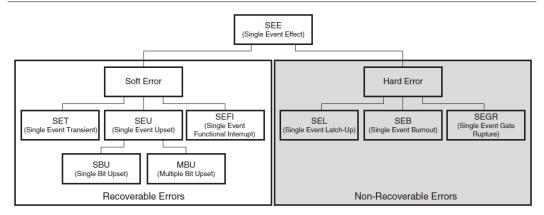

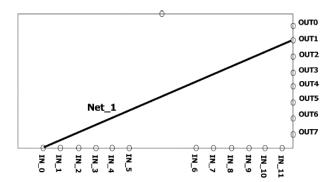

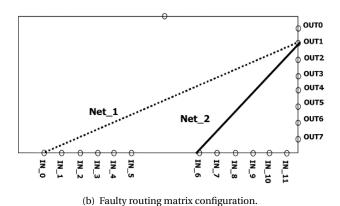

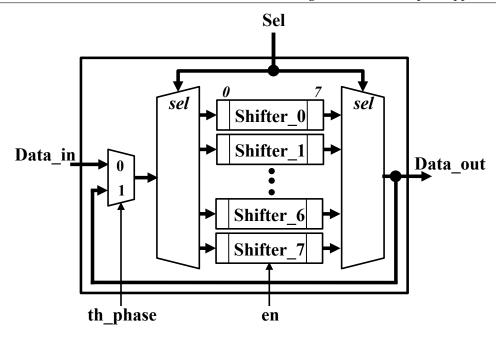

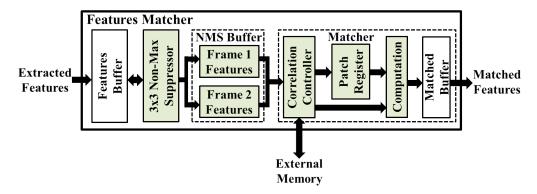

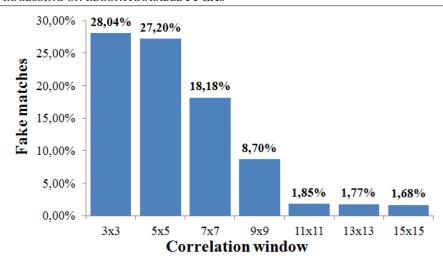

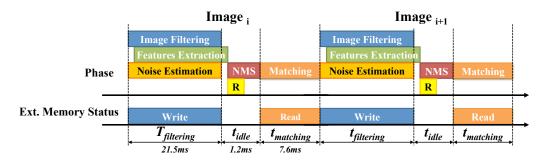

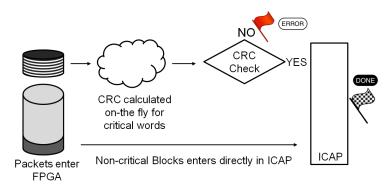

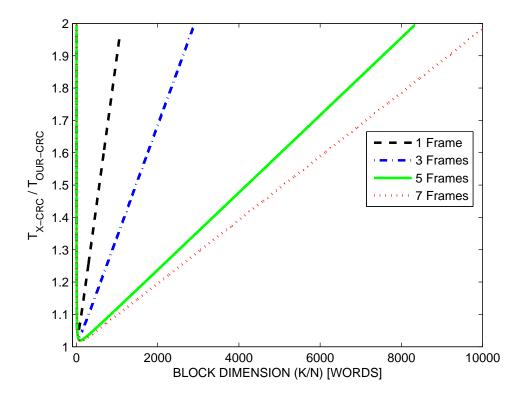

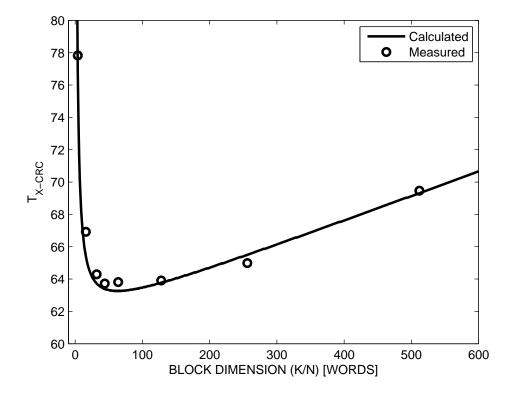

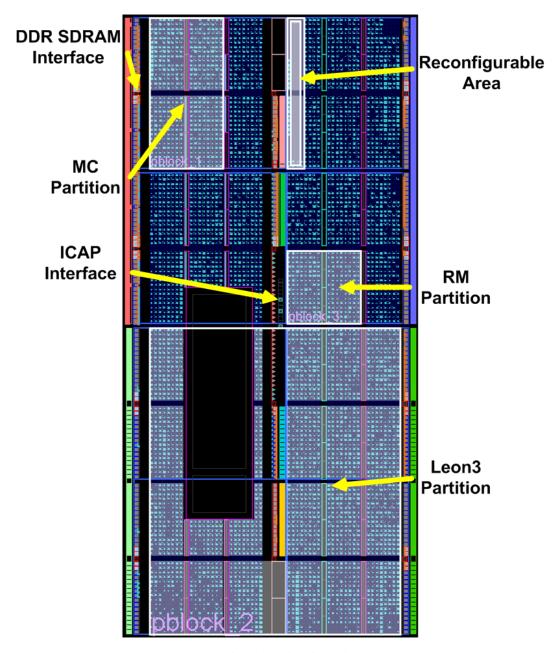

In particular, Equation 2.4 assumes that the PSF function is spatially invariant, meaning that each point of the image is blurred in the same way, independently from its location. Moreover, the blur is assumed to be a process that does not absorb or generate energy [28], therefore: