#### POLITECNICO DI TORINO Repository ISTITUZIONALE

#### Innovative Techniques for Testing and Diagnosing SoCs

| Original Innovative Techniques for Testing and Diagnosing SoCs / DE CARVALHO, Mauricio (2015).                                          |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                                                                                         |  |  |  |

|                                                                                                                                         |  |  |  |

| Availability: This version is available at: 11583/2612755 since:                                                                        |  |  |  |

| Publisher: Politecnico di Torino                                                                                                        |  |  |  |

| Published DOI:10.6092/polito/porto/2612755                                                                                              |  |  |  |

| Terms of use: openAccess                                                                                                                |  |  |  |

| This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository |  |  |  |

|                                                                                                                                         |  |  |  |

| Publisher copyright                                                                                                                     |  |  |  |

|                                                                                                                                         |  |  |  |

|                                                                                                                                         |  |  |  |

|                                                                                                                                         |  |  |  |

| (A dista basis as a same tage a)                                                                                                        |  |  |  |

(Article begins on next page)

#### POLITECNICO DI TORINO

#### DOCTORATE SCHOOL

Ph.D. IN COMPUTER AND CONTROL ENGINEERING - XXVI CYCLE

#### PHD THESIS

# INNOVATIVE TECHNIQUES FOR TESTING AND DIAGNOSING SOCS

**ADVISOR:**

PH.D. PAOLO BERNARDI

CANDIDATE: M.Sc. Mauricio De Carvalho

FEBRUARY, 2015

#### **Abstract**

We rely upon the continued functioning of many electronic devices for our everyday welfare, usually embedding integrated circuits that are becoming even cheaper and smaller with improved features. Nowadays, microelectronics can integrate a working computer with CPU, memories, and even GPUs on a single die, namely *System-On-Chip* (SoC). SoCs are also employed on automotive safety-critical applications, but need to be tested thoroughly to comply with reliability standards, in particular the ISO26262 functional safety for road vehicles.

The goal of this PhD. thesis is to improve SoC reliability by proposing innovative techniques for testing and diagnosing its internal modules: CPUs, memories, peripherals, and GPUs. The proposed approaches in the sequence appearing in this thesis are described as follows:

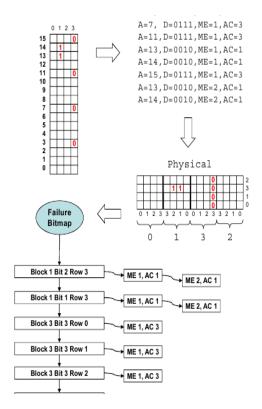

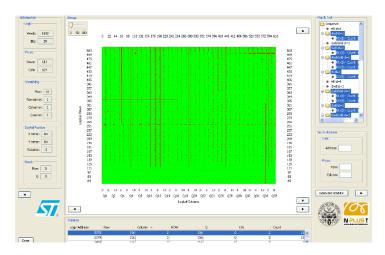

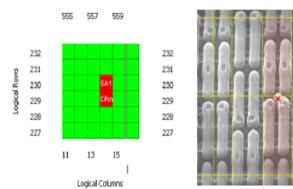

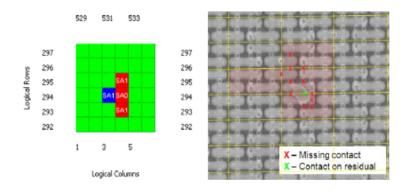

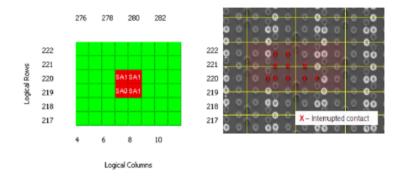

- 1. *Embedded Memory Diagnosis*: Memories are dense and complex circuits which are susceptible to design and manufacturing errors. Hence, it is important to understand the fault occurrence in the memory array. In practice, the logical and physical array representation differs due to an optimized design which adds enhancements to the device, namely *scrambling*. This part proposes an accurate memory diagnosis by showing the efforts of a software tool able to analyze test results, unscramble the memory array, map failing syndromes to cell locations, elaborate cumulative analysis, and elaborate a final fault model hypothesis. Several SRAM memory failing syndromes were analyzed as case studies gathered on an industrial automotive 32-bit SoC developed by STMicroelectronics. The tool displayed defects virtually, and results were confirmed by real photos taken from a microscope.

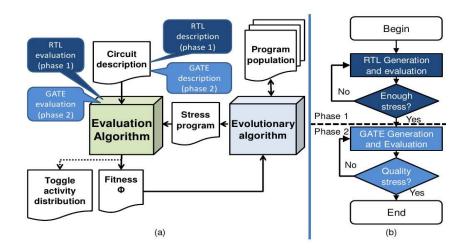

- 2. *Functional Test Pattern Generation*: The key for a successful test is the pattern applied to the device. They can be structural or functional; the former usually benefits from embedded test modules targeting manufacturing errors and is only effective before shipping the component to the client. The latter, on the other hand, can be applied during mission minimally impacting on performance but is penalized due to high generation time. However, functional test patterns may benefit for having different goals in functional mission mode. Part III of this PhD thesis proposes three different functional test pattern generation methods for CPU cores embedded in SoCs, targeting different test purposes, described as follows:

- a. Functional Stress Patterns: Are suitable for optimizing functional stress during

- Operational-life Tests and Burn-in Screening for an optimal device reliability characterization

- b. *Functional Power Hungry Patterns*: Are suitable for determining functional peak power for strictly limiting the power of structural patterns during manufacturing tests, thus reducing premature device over-kill while delivering high test coverage

- c. *Software-Based Self-Test Patterns*: Combines the potentiality of structural patterns with functional ones, allowing its execution periodically during mission. In addition, an external hardware communicating with a devised SBST was proposed. It helps increasing in 3% the fault coverage by testing critical *Hardly Functionally Testable Faults* not covered by conventional SBST patterns.

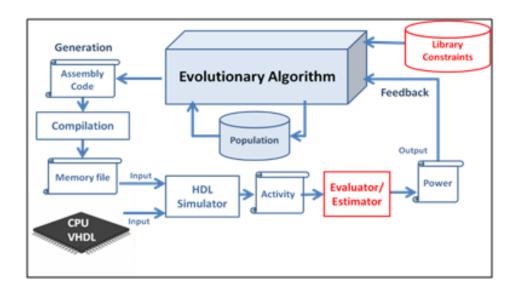

An automatic functional test pattern generation exploiting an evolutionary algorithm maximizing metrics related to stress, power, and fault coverage was employed in the above-mentioned approaches to quickly generate the desired patterns. The approaches were evaluated on two industrial cases developed by STMicroelectronics; 8051-based and a 32-bit Power Architecture SoCs. Results show that generation time was reduced upto 75% in comparison to older methodologies while increasing significantly the desired metrics.

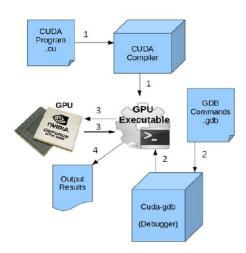

3. Fault Injection in GPGPU: Fault injection mechanisms in semiconductor devices are suitable for generating structural patterns, testing and activating mitigation techniques, and validating robust hardware and software applications. GPGPUs are known for fast parallel computation used in high performance computing and advanced driver assistance where reliability is the key point. Moreover, GPGPU manufacturers do not provide design description code due to content secrecy. Therefore, commercial fault injectors using the GPGPU model is unfeasible, making radiation tests the only resource available, but are costly. In the last part of this thesis, we propose a software implemented fault injector able to inject bit-flip in memory elements of a real GPGPU. It exploits a software debugger tool and combines the C-CUDA grammar to wisely determine fault spots and apply bit-flip operations in program variables. The goal is to validate robust parallel algorithms by studying fault propagation or activating redundancy mechanisms they possibly embed. The effectiveness of the tool was evaluated on two robust applications: redundant parallel matrix multiplication and floating point Fast Fourier Transform.

### Acknowledgements

Firt of all, I'd like to acknowledge the support of my advisor, PhD Paolo Bernardi, who has guided me from the beginning of this PhD Thesis and also for creating collaboration opportunities with valuable companies and research institutions. I'd also like to deeply express my sincere gratitude to the CAD group leader, Professor Matteo Sonza Reorda, who has generously spared his valuable time to give me support with his expertise, not only guiding me promptly through this research, but also for motivating me to finish this thesis at Politecnico di Torino.

I would also like to thank all of the CAD group members with whom I had the honour to work: Ernesto Sanchez, Michelangelo Grosso, Giovanni Squillero, Luca Sterpone, Lyl, Niccolò, Davide, Fabio, Marco Desogus, Marco Gaudesi, Salvatore, Riccardo, Gabriele, and many other assistant professors and students.

To Alberto Bosio, Patrick Girard, and all of the staff and PhD students at *Laboratoire d'Informatique, Robotique et Microelectronique de Montpellier* (LIRMM), I'm grateful for the collaboration opportunity in 2011 at this important research institution that contributed with important knowledge for part of this PhD thesis.

To Paolo Rech, who has shown to be a sincere friend during the bilateral collaboration projects at LIRMM in 2011 and at *Universidade Federal do Rio Grande do Sul* (UFRGS) in 2013.

To my friends Joaquim Detoni, Pedro Gusmão, and Balbina Mrozkiewicz, who have also undertaken the challenge of studying and living in Italy. I'm grateful for their friendship that helped me face this challenge with perseverance during 7 years living in Turin.

I'm thankful for all the sincere friends I made in Italy during my Master and PhD studies, that shared my suffering from the difficulty of living abroad, sometimes taking me to hospitals or lending money whenever needed, and also sharing pleasant times.

Last but not least, my immense gratitude for all of those that waited selflessly patient while I was unavailable working on my PhD: my mother Cleci, my father Robson, my brother Felipe, my girlfriend Camila, my aunts, my cousins, and all of my undergraduation and high school friends that were always helping me in some form.

## Contents

| Al | ostrac  | et e                                                                     | II  |

|----|---------|--------------------------------------------------------------------------|-----|

| A  | cknov   | vledgments                                                               | III |

| Li | st of l | Figures                                                                  | VII |

| Li | st of ' | Tables                                                                   | X   |

| Li | st of l | Publications                                                             | XI  |

| In | trodu   | action                                                                   | XII |

| Ι  | Ba      | ckground                                                                 | 5   |

| 1  | Reli    | ability on Semiconductor Devices                                         | 6   |

|    | 1.1     | Reliability Characterization                                             | 7   |

|    | 1.2     | Defect, Fault, Errors, and Failures                                      | 8   |

|    |         | 1.2.1 Defects                                                            | 8   |

|    |         | 1.2.2 Faults                                                             | 9   |

|    | 1.3     | Fault Models                                                             | 9   |

|    | 1.4     | Testing semiconductor devices                                            |     |

|    |         | 1.4.1 Functional vs. Structural Tests                                    |     |

|    |         | 1.4.2 Manufacturing, Incoming, and On-line Testing                       |     |

|    | 1.5     | Reliability Requirement Standards for High Reliable Electronic Systems . | 15  |

| 2  |         | e-of-the-Art testing and diagnosis                                       |     |

|    | effo    |                                                                          | 17  |

|    | 2.1     | System-On-Chip                                                           |     |

|    | 2.2     | CPU                                                                      |     |

|    | 2.3     | Memories                                                                 |     |

|    | 2.4     | Graphic Processing Units                                                 |     |

|    | 2.5     | Other literature                                                         |     |

|    |         | 2.5.1 Functional Test Pattern Generation                                 | 23  |

|    |      | 2.5.2   | Power Consumption of Embedded CPU cores during Testing         | 24 |

|----|------|---------|----------------------------------------------------------------|----|

| II | Er   | nbedd   | ed Memory Diagnosis                                            | 26 |

| 3  | Proj | posed M | Iemory Diagnosis                                               | 27 |

|    | 3.1  | Cumul   | ative Memory Analysis                                          | 27 |

|    |      | 3.1.1   | Memory Diagnosis Background                                    | 28 |

|    |      | 3.1.2   | Proposed Analysis Flow                                         | 30 |

|    |      | 3.1.3   | Experimental Results                                           | 37 |

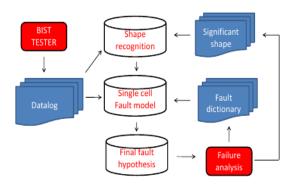

|    | 3.2  | _       | ized Memory Analysis                                           | 40 |

|    |      | 3.2.1   | Proposed Optimized Flow                                        | 41 |

|    |      | 3.2.2   | Failure shape recognition and completion                       | 42 |

|    |      | 3.2.3   | Single cell fault model recognition                            | 44 |

|    |      | 3.2.4   | Final fault hypothesis                                         | 47 |

|    |      | 3.2.5   | Cases of Study and Results                                     | 48 |

|    | 3.3  | Remar   | ks on Memory Diagnosis                                         | 51 |

| II | I F  | unctio  | onal Test Pattern Generation                                   | 52 |

| 4  | _    |         | unctional Stress Pattern                                       |    |

|    | Gen  | eration |                                                                | 53 |

|    | 4.1  |         | round on stress                                                |    |

|    |      | 4.1.1   | Functional stress quality evaluation metrics                   | 55 |

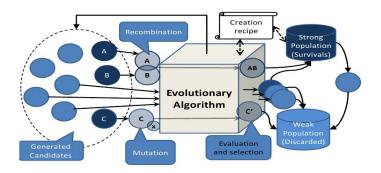

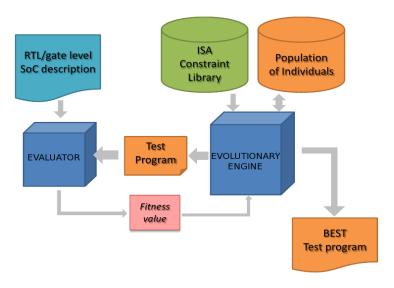

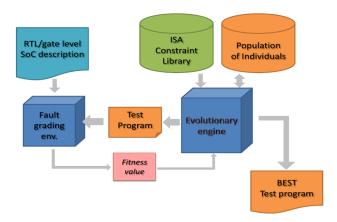

|    | 4.0  | 4.1.2   | Functional Program Generation using Evolutionary Algorithm     | 56 |

|    | 4.2  |         | sed Approach                                                   |    |

|    |      | 4.2.1   | Phase 1 Fast stress pattern generation at RTL                  | 57 |

|    | 4.2  | 4.2.2   | Phase 2 Initial stress qualities refinement at gate-level      | 58 |

|    | 4.3  |         | tudy and results                                               | 59 |

|    | 4.4  | Concil  | usions on Functional Stress Patterns                           | 63 |

| 5  | _    |         | unctional Power Hungry<br>neration                             | 64 |

|    | 5.1  |         | round on Power Consumption                                     | 66 |

|    | 5.2  | _       | sed Methodology                                                | 68 |

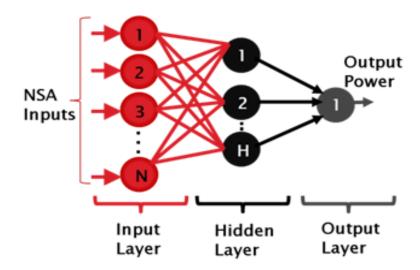

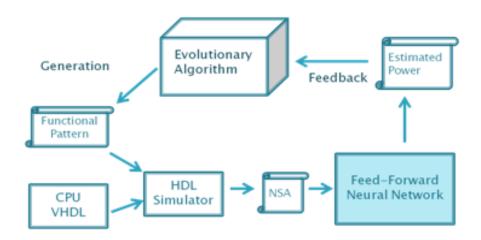

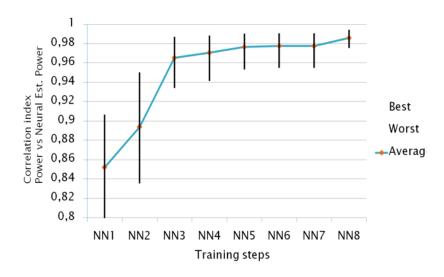

|    | 5.2  | 5.2.1   | FFNN Training Strategy                                         | 70 |

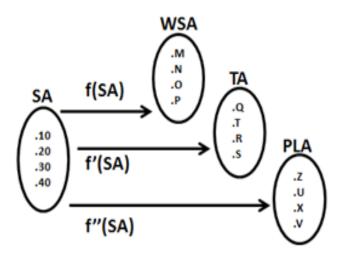

|    |      | 0.2.1   | 5.2.1.1 Sum SA Within the Clock Cycle                          | 71 |

|    |      |         | 5.2.1.2 The NSA Value                                          | 71 |

|    |      |         | 5.2.1.3 FFNN for Power Estimation                              | 72 |

|    |      |         | 5.2.1.4 FFNN Training Methodology                              | 74 |

|    |      | 5.2.2   | Increasing functional Peak Power Using the Trained FFNN as the |    |

|    |      |         | fast Power Estimator                                           | 76 |

|    | 53   | Case S  |                                                                | 76 |

|    |              | 5.3.1    | Intel 8051                                                   | 77  |

|----|--------------|----------|--------------------------------------------------------------|-----|

|    |              | 5.3.2    | Glitch and Valid Transition Constant Assignment for NSA Com- |     |

|    |              |          | putation                                                     | 77  |

|    |              | 5.3.3    | FFNN and Parameters                                          | 77  |

|    | 5.4          |          | 8                                                            | 78  |

|    |              | 5.4.1    | Training Trend                                               | 79  |

|    |              | 5.4.2    | The Computed Gate Type Weights                               | 80  |

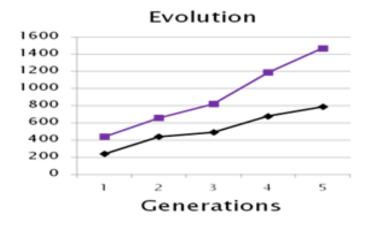

|    |              | 5.4.3    | Increasing functional Peak Power Evolution                   | 80  |

|    |              | 5.4.4    | Performance                                                  | 82  |

|    | 5.5          | Conclu   | sions                                                        | 83  |

| 6  | Prop         | osed SI  | BST Pattern                                                  |     |

|    | _            | eration  |                                                              | 85  |

|    | 6.1          | Autom    | atic and Manual SBST Pattern Generation                      | 85  |

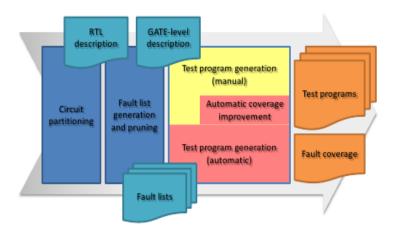

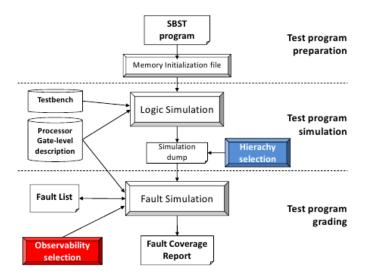

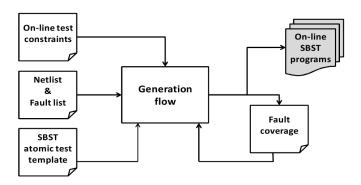

|    |              | 6.1.1    | Proposed SBST Program Generation Framework                   | 87  |

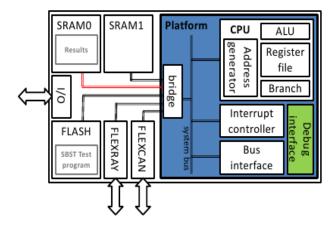

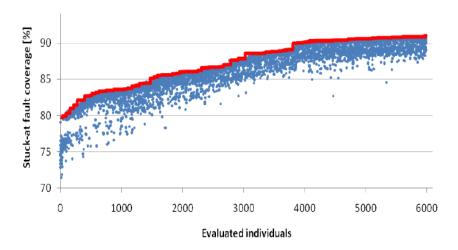

|    |              | 6.1.2    | Case Study                                                   | 90  |

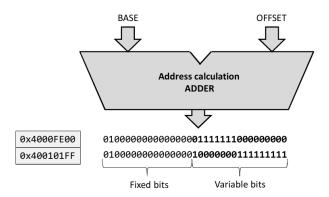

|    | 6.2          | On-line  | e Fault Coverage of the Address Calculating Unit             | 92  |

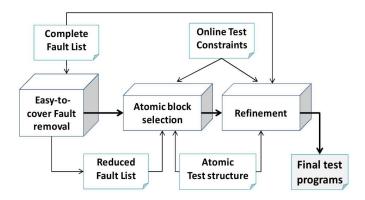

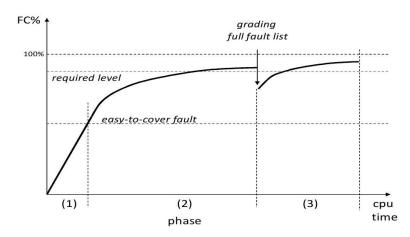

|    |              | 6.2.1    | Proposed SBST Generation Approach                            | 93  |

|    |              | 6.2.2    | Case studies and Results                                     | 100 |

|    |              | 6.2.3    | Conclusions                                                  | 102 |

|    | 6.3          | Increas  | sing Fault Coverage of CPUs During On-line Functional Test   | 102 |

|    |              | 6.3.1    | Background                                                   |     |

|    |              | 6.3.2    | Definition of the Problem                                    | 107 |

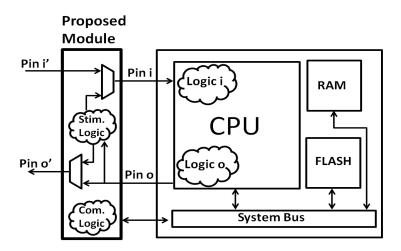

|    |              | 6.3.3    | Proposed Solution                                            | 108 |

|    |              |          | 6.3.3.1 Proposed Framework                                   | 108 |

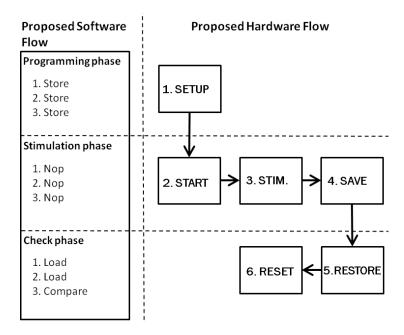

|    |              |          | 6.3.3.2 Hardware and Software Integration flow               |     |

|    |              |          | 6.3.3.3 Detailed hardware architecture                       |     |

|    |              |          | 6.3.3.4 Detailed Methodology                                 | 112 |

|    |              | 6.3.4    | Case Studies and Results                                     | 113 |

|    |              | 6.3.5    | Remarks on SBST for HFT coverage                             | 119 |

|    |              |          |                                                              |     |

| IV | 7 <b>F</b> : | ault In  | jection in GPGPU cores                                       | 121 |

| 7  | Prop         | osed G   | PGPU Fault Injection tool                                    | 122 |

|    | 7.1          |          | ound                                                         | 123 |

|    | 7.2          | Propos   | ed Approach                                                  | 126 |

|    | 7.3          | _        | tudies and Results                                           |     |

|    | 7.4          | Conclu   | sions on GPGPU fault injection                               | 133 |

| 8  | Con          | clusions |                                                              | 135 |

|    |              |          |                                                              |     |

| Re | feren        | ces      |                                                              | 138 |

# List of Figures

| 1.1<br>1.2 | Bathtub curve                                                                     |  |  |  |  |

|------------|-----------------------------------------------------------------------------------|--|--|--|--|

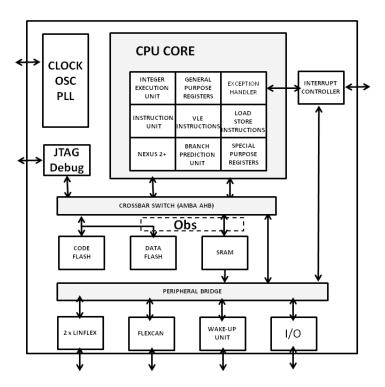

| 2.1        | SoC Architecture                                                                  |  |  |  |  |

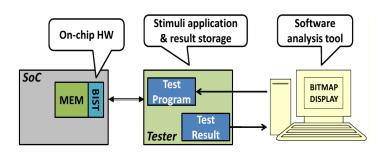

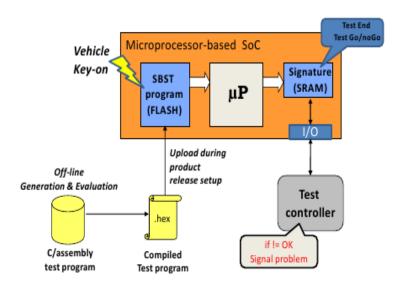

| 2.2        | Embedded CPU under SBST testing                                                   |  |  |  |  |

| 2.3        | EA: Optimization of a population                                                  |  |  |  |  |

| 2.4        | 1 1 1                                                                             |  |  |  |  |

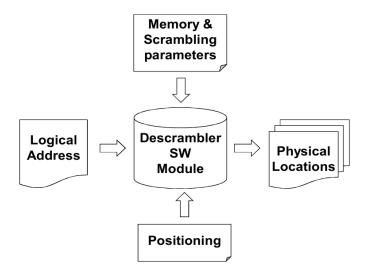

| 3.1        | Memory diagnosis flow components                                                  |  |  |  |  |

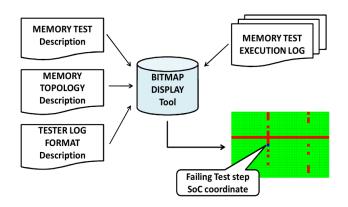

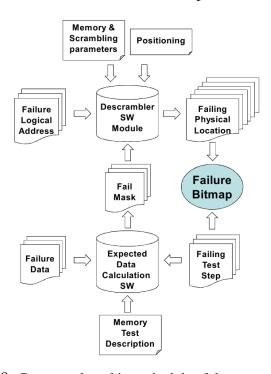

| 3.2        | Conceptual view for Bitmap Display tool                                           |  |  |  |  |

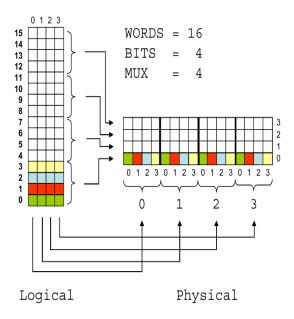

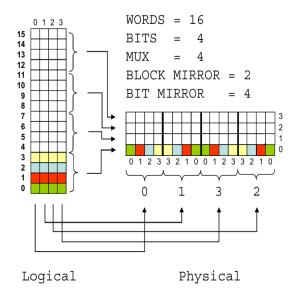

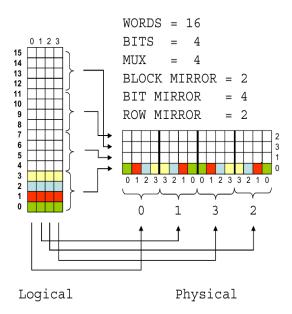

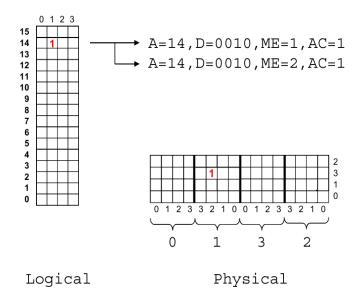

| 3.3        | Basic mapping between logical and physical SRAM view                              |  |  |  |  |

| 3.4        | Memory view with block and bit mirrors                                            |  |  |  |  |

| 3.5        | Memory logical to physical view with all mirrors                                  |  |  |  |  |

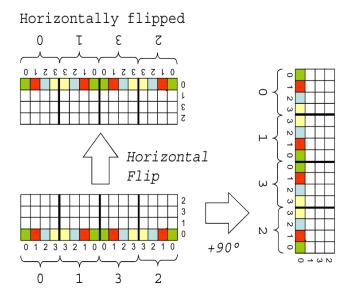

| 3.6        | Rotated and flipped SRAM configurations                                           |  |  |  |  |

| 3.7        | Address translation process                                                       |  |  |  |  |

| 3.8        | BIST responses and logical-physical fault location                                |  |  |  |  |

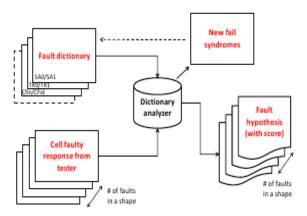

| 3.9        | Conceptual working principle of the proposed framework                            |  |  |  |  |

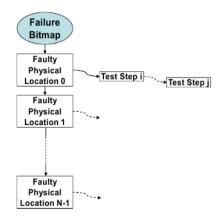

| 3.10       | Failure bitmap data structure                                                     |  |  |  |  |

| 3.11       | Example with pair and rows                                                        |  |  |  |  |

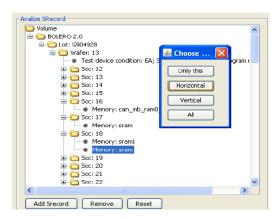

| 3.12       | (A) single (B) horizontal and (C) vertical cumulative analysis                    |  |  |  |  |

| 3.13       | Memory classification tree                                                        |  |  |  |  |

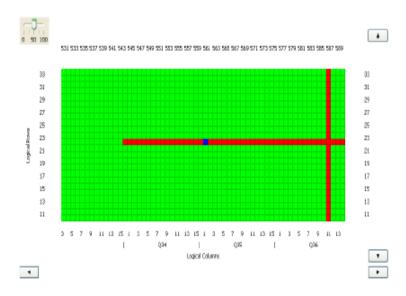

| 3.14       | Failure bitmap display window                                                     |  |  |  |  |

| 3.15       | Identified defective mechanism, a stuck-open fault                                |  |  |  |  |

| 3.16       | Proposed diagnosis flow                                                           |  |  |  |  |

| 3.17       | Bitmap with a partial row and a column shaped failures                            |  |  |  |  |

| 3.18       | (a) failure bitmap corrupted by noise and (b) intermittent fault effect           |  |  |  |  |

| 3.19       | logical hypothesis produced by comparing the gathered syndrome with known         |  |  |  |  |

|            | fault type responses                                                              |  |  |  |  |

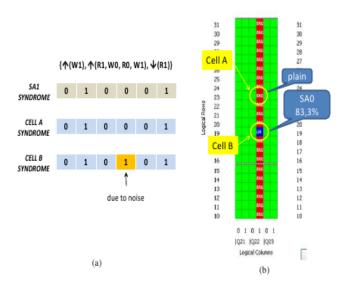

| 3.20       | Noisy test environment affecting fault model selection: in (a) the March test     |  |  |  |  |

|            | executed and a comparison within expected and obtained syndromes, in (b) the      |  |  |  |  |

|            | shape of the failure including fault model hypothesis                             |  |  |  |  |

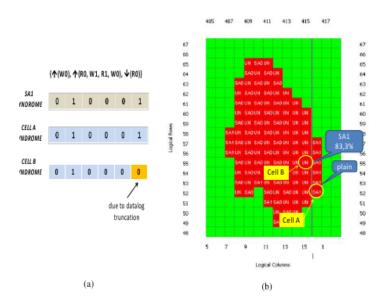

| 3.21       | Effect of data truncation; in (a) the March test executed and a comparison within |  |  |  |  |

|            | expected and obtained syndromes, in (b) the shape of the failure including fault  |  |  |  |  |

|            | model hypothesis                                                                  |  |  |  |  |

|      | Pair defect: logical and physical appearance of the faulty array According to the illustrated flow and without any correction | 49  |

|------|-------------------------------------------------------------------------------------------------------------------------------|-----|

|      | An irregular cluster showing many physical defects                                                                            | 50  |

|      | A regular cluster showing a composite logical hypothesis                                                                      | 50  |

| 3.25 | An irregular cluster showing a composite logical hypothesis                                                                   | 51  |

| 4.1  | Proposed approach; (a) Generation flow, (b) Decision making process                                                           | 57  |

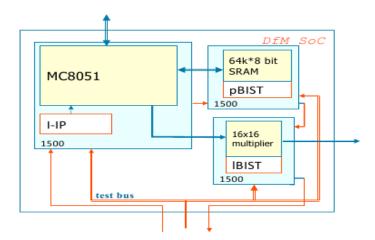

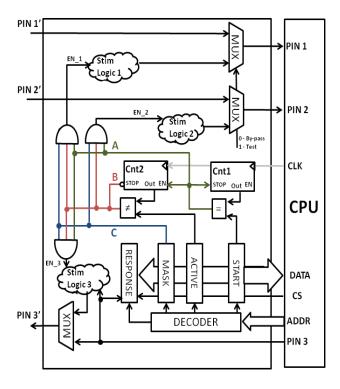

| 4.2  | Block diagram of the test-chip                                                                                                | 60  |

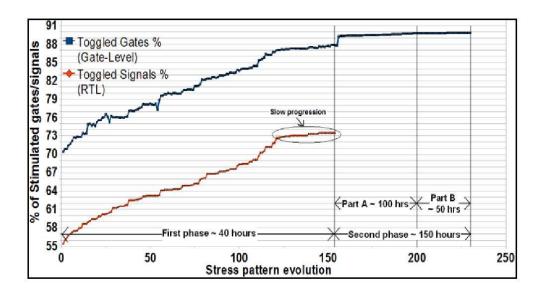

| 4.3  | Stimulated gates in evolution of the MEM                                                                                      | 60  |

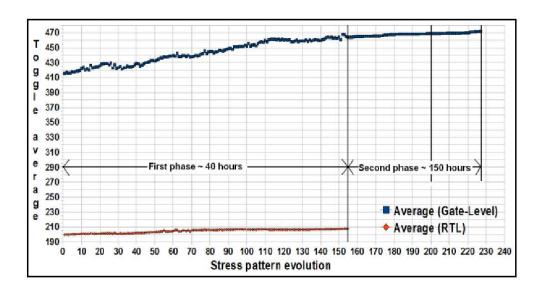

| 4.4  | AVG(TDMEM) evolution                                                                                                          | 61  |

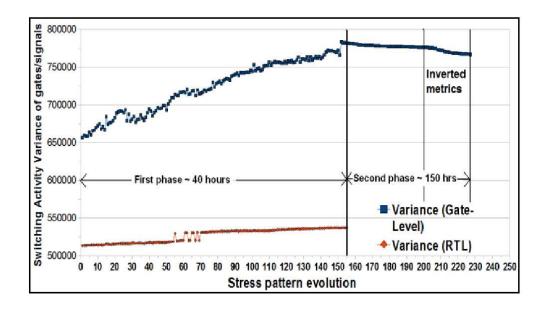

| 4.5  | VAR(TDMEM) evolution                                                                                                          | 62  |

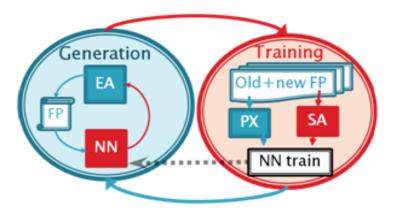

| 5.1  | Automatic functional pattern generation framework                                                                             | 69  |

| 5.2  | Matching SA pattern to WSA, TA and PLA power consumption                                                                      | 70  |

| 5.3  | Artificial intelligence feed-forward neural network.                                                                          | 73  |

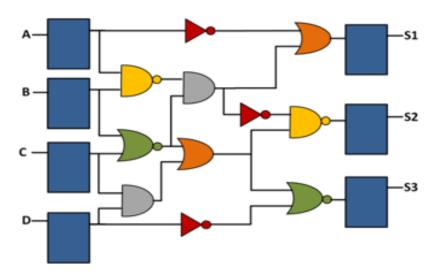

| 5.4  | A sample circuit with different gate types                                                                                    | 74  |

| 5.5  | 2-phase strategy to train the FFNN                                                                                            | 75  |

| 5.6  | Evolution curve to extract individuals                                                                                        | 75  |

| 5.7  | Final framework including the FFNN as the fast power estimator                                                                | 76  |

| 5.8  | 8051 Training trend                                                                                                           | 80  |

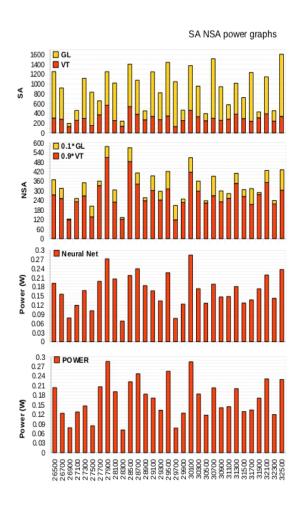

| 5.9  | SA, NSA, FFNN power estimation and power evaluation of a sample program                                                       | 81  |

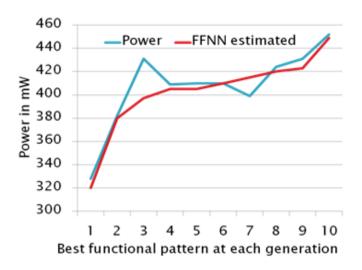

| 5.10 | Peak power evolution                                                                                                          | 82  |

| 6.1  | Conceptual representation of the in-field self-test procedure execution                                                       | 86  |

| 6.2  | Conceptual view of the proposed integrated test generation framework                                                          | 87  |

| 6.3  | Automatic SBST Pattern Generation framework                                                                                   | 88  |

| 6.4  | Fault Grading Environment                                                                                                     | 89  |

| 6.5  | SoC architecture with hierarchy selection (in blue), observability selection (in                                              |     |

|      | red) and one of the untestable fault pruning zones (in green)                                                                 | 91  |

| 6.6  | Evolution of test program fault coverage during automated program generation                                                  |     |

|      | for the adder module; each blue point represents an evaluated individual, while                                               |     |

|      | the red line traces the generation best individuals                                                                           | 91  |

| 6.7  | Conceptual view of the proposed generation approach                                                                           | 93  |

| 6.8  | Effect of address range selection for address calculation adder test                                                          | 95  |

| 6.9  | Atomic block pseudo-code                                                                                                      | 97  |

| 6.10 | Proposed framework for on-line testing                                                                                        | 98  |

| 6.11 | Fault coverage general trend along the generation process                                                                     | 99  |

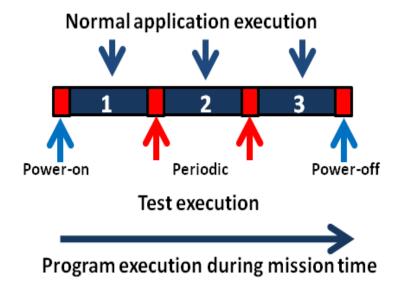

| 6.12 | Test scheduling during the operational-phase                                                                                  | 106 |

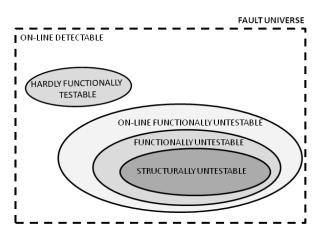

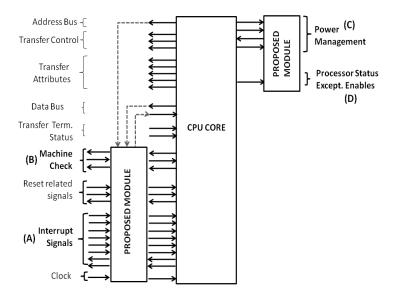

| 6.13 | On-line fault universe and relationship among categories                                                                      | 107 |

|      | Proposed framework                                                                                                            | 109 |

| 6.15 | Proposed hardware-software integration flow                                                                                   | 110 |

| 6.16 | Proposed architecture                                                                                                         | 112 |

| 6.17 | Target platform                                                                                                               | 114 |

LIST OF FIGURES LIST OF FIGURES

| 6.18 | Detailed interconnection scheme between the target device and the proposed  |

|------|-----------------------------------------------------------------------------|

|      | module                                                                      |

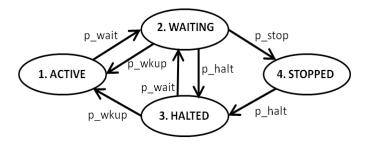

| 6.19 | Power states                                                                |

|      |                                                                             |

| 7.1  | A Simplified GPGPU Architecture                                             |

| 7.2  | A Simplified SMX Architecture                                               |

| 7.3  | Architecture of the proposed fault injector                                 |

| 7.4  | Representation of the 64-bit double floating point number                   |

| 7.5  | Fault Injection Environment                                                 |

| 7.6  | C code embedding a CUDA code and the possible fault injection points in the |

|      | GPGPU application                                                           |

## List of Tables

| 1.1 | Types of tests in semiconductor devices                              |

|-----|----------------------------------------------------------------------|

| 4.1 | Final results obtained for each SoC module                           |

| 5.1 | Power evaluation methods                                             |

| 5.2 | 8051 characteristics                                                 |

| 5.3 | Correlation indexes comparison                                       |

| 5.4 | Gate type characteristics and computed weights                       |

| 5.5 | Time consumption of each tool                                        |

| 5.6 | CPU time requirements                                                |

| 6.1 | Results of SBST program generation on some microprocessor modules 92 |

| 6.2 | Stuck-at Fault Coverage Percentual Obtained Along the Flow 101       |

| 6.3 | Stuck-at Fault Coverage for different atomic block/memory configura- |

|     | tions for case study 2 (before refinement)                           |

| 7.1 | Classification of faults affecting GPGPUs                            |

| 7.2 | List of the parsed information needed to inject a fault              |

| 7.3 | Matrix Multiplication results                                        |

| 7.4 | FFT results                                                          |

#### List of Publications

- De Carvalho M., Sabena D., Sonza Reorda M., Sterpone L., Rech P., Carro L. (2014)

*Fault Injection in GPGPU Cores to Validate and Debug Robust Parallel Applications*.

In: IEEE 20th International On-Line Testing Symposium (IOLTS), Platja d'Aro, July 7 9, 2014. pp. 210-211

- 2. **M. De Carvalho**,P. Bernardi,E. Sanchez,M. Sonza Reorda,O. Ballan (2014) *Increasing the Fault Coverage of Processor Devices during the Operational Phase Functional Test*. In: JOURNAL OF ELECTRONIC TESTING THEORY AND APPLICATIONS, April, 2014 vol. 30, pp. 317-328. ISSN 0923-8174

- 3. **M. De Carvalho**, P. Bernardi, E. Sanchez, M. Sonza Reorda, A. Bosio, L. Dilillo, M. Valka, P. Girard (2013) *Fast Power Evaluation for Effective Generation of Test Programs Maximizing Peak Power Consumption*. In: JOURNAL OF LOW POWER ELECTRONICS, vol. 9, pp. 253-263. ISSN 1546-1998

- 4. **M. De Carvalho**, P. Bernardi, E. Sanchez, M. Sonza Reorda, O. Ballan (2013) *Increasing fault coverage during functional test in the operational phase*. IEEE 19th International On-Line Testing Symposium (IOLTS) 2013. pp. 43-48

- P. Bernardi, L. Ciganda, M. De Carvalho, M. Grosso, J. Lagos-Benites, E. Sanchez, M. Sonza Reorda, O. Ballan (2012) On-Line Software-Based Self-Test of the Address Calculation Unit in RISC Processors. In: IEE 17th European Test Symposium (ETS).

- 6. P. Bernardi, M. De Carvalho, E. Sanchez, M. Sonza Reorda, A. Bosio, L. Dilillo, P. Girard, M. Valka (2012) *Peak Power Estimation: A Case Study on CPU Cores*. In: IEEE 21st Asian Test Symposium. pp. 167-172

- 7. M. Valka, A. Bosio, L. Dilillo, P. Girard, S. Pravossoudovitch, A. Virazel, E. Sanchez, M. De Carvalho, M. Sonza Reorda, (2011) *A Functional Power Evaluation Flow for Defining Test Power Limits during At-Speed Delay Testing*. In: IEEE 16th European Test Symposium (ETS). pp. 153-158

- 8. **M. De Carvalho**, P. Bernardi, M. Sonza Reorda, N. Campanelli, T. Kerekes, D. Appello, M. Barone, V. Tancorre, M. Terzi (2011). *Optimized embedded memory diagnosis*. In: IEEE 14th International Symposium on Design and Diagnostics of Electronic Circuits & Systems (DDECS). pp. 347-352

- 9. Campanelli N., Kekeres T., Bernardi P., **De Carvalho M.**, Panariti A., Sonza Reorda M., Appello D., Barrone M. (2010) *Cumulative embedded memory failure bitmap display & analysis*. In: 2010 IEEE 13th International Symposium on Design and Diagnostics of Electronic Circuits and Systems (DDECS), Vienna (Autria), 14-16 April 2010. pp. 255-260

- 10. **De Carvalho M.**, Bernardi P., Sanchez E., Sonza Reorda M. (2010) *An enhanced strategy for functional stress pattern generation for system-on-chip reliability characterization*. In: 11th International Workshop on Microprocessor Test and Verification 2010, Austin (USA), 13-15 December 2010.

#### Introduction

Everyday we rely on many different technological appliances for our well-being, ranging from mobility (cars, planes, etc) to commodities (cellphones, tablets, etc). From time to time, the capitalist market demand even smaller devices with enhanced features outperforming its ancestor. In order to be time and cost effective attending the urgent demand, it is more convenient to constantly decrease semiconductor technology, allowing integrating macro discrete components on a single micro device made of silicon, namely *microchip*.

Since the first manufactured microchip in 1958 [1], semiconductor manufacturing technology (capability of producing the smallest conducting line width) has scaled according to Moore's Law, from 600nm to 22nm (2012) [2]. Moore predicted that the number of transistors (the smallest working component in digital chips) doubled every 18 or 24 months. Nowadays, Very Large Scale Integration (VLSI) technology can place upto billions of transistors on a single die, only achievable thanks to the standard cell library design used by the VLSI method. In practice, it can integrate a full working computer composed of one or more Central Processing Units (CPU cores), many peripherals, different memory cores (SRAM, DRAM, ROM, FLASH), and other processing units like: Digital Signal Processing Units (DSP) and Graphic Processing Units (GPU). Often, these embedded modules are bought from specific Intellectual Property (IP) vendors that rarely provide the design hardware description code, thus, increasing even more test complexity; test pattern generation and application. Restrict embedded modules have restrict specific test application parameters, which makes silicon validation a challenging task for test engineers that must elaborate a correct and effective testing scheme in a suitable time. Testing comprises not only on developing reliability tools, but also programming creative and effective test patterns and guaranteeing the device's functions integrity according to specifications, often in off-line and on-line modes. Therefore, after 60 years of technology scaling, chips reaching to technology dimension limits tied to architecture complexity, Integrated Circuit (IC) manufacturers observed a reliability loss in their products. In such context, test and diagnosis has been thoroughly studied to improve test coverage and application as well as fault analysis and consequently aiding on manufacturing processes for improving product quality, yield, and reducing material costs.

Moreover, the development cost per transistor decreased over the years due to technology scaling. On the other hand, architecture complexity of semiconductor devices increased overall test cost. More specifically, complex miniaturized devices requires more

test time, specific hardware and software tools, qualified test engineers, and specialized equipments, i.e. Automatic Test Equipments (ATE) contributing on test costs. In order to be cost effective, IC manufacturers and research institutes proposed embedded test modules in the device itself. Rather than increasing the ATEs functions and performance, it was more convenient increasing chip area by introducing test structures capable of improving test coverage and performance during manufacturing tests. Several *Design-for-Testability* (DfT) on-silicon structures have become IC industry standards, like: *Scan-chain design*, *Software-Based Self-Test*, *Built-in Self Test*, *Memory Built-in Self-Test*, and *Boundary Scan design*. They basically aid on test digital modules, since analog designs are still crafted manually by back-end designers and do not benefit from standard methods.

The invasive effect of embedding IC's on everyday appliances also reached safety-critical automotive and aerospace applications. However, several automotive catastrophic failures occurred as an immediate counter-effect of this phenomenon, concerning authorities. As a response to these incidents, car manufacturers proposed the ISO26262 functional safety standard for road vehicles [3] demanding a number of auditing E/E processes increasing test strictness for improving reliability. In practice, all the ICs controlling critical parts (i.e. *Anti-Block Brake System* (ABS), *Electronic Power Steering* (EPS) controller, and *Suplemental Restraint System* controller (SRS) the popular Airbag) need to be strictly tested during manufacturing tests and constantly tested during on-line tests, in order guarantee reliability and consequently mission safety.

Reliability is the keyword that motivates the development of this PhD. thesis because technology is rapidly diffused throughout the world in a fast competitive market where failures are unacceptable, especially for systems employed in safety critical missions like automotive, medical, and aerospace applications. Therefore, reliability engineering was developed to provide tools to understand and correct mistakes in manufactured devices throughout all of their life phases:

- 1. Early-life: before shipping the component to the client

- 2. Operational useful life: when the component is being used in mission by a consumer

- 3. Ageing or Wear-out: when the physical structure is compromised by plastic stress carried out through operational life and defects start to appear causing failures

This PhD. thesis is made of four parts encompassing test and diagnosis techniques to attend high reliability levels of automotive SoCs and GPUs demanded by the ISO26262 standard. Initially, reliability concepts and state-of-the-art testing and diagnosis literature are described. Then, the proposed methods are thoroughly detailed: Embedded memory diagnosis, Functional Test Pattern Generation for embedded CPUs, and GPU Fault Injection tool for validating robust parallel applications.

This PhD. thesis is structured as follows:

Part I is composed of two chapters encompassing background on reliability concepts and state-of-the-art literature on testing and diagnosis of hardware modules embedded in SoCs:

In Chapter 1, the main concepts of "Reliability" applied to semiconductor devices are detailed. It mainly describes most of the mature testing and diagnosis procedures of microelectronic devices from early-life to end-of-life in order to achieve high reliability levels. Finally, functional safety standards for high reliable electronic components are described.

In Chapter 2, "State-of-the-Art test and diagnosis efforts" found in the literature are reported. This chapter allows understanding the knowledge barrier on new CMOS architectures testing methodologies, their weaknesses, and solution that need to be adopted in order to cover insurgent issues.

Part II composed of chapter 3 explains the "Embedded Memory diagnosis" proposed solutions aiming at improving failure analysis and locate root cause defects arising from manufacturing errors. Embedded memories are the most dense devices inside SoCs and usually present a high defect level rate. Nonetheless, they are used in the final product because there are several mechanisms for memory array correction, which is transparent to the functional mode. In this chapter, a proposed java tool is described. It has the capability of analyzing test data and applying two diagnosis techniques for better understanding the memory defects:

- Cumulative Memory Analysis; first reconstructing physical memory representation from the logical one, then visualizing defect locations in the memory array by analyzing test results

- Optimized Memory Analysis; from the test results (either full or partial), the method is able to map failing syndromes of known locations to fault models based on a cumulative fault dictionary

In Part III, this PhD. thesis proposes three methods for "Functional test pattern generation of embedded CPUs" in SoCs. Usually, functional pattern generation is a time consuming task, thus in order to be time efficient, we propose manual and automatic generation approaches aiming at:

- Chapter 4: Increasing workload stress for improving *Operational-Life Tests* and *Screening*

- Chapter 5: Increasing functional peak power for limiting power during structural testing, thus avoiding circuit over-killing

- Chapter 6: Increasing functional coverage during the functional test operational phase.

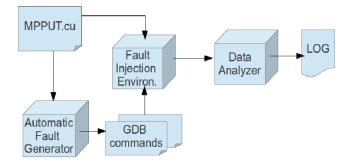

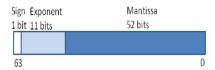

Part IV is composed of Chapter 7 describing the benefits of a proposed "Fault injection tool for validating robust *General Purpose Graphic Processing Units* (GPGPU) programs" used in safety-critical applications. Automotive GPGPU applications require the practices of software robustness even when running on robust hardware. However, validating robust GPGPU applications is a challenging task, since the application engineer does not own the GPGPU design and resorts to costly and time consuming radiation tests. Thus, in this chapter we propose a cheap and fast GPGPU fault injection mechanism able to corrupt applications, by inserting bit flips in strategic places to emulate *Single Event Transient* (SET) and *Single Event Upset* (SEU). In particular, we propose to use the tool to validate robust GPGPU applications, thus activating redundant techniques they possibly embed and observing fault propagation.

In Chapter 8, "Conclusions" are drawn.

In Chapter 9, "References" used in this thesis are listed.

# Part I Background

### 1. Reliability on Semiconductor Devices

This chapter describes reliability elements: reliability characterization, defects to failures, fault models, test types, test patterns, and finally the negative consequences of tests.

Reliability is the characteristic of an item, expressed by the probability that the item will perform its required function under given conditions for a stated time interval. From a qualitative point of view, reliability can be defined as the ability of an item to remain functional. Quantitatively, reliability specifies the probability that no operational interruptions will occur during a stated time interval. This does not mean that redundant parts may not fail, such parts can fail and be repaired (without operational interruption at system level). The concept of reliability thus applies to non-repairable as well as to repairable items. To make sense, a numerical statement of reliability must be accompanied by the definition of the required function, the operating conditions, and the mission duration. In general, it is also important to know whether or not the item can be considered new when the mission starts. An item is a functional or structural unit of arbitrary complexity that can be considered an entity for investigations. It may consist of hardware, software, or both and may also include human resources. Often, ideal human aspects and logistic support are assumed even if the term system is used instead of technical system.

For the microelectronics area, the reliable item must be a hardware system composed by countless different transistors whose transitions, when interleaved, perform a desired operation. This functional operation must be correct or corrected in time to be acceptable for a system user throughout a stated time interval under given conditions. Thus the whole system's reliability is dependent on its weakest component.

The proper definition of *reliability* stated by the IEEE standard dictionary [4] is:

"The ability of a system or component to perform its required functions under stated conditions for a specific period of time"

Reliability can be mathematically expressed as:

$$R(t) = e^{-\lambda t} \tag{1.1}$$

where: R is the reliability of a component working properly as a function of time t.  $\lambda$  is the constant failure rate extracted from a population of the same device.

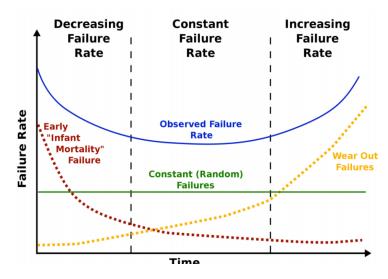

From a statistical point of view, exponential distributions are best suited to represent the reliability of a device when the failure rate is constant [5]. However, the failure rate is not constant throughout different life phases. In this case, the reliability of a given device changes in three life phases: Early-life, useful-life, and end-of-life. The bathtub curve drawn in Figure 1.1 shows this variation: In Early-life, the failure rate  $\lambda$  is high but decreasing, resulting on a large amount of *infant-mortality* components. Then, on the useful-life phase, the failure rate is relatively low and constant, that's where equation 1 applies. In this phase, the component is being used in applications during operational mission mode. Finally, the last phase is where components start presenting problems due to wear-out, and  $\lambda$  is low but increasing. Analogously, these life phases happen on living organisms: they born, live, and die.

Figure 1.1: Bathtub curve

#### 1.1 Reliability Characterization

Reliability characterization of semiconductor devices provides reliability and electrical measurements relevant to determine the physical failure rate throughout the component's entire life-cycle. It is fundamental to understand the accuracy and qualification of the advanced materials being used and the device's manufacturing processes adopted. This is very important on devices that work on critical environments like aerospace and automotive ones.

The purpose of *reliability characterization* is to develop methods and tools to evaluate and demonstrate reliability, maintainability, availability, and safety components, equipment, and systems, as well as to support development and production engineers in building these characteristics [6][7][8][9]. In order to be cost and time effective, reliability

engineering must be integrated in project activities, and support quality assurance and concurrent engineering efforts.

Thus, reliability characterization also targets the correct definition and reducing of failure rates in order to keep high quality in systems by keeping them reliable, maintainable, available, safe, and confidential.

#### 1.2 Defect, Fault, Errors, and Failures

The design process VLSI semiconductor devices depend on the effort of many engineers and technicians. A design becomes a physical device after manufacturing processes are performed that accounts on several tasks and materials in order to become the final product. In general, in a manufacturing lot, a single design is replicated several times during the manufacturing process such that costs are reduced. In most cases, process variations and fabrication mistakes (i.e. air impurities, mask misalignment, bad process tuning, and etc) make twin devices different one from another. They can be slightly different producing the desired outputs or not. In the latter case, the final product had a defect introduced by some source that modified the physical structure, permanent or temporary, producing a fault that may be perceived as an error by other logic and possibly resulting into a system failure, not working as it should, if propagated to the primary outputs. So, the logic is: Defects produce faults that may or may not produce a function error that will propagate to the output provoking or not a system failure.

#### 1.2.1 Defects

According to [10], **defect** in electronic systems is defined as:

"An unintended difference between the implemented hardware and its intended physical design."

A defect can be an impurity on the silicon structure connecting a wire to a voltage source, or ground as well as other wires resulting on a permanent erroneous behaviour. Usually, in VLSI devices, they cannot be mapped to a single fault, as they may produce different behaviours. For example, a microscopic misplaced metal particle connecting an output to a voltage source produces a stuck-at-1 (stuck-at-high), while if connected to ground, the output results on a stuck-at-0 (stuck-at low). Although it is the same defect, a misplaced metal fragment, it produces different situations resulting different faulty behaviors. For this reason, defects cannot be directly mapped into specific faults.

Moreover, there are specific malformed structures that are translated into transition delay defects. That is, cases like high metal resistivity or missing contacts may produce slow transitions, making a signal work as expected but slower. For this situation, there are

Chapter 1 1.3. Fault Models

two types of behaviour stemmed from transition delay defects: Slow-to-rise and slow-to-fall. The signal is able to switch from one logic level to another, but in a longer time than specified. If the delay is high enough, then the logic reading the value can perceive as a stuck-at fault as mentioned above.

Another situation that may happen, defects may be induced by some other source coming from the environment like: radiation particles, magnetic fields, high or low temperatures, and physical stress. In this case, the defect is transient and solely modifies the physical structure (or its functioning) momentarily, just enough to produce a transient fault or not, as explained in the first paragraph of this section.

The most common defects are:

- 1. Process Defects: missing contact windows, parasitic transistors, oxide break-down, etc.

- 2. Material Defects: bulk defects (cracks, crystal imperfections), surface impurities, etc.

- 3. Age Defects: dielectric breakdown, electromigration, etc.

- 4. Package Defects: contact degradation, seal leaks, etc.

- 5. Environment-induced Defects: radiation particles, humidity, vibrations, etc.

#### **1.2.2** Faults

Faults arise from defects and there is not a precise direct mapping from one to another, as explained in the last subsection. According to [10], the definition of **fault** is:

A representation of a defect at the abstracted function level

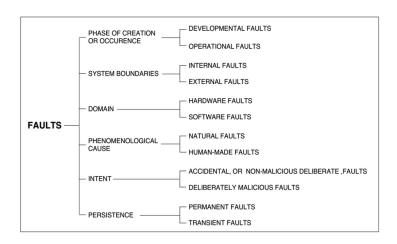

In addition, a small set of faults can represent a large set of defects. In practice, there are more defects than faults, thus a single fault can be represented by different types of defects. However, defects can only be detected but not accurately identified by analyzing the faulty behaviour of the logic. The possible listed faults observed in the past years has been classified by Avizienis et al. [6] and is shown in figure 1.2.

#### 1.3 Fault Models

In engineering, complex projects are primarily modelled then simulated before actually being produced. Modelling refers to developing an approximation of a real item, whereas simulation is the action of stimulating the model with inputs (derived manually from specifications) and observe the functional behavior. Thus, simulating models allows correcting or improving the design before being actually manufactured.

Chapter 1 1.3. Fault Models

Figure 1.2: Fault classification

Models bridge the gap between the physical reality and mathematical abstraction [10]. They allow the development and application of analytical tools. They are thus essential in design. The most important models in testing are those of faults.

Fault models are engineering models of a failing transistors, circuits, wires, memory cells, that could manifest failure and is unable to make the design function properly. The fault models are used to predict consequences and localization of a particular fault, allowing improving the fabrication process accuracy [11].

This PhD thesis uses the fault models for circuits and memories listed in the following list:

- a. Stuck at 0 (SA0): the wire/cell's content is always 0, even if a write 1 has been performed.

- b. Stuck at 1(SA1): the wire/cell's content is always 1, even if a write 0 has been performed.

- c. Rising Transition  $\uparrow / 0$  (TF1): the wire/cell fails to undergo a  $0 \to 1$  transition.

- d. Falling Transition  $\downarrow$  / 1 (TF0): the wire/cell fails to undergo a 1 $\rightarrow$  0 transition.

- e. Coupling fault Inversion (CFin): a transition in one wire/cell inverts the contents of a second wire/cell.

- f. Idempotent Coupling (CFid): a transition in one wire/cell forces the contents of a second wire/cell to a certain value (0 or 1).

- g. Bridging (BF): this fault model involves any number of wires/cells and is caused by a logic level rather than a transition. It normally consists of a galvanic connection between two (or more) wire/cells, or lines and a state of a line.

- h. State Coupling (SCF): a coupled wire/cell or line is forced to a certain value, when the coupling wire/cell or line is in a given state.

- i. Active Neighbourhood Pattern Sensitive (ANPSF): the content of a wire/cell, or the ability to change its contents, is influenced by the contents of other wires/cells in the circuit/memory. ANPSF corresponds to the base wire/cell changing its contents due to a change in the values hold by the neighbourhood wires/cells.

- j. Passive Neighbourhood Pattern Sensitive (PNPSF): the content of the base wire/cell cannot be changed (i.e., it cannot make a transition) due to a certain neighbourhood pattern.

#### 1.4 Testing semiconductor devices

Before describing the different tests applied to silicon devices, it is necessary to highlight the difference between verification and test [10] [12] [13]:

- **Verification** is the process of testing the design functions according to specifications <u>before</u> product manufacturing

- **Test and Validation** is the process of testing the design hardware by identifying the localization of potential defects caused by manufacturing errors, environment-induced errors, design errors, and ageing effect errors. This process of testing is performed <u>after</u> product manufacturing.

Semiconductor tests aims at identifying defects caused by manufacturing errors, process variation, and ageing effects, verifying whether the device's physical structure is corresponding to the design model, and consequently the functions are compliant to the specifications. Deep sub-micron technologies has shown to be rather susceptible to all sorts of noise and process variations, thus often constant testing is a requirement.

To guarantee the reliability of manufactured microelectronic devices, especially on those employed in safety critical applications, distinct tests are applied to the component at different production/life stages. Each test has its own test pattern targeting specific goals. Table 1.1 lists the tests applied to the semiconductor at several different stages/locations during manufacturing and operational phases. Moreover, suitable test patterns are carefully selected/developed during test application at each stage, thus guaranteeing the components' quality in high reliable applications.

From table 1.1, this thesis explains the differences between *Functional* and *Structural Tests* that are performed during *Manufacturing* and *On-line testing*. The following subsections define these concepts using in the reliability characterization process.

| Test # | Stage                | Test Type          | Applied Test Pattern           |

|--------|----------------------|--------------------|--------------------------------|

| 1      | Foundry              | Wafer level test   | Structural patterns            |

| 2      | Packaging company    | Package level test | Structural patterns            |

| 3      | Test company         | Parametric test    | Parametric patterns            |

| 4      | Test company         | Characterization   | Parametric and functional      |

|        |                      | test               | stress patterns followed by    |

|        |                      |                    | structural patterns            |

| 5      | Supplier/Design and  | Burn-in test       | Parametric and functional      |

|        | Test companies       |                    | stress patterns followed by    |

|        |                      |                    | Structural patterns            |

| 6      | Application develop- | Acceptance test /  | Structural and Functional pat- |

|        | ment company         | Incoming inspec-   | terns                          |

|        |                      | tion               |                                |

| 7      | Consumer             | On-line test       | Software-Based Self-Test       |

|        |                      |                    | (SBST) pattern during the      |

|        |                      |                    | operational mode               |

Table 1.1: Types of tests in semiconductor devices

#### 1.4.1 Functional vs. Structural Tests

Functional tests uses the circuits functional inputs to stimulate internal logic and observe results at the functional outputs [10] [12]. Usually, test patterns are manually written by verification engineers from the specifications. However, there are Functional Automatic Test Pattern Generators (ATPG) that construct a set of test patterns to completely exercise the circuit functions, which can be very naive and inefficient when targeting fault detection [10]. For example, if we consider stimulating all of the functional inputs of a three-operand 64-bit adder (two inputs and one output), the result would be a functional test pattern containing  $2^{n*2}$  patterns. Where n is the quantity of bits in each operand, in the example is 64, and +64 because we have 2 input operands. The number of functional input patterns is more than  $3 \times 10^{19}$  and would take an order of magnitude of about  $10^{22}$  years to be applied using a fast 1GHz Automatic Test Equipment (ATE).

Nevertheless, functional test patterns can be very effective on CPU cores when targeting different test targets; for example, functional power consumption and stress, software related faults, activation of mitigation techniques used for *dependable* systems, and etc. The main drawback of functional testing is pattern generation time that scales exponentially with the number of inputs and the sequential depth of circuits, i.e the number of memory elements embedded in the *Design-Under-Test* (DUT) [10].

Structural test, on the other hand, only exercises the minimal set of stuck-at faults on each line of the circuit to test the physical structure of the device [10] [12]. Structural tests are much more efficient than functional ones when targeting physical defects. It is thus, an important test for proving whether circuit physical integrity is structurally correct

as designed. It does not prove that the circuit functions are designed correctly according to specifications [10]. Considering the previous 64-bit adder example, structural tests are so powerful towards fault detection that, after discarding equivalent faults, each bit-slice in the adder would only have 27 faults. In this case, we only need 1,728 test-patterns to test the adder. The 1 *GHz* ATE would apply these patterns in 0.000001728 s, and since this test pattern set covers all possible structural stuck-at faults in the adder, it achieves exactly the same fault coverage as the intractable functional test pattern set described above. Frequently, the circuit designer will provide a limited subset of the functional test patterns for the circuit, but those typically cover only 70 to 75% of the total number of faults. Testing for only 75% of the modelled failures is of limited value - it will catch only the most easy to cover defects. Thus, we see the importance of ATPG algorithms. The vectors they produce supplement the functional test vectors from the designer to raise the stuck-at fault coverage to 98% or higher levels.

In complex synchronous circuits containing many sequential elements (latches and FFs), structural tests are even more efficient than functional tests, since they benefit from *Design-for-Test* (DfT) structures implemented in the design specially for aiding structural tests. DfT adds short-cuts in the design by connecting the output of one flip-flop/latch to the input of another until all memory elements in the circuit are connected in a chain, forming a large shift register, namely *scan-chain design*. Then, special test input and output ports are added to introduce a test pattern and read results, respectively. This approach potentials the ATPG's work on generating structural test patterns and eases the ATE test application by reducing the number of inputs and test time, as well as increasing significantly test coverage with respect to functional tests, as explained before.

The main drawback of structural tests are the side-effects it produces. For example, just the test pattern shifting operation in the scan-chain of a CPU core ages the scan elements significantly, especially in deep sub-micron technologies [14][15]. Then, after shifting the pattern through the scan-chain, the actual structural test happens, testing the internal logic which increases switching activity and consequently power consumption in an irresponsible manner, such that premature damage happens even on the most strongest components. Thus making testing inefficient and costly.

#### 1.4.2 Manufacturing, Incoming, and On-line Testing

*Manufacturing testing* uses deep knowledge of the design, equipments, materials, and communication protocols used in the fabrication process of a semiconductor device. Considering table 1.1, test from 1 to 5 are considered manufacturing tests. They comprise of all tests realized before shipping the component to the application company that will build a working application to satisfy a certain market niche with its product. The types of manufacturing tests are explained in the following paragraphs [10][12][13].

1. Wafer level test is the first test applied to the physical semiconductor design. In general terms, the wafer is where a population of components are printed using the manufac-

ture process and the first physical outcome of the design. The wafer is polished and cut into equal rectangular parts limiting boundaries of one device to another, called dies. The wafer test procedure uses a special ATE containing micro-probes that fit perfectly on the dies' micro-pads, allowing special test pattern application and result capturing. Usually, test patterns are functional and structural patterns with the minimal capability to separate dies containing many defects from defect-free ones. The former are marked with a sticker by the ATE identifying dies that needs to be removed, and the latter dies, namely *Known Good Dies*, go to the packaging process. This die separation process is also called *sorting*.

- 2. Package level tests are applied to known good dies after packaging. Packaging is the complicated task of bonding very thin wires to micro-pads of the die to pins that connect to the external world. This procedure is done either manually by packaging engineers or automatically by specialized equipments. Both cases are not error-free as they may have problems like: air impurity touching silicon surface, incorrect bonding, missing or open wires, connecting wires, die misplacement, electrostatic discharge (ESD) burning internal logic, corrosion due to high humidity, etc. Package level tests uses the ATE to inject test vectors (functional and structural) and determine good chips after packaging.

- 3. *Parametric tests* is the procedure of applying high/low voltages and currents stressing the chips pins and the logic, determining whether they work correctly according to electrical specifications. The key issue here is to provide correct limits of electrical stimuli to define if the chip and pins will work under certain conditions or not.

- 4. Characterization tests is usually applied to a random sample of a design production lot, by applying mission-like parametric stresses under high temperatures to quickly age the samples until all of them have failed. This procedure usually takes into account the Arrheinus chemical kinectic theory of semiconductor devices [16]. It is clear that using normal conditions for performing characterization tests would last for years and not days as proposed by the methodology. Characterization tests can also include Operational Life Tests where a phase of functional and parametric stresses are applied, followed by stress-free diagnostic tests which uses structural patterns to determine the amount of failed components [9]. This test diagnosis loop allows drawing the bathtub curve shown in figure 1.1 and determining the failure rate at each life phase to compute a more or less accurate reliability value of the production lot devices.

- 5. Burn-in or Screening: Burn-in, as the name suggests, is the process of heating the components at controlled higher temperatures inside an industrial oven for a stated time. It is used in OLTs, but during screening it uses characterization information acquired in the previous tests to age all of the devices of a production lot until they have reached the beginning of their useful-life phase. Then, final structural tests are performed to identify and remove infant mortality components from good ones. Finally, the good packaged devices are sold to the application development company. Most of

the times, the information about the electrical characteristics of the device is given to the application company.

Incoming inspection or Acceptance tests are applied by the application development company. If they are developing safety critical applications like automotive and aerospace, they must guarantee that the application will work according to reliability required standards. During component transportation there still exists a possibility that some components have been damaged internally either by ESD, vibrations, humidity and so forth. In this case, the application company can trigger limited structural tests embedded in the design whose programming has been given by the component manufacturer. The engineer programs a simple test routine to drive Built-in Self-Test (BIST) mechanisms and retrieve results for comparison. In other cases, this task is not possible due to manufacture secrecy and the application engineer must program manually functional patterns targeting functional error detection of the device only for the parts the application uses, otherwise test programming will be very time consuming. The failure rate in this phase should be low and constant as the device is matured in its useful life. Usually, the application company, client of the device manufacturer, can compare reliability figures obtained from manufacturing test information and the ones obtained by its own company during inspection tests.

On-line tests are applied to the device when already in mission, and all the manufacturing information is not accessible as well as embedded test structures like scan-chain, BIST, MBIST. DfT are mainly used during manufacturing testing, and besides being physically incorporated to the device, it is forcefully turned-off by the application company by soldering test pins to fixed values when in mission mode. This completely eliminates DfT structures from working in test mode. On the other hand, some international standards determine that a component controlling critical parts in safety critical applications should be constantly tested without disturbing normal operation during mission, as it can provoke catastrophic failures. Moreover, on-line testing allows retrieving information to the application company from activities acquired during mission mode and helps improving the application itself. Also, it allows warning end-users about imminent failures before they actually happen.

# 1.5 Reliability Requirement Standards for High Reliable Electronic Systems

The insurgence of even smaller and efficient microelectronic devices in safety-critical applications has concerned governments, authorities, and overall customers, due to possible reliability problems. Therefore, several standards were defined in order to guarantee mission safety by determining the usage of high reliable electronic components controlling critical parts in automotive and aerospace applications. Automotive critical parts can

be: air-bag, braking system, steering wheel, advanced assistance driving. In aerospace: take-off, landing, movement, and computation.

The International Electrotechnical Commission (IEC) develops and maintains international standards that provide systematic methods and tools for dependability assessment and management of equipment, services, and systems throughout their life cycles [17]. It defines dependability as:

"the collective term used to describe the availability performance and its influencing factors: reliability performance, maintainability performance and maintenance support performance" [18]

Reliability is directly correlated to safety, while the first tries to improve costs targeting more profit, the second assesses the safety quality demanded by standards. Usually, high reliability necessary attain high safety levels [8], thus ensuring protection against any hazard affecting the system, namely functional safety. IEC 61508 [19] defines specific rules for assessing functional safety in electrical/electronic safety-related systems.

Reliability has become a problem when dealing with new products in safety-critical applications, therefore, each field is adopting its own standard. In particular, car manufacturers developed the ISO 26262 standard [3], which is an adaptation of the IEC 61508 for Automotive electric and/or electronic (E/E) Systems in series production passenger cars. The standard addresses possible hazards caused by malfunctioning behaviour of E/E safety-related systems and their interactions. It demands a number of auditing processes during the whole product's lifecycle, to ensure high reliability and mission safety throughout the system useful life. Remarkably, in mission testing for error detection demands the adoption of on-line self-test technique as an essential test process in critical E/E vehicle parts.

Other examples of application specific standards dealing with Reliability, Availability, Maintainability and Safety (RAMS) issues are:

- Railway E/E equipment and programmable electronic systems: CENELEC EN 50126 [20]

- Aerospace hardware and software electronic systems: DO-254 [21], DO-178C [22]

, ARP4754 [23]

- Nuclear Power Plants: IEC61513 [24]

- Medical Systems: IEC62353[25]

# 2. State-of-the-Art testing and diagnosis efforts

This chapter describes the state-of-the art testing and diagnosis techniques for reliable semiconductor devices, especially for SoCs. Initially, SoCs are described and then its internal modules; CPU, memories, and GPUs.

#### 2.1 System-On-Chip

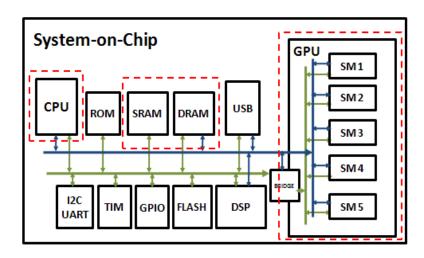

The need for even smaller, faster, power efficient, improved functions of semiconductor devices tied to technology scaling, led to the development of System-On-Chips. They include a full working computer with *CPU*, *memories*, peripherals, and *image processing units* on a single die. With the advent of SoCs, integrating many hardware functions on a single die consequently reduced testing costs by integrating standard design and test methodologies applicable for any internal logic.

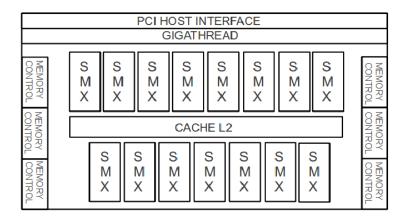

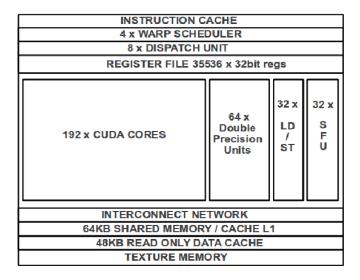

Figure 2.1 shows the internal architecture of the 32-bit CPU LEON SoC currently owned by AEROFLEX, but originally developed by the European Space Research and Technology Centre (ESTEC) part of the European Space Agency (ESA). It has embedded a SPARC V8 RISC CPU core, memory cores (SRAM, DRAM, and Flash), communication and processing peripherals (USB, UART, DSP, etc), and a Graphics Processing Unit (GPU) accounting on many serial multiprocessors (SM) containing hundreds of processing elements for parallel computation. This device has been used in aerospace applications with radiation hardening (radHard) hardware. This SoC architecture presented is a **good example** for showing, on a single device, the target modules (in red) this PhD thesis focuses.

Although testing has many issues that need tackling, this PhD thesis concentrates on embedded memory diagnosis, functional pattern generation for testing CPU cores, and fault injection in GPGPUs. The following sections describe and list the state-of-the-art testing and diagnosis efforts realized in the past.

Chapter 2 2.2. CPU

Figure 2.1: SoC Architecture

#### **2.2 CPU**

CPUs are the processing units responsible for controlling the SoC. It controls all the SoC peripherals by executing instructions previously programmed by engineers. Usually, instructions are placed in the instruction memory, and are decoded and executed by the CPU controlling the datapath to manipulate application data; whether external or internal information, finally restoring to the data memory as the final outcome. In general, SoCs have the potentiality to execute a *Real Time Operating System* (RTOS) to concurrently manage peripherals, software implemented algorithms and applications.

Testing digital CPU cores and peripherals can be rather simple during manufacturing tests by resorting to mature techniques (*Design-for-Testability*) developed throughout the years:

a. Boundary and Scan-Chain Designs [26] [27]: Joint Test Access Group Port is the common name for the industry standard IEEE 1149.1 and IEEE 1500. It adds a special test access port (TAP) and internal test modules to make structural testing easier, faster, and efficient and has the potentiality to exploit hardware and software debugging. Basically, the methodology exploits internal memory elements (Flip-Flops and Latch) to easily insert structural patterns for testing physical internal wires and logic gates during **manufacturing testing**. Flip Flops are slightly modified for being capable of operating in test and functional modes, by inserting a multiplexer on its primary input and adding a test mode selection. The multiplexer takes as inputs the functional inputs and the output of another FF. In test mode, all FFs are linked on a chain, where

Chapter 2 2.2. CPU

the output of one element is the input of another. This sort of design is named scanchain. It allows not only testing the CPU but also peripherals, however, the design must consider modifying the SoC such that test and functional modes do not interfere with one another, namely DfT design rules. Moreover, the standard defines boundary scan strategy able to test boundary pads as well as testing many devices in sequence.

- b. Built-In Self-Test (BIST) [10] is a type of test that can be used for manufacturing, acceptance, and on-line tests. It employs a Linear Feed-Back Shift Register for generating random stimuli which is applied to the internal logic that produces execution results and stores them in a Multiple Input Signature Register (MISR). By analyzing the contents of the MISR, the test is capable of identifying possible failures of specific modules. In the literature, there are several works exploiting BIST during on-line and off-line modes [28][29][30].

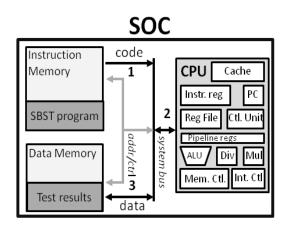

- c. Software-Based Self-Test (SBST) patterns are useful for testing the CPU cores embedded in a SoC. Usually, they correspond to a set of assembly routines able to apply the correct test vectors in the correct spots while the device is running in functional mode. SBST techniques for testing embedded CPU cores in SoCs during the operational phase may be preferred to hardware techniques like BIST (Built-In Self-Test) because they: