## POLITECNICO DI TORINO Repository ISTITUZIONALE

## A New Mirroring Circuit for Power MOS Current Sensing Highly Immune to EMI

Original

A New Mirroring Circuit for Power MOS Current Sensing Highly Immune to EMI / Aiello O. ; Fiori F. - In: SENSORS. - ISSN 1424-8220. - ELETTRONICO. - 2:13(2013), pp. 1856-1871.

*Availability:* This version is available at: 11583/2506030 since:

Publisher: Basel : Molecular Diversity Preservation International (MDPI)

Published DOI:10.3390/s130201856

Terms of use: openAccess

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

Publisher copyright

(Article begins on next page)

Article

# A New Mirroring Circuit for Power MOS Current Sensing Highly Immune to EMI

## **Orazio Aiello \* and Franco Fiori**

Microelectronics EMC Group, Eln. Department, Politecnico di Torino, Corso Duca degli Abruzzi, 24, I-10129 Torino, Italy; E-Mail: franco.fiori@polito.it

\* Author to whom correspondence should be addressed; E-Mail: orazio.aiello@polito.it; Tel.: +39-011-090-4223; Fax: +39-011-564-4099.

Received: 8 November 2012; in revised form: 27 December 2012 / Accepted: 8 January 2013 / Published: 31 January 2013

**Abstract:** This paper deals with the monitoring of power transistor current subjected to radio-frequency interference. In particular, a new current sensor with no connection to the power transistor drain and with improved performance with respect to the existing current-sensing schemes is presented. The operation of the above mentioned current sensor is discussed referring to time-domain computer simulations. The susceptibility of the proposed circuit to radio-frequency interference is evaluated through time-domain computer simulations and the results are compared with those obtained for a conventional integrated current sensor.

**Keywords:** current sensor; CMOS integrated circuit; smart power; electromagnetic interference (EMI); electromagnetic compatibility (EMC); senseFET; miller effect

## 1. Introduction

In the last decades, the development of CMOS technologies in terms of scale integration and component performance has made the integration of full electronic system into a single chip possible. Such System-on-Chips (SoCs) comprise complex high-speed digital blocks, analog circuits and power section [1,2]. The power-supply voltage of such integrated circuits has decreased over time, leading to lower noise margins. However, the level of disturbances collected by the wiring harnesses of the

electronic systems from the surrounding environment has strongly increased because of the widespread use of wireless systems for radio/TV broadcasting and mobile communications. In this context, the need to understand the effect of radio frequency interference (RFI) on baseband integrated circuits has continued to grow and several studies have tried to set out design guidelines and new circuit topologies for making integrated circuits immune to RFI [3–8]. Such disturbances superimposed onto nominal signals are of particular concern in the design of input and output front-end integrated circuits like those included in smart power ICs, which cannot be protected using EMI-filters at the PCB level because either their presence can affect the nominal circuit operation or the PCB is not present since the SoC is encapsulated inside the sensor (actuator) plastic holder. For instance, EMI filters and capacitors cannot be connected to the power transistor terminals because they would reduce the power efficiency. As a result, the power transistors that drive actuators through cables can experience high-level RFI that can lead to unexpected transistor switching and leakage currents, as shown in [9,10]. In addition to this problem, the circuits that are connected to the transistors' terminals, including circuits embedded in smart power ICs for monitoring the operation of the power transistors, are also affected by RFI.

Within the aforementioned context, this paper investigates the susceptibility of integrated current sensors that are used in power circuits for control and/or safety purposes to RFI. The current of a power transistor can be sensed by using one of the circuits presented in [11], but only a few of them are suitable for integration on silicon. Among these integrated current sensors, one of the most frequently used is that based on a small transistor namely SenseFET. The voltages at the terminals of the SenseFET are kept equal to those of a power transistor in which the current to be detected flows. In this way, such a current is scaled by a constant K and provided by the SenseFET. K depends only on the aspect ratios  $\left(\frac{W}{L}\right)$  of the two transistors. In this circuit, the SenseFET is electrically connected to the terminals of the power transistor and therefore it is affected by the RF disturbances collected by cables. In order to design embedded current sensor immune to such RF interferences, this paper presents a new integrated current-sensing solution conceived to be electrically not connected to the power transistor drain that can be affected by disturbances. The current is sensed whenever during its transient the power transistor and the SenseFET both operate in saturation. Therefore, the current flowing through the power transistor is mirrored by the SenseFET, is not dependent on the drain-source voltage and is only related with the mirroring factor K. The paper is organized as follows. Section 2 describes the operation of a common integrated current sensor. Section 3 summarizes the switching behavior of power MOSFETs. On the basis of such a behavior, a new current sensor not electrically connected to the drain terminal of the power transistor is proposed in Section 4. Then, the results of computer simulations aimed at evaluating the susceptibility of the proposed current sensor, the MagFET-based sensor and the commonly used current sensor to RFI are shown in Section 5. Finally, some concluding remarks are drawn in Section 6.

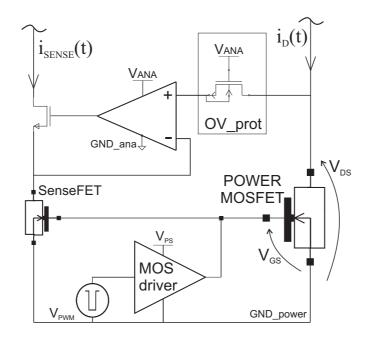

#### 2. A Conventional Current Sensor: The SenseFET

Common current sensors for integrated applications are based on the SenseFET circuit topology, in which the current  $i_D(t)$  that flows through an MOS Power transistor is sensed using an elementary transistor of the same type that is used in the power transistor. Figure 1 shows the operation of the

1858

SenseFET current sensor, where the gate terminals of the aforementioned transistors are connected to each other and driven by an MOS driver, while the drain-to-source voltage of the SenseFET is made equal to that of the power transistor by means of a voltage follower. In this circuit, the relationship between the power transistor current ( $I_D$ ) and the sensed current ( $I_{SENSE}$ ) can be written as

$$K = \frac{\left(\frac{W}{L}\right)_{\text{power}}}{\left(\frac{W}{L}\right)_{\text{sense}}} \tag{1}$$

where  $\left(\frac{W}{L}\right)_{\text{power}}$  and  $\left(\frac{W}{L}\right)_{\text{sense}}$  are the aspect ratios of the power and SenseFET transistors, respectively. K is typically not lower than 10<sup>3</sup>. The scaled current  $I_{\text{SENSE}}$  is then converted to a voltage, using a resistor to be used for digital signal processing. This paper focuses on a low side sensing topology highlighted in Figure 1.

Figure 1. Current sensor based on the SenseFET technique.

However, the same reasoning can be applied for the high side topologies. In this technique the power dissipation is low and the accuracy is related to the matching of the SenseFET and the Power MOS. The two transistors are driven in the deep triode region by the same gate-source voltage and have to be kept at the same drain-source voltages. Therefore, to minimize the error in the sensed current, the amplifier needs to have a very high gain. Moreover, the amplifier should maintain the accuracy across the large input common-mode range. Although several circuit topologies of current sensors have been proposed, all of them include an amplifier, which implies stability issues, limited bandwidth and increased design complexity. In fact, the improvements in integrated current-sensing are basically focused on increasing amplifier performance [12–19]. Furthermore, the presence of the amplifier increases the overall susceptibility of the commonly employed SenseFET-based current sensing to EMI. In fact, this amplifier is connected through an over-voltage protection (see Figure 1) to the power transistor drain, and hence to the wiring interconnects at the system level that collect EMI. Since interference with an amplitude of hundreds of mV causes distortion in the amplifier and in the over-voltage protection, the operation of the current sensor can be impaired [6].

For all the above mentioned reasons, a new current sensor with improved performance due to the absence of any amplifier has been designed and its immunity to EMI is specifically addressed in this paper.

#### 3. Power MOSFET Switching Characteristics

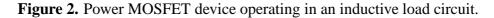

The Power MOSFET is usually employed as a switch in circuits for energy conversion and management applications and to drive high-power loads. For instance, a Power MOSFET is used to control the current in inductive loads such as the windings of motors. A Power MOSFET that drives an inductive load is represented in Figure 2 where a freewheeling diode carries the load current when the Power MOS is switched-off and a stray inductance is included to account for package and board parasitic elements.

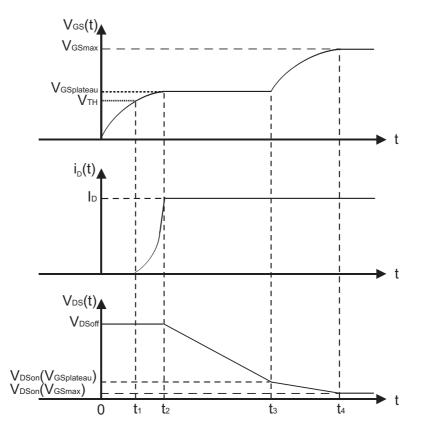

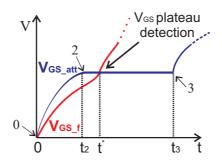

The switching behavior of Power MOSFET structures is governed by the gate drive circuit and the nature of the load. The power transistor is switched on and off by a control or gate drive circuit, which can be represented (Thevenin's equivalent) as a DC voltage  $V_{\rm G}$  with a series resistance  $R_{\rm G}$ . The load current  $i_{\rm L}$  transfers between the power MOSFET device and the freewheeling diode during each operating cycle. The inductor is charged and its current is increased when the Power MOSFET is turned-on while it is discharged when the load current flows through the diode. However, the change in the inductor current is small during one cycle, allowing the assumption that the current  $I_{\rm L}$  is constant. On the basis of that, a new current sensor that operates during the transient of the Power MOSFET has been conceived. To this purpose, the waveform of the transient of a Power MOSFET is represented in Figure 3 and described in the following. Whenever the Power MOSFET is in off-state, the load current flows through the freewheeling diode. The initial conditions for the Power MOSFET are defined by  $v_{\rm GS}(0) = 0$ ,  $i_{\rm D}(0) = 0$ ,  $v_{\rm DS}(0) = V_{\rm DSOFF}$ . During the turn-on process, the gate bias voltage source  $V_{\rm G}$  starts to charge the capacitances of the Power MOSFET. Since no drain current can flow through the power MOSFET device until the gate voltage exceeds its threshold voltage, the drain voltage initially remains

at the drain bias voltage. The gate–drain capacitance  $C_{\rm GD}(V_{\rm DS_{OFF}})$  remains constant because the drain voltage is constant. Consequently, the time constant for charging the gate of the power MOSFET device is  $R_{\rm G} \cdot [C_{\rm GS} + C_{\rm GD}(V_{\rm DS_{OFF}})]$ , resulting in a gate voltage given by

$$v_{\rm GS}(t) = V_{\rm GS_{max}} \cdot \left[ 1 - e^{-\frac{t}{R_{\rm G} \cdot [C_{\rm GS} + C_{\rm GD}(V_{\rm DS}_{\rm OFF})]}} \right]$$

(2)

and represented in Figure 3. The gate voltage reaches the threshold voltage at time  $t_1$ :

$$v_{\rm GS}(t)|_{t=t_1} = V_{\rm TH} \tag{3}$$

$$t_1 = R_{\rm G} \cdot \left[C_{\rm GS} + C_{\rm GD}(V_{\rm DS_{\rm OFF}})\right] \cdot \ln\left(\frac{V_{\rm GS_{\rm max}}}{V_{\rm GS_{\rm max}} - V_{\rm TH}}\right) \tag{4}$$

Once the gate voltage exceeds the threshold voltage, drain current begins to flow.

$$i_{\rm D}(t) = \frac{\mu_{\rm ni} C_{\rm OX} W_{\rm CH}}{L_{\rm CH}} \cdot [v_{\rm GS}(t) - V_{\rm TH}]^2$$

(5)

Although the drain current increases, the drain voltage remains at the drain supply voltage  $V_{\text{DS}_{\text{OFF}}}$ because the diode cannot sustain any voltage until all of the load current is transferred to the Power MOSFET. Since the drain voltage remains constant, the drain–gate capacitance is also invariant in the range  $[t_1 - t_2]$ . Consequently, the gate voltage continues to increase at an exponential rate as described by Equation (2) with the same time constant. The drain current increases as the square of the gate voltage as described by Equation (5) with a nonlinear waveform as represented in Figure 3.

The drain current increases until it becomes equal to the load current  $I_{\rm D} = I_{\rm L}$  and  $v_{\rm GS}(t)$  reaches the voltage plateau  $V_{\rm GS_{plateau}}$  at the time  $t_2$ .

$$v_{\rm GS}(t)|_{\rm t=t_2} = V_{\rm GS_{plateau}} = V_{\rm GS_{max}} \cdot \left[1 - e^{-\frac{t_2}{R_{\rm G} \cdot [C_{\rm GS} + C_{\rm GD}(V_{\rm DS}_{\rm OFF})]}}\right]$$

(6)

$$t_2 = R_{\rm G} \cdot \left[C_{\rm GS} + C_{\rm GD}(V_{\rm DS_{\rm OFF}})\right] \cdot \ln\left(\frac{V_{\rm GS_{\rm max}}}{V_{\rm GS_{\rm max}} - \sqrt{\frac{I_{\rm D}L_{\rm CH}}{\mu_{\rm n}C_{\rm ox}W_{\rm CH}}} - V_{\rm TH}\right).$$

(7)

All of the load current has transferred from the diode to the Power MOSFET device at time  $t_2$  and the diode is now able to support voltage. The drain-source voltage of the Power MOSFET starts to reduce at this time. Since the drain current is constant and equal to the load current ( $I_D = I_L$ ), the gate voltage at time  $t_2$  can be also expressed as

$$v_{\rm GS}(t)|_{t_2-t_3} = V_{\rm GS_{plateau}} = V_{\rm TH} + \sqrt{\frac{I_{\rm D}L_{\rm CH}}{\mu_{\rm n}C_{\rm ox}W_{\rm CH}}}.$$

(8)

The gate-source voltage remains constant at the plateau voltage until the drain-source voltage has reduced to the on-state voltage drop corresponding to the product of the load current and the on-resistance of the device at a gate bias equal to the plateau voltage. Since the gate voltage is constant during the plateau phase, all the gate current  $i_{G_{plateau}}$  is used to charge the gate–drain or Miller capacitance. The gate current during the plateau phase is given by

$$i_{\rm G_{plateau}} = \frac{V_{\rm GS_{max}} - V_{\rm GS_{plateau}}}{R_{\rm G}}.$$

(9)

As this current charges the gate-drain capacitance, its voltage decreases at a rate given by

$$\frac{dv_{\rm GD}(t)}{dt} = -\frac{i_{\rm GP}(t)}{C_{\rm GD}(v_{\rm DS}(t))}.$$

(10)

Since the gate–source voltage is constant at  $V_{GS_{plateau}}$  during this time, the drain voltage also decreases linearly with time:

$$\frac{dv_{\rm DS}(t)}{dt} = \frac{dv_{\rm GD}(t)}{dt} = -\frac{i_{\rm GP}(t)}{C_{\rm GD}(v_{\rm DS}(t))} = -\frac{V_{\rm GS_{max}} - V_{\rm GS_{plateau}}}{R_{\rm G} \cdot C_{\rm GD}(v_{\rm DS}(t))}.$$

(11)

At the end of the plateau phase at time  $t_3$ , the drain-source voltage becomes equal to the on-state voltage drop corresponding to the plateau gate bias voltage. Based on this, the duration of the plateau can be expressed as:

$$\int_{t_2}^{t_3} dv_{\rm D} = \int_{t_2}^{t_3} -\frac{V_{\rm GS_{max}} - V_{\rm GS_{plateau}}}{R_{\rm G} \cdot C_{\rm GD}(v_{\rm DS}(t))} dt$$

(12)

$$t_3 - t_2 = \frac{R_{\rm G} \cdot C_{\rm GD_{AVG}}}{V_{\rm GS_{max}} - V_{\rm GS_{plateau}}} \cdot \left[V_{\rm DS_{OFF}} - I_{\rm D}R_{\rm DS_{ON}}(V_{\rm GS_{plateau}})\right]$$

(13)

where  $C_{\text{GD}_{av}}$  is the gate–drain capacitance assumed to have a constant average value during the transient and  $R_{\text{DS}_{ON}}(V_{\text{GS}_{\text{plateau}}})$  is the on-resistance of the power MOSFET device for a gate-source voltage equal to the plateau voltage. Beyond the plateau, the gate voltage increases exponentially again as shown in the Figure 3 until it reaches the gate supply voltage. The time constant for this exponential rise is different from the initial phase due to the large gate–drain capacitance. The increasing gate voltage produces a reduction of the on-resistance of the power MOSFET device, resulting in a small reduction of the drain voltage during this fourth phase of the turn-on process.

Considering reasonable value for the parasitics of the Power transistor sized in the order of  $mm^2$  and for the integrated driving resistance  $R_G$ , the interval time  $(t_3 - t_2)$  results to be larger than hundreds of nanoseconds. On the basis of a trigger event occurring during this interval, a new current sensor is proposed in Section 4.

#### 4. A New Current Sensor Based on the Miller Effect

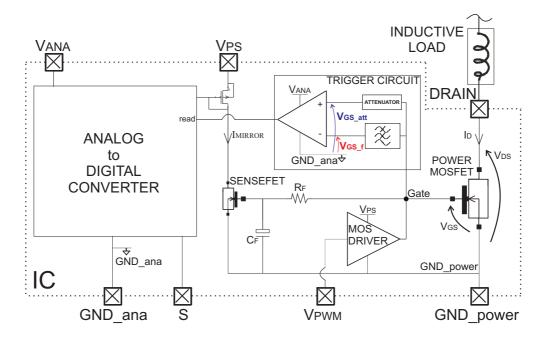

In order to design a current sensor immune to EMI, a new circuit is conceived, which is not electrically connected with the Power MOSFET drain terminal that is prone to disturbances. To this purpose, the current that flows through the Power MOSFET ( $i_D$ ) is mirrored and processed during the  $V_{GS}$  voltage plateau due to the Miller effect (between points 2 and 3 in Figure 3). In this region, the Power MOSFET operates in the saturation region and the mirrored current  $I_{MIRROR}$  is not dependent on the drain-source voltage and is only related with the mirroring factor K. The Power MOSFET is driven by a PWM signal that provides both the proper-timing driving voltage and a negative pulse that generates a switching transient with negligible reduction of the current in inductive loads.

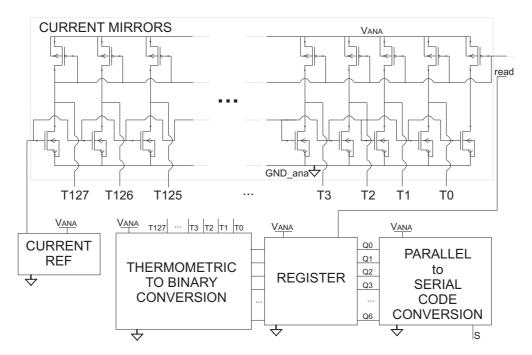

The block diagram of the proposed current sensor is shown in Figure 4. A low-pass RC filter  $(R_F - C_F)$  with a cut-off frequency significantly lower than the frequency of the EMI disturbances is placed between the Power MOSFET and SenseFET gates. In particular,  $R_F = 10 \ k\Omega$  and  $C_F = 2 \ pF$ , so that the cut-off frequency is less than 10 MHz ( $f_{CUT,OFF} \approx 8 \ MHz$ ). The current  $I_{unknown}$  is mirrored by a SenseFET, processed and converted in a serial code (Analog to Digital Converter in Figure 4, further reported in Figure 5). The SenseFET current, in turn, is mirrored 128 times. Each of these currents is compared with progressively scaled current references in order to provide a thermometric digital code of the SenseFET current  $I_{MIRROR}$ . Then, a further thermometric-to-binary conversion is provided [20]. As soon as a trigger event occurs, the binary code is written in a register. Such a binary word provides the value of the current to detect  $I_{unknown}$ , which is then converted to a serial code.

Figure 5. Analog to Digital Converter in Figure 4.

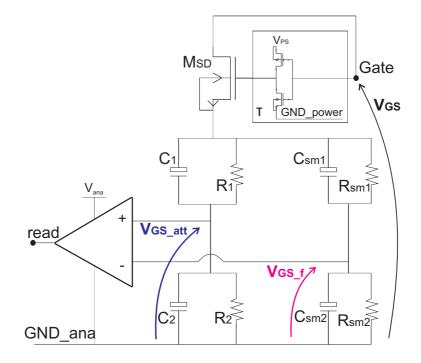

The trigger circuit is based on the comparison of an attenuated gate-source characteristic  $V_{\text{GS}_{\text{att}}}$  with the gate-source voltage after a low-pass filtering process  $V_{\text{GS}_{\text{f}}}$ . Both these two voltages are obtained from the gate-source voltage  $V_{\text{GS}}$  by means of only passive component as represented in Figure 6. An inverting stage made of a high voltage inverter allows to null the current dissipation whenever the  $V_{\text{GS}}$  voltage transient ends. Neglecting the drop voltage across the transistor  $M_{\text{SD}}$  that operates in triode during the transient, the voltage  $V_{\text{GS}_{\text{att}}}$  is given by:

$$V_{\text{GS\_att}} = \frac{R_2(1 + sR_1C_1)}{R_2(1 + sR_1C_1) + R_1(1 + sR_2C_2)} V_{\text{GS}}$$

(14)

Setting  $R_1C_1 = R_2C_2$  the voltage  $V_{\text{GS}_{\text{att}}}$  is simply the gate-source voltage  $V_{\text{GS}}$  scaled by a factor  $k_{din\_adp}$  independently by the frequency components of the switching transient of the Power MOSFET.

$$V_{\rm GS\_att} = \frac{R_2}{R_1 + R_2} V_{\rm GS} = \frac{C_1}{C_1 + C_2} V_{\rm GS} = k_{din\_adp} \cdot V_{\rm GS}$$

(15)

where  $k_{din\_adp}$  is set in order to not overcome the maximum voltage deliverable to the analog blocks.

$$k_{din\_adp} = \frac{R_2}{R_1 + R_2} = \frac{C_1}{C_1 + C_2}$$

(16)

#### Figure 6. Trigger circuit.

The voltage  $V_{\text{GS}_{f}}$  is obtained by a filtering and the passive components  $(R_{sm1}, C_{sm1}, R_{sm2})$  and  $C_{sm2}$  are set to makes this voltage  $V_{\text{GS}_{f}}$  lower than the attenuated voltage  $V_{\text{GS}_{att}}$  during the interval  $[0 - t_1]$ . At the same time, the passive components are set such that the filtered voltage  $V_{\text{GS}_{f}}$  reaches the attenuated voltage  $V_{\text{GS}_{att}}$  at the time  $t^*$  during the plateau, as sketched in Figure 7.

$$\begin{cases} V_{\text{GS}_{f}}(t) < V_{\text{GS}_{att}}(t) & \text{if } 0 < t < t^{*} \\ V_{\text{GS}_{f}}(t) > V_{\text{GS}_{att}}(t) & \text{if } t^{*} < t < t_{3} \end{cases}$$

(17)

Figure 7. Principle of the detection of the gate-source plateau.

Sensors 2013, 13

Assuming  $V_{\text{GS}}$  as a ramp before the voltage plateau, it can be shown that the filtered voltage  $V_{\text{GS}}(t)$  can be expressed as:

$$V_{\text{GS}\_f}(t) = \begin{cases} \frac{mG}{(s_p)^2} (s_p - s_z)(1 - e^{-s_p \cdot t}) + \frac{mGs_z}{s_p} \cdot t & \text{if } 0 < t < t_2 \\ \frac{mG}{s_p^2} (s_p - s_z)e^{-s_p \cdot t} (e^{s_p \cdot t_2} - 1) + \frac{mGs_z}{s_p} \cdot t_2 & \text{if } t_2 < t < t_3 \end{cases}$$

(18)

where

$$m = \frac{V_{TH}}{t_1} \tag{19}$$

$$G = \frac{C_{sm1}}{C_{sm1} + C_{sm2}}$$

(20)

$$s_z = \frac{1}{R_{sm1} \cdot C_{sm1}} \tag{21}$$

$$s_p = \frac{R_{sm1} + R_{sm2}}{R_{sm1} \cdot R_{sm2} \cdot (C_{sm1} + C_{sm2})}$$

(22)

On the basis of the two considered voltages  $V_{\text{GS}_f}$  and  $V_{\text{GS}_{\text{att}}}$ , it is possible to find out the time  $t^*$  during the voltage plateau when they are equal.

$$V_{\text{GS}_{f}}(t^*)|_{(t_2 < t^* < t_3)} = k_{din\_adp} V_{GS_{plateau}}$$

$$\tag{23}$$

$$\frac{mG}{s_p^2}(s_p - s_z)e^{-s_p \cdot t^*}(e^{s_p \cdot t_2} - 1) + \frac{mGs_z}{s_p} \cdot t_2 = k_{din\_adp}V_{GS_{plateau}}$$

(24)

$$t^* = -\frac{1}{s_p} \cdot \ln\left[\frac{k_{din\_adp}V_{GS_{plateau}} - \frac{mGs_z}{s_p}t_2}{\frac{G}{s_p^2}(s_p - s_z)(e^{s_p \cdot t_2} - 1)}\right].$$

(25)

Firstly, a minimum value for  $C_{sm1} = 200$  fF is set and a reasonable value of  $R_{sm1} = 62 \ k\Omega$  is chosen to set the zero  $s_z = 12.8 \ MHz$ . Consequently, the value of  $C_{sm2} = 2.5 \ pF$  and  $R_{sm2} = 19 \ k\Omega$  are set in order to place the pole  $s_p = 4.05 \ MHz$  before the zero. In this way an instant  $t^*$  in the range  $[t_2 - t_3]$  according to Equation (25) is found out and a correct trigger event can be provided. As soon as the mentioned two voltages  $V_{GS_{att}}$  and  $V_{GS_{att}}$  reach the same value during the gate-source plateau voltage due to the Miller effect, a comparator finds out a trigger event. Such an event enables to write the register whenever the Power MOSFET is in saturation during its switching transient. In the register, the digital value of the SenseFET current  $I_{MIRROR}$  is stored. Such a value represents the current to sense  $I_{unknown}$ scaled by the mirroring ratio K.

The proposed circuit is suitable for inductor current monitoring in DC-DC converter that operates in Continuous Conduction Mode (CCM) and whenever the detection of the current flowing in a Power MOSFETs operating in PWM that drive resistive and inductive loads is needed. The current to be monitored ranges from 100  $\mu A$  to 5 A, and the mirroring factor K has been set  $\mathbf{K} = 10^4$ . The sensibility of the designed sensor is 50  $\mu A$  (LSB). The absence of the amplifier provides an higher immunity to EMI and a faster response in inductor-current monitoring than the traditional current-sensing technique as shown in Section 5.

#### 5. Prediction of Integrated Current Sensors to RFI

This section shows the results of the time-domain simulations carried out to evaluate the susceptibility of the proposed current sensor and the traditional sensor to RFI.

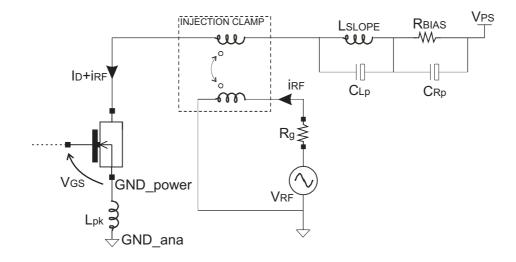

The proposed new current sensor is based on the transient behavior of the Power MOSFET in which the current to detect flows, and such a transient strongly depends on the parasitics of the Power transistor itself. For this reason, no other additional parasitic capacitances due to the test circuit have to affect the transient behavior of the Power MOSFET. Therefore, a CW RFI current of magnitude  $i_{\rm RF} = 200$  mA has been superimposed onto the current to detect  $I_{\rm D}$  by means of a toroidal RF transformer.

In fact, the analyses of the susceptibility to RFI have been carried out referring to the schematic view of Figure 8 similarly to immunity tests [21]. A resistor  $R_{\text{BIAS}}$  sets the value of the current  $I_{\text{D}}$ .

**Figure 8.** Schematic view of the Power MOSFET considered in the time-domain simulations.

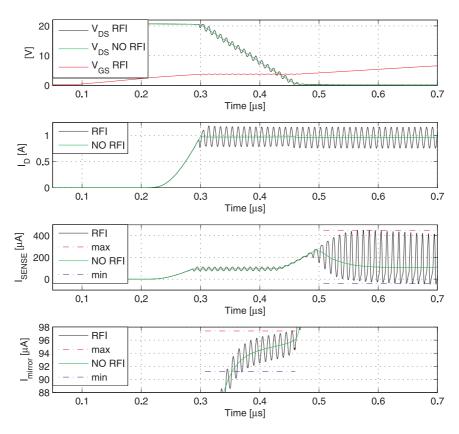

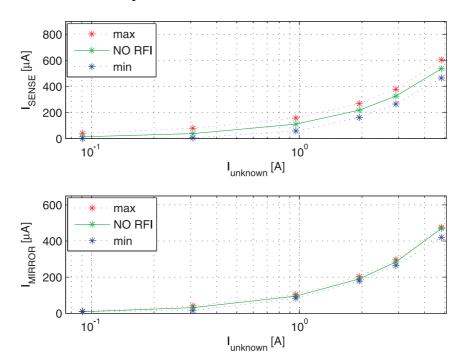

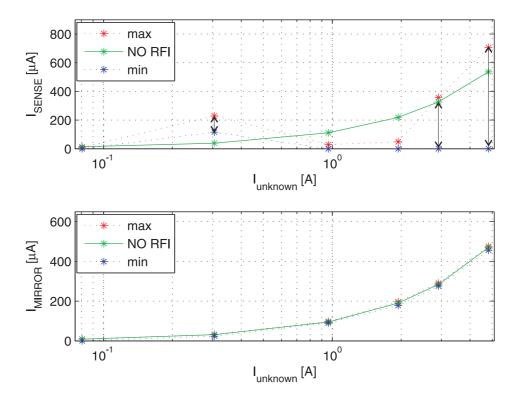

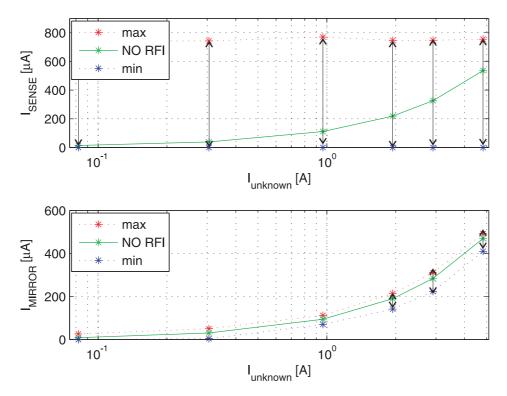

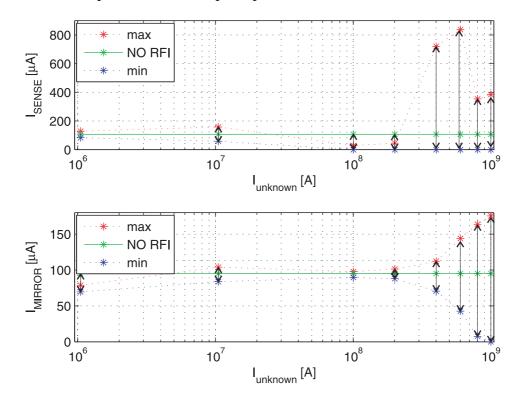

Figure 9 shows the switching transient traces ( $V_{\rm DS}$ ,  $V_{\rm GS}$ ) of a Power MOSFET in which the current to be detected  $I_{\rm D}$  flows, as well as the respective currents provided by a traditional SenseFET sensor ( $I_{\rm SENSE}$ ) and the proposed new sensor ( $I_{\rm MIRROR}$ ). In such a time-domain simulations, a CW RFI current  $i_{\rm RF} = 200 \ mA$  at 100 MHz superimposed on the drain current have been considered. The currents provided by the traditional SenseFET sensor ( $I_{\rm SENSE}$ ) and by the proposed new sensor ( $I_{\rm MIRROR}$ ) versus current to sense  $I_{\rm D}$  and their minimum and maximum errors due to the aforementioned RFI magnitude at 10 MHz, 100 MHz and 400 MHz are shown respectively in Figures 10–12. Furthermore, the minimum and maximum errors of the two considered currents due to a CW RFI  $i_{\rm RF} = 200 \ mA$  superimposed on the drain current  $I_{\rm D}$  versus frequency are reported in Figure 13. The results highlight that the immunity of the proposed current sensor to RFI is significantly greater than that of the conventional SenseFET circuit shown in Figure 1. **Figure 9.** Switching transient traces of a Power MOSFET ( $V_{\text{DS}}$ ,  $V_{\text{GS}}$ ,  $I_{\text{D}}$ ) and the respective currents provided by a traditional SenseFET sensor ( $I_{\text{SENSE}}$ ) and the new sensor based on the Miller effect ( $I_{\text{MIRROR}}$ ). CW RFI current amplitude 200 mA @ 100 MHz superimposed on the drain current.

Figure 10. Maximum and minimum current-sensing of the traditional SenseFET current sensor ( $I_{\text{SENSE}}$ ) and the new sensor based on the Miller effect ( $I_{\text{MIRROR}}$ ) versus current to sense  $I_{\text{D}}$ . CW RFI current amplitude 200 mA @ 10 MHz.

**Figure 11.** Maximum and minimum current-sensing of the traditional SenseFET current sensor ( $I_{\text{SENSE}}$ ) and the new sensor based on the Miller effect ( $I_{\text{MIRROR}}$ ) versus current to sense  $I_{\text{D}}$ . CW RFI current amplitude 200 mA @ 100 MHz.

Figure 12. Maximum and minimum current-sensing of the traditional SenseFET current sensor ( $I_{\text{SENSE}}$ ) and the new sensor based on the Miller effect ( $I_{\text{MIRROR}}$ ) versus current to sense  $I_{\text{D}}$ . CW RFI current amplitude 200 mA @ 400 MHz.

Figure 13. Maximum and minimum current-sensing of the traditional SenseFET current sensor ( $I_{\text{SENSE}}$ ) and the new sensor based on the Miller effect ( $I_{\text{MIRROR}}$ ) versus frequency. CW RFI current amplitude 200 mA superimposed on a current  $I_{\text{D}} = 1A$ .

#### 6. Conclusions

In this work, the susceptibility of common integrated sensors to RFI has been discussed for power transistor current monitoring. In order to improve the immunity of Power MOSFET transistor to RFI in current sensing, a new integrated solution has been proposed. It exploits the Miller effect on the switching transient of the Power MOSFET. The detection of the gate-source voltage plateau due to the Miller effect allows to mirror the current to be detected whenever the Power MOSFET operates in saturation. In this way, the mirrored current is not dependent on the drain-source voltage and the RFI that reaches the drain terminal of the Power MOSFET does not strongly influence the operation of the current sensor. Furthermore, there is no need to connect any amplifier to the drain terminal of the Power MOSFET, hence eliminating a barrier on the overall current sensor performance. The operation of the new current sensing circuit and that of a conventional current sensor have been compared in time-domain simulations. Since the novel sensor operates during the switching transient, it provides a faster current detection than the traditional sensor. Whereas the amplifier usually limits the performance of the SenseFET-technique, no such issue has to be considered for the new sensor. The susceptibility of the proposed current monitoring solution has been evaluated through time-domain simulations and compared with that of a conventional current sensor. The analyses carried out in this work have shown a significant improvement in the immunity to RFI in the range 1 MHz-1 GHz that the new proposed solution enables.

#### References

- 1. Murari, B.; Bertotti, F. Smart Power ICs; Springer: Berlin, Germany, 1995.

- 2. Baliga, B.J. Fundamentals of Power Semiconductor Devices; Springer: New York, NY, USA, 2008.

- Richelli, A. Increasing EMI immunity in novel low-voltage CMOS OpAmps. *IEEE Trans. EMC* 2012, 54, 947–950.

- 4. Fiori, F. Susceptibility of CMOS voltage comparators to radio frequency interference. *IEEE Trans. EMC* **2012**, *54*, 434–442.

- 5. Aiello, O.; Fiori, F. On the susceptibility of embedded thermal shutdown circuit to radio frequency interference. *IEEE Trans. EMC* **2012**, *54*, 405–412.

- 6. Fiori, F.; Crovetti, P.S. Complementary differential pair with high immunity to RFI. *IEEE Electron*. *Lett.* **2002**, *38*, 1663–1664.

- 7. Redoute, J.M.; Steyaert, M. *EMC of Analog Integrated Circuits*; Springer: New York, NY, USA, January 2010.

- Ramdani, M.; Sicard, E.; Boyer, A.; Ben Dhia, S.; Whalen, J.J.; Hubing, T.H.; Coenen, M.; Wada, O. The electromagnetic compatibility of integrated circuits—Past, present and future. *IEEE Trans. EMC* 2009, *51*, 78–100.

- 9. Bona, C.; Fiori, F.L. A new filtering technique that makes power transistors immune to EMI. *IEEE Trans. Power Electron.* **2011**, *26*, 2946–2955.

- Jovic, O.; Stuermer, U.; Wilkening, W.; Maier, C.; Baric, A. Susceptibility of PMOS Transistors under High RF Excitations at Source Pin. In *Proceedings of the 20th International Zurich Symposium*, Zurich, Swiss, 12–16 January 2009; Volume 58, pp. 401–404.

- 11. Patel, A.; Ferdowsi, M. Current sensing for automotive electronics? A survey. *IEEE Trans. Veh. Technol.* **2009**, *58*, 4108–4119.

- 12. Fai, L.C.; Mok, P.K.T. A monolithic current-mode CMOS DC-DC converter with on-chip current-sensing technique. *IEEE J. Solid State Circ.* **2004**, *39*, 3–14.

- Chen, J.J.; Su, J.H.; Lin, H. Y.; Chang, C.C.; Lee, Y.; Chen, T.C.; Wang, H.C.; Chang, K.S.; Lin, P.S. Integrated current sensing circuits suitable for step-down DC-DC converters. *IEEE Electron. Lett.* 2004, 40, 200–202.

- 14. Leung, C.Y.; Mok, P.K.T.; Leung, K.N.; Chan, M. An integrated CMOS current-sensing circuit for low-voltage current-mode buck regulator. *IEEE Trans. Circ. Syst.* **2005**, *52*, 394–397.

- Dake, T.; Ozalevli, E. A precision high-voltage current sensing circuit. *IEEE Trans. Circ. Syst.* 2008, 55, 1197–1202.

- 16. Yuan B.; Lai, X. On-chip CMOS current-sensing circuit for DC-DC buck converter. *IEEE Electron*. *Lett.* **2009**, *45*, 102–103.

- Mengmeng, D.; Hoi, L. An integrated speed- and accuracy-enhanced CMOS current sensor with dynamically biased shunt feedback for current-mode buck regulators. *IEEE Trans. Circ. Syst.* 2010, 57, 2804–2814.

- 18. Mengmeng, D.; Hoi, L.; Jin, L. A 5-MHz 91% peak-power-efficiency buck regulator with auto-selectable peak- and valley-current control. *IEEE J. Solid State Circ.* **2011**, *46*, 1928–1939.

- 19. Leung, C.Y.; Mok, P.K.T.; Leung, K.N. A 1-V integrated current-mode boost converter in standard 3.3/5-V CMOS technologies. *IEEE J. Solid State Circ.* **2005**, *40*, 2265–2274.

- Sail, E.; Vesterbacka, M. Thermometer-to-Binary Decoders for Flash Analog-to-Digital Converters. In *Proceedings of the 18th European Conference on Circuit Theory and Design*, Seville, Spain, 26–30 August 2007; pp. 240–243.

- 21. Road Vehicles: Component Test Method for Electrical Disturbances from Narrowband Radiated Electromagnetic Energy. Part 4: Bulk Current Injection (BCI). The International standard ISO 11452-4; ARRB Group Limited: Vermont South, Australia, 2001.

© 2013 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution license (http://creativecommons.org/licenses/by/3.0/).