#### Lehigh University Lehigh Preserve

Theses and Dissertations

1991

# A study of DC-DC converters with focus on analysis techniques and current mode control

Douglas B. Lebo *Lehigh University*

Follow this and additional works at: https://preserve.lehigh.edu/etd Part of the <u>Electrical and Computer Engineering Commons</u>

**Recommended** Citation

Lebo, Douglas B., "A study of DC-DC converters with focus on analysis techniques and current mode control" (1991). *Theses and Dissertations*. 5460. https://preserve.lehigh.edu/etd/5460

This Thesis is brought to you for free and open access by Lehigh Preserve. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of Lehigh Preserve. For more information, please contact preserve@lehigh.edu.

## A Study of DC-DC Converters

# With Focus on Analysis Techniques and Current Mode Control

by

Douglas B. Lebo

A Thesis

Presented to the Graduate Committee

of

Lehigh University

in Candidacy for the Degree of

Master of Science

in

Electrical Engineering

Lehigh University

This thesis is accepted and approved in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering.

VA sør in charge, Α

Lauve

5/6/91

Date

CSEE Department Chairperson.

ii

## Acknowledgments

I would like to thank the following people for motivating me to write this paper:

My wife, for putting up with my physical and sometimes mental absence while working on, or thinking about this paper; and for pushing me to finish what was started.

My parents, for encouraging me to pursue higher education; and providing me with the opportunity to do so.

My advisor, who taught me a great deal when I was an undergraduate. Who shed light on the process of writing this paper; and gave me insight into the problem at hand, yet let me pursue the topic without interference.

My Grandfather, Homer C. Althouse, who got me interested in electronics many years ago; and who taught me much about problem solving and "Good old down home ingenuity". I dedicate this work in memory of him.

# **Table of Contents**

| Abstract                                              |    |

|-------------------------------------------------------|----|

| Introduction                                          |    |

| Basic Topologies                                      |    |

| The Buck Converter                                    | 7  |

| The Flyback Boost Converter                           | 10 |

| The Boost - Buck Converter                            |    |

| Creation of "New" Topologies from Existing Ones       |    |

| The CUK Converter                                     |    |

| Discontinuous Operation                               |    |

| Current mode control                                  |    |

| Analysis Techniques                                   |    |

| State Space Averaging                                 |    |

| Extending State Space Averaging into a Computer Model |    |

| Continuous Mode Boost Converter Model                 |    |

| Discontinuous Mode Boost Model                        |    |

| Modeling Current Mode Control                         |    |

| Integrating Discontinuous and Continuous Mode Models  |    |

| Design of a Boost Converter With the Aid of Pspice    |    |

| Design Verification                                   |    |

| Conclusion                                            |    |

| Bibliography                                          |    |

| Vita                                                  |    |

# List of Figures

| Figure 1 - Pulse Width Modulation Definitions                                                       |

|-----------------------------------------------------------------------------------------------------|

| Figure 2 - Buck Converter                                                                           |

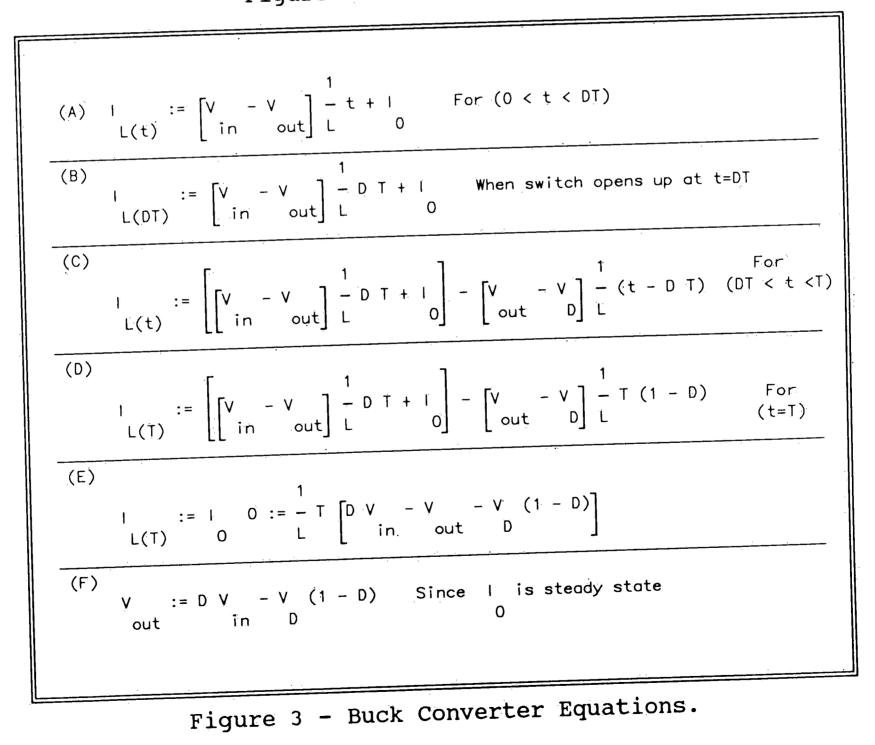

| Figure 3 - Buck Converter Equations                                                                 |

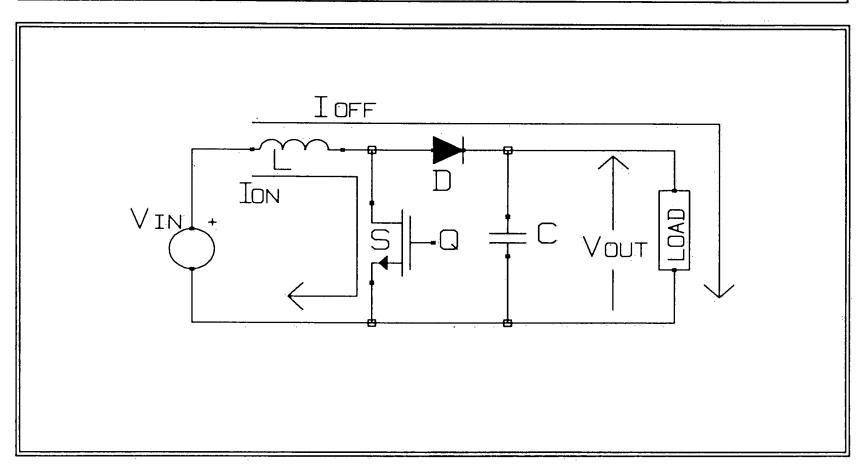

| Figure 4 - Boost Converter                                                                          |

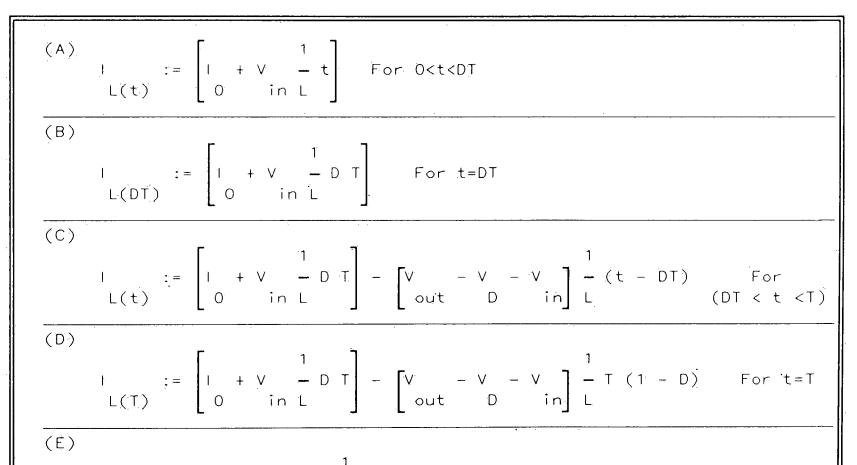

| Figure 5 - Boost Converter Equations                                                                |

| Figure 6 - Boost - Buck Converter                                                                   |

| Figure 7 - Boost - Buck Converter Equations                                                         |

| Figure 8 - The Creation of the Boost-Buck Converter from the Boost and Buck<br>Topologies           |

| Figure 9 - The CUK Converter                                                                        |

| Figure 10 - CUK Converter Equations Part 1                                                          |

| Figure 11 - CUK Converter Equations Part 2                                                          |

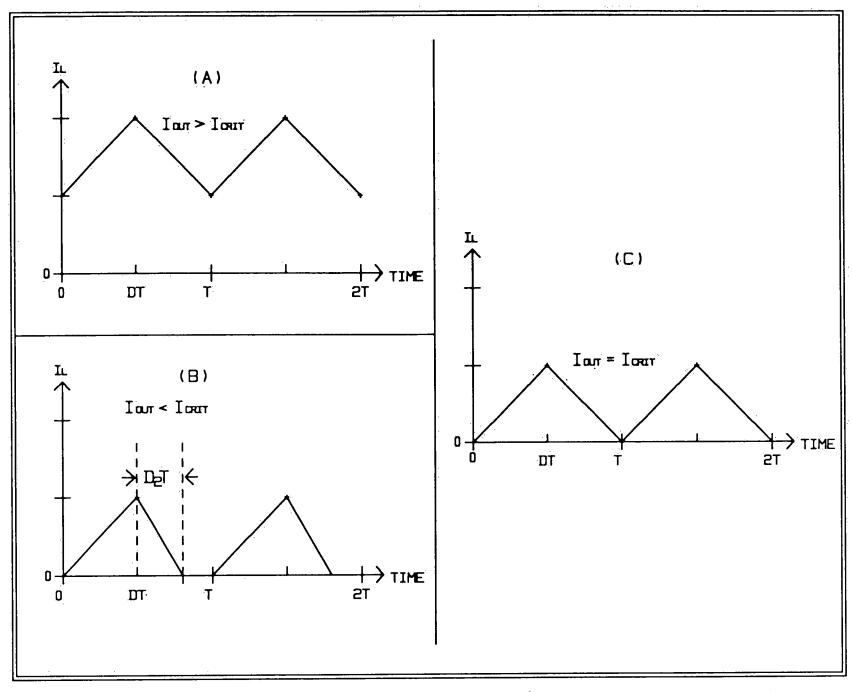

| Figure 12 - Continuous vs Discontinuous Mode Inductor Currents                                      |

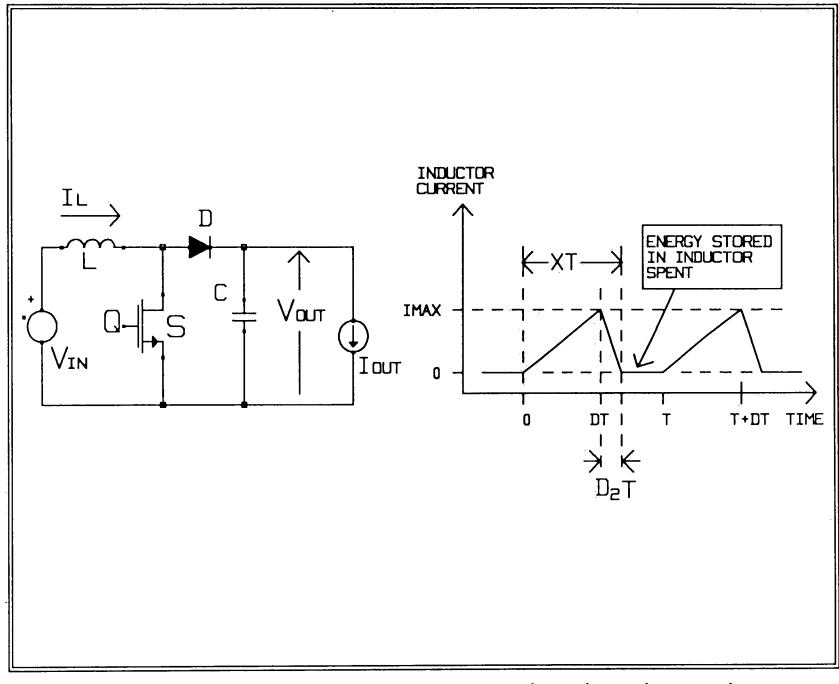

| Figure 13 - Boost Regulator Operating in Discontinuous Mode                                         |

| Figure 14 - Impact of Discontinuous Mode on the Boost Regulator Input to<br>Output Voltage Function |

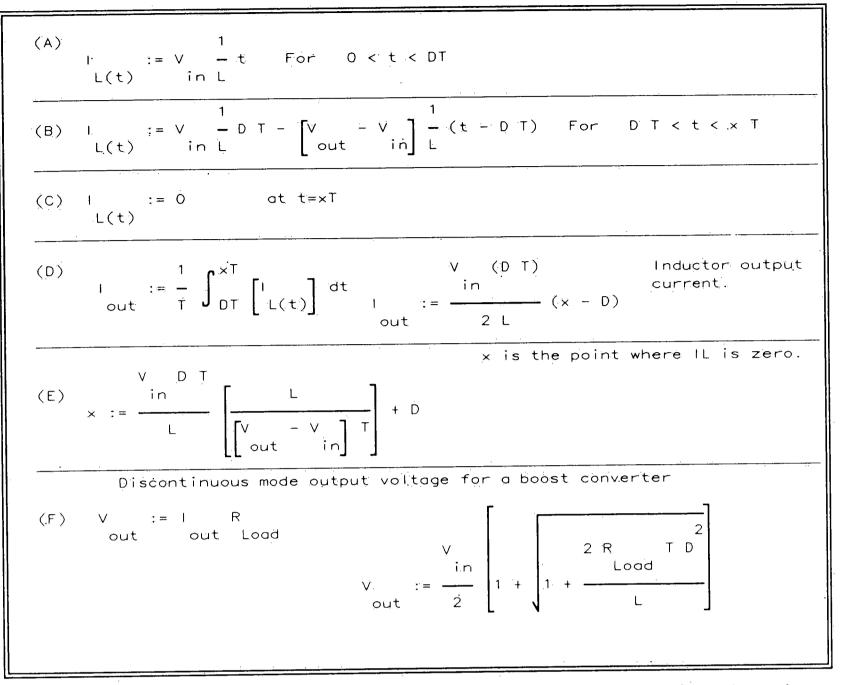

| Figure 15 - Boost-Buck Regulator with a Voltage Feedback Loop                                       |

| Figure 16 - Boost Regulator with Voltage and                                                        |

| Current Feedback. (Current Mode)                                                                    |

| Figure 17 - Boost Regulator with Current Mode Feedback                                              |

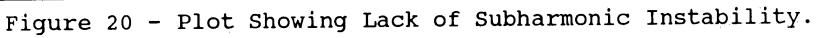

| Figure 18 - Plot Showing Subharmonic Instability                                                    |

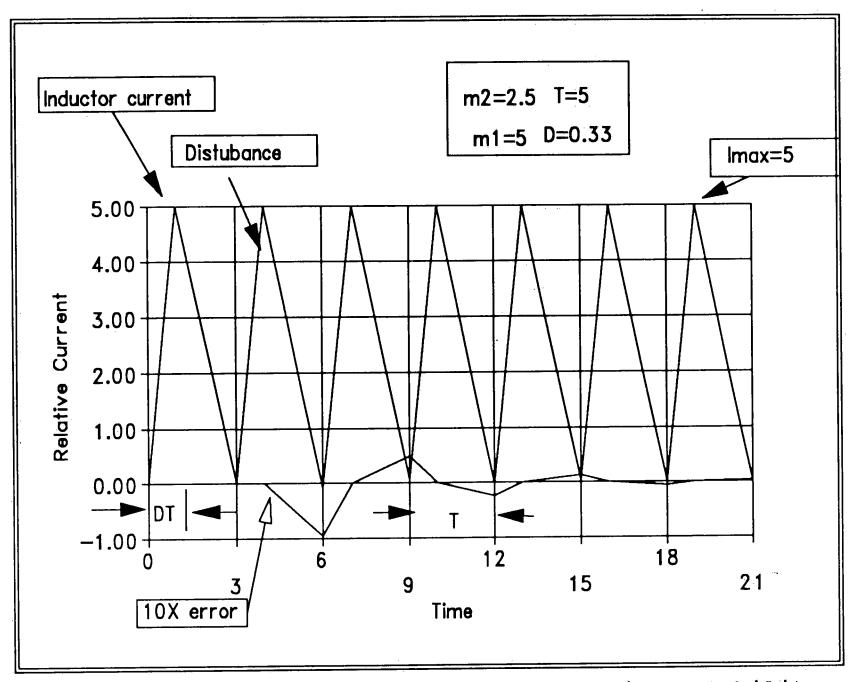

| Figure 19 - Magnified Second Cycle of Previous Plot                                                 |

| Figure 20 - Plot Showing Lack of Subharmonic Instability                                            |

| Figure 21 - Magnified Second Cycle of Previous Plot                                                 |

| Figure 22 - Quantitative Subharmonic Instability Derivation                                         |

| Figure 23 - Slope to Duty Cycle Linkage                                                             |

| Figure 24 - Linear LCR circuit with Conventional and State Notation                                 |

| Figure 25 - Linear State Analysis of a LCR Circuit                                                  |

| Figure 26 - Generalized State Equations for a n Switch Condition Network 42                         |

| Figure 27 - Sampled Data State Equations                                                            |

| Figure 28 - Sampled Data State Equations                                                            |

| Figure 29 - State Equations for a Two Condition System                                              |

| Figure 30 - State Space Averaged Matrix Definitions                                                 |

V

| Figure 31 - State Space Averaged Matrix Definitions Extended                                                                 | 10       |

|------------------------------------------------------------------------------------------------------------------------------|----------|

| to 3 and n Switch Conditions                                                                                                 | 49       |

| Figure 32 - Application of Small Signal Approximation to the Nonlinear                                                       | 50       |

| System.                                                                                                                      |          |

| Figure 33 - Small Signal State Equations                                                                                     |          |

| Figure 34 - Small Signal State Equation Definitions.                                                                         | 52<br>52 |

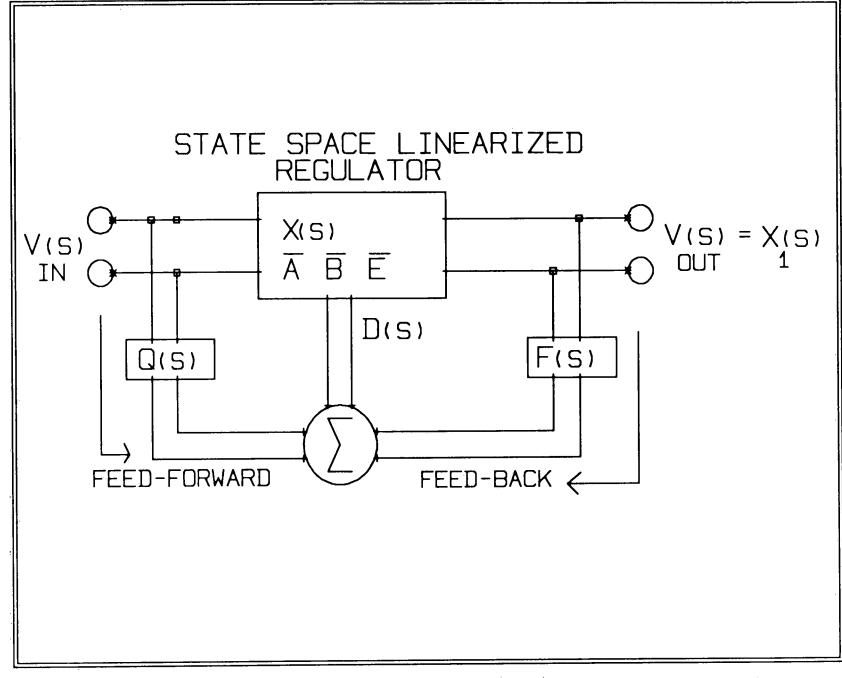

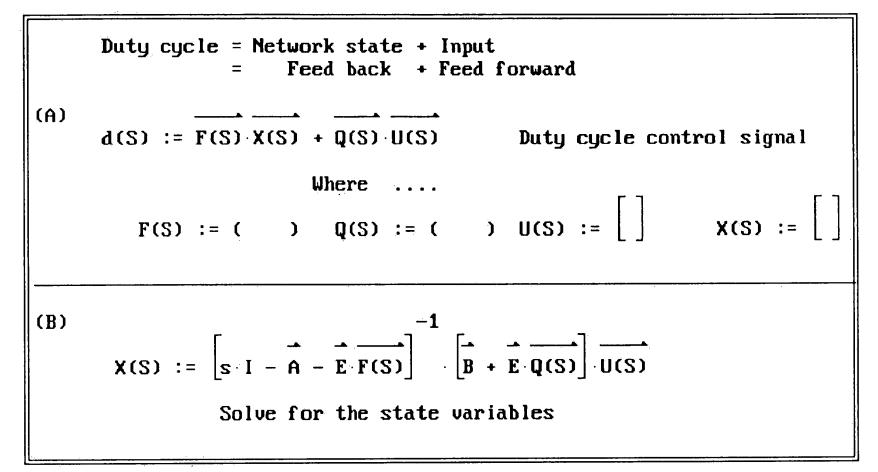

| Figure 35 - Flow Diagram Depicting Feedback and Feedforward Control                                                          | 33       |

| Figure 36 - General State Space Averaged and Linearized System                                                               | 54       |

| Representation.                                                                                                              |          |

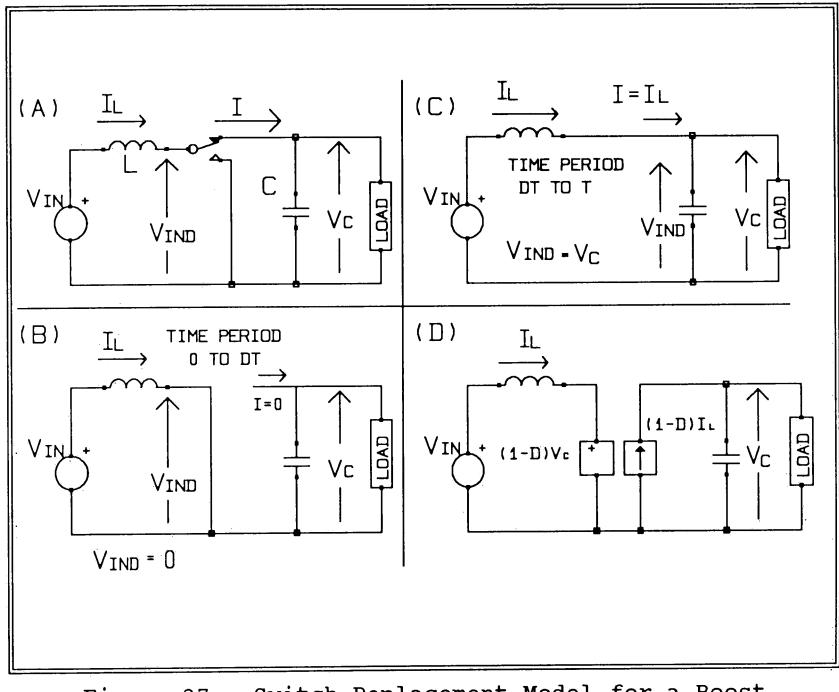

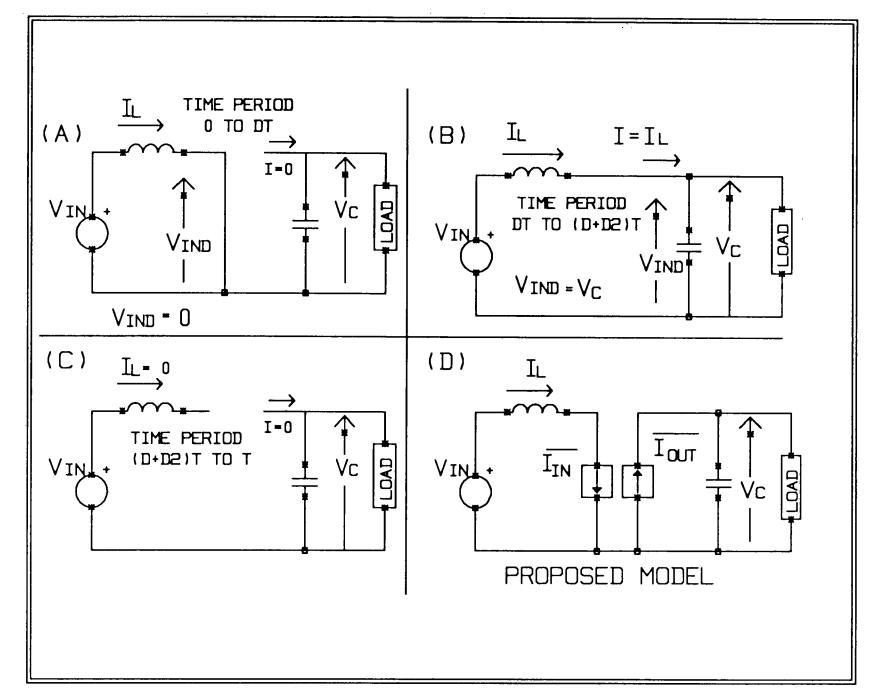

| Figure 37 - Switch Replacement Model for a Boost Converter                                                                   |          |

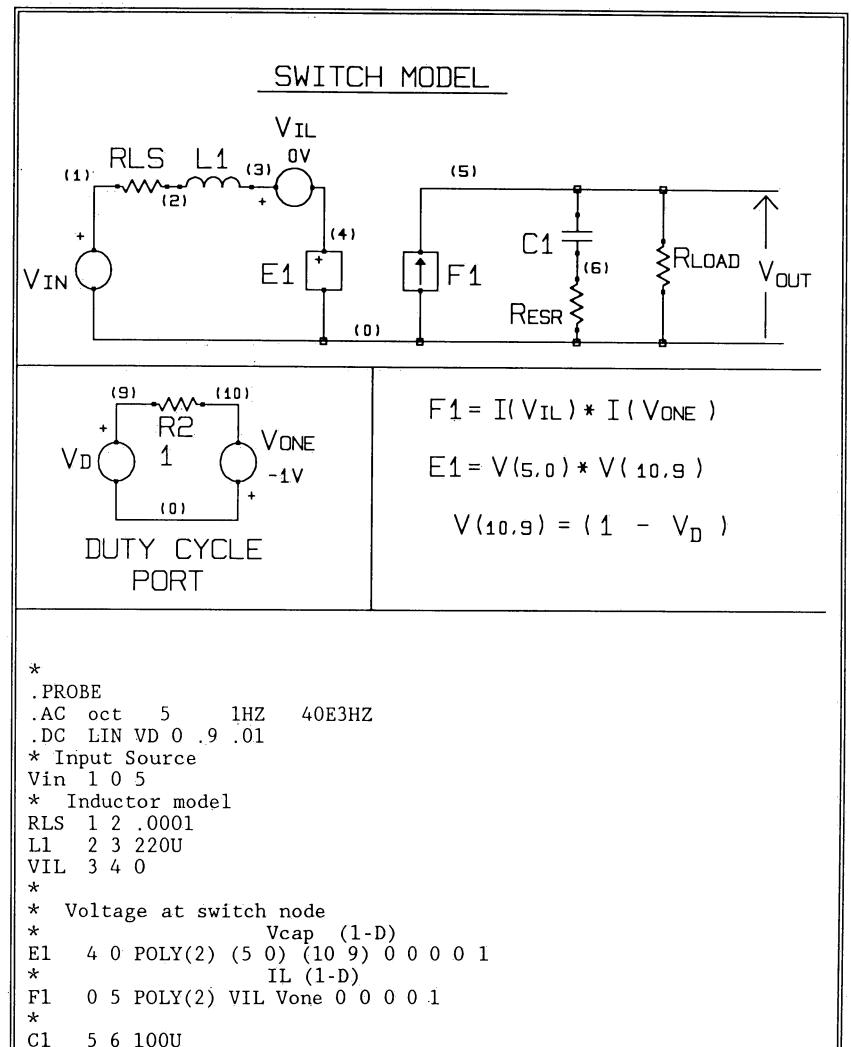

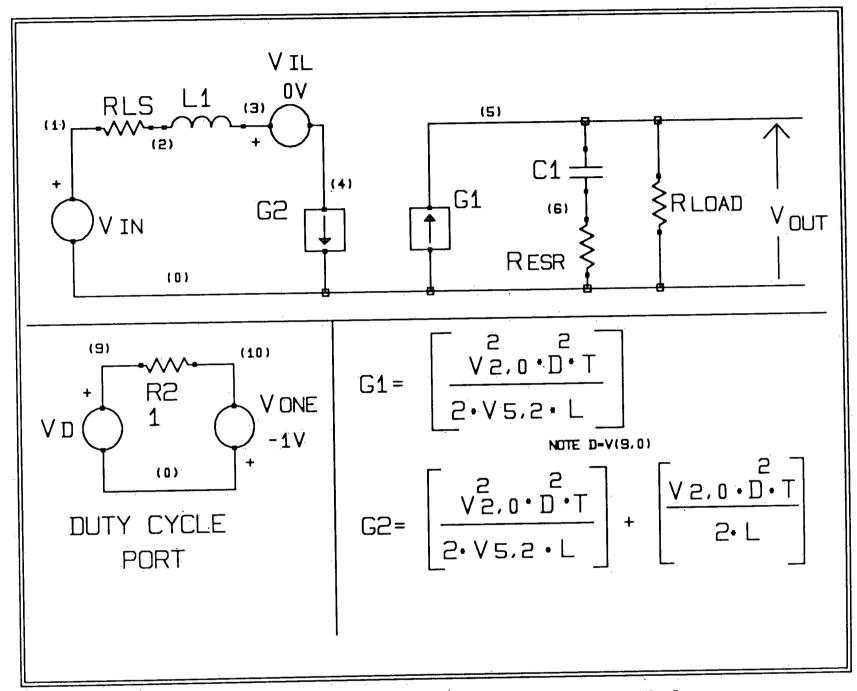

| Figure 38 - Spice Model of a Continuous Mode Duty Cycle Controlled Boos<br>Regulator                                         | 58       |

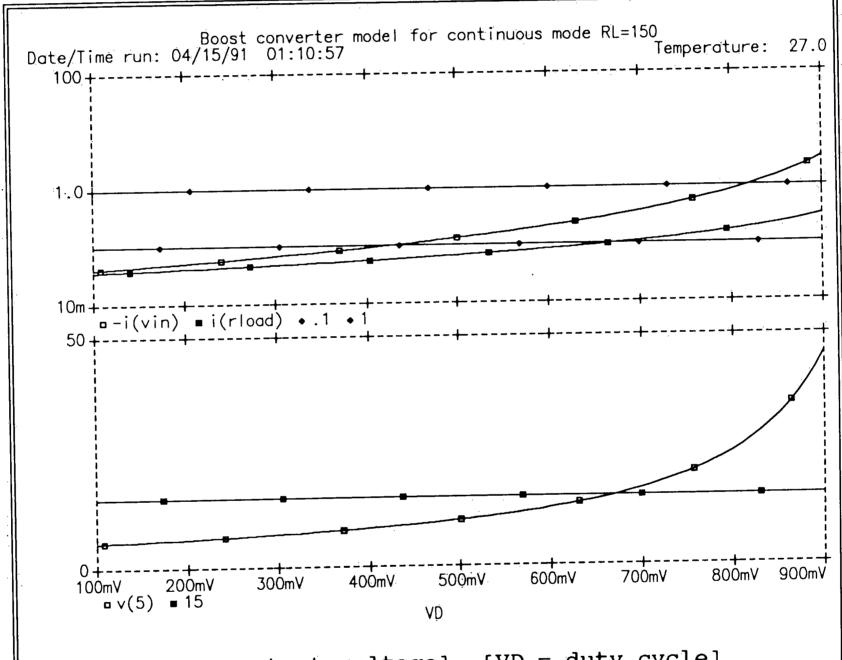

| Figure 39 - Boost Converter Simulation.                                                                                      | 59       |

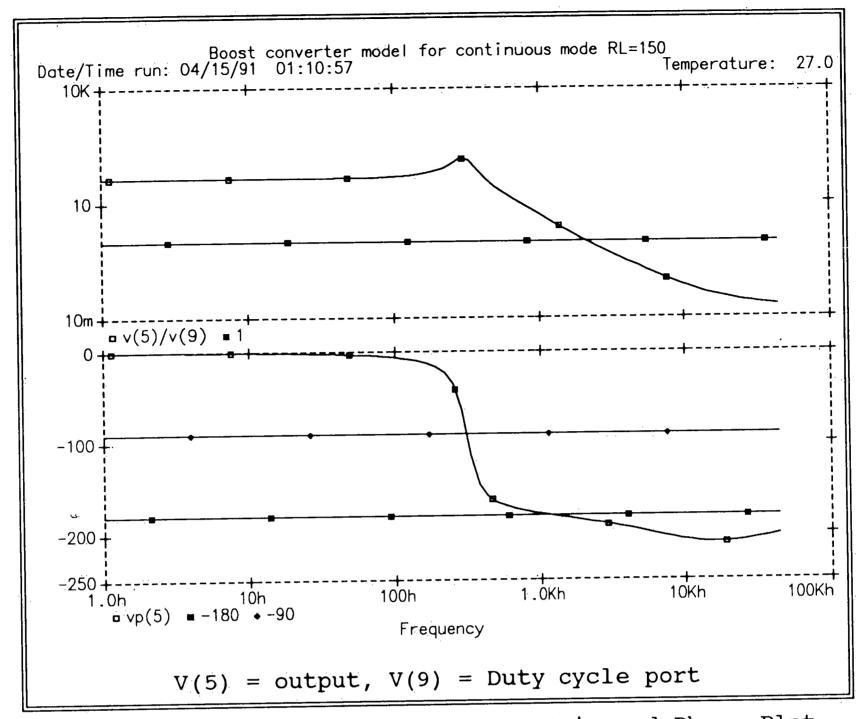

| Figure 39 - Boost Converter Simulation<br>Figure 40 - Pspice Boost Converter Gain and Phase Plot                             | 60       |

| Figure 40 - Pspice Boost Converter Gain and Fiase Figure 41 - Discontinuous Mode Switch Terminal Conditions.                 | 61       |

| Figure 41 - Discontinuous Mode Switch Terminal Conditions<br>Figure 42 - Discontinuous Mode Average Terminal Conditions      | 62       |

| Figure 42 - Discontinuous Mode Average Terminar Conditions<br>Figure 43 - Discontinuous Mode Model                           |          |

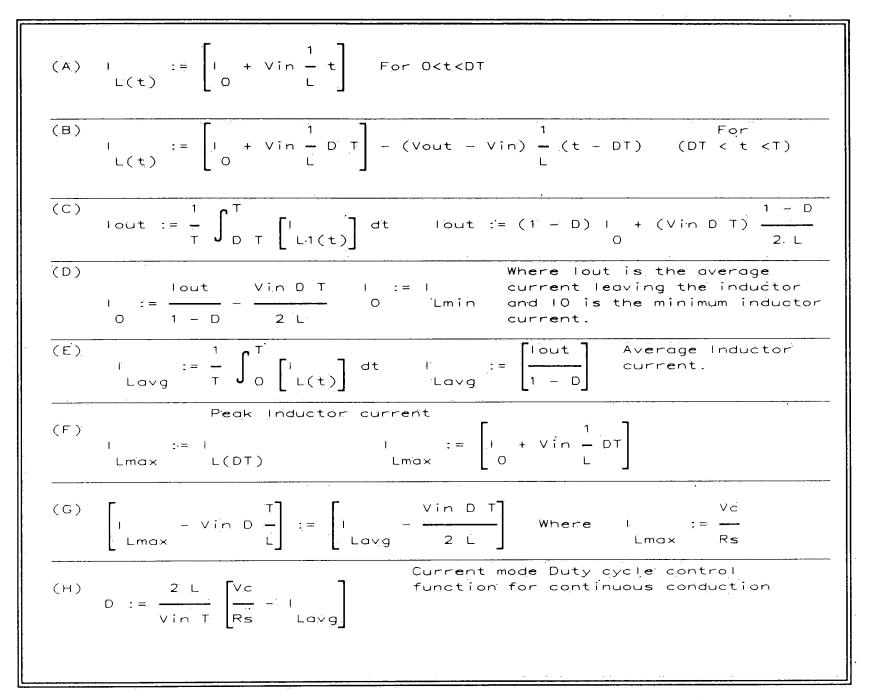

| <sup>°</sup> Figure 43 - Discontinuous Model Model<br>Figure 44 - Duty Cycle to Current Mode Control                         | 64       |

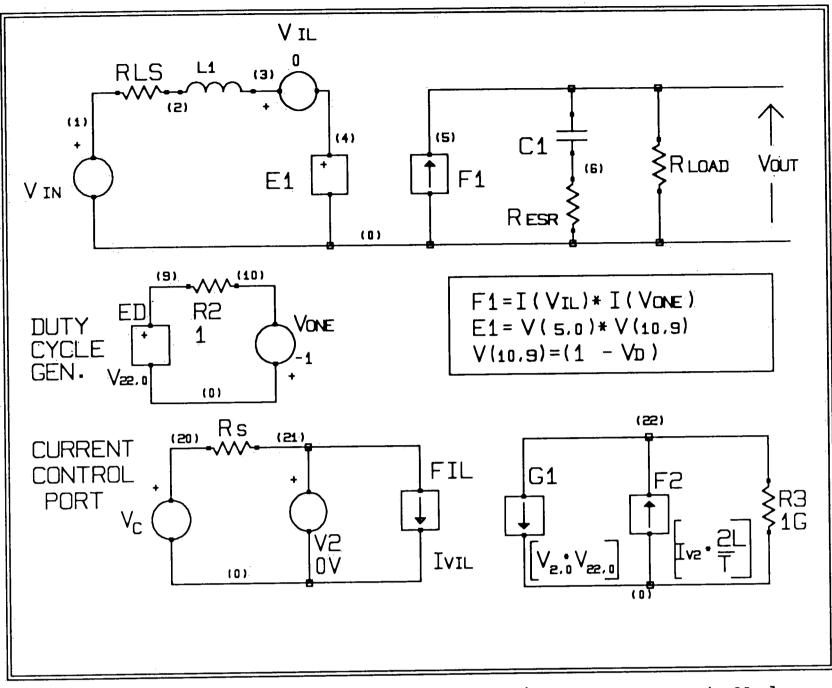

| Figure 44 - Duty Cycle to Current Mode Control<br>Figure 45 - Spice Model of a Continuous Current Mode Controlled Boost      |          |

| Figure 45 - Spice Model of a Continuous Current Mode Controlled Doost<br>Regulator                                           | 66       |

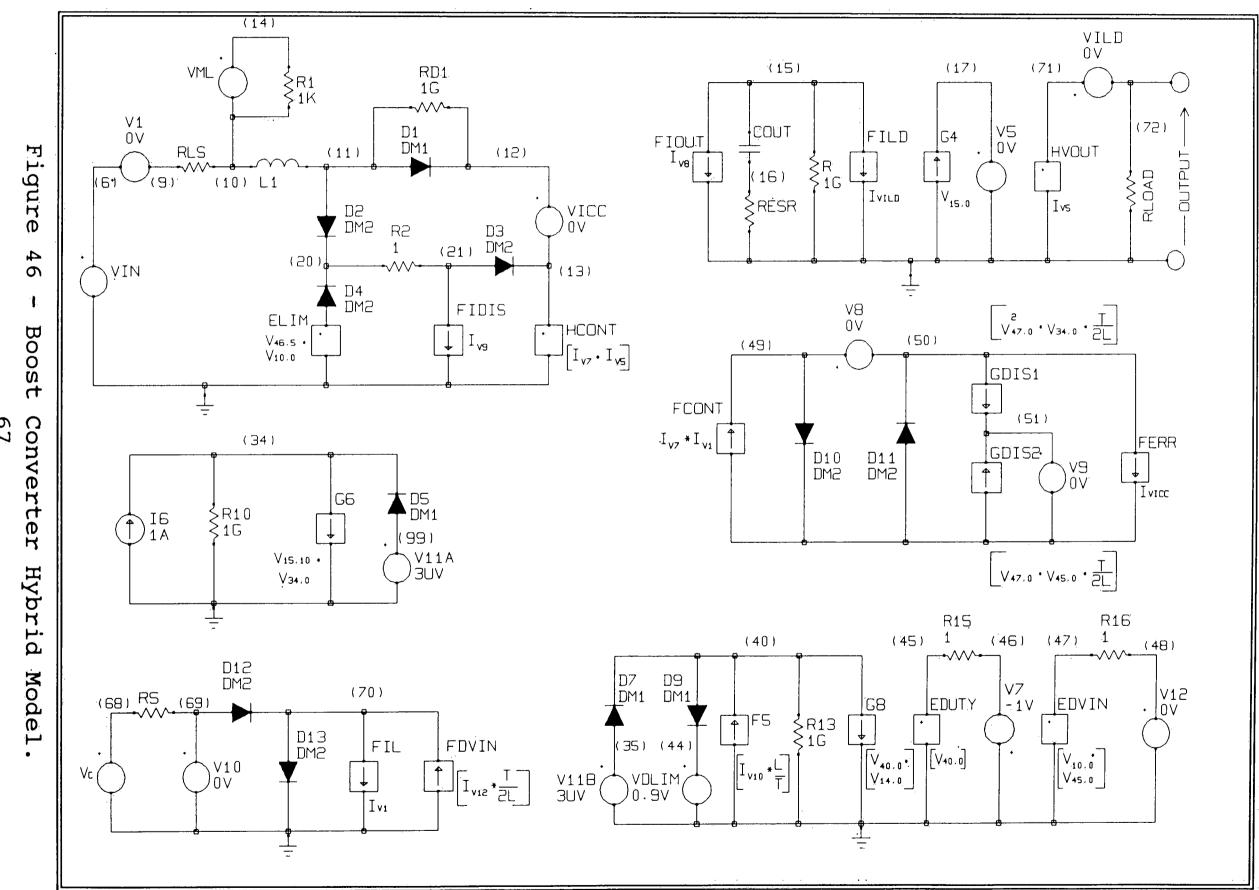

| Figure 46 - Boost Converter Hybrid Model.                                                                                    | 67       |

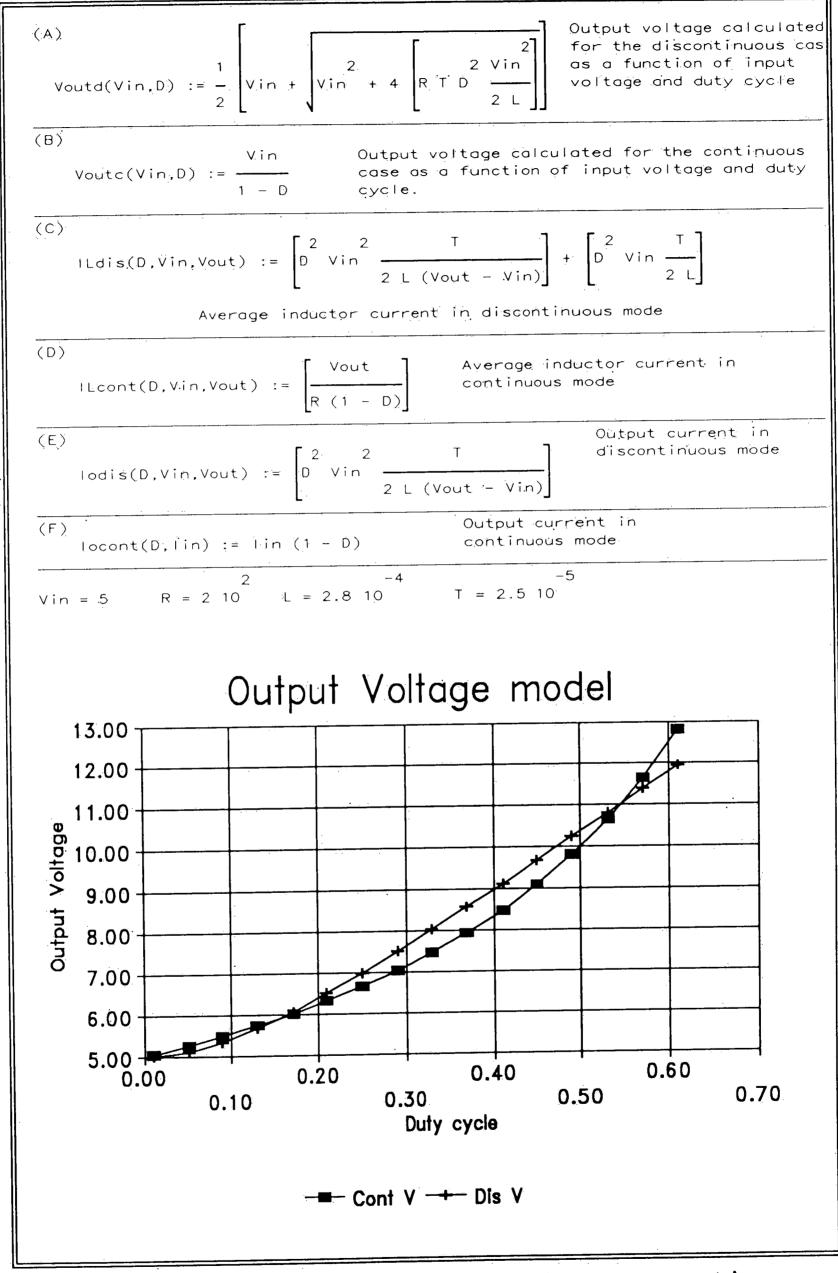

| Figure 46 - Boost Converter Hybrid Model and Figure 47 - Discontinuous vs Continuous Operation                               | 69       |

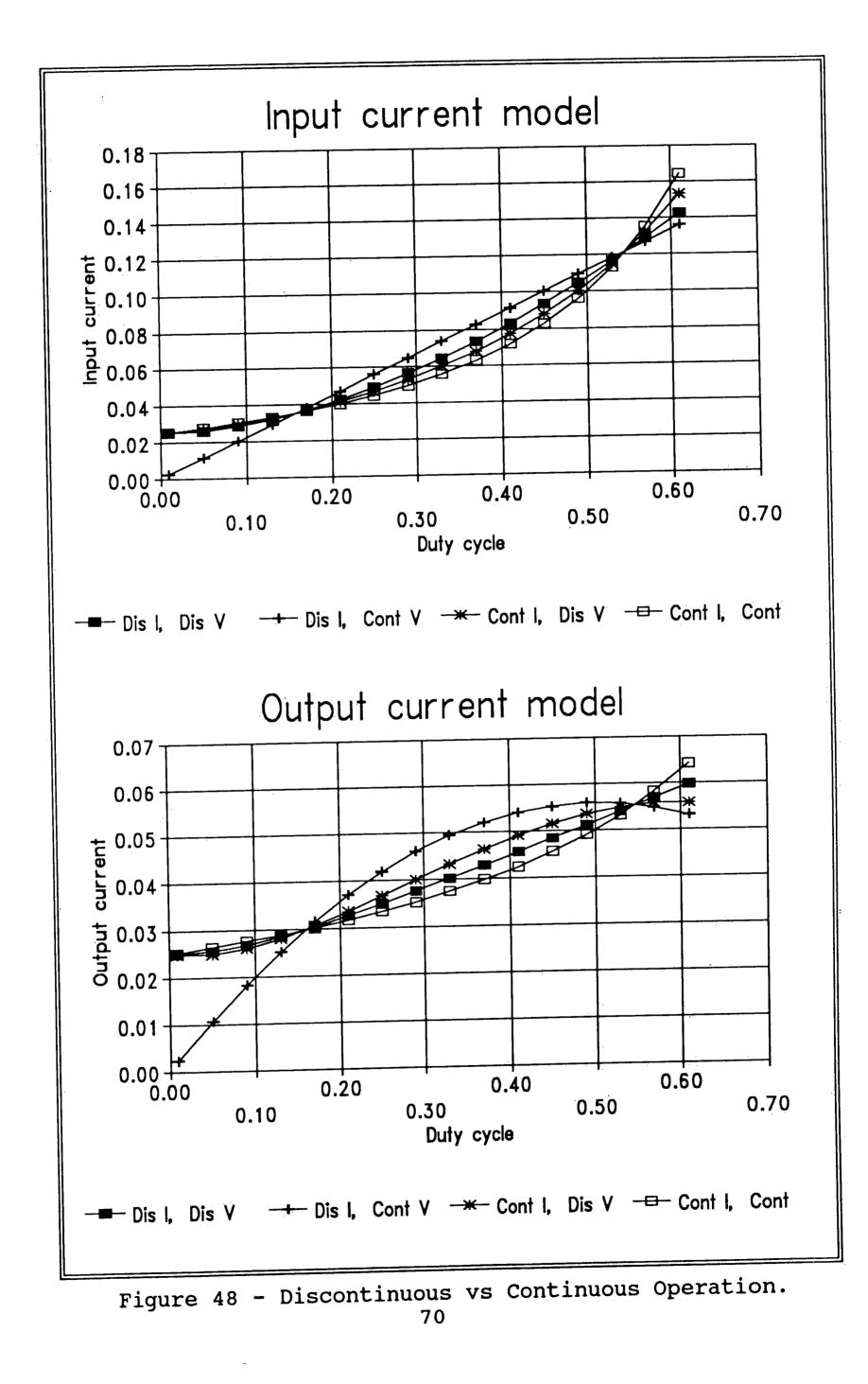

| Figure 47 - Discontinuous vs Continuous Operation                                                                            | 70       |

| Figure 48 - Discontinuous vs Continuous Operations.<br>Figure 49 - Converter Design Specifications                           | 74       |

| Figure 49 - Converter Design Specifications<br>Figure 50 - Design Equations Part 1                                           |          |

| Figure 50 - Design Equations Part 2<br>Figure 51 - Design Equations Part 2                                                   |          |

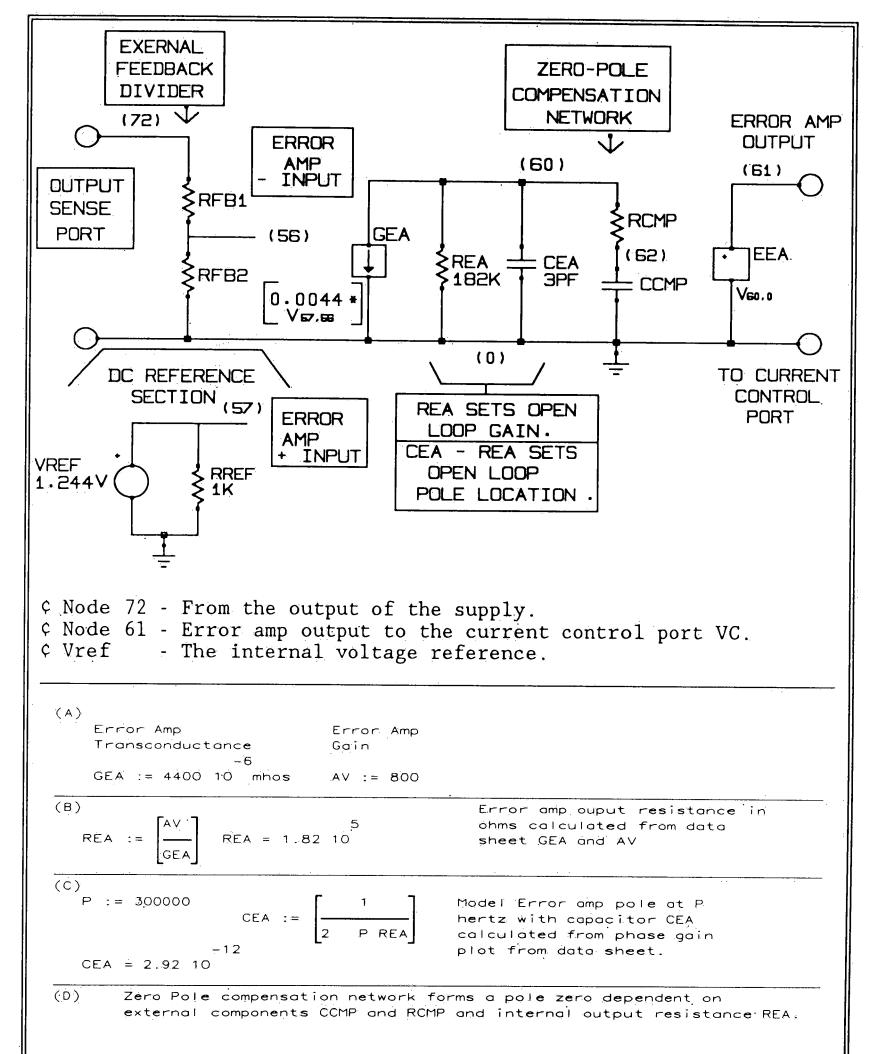

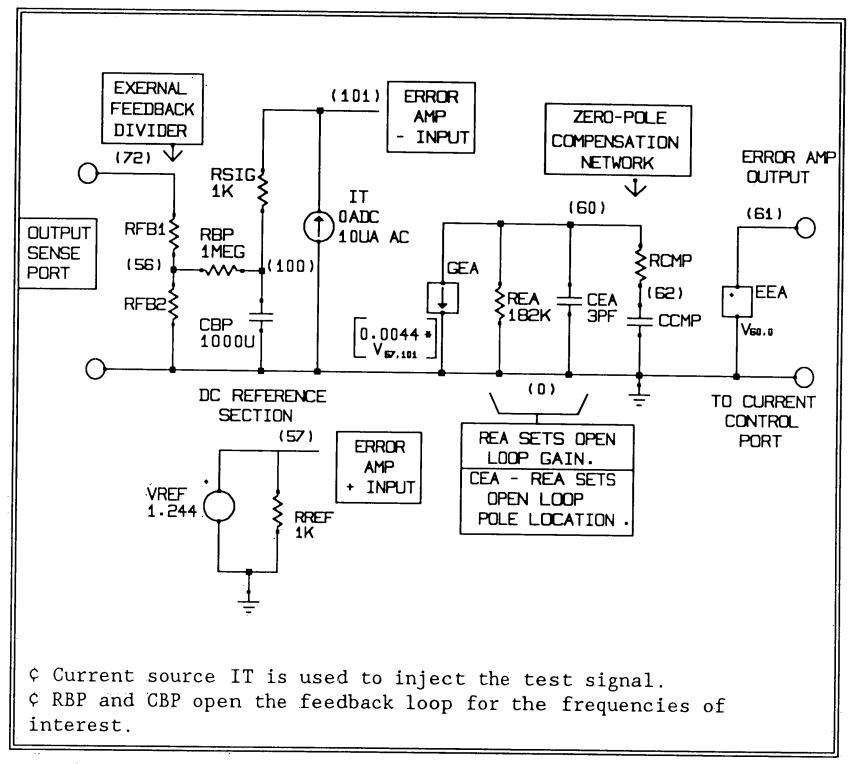

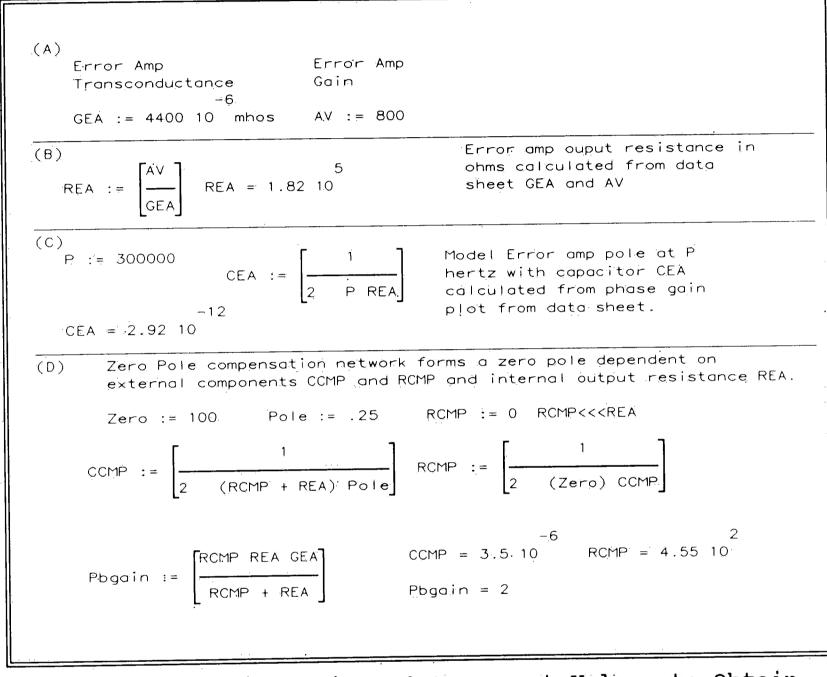

| Figure 51 - Design Equations Fart 2<br>Figure 52 - Calculation of Error Amplifier Model Parameters                           | 80       |

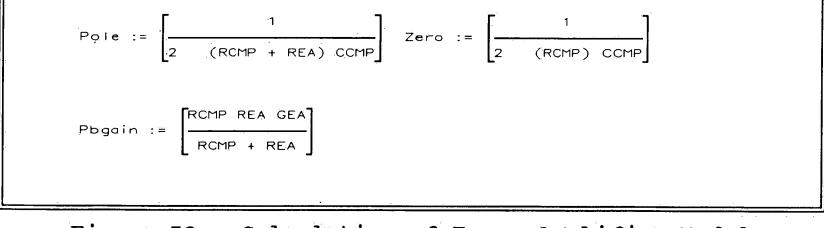

| Figure 52 - Calculation of Error Amplifier Moder Figure 53 - Final Model of Boost Converter                                  | 82       |

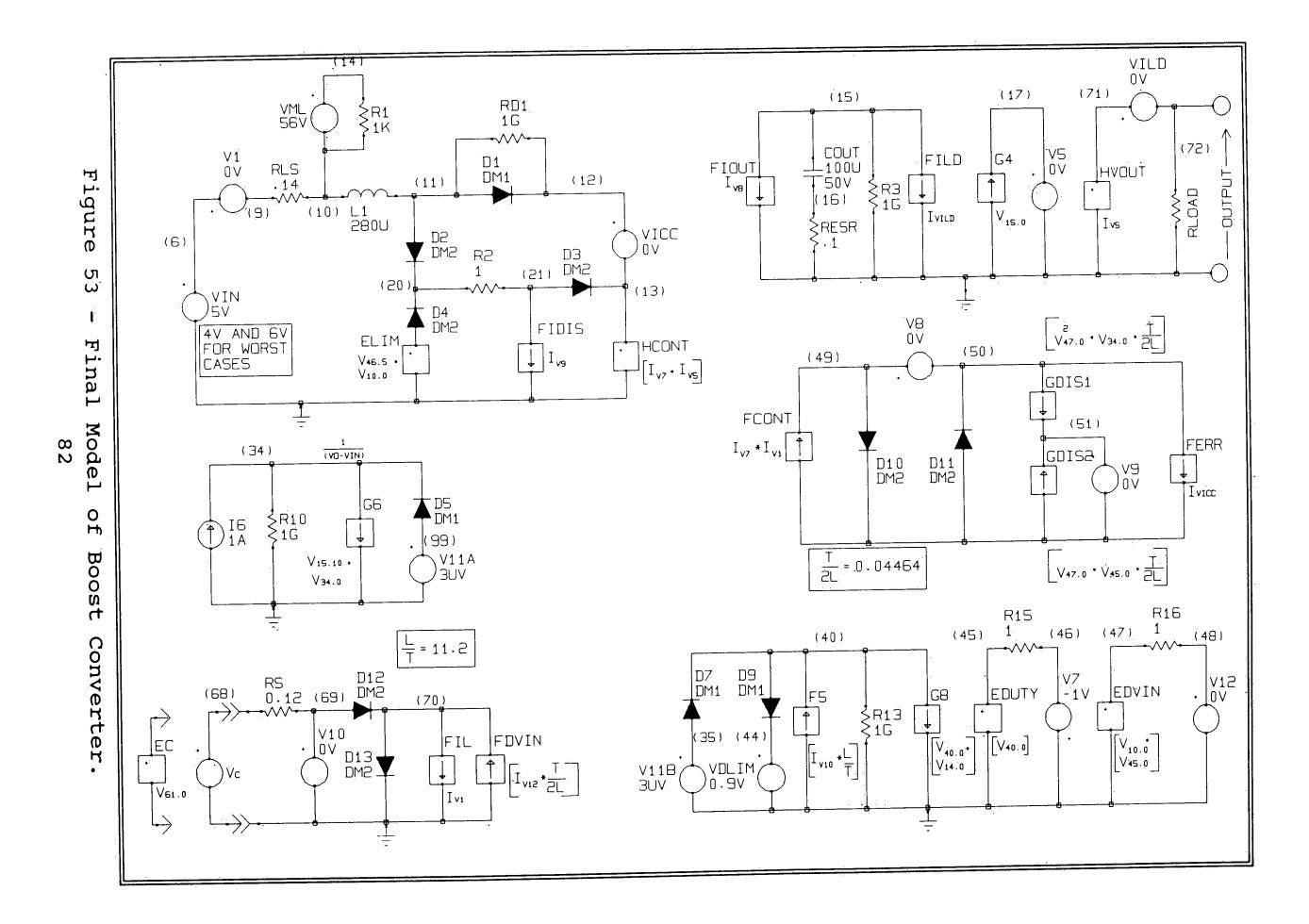

| Figure 53 - Final Model of Boost Converter and Figure 54 - DC simulation of Finished Circuit                                 | 83       |

| Figure 54 - DC simulation of Philshed Cheditanian Simulations                                                                |          |

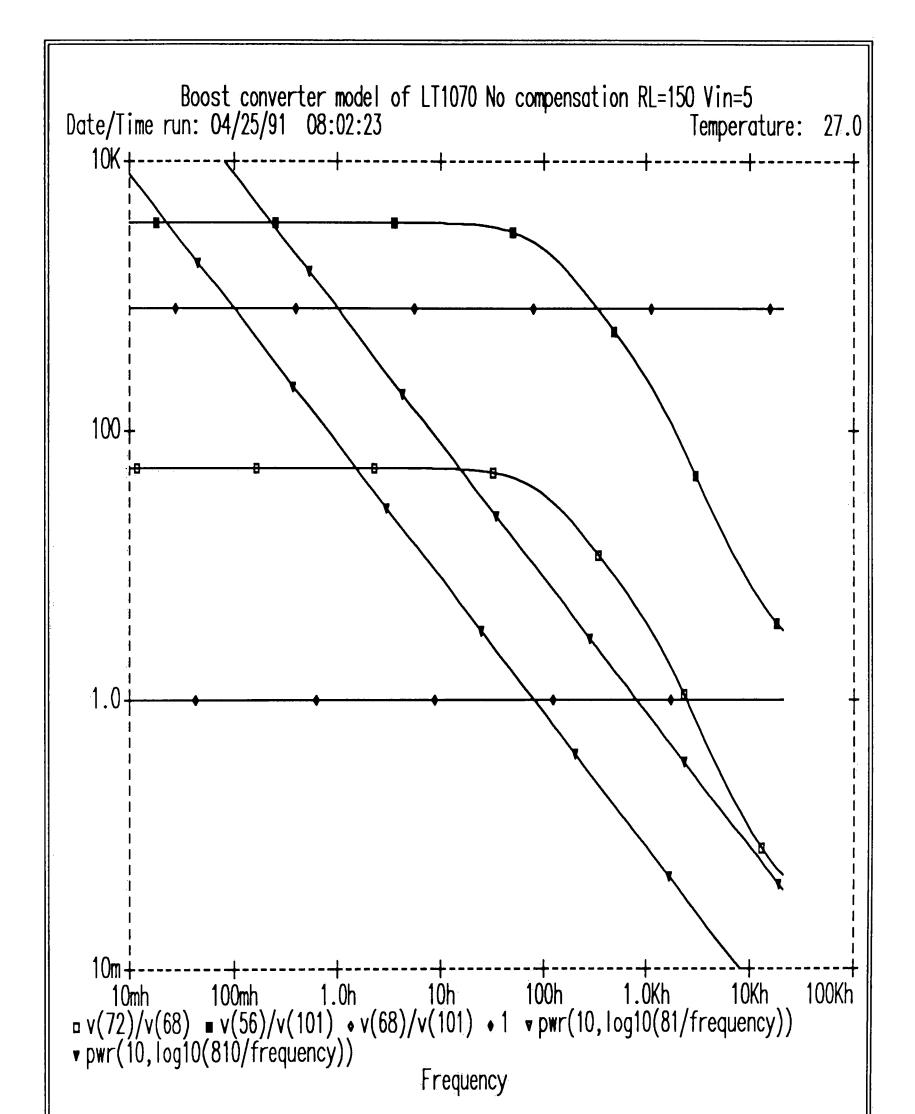

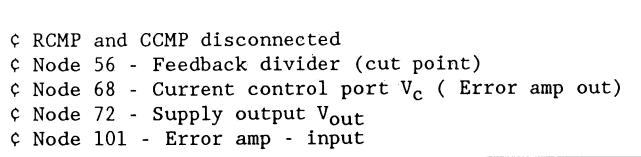

| Figure 55 - Error Amplifier Model for Thase and Gain Stindard Stream Figure 56 - 150 ohm Load Gain Plot With No Compensation |          |

| Figure 56 - 150 ohm Load Gain Flot With No Compensation.                                                                     |          |

| Figure 57 - 150 ohm Load Phase Flot with No Compensation desired Pole Zer                                                    | 0        |

| Figure 58 - Calculation of Component Values to Obtain Desired Pole Zero<br>Location                                          | 89       |

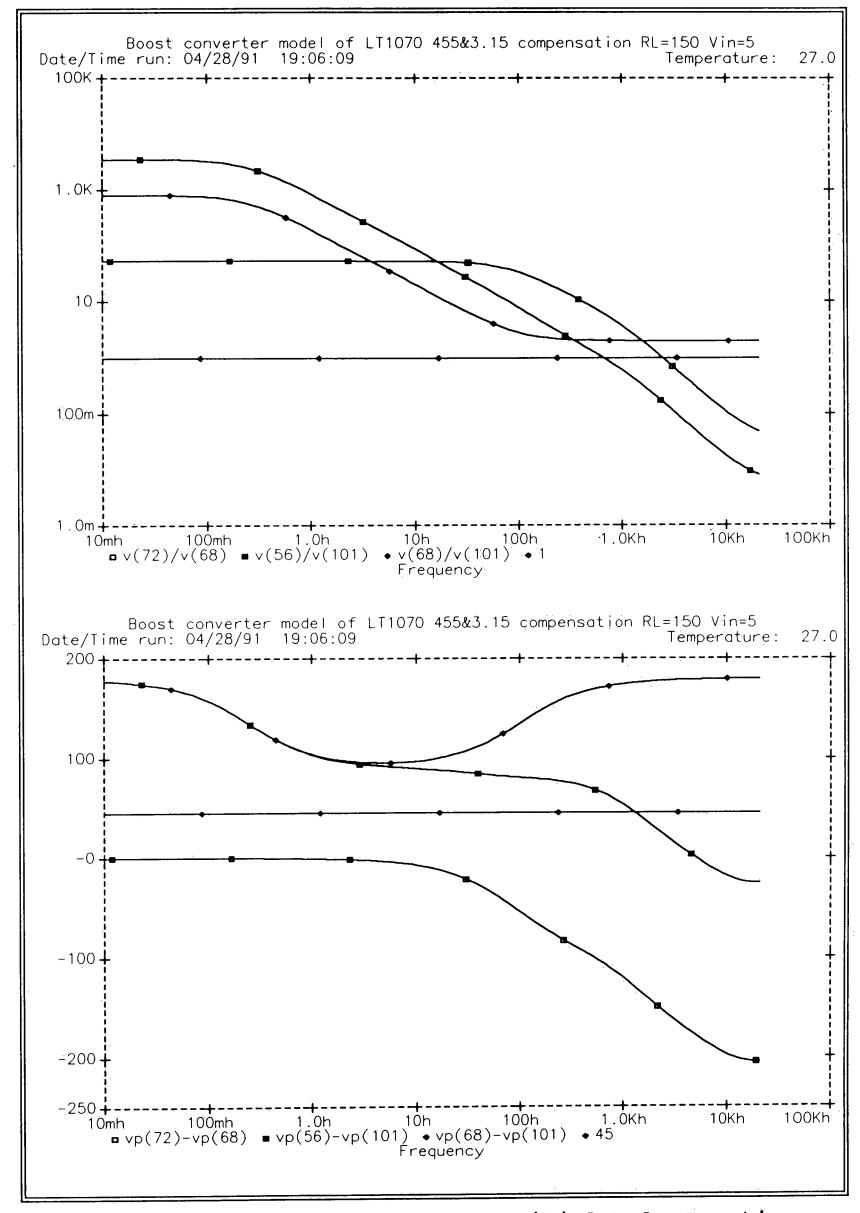

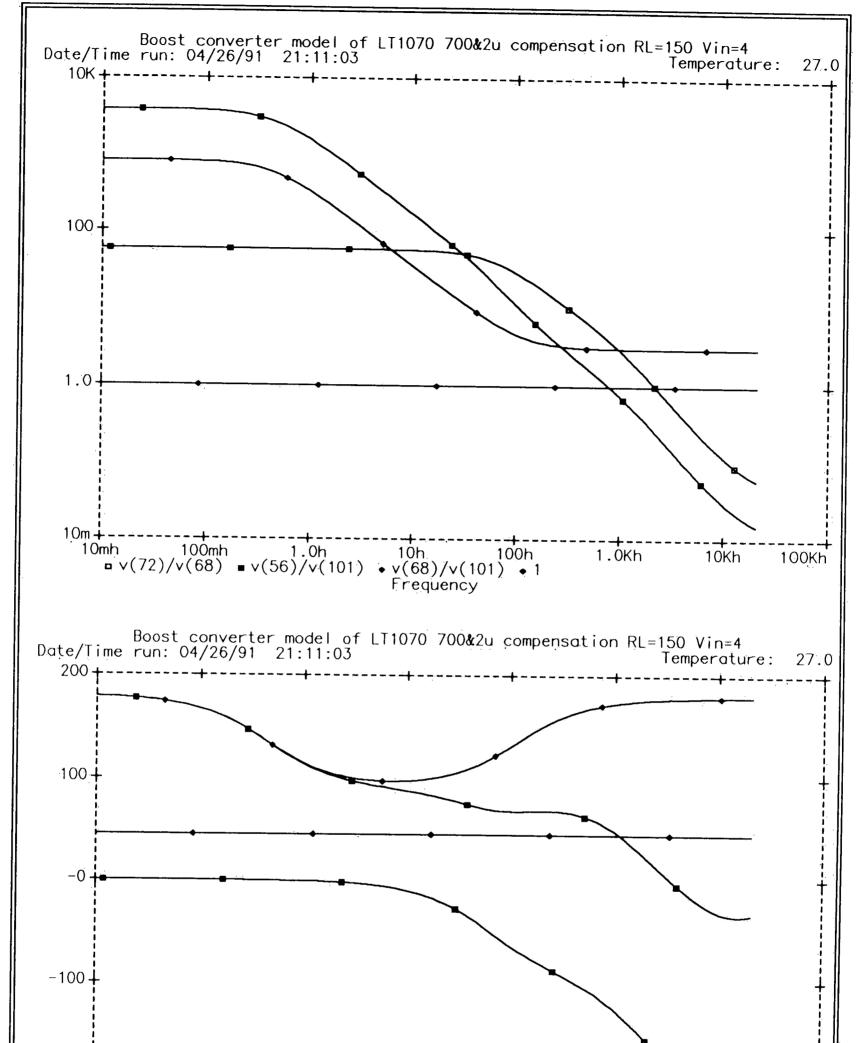

| Figure 59 - Gain and Phase for Initial Pole Location                                                                         |          |

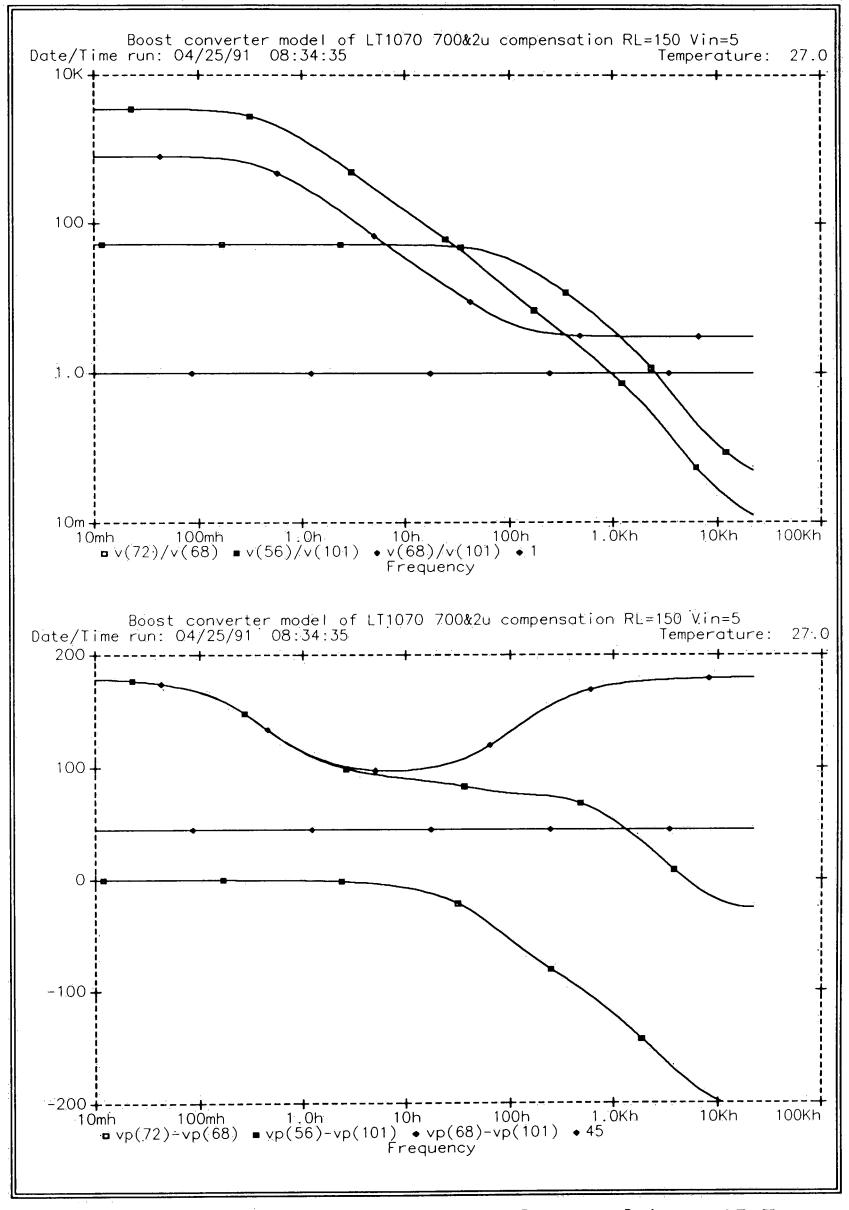

| Figure 60 - Gain and Phase for Pole Moved to 0.45 Hz                                                                         |          |

| rigure ou - Gain and Thase for Fore Moved to the vi                                                                          |          |

| · -                                                                                                                          |          |

.

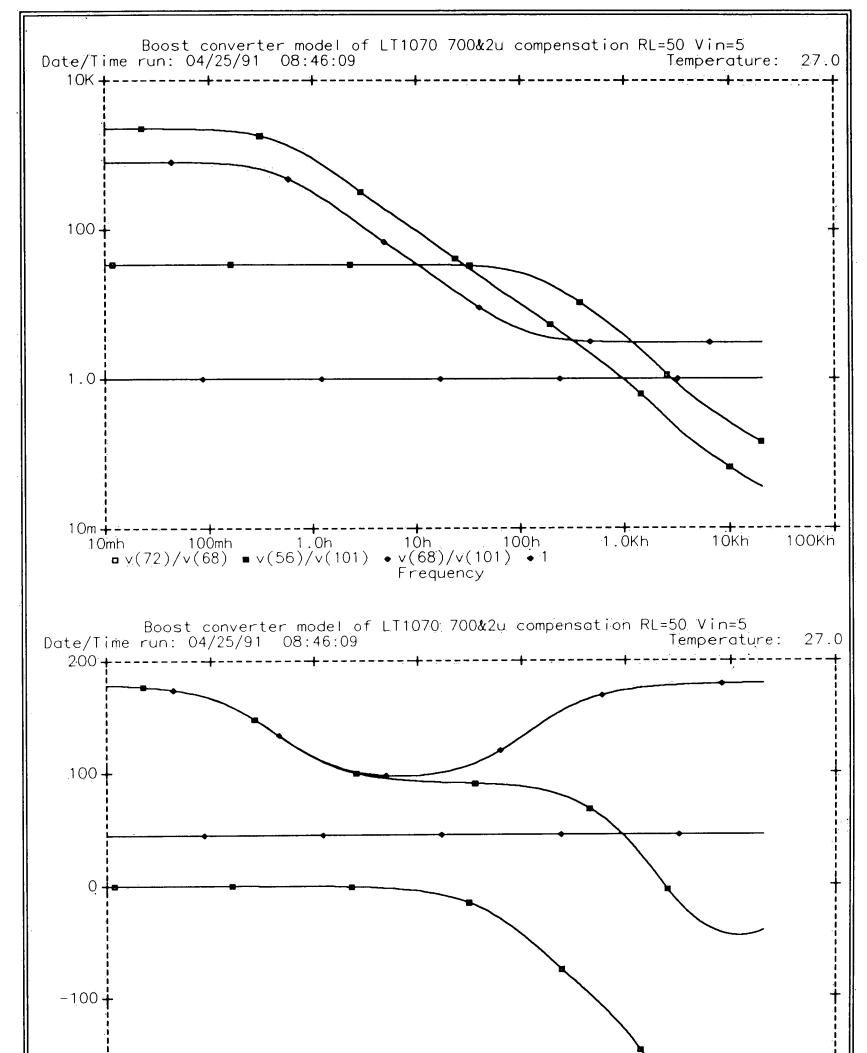

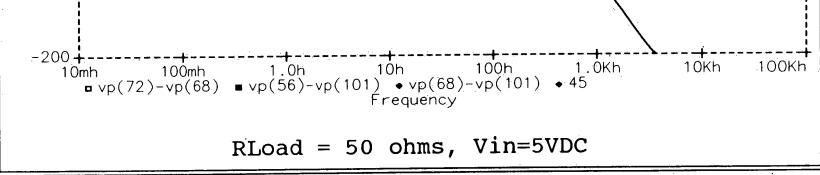

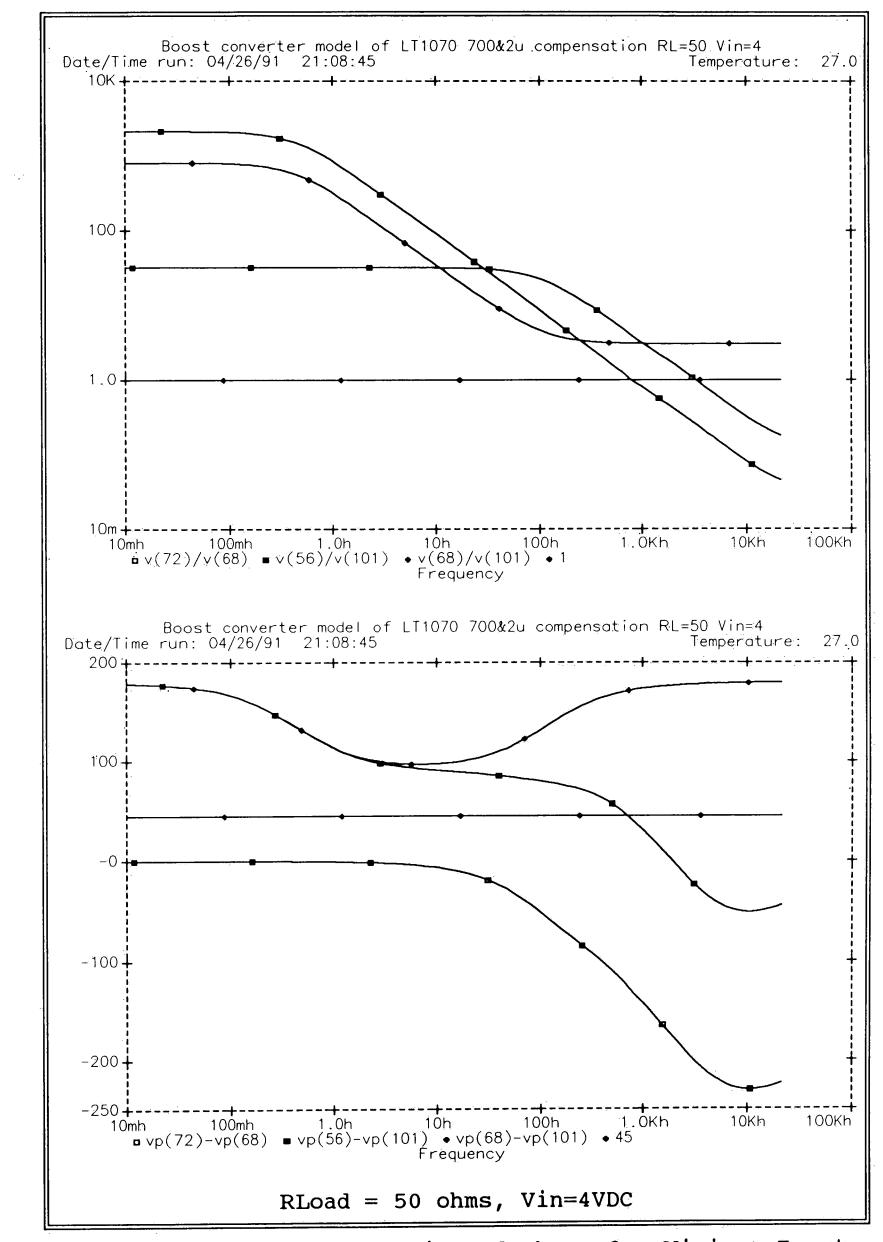

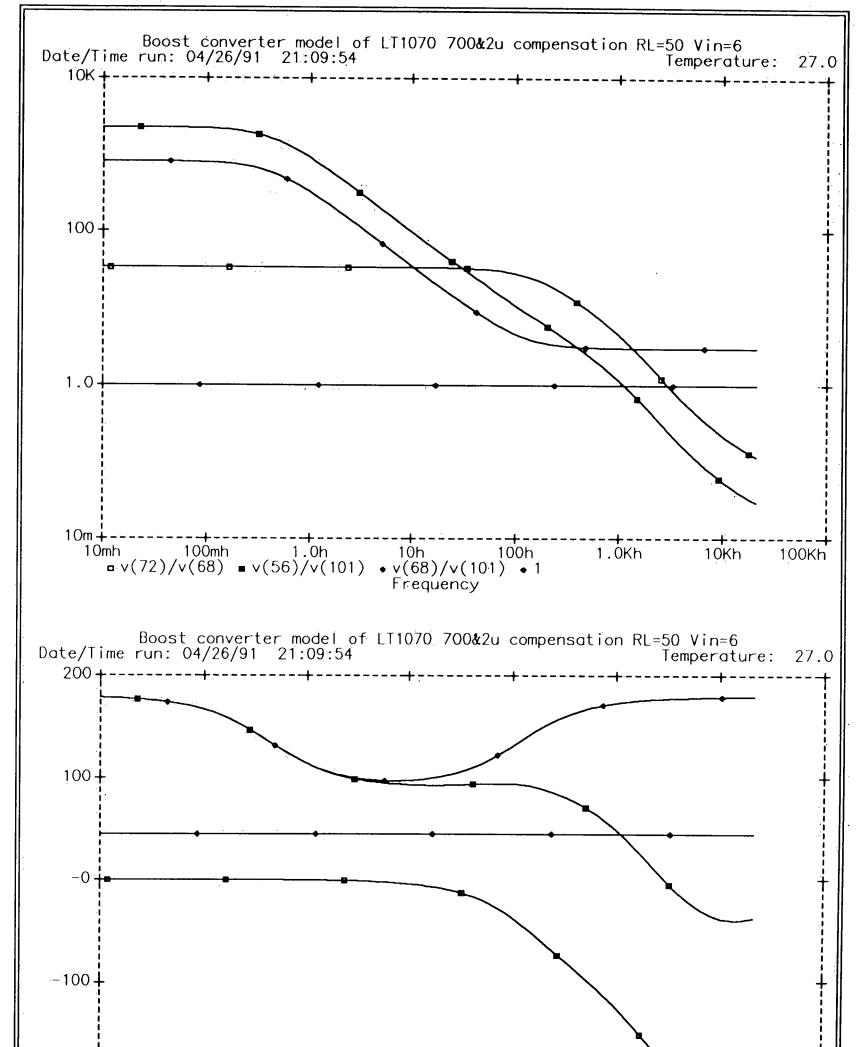

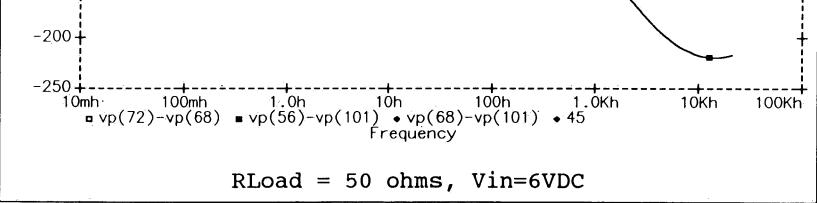

| Figure 61 - 50 ohm Load Gain and Phase for Nominal Input         |     |

|------------------------------------------------------------------|-----|

| Figure 62 - 50 ohm Load Gain and Phase for Minimum Input         |     |

| Figure 63 - 50 ohm Load Gain and Phase for Maximum Input.        |     |

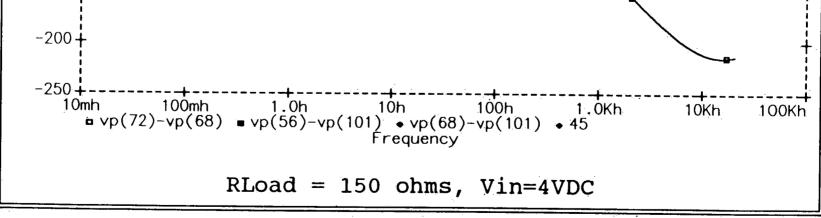

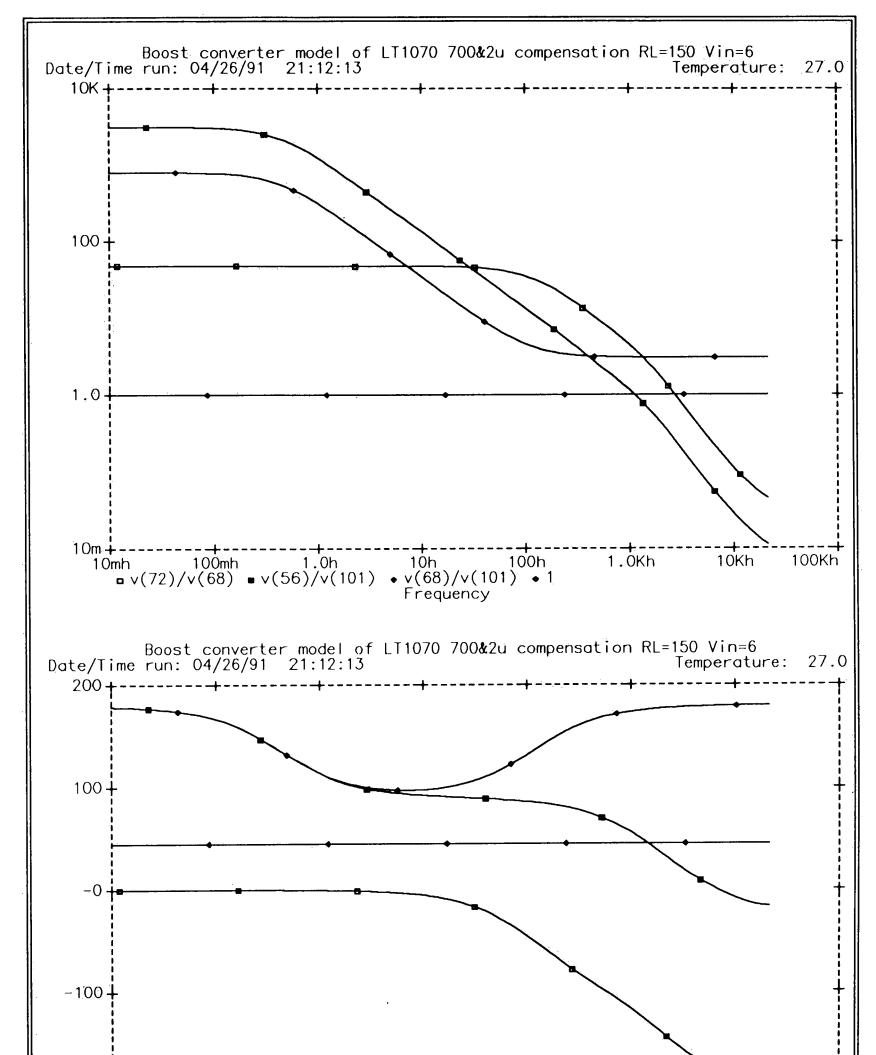

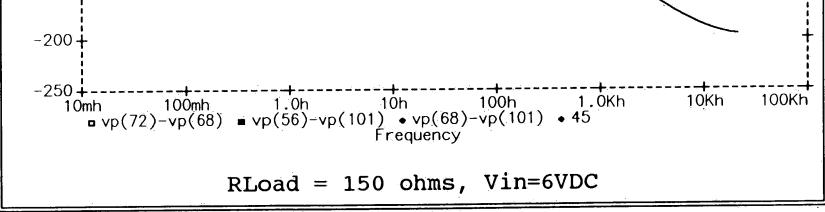

| Figure 64 - 150 ohm Load Gain and Phase for Minimum Input        |     |

| Figure 65 - 150 ohm Load Gain and Phase for Maximum Input        | 97  |

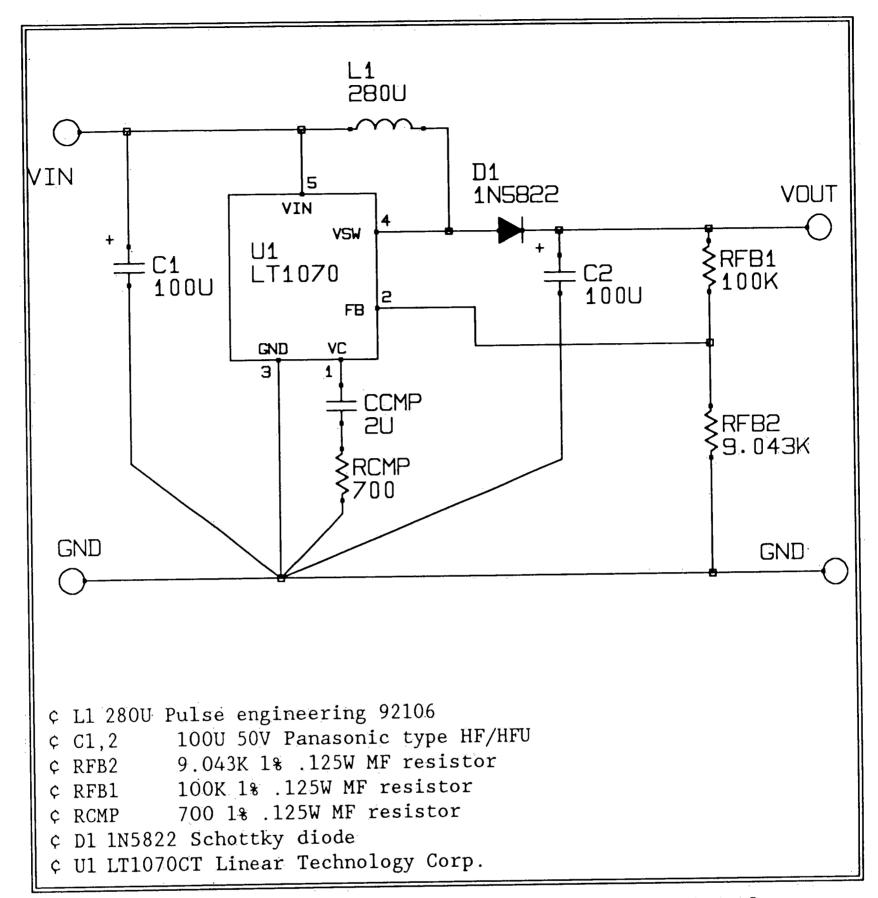

| Figure 66 - Prototype Circuit With Component Values              |     |

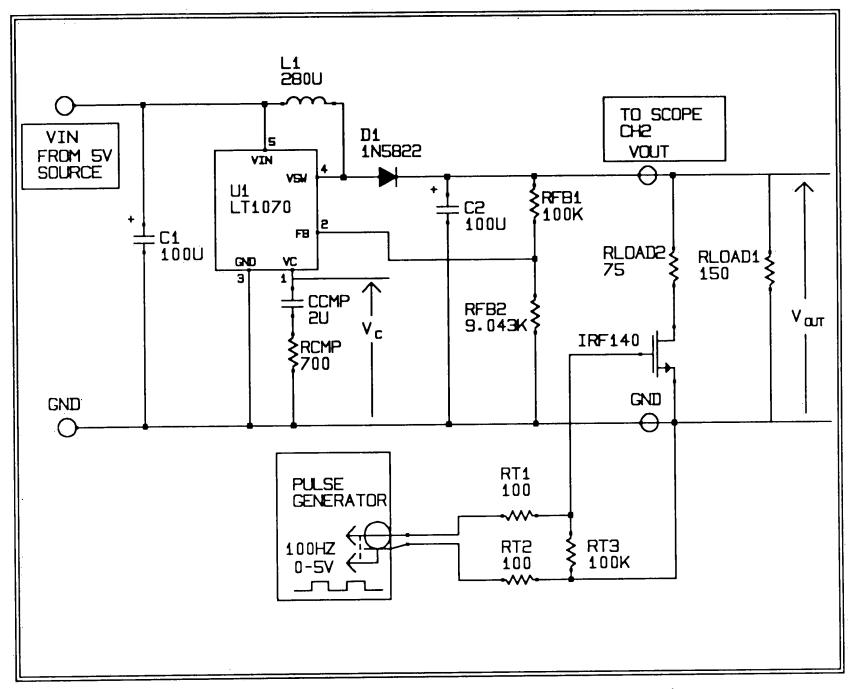

| Figure 67 - Variable Load Test Circuit.                          |     |

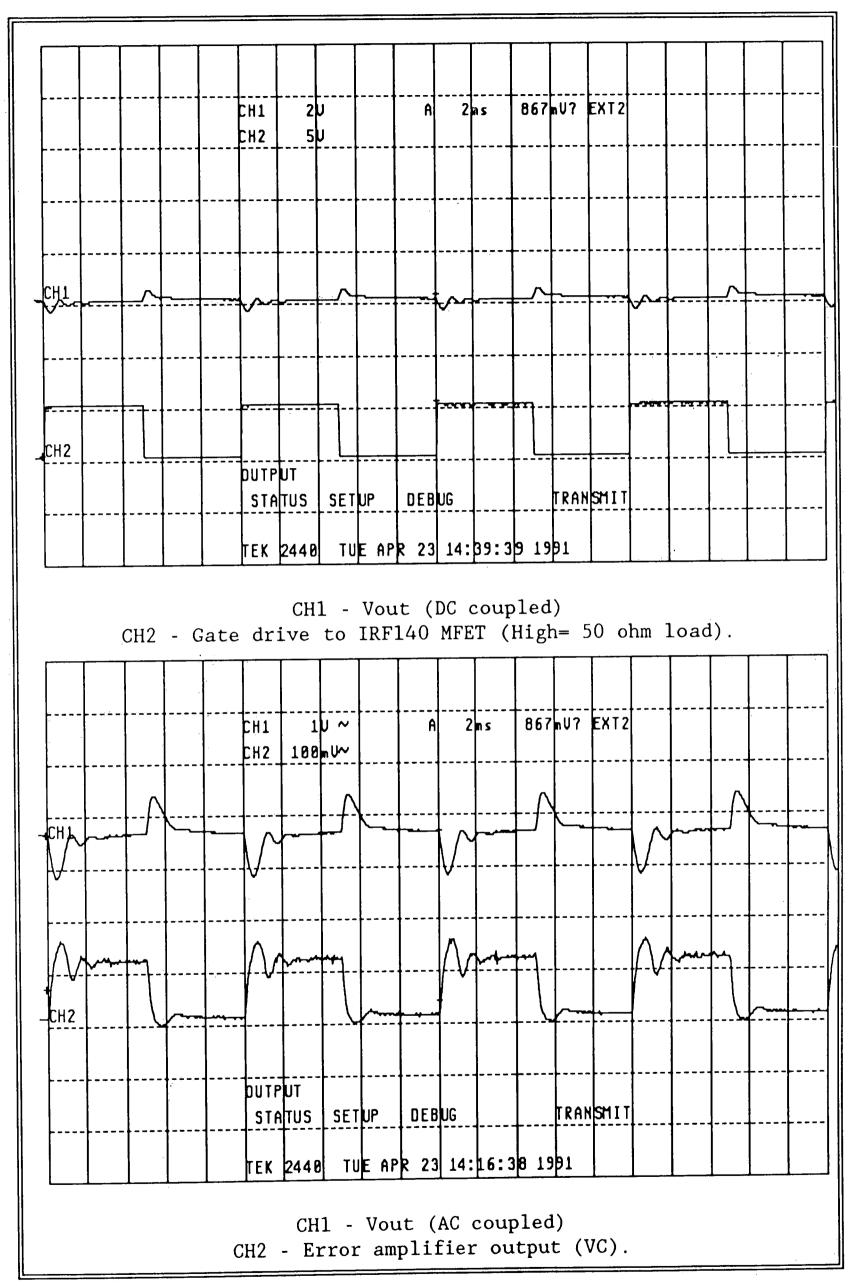

| Figure 68 - Transient Response                                   | 100 |

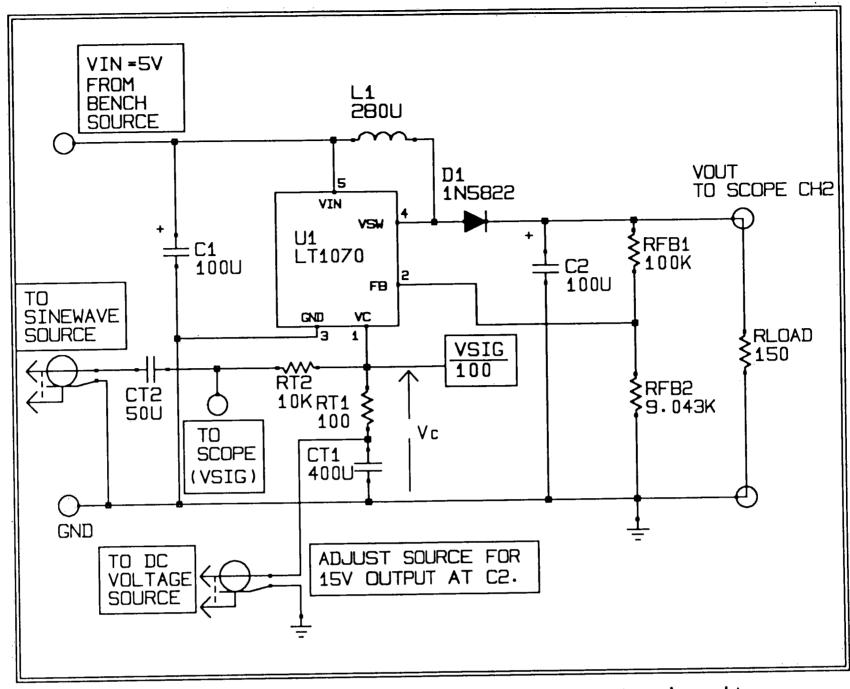

| Figure 69 - Phase and Gain Bench Test Circuit.                   | 102 |

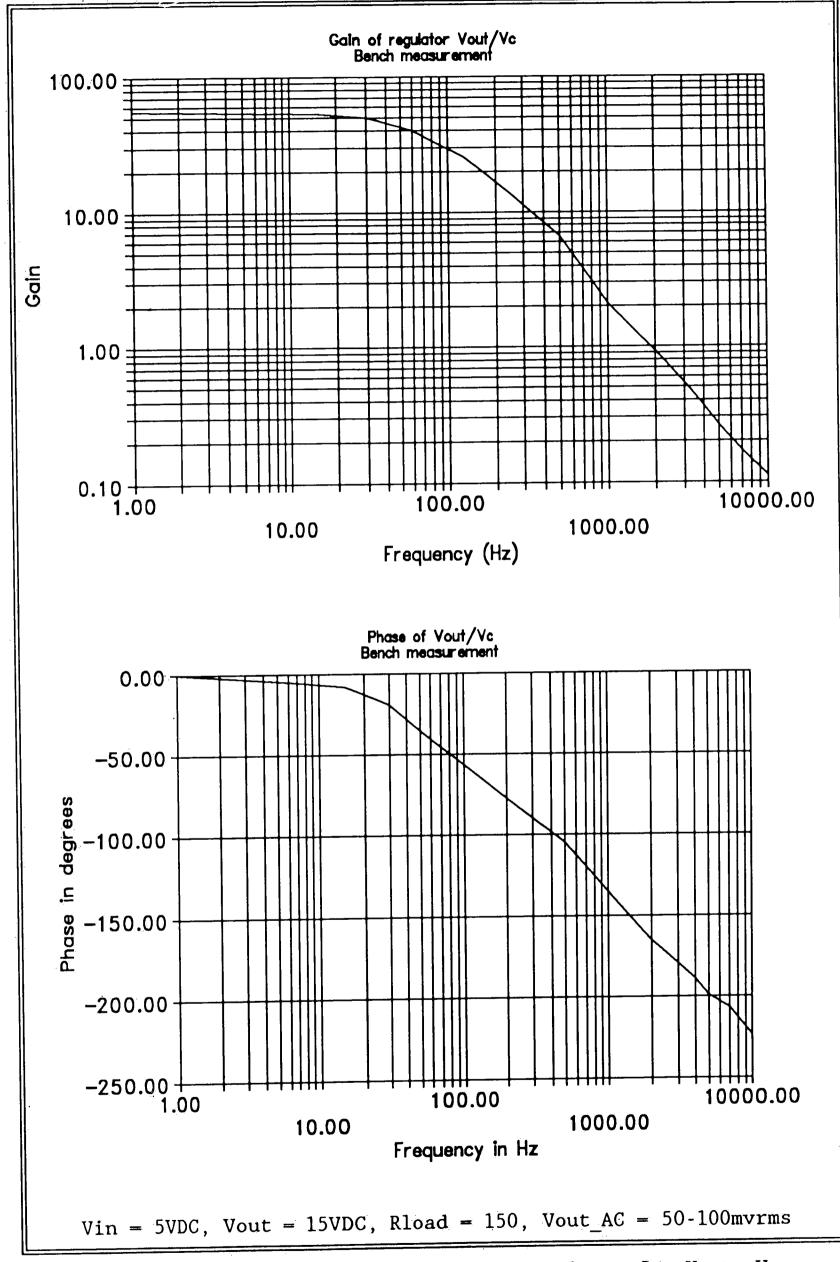

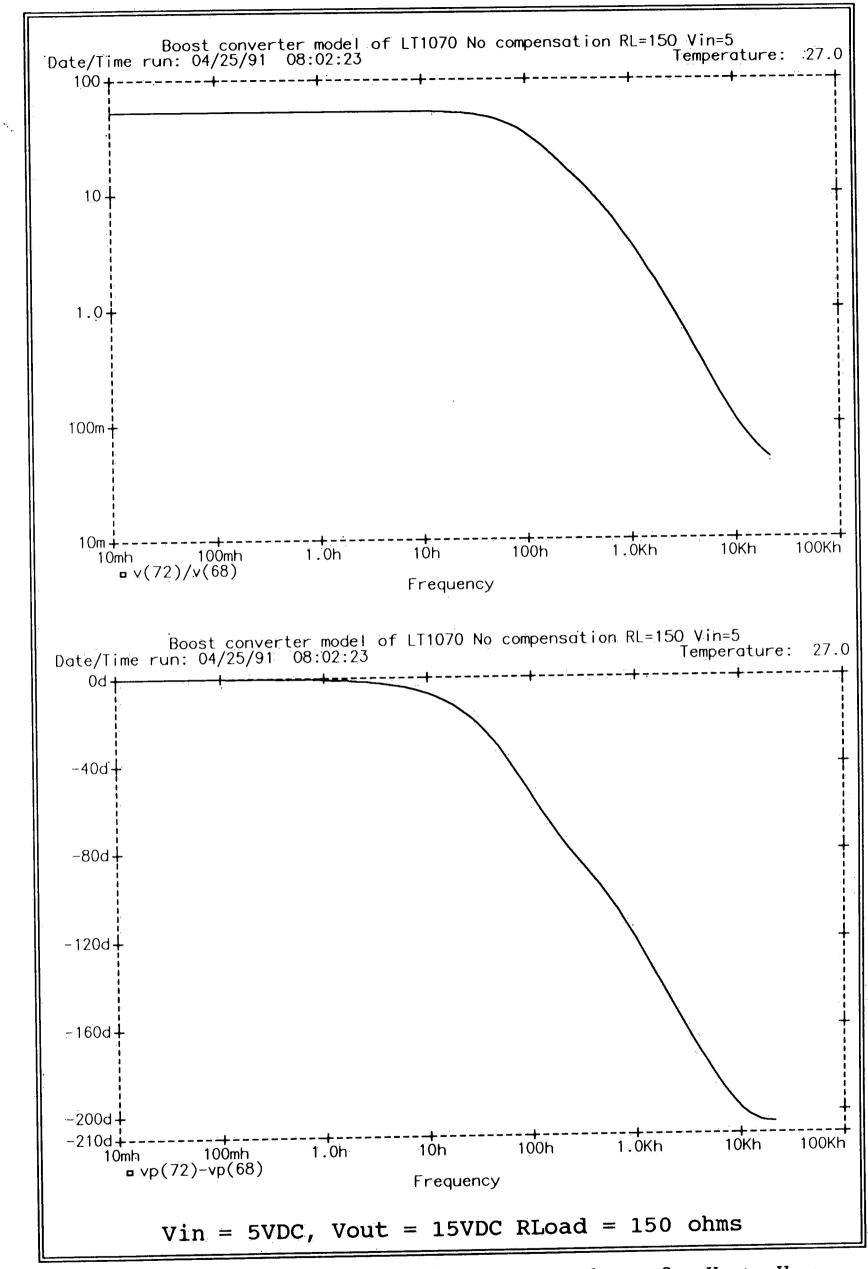

| Figure 70 - Measured Gain and Phase of Regulator for Vc to Vout  |     |

| Figure 71 - Simulated Gain and Phase of Regulator for Vc to Vout |     |

|                                                                  |     |

· .

-9%-

5-

#### Abstract

Switch mode DC-DC converters are becoming increasingly prevalent in today's miniaturized low power equipment. This paper investigates single inductor pulse width modulated converter topologies, and the analysis tools available to deal with these circuits. The Boost, Buck, Boost-Buck, and CUK topologies are introduced, and the large signal operation of each is discussed. Discontinuous operation, Duty cycle control, and Current mode control are presented as generalized extensions of the previous topologies. State Space Averaging and Linearization is introduced as a method of representing a time variant circuit as a time invariant one to facilitate small signal analysis. Nonlinear time invariant circuit models to aid in the characterization of converter circuits are derived from the concepts of state space averaging . These models are transformed into spice models using the nonlinear dependent source feature of

spice. A sample Boost converter is designed using the

spice models as a tool to compensate the feedback loop of

the converter and a comparison is done between the real

life implementation of the circuit and the predictions

1

made by the model.

#### Introduction

Today's ever decreasing packaging volume requirements coupled with the increased use of battery powered applications has led to a wide spread adoption of Switch Mode power supplies in many applications. From commanding just 17% of the power supply market in 1979, the switch mode power supply market has grown to capture 63% of the market by year end of 1989.1 Design of these supplies has long been considered a black art left to a vendor with a proven track record, while leaving small applications such as on card regulation to single chip power miserly linear solutions or expensive hybrid IC switch mode supplies. Recent offerings by semiconductor manufacturers of new control integrated circuits and complete "drop in solutions" has given the novice a path to the successful design of supplies provided that the semiconductor manufacturer's design notes are followed. Many of the predesigned integrated circuit solutions reduce the effort required to design a circuit at the expense of providing less than optimal efficiency and load regulation. While

the simplification of switch mode power supply design has

led to increased use, some designers are not comfortable

using or modifying existing circuits which use a

technology that they do not fully understand. It is the

author's opinion that much of the reluctance of designers

<sup>1</sup> Electronic Design December 1990.

to use switchmode power supplies comes from a lack of understanding coupled with an extensive history of horror stories involving these circuits. This paper is intended to familiarize designers with some of the design strategies, analysis tools, and circuit topologies used for these circuits so they can be better equipped in the design, and selection processes of switch mode supplies.

As with any regulator circuit, there is a mechanism for controlling the flow of energy to the load to achieve regulation. Switching regulators store a fixed amount of energy supplied by the input source in the magnetic field of an inductor, and then later release the stored energy to the load. Storage and release of energy is governed by the circuits switch mechanism. Altering the output voltage of the supply is implemented by regulating the ratio of energy storage time to energy release time. This differs from the regulation mechanism in a linear supply which essentially operates as a variable resistive voltage divider to dissipate unused energy. Switching regulator control techniques will all center around the modulation

of the switch on time to off time ratio since energy transfer is governed by the switching modulation method. Some of the modulation methods used are: fixed switch on time with variable switch off time, fixed switch off time with variable on time, and fixed cycle time where the sum

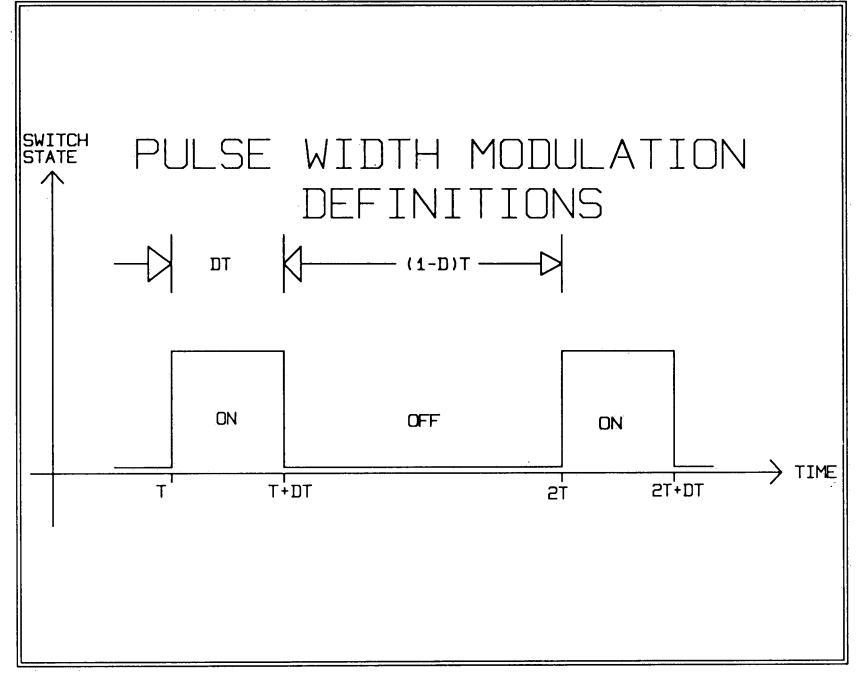

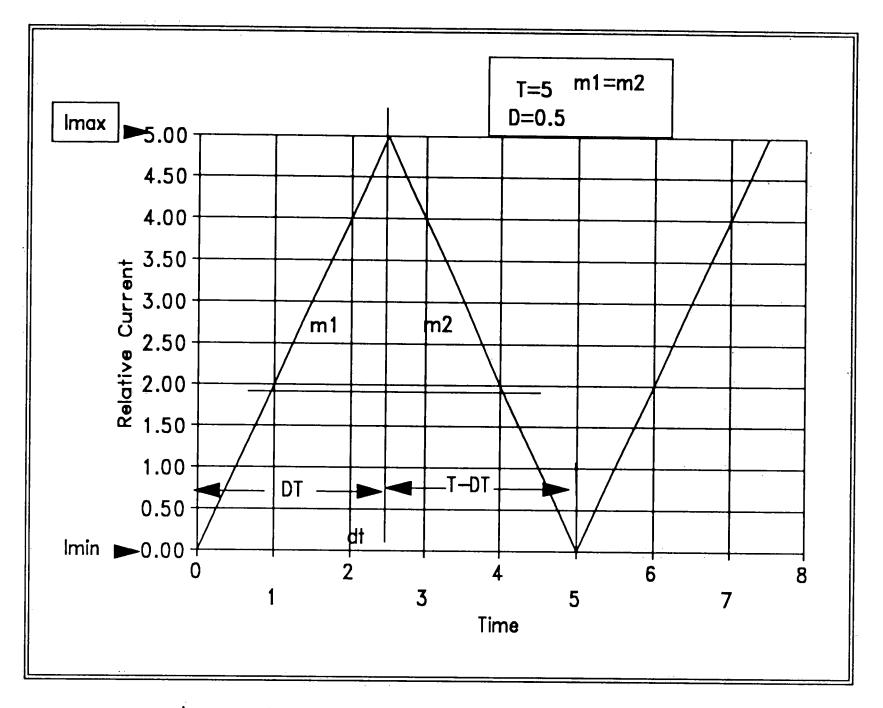

of the switch on and off time is constant. The latter is simply pulse width modulation of a fixed frequency clock and is by far the dominant method in use today for switch mode DC-DC converters. Pulse width modulation (PWM) control's key advantage is that the lowest frequency component of ripple generated by the switching action is constant lending to a simple output filter implementation to achieve low output ripple. However, other modulation methods are used to meet special performance requirements. Fixed on-variable off time is used by some of the single IC regulator solutions offered by IC vendors such as Linear Technologies. For example, the quiescent current of the LT-1073 is considerably lower than in a typical PWM controlled circuit. Throughout this paper we will focus on PWM so some definitions are in order. If one defines T to be the constant period of the clock and D the variable duty cycle of the switch, then switch on time will be denoted as (  $t_{on} = D \cdot T$  ) and switch off time denoted as  $(t_{off} = (1-D)^T)$ . (See figure 1)

Figure 1 - Pulse Width Modulation Definitions.

Pulse width modulated switch mode supplies can be divided into one of the two following basic types: The Forward Converter Topology where current from the source flows from the source into the load during the switch on time; and the Flyback topology where energy is transferred from the source to the inductor during switch on time, and

from the inductor to the load during switch off time. There is some discrepancy in the literature on these definitions especially concerning flyback topologies, so the reader should be aware of the use of them when reading other literature on the subject.

Independent of what topology is used it is of the utmost importance to fully understand where energy is being supplied from, stored in, and dissipated to during each portion of the clock. For the purposes of the initial discussion of each topology, we will assume that there is energy stored in the inductor at the end of each cycle implying that there is current flow through the inductor.

| n    | • <b>• • • •</b> |              |      | •   |

|------|------------------|--------------|------|-----|

| Basi |                  | 000          | 0102 | ies |

|      |                  | ~ <b>r</b> ~ | -~0  |     |

Depending on the topology chosen, converters can produce an output voltage which has a magnitude greater or less than the input while maintaining or reversing the polarity relationship between the input and output. The Buck converter produces an output which is less in magnitude, and the same polarity as the input. The Boost topology maintains the polarity of the input, yet produces an output magnitude greater than that of the input. A Boost-Buck converter inverts the polarity of the input, but can produce an output voltage with a magnitude above

or below that of the input.

### The Buck Converter

A simplified diagram of a forward buck converter is shown in figure 2. As suggested by its name, the buck converter produces an output voltage which is less than the input potential.

Figure 2 - Buck Converter.

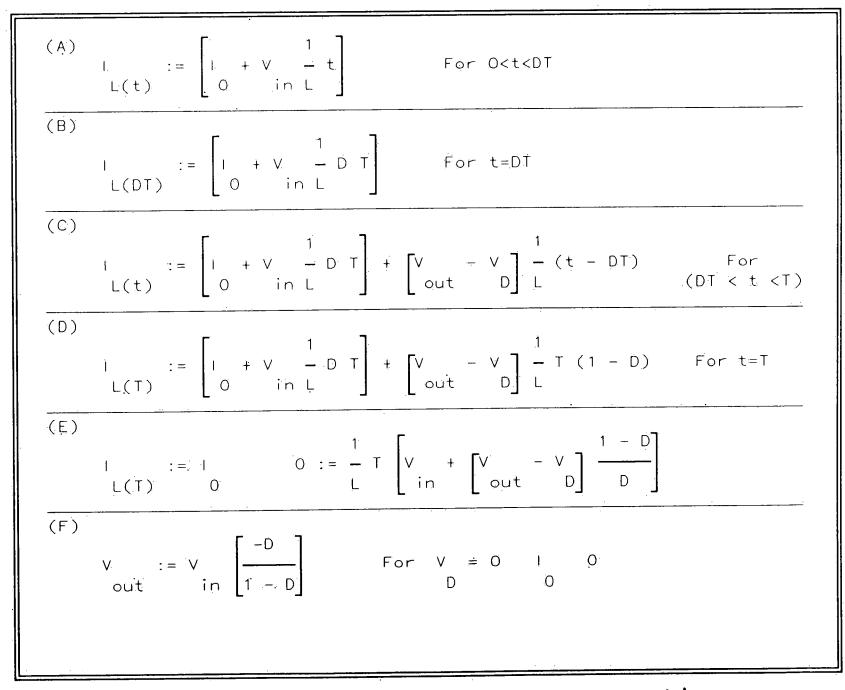

To analyze the large signal behavior of the circuit, piecewise linear analysis techniques will be used in conjunction with making the assumption that the output of the supply is an ideal voltage source of magnitude  $V_{out}$ . If one assumes that the filter cap is large enough to maintain an approximately constant output voltage throughout a cycle then when the switch is closed at the beginning of a clock cycle, the inductor current will start to rise approximating a liner ramp as described in figure 3A. At the end of the switch dutycycle, the switch opens up defining the maximum inductor current as approximately that described in figure 3B. The voltage across the inductor will instantaneously reverse and increase in magnitude until the voltage across it is a diode drop above the output voltage; there it will remain clamped as long as there is energy stored in the inductor. Energy stored in the inductor is now discharged according to equation 3C until the end of the clock cycle T. Since the circuit is assumed to be in a steady state condition, the energy stored in the inductor at the start of the next

cycle must equal that stored at the beginning of the

present cycle. By invoking an inductor current boundary condition at the switch turn on point of the second cycle

$[I_0(T-) = I_0(T+)]$ , a solution for the output voltage as

a function of input voltage and duty cycle can be realized

as carried out in figures 3E and 3F.

### **The Flyback Boost Converter**

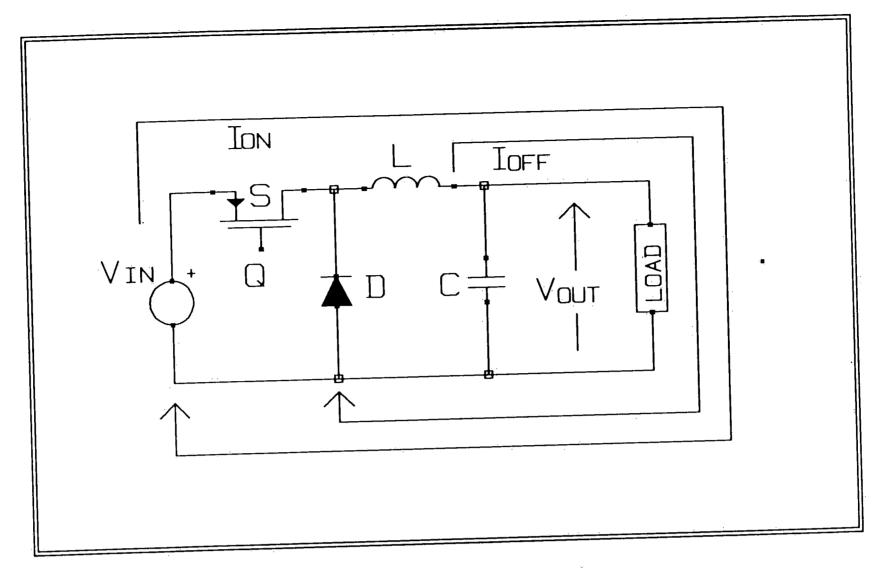

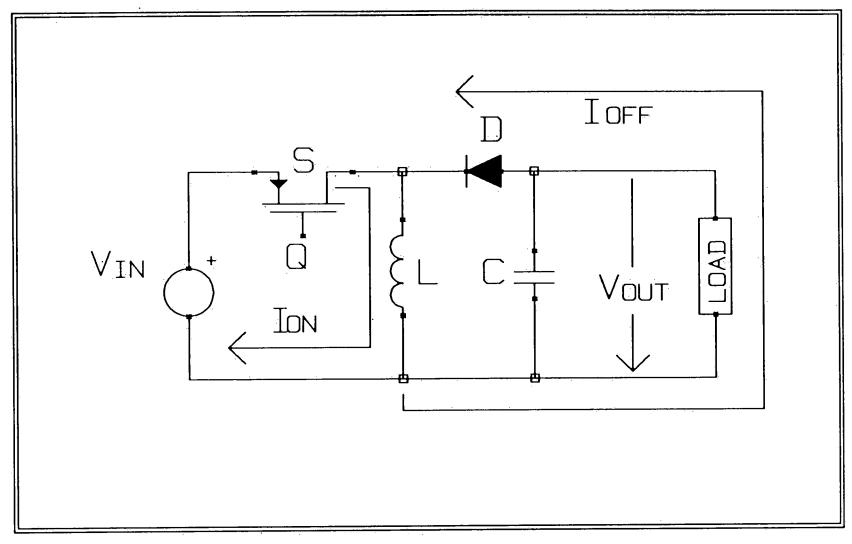

Figure 4 - Boost Converter.

$$I = I = 0 = -T \left[ V - \left[ V + V \right] (1 - D) \right]$$

$$I = V = \frac{1}{(F)}$$

$$V = V = \frac{1}{(I - D)} - V (1 - D) = For I = 0$$

out in I - D = D = 0

Figure 5 - Boost Converter Equations.

A flyback boost converter is pictured in figure 4. Boost converters use the same four basic components that their forward counterparts do, yet produce an output voltage which is greater than the input potential. During the switch on time interval the inductor is connected across the input source, while during the switch off period it is in series with the source and load. Effectively, the potential induced across the inductor is added to the input source there by boosting the output voltage above the input voltage. Since the inductor is across the source when the switch is closed, the inductor charging current is simply a linear ramp described by the equation in figure 5A. When the switch opens at the end of the duty cycle interval t=DT, the energy stored in the inductor is at its maximum and the voltage across the inductor reverses and rises until the blocking diode conducts. At this point, the voltage across the inductor is clamped to ( $V_{out} - V_{in} - V_{Diode}$ ) so the energy stored in the magnetic field of the inductor is discharged into the load as described by the equation in figure 5C. If a

steady state condition is assumed where the minimum

inductor current  $I_0$  is the same for all cycles of the

clock; equation 5D can be solved for  $V_{out}$  as a function of

$V_{in}$  as carried out in figures 5E and 5F.

Figure 6 - Boost - Buck Converter.

Figure 7 - Boost - Buck Converter Equations

12

.

#### **The Boost - Buck Converter**

A simplified boost-buck flyback converter is shown in figure 6. The boost-buck regulator differs from the boost topology in that the inductor voltage is not added to the input voltage during the energy transfer period. This allows the magnitude of the output voltage to span from zero to above the input voltage depending on the switch duty cycle. The energy storage phase is the same as that of the boost converter, so the same equations for inductor charging current may be utilized. When the switch opens up at the end of the inductor charging phase, the potential across the inductor reverses and is clamped to Vout by the charge on the output capacitor. Consequently, the energy stored in the inductor is discharged as a current ramp until the end of the clock cycle as described by figure 7C. Again assuming a steady state condition for the minimum inductor current  $I_0$ , the output voltage can be calculated as demonstrated in equations 7E and 7F.

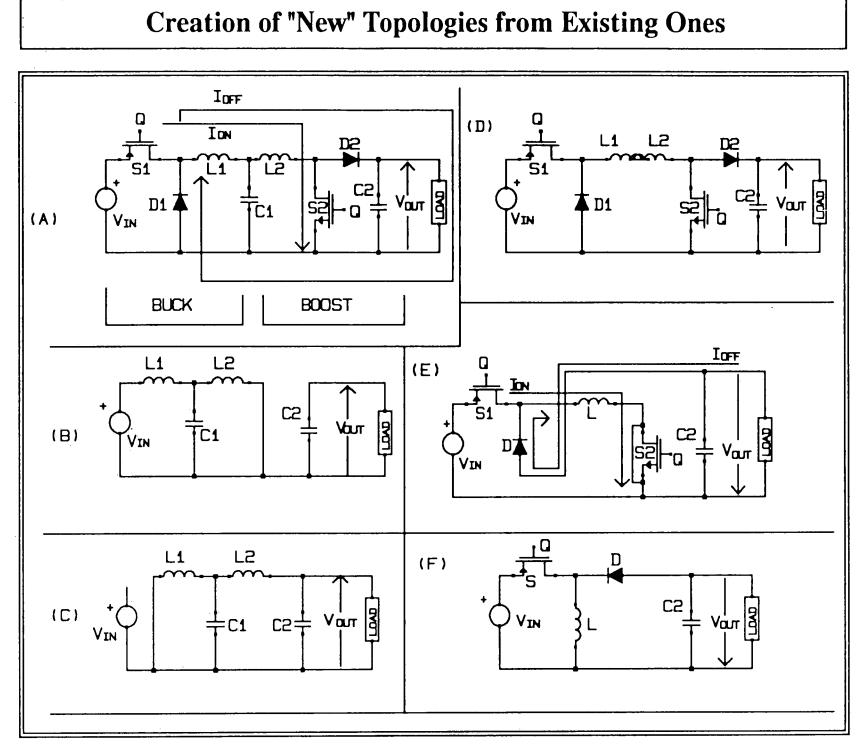

Figure 8 - The Creation of the Boost-Buck Converter from the Boost and Buck Topologies.

Although some consider the boost-buck converter to be a basic topology it can be thought of as a cascade of a Consider the circuit shown in buck and a boost converter. figure 8A consisting of a buck converter feeding the input

of a boost converter. If one were to synchronize the

switches it can be seen that during switch on time the

current flows from the source to ground via the switches

(Figure 8B). As discussed before, the only parameter

which matters when the switch opens is the amount of

energy stored in each inductor. The capacitor C1, located between the two converters, does little to alter this. By removing capacitor C1, and combining L1 and L2 into L a non-inverting two switch topology emerges (Figure 8D). The two switches can be combined into one by observing that both are only needed if polarity reversal is not desirable. Further reduction can be obtained by noting that the current flow in switch two is unidirectional so it can be replaced by a diode yielding the boost-buck topology as discused before (Figure 8E and 8F). If one examines the function for  $V_{out}$  previously derived in figure 7, one finds that it is the product of the boost and buck converter output voltage functions, further indicating the relationship between the topologies.

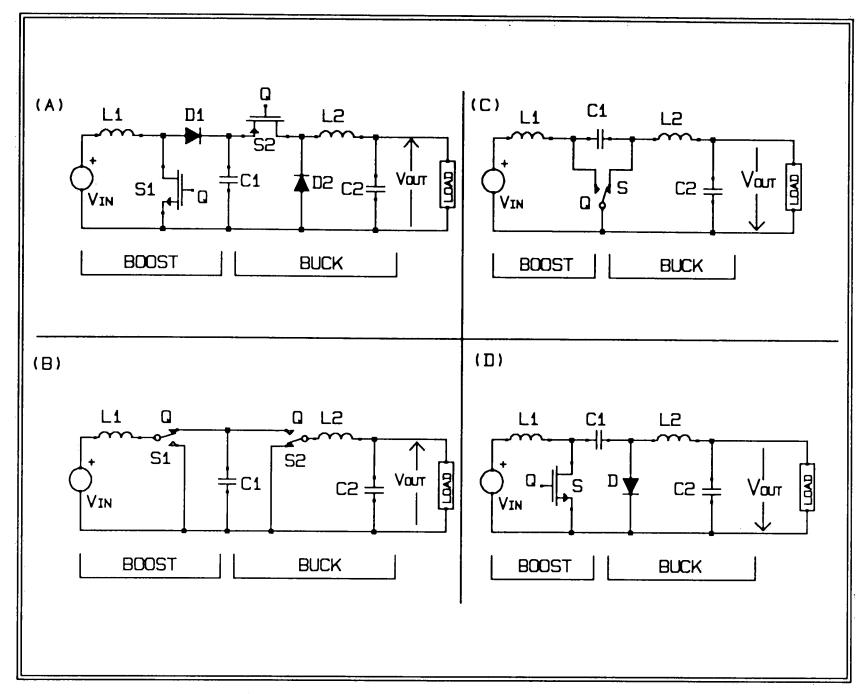

#### The CUK Converter

It can be observed from this discussion that "new" converter topologies can be synthesized from combinations of the basic boost or buck converter. As previously demonstrated, a boost buck converter is simply the cascade

of two basic topologies. Of particular importance is the Cuk converter (Pronounced "Chook". Named after Dr. Slobodan Cuk) which is generated by preceding the buck converter with a boost converter; a reverse of the boostbuck topology (Figure 9A).

Figure 9 - The CUK Converter.

As before, integration of the two topologies starts with removing the diode and switch combinations by replacing them with there ideal switch counterparts (figure 9A to 9B). The second integrating step is observing the energy sources and sinks during each switch state. During the

switch on period both inductors are being charged, one

from the source and one from C1. During the switch off

period inductor L1 is transferring its stored energy to C1

and inductor L2 is transferring its stored energy to the

load filtered by C2. The load and the source are

completely isolated during both periods of the clock. In 16 this case, it is observed that the filter capacitor can not be omitted since energy stored in it during the switch off period is required to supply the second stage when the switches are on. By using the previous observations, the circuit in figure 9B can be transformed to that in figure 9C by moving C1 and combining S1 and S2. The circuit in figure 9C charges both inductors during the switch on period and discharges them during the switch off period. However, one functional difference does exist between figure 9B and 9C. The polarity of the output is inverted because the reference side of C1 is flipped between switch states.

$$A = \begin{bmatrix} 1 & + V & \frac{1}{L} & t \\ 10 & \ln L & 1 \end{bmatrix} \text{ For } 0 < t < DT$$

$$B = \begin{bmatrix} 1 & + V & \frac{1}{L} & D & T \\ 10 & \ln L & 1 \end{bmatrix} \text{ For } t = DT$$

$$C = \begin{bmatrix} 1 & + V & \frac{1}{L} & D & T \\ 10 & \ln L & 1 \end{bmatrix} - \begin{bmatrix} V & + V & - V \\ c & D & in \end{bmatrix} \frac{1}{L} (t - DT) \text{ For } t < T)$$

$$D = \begin{bmatrix} 1 & + V & \frac{1}{L} & D & T \\ 10 & \ln L & 0 & T \end{bmatrix} - \begin{bmatrix} V & + V & - V \\ c & D & in \end{bmatrix} \frac{1}{L} T (1 - D) \text{ For } t < T)$$

Figure 10 - CUK Converter Equations Part 1.

$$A = \begin{bmatrix} 1 \\ 20 \end{bmatrix} := \begin{bmatrix} 1 \\ 20 \end{bmatrix} \begin{bmatrix} V \\ c \end{bmatrix} = \begin{bmatrix} 1 \\ 20 \end{bmatrix} \begin{bmatrix} V \\ c \end{bmatrix} = \begin{bmatrix} 1 \\ 20 \end{bmatrix} \begin{bmatrix} V \\ c \end{bmatrix} = \begin{bmatrix} 1 \\ 20 \end{bmatrix} \begin{bmatrix} V \\ c \end{bmatrix} = \begin{bmatrix} 1 \\ 20 \end{bmatrix} \begin{bmatrix} V \\ c \end{bmatrix} = \begin{bmatrix} 1 \\ 20 \end{bmatrix} \begin{bmatrix} V \\ c \end{bmatrix} = \begin{bmatrix} 1 \\ 20 \end{bmatrix} \begin{bmatrix} V \\ c \end{bmatrix} = \begin{bmatrix} 1 \\ 20 \end{bmatrix} \begin{bmatrix} V \\ c \end{bmatrix} = \begin{bmatrix} 1 \\ 20 \end{bmatrix} \begin{bmatrix} V \\ c \end{bmatrix} = \begin{bmatrix} 1 \\ 20 \end{bmatrix} \begin{bmatrix} V \\ c \end{bmatrix} = \begin{bmatrix} V \\ c$$

Figure 11 - CUK Converter Equations Part 2.

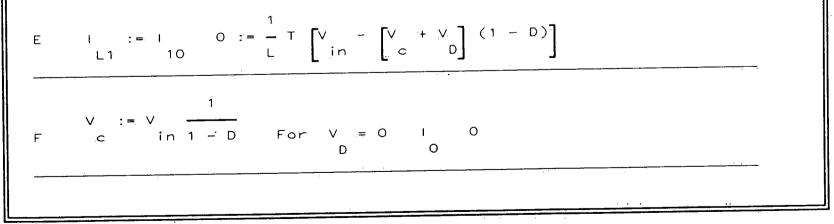

Now that the CUK topology has been defined, the previously used analysis techniques can be applied to solve for V<sub>out</sub> and the inductor currents. With the switch closed inductor L1 is being charged across the input source, so the current can again be described as a linear ramp defined in figure 10A. To describe the current in

L2, an assumption needs to be made about the voltage across C1. The voltage across C1 should be relatively constant over a clock cycle since it is essentially the output filter capacitor of a boost regulator. With this assumption in hand, the current through L2 is simply another linear ramp described by figure 11A. When the 18 switch opens, inductor L1 transfers its stored energy to As discussed before, the voltage across C1 is C1. relatively constant so the discharge current of L1 can be approximated by the equation in figure 10C. Inductor L2 is clamped across the output voltage during the switch off period, so the energy stored in it is discharged as described by figure 11C. By solving for the inductor currents at the end of each cycle, two expressions emerge: one for  $V_{C1}$  as a function of  $V_{in}$  and one for  $V_{out}$  as a function of  $V_{C1}$  (Figures 10F and 11F). Combining the two expressions yields the input voltage to output voltage function described in figure 11F. Comparing this with the individual functions of the boost and the buck converter shows that the CUK converter DC input to output function is the product of the two elementary converter input to output functions, as one would expect.

#### **Discontinuous Operation**

Up to this point we have assumed that the inductor current never reaches zero before the end of a clock cycle which implies that the load current is sufficient to maintain energy transfer during switch off time. As long as the load current is great enough to sink the energy from the inductor, the average charge on the filter capacitor will remain unchanged indicating that the output 19 voltage will remain constant (Figure 12A). If the output current is decreased to the point where the incremental energy stored in the inductor is greater than that consumed by the load; the excess energy will be dumped into the filter capacitor causing the output voltage of the circuit to increase until a new steady state output power is reached. An increase in steady state output voltage causes the inductor to discharge at a grater rate so the inductor current will reach zero before the end of the clock cycle as shown in figure 12B. This mode of operation is termed discontinuous operation since the inductor current flow is no longer continuous.

Figure 12 - Continuous vs Discontinuous Mode Inductor Currents.

It should be noted that determining the mode of operation the circuit is in, is of the utmost importance when evaluating control loop stability since the loop gain of the control loop depends on the mode of operation. The boundary of continuous to discontinuous operation is

termed the critical load current and is defined as the

load condition that causes the inductor current to just

reach zero at the end of a cycle (Figure 12C).

Figure 13 - Boost Regulator Operating in Discontinuous Mode.

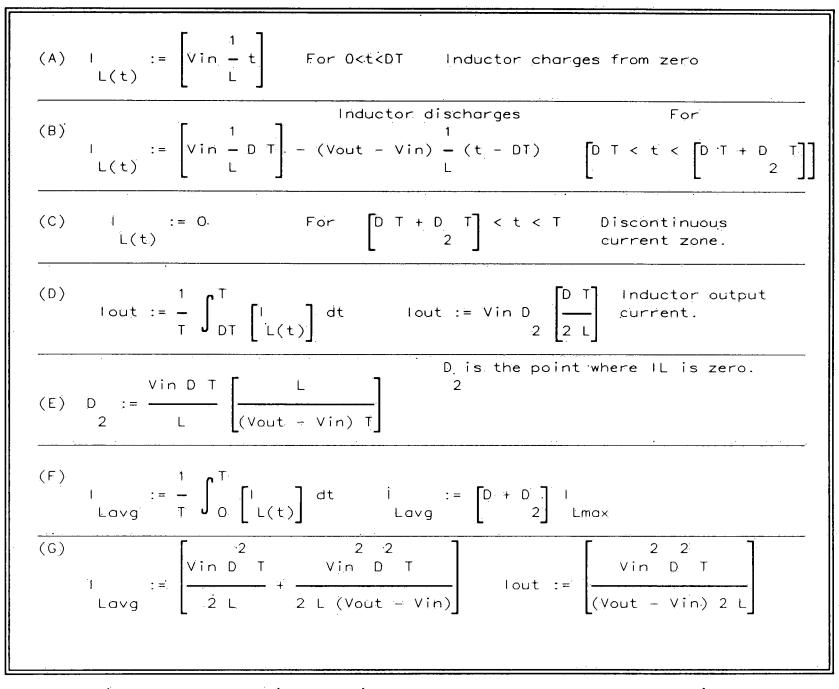

Consider the operation of the boost converter operating in discontinuous conduction mode shown in figure 13. To analyze the properties of the discontinuous mode circuit we will assume that the inductor current reaches zero at a point in time located between DT and T

defined as xT, and that the load voltage has stabilized to

some steady state value define as Vout.

Figure 14 - Impact of Discontinuous Mode on the Boost Regulator Input to Output Voltage Function.

For discontinuous operation the inductor always starts charging from a totally discharged state since all stored energy is expelled within each cycle of the clock. As a result, the inductor charging current becomes a simple function of duty cycle and input voltage

(figure 14A). When the switch opens up the inductor

discharges at a rate controlled by the difference between the input and output voltages described by the equation in figure 14B. By integrating the inductor current over the time which current is flowing to the output a solution for the output current as a function of dutycycle, input 23 voltage, and time point xT is obtained. The arbitrary time point xT is simply the solution of equation 14B for  $I_L(t)=0$ . Combining equations 14D and 14E and solving the quadratic for  $V_{out}$  yields the discontinuous output voltage function in equation 14F. An insight into the consequence of discontinuous mode operation can be seen by comparing equation 14F to the continuous case output equation. For the continuous case the output voltage is only dependent on duty cycle while for the discontinuous case the output voltage is a function of the load, inductor value, clock period, and duty cycle.

#### **Current Mode Control**

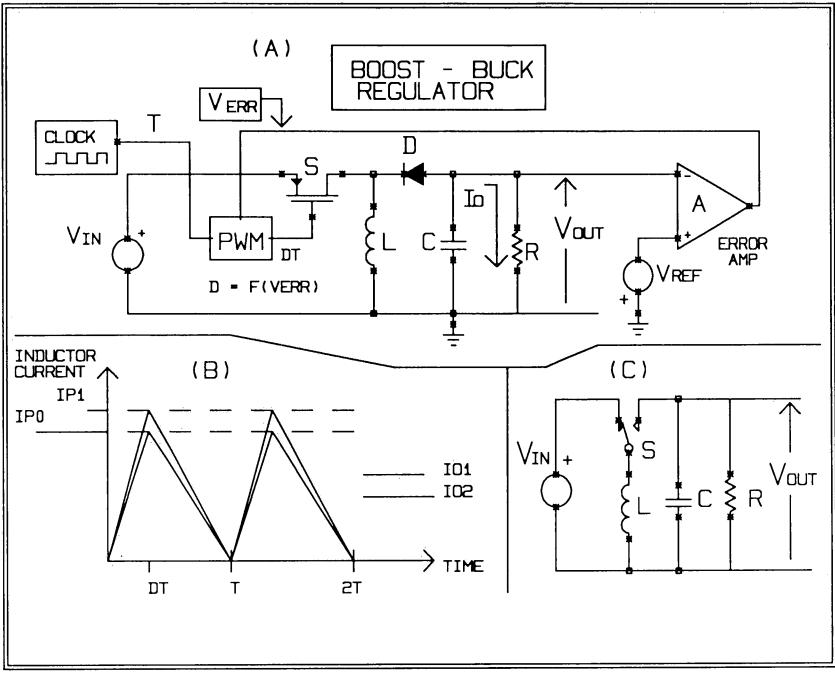

Up until now we have assumed the presence of a feedback loop which adjusts the pulse width of the switch to achieve output voltage regulation. Figure 15A shows a boost-buck regulator with such a voltage feedback loop.

Figure 15 - Boost-Buck Regulator with a Voltage Feedback Loop.

The feedback loop consists of an error amplifier which feeds a correction signal to the pulse width modulator to correct for a difference between the output and the desired output or reference. For a constant output load and input condition, the switch will remain at a constant

duty cycle  $D_1$  and consequently the peak inductor current will remain constant at  $I_{P0}$  (See figure 15B). If the input voltage is suddenly increased then the energy stored in the inductor must rise to a new value  $I_{p1}$  and the output voltage must also rise until the feedback loop

responds, many clock cycles later, by decreasing the duty cycle to reduce the energy stored in the inductor. Since the source and load are disconnected during the energy storage and transfer periods, the energy transferred to the load must have been completely stored in the inductor at one time (See figure 15C). With this in mind, it stands to reason that controlling the peak inductor current in a boost-buck regulator is equivalent to controlling the output voltage for a given output load condition. If the voltage control loop were eliminated and replaced with a circuit which always charges the inductor to a preset value on every clock cycle then a change in V<sub>in</sub> would not produce a change in V<sub>out</sub> since the energy stored in the inductor is constant (See figure 17). Of course this is assuming that the output load condition is constant.

1.10

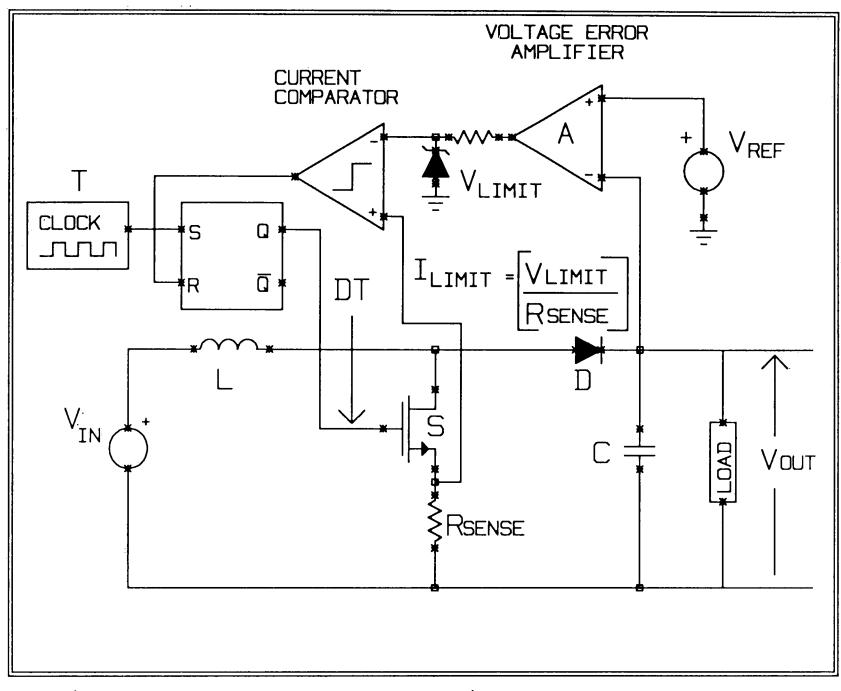

Figure 16 - Boost Regulator with Voltage and Current Feedback. (Current Mode)

Unfortunately load conditions do vary, so the previous concept must be integrated into a circuit which controls both peak inductor current and output voltage. The regulator shown in figure 16 has a secondary feedback loop which controls the peak inductor current on every

cycle as a function of the error voltage generated by a primary voltage control feedback loop. The peak inductor current is fixed for a given set of output load conditions by the secondary current feedback loop. Regulating the peak inductor current inside the voltage feedback loop is

termed current mode control. An error signal, representing output voltage error generated from the voltage feedback loop, controls the peak inductor current and therefore the peak energy stored in the inductor. If Vin should change, the current feedback loop compensates by turning the switch off earlier or later depending on the polarity of the disturbance. Current mode control can be viewed as regulating the internal magnetic state of the system by using the inductor current state variable as a source of feedback. One benefit of controlling the peak inductor current on a cycle by cycle basis is that cycle by cycle current limiting can easily be added to a current mode regulator by limiting the current feedback reference signal. Cycle by cycle current limit can be used to prevent inductor saturation. Inductor saturation can be disastrous since the incremental inductance of a non air core inductor decreases to a near core-less value during saturation. A sharp decrease in inductance leads to a rapid increase in inductor current since the inductor is across a voltage source with a very low series resistance.

The rate of rise of switch current is inversely

proportional to the inductance, so decreasing the inductance results in a runaway rise in inductor and therefore switch current. High current stress of the switch leads to semiconductor reliability limitations and consequently should be avoided at all costs if future

component failures are to be avoided. Converters using current mode control may have their outputs paralleled without the fear of one supply current hogging. This often is a requirement for high reliability systems.

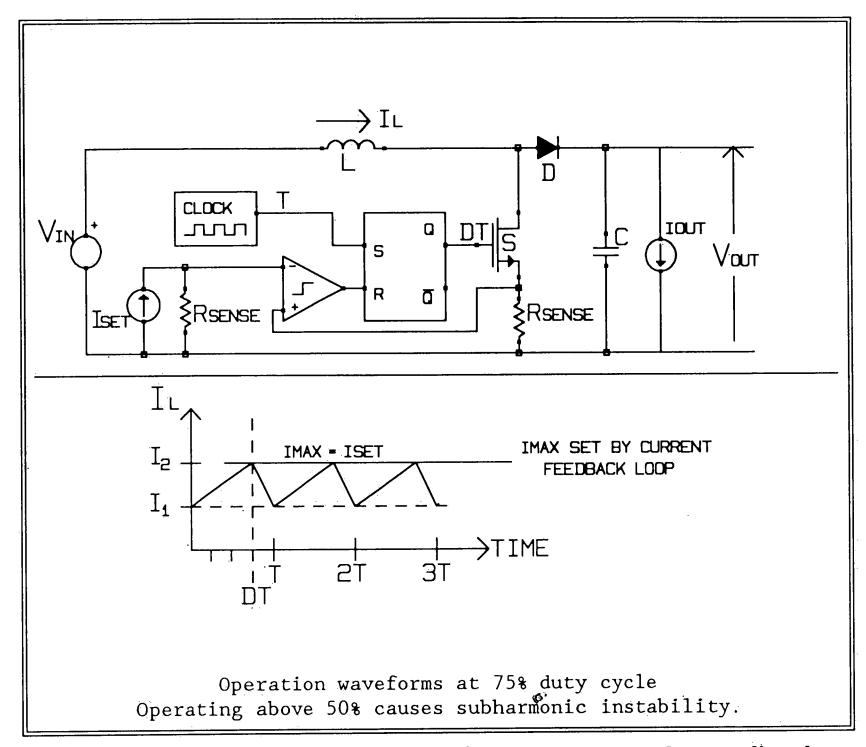

Current mode control is not without some problems. When used in the boost topology duty cycles must be limited to less than 50% in order to prevent sub-harmonic instability. Sub-harmonic instability is a oscillatory effect which occurs independent of the presence of the primary voltage feedback loop. Consider the operation of the open loop current mode boost converter in figure 17.

- e

Figure 17 - Boost Regulator with Current Mode Feedback.

The waveforms shown look reasonable as derived from simple energy transfer methods but deficiencies are hidden in this type of analysis. Complications begin to show up if one inserts a small one cycle long glitch in the inductor

current and follows the added current through successive

cycles of the clock. The glitch can be viewed as a change

in inductor charging slope perhaps caused by a disturbance

in  $V_{\mbox{in}}$  which causes the inductor current at the end of the clock cycle not to equal the inductor current at the

beginning of the cycle.

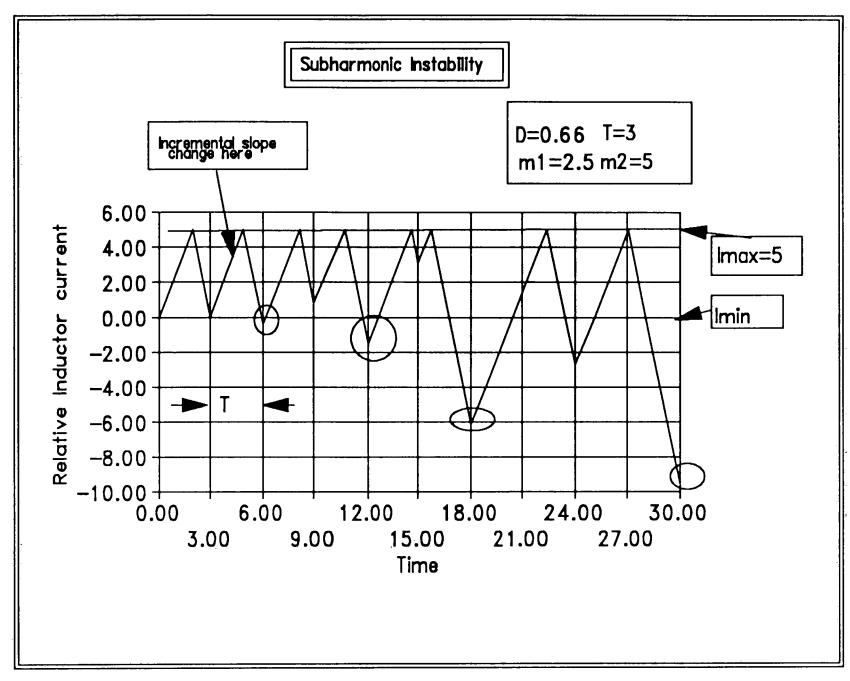

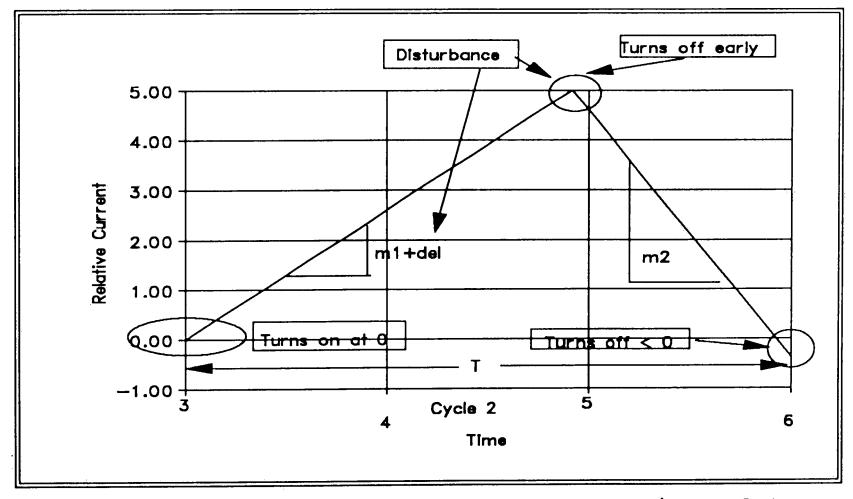

Consider the waveform shown in figure 18 where the inductor current relative to the minimum steady state inductor current is plotted against time. The first cycle displayed shows the inductor charging from Imin to the peak current set point  $I_{max}$  with a slope of  $m_1$  and then discharging from  $I_{max}$  to  $I_{min}$  with a slope of  $m_2$ . On the second cycle the glitch energy is added to alter the charging rate so the inductor charges with a slope of { m1 + del } where del is caused by a glitch added to the supply of the regulator. For the case shown, the glitch causes the inductor to reach  $I_{max}$  earlier than expected. The inductor now discharges until the end of the clock cycle to a lower current than from which it began. The current is plotted as relative to "ideal current" so the graphed current at the end of each cycle is the glitch current for that cycle resulting from the initial glitch during the second cycle. Figure 19 provides a magnified view of the inductor current on the second cycle of the Successive cycles of the clock depict the clock. propagation of the glitch energy added on cycle number two

through the next eight cycles. If we evaluate the glitch

at the end of each clock interval it is obvious from

figure 18 that the inductor current is unstable for this

condition in view of the glitch energy growing from one

cycle to the next.

Figure 18 - Plot Showing Subharmonic Instability.

Figure 19 - Magnified Second Cycle of Previous Plot.

Figure 21 - Magnified Second Cycle of Previous Plot.

If we change the duty cycle of the regulator to 33% as shown in figure 20; and again insert the glitch energy on cycle number two, a different result is uncovered. The added glitch energy decays to zero over the next few cycles of the clock. A dramatic difference between the 66% duty cycle case and the 33% duty cycle case is demonstrated by the need to plot the glitch energy at ten times its actual value for the 33% case to even see its effect on successive cycles. For the 33% duty cycle case the added glitch energy decays instead of growing as it did before which indicates that the system is stable.

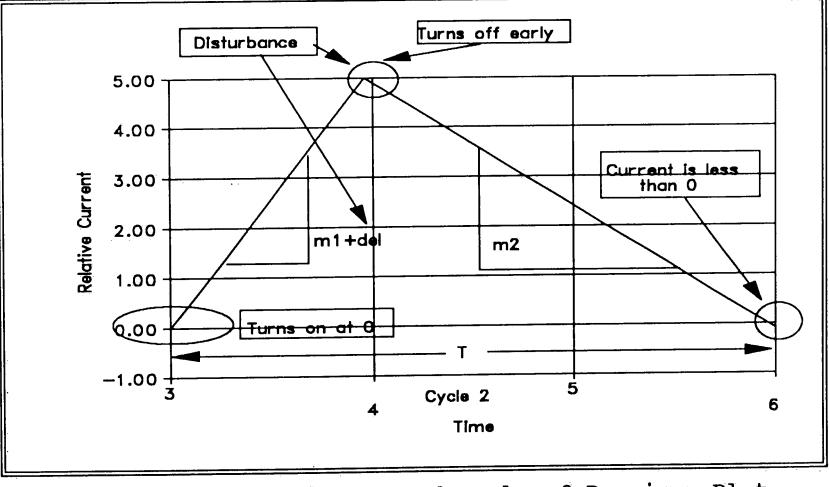

A more quantitative solution to the problem can be obtained by assigning the notation  $d_n$  as the current glitch magnitude on clock cycle number n and  ${\tt d}_{n+k}$  as the magnitude of the initial glitch current after k clock cycles from n. One can develop a open form expression for the glitch current by inserting the initial glitch on cycle n and developing an expression for the glitch size on cycle n+1, n+2, ..., and n+k as done in figures 22C-22G. A closed form expression for the glitch current can

be realized by substituting equation 22C into equation 22H

and reducing the infinite sum as demonstrated in equation

22H.

| <u> </u> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (A)      | $i := \begin{bmatrix} i + \delta + m & d \\ 1 & n & 1 & n \end{bmatrix} \text{ glitch on} $ $2 \begin{bmatrix} i + \delta + m & d \\ 1 & n & 1 & n \end{bmatrix} \text{ rising edge} \begin{bmatrix} i - i \\ 2 & 1 \end{bmatrix} := \begin{bmatrix} m & T \\ 2 \\ \end{bmatrix} \text{ Steady} $ $5 \text{ state periods} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| (B)      | $i := \begin{bmatrix} i + \delta + m - d - T \\ 1 - n - 1 - n \end{bmatrix} glitch on rising edge \begin{bmatrix} i - i \\ 2 - 1 \end{bmatrix} := \begin{bmatrix} m - T \\ 2 \\ - m \\ 2 - 1 \end{bmatrix} Steady state periods to peak amplitude t$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| (D)      | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| (E)      | $\delta := \begin{bmatrix} i & -i \\ 2 & 1 \end{bmatrix} \begin{bmatrix} m \\ 2 \\ m \\ 1 \end{bmatrix} - m \begin{bmatrix} m \\ 2 \\ -m \end{bmatrix} \begin{bmatrix} m \\ 2 \\ -m \end{bmatrix} - \frac{2}{1} \end{bmatrix} \begin{bmatrix} m \\ from cycle n \\ propagated to cycle \\ n \\ n \end{bmatrix} + \frac{2}{1} \end{bmatrix} \begin{bmatrix} m \\ 2 \\ -m \end{bmatrix} \begin{bmatrix} m \\ 2 \\ -m \end{bmatrix} + \frac{2}{1} \end{bmatrix} \begin{bmatrix} m \\ 2 \\ -m \\ n \\ m \\ n+1 \end{bmatrix} + \frac{2}{1} \end{bmatrix} \begin{bmatrix} m \\ 2 \\ -m \\ n \\ n \\ n \end{bmatrix} + \frac{2}{1} \end{bmatrix} \begin{bmatrix} m \\ 2 \\ -m \\ n \\ n \\ n \\ n+1 \end{bmatrix} + \frac{2}{1} \end{bmatrix} \begin{bmatrix} m \\ 2 \\ -m \\ n \\ n \\ n \\ n+1 \end{bmatrix} + \frac{2}{1} \end{bmatrix} \begin{bmatrix} m \\ 2 \\ -m \\ n \\ n \\ n \\ n+1 \end{bmatrix} + \frac{2}{1} \end{bmatrix} \begin{bmatrix} m \\ 2 \\ -m \\ n \\ n \\ n \\ n \\ n+1 \end{bmatrix} + \frac{2}{1} \end{bmatrix} \begin{bmatrix} m \\ 2 \\ -m \\ n \\ $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| (F)      | $\delta := \begin{bmatrix} i & -i \\ 2 & 1 \end{bmatrix} \begin{bmatrix} m \\ 2 \\ 1 + -m \\ m \\ 1 \end{bmatrix} - m T = \begin{bmatrix} m \\ 2 \\ -m \\ n+1 \\ m \\ 1 \end{bmatrix} - \delta - propagated to cycle n n+1 m n+2 as a function of 1 the previous cycle $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| (G)      | $\delta := \begin{bmatrix} i & -i \\ 2 & 1 \end{bmatrix} \begin{bmatrix} m \\ 2 \\ m \\ 1 \end{bmatrix} - m \begin{bmatrix} m \\ 2 \\ 1 \\ m \\ 1 \end{bmatrix} - m \begin{bmatrix} m \\ 2 \\ 1 \\ m \\ 1 \end{bmatrix} + \delta \begin{bmatrix} m \\ 2 \\ m \\ 1 \end{bmatrix} = \frac{2}{1 - \frac{2}{1}} + \frac{2}{1 - \frac{2}{1}} = \frac{2}{1 - \frac{2}{1}} + \frac{2}{1 - \frac{2}{1}} = \frac{2}{1 - \frac$ |

| (Н)      | $\delta := \begin{bmatrix} i & -i \\ 2 & 1 \end{bmatrix} \begin{bmatrix} m \\ 1 + \frac{2}{m} \\ 1 \end{bmatrix} - m T \\ 2 \end{bmatrix} \begin{bmatrix} -m \\ 2 \\ m \\ 1 \end{bmatrix} + \delta \begin{bmatrix} -m \\ 2 \\ m \\ 1 \end{bmatrix} + \delta \begin{bmatrix} -m \\ 2 \\ m \\ 1 \end{bmatrix}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|          | Substitute equation C $\begin{bmatrix} 1 \\ -mZ \\ 1 + \frac{-mZ}{m1} \end{bmatrix}$ As j> inf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Figure 22 - Quantitative Subharmonic Instability Derivation.

The closed form expression in figure 22I indicates that the glitch current decays for the condition of the time rate of inductor charge current greater than the time rate of discharge. In the opposite condition the glitch current grows leading us to the conclusion that the system is unstable.

Intuitively one can translate the inductor charging slope boundary condition  $(m_1 = m_2)$  to the condition where duty cycle equals fifty percent (D=0.5); therefore a current mode boost regulator operating in continuous conduction mode is unstable for duty factors greater than fifty percent (Figure 23). This finding concurs with the previous graphic example. It should be noted that this condition does not occur if the regulator in operating in discontinuous mode.

Figure 23 - Slope to Duty Cycle Linkage

Fortunately there are ways to alleviate subharmonic instability without limiting the duty cycle of the regulator to less then fifty percent. A technique known as slope compensation modulates the current feedback loop's peak inductor current set point as a function of switch duty cycle. This is accomplished by deriving a

ramp from the clock and adding it to the sensed inductor

current or to the voltage error amplifier output. Some

integrated controllers such as the National LM1577-xx

provide slope compensation within the IC while others

require the user to add peripheral circuitry to accomplish the task.

#### **Analysis Techniques**

At first look one might be tempted to consider a raw transient analysis approach using a generalized analysis program such as Spice for the analysis of switching regulator circuits. The drawbacks of this approach are that simulation times will be excessive and the stability of the control loop is often ignored due to the neglect of small signal analysis. Spice can only perform a small signal analysis in one state of the circuit at a time unless something is done to generate a circuit model which represents both states in one circuit.

It soon becomes obvious that more than one analysis technique may be required for every design. One technique is needed to determine the large signal state of the magnetics while another is needed to determine the stability of the feedback loop(s), input impedance, and output impedance. Small signal approaches must somehow

combine the small signal models of the various switch states into one simulateble model which can be used to predict control loop stability. To be of any use, a solution must characterize the input to output path as well as the duty cycle to output of the circuit under

study. Modeling and analysis techniques must provide design insight into the circuit operation as well as solve the problem at hand. In the quest for accurate design tools the need for non-laborious solutions must not be overlooked.

# **State Space Averaging**

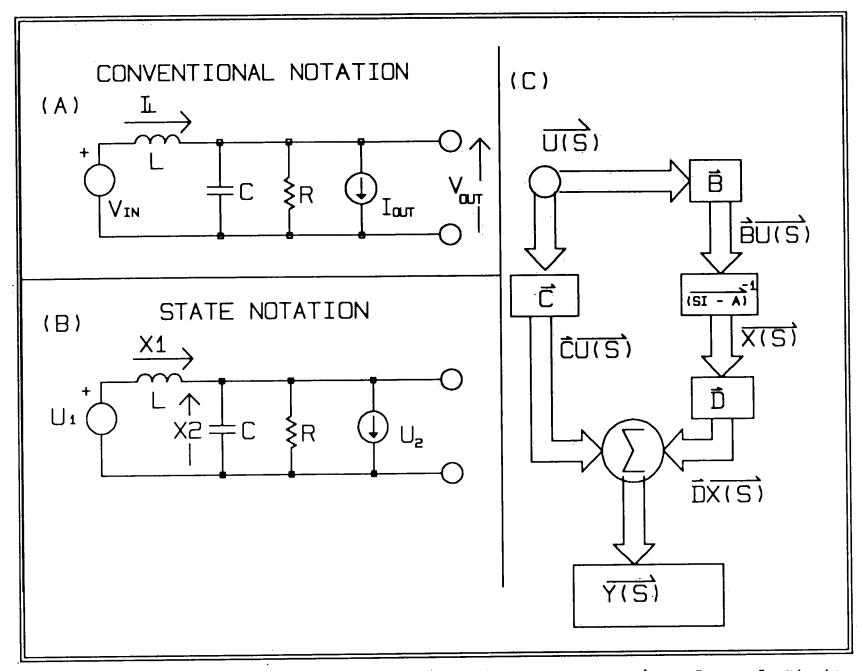

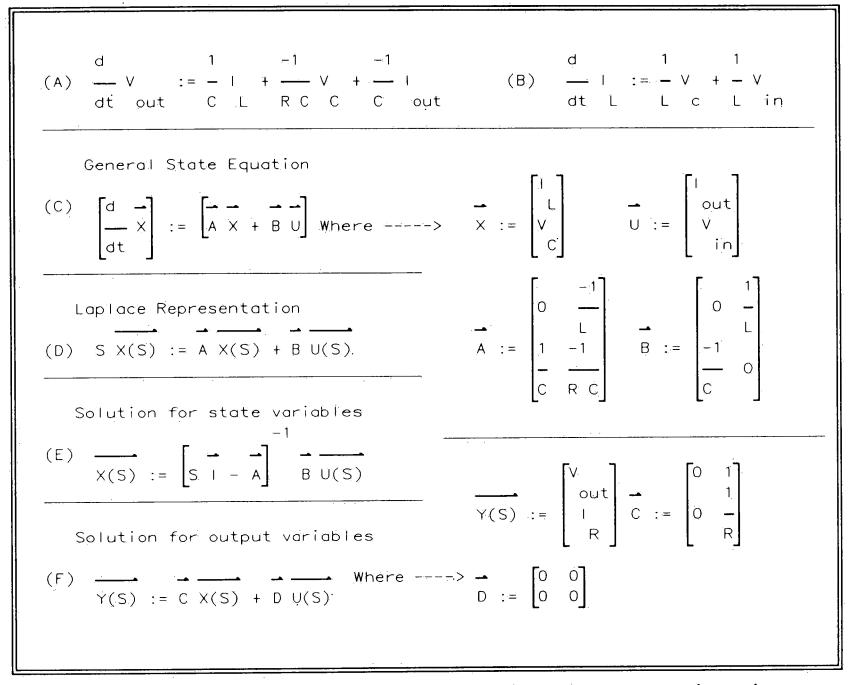

State space averaging is a technique which is an extension of state variable analysis techniques used in linear circuit analysis. Let us first consider the state variable analysis of the linear time invariant LCR circuit shown in Figure 24A.

Figure 24 - Linear LCR circuit with Conventional and State Notation.

By writing a loop equation for  $V_{out}$  and a node equation for  $I_L$  one can rearrange the terms of each equation to solve for the derivatives of the inductor state  $I_L$  and the capacitor state  $V_C$  (See figure 25A and 25B). This now can be written in the general form shown in figure 25C where vector X represents the states of the two energy storing

elements, vector U represents the input(s) to the system,

matrix A describes the sourceless properties of the

network, and matrix B describes the reaction of the system

to the source vector. A solution for the state variables

of the system may be solved for by converting the

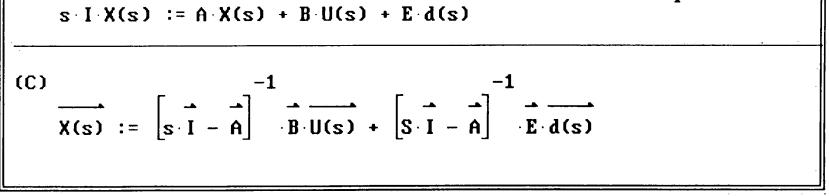

derivatives to a Laplace transform representation and applying the manipulation shown in figures 25D and 25E.

Figure 25 - Linear State Analysis of a LCR Circuit.

In most cases the state variables are not the variables of interest so a method to obtain the desired output variables is needed. The desired output variables

represented by Y(S) in figure 24C and 25F are simply a sum of the state variables X(S) and the input source vector U(S) weighted by the matrices C and D.

In order to apply the previously described technique to any system, the state variables must be a continuous linear function of time. Obviously switching regulators meet this criteria within each condition of the switch since they are combinations of linear circuit elements, but fail to meet the criteria across switch transition boundaries. If one were to separate the system into equivalent linear circuits for each condition of the system; the state variables within each time cell of these linear circuits could be solved for in a piecewise manner using the previously mentioned techniques provided that the boundary condition between each switch condition is known (See figure 26).

```

Generalized state equations for n time periods

within a period kT (k>=0

note that there are n unique A and B matrices pairs one

for each state of the system.

x'(t) = A_1x(t) + B_1u(t) {kT < t < kT+t<sub>1</sub>-}

x'(t) = A_2x(t) + B_2u(t) {kT+t<sub>1</sub>+ < t < kT+t<sub>2</sub>-}

x'(t) = A_2x(t) + B_2u(t) {kT+t<sub>2</sub>+ < t < kT+t<sub>3</sub>-}

```

$$x'(t) = A_3x(t) + B_3u(t)$$

$$(kT+t_2 + < t < KT+t_3)$$

$$(t) = A_nx(t) + B_nu(t)$$

$$(kT+t_{n-1} + < t < (k+1)T-)$$

Figure 26 - Generalized State Equations for a n Switch

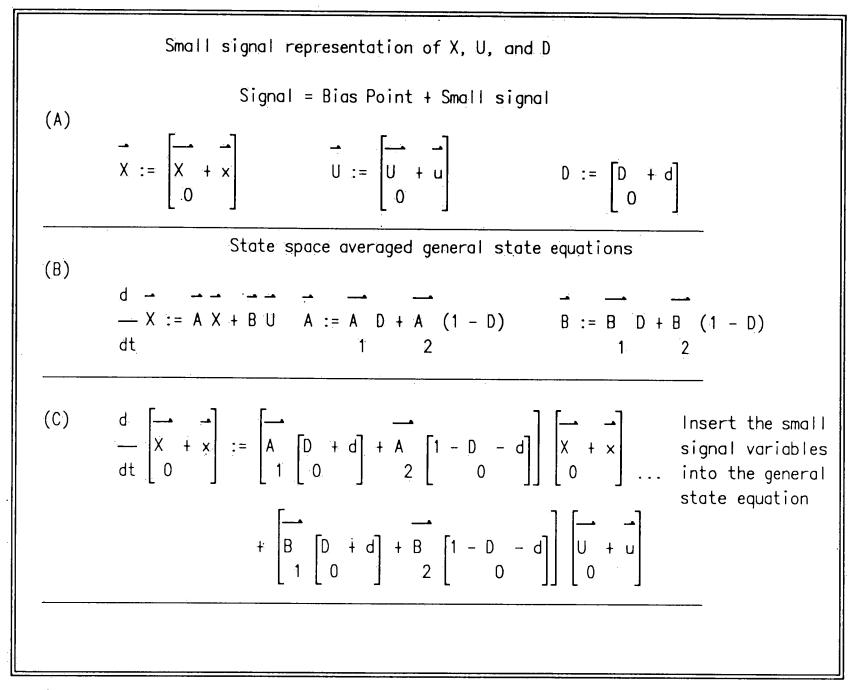

Solving the separate state equations at each boundary condition for every clock cycle would become a computation intensive task which negates the original intent of modeling the system to allow classical small signal analysis techniques to be utilized. Since the switching regulator is discontinuous by its nature, it is necessary to force the system into a continuous representation by ignoring the switching components present in the state variables. In short, we are only interested in the value of the state variables X(t) just before a change in system condition such as a switch transition point.

For initial discussion sake, let's consider the case of a system with two switch states (n=2). If we redefine the switch condition time intervals  $\{t_1, t_2, .., t_n\}$  shown in figure 26 as percentages of the periodic interval T;  $t_1$ on the kth cycle would be denoted  $\{d_{<1,k>T}\}$ . Two state equations are now needed to describe the system, one for each switch condition. The first state equation describes the system during the time period  $d_{<1,k>T}$ , where the switch is closed while a second state equation is needed

for the time period  $d_{<2,k>T} = \{ 1 - d_{<1,k>T} \}$ , where the switch is off. Matrices  $A_1$  and  $B_1$  describe the system while the switch is on and matrices  $A_2$  and  $B_2$  describe the system when the switch is off. In order to merge the two state equations into one, we must ignore the switching

components present in X(t) which implies that we are sampling X(t) just before the switch transition points but not during the actual transition where a discontinuity in the signal is known to exist. We can consider X(kT) and X((k+d)T) to be a sampled data representation of a continuous version of X(t) with samples at the beginning of the respective interval; whether it be the switch opening or switch closing interval. Two state equations may now be written in figures 27A-D using the sampled data signal in place of the previously used continuous signals X(t) and U(t). If we assume that the clock interval T is much smaller than the smallest period of interest desired from the analysis, then the derivative of the discrete state variables X(kT) and X(kT+dT) may be approximated by calculating the slope with respect to time between samples (figures 27E and 27F).

i.

Figure 27 - Sampled Data State Equations.

Inserting the approximated derivatives into the generalized state equation for each switch condition and changing the dependent variable time to the sample time generates a state equation for each switch condition on the kth cycle as detailed in figures 27E and 27F.

$$(A) \begin{bmatrix} \overline{X((k+d) T) - X(kT)} \\ d T \end{bmatrix} := \begin{bmatrix} \overline{A} & \overline{X(kT)} + \overline{B} & U(kT) \\ 1 & 1 & 1 \end{bmatrix}$$

Switch closed

evaluated beginning

of the cycle

$$(B) \begin{bmatrix} \overline{X((k+1) T) - X((k+d) T)} \\ (1-d)T \end{bmatrix} := \begin{bmatrix} \overline{A} & \overline{X((k+d) T)} + \overline{B} & U((k+d) T) \\ 2 & 2 \end{bmatrix}$$

Switch open evaluated at the

beginning of the duty cycle

$$(C) \\ \overline{X((k+d) T)} := d T \begin{bmatrix} \overline{A} & \overline{X(kT)} + \overline{B} & U(kT) \\ 1 & 1 & 1 \end{bmatrix} + \overline{X(kT)}$$

$$(0) \\ \overline{X((k+1) T)} := (1-d) T \begin{bmatrix} \overline{A} & \overline{X((k+d) T)} + \overline{B} & U((k+d) T) \\ 2 & 2 \end{bmatrix} + \overline{X((k+d) T)} \end{bmatrix} + \overline{X((k+d) T)}$$

Figure 28 - Sampled Data State Equations.

By choosing the beginning of the clock cycle as the reference point and applying the manipulations in figures 28A and 28B; an equation representing the value of the sampled state variables on the next clock cycle as a function of the current clock cycle is formed in figure

28C and 28D. The equation in figure 29A has terms which

are first and second order functions of the clock period T

that we have already assumed to be small compared to the

- period of interest. By setting second order time terms to

- zero and approximating the source vector U at time (k+dT)

- with its derivative in equation 29B, a function which