#### Lehigh University Lehigh Preserve

Theses and Dissertations

1990

#### The design of a 70 mhz digitally controlled gain amplifier and quadrature demodulator for the GSM European digital cellular system

Scott Leonard Forgues *Lehigh University*

Follow this and additional works at: https://preserve.lehigh.edu/etd Part of the <u>Electrical and Computer Engineering Commons</u>

#### **Recommended** Citation

Forgues, Scott Leonard, "The design of a 70 mhz digitally controlled gain amplifier and quadrature demodulator for the GSM European digital cellular system" (1990). *Theses and Dissertations*. 5409. https://preserve.lehigh.edu/etd/5409

This Thesis is brought to you for free and open access by Lehigh Preserve. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of Lehigh Preserve. For more information, please contact preserve@lehigh.edu.

#### THE DESIGN OF A 70 MHZ DIGITALLY CONTROLLED GAIN AMPLIFIER AND QUADRATURE DEMODULATOR FOR THE GSM EUROPEAN DIGITAL CELLULAR SYSTEM

ſſ.

цŤ

**~**

•••

by

Scott Leonard Forgues

A Thesis Presented to the Graduate Committee of Lehigh University in Candidacy for the Degree of Master of Science in Electrical Engineering

> Lehigh University November, 1990

> > 2

\*

~

#### Approval

This thesis is accepted and approved in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering.

007. 29/ 1990 Date

۲

Vonder Vin

Professør in Charge

.D.Var Laurence

CSEE Department Chairman

√<sup>r</sup>

Å

.

- ii -

#### Acknowledgements

The author would like to thank his advisor, Dr. Douglas Frey, for his guidance in the presentation of this thesis.

The author would also like to thank the GSM Digital Cellular Development Team at AT&T Bell Laboratories in Reading, PA. The team, consisting of Paul C. Davis, Iconomos A. Koullias, David E. Bien, Karl R. Gardner, Guy J. Shovlin, and Stephen E. Parks, provided the driving force in the definition, design, and manufacture of the integrated circuit described herein. In addition, they provided the support and guidance needed to bring this thesis to a reality.

Most importantly, a special thanks goes to my parents, Gerald and Mignonne Forgues. For without their support and encouragement, my many years of academic pursuits would not be possible.

#### **Table of Contents**

6

| 1. Abstract 1                                             |

|-----------------------------------------------------------|

| 2. Introduction                                           |

| 2.1 The GSM Digital Cellular Telephone System             |

| 2.2 GSM Requirements for the IF Amplifier and Demodulator |

| 2.2.1 Power Level Detection                               |

| 2.2.2 Required Gain                                       |

| 2.2.3 Noise Figure Requirements4                          |

| 2.2.4 Power Consumption4                                  |

| 2.2.5 Input and Output Definition                         |

| 2.2.6 GMSK Demodulator Requirements5                      |

| 2.2.7 Temperature and Supply Requirements                 |

| 2.3 Circuit Implementation5                               |

| 2.4 IF Amplifier Definition6                              |

| 2.4.1 Gain Error Allocation7                              |

| 2.4.2 Linear Array Limitations7                           |

| 2.5 Double Balanced Mixer and Output Stage Subcircuit     |

| Definition                                                |

| 2.6 Quadrature Phase Shifter Subcircuit Definition        |

| 2.7 Digitally Controlled Bandgap Reference Subcircuit     |

| Definition9                                               |

| 3. Digitally Controlled Gain IF Amplifier                 |

| 3.1 Dual Gain State Differential Amplifier (DGSDA) Design |

| 3.1.1 Calculation of Gain, Input Impedance, and Output    |

| Impedance12                                               |

| 3.1.2 Determination of Component Values and Tail          |

| Currents                                                  |

| 3.1.3 Errors Due to Temperature and Process               |

| Variations15                                              |

| 3.1.4 Example Calculation for the 24 / 0 dB DGSDA         |

| 3.2 Digitally Controlled Current Switch (DCCS) Design     |

| 3.2.1 Digitally Controlled Current Switch Operation       |

| 3.3 Emitter Follower Design                               |

•

.

#### **Table of Contents**

•

| 3.3.1 Example Calculations for 24 / 0 dB Emitter    |    |

|-----------------------------------------------------|----|

| Follower                                            | 24 |

| 3.4 Interconnection of Differential Amplifiers      |    |

| 3.4.1 Using Coupling Capacitors to Reduce Offset    |    |

| Problems                                            | 26 |

| 3.4.2 Calculated IF Amplifier Gain and Error        |    |

| Performance                                         | 27 |

| 3.4.3 IF Amplifier Simulation Results               |    |

| 4. Double Balanced Mixer and Output Stage           | 30 |

| 4.1 GMSK Demodulation                               |    |

| 4.2 Double Balanced Mixer Design                    |    |

| 4.2.1 Mixer Operation                               | 33 |

| 4.2.2 Gain Determination and Selection              |    |

| 4.2.3 Low Pass Output Filter                        |    |

| 4.3 Output Stage Design                             |    |

| 4.4 Example Calculation for Mixer and Output Stages |    |

| 4.5 Simulation Results                              |    |

| 5. Quadrature Phase Shifter                         | 43 |

| 5.1 Buffer Design                                   | 43 |

| 5.2 Phase Shifter Design                            | 44 |

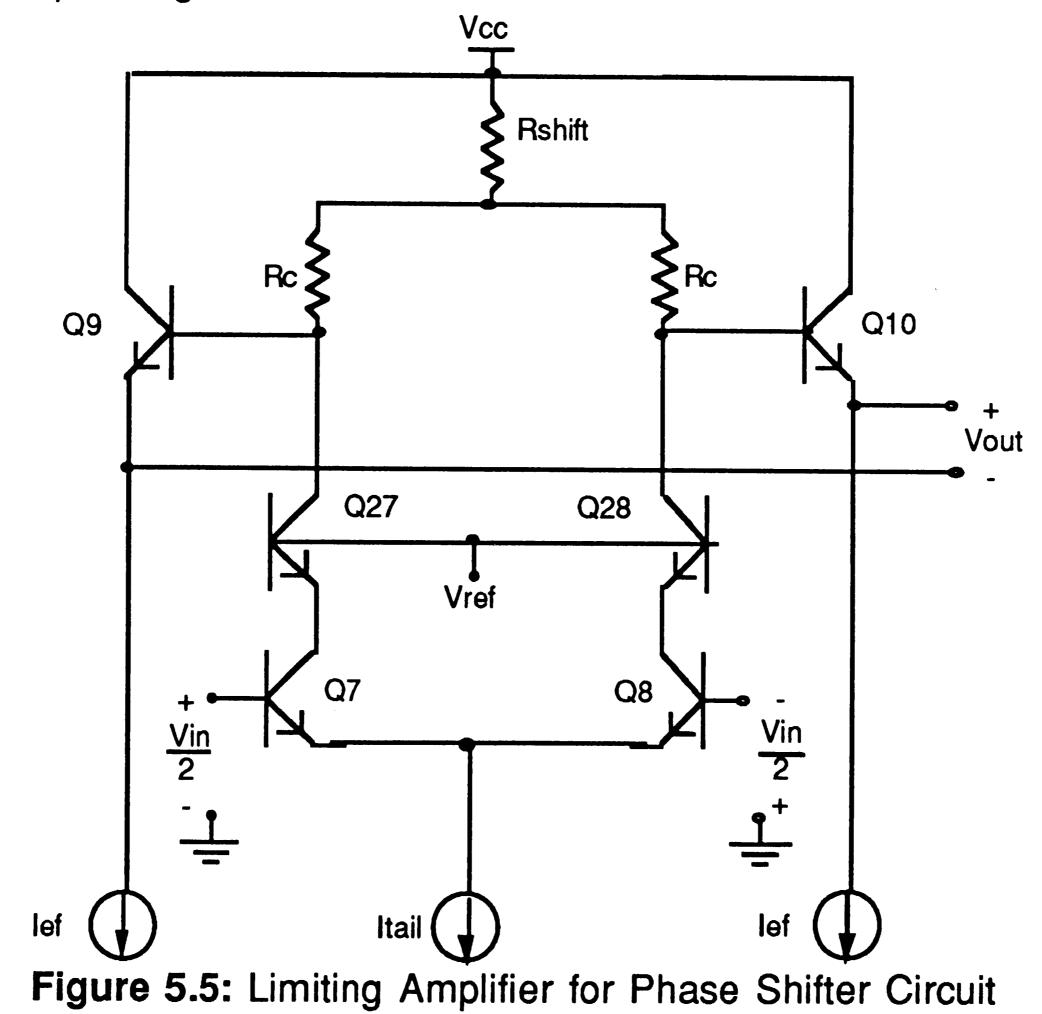

| 5.3 Limiting Amplifier Design                       | 48 |

| 5.4 Simulation Results                              | 50 |

| 6. Digitally Controlled Bandgap Voltage Reference   | 51 |

| 6.1 Digitally Controlled Bandgap Design             | 52 |

| 6.2 Reference Voltage Design                        | 53 |

| 6.3 Temperature Dependent Current Mirror Design     | 53 |

| 6.4 Temperature Independent Current Mirror Design   |    |

| 6.5 Saturating Transistor Design                    | 54 |

| 6.6 Simulation Results                              | 55 |

| 7. Implementation and Experimental Results          | 57 |

| 7.1 Implementation of Block Diagram                 | 57 |

| 7.2 Layout                                          |    |

| 7.2.1 Floor Plan                                    |    |

r.

• • •

•

#### **Table of Contents**

.

• ...

.

۵

Ŷ

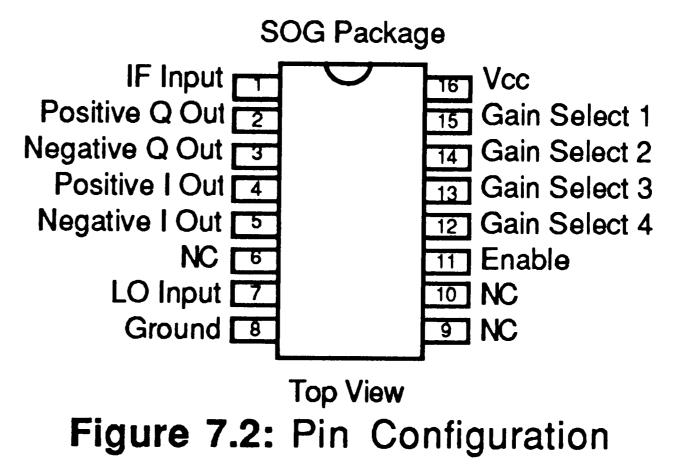

| 7.2.2 Pad and Pin Selection                             | 60 |

|---------------------------------------------------------|----|

| 7.3 Packaging                                           | 60 |

| 7.4 DC Simulation Results                               |    |

| 7.5 Experimental Results                                | 63 |

| 7.5.1 DC Results                                        |    |

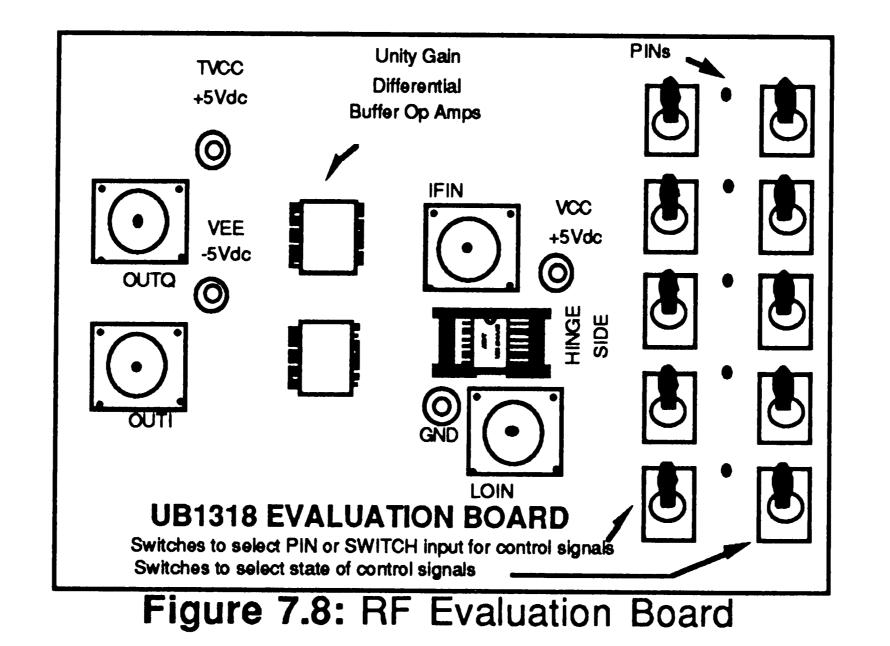

| 7.5.2 RF Evaluation Board Design                        |    |

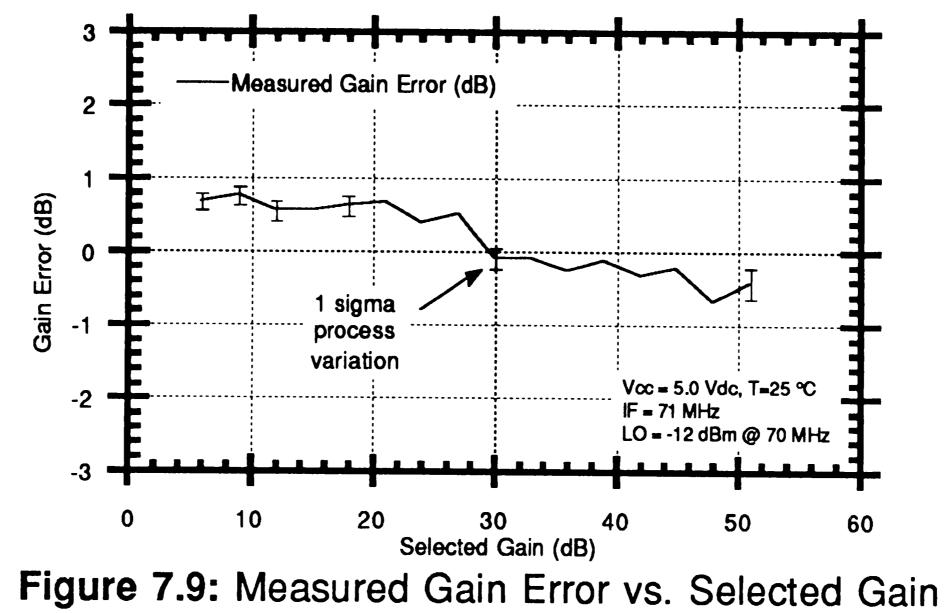

| 7.5.3 Gain and Phase Results                            |    |

| 7.5.4 Noise Results                                     | 73 |

| 7.5.5 Switching Speed Results                           | 73 |

| 7.6 Experimental Problems                               | 74 |

| 8. Conclusions                                          | 76 |

| Bibliography                                            |    |

| Appendices                                              |    |

| Appendix 1 - IF Amplifer Gain Test Simulation Results   |    |

| Appendix 2 - Mixer Gain & Phase Test Simulation Results |    |

| Appendix 3 - DC Operating Point Test Simulation Results |    |

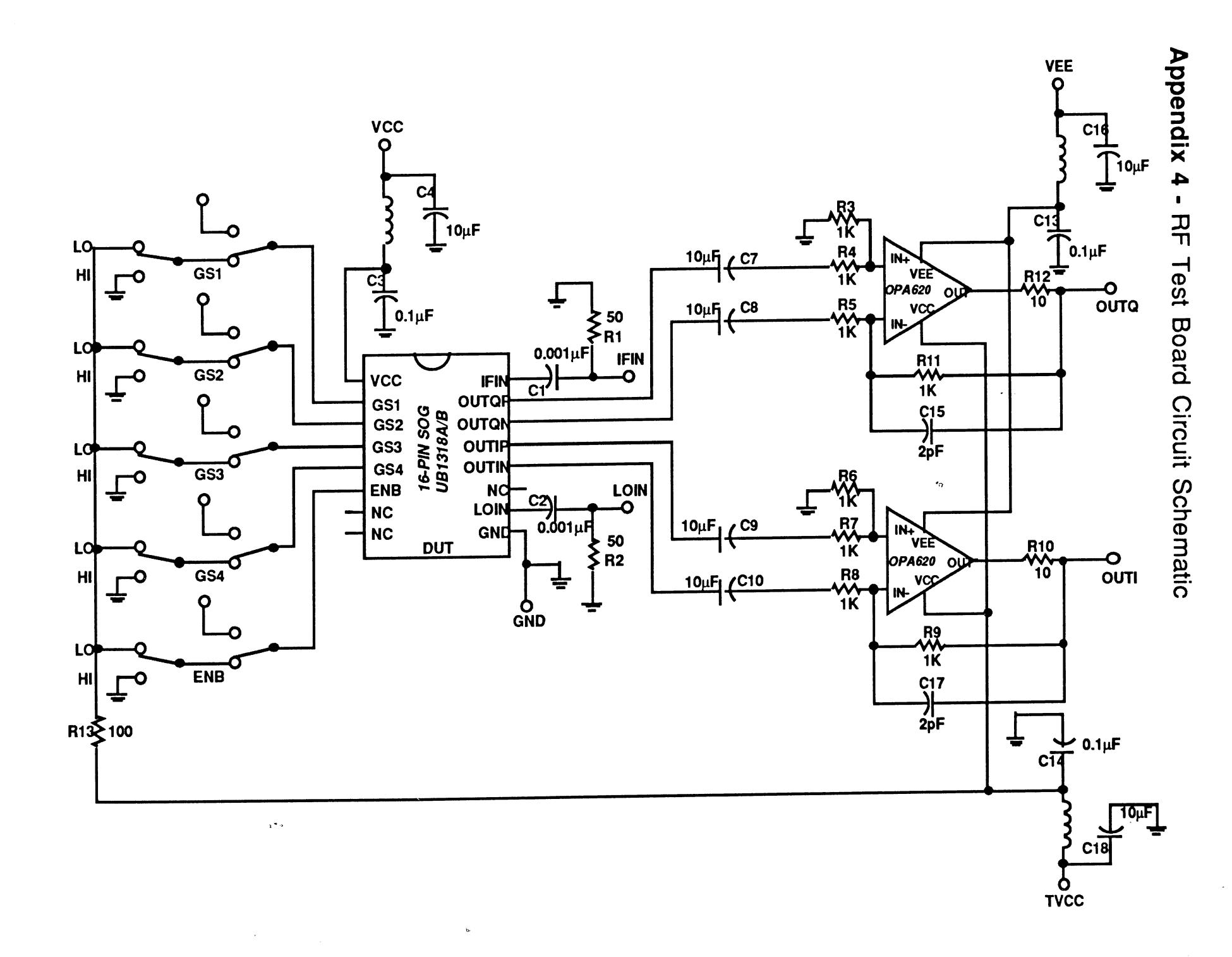

| Appendix 4 - RF Test Board Circuit Schematic            |    |

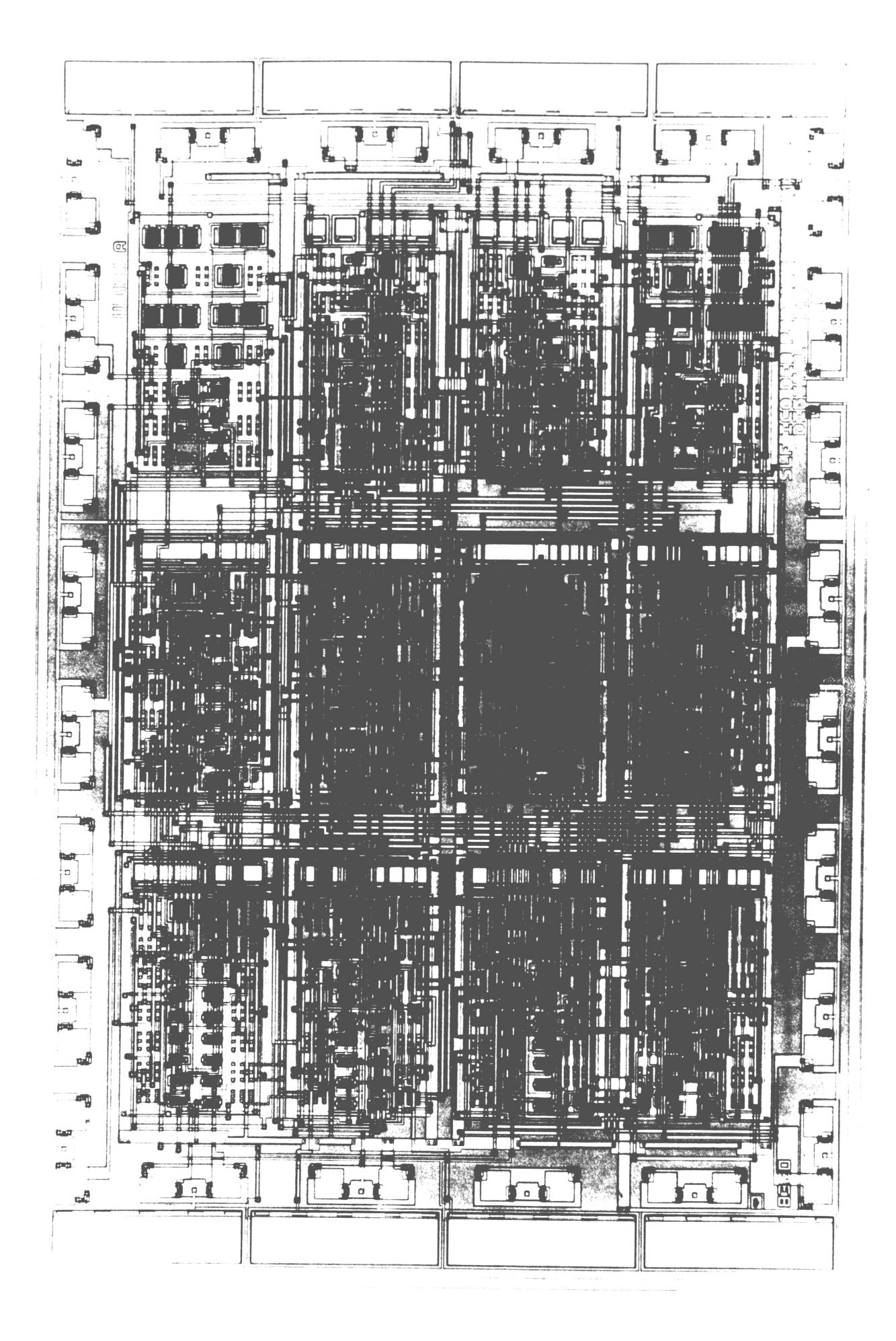

| Appendix 5 - Chip Photomicrograph                       |    |

| Appendix 6 - Impedance Test Simulation Results          |    |

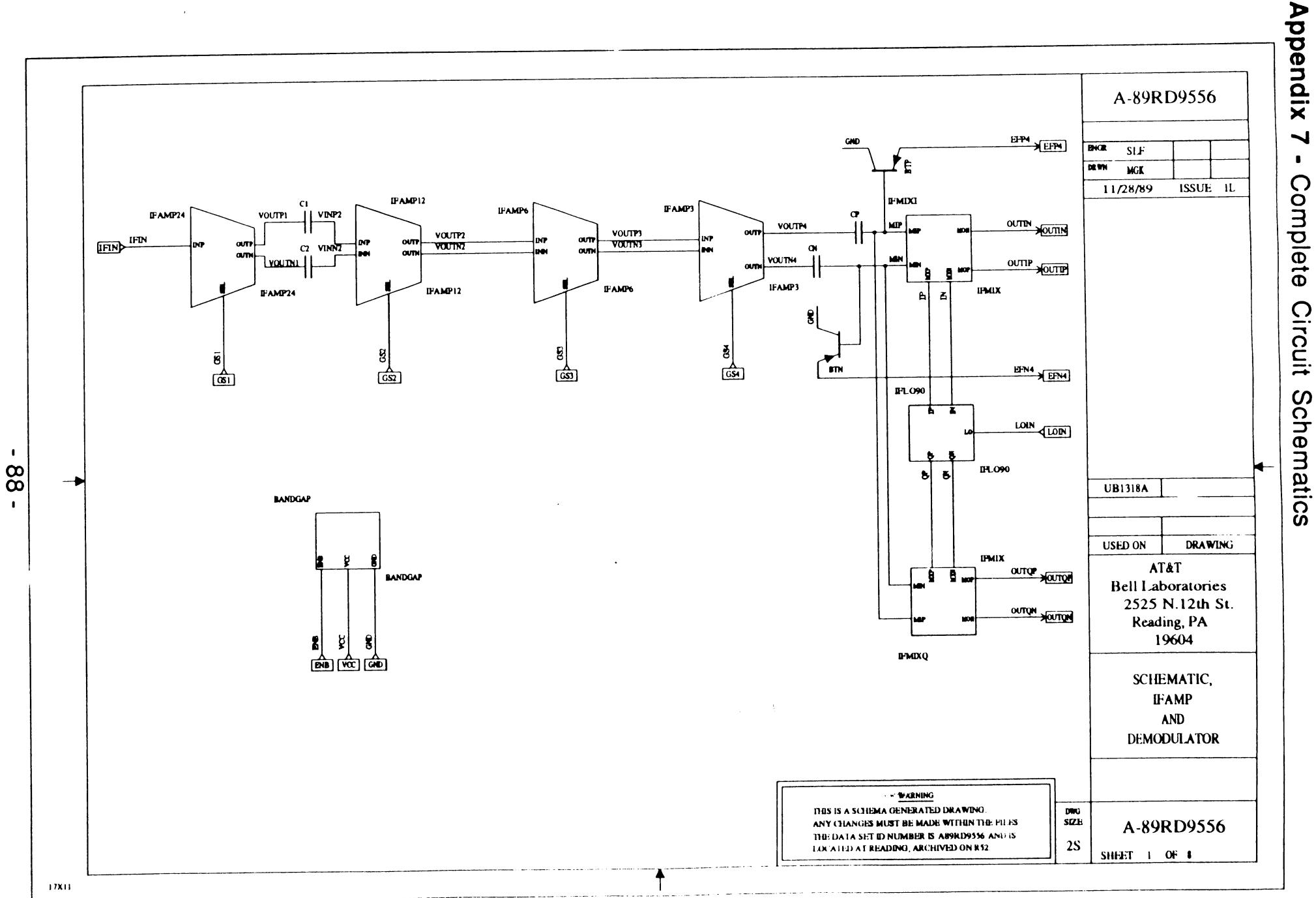

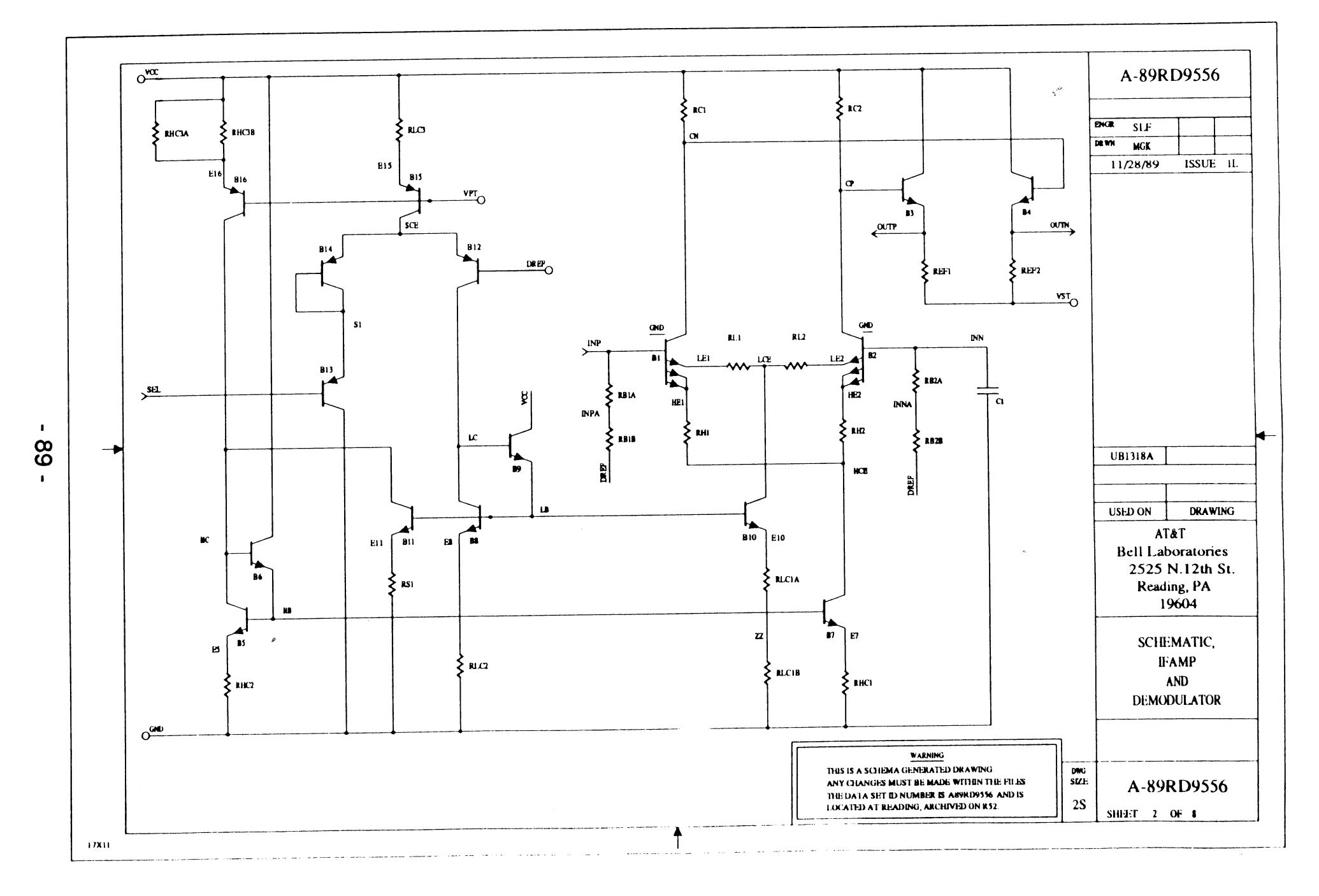

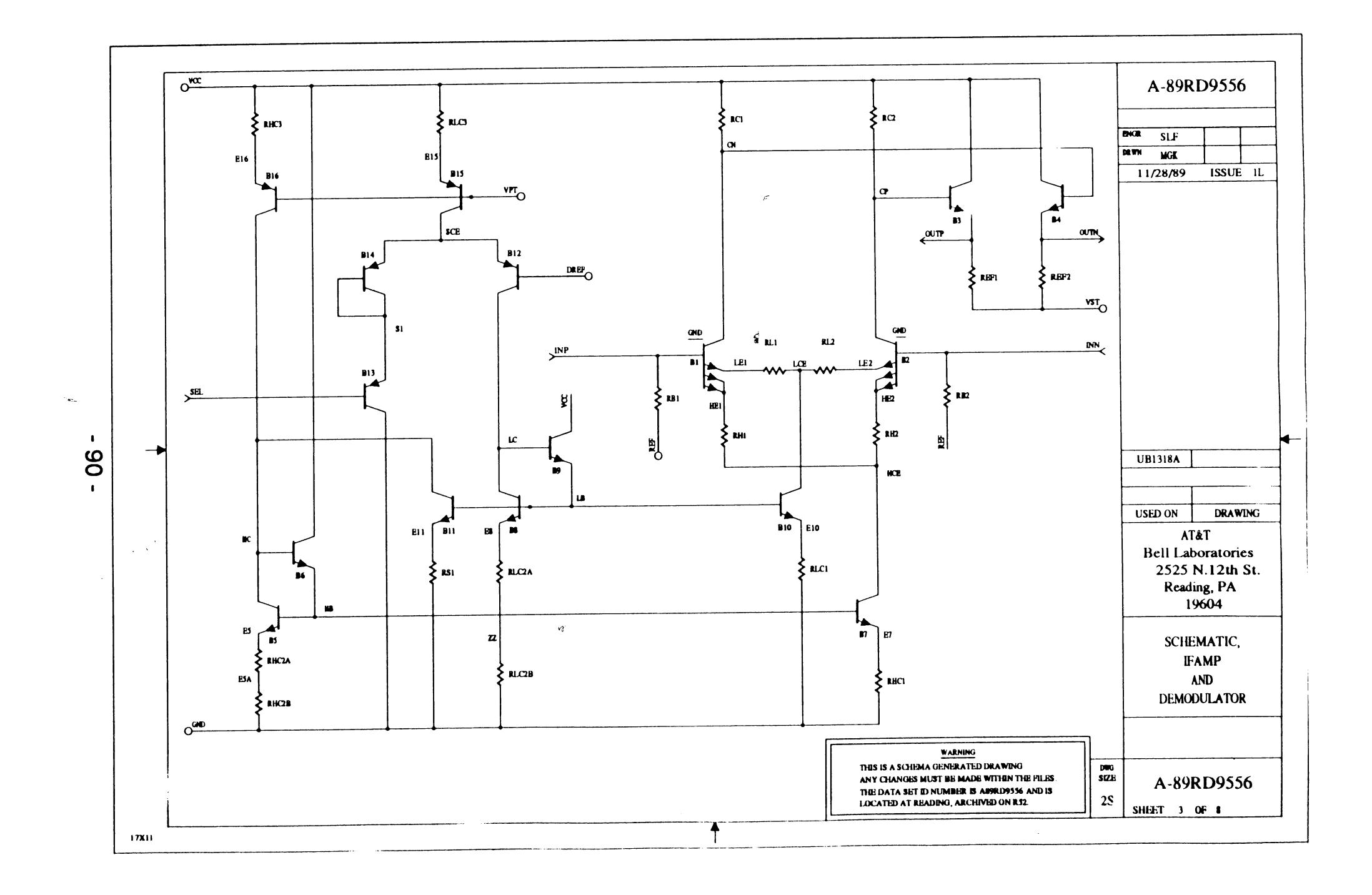

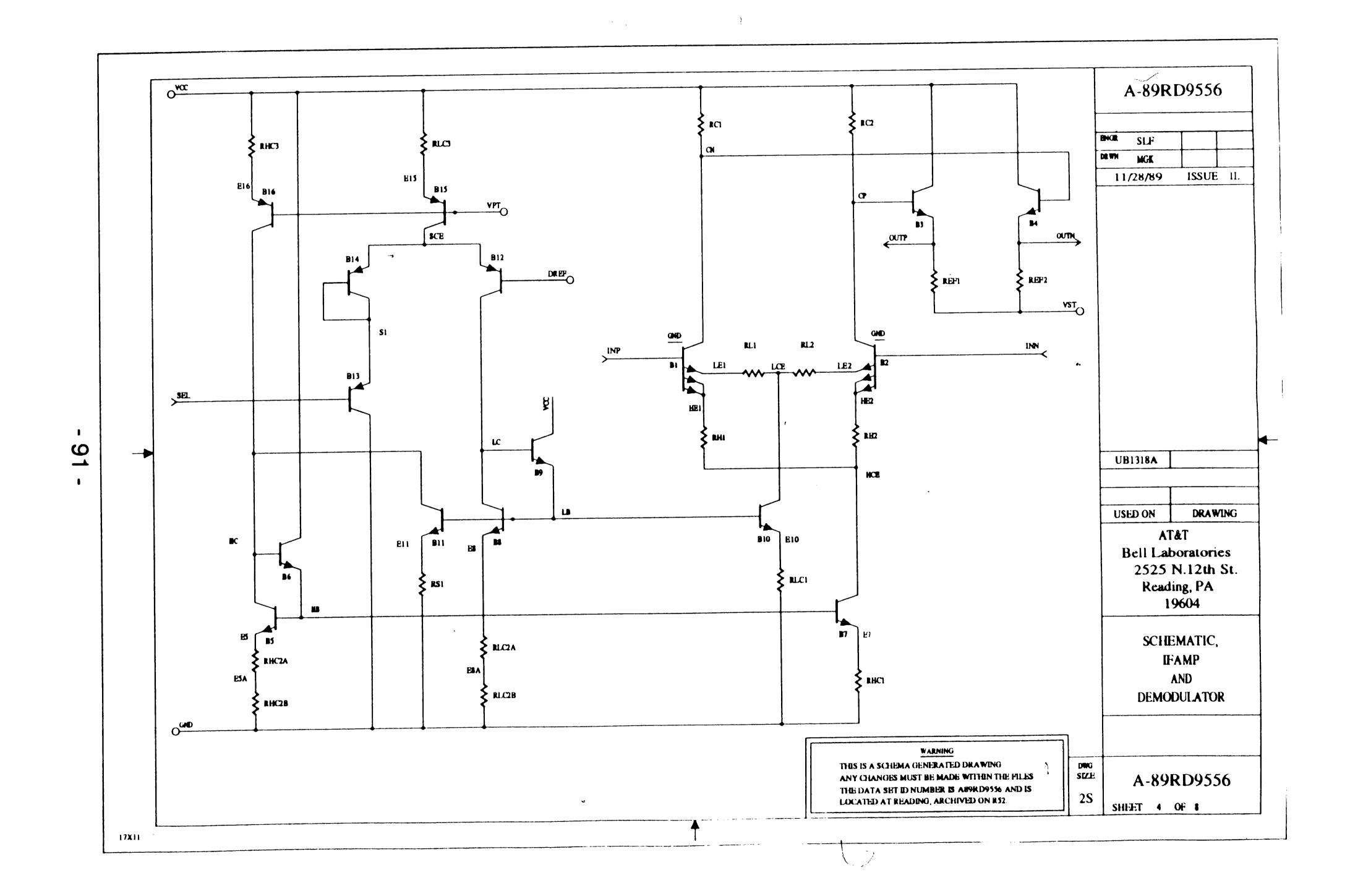

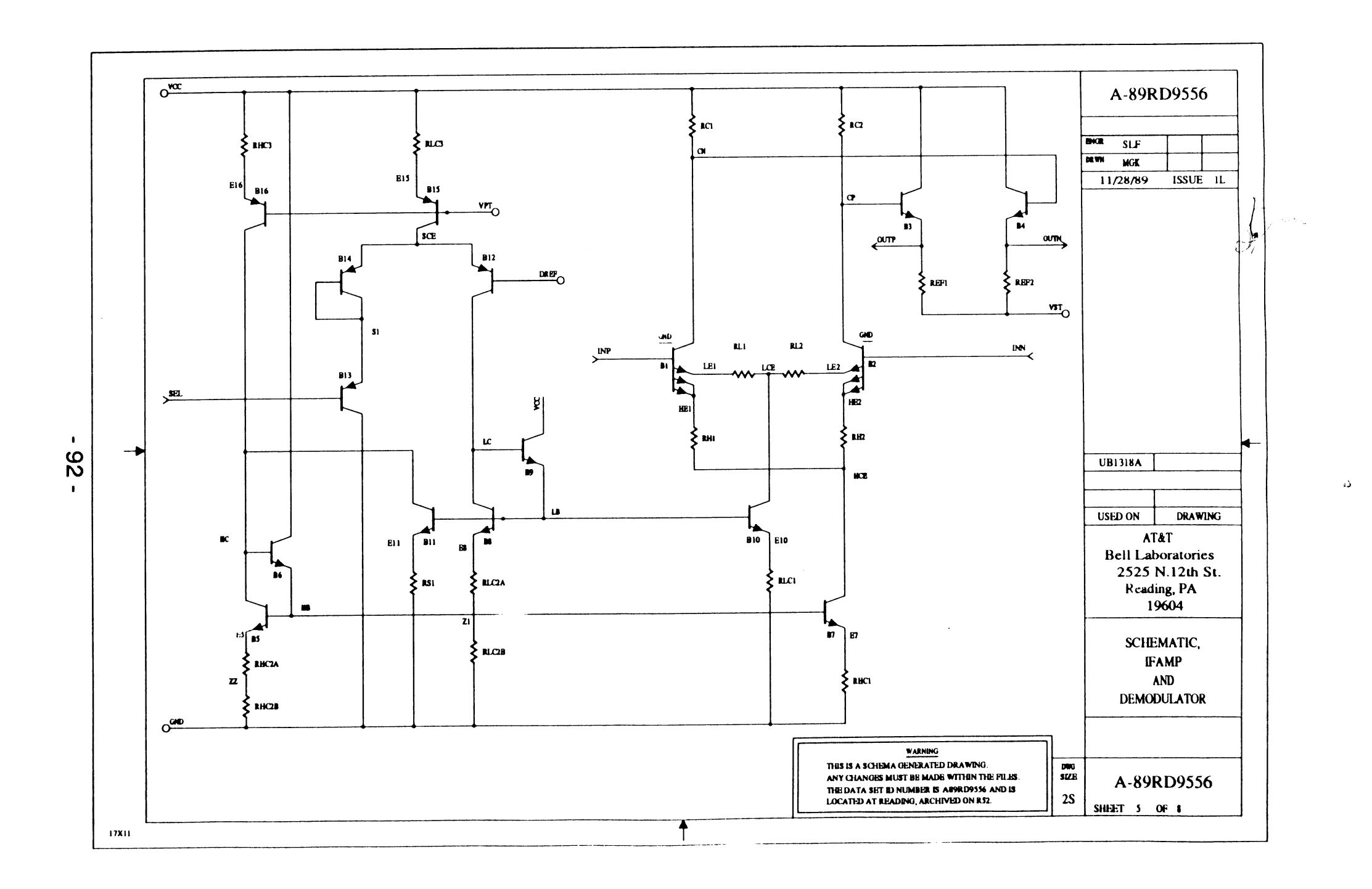

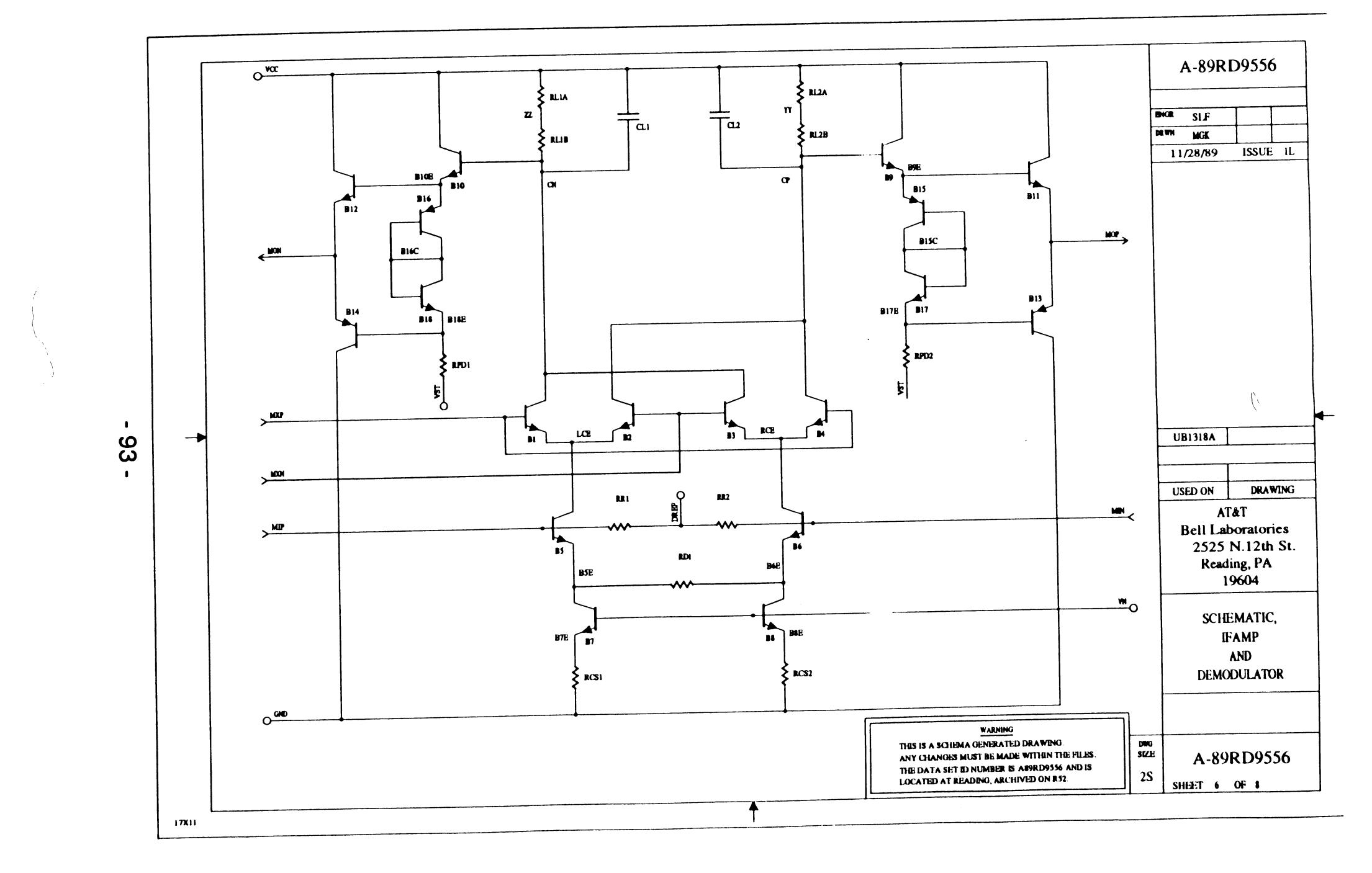

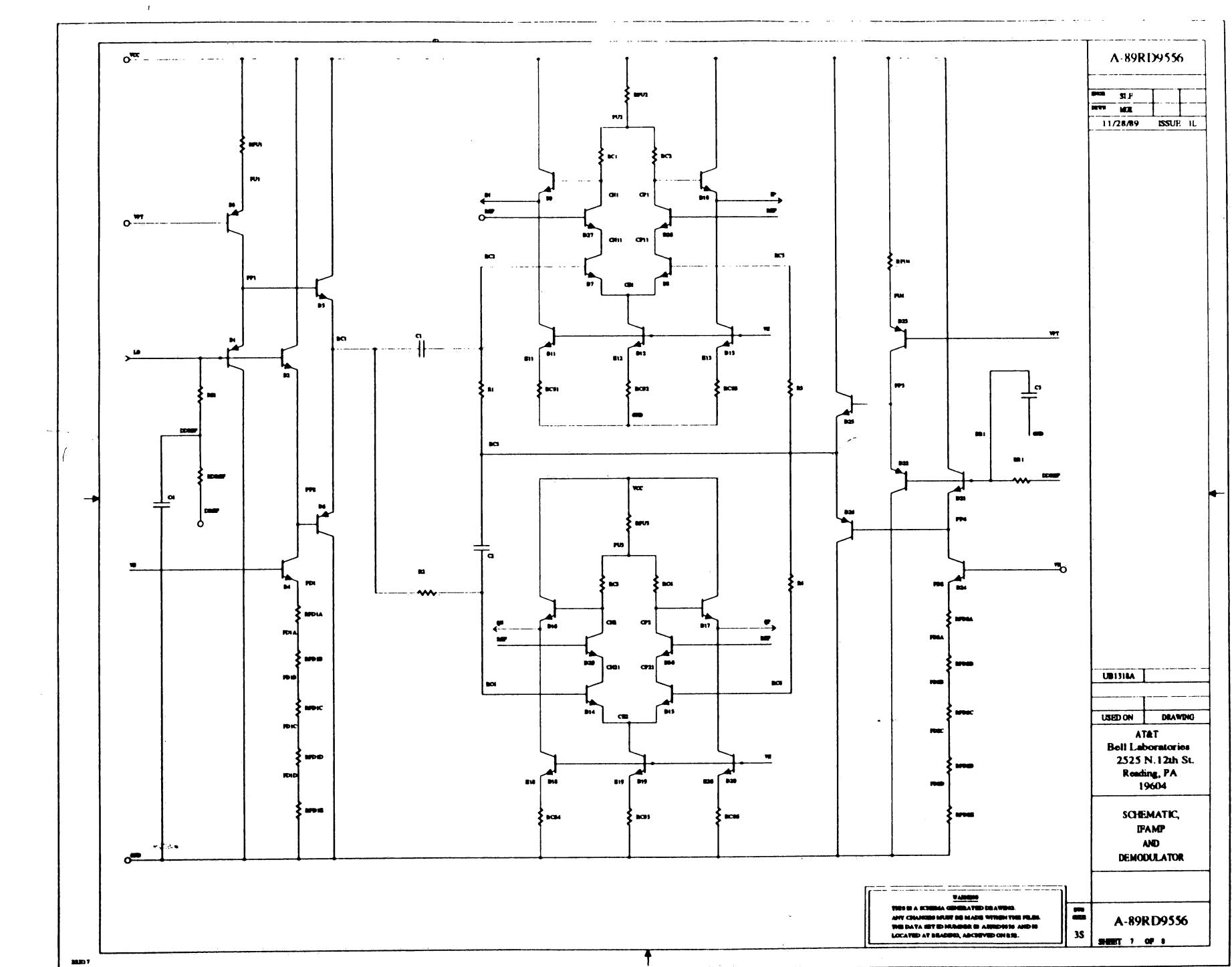

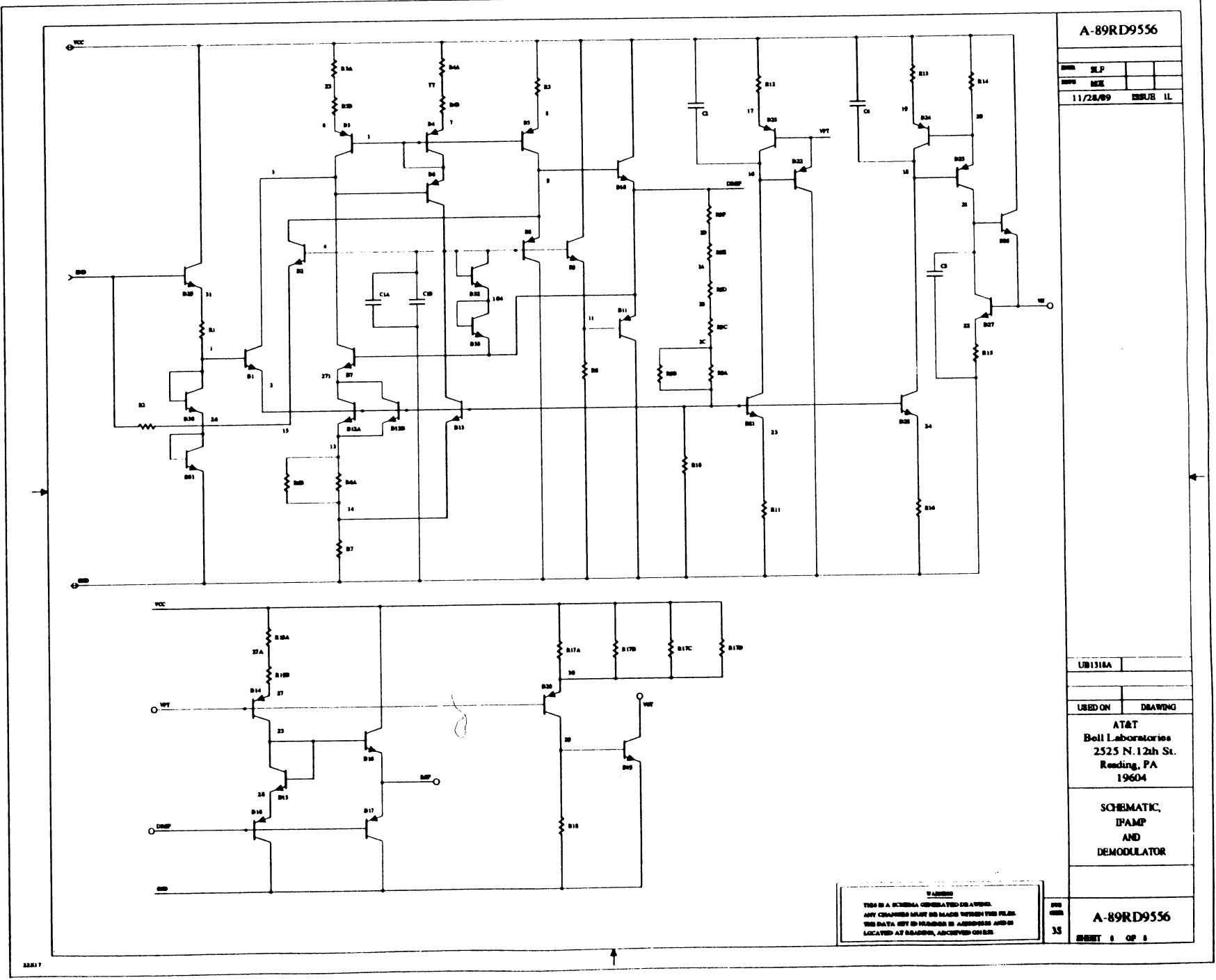

| Appendix 7 - Complete Circuit Schematics                |    |

| Vita                                                    |    |

|                                                         |    |

.

#### List of Tables

· ·

;

1

| Table 2.1: Gain Select Truth Table                            | 6  |

|---------------------------------------------------------------|----|

| Table 2.2: AT&T ALA202 Linear Array Component Totals          | 7  |

| Table 3.1: Resistor Values and Gains for the DCGDA Amplifiers | 27 |

| Table 3.2: Simulated Gains for the DCGDA Amplifiers           | 29 |

| Table 4.1: Phase Input Bit Representation                     | 31 |

| Table 7.1: Simulated DC Results                               | 61 |

| Table 7.2: Measured DC Results                                | 64 |

.

) "{·

- vii -

- and the

#### List of Figures

`

...

2

|        | Figure 2.1: IF Amplifier and Demodulator Block Diagram                | 6   |

|--------|-----------------------------------------------------------------------|-----|

|        | Figure 2.2: Mixer and Output Stage Block Diagram                      |     |

|        | Figure 2.3: Quadrature Phase Shifter Block Diagram                    | 9   |

|        | Figure 3.1: Digitally Controlled Gain Differential Amplifier (DCGDA)  |     |

|        | Subcircuit                                                            | 10  |

|        | Figure 3.2: Dual Gain State Differential Amplifier (DGSDA) Subcircuit | 11  |

|        | Figure 3.3: DGSDA Small-signal Equivalent Circuit                     | 12  |

|        | Figure 3.4: DGSDA Two-port Equivalent Circuit                         | 13  |

|        | Figure 3.5: Digitally Controlled Current Switch (DCCS) Subcircuit     |     |

|        | Figure 3.6: VRHC2, VBC11, and IQ11 During State Change                | 21  |

|        | Figure 3.7: Itail L and Itail H During State Change                   | 22  |

|        | Figure 3.8: Emitter Follower Subcircuit                               | 23  |

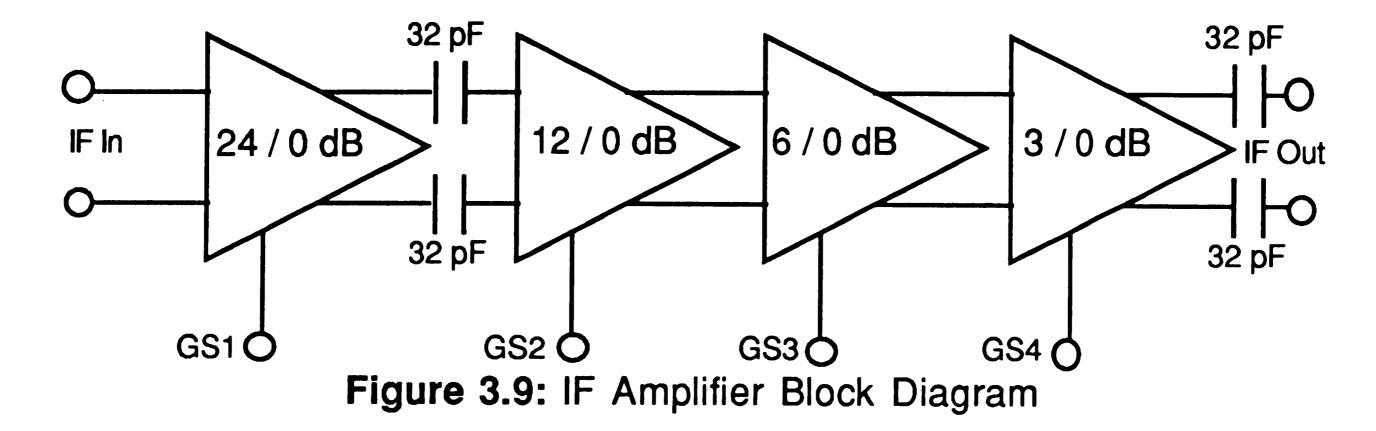

|        | Figure 3.9: IF Amplifier Block Diagram                                | 27  |

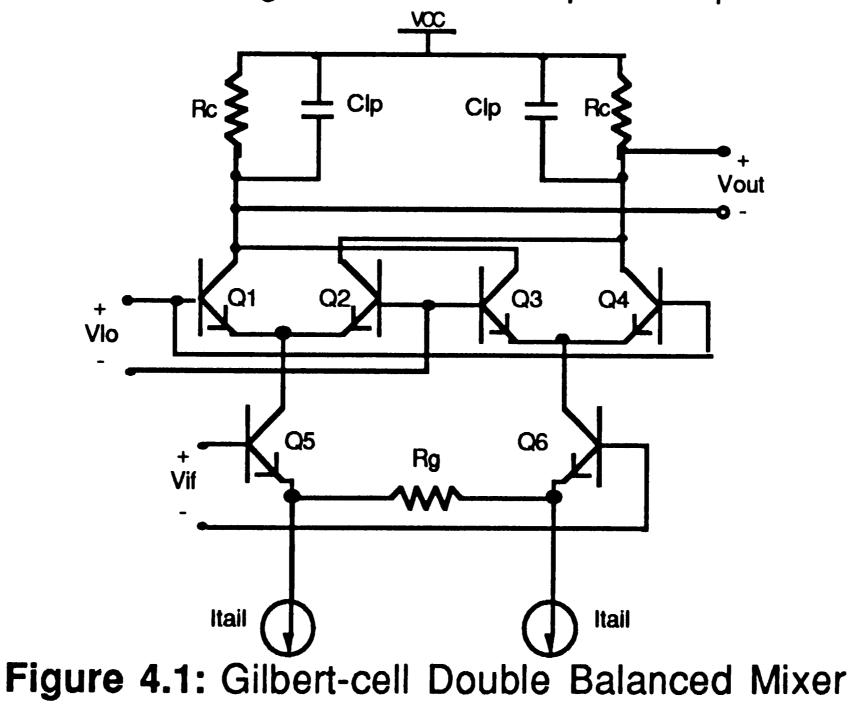

|        | Figure 4.1: Gilbert-cell Double Balanced Mixer                        | 32  |

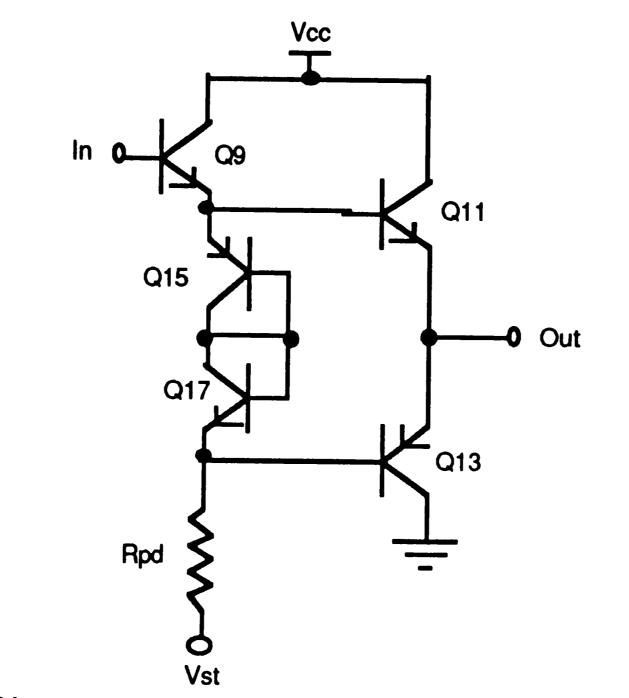

|        | Figure 4.2: Class AB Complementary Push-pull Output Stage             | 37  |

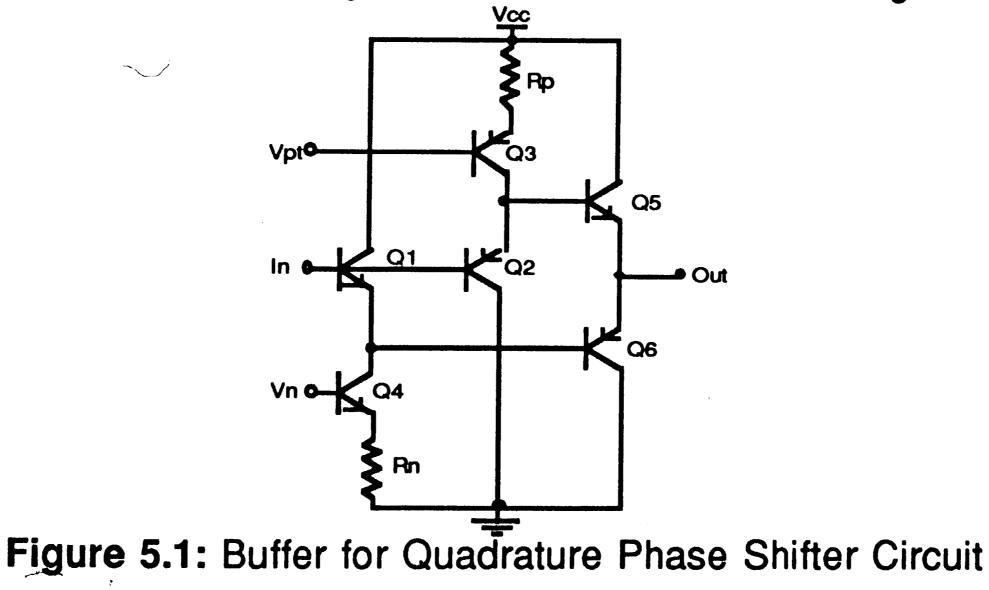

|        | Figure 5.1: Buffer for Quadrature Phase Shifter Circuit               | 43  |

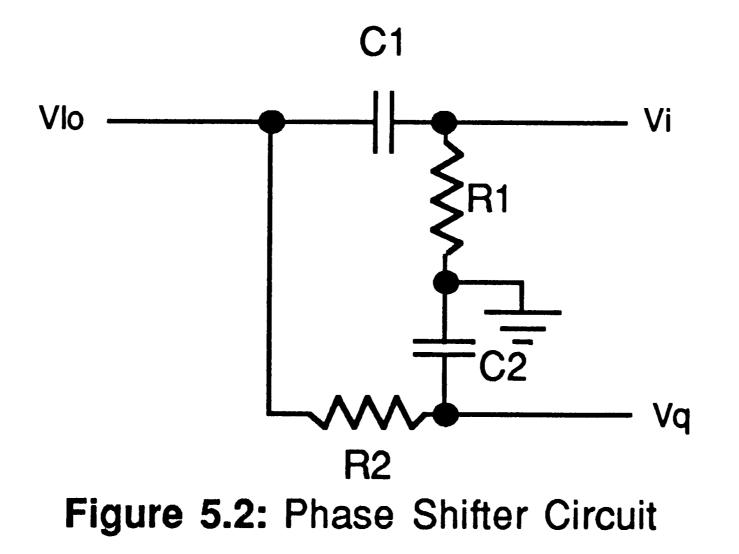

|        | Figure 5.2: Phase Shifter Circuit                                     | 44  |

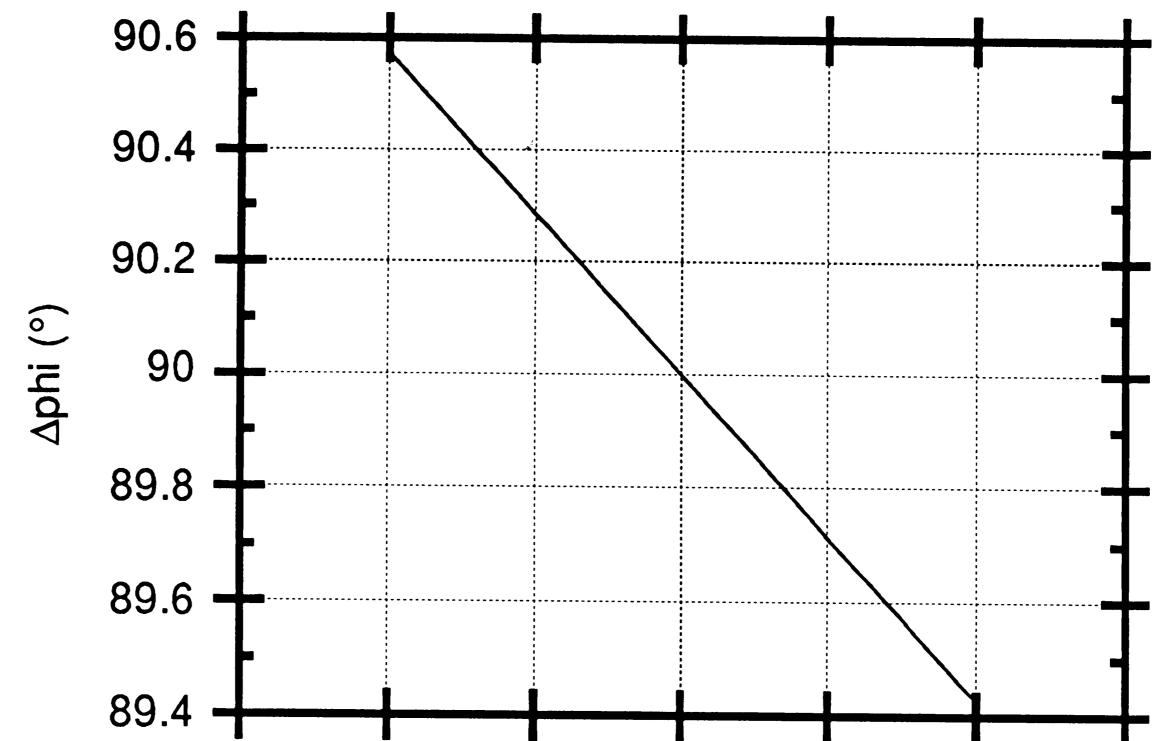

|        | Figure 5.3: Phase Shifter Phase vs. Time Constant Error               | .46 |

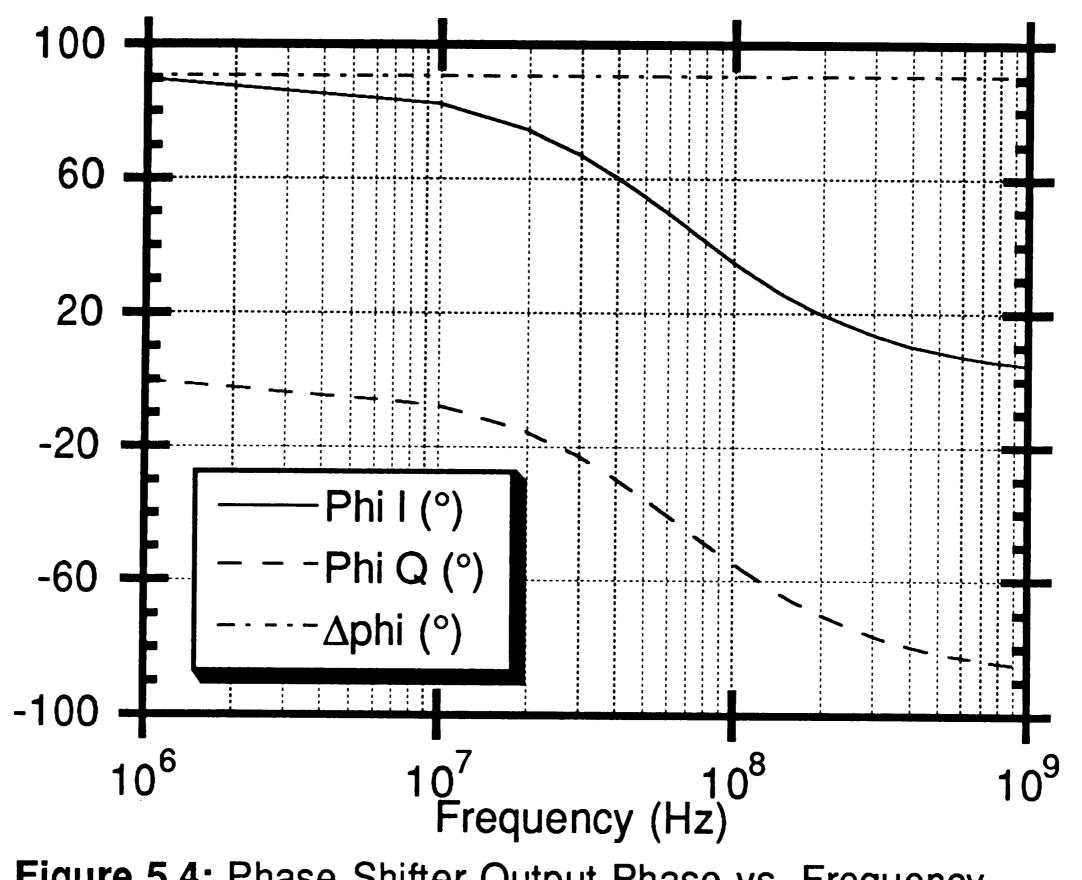

|        | Figure 5.4: Phase Shifter Output Phase vs. Frequency                  | .47 |

|        | Figure 5.5: Limiting Amplifier for Phase Shifter Circuit              | 48  |

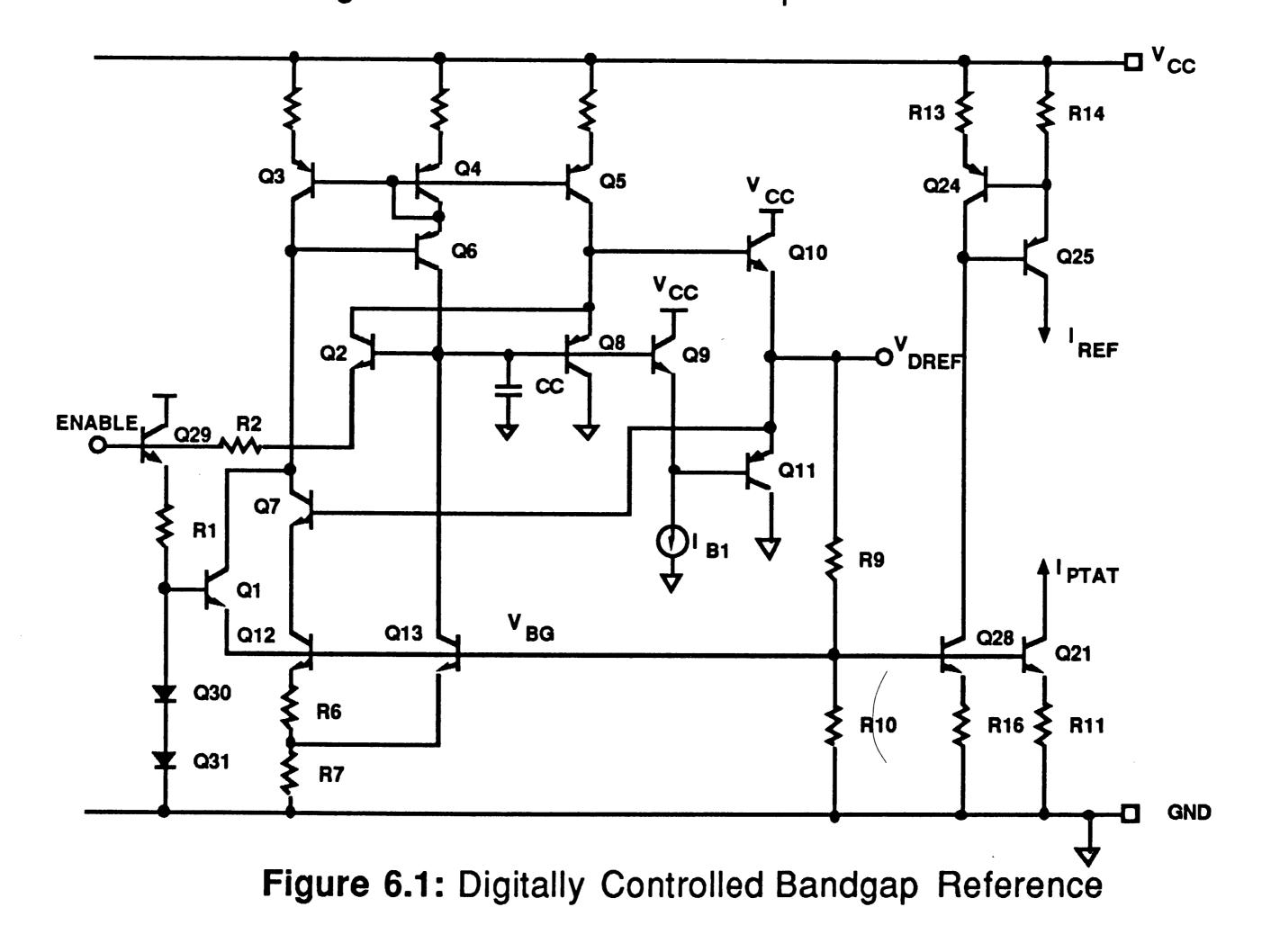

| .*     | Figure 6.1: Digitally Controlled Bandgap Reference                    | 51  |

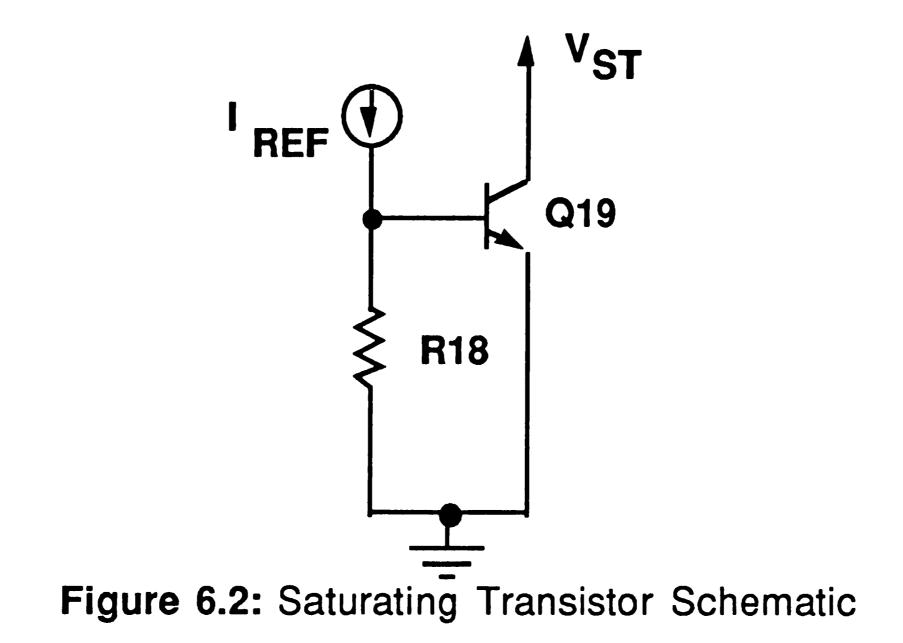

| ·<br>· | Figure 6.2: Saturating Transistor Schematic                           | .55 |

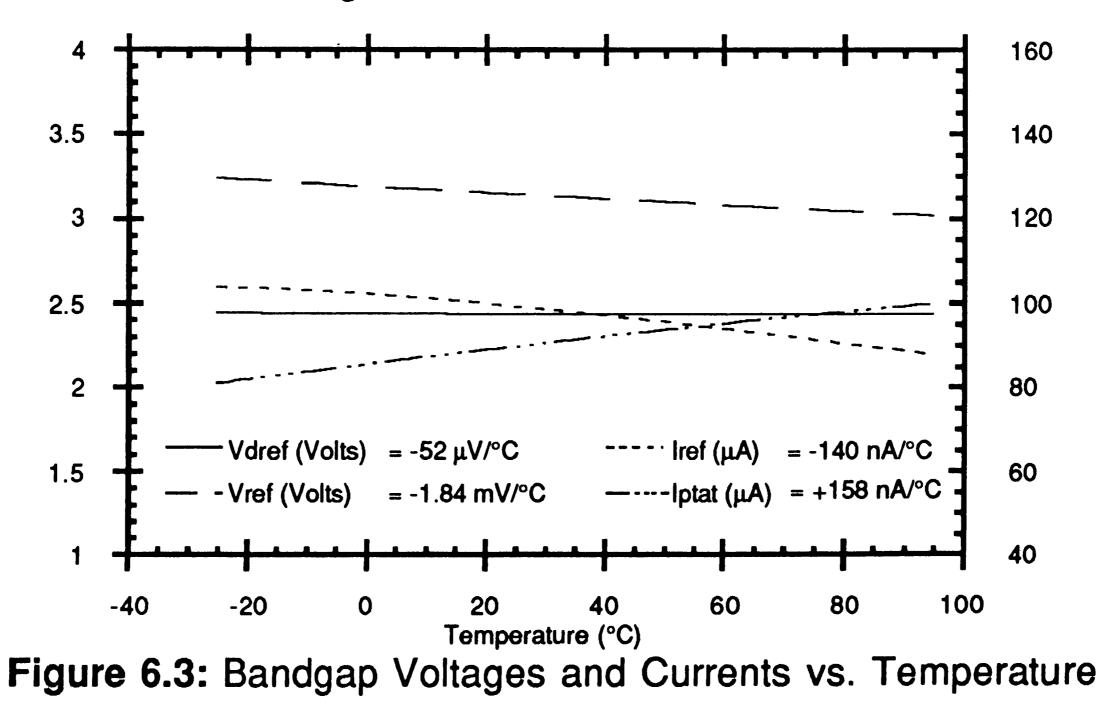

|        | Figure 6.3: Bandgap Voltages and Currents vs. Temperature             | .55 |

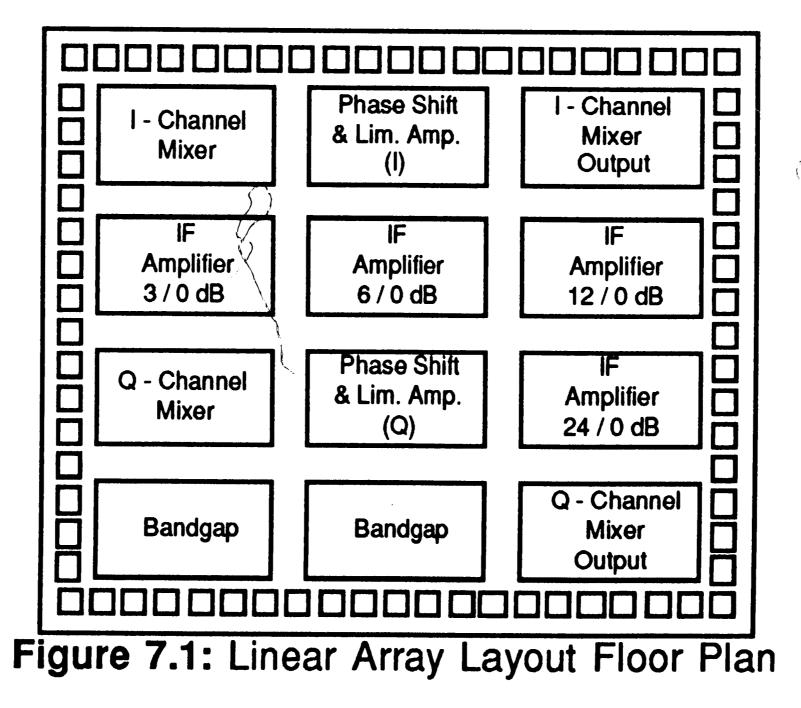

|        | Figure 7.1: Linear Array Layout Floor Plan                            | .59 |

|        | Figure 7.2: Pin Configuration                                         | .60 |

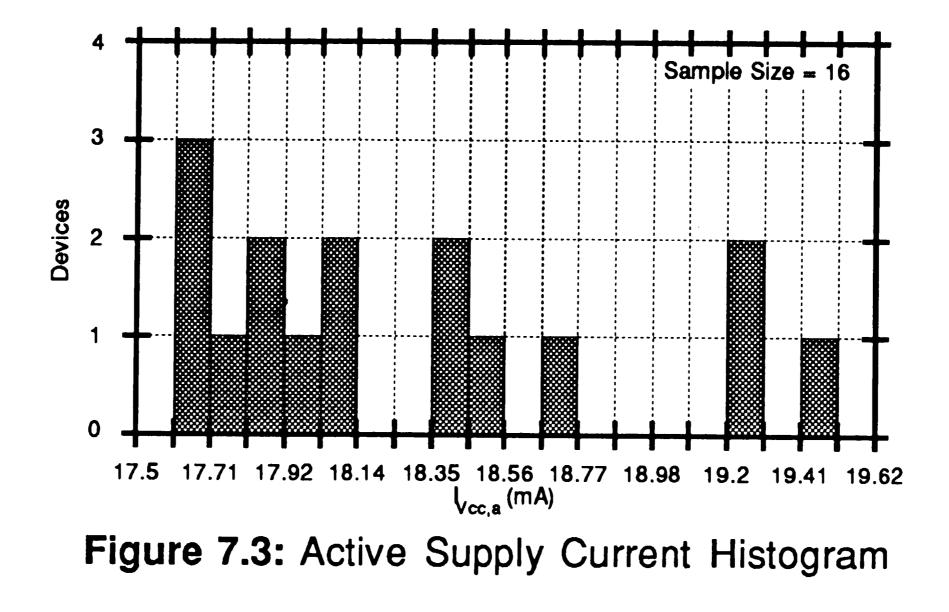

|        | Figure 7.3: Active Supply Current Histogram                           | .65 |

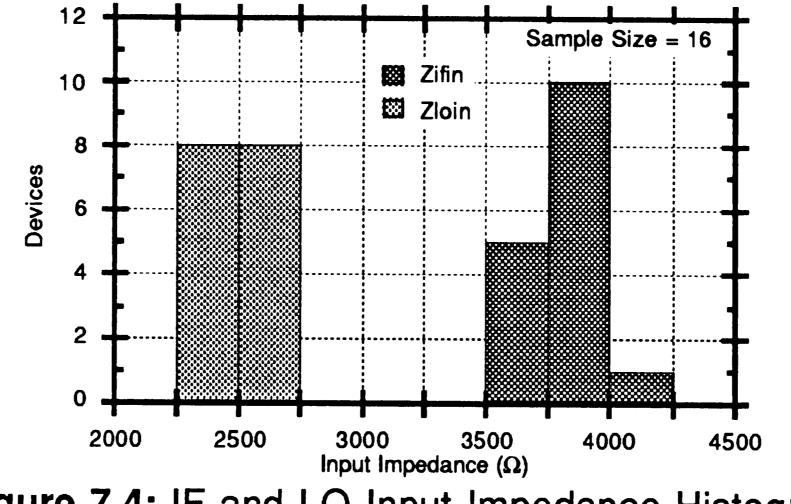

|        | Figure 7.4: IF and LO Input Impedance Histogram                       | .65 |

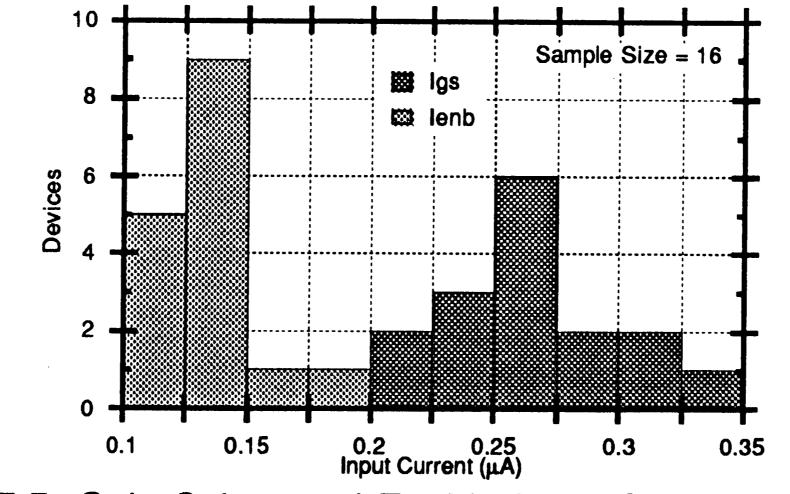

|        | Figure 7.5: Gain Select and Enable Input Current Histogram            | .65 |

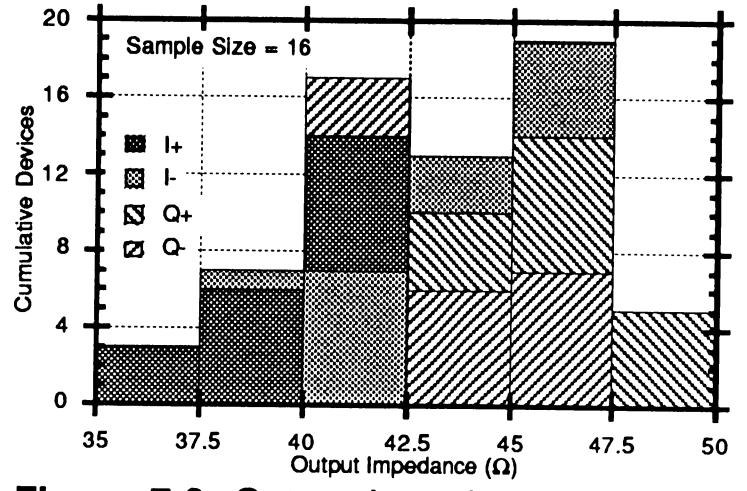

|        | Figure 7.6: Output Impedance Histogram                                | .66 |

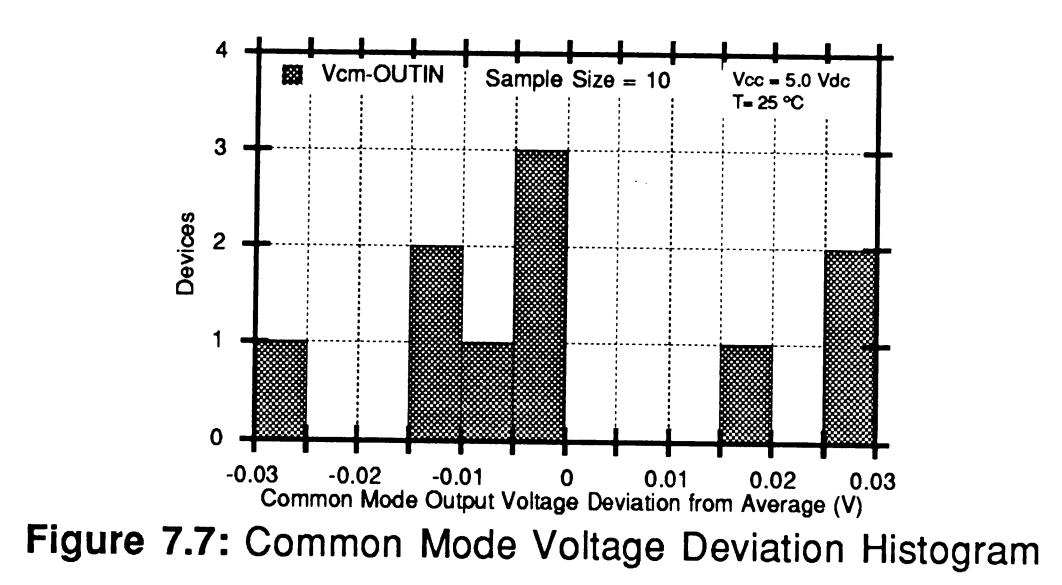

|        | Figure 7.7: Common Mode Voltage Deviation Histogram                   | .66 |

|        | Figure 7.8: RF Evaluation Board                                       |     |

|        | Figure 7.9: Measured Gain Error vs. Selected Gain                     |     |

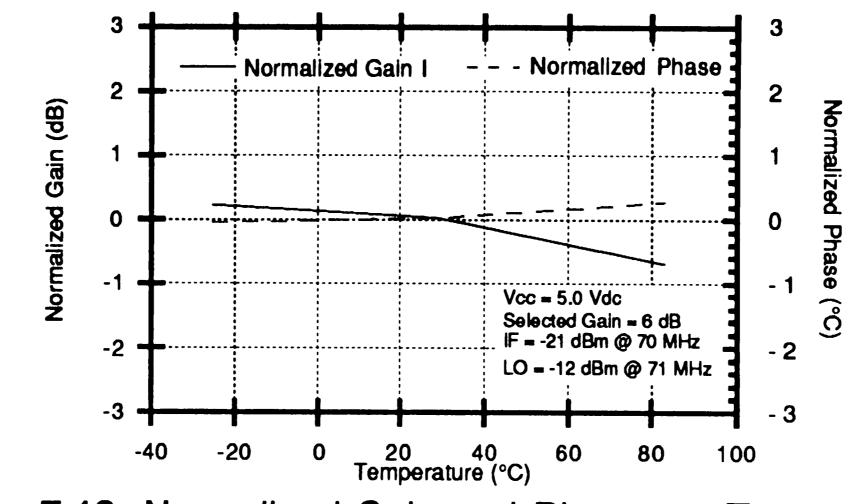

|        | Figure 7.10: Normalized Gain and Phase vs. Temperature                |     |

|        | h                                                                     |     |

#### List of Figures

/

.

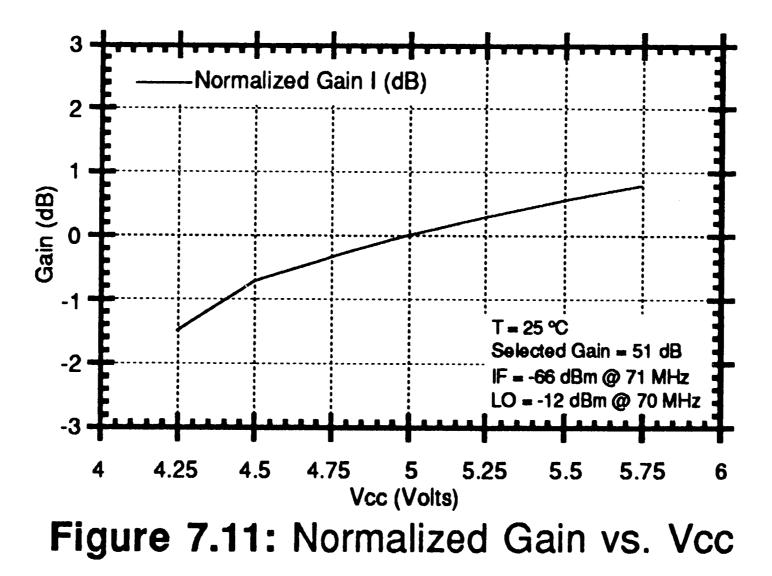

| Figure 7.11: Normalized Gain vs. Vcc                     | 69 |

|----------------------------------------------------------|----|

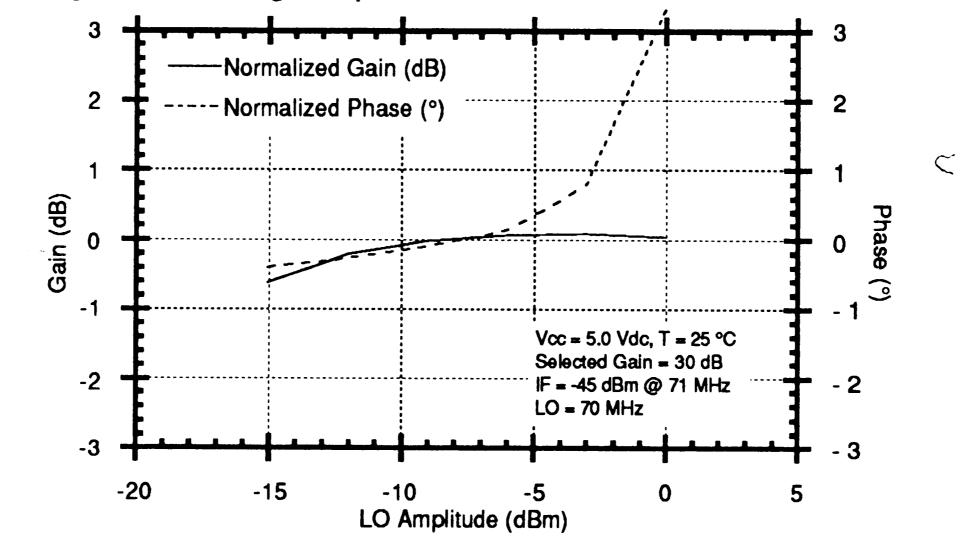

| Figure 7.12: Normalized Gain and Phase vs. LO Amplitude  | 70 |

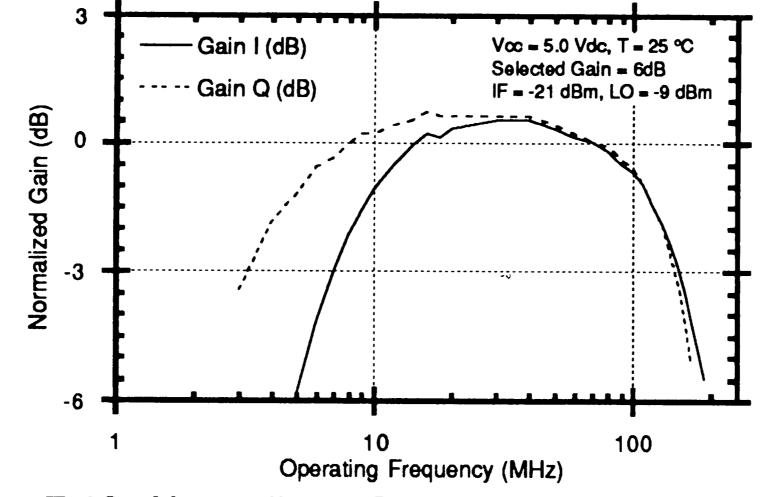

| Figure 7.13: Normalized Gain vs. Operating Frequency     | 71 |

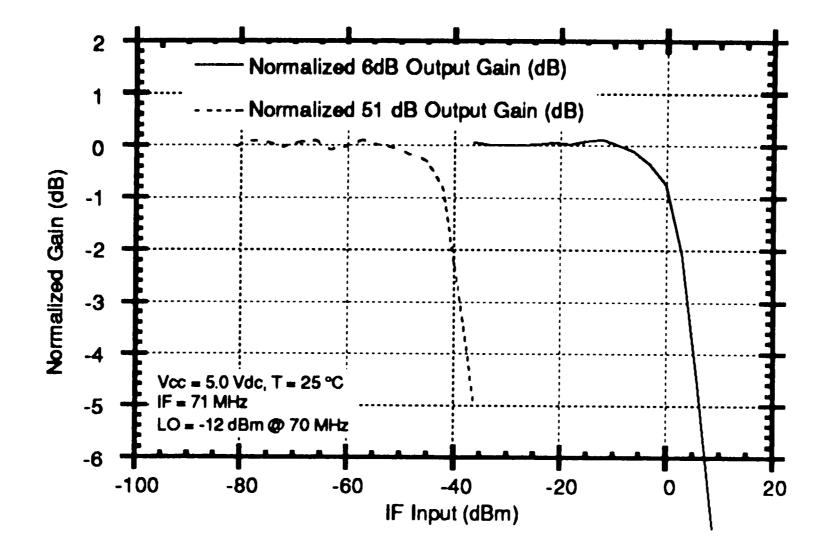

| Figure 7.14: 6 dB and 51 dB Normalized Gain vs. IF Input | 72 |

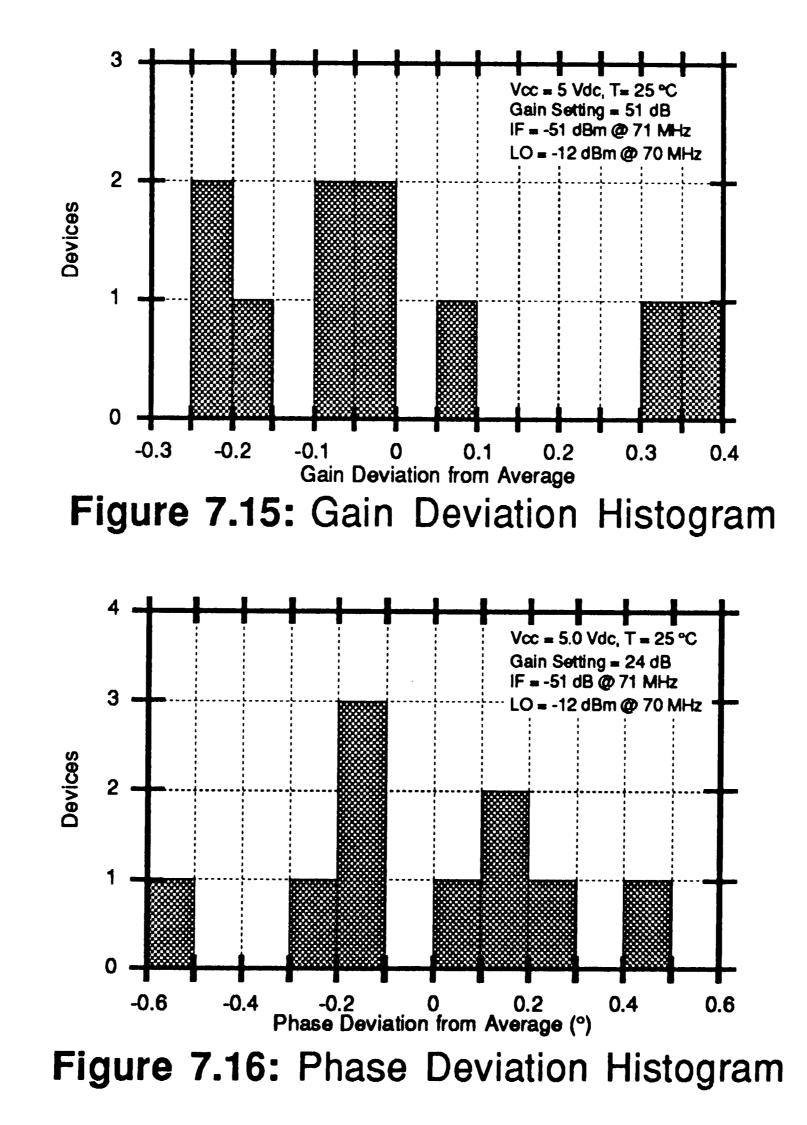

| Figure 7.15: Gain Deviation Histogram                    | 72 |

| Figure 7.16: Phase Deviation Histogram                   | 72 |

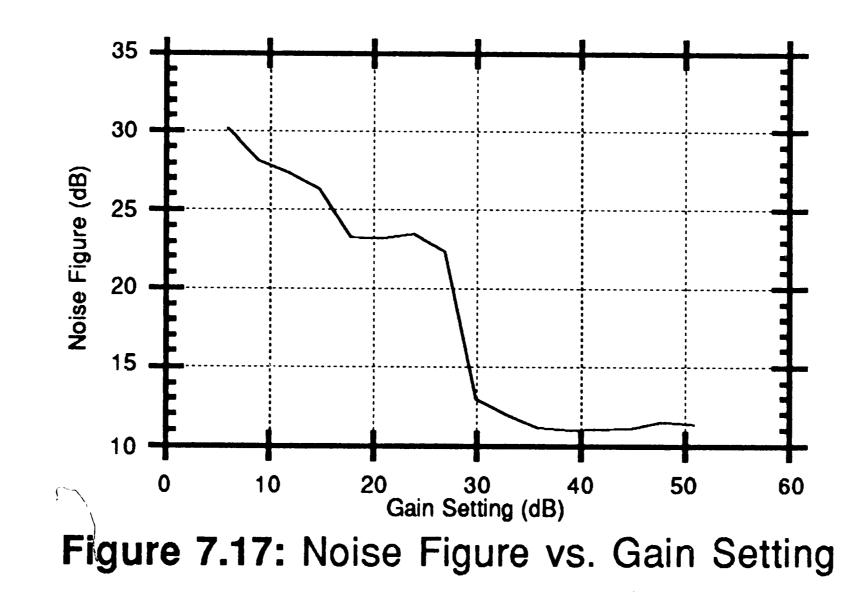

| Figure 7.17: Noise Figure vs. Gain Setting               | 73 |

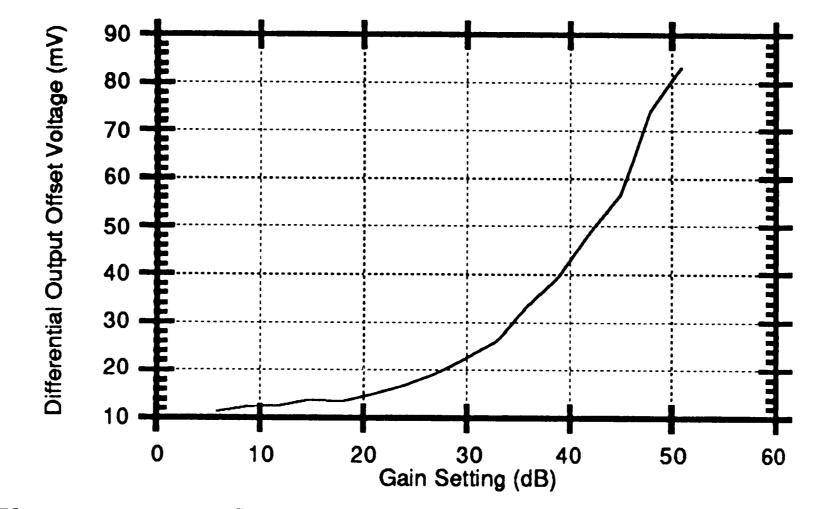

| Figure 7.18: Output Offset Voltage vs. Gain Setting      | 75 |

- ix -

#### 1. Abstract

The design of a 70 MHz Digitally Controlled Gain Amplifier and Quadrature Demodulator for the GSM European Digital Cellular System is described. This integrated circuit is used in the receive path for mobile terminals that comply with the GSM European Digital Cellular Standard.

The circuit provides digitally controlled amplification of a Gaussian-filtered Minimum Shift Keying (GMSK) modulated signal at an intermediate frequency of 70 MHz. The digitally controlled gain has a range of 0 to 45 dB as selected in 3 dB steps by four gain select signals. The gain error for any setting is less than  $\pm$ 3 dB over temperature and processing variations.

The circuit also provides GMSK demodulation by mixing two local oscillator signals that are 90° out of phase from each other with the amplified IF GMSK signal. The mixing is performed by two double balanced mixers that use Gilbert cell multipliers. The 90° out of phase local oscillator signals are

derived from an external local oscillator of frequency equal to the IF frequency. An RC phase shifter with limiting amplifiers provides two 90° out of phase square wave outputs to drive the In-phase and Quadrature mixers.

A digitally controlled bandgap provides stable reference voltages and currents. The bandgap has a sleep mode that is enabled by a TTL compatible input. In the sleep mode, the entire circuit is turned off and draws less than 50  $\mu$ A of supply current.

The integrated circuit is fabricated in AT&T's High Frequency Complementary Bipolar Integrated Circuit (CBIC-U) process on the ALA202 linear array. This 100 mW circuit requires a single +5 Volt power supply and has a chip area of 12.2 mm<sup>2</sup>. The circuit is packaged in a 16 pin Small Outline Gull Wing (SOG) package and has 13 active pins.

The manufactured circuit has been tested for DC, gain and phase, noise, and switching speed characteristics. An analysis of the measured characteristics is presented. In addition, improvements are suggested and conclusions about the design and its performance are made.

#### 2. Introduction

May 1

The Groupe Speciale Mobile (GSM) Digital Cellular Telephone System is a standard that has been developed for use by member countries of the European Economic Community as a common standard for digital cellular communications throughout Europe. The standard defines a system that will use Gaussian-filtered Minimum Shift Keying (GMSK) as a means of modulating the radio frequency (RF) signal that is transmitted and received between mobile terminals and base stations that are connected to the public telephone network.

This work presents the design and experimental results of an integrated circuit for mobile terminals that will amplify and demodulate a received GMSK signal that has been down-converted to an intermediate frequency (IF) of 70 MHz.

#### 2.1 The GSM Digital Cellular Telephone System

The GSM Digital Cellular System uses RF transmit and receive frequencies in the 900 MHz to 1 GHz range [1]. The RF signal is modulated with 124 GMSK channels each separated by 200 kHz [1] within the RF band. In a mobile terminal, an RF circuit is used to down-convert one of the 124 channels that is received in the 935 MHz to 960 MHz [1] mobile receive band to an IF frequency of 70 MHz. The circuit described provides amplification and demodulation of the 70 MHz GMSK modulated IF signal. The demodulated signal is then filtered and processed by an external circuit so as to provide a data stream to a series of digital signal processors, microprocessors, and digital to analog converters.

A "ping-pong" receive/transmit approach for each multi-channel station is used, whereby the receiver and transmitter are alternately switched on for short bursts. The burst-mode operation presupposes a new approach to AGC which requires digital gain control. In a conventional radio system, the desired analog control voltage is stored on a capacitor. In GSM, it is stored in memory by a microprocessor so the receiver may start each burst of a series at the correct gain level. The gain is changed between bursts to avoid

the "clicks" of digital AGC. As required by the GSM system, digital control provides the ability to measure the absolute level of the received RF signal. The accuracy is limited by the tolerance of the gain, which is allocated to be  $\pm 3$  dB for the IF amplifier/demodulator portion of the receiver path [2]. A hybrid analog / digital AGC may also be used as a gain control [12], but this approach requires the use of costly analog-to-digital converters so that the microprocessor may obtain data concerning the input signal level.

· •

#### 2.2 GSM Requirements for the IF Amplifier and Demodulator

The GSM system requirements together with the requirements of several mobile terminal manufacturers were used to determine some specifications and design constraints for the IF amplifier and demodulator. The following sections describe these issues with respect to the design.

#### 2.2.1 Power Level Detection

The GSM specification requires that the received RF signal power level should be known to the microprocessors [3]. The method of power level detection is not described in the system requirements and is subject to the discretion of the mobile terminal manufacturer. The method that is used, when the circuit described is utilized in the signal path, is digital gain control. By maintaining a constant output level after demodulation by microprocessor control, the RF input level may be calculated by the microprocessor by software control. This is done by programming the microprocessor with the specified power level gains and losses through all stages that precede demodulation except for the digitally controlled IF amplifier. The input level may then be calculated output power level, and the microprocessor controlled IF amplifier gain that is required to maintain the desired output power level.

#### 2.2.2 Required Gain

The digitally controlled gain IF amplifier has a required maximum gain of 45 dB and a required minimum gain of 0 dB. The GMSK demodulator stage has a 6 dB conversion gain requirement. Through both the IF amplifier and the

GMSK demodulator, the total conversion gain error must be less than  $\pm 3 \text{ dB}$  from the defined total conversion gain of 51 dB [3].

#### 2.2.3 Noise Figure Requirements

The noise figure of the circuit must be as low as possible since this circuit is intended to amplify relatively low level signals that are only minimally amplified in the RF to IF down conversion stage. Since the circuit has a range of gain levels, the highest level of gain requires the lowest noise figure, while the lowest level of gain only does not require as low a noise figure. The design goal for this circuit is to have a noise figure of less than 10 dB for its highest gain setting and a maximum noise figure of 30 dB for the lowest gain setting.

#### 2.2.4 Power Consumption

Since the described circuit is intended for use in a mobile terminal, the total

power consumption must be kept as low as possible. This is to avoid an excessive power drain on the battery powered mobile terminals. A goal of less than 100 mW is desired with a nominal single supply voltage of +5 Volts. In addition, during the mobile transmit cycle of communication with the base station, the receive path must be able to be turned off by digital control. When the receive path is turned off, this is known as the sleep mode. The circuit described must be capable of drawing less than 50  $\mu$ A during the sleep mode and the settling time when switching between modes should be less than 25  $\mu$ s.

#### 2.2.5 Input and Output Definition

The input to the IF amplifiers should be single-ended with an input impedance of greater than 300  $\Omega$ . The local oscillator (LO) input to the GMSK demodulator should also be single-ended with an input impedance of greater than 300  $\Omega$ .

Following the GMSK demodulation, the circuit should have In-phase (I) and Quadrature (Q) differential outputs. Each output should have a single ended

output impedance of 50  $\Omega$  or less and be capable of a baseband frequency range of DC to 1 MHz. Also, the output stage must be capable of driving a 1 Vpp differential signal with a 1 k $\Omega$  resistive load in parallel with a 30 pF capacitive load on each output.

#### 2.2.6 GMSK Demodulator Requirements

GMSK demodulation is implemented by mixing the IF signal from the IF amplifier with two local oscillator (LO) signals that are equal in frequency to the IF signal, but phase shifted 90° with respect to each other. The local oscillator should be such that a +45° phase shifted LO signal is mixed with the IF signal in the I channel mixer and a -45° phase shifted LO signal is mixed with the IF signal in the Q channel mixer. The phase shifter requires an error of  $\pm 3^\circ$  with respect to the 90° I and Q phase shift requirement.

#### 2.2.7 Temperature and Supply Requirements

The IF amplifier and demodulator should meet all specifications for an ambient temperature range of -25 °C to +85 °C with a positive supply voltage range of +4.75 Volts to +5.25 Volts.

#### 2.3 Circuit Implementation

----~

Considering the requirements of section 2.2, AT&T's High Frequency Complementary Bipolar Integrated Circuit technology (CBIC-U) is suitable for the implementation of the circuit. The CBIC-U technology has an NPN transistor  $f_T$  of 4.0 GHz and a PNP transistor  $f_T$  of 2.5 GHz. The AT&T ALA202 linear array was used to fabricate the circuit. This enables a fast design turn around time with minimal cost of manufacture. With a design at this frequency, some gain penalties are paid due to increased layout parasitics in the array, but they may be accounted for in the design of the gain stages.

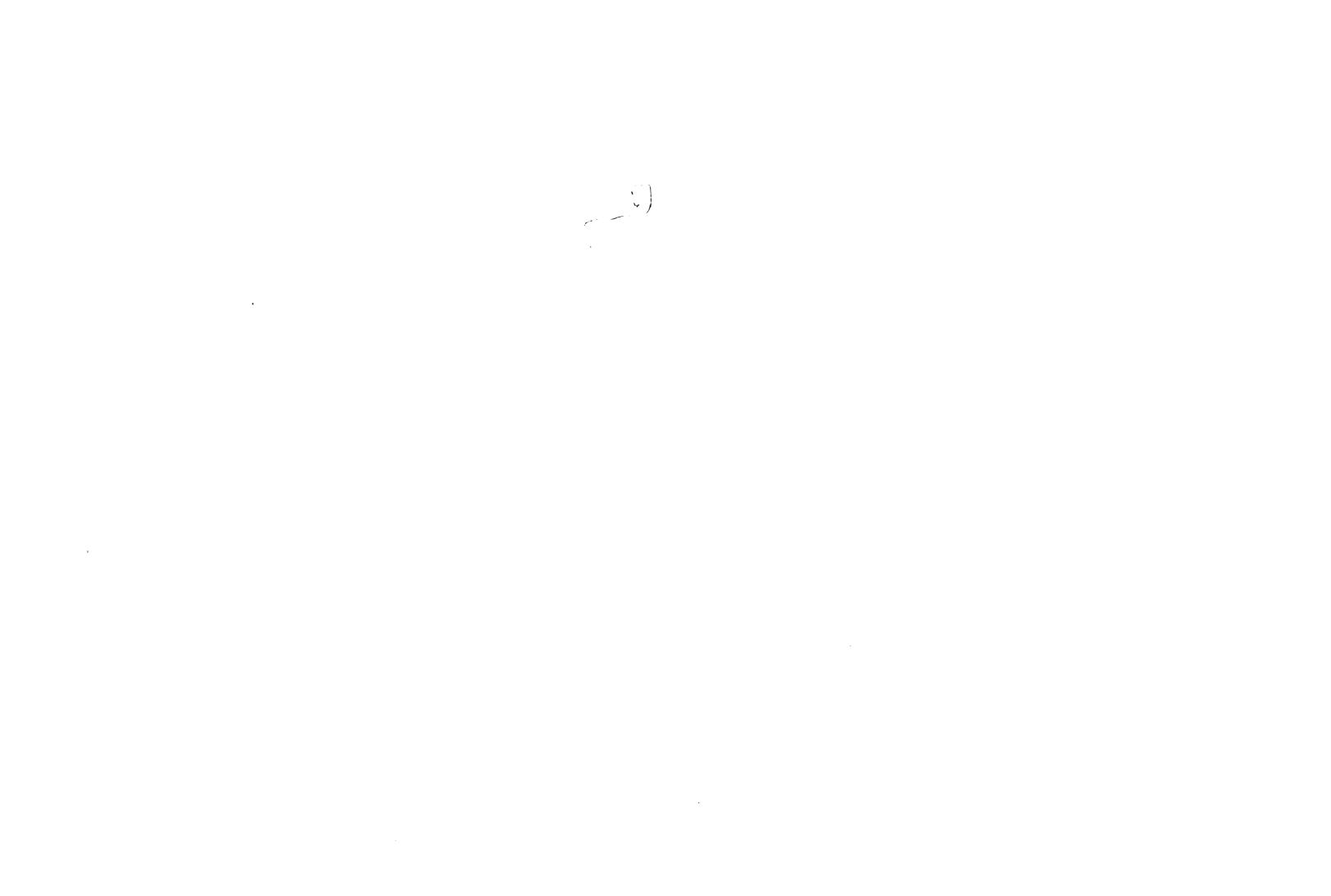

The circuit's block diagram is shown in figure 2.1. Note that the digitally controlled amplifier provides the desired 0 - 45 dB gain is 3 dB steps while the I and Q mixers with the phase shifter provide the GMSK demodulation.

7

Figure 2.1: IF Amplifier and Demodulator Block Diagram

#### 2.4 IF Amplifier Definition

The IF amplifier subcircuit is comprised of multiple digitally controlled gain amplifiers. To obtain the required 45 dB of gain switchable in 3 dB steps, the amplifiers are partitioned such that the gain steps may be selected with a N-bit binary word. To obtain a 3 dB resolution of gain steps over the range of 0 dB to 45 dB, N = 16 gain steps are needed. Therefore, four binary Gain Select control signals are required. The gain select truth table, shown in

Table 2.1, shows the bit patterns that should be applied to the four Gain Select inputs to obtain the corresponding gain through the IF amplifier subcircuit. It is evident from Table 2.1 that the four amplifiers should be selected to provide switchable gains of 24 dB / 0 dB, 12 dB /0 dB, 6 dB / 0 dB, and 3 dB / 0 dB.

The selection of the circuit topology for the digitally controlled gain amplifiers is dictated by three main considerations. First, the total gain error through the chain of amplifiers and through the mixer stages must be less than  $\pm 3$  dB regardless of the selected gain. Second, the number of available transistors for each amplifier must be kept to a minimum. This is required because the circuit is to be built on a linear array that has a limited number of transistors and resistors available. The last consideration is to minimize the allocated current consumption for the IF amplifier.

$\langle \downarrow \rangle$

| GS1 GS2 GS3 GS4 Gain |   |   |   |       |  |

|----------------------|---|---|---|-------|--|

| Н                    | Η | Η | Η | 0 dB  |  |

| Н                    | Η | Η | L | 3 dB  |  |

| Н                    | Η | L | Η | 6 dB  |  |

| Н                    | Η | L | L | 9 dB  |  |

| Η                    | L | H | Η | 12 dB |  |

| Н                    | L | Н | L | 15 dB |  |

| Н                    | L | L | H | 18 dB |  |

| Н                    | L | L | L | 21 dB |  |

| L                    | Η | Η | H | 24 dB |  |

| L                    | Η | Η | L | 27 dB |  |

| L                    | Н | L | H | 30 dB |  |

| L                    | Н | L | L | 33 dB |  |

| L                    | L | Н | Η | 36 dB |  |

| L                    | L | Η | L | 39 dB |  |

| L                    | L | L | Η | 42 dB |  |

| L                    | L | L | L | 45 dB |  |

| Table 2.1: Gain      |   |   |   |       |  |

Select Truth Table

#### 2.4.1 Gain Error Allocation

The gain error specification may be defined by allocating a fraction of the gain error to each of the gain stages. The simplest allocation is to divide the total required gain error by the number of stages in the signal path. Therefore, with a total required gain error of  $\pm 3$  dB through four gain stages and a mixer, the gain error for each stage is allocated to be  $\pm 0.6$  dB.

#### 2.4.2 Linear Array Limitations

The AT&T ALA202 linear array consists of 9 "standard" tiles, 2 "power" tiles, and 1 "input" tile each containing a number of NPNs, PNPs, and resistors. Table 2.2 shows the component totals per tile for the ALA202 [4].

| Component   | Туре                                  | Standard | Input | Power |

|-------------|---------------------------------------|----------|-------|-------|

| Transistors | · · · · · · · · · · · · · · · · · · · |          |       |       |

| NPN         | 1/3X                                  | -        | 2     | -     |

| NPN               | 1X      | 9  | 7  | 2  |

|-------------------|---------|----|----|----|

| NPN               | 2X      | 2  | 2  | 2  |

| NPN               | 5X      | 1  | 1  | 2  |

| NPN               | 15X     | -  | -  | 2  |

| PNP               | 1/3X    | -  | 2  | -  |

| PNP               | 1X      | 5  | 3  | 2  |

| PNP               | 2X      | 2  | 2  | 2  |

| PNP               | 5X      | -  | -  | 2  |

| PNP               | 15X     | -  | -  | 2  |

| 50 Ω/sq Resistors | 50 Ω    | 8  | 8  | -  |

|                   | 100 Ω   | 40 | 40 | 40 |

|                   | 200 Ω   | 8  | 8  | -  |

| 1 kΩ/sq Resistors | 1 kΩ    | 4  | 4  | -  |

|                   | 2 kΩ    | 20 | 20 | 20 |

|                   | 4 kΩ    | 4  | 4  | -  |

| Capacitors        | 0.75 to | 1  | 1  | -  |

| -                 | 3.35 pF |    |    |    |

|                   | 1.0 pF  | 2  | 2  | -  |

Table 2.2: AT&T ALA202 Linear Array Component Totals

The design of each gain stage in the IF amplifier should be constrained to the components available to a single "standard" tile so as to minimize interconnect capacitance within each amplifier and for ease of layout, since

each amplifier will have similar topologies. The detailed design of the IF amplifier and each of its stages will be discussed in section 3.

# 2.5 Double Balanced Mixer and Output Stage Subcircuit Definition

The I and Q Double Balanced Mixers of the GMSK demodulation stage is required to have a conversion gain of 6 dB with a gain error of  $\pm 0.6$  dB. In addition, the mixers should be capable of handling a 0.5 Vpp differential input and providing a 1 Vpp output without distortion. The output must have a 50  $\Omega$  output impedance and be able to drive a 1 k $\Omega$  load in parallel with 30 pF.

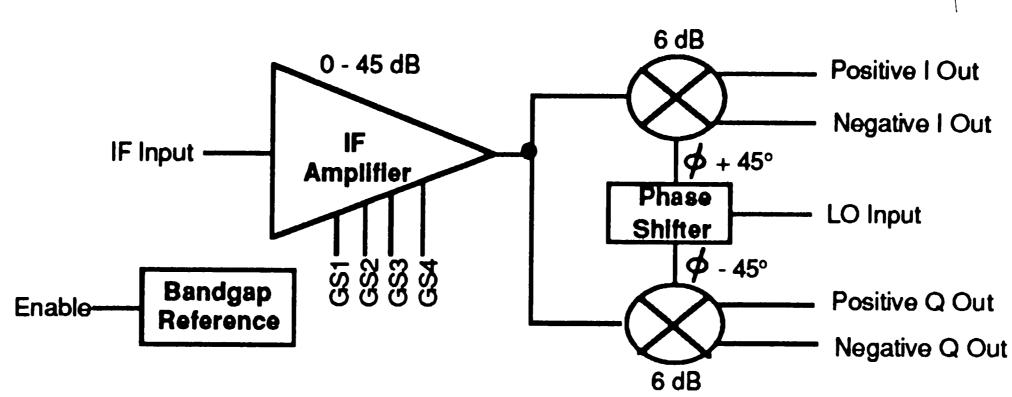

A Gilbert cell multiplier is well suited to the implementation of the demodulation and gain requirements of the GMSK demodulator since it provides for phase detection through alternate +1 and -1 switching. In addition, a push-pull output stage is also suitable to meet the load and output impedance requirements that have been stated. Figure 2.2 shows the block diagram of the mixer and output stages. In section 4, the mixer and output circuits will be discussed in more detail.

#### 2.6 Quadrature Phase Shifter Subcircuit Definition

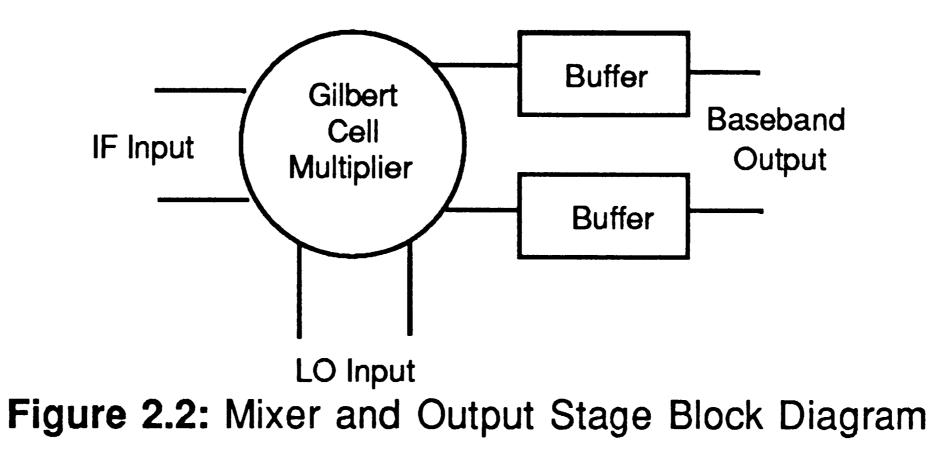

The quadrature phase shifter, as part of the GMSK demodulator, is required to provide two 70 MHz local oscillator signals to the I and Q mixers, each of which are to be  $90^{\circ}\pm3^{\circ}$  apart in phase. Given an externally provided LO signal, the circuit should provide the two signals such that they are phase shifted  $\pm45^{\circ}$  and  $\pm45^{\circ}$  from the external 70 MHz LO signal. To assure a

minimum mixer output gain error between channels, the outputs should be large enough so as to fully switch each of the mixer's LO inputs. Also, the minimum LO input level to the phase shifter should be approximately 100 mVpp. The block diagram of figure 2.3 shows the configuration needed to provide the desired phase shift while insuring full switching of the mixers.

The buffer provides the desired input impedance, while the RC network provides the two +45° and -45° phase shifter outputs. The RC network drives

two limiting amplifiers that provide two equal, but 90° out of phase, square wave outputs to the I and Q mixers. Section 5 will present the design of the quadrature phase shifter.

# 2.7 Digitally Controlled Bandgap Reference Subcircuit Definition.

The digitally controlled bandgap must be able to provide stable voltage references so as to set up current mirrors and reference levels throughout the circuit. In addition, the bandgap must have the capability to be turned off by digital control such that all subcircuits that are drawing current will be turned off. Section 6 will discuss the design of the digitally controlled bandgap and the current mirrors it sets up.

#### 3. Digitally Controlled Gain IF Amplifier

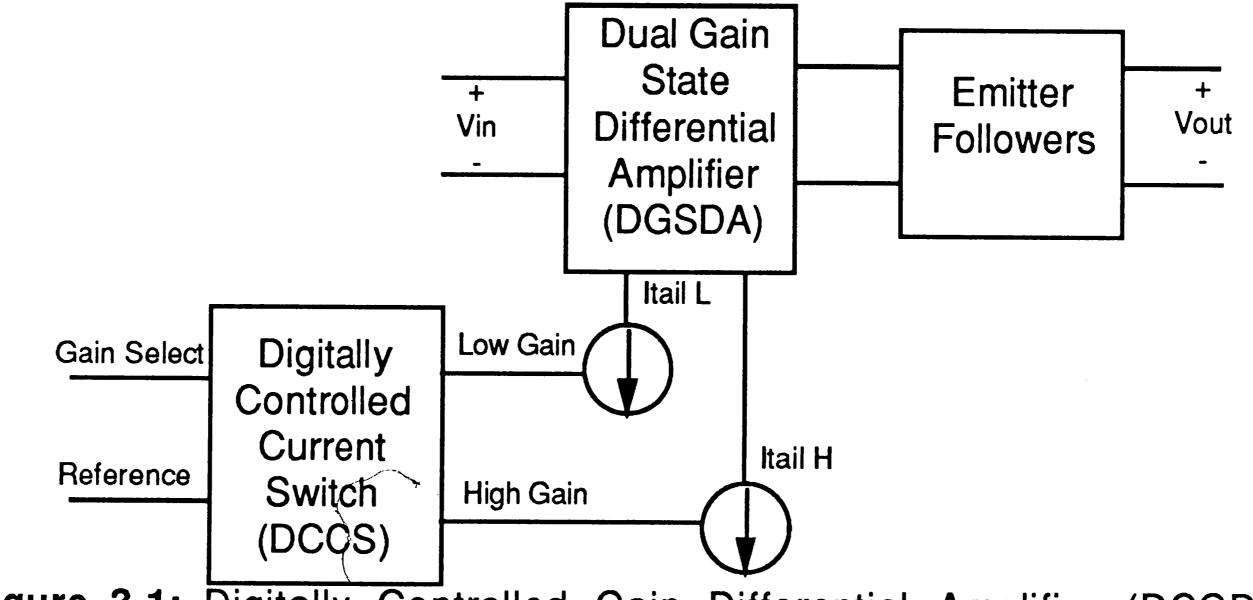

The Digitally Controlled Gain IF Amplifier consists of four Digitally Controlled Gain Differential Amplifiers (DCGDA). Each DCGDA has three distinct sections. First, two levels of amplification are provided by a Dual Gain State Differential Amplifier (DGSDA) whose gain is dependent upon the selection of tail current sources. Second, the selection of tail current sources is controlled by a Digitally Controlled Current Switch (DCCS). Lastly, the differential amplifier is buffered by a pair of emitter followers. Figure 3.1 shows a block diagram of the DCGDA subcircuit.

ß

Figure 3.1: Digitally Controlled Gain Differential Amplifier (DCGDA) Subcircuit

The following sections describe the operation and design of the previously described subcircuits. In addition, issues such as gain error due to temperature and processing variations will also be discussed. Also, an example calculation for the important parameters of s DCGDA subcircuit will be presented. The chapter will conclude with a comparison of the calculated and simulated gains and gain errors.

#### 3.1 Dual Gain State Differential Amplifier (DGSDA) Design

The Dual Gain State Differential Amplifier is, in effect, an emitter-coupled pair with emitter degeneration. This type of differential amplifier has a

voltage gain that is determined roughly by the formula [5] as found in equation 3.1.

ν

$$A_v = \frac{R_c}{\frac{1}{g_m} + R_e}$$

(Eq. 3.1)

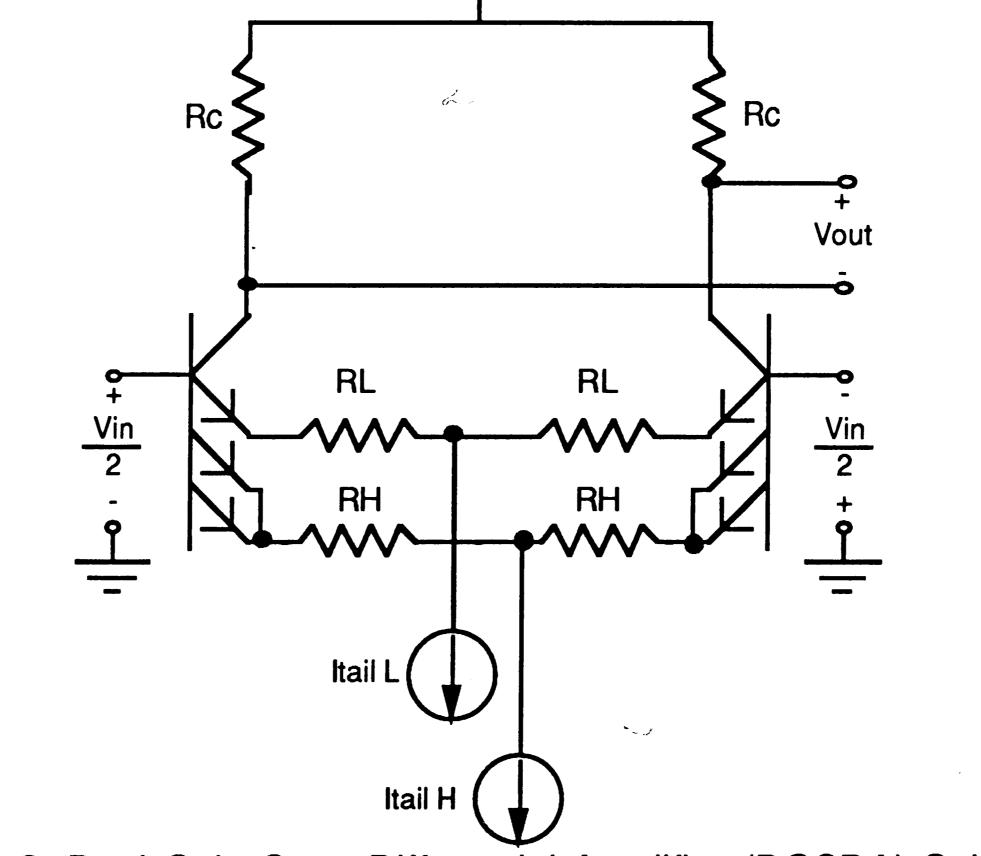

To facilitate the required selection of two separate voltage gains in the DGSDA,  $R_e$  may be changed while  $\frac{1}{g_m}$  and  $R_c$  is held constant. This is accomplished by splitting the emitters of the input transistors in the emitter-coupled pair and connecting two sets of emitter degeneration resistors to the split emitters. Switching between the two sets of  $R_e$  may be achieved by selecting either  $I_{tail L}$  or  $I_{tail H}$ , each of which drive separate sets of emitter resistors. The Digitally Controlled Current Switch, to be described in section 3.2, performs the selection. The DGSDA is shown in figure 3.2.

Figure 3.2: Dual Gain State Differential Amplifier (DGSDA) Subcircuit

In the DGSDA configuration, the differential amplifier acts as two separate emitter coupled pairs with a common collector, a common base, and a common load between them. A benefit of the common collector and common

load is the sharing of collector to substrate capacitance, layout parasitics, and resistor parasitic capacitance. This causes the overall capacitance to be lower at the collector. Therefore, the gain will roll off at a higher frequency due to a lower RC time constant. In addition, the sharing of transistors eliminates two devices from the transistor count. This is an important consideration when designing with a linear array.

1

### 3.1.1 Calculation of Gain, Input Impedance, and Output Impedance

Since the DGSDA may be considered as two separate emitter coupled pairs with emitter degeneration, the design equations may be found based on this property. The following will show how the design equations that primarily effect the performance of the circuit were found. They are the high frequency small-signal gain, the input impedance, and the output impedance.

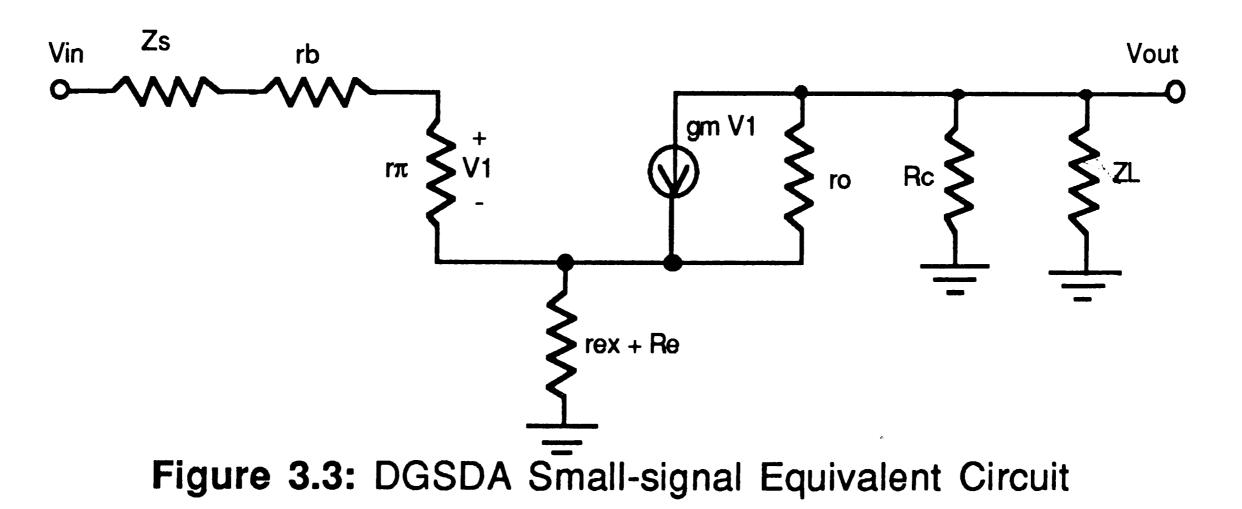

The small-signal gain equation as used in Eq. 3.1 is appropriate for low frequency and low gain differential amplifier designs. Since this design is intended to operate at an IF frequency of 70 MHz and the highest gain setting for a DGSDA is 24 dB, a more detailed gain equation should be used. Using the half-circuit concept [5, 6] to determine the gain, input impedance, and output impedance of an emitter-coupled pair with emitter degeneration, the small-signal equivalent circuit of figure 3.3 may be used.

The small-signal equivalent circuit of figure 3.3 includes the source impedance,  $Z_s$ , as seen across one input of the emitter-coupled pair and the load impedance,  $Z_L$ , on each DGSDA output. The load impedance includes

the layout parasitic capacitance, the collector-to-base capacitance of the emitter follower, and the  $R_c$  resistor parasitic capacitance.

÷

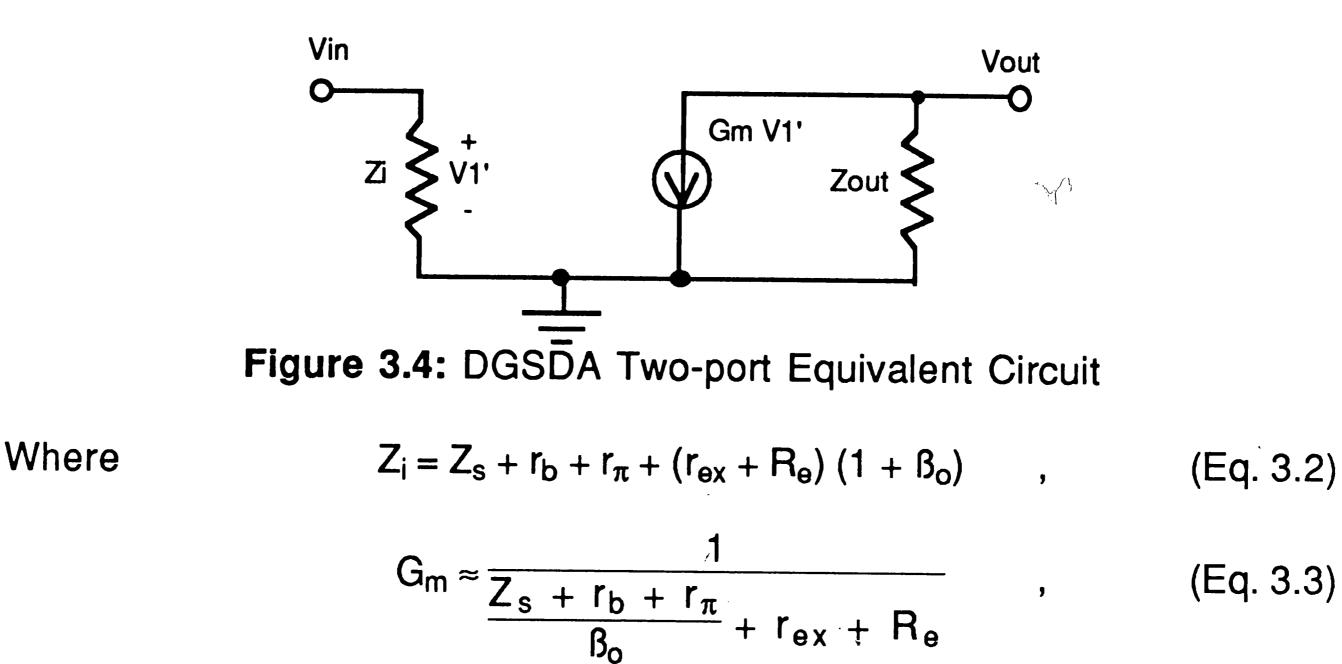

To simplify the design, a two-port equivalent circuit [6] may be found such as that shown in figure 3.4.

and

$$Z_{out} = R_c || Z_L || r_o(g_m R_e + 1)$$

(Eq. 3.4)

Since each DCGDA is preceded by a low source impedance, then  $Z_s$  may be neglected in equations 3.2 and 3.3. Also,  $r_b$  may be neglected since it is usually very small. Therefore, Equations 3.2 and 3.3 may be re-written as shown in equations 3.5 and 3.6, respectively.

and

$$Z_{i} \approx r_{\pi} + (r_{ex} + R_{e})\beta_{o} \qquad (Eq. 3.5)$$

$$G_{m} \approx \frac{1}{\frac{1}{g_{m}} + r_{ex} + R_{e}} \qquad (Eq. 3.6)$$

Furthermore, since  $r_o(g_m R_e + 1)$  should be very large, then equation 3.4 may be approximated as shown in equation 3.7

$$Z_{out} \approx R_c \parallel Z_L \tag{Eq. 3.7}$$

where  $Z_L$  includes  $C_{cs}$ ,  $C_{layout}$ ,  $C_{Rc}$ , and  $C_{\mu ef}$ .

Using the two-port equivalent circuit of figure 3.4, the differential input impedance [5] may be found directly from equation 3.8,

$$Z_{in} = 2 Z_i \approx 2 [r_{\pi} + (r_{ex} + R_e) \beta_o]$$

(Eq. 3.8)

and the voltage gain may be found by equation 3.9.

$$A_{v} = G_{m} Z_{out} \approx \frac{R_{c} \parallel Z_{L}}{\frac{1}{g_{m}} + r_{ex} + R_{e}}$$

(Eq. 3.9)

It is now evident that the gain, as determined by Equation 3.9, differs from Equation 3.1 by the addition of the parasitic capacitances of  $Z_L$ . This becomes significant at the 70 MHz frequency of operation.

#### 3.1.2 Determination of Component Values and Tail Currents

To obtain a design for the DGSDA, the desired voltage gain (Eq. 3.9), the gain error requirement, and the output swing requirement may be used to find the desired values of R<sub>c</sub>, R<sub>e</sub>, and I<sub>tail</sub>. This is accomplished by also keeping in mind the effects of the load capacitance, CL, and the resistor tolerance,  $\mathcal{E}_{R}$ .

A portion of the gain error budget should be allocated so as to account for the gain rolloff error due to the R<sub>c</sub>C<sub>L</sub> time constant. Since the pole of the differential amplifier's transfer function is found at fopRcCL, then the gain rolloff error may be found by equation 3.10.

$$\varepsilon_{AV_T} = 20 \log \sqrt{(f_{op}R_cC_L)^2 + 1}$$

(Eq. 3.10)

The loading capacitance,  $C_L$ , consists of the collector to substrate capacitance (C<sub>cs</sub>), the collector to base capacitance of the emitter follower  $(C_{\mu ef})$ , the estimated layout capacitance  $(C_{layout})$ , and the  $R_c$  resistor parasitic capacitance (C<sub>Rc</sub>).

Using a rearranged equation 3.10, a nominal value for the collector resistor,  $R_c$ , may be found as shown in equation 3.11. The resistor tolerance,  $\mathcal{E}_R$  is used so as to insure that the maximum  $R_c$  will not cause the gain rolloff error to exceed its desired value.

$$R_{c} = \frac{\sqrt{\frac{\epsilon_{AV_{T}}}{10 - 1}}}{2\pi f_{op} C_{L}(1 + \epsilon_{R})}$$

(Eq. 3.11)

To obtain the required output voltage swing, the value for  $I_{tail}$  may be found by using equation 3.12.

$$I_{\text{tail}} = \frac{V_{\text{OUTmax p-p}}}{(R_c)(1 + \mathcal{E}_R)}$$

(Eq. 3.12)

Now, the gain setting resistor  $R_{e}$  may be found by rearranging equation 3.9 to that as shown in equation 3.13.

$$R_{e} = \frac{R_{c} \parallel Z_{L}}{A_{v}} - r_{ex} - \frac{1}{g_{m}}$$

(Eq. 3.13)

The output and input impedances may then be calculated by using equations 3.7 and 3.8, respectively.

#### 3.1.3 Errors Due to Temperature and Process Variations

Another important characteristic of the IF amplifier is it's requirement to maintain a relatively stable gain over variations of temperature and process parameters. Therefore, the following will address these issues as they effect the basic design equations.

To reduce temperature effects on the gain of the DGSDA, the tail currents should be proportional to temperature. This is evident when examining the approximate gain equation (Eq. 3.1). The equation shows that the gain is dependent on  $R_c$ ,  $R_e$ , and  $g_m$ . One aspect of the gain equation's dependence on temperature is the inversely proportional to temperature

- 15 -

value of  $g_m$ . Since  $g_m = \frac{l_c}{V_T}$  and  $V_T = \frac{kT}{q}$ , then it may be seen that for  $g_m$  to be independent of temperature, then  $I_c$  should be proportional to temperature. The temperature dependent current mirror, as described in section 6.3, provides the tail currents through the Digitally Controlled Current Switch so as to drive the DGSDA. Therefore, a major contributor to temperature dependent gain error is cancelled so that  $g_m$  is independent of temperature.

Examining the expanded gain equation of equation 3.9, it is apparent that variations in gain due to temperature are not solely due to changes in  $g_m$  Therefore, the variations with temperature for the remaining parameters should be considered. Since  $r_{ex}$  is small relative to  $\frac{1}{g_m}$  and  $R_e$ , then the change with respect to temperature of the gain due to  $r_{ex}$  may be neglected. The effects of temperature on  $Z_L$  due to  $C_{cs}$ ,  $C_{layout}$ ,  $C_{Rc}$ , and  $C_{\mu ef}$  may also be neglected since the temperature dependency of these capacitances is small. The remaining parameters in equation 3.9 are  $R_c$  and  $R_e$ . Since these

two resistors are designed such that they are of the same type, the values should approximately track. Using equation 3.14, the temperature coefficient of  $A_v$  may be found.

$$\frac{1}{A_{v}}\frac{\partial A_{v}}{\partial T} \approx \left[ \left( \frac{R_{c} \parallel Z_{L}}{R_{c}} \right)^{2} - \frac{R_{e}}{\frac{1}{g_{m}} + r_{ex} + R_{e}} \right] \frac{1}{R}\frac{\partial R}{\partial T} \qquad (Eq.3.14)$$

Another major contributor to gain error is the error caused by the resistor tracking errors between  $R_c$  and  $R_e$ . This gain error maybe found by using equation 3.15.

$$\varepsilon_{AV_R} \approx 20 \log \left[1 + \frac{1}{2} \left(1 + A_{Vo} \frac{R_{eo}}{R_{co}}\right) \varepsilon_{Rtrack}\right]$$

(Eq.3.15)

#### 3.1.4 Example Calculation for the 24 / 0 dB DGSDA

As an example, the  $R_c$ ,  $I_{tail}$ , and  $R_e$  may be found for the 24 / 0 dB gain stage. Using these parameters, the gain errors due to temperature and process variations may also be calculated.

# For the 0 dB gain setting, a maximum output level of at least 0.5 Vpp is required with a total gain error ( $\mathcal{E}_{AV}$ ) of ±0.6 dB. First, the load capacitance should be estimated. Therefore, the C<sub>cs</sub> is approximately 0.20 pF, while the C<sub>µef</sub> of the emitter follower may be estimated to be 0.15 pF. The C<sub>layout</sub> and the C<sub>Rc</sub> is approximately 0.15 pF and 0.1 pF, respectively. Therefore, the total estimated loading capacitance, CL, is 0.60 pF. Thus, with a resistor tolerance of 20% and an allocated rolloff gain error of ±0.3 dB then equation 3.11 may be used to calculate R<sub>c</sub> as found in equation 3.16.

$$R_{c} = \frac{\sqrt{10^{0.3 \text{ dB}}}{10^{10} - 1}}{2\pi (70 \text{ MHz})(0.60 \text{ pF})(1 + 0.2)} = 845 \Omega \qquad (\text{Eq.3.16})$$

Now,  $I_{tail}$  may be found with equation 3.12 as shown in equation 3.17 with an output swing of 0.5 Vpp.

#### 0.5 Vnn

$$I_{\text{tail}} = \frac{0.5 \text{ vpp}}{(845 \Omega)(1 - 0.2)} = 740 \,\mu\text{A} \qquad (\text{Eq. 3.17})$$

and with equation 3.13,  $R_e$  may be calculated to be the value as found in equation 3.18.

$$R_{\theta} = \frac{\frac{1}{\sqrt{\left(\frac{1}{845 \ \Omega}\right)^2 + \left(2\pi (70 \text{MHz})(0.60 \text{pF})\right)^2}}}{1} - 1 \ \Omega - \frac{\frac{26 \text{ mV}}{740 \ \mu \text{A}}}{2} = 753 \ \Omega \text{ (Eq. 3.18)}$$

When in the high gain state, 24 dB of gain is required. Since R<sub>c</sub> is shared then the previously calculated value must be used. Due to the high gain of this setting, it is obvious that a small R<sub>e</sub> will result. To decrease the dependence of gain on g<sub>m</sub>, a larger tail current should be selected so that the  $\frac{1}{g_m}$  term in the gain equation (Eq. 3.6) may be smaller Therefore, I<sub>tail</sub> may be selected to be 2 mA so as to decrease  $\frac{1}{g_m}$ . Any more current would be too much considering the constraints of the power budget. Thus, the only

remaining parameter to be calculated is  $R_{e}$ . Using equation 3.13  $R_{e}$  is found in equation 3.19.

$$R_{\theta} = \frac{\frac{1}{\sqrt{\left(\frac{1}{845 \ \Omega}\right)^{2} + \left(2\pi (70 \text{MHz})(0.60 \text{ pF})\right)^{2}}}}{15.85} - 1 \ \Omega - \frac{26 \text{ mV}}{\frac{2 \text{ mA}}{2}} = 25 \ \Omega \text{ (Eq. 3.19)}$$

Now,  $Z_{in}$  and  $Z_{out}$  may be found from equations 3.7 and 3.8, as calculated in equations 3.20 and 3.21, respectively.

$$Z_{out} = R_c \parallel Z_L = \frac{1}{\sqrt{\left(\frac{1}{845 \ \Omega}\right)^2 + \left(2\pi (70 \text{MHz})(0.60 \text{pF})\right)^2}} = 825 \ \Omega \quad (\text{Eq. 3.20})$$

$$Z_{in} = 2 \ Z_i \approx 2 \left[\frac{57}{\frac{2 \ \text{mA}}{\Omega / \Omega \text{cm} M^2}} + (1 \ \Omega + 25 \ \Omega) 57\right] = 5928 \ \Omega \quad (\text{Eq. 3.21})$$

L2(26mV)

Where  $Z_{in}$  is the minimum value as found in the high gain state and  $\beta_0$  is found by equation 3.21.

$$\beta_{o} = \frac{f_{T}}{f_{op}} = \frac{4.0 \text{ GHz}}{70 \text{ MHz}} = 57$$

(Eq.3.21)

where  $f_T$  is found from the AT&T ALA202 Data Sheet [4].

The errors due to temperature and resistor tracking errors may now be calculated. Using a temperature coefficient of 1300 ppm/°C [4] for 50  $\Omega$ /sq. implanted boron resistors in equation 3.14, the gain temperature coefficient for the low gain state is found to be that as calculated in equation 3.23,

$$\frac{1}{A_{v}} \approx \left[ \left( \frac{825 \Omega}{845 \Omega} \right)^{2} - \frac{753 \Omega}{\frac{26 \text{ mV}}{370 \mu \text{A}} + 1 \Omega + 753 \Omega} \right] 1300 \frac{\text{ppm}}{\text{°C}} = 52 \frac{\text{ppm}}{\text{°C}} (\text{Eq.3.23})$$

while, for the high gain state, the gain temperature coefficient is found by equation 3.24.

$$\frac{1 \partial A_{v}}{A_{v} \partial T} \approx \left[ \left( \frac{825 \Omega}{845 \Omega} \right)^{2} - \frac{25 \Omega}{\frac{26 \text{ mV}}{1 \text{ mA}} + 1 \Omega + 25 \Omega} \right] 1300 \frac{\text{ppm}}{\text{°C}} = 614 \frac{\text{ppm}}{\text{°C}} (\text{Eq.3.24})$$

Therefore, with a maximum temperature swing of  $\pm 60$  °C from the nominal temperature, the maximum change in gain for the 0 dB and the 24 dB settings would be the changes as found by equations 3.25 and 3.26, respectively.

$$\begin{aligned} & \mathcal{E}_{AV_{T}} = 20 \log \left[ 1 + \frac{(\pm 60 \ ^{\circ}\text{C})(52 \ \text{ppm/}^{\circ}\text{C})}{10^{6}} \right] = \pm 0.027 \ \text{dB} \ (\text{Eq.3.25}) \\ & \mathcal{E}_{AV_{T}} = 20 \log \left[ 1 + \frac{(\pm 60 \ ^{\circ}\text{C})(614 \ \text{ppm/}^{\circ}\text{C})}{10^{6}} \right] = \pm 0.314 \ \text{dB} \ (\text{Eq.3.26}) \end{aligned}$$

The gain error due to resistor tracking errors may be found with equation 3.15 using a resistor tracking error of approximately 1% [4]. The maximum

error with the low gain selected is as found in equation 3.27,

$$\mathcal{E}_{AV_R} \approx 20 \log \left[ 1 + \frac{1}{2} \left( 1 + 1 \frac{753 \ \Omega}{845 \ \Omega} \right) 0.01 \right] = \pm 0.082 \ dB(Eq.3.27)$$

and for the high gain selected the maximum error is as found in equation 3.28.

$$\mathcal{E}_{AV_R} \approx 20 \log \left[ 1 + \frac{1}{2} \left( 1 + 15.85 \frac{25 \Omega}{845 \Omega} \right) 0.01 \right] = \pm 0.064 \text{ dB} (Eq.3.28)$$

The cumulative gain error is the sum of the errors due to the allocated rolloff error of -0.3 dB, the error due to temperature, and the error due to resistor tracking. This results in a total gain error of  $\pm 0.409$  dB for the 0 dB gain setting and  $\pm 0.678$  dB for the 24 dB setting. It is now evident that the upper limit for the total gain error occurs when the high gain mode is selected. The results for the 24 dB setting are found to be slightly outside the target value range of  $\pm 0.6$  dB gain error. This shouldn't be a problem because the following three gain stages of the Digitally Controlled Gain IF Amplifier have maximum gains of 12 dB, 6 dB, and 3 dB. Each of these gain stages should

have a smaller maximum gain error such that the total gain error through the IF amplifier will result in the target of ±3 dB. Of course, the emitter follower stage will also contribute some gain error. Section 3.4 will show the total gain error through all four stages.

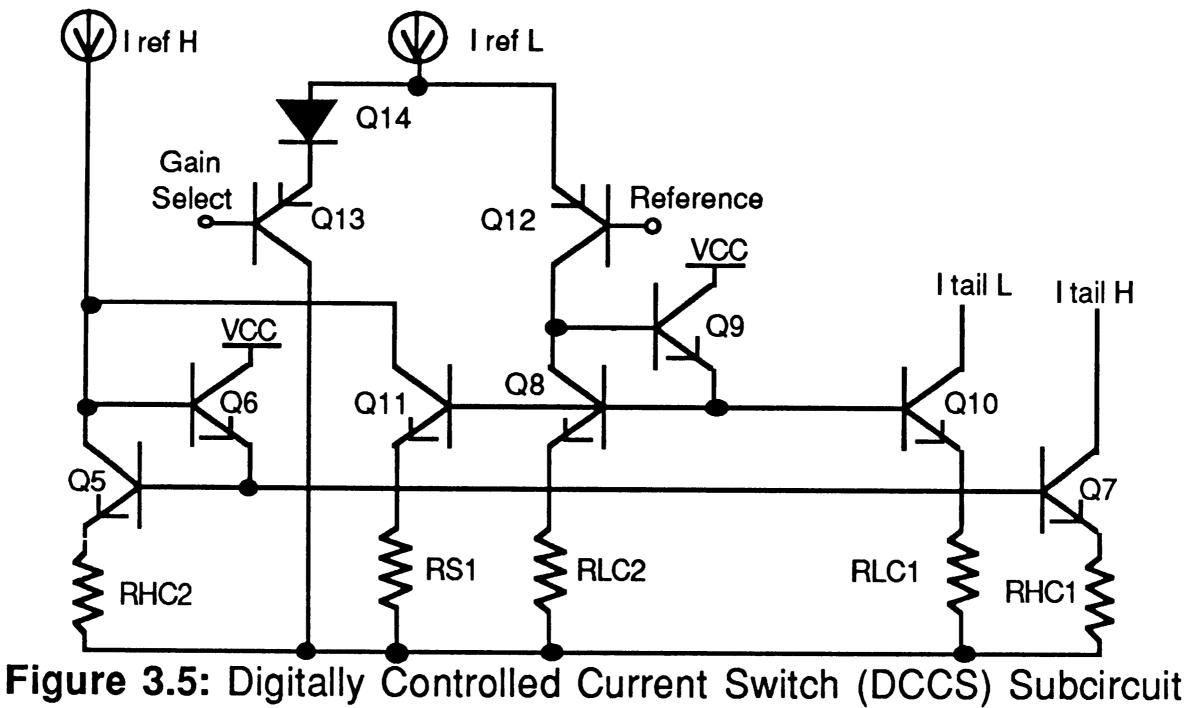

#### 3.2 Digitally Controlled Current Switch (DCCS) Design

The operation of the Dual Gain State Differential Amplifier is dependent upon the circuitry that controls the selection of tail currents. This section will discuss the operation of the circuit that performs this task. The Digitally Controlled Current Switch (DCCS) subcircuit is shown in figure 3.5

#### 3.2.1 Digitally Controlled Current Switch Operation

Depending upon the state of the DCCS, the reference currents I<sub>ref H</sub> and Iref L ultimately drive the differential amplifier tail currents Itail H and Itail L , through emitter degenerated current mirrors. Since  $I_{\text{ref H}}$  and  $I_{\text{ref L}}$  are derived from a proportional to absolute temperature (PTAT) current mirror that is described in section 6.3, then the currents  $I_{tail H}$  and  $I_{tail L}$  will also be proportional to absolute temperature. Therefore, the temperature dependency of  $g_m$  in the differential amplifiers, as mentioned in section 3.1.3, will be cancelled.

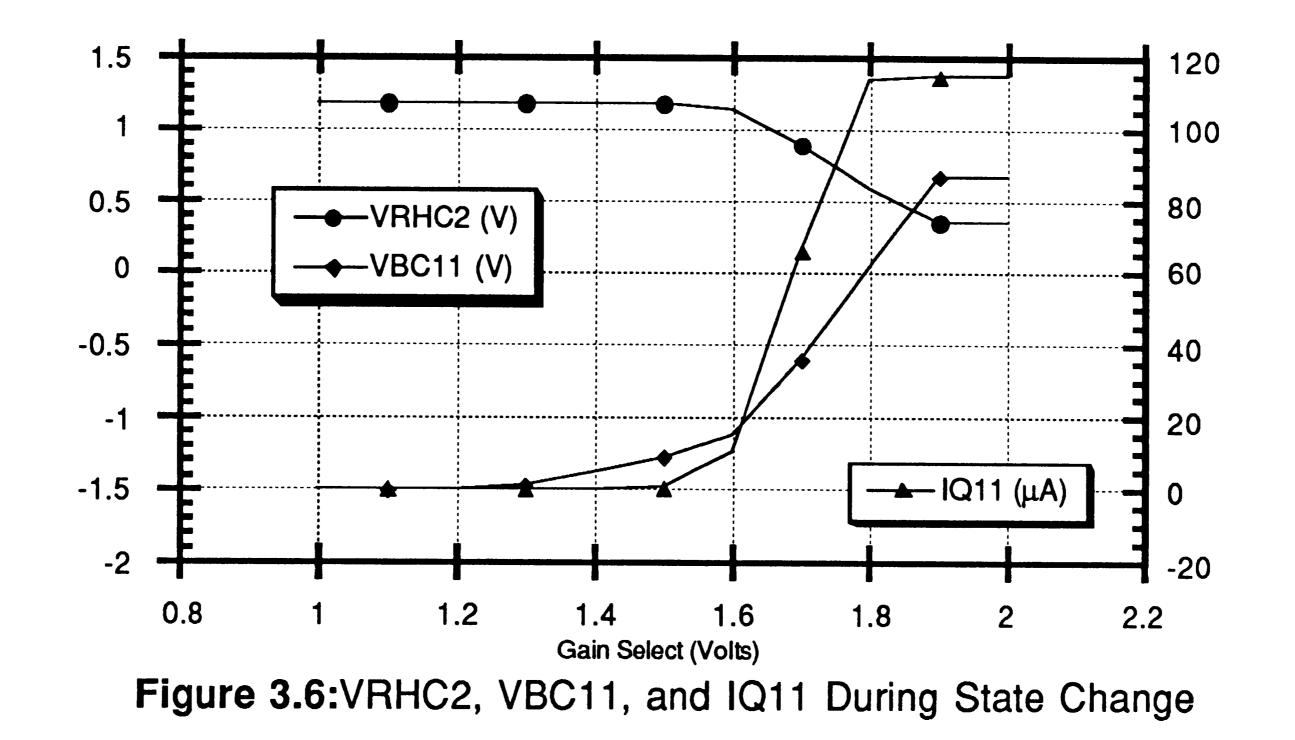

At the heart of the DCCS are transistors Q12, Q13, and Q14 that form a PNP differential pair. These transistors steer the current  $I_{ref L}$  either to ground or to the low-state current mirror (Q8, Q9, and Q10) that provides the current  $I_{tail L}$ . The base rail of the low-state current mirror is connected to transistor Q11. If the signal Gain Select is above Reference so that Q12 conducts and Q13 and Q14 doesn't, then the current  $I_{ref L}$  drives the low-state current mirror. This provides the tail current  $I_{tail L}$  and also causes Q11 to begin conducting. When Q11 starts to conduct, the voltage across RHC2 decreases since Q11 is sinking some of the current from  $I_{ref H}$ . Therefore, the initially reverse-biased base-to-collector junction of Q11 begins to forward bias so that Q11 moves into the saturation region. With Q11 in saturation, all of the current  $I_{ref H}$  is sunk to ground through Q11. Thus, the mirror that provides the current  $I_{tail H}$  is turned off due to a lack of current. Figure 3.6 shows a simulation of the voltage across RHC2, the base-to-collector voltage of Q11, and the collector current of Q11 where it is seen how the saturation of Q11

occurs as the Gain Select voltage rises.

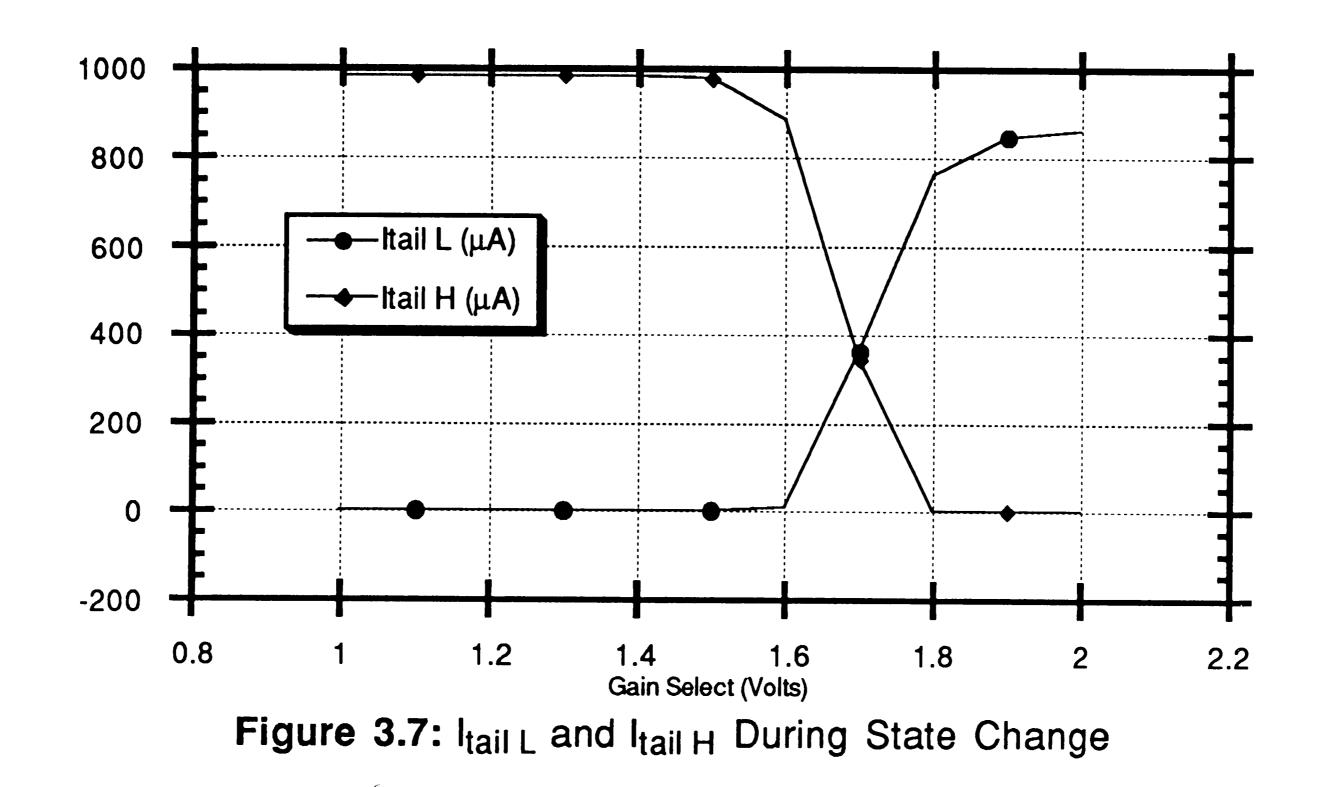

When Gain Select is below Reference so Q13 and Q14 conduct and Q12 is off, then the current  $I_{ref L}$  is sunk to ground through Q13 and Q14. Therefore, the low-state current mirror is turned off, which also turns off Q11 so the high-state current mirror (Q5, Q6, Q7) may provide the current  $I_{tail H}$  by mirroring

$I_{ref H}$ . The switching of  $I_{tail H}$  and  $I_{tail L}$  is shown in figure 3.7 as Gain Select increases.

The transistors Q6 and Q9 of the high-state and low-state current mirrors are provided as "beta helpers" to reduce the effects of low  $\beta$  on the error of the current mirrors [6]. Also, for each of the current mirrors, the resistor values (RLC1, RLC2, RHC1, and RHC2) are selected so as to provide a high current gain between the reference currents and the tail current outputs. The high gain is needed to allow the use of small reference currents so that the low supply current target is met. Each pair of resistors sets the gain such that the tail currents are appropriate for each stage as defined in the previous discussion. The formula used to obtain the resistor values for the current mirrors is the transcendental equation 3.29 as shown below.

$$V_{T} ln \left[ \frac{I_{ref}}{I_{tail}} \frac{Size_{tail}}{Size_{ref}} \right] = I_{tail} R_{tail} - I_{ref} R_{ref}$$

(Eq.3.29)

The Reference signal is a temperature independent voltage derived from the bandgap reference as described in section 6. Since this reference voltage is also used in the mixers and the phase shifter, the diode Q14 is required to lower the switch point so as to obtain near-TTL compatible logic levels.

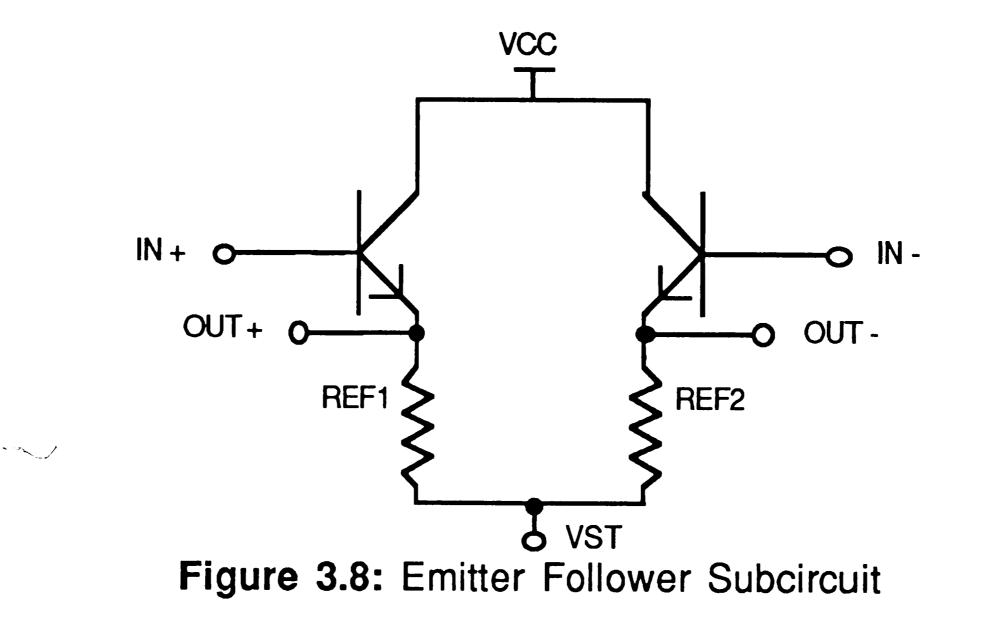

#### **3.3 Emitter Follower Design**

The emitter follower subcircuit is shown in figure 3.8. This circuit was selected as a unity-gain buffer between the differential pair output and the next stage, whether it is another differential pair or coupling capacitors.

The node  $V_{ST}$  is connected to the collector of a large saturating transistor that is described in the bandgap description of section 6. With the bandgap circuit enabled,  $V_{ST}$  is equal to the  $V_{SAT}$  of a large NPN saturating transistor, while when the circuit is disabled,  $V_{ST}$  goes high so that only a minimum of current is drawn through the emitter followers. The emitter followers of each stage in the IF amp are connected to this node. This connection facilitates the low supply current requirement of the sleep mode whose implementation is to be described in section 6.

In selecting  $R_{EF}$ , a primary consideration is to avoid slew rate limiting when driving large capacitances such as the parasitic capacitance of the coupling capacitors between the first and second stages and following the last stage of the IF amplifier. Therefore, the current needed to drive the load capacitance may be found by equation 3.30,

$$I_{EF min} = C_L(f_{op})V_{peak s-e}$$

(Eq. 3.30)

and to determine  $R_{EF}$ , worst case conditions must be considered as done in equation 3.31.

$$V_{cc min} - \frac{I_{tail max}}{2} R_{c}(1 + \mathcal{E}_{R}) - V_{be max} - V_{st max}$$

$$R_{EF} = I_{EF min}(1 + \mathcal{E}_{R})$$

(Eq. 3.31)

The gain of the emitter follower may be determined by the formula [6] in equation 3.32.

$$A_{v EF} = 20 \log \left[ \frac{1}{\frac{R_{c} + \beta_{o} \frac{V_{T}}{I_{EF}}}} \right]$$

(Eq. 3.32)

$$\frac{R_{c} + \beta_{o} \frac{V_{T}}{I_{EF}}}{(\beta_{o} + 1)R_{EF}} \right]$$

The gain of an emitter follower has a temperature coefficient that is given by equation 3.33.

$$\frac{1}{A_v} \frac{\partial A_v}{\partial T} \approx -\frac{k}{ql_{EF}} \frac{1}{R_{EF}}$$

(Eq. 3.33)

# In order to have a negligible loading effect on the load resistor of the differential pair, the emitter follower exhibits a high input impedance as shown by equation 3.34 [6]

$$R_i = \beta_o \frac{V_T}{I_{EF}} + R_{EF}(\beta_o + 1)$$

(Eq.3.34)

Also, the emitter follower has a low output impedance as shown by equation 3.35.

$$R_{o} = \left[\frac{1}{g_{m}} + \frac{R_{c}}{(1 + \beta_{o})}\right] \|R_{EF}$$

(Eq. 3.35)

#### 3.3.1 Example Calculations for 24 / 0 dB Emitter Follower

~.)

To continue the example as discussed before so as to obtain a design for the emitter follower stage for the 24 / 0 dB amplifier, the emitter follower current may be found using equation 3.30 as shown in equation 3.36. The load capacitance is equivalent to the bottom plate to substrate parasitic

capacitance of about 1 pF for the 32 pF coupling capacitor that follows the 24 / 0 dB amplifier and a layout capacitance of about 0.5 pF

$$I_{\text{EF min}} = (1.5 \text{ pF})(2\pi)(70 \text{ MHz})(0.30 \text{ V}) = 198 \mu\text{A}$$

(Eq. 3.36)

.

ſ.

Now, using this current, the emitter follower load resistor may be found with equation 3.31 as shown in equation 3.37.

03

هی کن ا

$$\frac{4.75 \text{ V} - \frac{2 \text{ mA}}{2} (845 \Omega)(1 + 0.2) - 0.8 \text{ V} - 0.3 \text{ V}}{198 \mu \text{A}(1 + 0.2)} = 11 \text{ k}\Omega \quad (\text{Eq. 3.37})$$

Given the calculated values of  $I_{EF}$  and  $R_{EF}$ , the gain through the emitter follower may be calculated using equation 3.32 as shown in equation 3.38.

$$A_{v EF} = 20 \log \left[ \frac{1}{845 \Omega + 57 \frac{26 \text{ mV}}{198 \mu \text{A}}} \right] = -0.113 \text{ dB}(\text{Eq. 3.38})$$

$$\left[ 1 + \frac{(57 + 1)11 \text{ k}\Omega}{(57 + 1)11 \text{ k}\Omega} \right]$$

Also, the gain error due to temperature may be found using equation 3.33, as shown in equation 3.39, and converting to decibels as found in equation 3.40.

$$\frac{1}{A_{v}}\frac{\partial A_{v}}{\partial T} \approx -\frac{1.38 \times 10^{-23} \frac{J}{K}}{(1.602 \times 10^{-19} \text{C})(198 \ \mu\text{A})} \frac{1}{11 \ \text{k}\Omega} = -40 \frac{\text{ppm}}{^{\circ}\text{K}} (\text{Eq. 3.39})$$

$$\mathcal{E}_{\text{AV}_{T}} = 20 \log \left[1 + \frac{(\pm 60 \ ^{\circ}\text{K})(-40 \ \text{ppm}/^{\circ}\text{K})}{10^{6}}\right] = \frac{1}{4} 0.021 \ \text{dB} (\text{Eq. 3.40})$$

The input and output impedances may now be found using the emitter follower current and load resistor as shown in equation 3.41 and 3.42, respectively.

$$R_i = 57 \frac{26 \text{ mV}}{198 \mu \text{A}} + 11 \text{ k}\Omega(57 + 1) = 645 \text{ k}\Omega$$

(Eq.3.41)

$$R_{o} = \left[\frac{26 \text{ mV}}{198 \mu \text{A}} + \frac{845 \Omega}{(1+57)}\right] \parallel 11 \text{ k}\Omega = 144 \Omega \qquad (\text{Eq. 3.42})$$

With the calculated values as found above, it is evident that the input impedance of the emitter follower is much higher than the differential pair load resistor. Therefore, the conclusion made previously that it has a negligible effect may be considered to be true. Also, the gain loss as contributed by the emitter follower may be considered to be small, but since the specifications of each amplifier call for a  $\pm 0.6$  dB error, a recalculation of the resistor may be considered. Since the ADVICE [7] simulator may be used to "fine tune" the design, the recalculation will, in effect, be made after performing worst case simulations and adjustments of the resistor values are found to meet the specifications.

#### 3.4 Interconnection of Differential Amplifiers

The complete IF amplifier stage is made complete by the interconnection of the four Digitally Controlled Differential Amplifiers each with gains of 24 / 0, 12 / 0, 6 / 0, and 3 / 0 dB. This section will discuss how offset problems may be reduced, the overall calculated gain and error performance of the complete IF amplifier, and simulation results of the complete IF amplifier.

#### 3.4.1 Using Coupling Capacitors to Reduce Offset Problems

With a total maximum gain of 45 dB, the IF amplifier could be susceptible to the amplification of the input offset voltage. If this occurs, with maximum gain, the output of the IF stage could be pinned to one of the supply rails. To reduce the possibility of this happening, capacitors should be placed between the 24 dB and the 12 dB amplifiers. The addition of coupling capacitors between these stages splits the possible gain of an offset into 24 dB and 21 dB maximum gain segments. Although these gains are still fairly large, with proper device placement in the layout of the differential pairs, the offsets shouldn't be large enough to cause latching of each segments outputs. The coupling capacitors should be as large as possible so as to reduce the voltage divider loss between the high frequency coupling capacitor impedance and the input impedance of the next stage. Therefore, the largest available capacitors on the ALA202 array were used. The 32 pF capacitance should be large enough at the 70 MHz operating frequency. A

block diagram of the four DCGDA stages is shown in figure 3.9 with the placement of the coupling capacitors.

# 3.4.2 Calculated IF Amplifier Gain and Error Performance

In the previous sections, an example calculation for the 24 / 0 dB Digitally Controlled Gain Differential Amplifier was performed. The resistor values and the gain performance characteristics for examples of the remainder of the blocks is presented here. In addition, the total maximum gain error is

also presented by finding the sum of the gains for each block in the IF amplifier stage. Table 3.1 shows the calculated values.

| Stage   | R <sub>c</sub> | I <sub>tail</sub> | Re  | I <sub>EF</sub> | R <sub>EF</sub> | AVEF   | A <sub>V nom</sub> | A <sub>V min</sub> | A <sub>V max</sub> | ΔΑγ    |

|---------|----------------|-------------------|-----|-----------------|-----------------|--------|--------------------|--------------------|--------------------|--------|

| Units   | Ω              | mA                | Ω   | μΑ              | kΩ              | dB     | d B                | d B                | d B                | d B    |

| 24/0 dB | 845            | 0.74              | 753 | 198             | 11              | -0.113 | 0.0                | -0.501             | +0.275             | ±0.388 |

|         |                | 2                 | 25  |                 |                 |        | 24.0               | 23.230             | 24.544             | ±0.657 |

| 12/0 dB | 845            | 0.74              | 753 | 66              | 39              | -0.091 | 0.0                | -0.483             | +0.301             | ±0.392 |

|         |                | 0.74              | 136 |                 |                 |        | 12.0               | 11.356             | 12.462             | ±0.553 |

| 6/0 dB  | 845            | 0.74              | 753 | 66              | 39              | -0.091 | 0.0                | -0.483             | +0.301             | ±0.392 |

|         |                | 0.74              | 342 |                 |                 |        | 6.0                | 5.463              | 6.355              | ±0.446 |

| 3/0 dB  | 845            | 0.74              | 753 | 198             | 13              | -0.097 | 0.0                | -0.488             | +0.294             | ±0.391 |

|         |                | 0.74              | 512 |                 |                 |        | 3.0                | 2.490              | 3.316              | ±0.413 |

Table 3.1: Resistor Values and Gains for the DCGDA Amplifiers

The total maximum low-gain error due to DCGDA errors is equivalent to the difference between 45 dB and the sum of the  $A_{V min}$  gains for the maximum gain settings of each stage, while the total maximum high-gain error is the same except the A<sub>V max</sub> gains are used. This results in a maximum low-gain error of -2.461 dB and a maximum high-gain error of +1.677 dB. Therefore,

ć

the total gain error is close to the allocated  $\pm 2.4$  dB error for the full IF amplifier stage.

An additional gain error may be due to the coupling capacitor between the 24 / 0 dB and 12 / 0 dB stages and the coupling capacitor at the output of the IF amplifier stage. Each coupling capacitor is 32 pF and the 12 / 0 dB amplifier has an input impedance of approximately 10 k $\Omega$ , while the two mixers connected to the output of the IF amplifier stage each has an approximate input impedance of 10 k $\Omega$  for a parallel impedance of 5 k $\Omega$ . It is evident, since the impedance of the 32 pF capacitor at 70 MHz is 71  $\Omega$ , that this voltage divider gain error is negligible.

# 3.4.3 IF Amplifier Simulation Results

The IF amplifier simulations are focused on determining the gain variation through the four DCGDA amplifier stages. Through the use of ADVICE [7], the full IF amplifier, including the coupling capacitors, was simulated. An approach was taken whereby two simulations were performed, one with all gains low and one with all gains high. By finding the gain through each stage for the two states, the two gains for each stage was determined. Simulations were performed at three junction temperatures, -25 °C, 25 °C, and 95 °C. Only the 95 °C temperature included a 10 °C increment above the maximum 85 °C ambient temperature to account for the thermal impedance of the package.

During the simulation phase of the design, resistor values, such as  $R_c$  and  $R_e$ , were changed slightly so as to center the gain variations within the  $\pm 0.6$  dB gain error allowed for each amplifier. Also, the tail currents were changed slightly so as to achieve the desired performance while achieving the lowest supply current possible. In practice, none of the resistor values or tail currents were changed enough so as to warrant the re-calculation of the design parameters by hand. Table 3.2 shows a summary of the simulation results where the nominal values are at 25 °C and the minimum and maximum values are for the range of temperatures. The full set of simulation results for the IF amplifiers is shown in appendix 1.

| Stage   | A <sub>V nom</sub> | A <sub>V min</sub> | A <sub>V max</sub> | ΔΑν    |

|---------|--------------------|--------------------|--------------------|--------|

| Units   | dB                 | dB                 | dB                 | dB     |

| 24/0 dB | +0.325             | -0.455             | +0.395             | ±0.425 |

|         | +24.28             | +22.96             | +24.65             | ±0.845 |

| 12/0 dB | -0.026             | -0.652             | +0.167             | ±0.409 |

|         | +11.93             | +11.12             | +12.16             | ±0.520 |

| 6/0 dB  | +0.141             | -0.491             | +0.369             | ±0.430 |

|         | +6.11              | +5.43              | +6.37              | ±0.470 |

| 3/0 dB  | +0.072             | -0.661             | +0.193             | ±0.427 |

|         | +3.18              | +2.53              | +3.30              | ±0.385 |

Δ

Table 3.2: Simulated Gains for the DCGDA Amplifiers

By comparing the  $\Delta A_V$  columns of tables 3.1 and 3.2, it may be seen that the calculations for the gain error in each amplifier was reasonably close. Some explanation for the discrepancies is that ADVICE [7] uses significantly more sophisticated models that those that were used to determine the design equations. Also, since some of the resistor values were modified slightly, this may also be offered as an explanation.

The simulations show that a total minimum gain error of -2.96 dB and a total maximum gain error of +1.48 dB results in a  $\pm$ 2.22 dB spread of the gain errors. This compares with the -2.606 dB minimum and +1.822 dB maximum gain errors that resulted in a  $\pm$ 2.214 dB spread. Due to the limited resistor selection in the use of a linear array, the centering of the spread was considerably difficult.

# 4. Double Balanced Mixer and Output Stage

The In-phase (I) and Quadrature (Q) mixers of the integrated circuit are shown as blocks in figure 2.1. Their function is to perform demodulation of a Gaussian-filtered Minimum Shift Keying (GMSK) signal at a frequency of 70 MHz, such that the I and Q outputs result in digital signals at frequencies up to 1 MHz. Output stages are included on the differential outputs of both the I and Q mixers. The output stages provide buffering to drive the output load as specified in section 2.2.5.

The following sections describe the operation and design of the double balanced mixer and output stages. Section 4.1 describes how GMSK demodulation is performed in this circuit. The design of the double balanced mixer and the output stage is described in sections 4.2 and 4.3, respectively. An example calculation of component values, gain, and gain errors for the mixer and output stages is presented in section 4.4, while section 4.5 discusses and presents the simulation results for the combined mixer and output stages.

# 4.1 GMSK Demodulation

GMSK signals are similar in nature to Quadrature Phase Shift Keying (QPSK) signals in that the information content of the signal is based on the relative phase of the modulated signal. A means of demodulation for this type of signal is by the multiplication of two equal frequency signals. The multiplication of the GMSK signal with a local oscillator (LO) signal of constant phase and a frequency equal to that of the input signal will result in the demodulation of the input signal's information content [9].

A GMSK input signal, s(t), is phase modulated such that the mathematical representation of the signal is as shown in equation 4.1.

$$s(t) = A_i \cos (2\pi f_0 t + \theta_i(t))$$

(Eq. 4.1)

where

$$\theta_{i}(t) = \{\theta_{1}, \theta_{1} + 90^{\circ}, \theta_{1} + 180^{\circ}, \theta_{1} + 270^{\circ})\}$$

This GMSK modulated signal, s(t), contains information that consists of two separate bit streams. Each of the four possible phase settings of  $\theta_i$  represents two bits of information for a single data time frame.

The multiplication of the input signal, s(t), and the local oscillator signals,  $LO_i(t)$  and  $LO_q(t)$ , produces the two bit stream outputs. The mathematical representations of the local oscillator I and Q mixer inputs are shown in equations 4.2 and 4.3, while the resulting output formulas are shown in equations 4.4 and 4.5 for the I and Q channels, respectively. The output equations assume that there is a low pass filtering circuit on the output of the mixers so as to remove a component equal to twice the carrier frequency that would remain in the output signal. The following sections will describe this filtering circuit.

$$LO_{i}(t) = A_{lo} \cos (2\pi f_{o} t + \theta_{lo})$$

(Eq. 4.2)

$$LO_q(t) = A_{lo} \sin (2\pi f_0 t + \theta_{lo})$$

(Eq. 4.3)

$$out_i(t) = A_i A_{lo} \left[ \frac{1}{2} \cos (\theta_i(t) - \theta_{lo}) \right]$$

(Eq. 4.4)

$$out_q(t) = A_i A_{lo} \left[ -\frac{1}{2} \sin (\theta_i(t) - \theta_{lo}) \right]$$

(Eq. 4.5)

It can be seen from equations 4.4 and 4.5, that the phase,  $\theta_i$ , may be changed so that, when demodulated, the I and Q output levels will represent either a binary 1 or 0. Table 4.1 shows an example of the possible decoding patterns that could result from the I and Q outputs in a single data time frame.

| Dutput |

|--------|

| 0      |

| 1      |

| 0      |

| 1      |

|        |

Table 4.1: Phase Input Bit Representation

The bit representations of the I and Q outputs are determined by a decision circuit that is externally connected to the mixer outputs. An optimum

detectable output will result as long as  $|\theta_{lo} - \theta_1|$  is equal to some multiple of 45°. If  $|\theta_{lo} - \theta_1|$  is equal to 0°, 90°, 180°, or 270°, then the decision circuit may produce errors for some bits. Therefore, external circuitry should be used in the integrated circuit's application so as to change the local oscillator phase,  $\theta_{lo}$ , such that the output is detectable and a low bit error rate will result [3].

The use of a double balanced Gilbert-cell mixer [6, 8] will implement the multiplication function that is required for GMSK demodulation. The design of this mixer circuit is discussed in the next section.

#### 4.2 Double Balanced Mixer Design

The Gilbert-cell double balanced mixer [6, 8] of figure 4.1 performs the demodulation function as described in the previous section. The differential input signal,  $V_{if}$ , is applied to the bases of transistors Q5 and Q6, while the local oscillator signal,  $V_{lo}$ , is across the input of the cross coupled pair of transistors Q1 through Q4. The emitter degeneration resistor,  $R_g$ , is used to develop a conversion gain which is defined as the ratio of the output level to the IF input level, each at their respective frequencies. The output stage, to be described later, is differentially driven by the output  $V_{out}$ .

The following sections will describe the operation of the mixer, the determination of conversion gain, and the low pass output filtering circuit.

#### 4.2.1 Mixer Operation

W

Ø

The demodulation of the GMSK modulated signal in this circuit is performed somewhat differently than the simple multiplication as described in the previous section. The LO inputs of the mixer are designed so that the amplitude is much larger than  $2 \cdot V_T$ . As explained in Grey and Meyer [6], this causes the transistors Q1 through Q4 to behave like switches, so that the signals from the linearly operating devices Q5 and Q6 are multiplied by a +1 to -1 square wave. Therefore, the input signal, s(t), as shown in equation 4.1, is multiplied with the square wave functions as shown in equation 4.6 for the I channel and equation 4.7 for the Q channel.

$$LO_i(t) = \sum_{n=1}^{\infty} A_n \cos (2\pi n f_0 t + n\theta_{l0})$$

(Eq. 4.6)

here

$$LO_q(t) = \sum_{n=1}^{\infty} A_n \sin (2\pi n f_0 t + n\theta_{l0}) \qquad (Eq. 4.7)$$

$$A_n = \frac{\sin n\frac{\pi}{2}}{\frac{\pi}{4}}$$

The resulting outputs for both the I and Q channels are shown in equations 4.8 and 4.9, where only the n=1 component is within the pass band of the low pass filter.

$$out_i(t) = \frac{2KA_i}{\pi} \left[ \cos \left(\theta_i(t) - \theta_{io}\right) \right]$$

(Eq. 4.8)

$$out_{q}(t) = -\frac{2KA_{i}}{\pi} \left[ sin \left( \theta_{i}(t) - \theta_{10} \right) \right]$$

(Eq. 4.9)

#### where K = gain from transistors Q5 and Q6

From equations 4.8 and 4.9, it is seen that they are similar to equations 4.4 and 4.5 in that they result in output voltages that are proportional to the input phase  $\theta_i(t)$ . The advantage of using the square wave input is evident from

equations 4.8 and 4.9 in that the output level is independent of the LO input amplitude.

Since the specification of section 2.2.2 calls for a conversion gain of 6 dB through the mixers, the transistors Q5 and Q6 must exhibit a gain of K so that the factor in the output equations with yield the desired gain. As seen in the next section, the calculation of the gain factor is similar to the gain calculations as found in the IF amplifiers.

#### 4.2.2 Gain Determination and Selection

The mixer gain factor may be found by simplifying the configuration of Q5, Q6, R<sub>g</sub>, and I<sub>tail</sub> such that it resembles the emitter degenerated emitter coupled pair of figure 3.2 in the IF amplifier section. This is done by assuming that the resistor R<sub>g</sub> is split into two resistors each of value R<sub>g</sub> / 2 that are driven at their common point by a current source equal to  $2 \cdot I_{tail}$ .

Therefore, the gain of these transistors may be found by using equation 3.1 with the appropriate parameters, as shown in equation 4.10.

$$K = \frac{R_{c}}{\frac{V_{T}}{2 \cdot I_{tail}} + \frac{R_{g}}{2}}$$

(Eq. 4.10)

With the combination of equations 4.8, 4,9, and 4.10, the overall mixer gain may be found for each channel by equations 4.11 and 4.12.

$$out_{i}(t) = \frac{4A_{i}}{\pi} \cdot \frac{R_{c}}{\frac{V_{T}}{I_{tail}} + R_{g}} \left[ cos \left(\theta_{i}(t) - \theta_{lo}\right) \right]$$

(Eq. 4.11)

$$out_{q}(t) = -\frac{4A_{i}}{\pi} \cdot \frac{R_{c}}{\frac{V_{T}}{I_{tail}} + R_{g}} \left[ sin \left(\theta_{i}(t) - \theta_{lo}\right) \right]$$

(Eq. 4.12)

Assuming that the condition of optimum detection is achieved, as set forth at the end of section 4.1, the absolute value of the multiplier due to the cosine and sine terms in equations 4.11 and 4.12 will have a value of  $1/\sqrt{2}$ . Therefore, the mixer gain may be found by equation 4.13.

$$A_{V} = \frac{4}{\pi} \cdot \frac{R_{c}}{V_{T}} \cdot \frac{1}{\sqrt{2}}$$

(Eq. 4.13)

$$\frac{1}{V_{T}} + R_{g} \cdot \frac{1}{\sqrt{2}}$$

Since the calculation of gain is similar to that of the IF amplifiers, then the calculation of gain errors will also be similar. The calculation of gain error may be simplified in that the effects of parasitic capacitances on the gain may be neglected, since at the load resistor, the output frequency is less than 1 MHz. Therefore, the 0.3 dB rolloff error allocation may be eliminated.

Equation 3.14 may be used for the gain temperature coefficient due to resistor temperature coefficient with some modifications as shown in equation 4.14.

$$\frac{1}{A_{v}}\frac{\partial A_{v}}{\partial T} \approx \frac{4}{\pi} \cdot \frac{1}{\sqrt{2}} \left[ 1 - \frac{R_{g}}{V_{T}} - \frac{R_{g}}{V_{T}} \right] \frac{1}{R}\frac{\partial R}{\partial T}$$

(Eq.4.14)

The gain error due to resistor tracking errors may be found with equation 4.15. This is similar to equation 3.15 as used for the IF amplifiers.

$$\varepsilon_{AV_{R}} \approx 20 \log \left[ 1 + \frac{1}{2} \left( 1 + \frac{A_{Vo}}{2} \frac{R_{go}}{R_{co}} \right) \varepsilon_{Rtrack} \right] \qquad (Eq.4.15)$$

Since the tail current, I<sub>tail</sub>, of the mixer stages is not proportional to absolute temperature, then an additional error factor due to temperature is introduced. This temperature coefficient may be found by equation 4.16.

$$\frac{1}{A_v}\frac{\partial A_v}{\partial T} = -\frac{4}{\pi} \cdot \frac{1}{\sqrt{2}} \cdot \frac{1}{T_0} \cdot \frac{V_{T_0}}{V_{T_0} + R_g I_{tail}}$$

(Eq. 4.16)

The formulas described to calculate the mixer gain and gain error will be used in an example calculation as shown in section 4.4. The example calculation will also include the gain and gain errors for the output stage.

, f

#### 4.2.3 Low Pass Output Filter

In order to remove the high frequency components of the mixed IF and LO signals from the output, capacitors were added in parallel with the collector resistors to act as a low pass filter. The output voltage transfer function has a one pole rolloff which is characterized by equation 4.17.

$$TF_{LP} = \begin{pmatrix} 1 \\ 1 + j \frac{f_0}{f_{LP}} \end{pmatrix}$$

$$f_{LP} = \frac{1}{2\pi R_c C_{IP}}$$

(Eq. 4.17)

where

The pole of the transfer function should be set at least one decade below the lowest unwanted high frequency component that may result. This will achieve at least a 20 dB attenuation of all high frequency components. The

lowest high frequency component that could result in the outputs of equations 4.11 and 4.12 without filtering is at the operating frequency of 70 MHz. Therefore, the low pass frequency,  $f_{LP}$ , should be set at no less than 7 MHz.

#### 4.3 Output Stage Design

As stated in section 2.2.5, the differential output stage of each mixer must be able to drive a 1 k $\Omega$  resistive load in parallel with a 30 pF capacitive load, exhibit an output impedance of no more than 50  $\Omega$ , and be capable of a 1 Vpp differential signal swing at frequencies of 1 MHz or less without distortion. In order to adhere to the goal of a low overall power dissipation for the circuit, a class AB complementary push-pull output stage was selected. The circuit diagram for each side of the mixer's differential output is shown in figure 4.2

Figure 4.2: Class AB Complementary Push-pull Output Stage

The base of transistor Q9 is connected to one of the differential outputs of the mixer stage as shown in figure 4.1. This transistor acts as an emitter follower