#### Lehigh University Lehigh Preserve

Theses and Dissertations

1989

# The development of a merged bipolar-CMOS technology

Joseph R. Radosevich *Lehigh University*

Follow this and additional works at: https://preserve.lehigh.edu/etd Part of the <u>Electrical and Computer Engineering Commons</u>

#### **Recommended** Citation

Radosevich, Joseph R., "The development of a merged bipolar-CMOS technology" (1989). *Theses and Dissertations*. 5239. https://preserve.lehigh.edu/etd/5239

This Thesis is brought to you for free and open access by Lehigh Preserve. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of Lehigh Preserve. For more information, please contact preserve@lehigh.edu.

# THE DEVELOPMENT OF

# A MERGED

# **BIPOLAR - CMOS TECHNOLOGY**

by

Joseph R. Radosevich

A Thesis

Presented to the Graduate Committee

٠,

of Lehigh University

in Candidacy for the Degree of

Master of Science

2

...

in

Electrical Engineering

(

Lehigh University

1989

Certificate of Approval

This thesis is accepted and approved in partial fulfillment of the requirements for the degree of Master of Science.

Ł

n . . Il 14. (date)

~

÷

З¥

¢.

Ð

-7. -7.

•

Mum.

Professor in Charge

Lawrence & Varierin

в,

Chairman of Department

- ii -

# CONTENTS

.

|    | ABSTRACT                                      |   |

|----|-----------------------------------------------|---|

| 1. |                                               |   |

|    | 1.1 Background                                | 2 |

|    | 1.2 Historical Review Of BiCMOS               | 3 |

|    | 1.3 Purpose Of The Work                       | 6 |

| 2. | THEORY AND MODELING OF THE BIPOLAR TRANSISTOR | 7 |

|    | 2.1 Uniformly Doped Transistor                | 7 |

٩

•

.

|    | 2.2         | Kecc  | mbinati     | on The   | югу     | •          | •    | •   | •    | • | • | ٠ | • | • | • | • | •  | • | ٠         | •        | •      | • | • | 13 |

|----|-------------|-------|-------------|----------|---------|------------|------|-----|------|---|---|---|---|---|---|---|----|---|-----------|----------|--------|---|---|----|

|    | 2.3         | Emit  | ter Effic   | iency    | •       | •          | •    | •   | •    | • | • | • | ٠ | • | • | • | •  | • | •         | •        | •<br>• | • | • | 15 |

|    | 2.4         | Forw  | ard-Acti    | ve Cu    | rrent   | Gair       | n    | •   | •    | • | • | • | • | • | • | • | ٠  | • | •         | •        | •      | • | • | 16 |

|    | 2.5         | Grad  | ed Base     | Transi   | stor    | •          | •    | •   | •    | • | • | ٠ | • | • | • | • | •  | • | •         | •        | •      | ٠ | • | 19 |

| 3. | EX          | PERIN | <b>ENTS</b> | ••       | •       | •          | •    | •   | •    | • | • | ٠ | • | • | • | • | •  | • | •         | •        | •      | • | • | 23 |

|    | 3.1         | СМО   | S FABF      | NICAT    | ION     | •          | •    | •   | •    | • | • | • | • | • | • | • | •  | • | l;<br>● · | •        | •      | • | • | 23 |

|    | 3. <b>2</b> | Deten | minatior    | of Ba    | ase Pa  | aran       | nete | ers |      | • | • | • | ٠ | • | • | ٠ | €: | • | •         | •        | •      | • | • | 29 |

|    | 3.3         | Manu  | facturing   | g Diffic | culties | <b>3</b> . | •    | •   | •    | • | ٠ | • | • | • | • | • | •  | • | •         | •,*<br>× | •      | ٠ | • | 47 |

|    | 3.4         | Deten | nination    | Of Ne    | w Ba    | ise I      | Para | amo | eter | 2 | • | • | • | • | • | • | •  | ٠ | •         | •        | •      | • | • | 60 |

|    |             |       |             |          |         |            |      |     |      |   |   |   |   |   |   |   |    |   |           |          |        |   |   |    |

.

- iii -

¥

| 4. | CONCL | LUSI | ON | S | • | • | ٠ | • | ٠ | • | • | • | ٩ | • | • | • | • | ٠ | • | • | • | • | • | • | • | 64 |

|----|-------|------|----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----|

|    | VITA  | ••   | •  | • | • | • | • | • | • | • | • | ٠ | • | • | • | • | ٠ | • | • | ٠ | • | • | • | • | • | 70 |

| RE | FEREN | CES  | •  | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | ٠ | • | • | • | 0 | • | 71 |

.

•

.

· \* \*

ι,

.

.

# LIST OF FIGURES

| Figure 1  | . (a) A diagram of a bipolar transistor showing two pri junctions spaced W  |    |

|-----------|-----------------------------------------------------------------------------|----|

|           | units apart                                                                 | 7  |

| Figure 2. | Semilogarithmic plot of collector current versus base-emitter voltage for a |    |

|           | forward-active biased npn transistor <sup>[27]</sup>                        | 12 |

| Figure 3. | Measured collector and base currents plotted as a function of base-emitter  |    |

|           | voltage <sup>[27]</sup>                                                     | 14 |

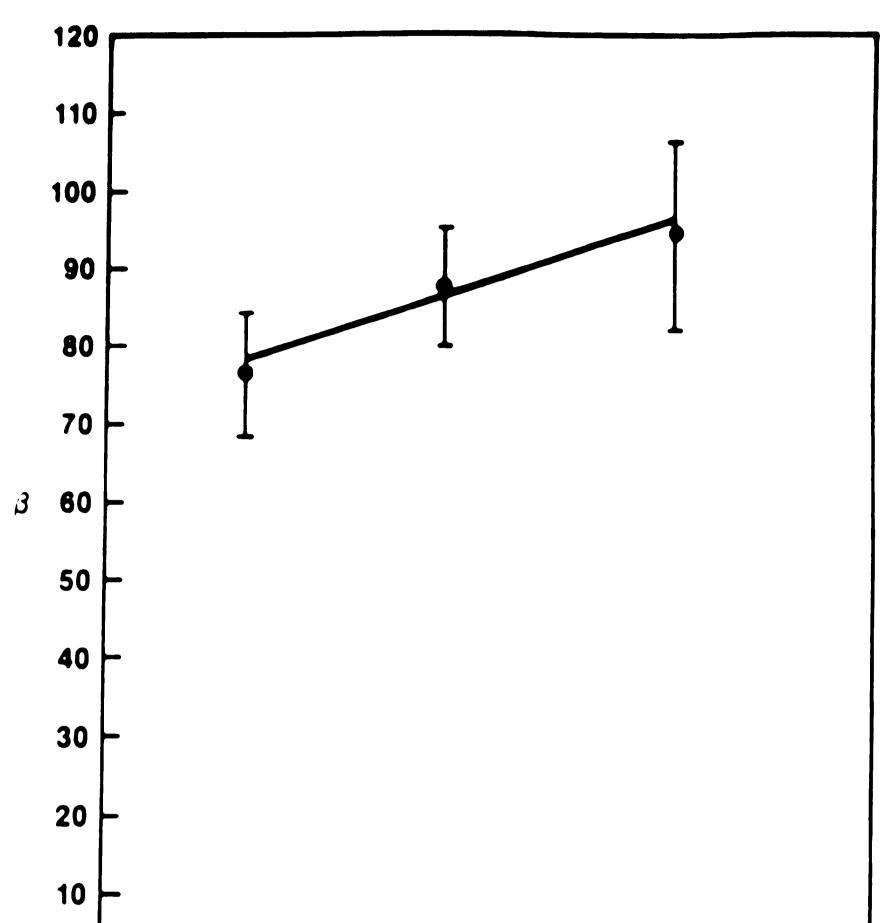

Figure 4. Common-emitter current gain versus the inverse of the base implant dose for

| e alle ouse implait dose foi |  |

|------------------------------|--|

|                              |  |

|           | all implanted transistors <sup>[31]</sup>                                                       |

|-----------|-------------------------------------------------------------------------------------------------|

| Figure    | 5. Forward active current gain ( $\beta_F$ ) as a function of collector current <sup>[27]</sup> |

|           | • • • • • • • • • • • • • • • • • • • •                                                         |

| Figure    | 6. Mask 1: <i>n</i> -tub formation                                                              |

| Figure    | 7. Mask 2: Active gate region definition                                                        |

| Figure 8  | 8. Mask 3: Phosphorus channel-stop implant                                                      |

| Figure 9  | <b>Mask 4: Gate definition</b>                                                                  |

| Figure 10 | Mask 5: <i>n</i> -channel source/drain formation                                                |

|           |                                                                                                 |

.

·ə

• .

\*

, ,

| Figure 11. | Mask 6: Contact window formation                                                                                                                  | 27  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 12. | Mask 7: Metal interconnections formed                                                                                                             | 28, |

| Figure 13. | Mask 8: Encapsulation - completed device                                                                                                          | 28  |

| Figure 14. | A plot of current gain versus the reciprocal of the base implant dose for the                                                                     |     |

|            | experimental cells of the second wafer lot                                                                                                        | 36  |

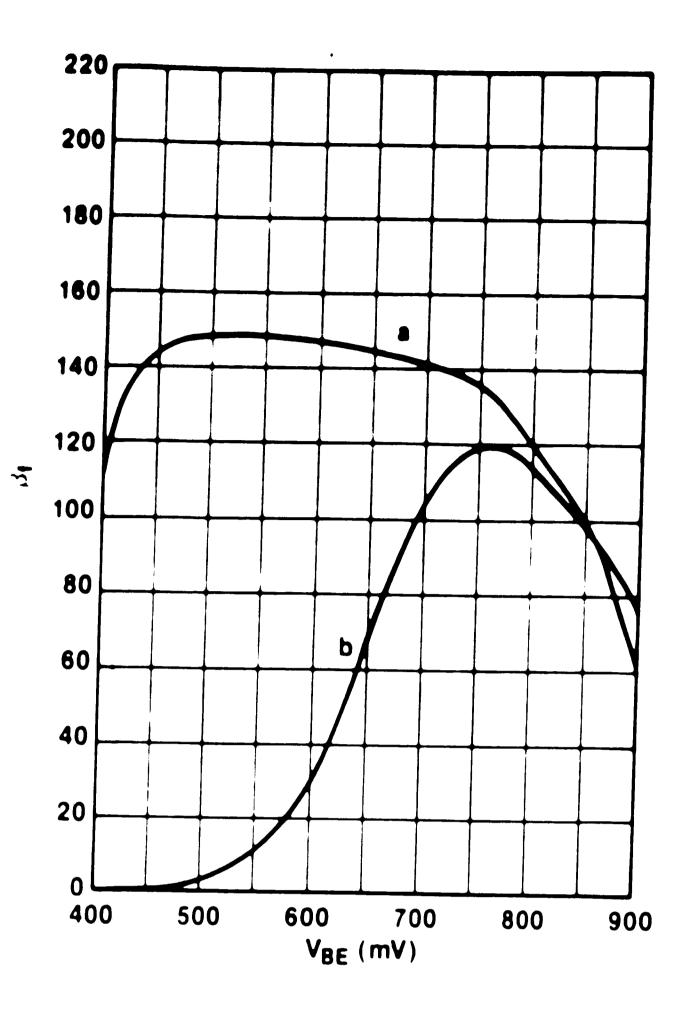

| Figure 15. | $\beta_f$ versus base-emitter bias (V_{BE}) of the bipolar transistor for the active base                                                         |     |

|            | implant conditions a) $3.0 \times 10^{14}$ cm <sup>-2</sup> b) $3.3 \times 10^{14}$ cm <sup>-2</sup> c) $3.7 \times 10^{14}$ cm <sup>-2</sup> and |     |

|            | d) $4.0 \times 10^{14}$ cm <sup>-2</sup> . The emitter size is $4.75 \mu m \times 4.75 \mu m$                                                     | 39  |

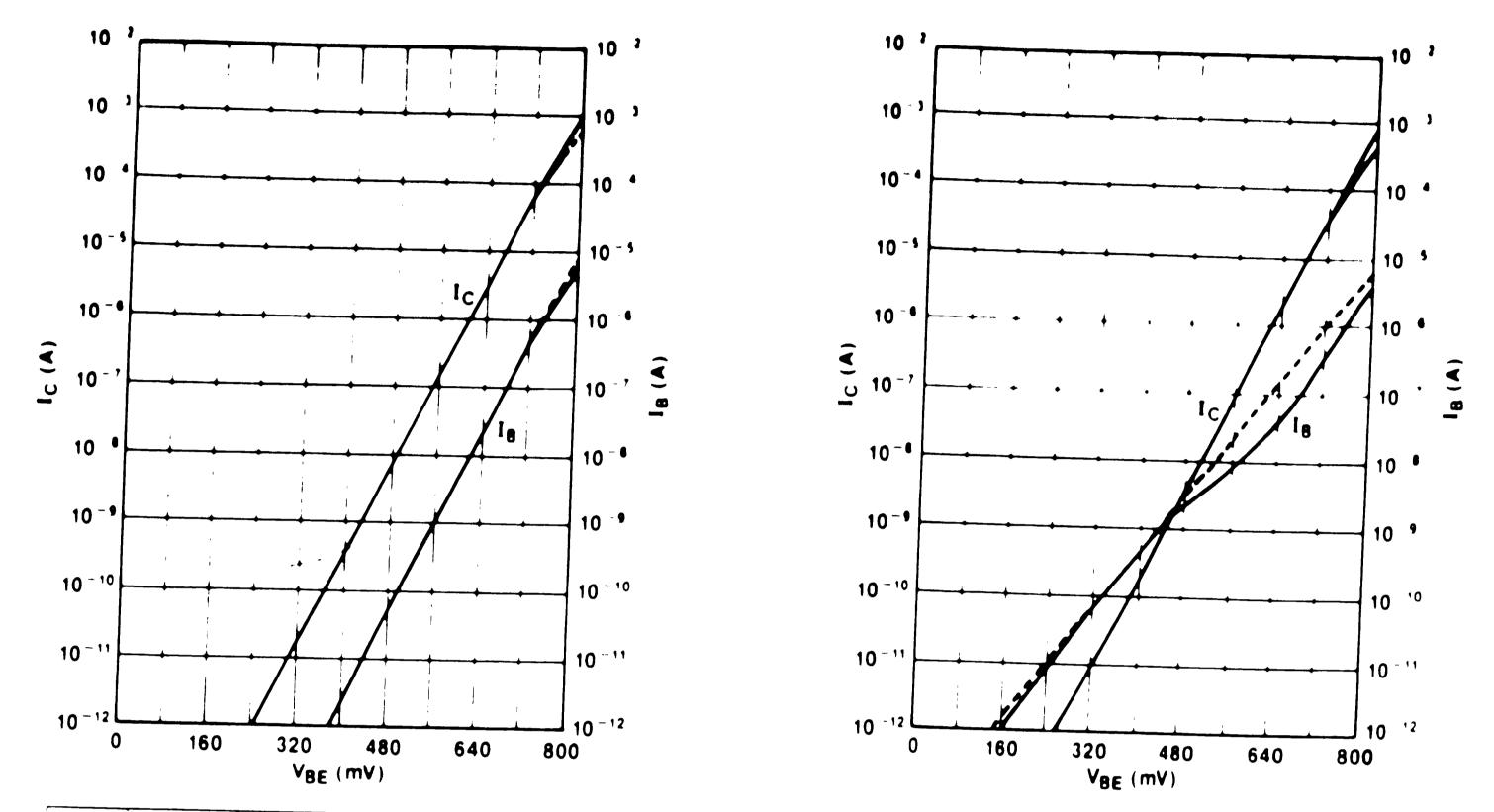

Figure 16. Collector current  $I_C$  and base current  $I_B$  versus base-emitter voltage  $V_{BE}$  for

|            | a bipolar transistor with an active base doping of a) $3.0 \times 10^{14}$ cm <sup>-2</sup> b)                                                    |          |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|            | $3.3 \times 10^{14}$ cm <sup>-2</sup> c) $3.7 \times 10^{14}$ cm <sup>-2</sup> and d) $4.0 \times 10^{14}$ cm <sup>-2</sup> . The emitter size is |          |

|            | 4.75μm ×4.75μm                                                                                                                                    | 0        |

| Figure 17. | A plot of the total hole charge in the quasi-neutral base region $Q_{B0}$ / qA                                                                    |          |

|            | versus base implant dose                                                                                                                          | 2        |

| Figure 18. | A plot of common-emitter current gain versus base doping in the quasi-                                                                            |          |

|            | neutral base region $Q_{B0}$ / qA for the measured wafers from the second                                                                         |          |

|            | experimental lot                                                                                                                                  | <b>}</b> |

|            | -                                                                                                                                                 |          |

.

.

. × .

.

-

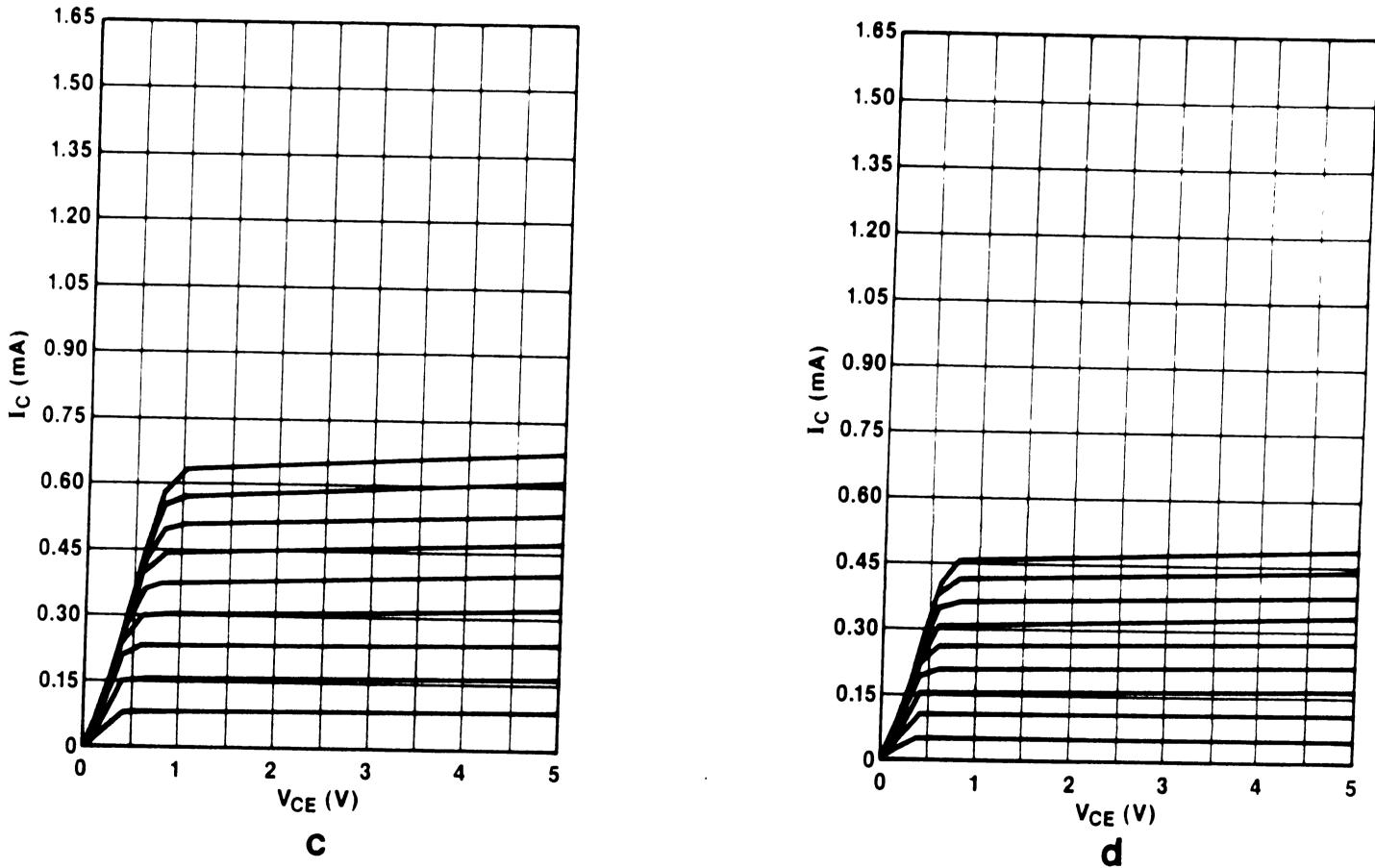

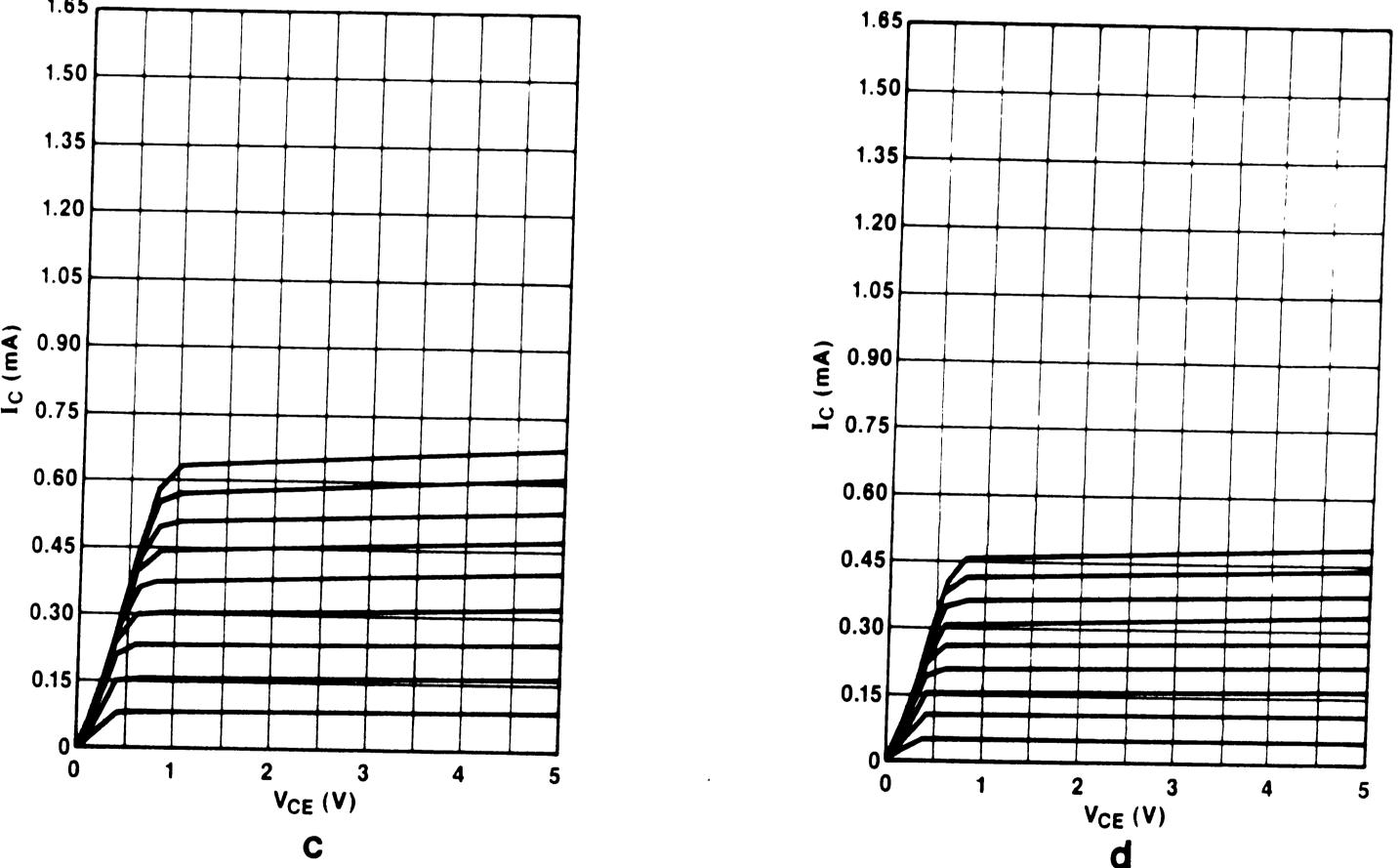

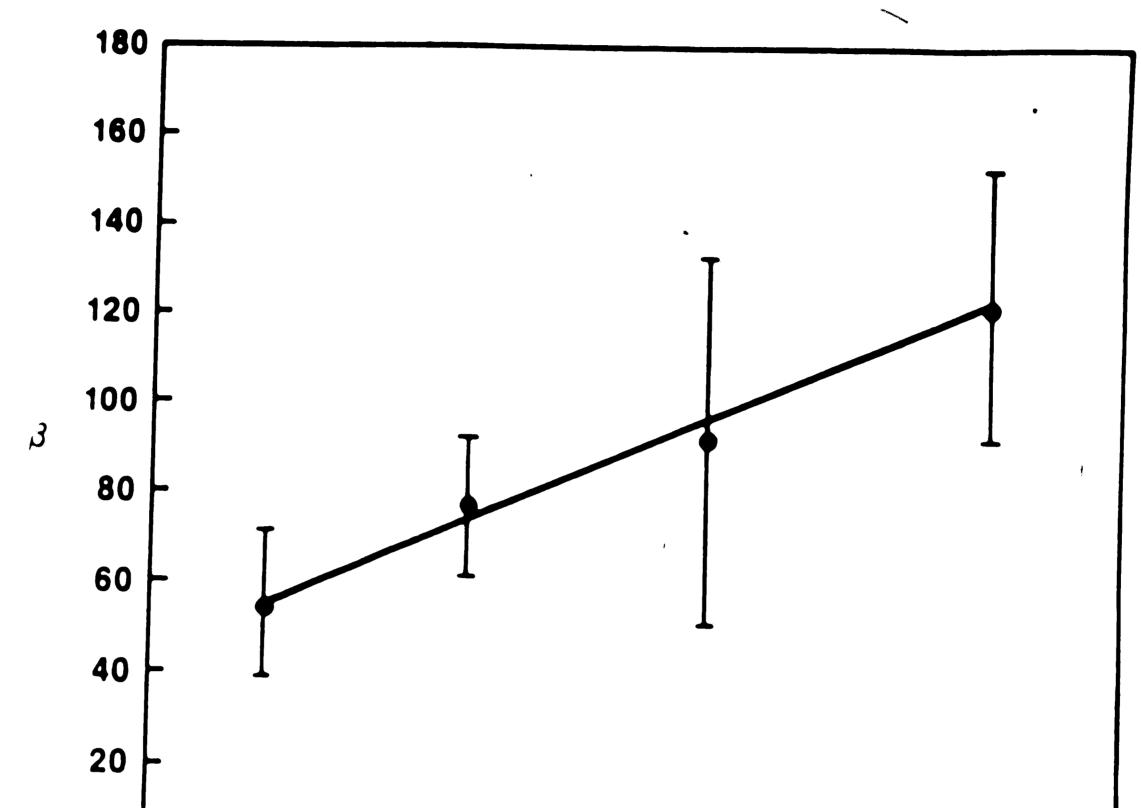

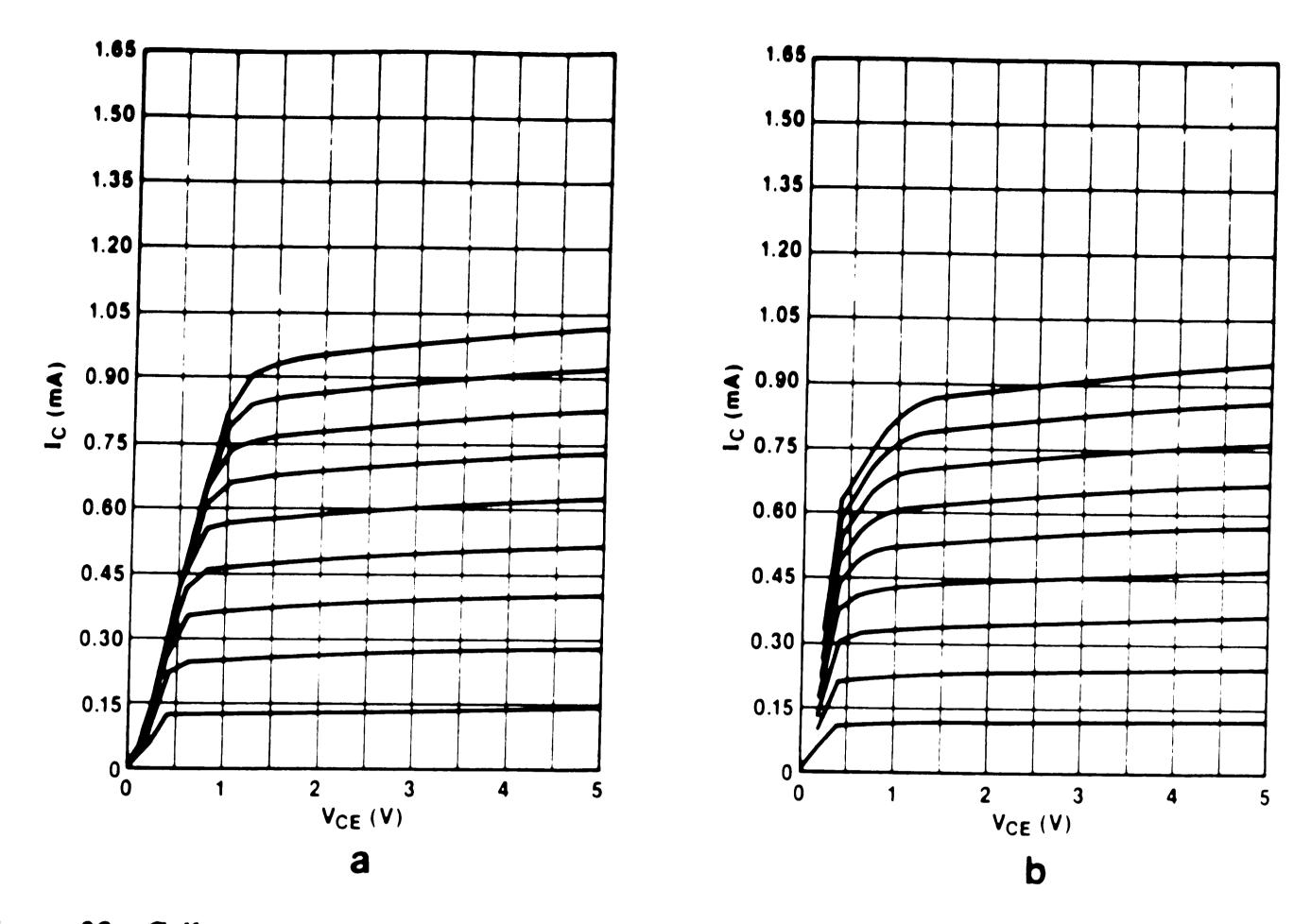

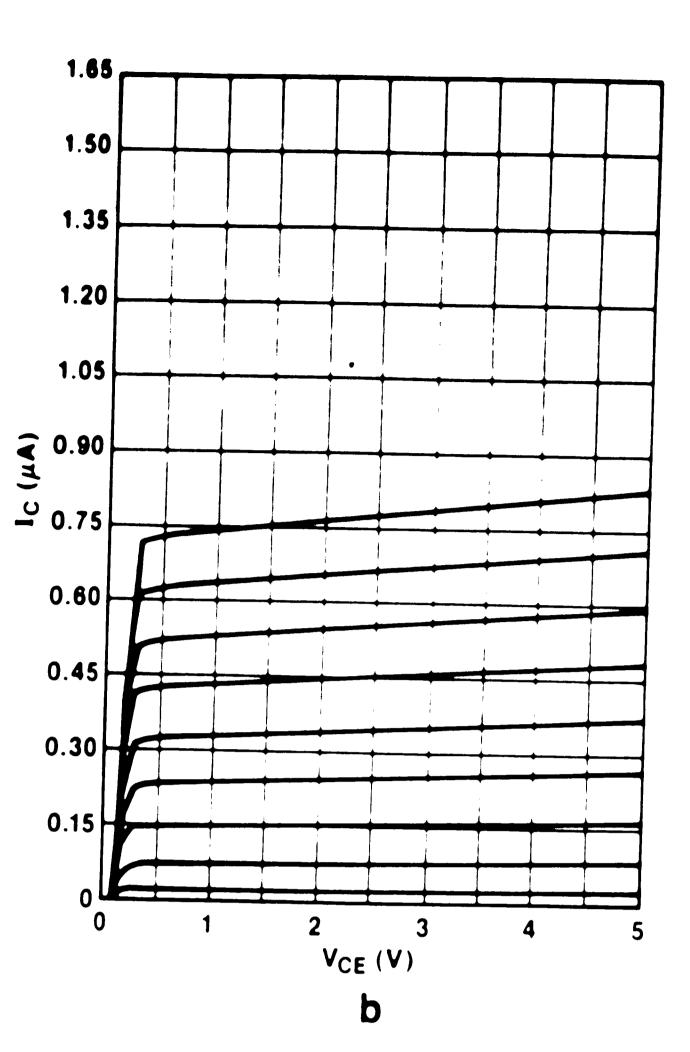

| Figure 19. Collector current $I_C$ versus collector voltage $V_{CE}$ for a bipolar transistor with                                 |

|------------------------------------------------------------------------------------------------------------------------------------|

| an active base doping of a) $3.0 \times 10^{14}$ cm <sup>-2</sup> b) $3.3 \times 10^{14}$ cm <sup>-2</sup> c) $3.7 \times 10^{14}$ |

| cm <sup>-2</sup> and d) $4.0 \times 10^{14}$ cm <sup>-2</sup> . $I_B = 1.0 \mu A$ per step, 9 steps, the emitter size is           |

| 4.7 <b>5μm ×4.75μm </b>                                                                                                            |

| Figure 20. A plot of gain versus reciprocal base implant dose for the experimental cells                                           |

| of wafer lot number three                                                                                                          |

| Figure 21. $\beta_f$ versus base-emitter bias (V <sub>BE</sub> ) for two devices with the same processing                          |

| conditions a) a device with near ideal characteristics b) a device with                                                            |

,

₽**₩**

. •

•

÷

.

ی ب

|            | significant base recombination current.                                                 | 48 |

|------------|-----------------------------------------------------------------------------------------|----|

| Figure 22. | Collector current $I_C$ and base current $I_B$ versus base-emitter voltage $V_{BE}$ for |    |

|            | a bipolar transistors with a) near ideal characteristics and b) exhibiting large        |    |

|            | recombination components                                                                | 9  |

| Figure 23. | Collector current $I_C$ versus collector voltage $V_{CE}$ for bipolar transistors with  |    |

|            | a) near ideal current-voltage characteristics and b) significant base                   |    |

|            | recombination current. Base current $I_B = 1.0\mu A$ to 9.0 $\mu A$ , 1.0 $\mu A$       |    |

F . . • .

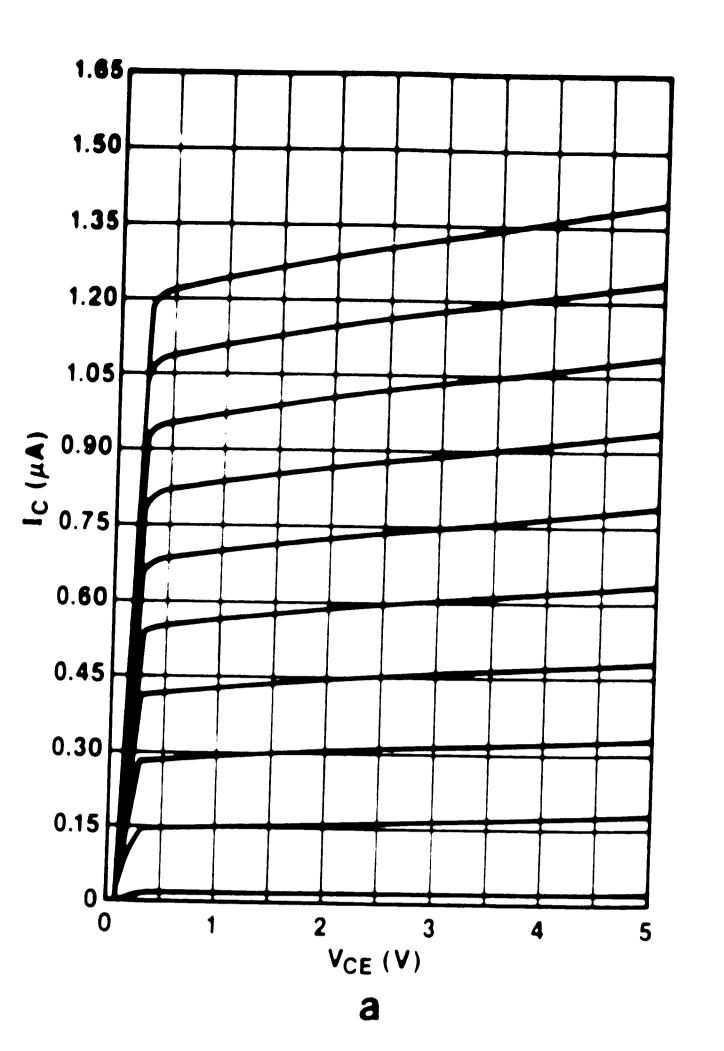

Figure 24. Collector current  $I_C$  versus collector voltage  $V_{CE}$  for bipolar transistors with

a) near ideal current-voltage characteristics and b) significant base

recombination current. Base current  $I_B = 1.0nA$  to 91nA, 10nA.

| steps. | • | • | • | • | • | ٠ | • | • | • | ٠ | • | • | • | ٠ | • | • | • | • | ۱. | • | ë, | • | 54 |

|--------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----|---|----|---|----|

|--------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----|---|----|---|----|

Figure 25. A plot of current gain versus 1 / base implant dose for the no phosphorus and

| poly0 drive experiment | • | ٠ | ٠ | • |  | • | • | • | • | • | • | ٠ |  | • | ٠ | Þ | • | 65 |

|------------------------|---|---|---|---|--|---|---|---|---|---|---|---|--|---|---|---|---|----|

|------------------------|---|---|---|---|--|---|---|---|---|---|---|---|--|---|---|---|---|----|

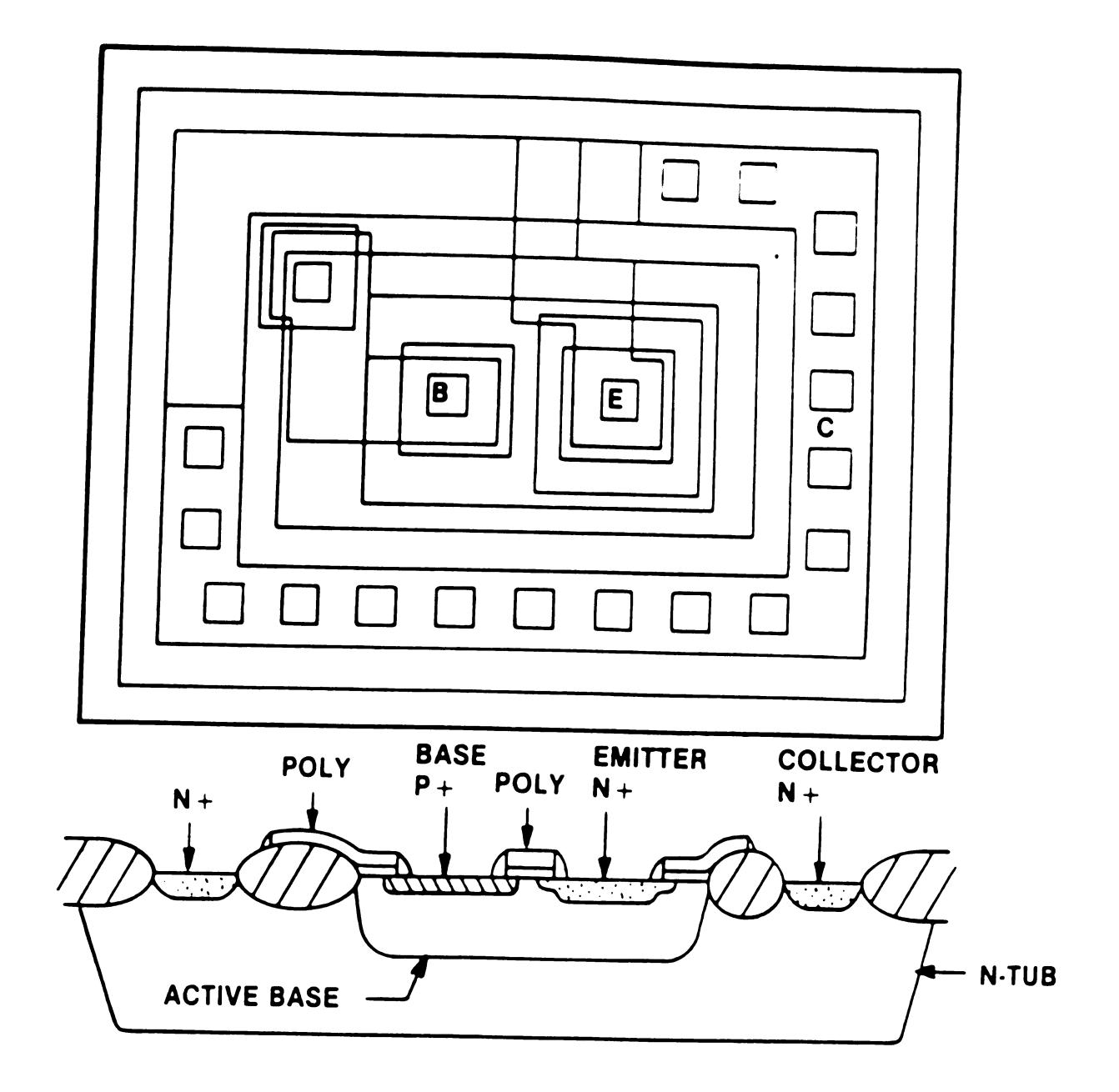

| Figure 26. | A layout and | cross-section of a npn transist | r. | • | ٠ | ÷ | • | • | • | ٠ | • | • | 66 |

|------------|--------------|---------------------------------|----|---|---|---|---|---|---|---|---|---|----|

|------------|--------------|---------------------------------|----|---|---|---|---|---|---|---|---|---|----|

-

,

. . .

ý . .

i

۲۰۰۰ ب

## LIST OF TABLES

| TABLE 1  | Critical dimensions of the Twin-Tub III CMOS technology                     | :3 |

|----------|-----------------------------------------------------------------------------|----|

| TABLE 2  | Key parameters of the Twin-Tub III CMOS technology                          | 9  |

| TABLE 3. | Proposed flow of the Twin-Tub III BiCMOS technology                         | 0  |

| TABLE 4. | Test results from the first experimental wafer lot - base drive-in at 900°C |    |

|          | for 60 min                                                                  | \$ |

|          |                                                                             |    |

TABLE 5. Test results from the second experimental wafer lot - base drive-in at 900°C

.

**N**\_\_

•

|          | for 60 min                                                                          |

|----------|-------------------------------------------------------------------------------------|

| TABLE 6. | Measurements of forward active current gain ( $\beta_f$ ), collector current slope, |

|          | and $I_S$ with calculated values of $Q_{B0}$ / qA for each base implant dose of the |

|          | second experimental wafer lot                                                       |

| TABLE 7. | Test results from the third experimental lot - base drive-in at 900°C for 60        |

|          | min                                                                                 |

| TABLE 8. | Gain and gain versus collector current density for the experimental cells of        |

|          | wafer lot number four - base dose $2.8 \times 10^{14}$ cm <sup>-2</sup>             |

|          |                                                                                     |

.

1

• • . . a. . • .

| TABLE 9   | . Gain and gain versus collector current density for the experimental cells of   |   |

|-----------|----------------------------------------------------------------------------------|---|

|           | wafer lot number five - base dose $3.2 \times 10^{14}$ cm <sup>-2</sup>          | 5 |

| TABLE 10. | Gain and gain versus collector current for the experiments on wafer lot          |   |

|           | number six                                                                       | ) |

| TABLE 11. | Gain and gain versus collector current for the experiments investigating $\beta$ |   |

|           | fall-off on wafer lot number seven 61                                            |   |

| TABLE 12. | Bipolar transistor characteristics of the no phosphorus and no phosphorus        |   |

|           | poly0 drive experiment                                                           |   |

TABLE 13. Final process flow of the Twin-Tub III BiCMOS technology . . . . . 67

• • . • • •

- X -

>

ж.,

N

.

$\overline{}$

, ;

#### ABSTRACT

۹.

A process merging a bipolar transistor with an existing CMOS technology is described. With the development charter specifying that there be no modifications to the existing CMOS process parameters, there were many constraints placed on the development of the integrated process. Computer simulations were performed, test patterns created and experiments designed to determine the proper bipolar parameters. By settling for a moderate performance *npn* bipolar transistor, however, the number of added processing steps was minimized and a low cost manufacturable product achieved.

The key factors of this process include using the CMOS *n*-tub as the collector of the bipolar transistor, implanting boron into the collector and driving it in to form the base and using the CMOS source/drain implants for the emitter and  $n^+$ -contact to the collector. Contact

to the active base diffusion is formed concurrently with the source/drain boron diffuoride implant of the *p*-channel transistors. The tantalum silicide/*n*-polysilicon CMOS gate structure is used as a spacer to separate the  $n^+$ -emitter from the  $p^+$ -base contact. To guard against emitter to collector punch-through, the silicide/gate oxide spacer is also used to separate the  $n^+$ -emitter from the heavy channel stop doping under the collector field oxide. Although transistors were fabricated with common-emitter dc current gains in the range of 50-100 with acceptable break-down voltages, a problem with decreased gain at small collector currents was observed on many devices. To overcome this effect, it was experimentally determined that an additional mask step was required to block out the CMOS phosphorus graded junction implant from the bipolar emitter structure.

### I. INTRODUCTION

#### 1.1 Background

Combining high performance bipolar and MOS transistors on the same integrated circuit is attractive to the VLSI designer. MOS transistors maintain an edge in packing density and the ability to integrate large complex functions with high yields. CMOS circuits have the additional advantage of low power dissipation and large noise margins. The bipolar transistor has an advantage in switching speed, better noise performance, superior analog performance and greater current drive per unit area than an MOS transistor.

Optimization of MOS transistors implies reducing gate oxide thicknesses, junction depths, polysilicon or polycide sheet resistance and gate lengths, lower process temperatures and more stringent lithographic capabilities. These trends are consistent with bipolar VLSI technology. For enhanced bipolar performance, polysilicon emitters, walled emitters, Schottky diodes and thin epitaxy with buried layers are necessary components. A common need of both technologies is a high density multilayer interconnect scheme.

By judiciously mixing the two technologies, the performance of high speed digital/analog systems can exceed circuits based on either technology alone. As many of the features distinguishing bipolar and MOS technologies are becoming less distinct in VLSI, the advantage of having both transistors on the same integrated circuit will increase. Thus, there has been a great deal of interest shown in the combined bipolar-CMOS process usually known as BiMOS or BiCMOS.

The BiCMOS technology has begun to be used widely in many kinds of integrated circuits ranging from linear ICs, Power ICs <sup>[1]</sup> and analog-digital mixed LSIs <sup>[2]</sup> <sup>[3]</sup> to high speed digital VLSIs. High speed low power logic and memory applications include high speed gate arrays, <sup>[4]</sup> <sup>[5]</sup> microprocessors and static RAMs.<sup>[6]</sup> <sup>[7]</sup> While the speed of BiCMOS circuits can come close to that of bipolar ECL devices, the power consumption remains at a level similar to

a CMOS device. BiCMOS is, therefore, regarded as a suitable technology for realizing both high speed and high density at the same time.

The first 2.0µm design rule BiMOS products, with twice the speed advantage over CMOS, appeared on the market place in 1985. It was two years after 2.0µm CMOS but one year ahead of the next generation, 1.3µm CMOS products. The first 1.3µm BiCMOS products were introduced in 1987 with CMOS products of the same performance expected in 1990. [5] BiCMOS can smooth cycles in the integrated circuit industry by working between new generation CMOS introductions. It may provide a way to increase circuit performance without shrinking process design rules and thereby extend the the life of each CMOS technology.

# 1.2 Historical Review Of BiCMOS

۸,

As early as 1968, merged CMOS and bipolar devices had been proposed and a paper published by Lin .et.al.<sup>[8]</sup> In this early attempt, common-collector npn transistors were fabricated using a diffused  $n^+$  source-drain region as emitter, a diffused  $p^-$  isolation region as a base and a  $n^-$  substrate as a collector. With the common-collector bipolar transistor being unsuitable for many circuit applications, the approach did not progress.

Two paths of technology integration were then pursued. One approach involved adding CMOS capability into existing bipolar processes.<sup>[9]</sup> [10] These technologies involved epitaxial layers and isolations so that process complexity is too high and circuit density too low for large-scale integration.<sup>[11]</sup> Since a relatively thick epitaxial layer is used to admit the deep well diffusion of the CMOS process, the cut-off frequency  $(f_t)$  of the bipolar transistor is also compromised.

A more attractive solution to the compatibility problem of MOS and bipolar transistors was offered when a CMOS extension of NMOS technology was demonstrated by utilizing a lightly doped p-type substrate and placing the p-channel transistors into an n-well.<sup>[12]</sup> [13] Tripple-

3

•

diffused, self-isolated bipolar transistors using the *n*-well as the collector were described for this process by Black .et.al<sup>[12]</sup> in 1976 but unfavorable tradeoffs between device parameters were necessary. Some of these problems were resolved by Hoefflinger .et.al <sup>[14]</sup> in a later fully ion implanted process with a two-step implanted base. The two-step implanted base, one for the active base with low dose and the other with low energy and high dose for the inactive base, was introduced to allow the independent adjustment of the bipolar transistor parameters. With a strong forward-active gain ( $\beta_f$ ) dependence on collector current, limited active base profile optimization and large device geometries associated with these technologies, efforts continued to achieve better bipolar characteristics.

These approaches to BiCMOS technology are oriented to fabricating bipolar transistors in CMOS LSI's without drastically changing the CMOS processes they are based upon. <sup>[3]</sup> <sup>[15]</sup> <sup>[16]</sup> <sup>[17]</sup> <sup>[18]</sup> By using the *n*-MOS threshold adjust step as the bipolar base implant, Momose .et.al <sup>[15]</sup> and Miyamoto .et.al<sup>[16]</sup> developed technologies which do not require any additional processing or mask steps to fabricate the bipolar transistor. Zeitzoff .et.al <sup>[18]</sup> uses the  $p^+$  source and drain implant to act as the base dopant, again manufacturing a bipolar transistor with the addition of no extra processing steps. Yue .et.al <sup>[17]</sup> and Reich .et.al <sup>[3]</sup> used an active-base photomask to mask the active area of the *npn* transistor. While adding additional steps to the process, this enhancement allows adjustment of the bipolar transistor parameters independently from the CMOS parameters.

In order to improve MOS LSI drive ability and speed, CMOS LSI's began adopting these bipolar transistors in special circuits such as output drivers and sense amplifiers. Having bipolar transistors with wide base widths and large collector resistance restrains the performance with respect to maximum collector current and cut-off frequency and is poor in comparison with that of bipolar LSIs. As a result, circuit performance itself had not shown remarkable improvement.<sup>[19]</sup>

Δ

With performance of earlier BiCMOS being dominated by the individual characteristics of bipolar drivers and CMOS logic circuits, its applications had been limited to specific fields. High performance BiCMOS opens new fields by placing bipolar and CMOS devices on the same chip in an uncompromised form and combining them in unit circuits rather than limited to separate areas of the chip.

High performance BiCMOS technologies were introduced as CMOS processes moved below 2.0µm design rules. Epitaxial structures were generally adopted and the addition of a buried layer to the BiCMOS process was introduced by Walczyk .et.al <sup>[20]</sup> and Momose .et.al. <sup>[6]</sup> This was immediately followed by integrating these features with the twin-well CMOS process by Kobayashi .et.al.<sup>[21]</sup> Watanabe .et.al <sup>[22]</sup> and Ikeda .et.al <sup>[23]</sup> further extended the bipolar transistor optimization with the addition of polysilicon emitters.

To increase the operating speed and high integration even further, scaling down of the BiCMOS devices into the submicron range is desirable. Based on a  $0.8\mu$ m twin-well CMOS processes, the first submicron BiCMOS processes were introduced in December, 1987 by Iwai .et.al <sup>[24]</sup> and Havemann .et.al <sup>[7]</sup> In the first technology, an ion-implanted emitter was chosen to minimize the production cost and limit the additional mask count to three.<sup>[24]</sup> By optimizing the bipolar transistor, sufficiently high performance for BiCMOS gates was obtained. The second process requires an extra mask count of four but has a polysilicon emitter for improved bipolar performance.

There was some concern that in scaling further down to half-micron dimensions, BiCMOS could loose its advantage of higher driving capability relative to CMOS. In a study by Momose .et.al, <sup>[25]</sup> a scaled 0.5 $\mu$ m BiCMOS was fabricated with electron beam lithography. It generally follows the trend of earlier processes with three additional mask steps and ion implantation for the  $n^+$  buried layer, collector contact and active base regions. The feasibilities and capabilities of the process were evaluated in terms of device characteristics and

.

propagation delay time of ring oscillators. This data indicates BiCMOS is still effective at a half micron technology. With a load of 1.0pf they found the BiCMOS delay time to be 66% of that of pure CMOS.

Although BiCMOS has evolved into the sub-micron range, processes based on the evolution of a CMOS process generally produce bipolar devices that are greatly inferior to the state of the art super self-aligned bipolar device. Chiu .et.al <sup>[26]</sup> describe a non-overlapping super self-aligned structure that is optimal for both MOS and bipolar. Their approach realizes high speed by minimizing parasitic capacitances and resistance. Source/drain and emitter/extrinsic base junctions are formed and contacted by doped polysilicon, thin epi grown on arsenic buried layer and a fully recessed oxide isolation scheme are additional features of the technology.

1.3 Purpose Of The Work

There has been a demonstrated commitment to BiCMOS technologies observed in the literature. The advantages to having bipolar and CMOS transistors on the same integrated circuit chip have been noted.

A process merging a *npn* vertical transistor with the Twin Tub CMOS III technology will be described. Several minimum size bipolar transistor designs were developed, fabricated and used as a basis for a complete test chip. After the initial simulations and studies, experiments were performed to characterize and optimize the base parameters. A problem encountered with the performance of the bipolar transistor will be discussed.

The work presented in this thesis documents the development effort and process optimization performed to integrate a functional *npn* device into the Twin Tub III CMOS process.

### 2. THEORY AND MODELING OF THE BIPOLAR TRANSISTOR

## 2.1 Uniformly Doped Transistor

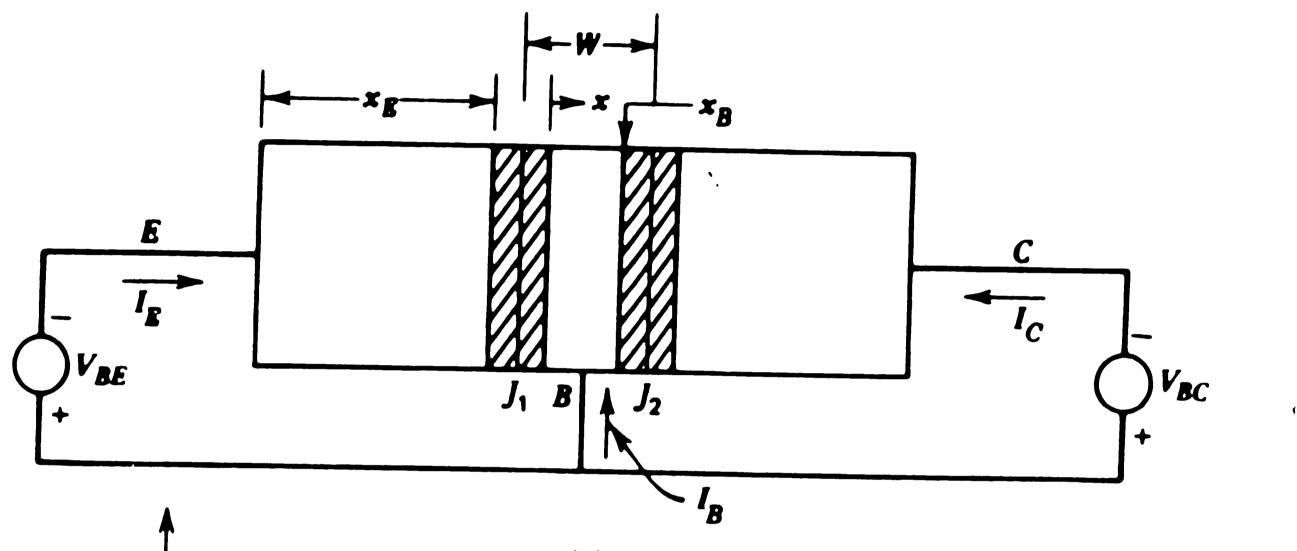

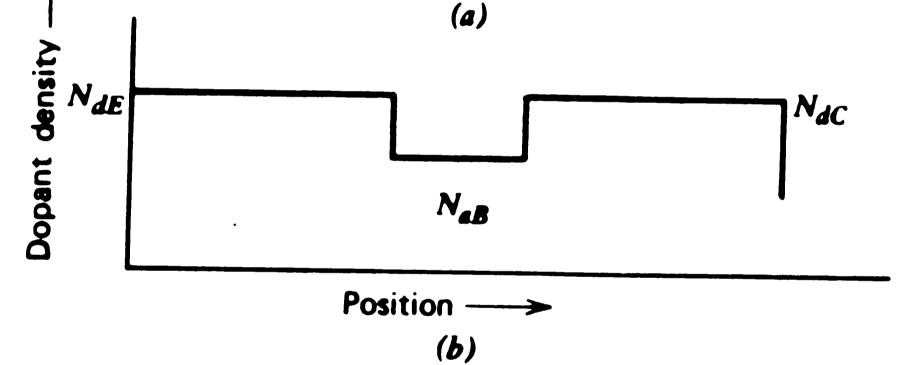

Figure 1<sup>[27]</sup> is a simple one dimensional realization of a structure showing the action of an npn bipolar transistor.

Figure 1. (a) A diagram of a bipolar transistor showing two pn junctions spaced W units apart (b) Doping density versus longitudinal position for the bipolar transistor above<sup>[27]</sup> "

A bar of semiconductor material with a cross-sectional area A is shown with two pn junctions spaced a distance W apart. W is small enough so that electrons injected across Junction 1 ( $V_{BE}$  positive) are in the vicinity of Junction 2 and the loss of electrons by recombination in the middle base region is minimal. It is also assumed that electron recombination or generation in the base region is not significant and there is a negligible flow of holes (base majority carriers) between the junctions into the base. Defining the longitudinal dimension as x, the expression for hole current in the x direction (assuming no recombination) can be written

$$J_{p} = 0 = q\mu_{p}pE_{x} - qD_{p}\frac{dp}{dx}$$

(1)

Solving for the electric field  $E_x$  gives

$$E_{x} = \frac{D_{p}}{\mu_{p}} \frac{1}{p} \frac{dp}{dx}$$

(2)

٠

by using the Einstein relationship

$$D_{p} = \left(\frac{kT}{q}\right)\mu_{p}$$

(3)

it can be written in the form

$$E_{x} = \frac{kT}{q} \frac{1}{p} \frac{dp}{dx}$$

(4)

This the built-in electric field from free carriers and fixed impurities.

The electron current is written

$$J_n = q\mu_n nE + qD_n \frac{dn}{dx}$$

(5)

From the earlier calculations of base current there is an expression for the electric field

$$E_{\mathbf{x}} = \frac{D_{\mathbf{p}}}{\mu_{\mathbf{p}}} \frac{1}{\mathbf{p}} \frac{d\mathbf{p}}{d\mathbf{x}}$$

(6)

Substituting for  $E_x$  in equation 5 then gives

.

$$J_n = kT\mu_n \frac{n}{p} \frac{dp}{dx} + qD_n \frac{dn}{dx}$$

(7)

By using the Einstein relationship the following expression for the current density is obtained.

•

$$J_{n} = \frac{qD_{n}}{p} \left[ n \frac{dp}{dx} + p \frac{dn}{dx} \right]$$

(8)

This can be expressed as

٠

1

$$J_{n} = \frac{qD_{n}}{p} \frac{d(pn)}{dx}$$

(9)

An integral form of the above equation is written with arbitrary limits x and x' and recombination treated as negligible so that  $J_n$  can be removed from the integral.

$$J_n \int_{x}^{x} \frac{p}{q} \frac{dx}{D_n} = \int_{x}^{x} \frac{d(pn)}{dx} dx$$

(10)

Since the right-hand side of the above equation is a perfect differential this can be written

$$J_{n} \int_{x}^{x} \frac{p}{q} \frac{dx}{D_{n}} = p(x')n(x') - p(x)n(x)$$

(11)

Using the junctions as boundaries of the regions then x = 0 becomes the lower limit and  $\dot{x} = x_B$  the upper limit of the integrals. The carrier densities at either side of a biased *pn* junction are dependent upon the applied voltage according to the relationship

$$pn = n_i^2 e^{\frac{qV_a}{kT}}$$

(12)

(13)

4

where  $V_a$  is the applied voltage. From this equation the *pn* products at the boundaries can then be related to the junction voltages.

$$p(0)n(0) = n_i^2 e^{\frac{q v_{BB}}{kT}}$$

$$p(\mathbf{x}_{\mathrm{B}})n(\mathbf{x}_{\mathrm{B}}) = n_{\mathrm{i}}^{2} \mathrm{e}^{\frac{\mathrm{q} V_{\mathrm{BC}}}{\mathrm{k} \mathrm{T}}}$$

9

Thus the electron current in the base can be expressed as a function of the junction voltages  $V_{BE}$  and  $V_{BC}$ .

$$J_{n} \int_{0}^{x_{B}} \frac{p}{q} \frac{dx}{D_{n}} = n_{i}^{2} \left[ e^{\frac{qV_{BC}}{kT}} - e^{\frac{qV_{BB}}{kT}} \right]$$

(14)

Rearranging terms, the following expression for electron current density is obtained.

$$J_{n} = \frac{qn_{i}^{2} \left( e^{\frac{qV_{BC}}{kT}} - e^{\frac{qV_{BB}}{kT}} \right)}{\int_{0}^{x_{B}} \int_{D_{n}}^{p} dx}$$

(15)

$D_n$  is frequently a weak function of position in the base and can be expressed as an average value  $D_n$  and removed from the integral in the denominator of the right-hand side of the last

equation. With  $D_n$  removed, the integral expresses the total majority-carrier charge in the base. Multiplying by qA will convert this density into the total majority carrier charge in the base. We now define the majority carrier charge in the base as  $Q_{B0}$ .

$$Q_{B0} = qA \int_{0}^{x_{B}} pdx$$

(16)

The electron current flowing from the first to the second junction can be expressed as

$$I_{n} = I_{S} \left[ e^{\frac{qV_{BC}}{kT}} - e^{\frac{qV_{BE}}{kT}} \right]$$

(17)

10

(18)

2

where

From equation 17 the relationship between the junction voltages and current is clearly seen.

The condition  $V_{BE}$  positive and  $V_{BC}$  zero or negative is known as forward-active bias for an *npn* transistor. This bias results in electron injection at the emitter-base junction and electron collection at the base-collector junction. With  $V_{BC}$  negative and  $V_{BE} \gg kT/q$  it is seen from equation 17 that an electron current of

$$I_n \approx -I_S e^{\frac{qV_{BB}}{kT}}$$

(19)

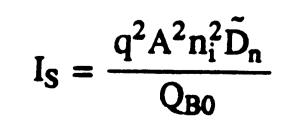

will flow from left to right across the collecting junction  $J_2$  of figure 1. Equation 19 shows that under forward-active bias conditions, collector current is exponentially related to emitter-base voltage. Experimentally, this relationship is found to hold over many decades of collector current. Figure 2 <sup>[27]</sup> shows a logarithmic plot of the collector current  $I_C$  as a function of the base-emitter bias  $V_{BE}$ . The intercept of an extrapolated line drawn through the collector current measurements with the current axis at  $V_{BE} = 0$  yields a value for  $I_S$  in equation 19. Once  $I_S$  is known, the built-in base charge in the quasi-neutral region can be obtained from equation 18 since all the other parameters are known.

$Q_{B0}$  represents the total hole charge in the quasi-neutral base as the base-emitter bias tends to zero and is given by

$$Q_{B0} = \frac{q^2 A^2 n_i^2 \tilde{D}_n}{I_S}$$

(20)

This charge is built in during processing of the transistor.

Determining a value of  $Q_{B0}$  through current-voltage measurements on the transistor was first described by H. K. Gummel<sup>[28]</sup>. The number of base dopant atoms (per cm<sup>2</sup>) in the quasi-neutral region given by

Figure 2. Semilogarithmic plot of collector current versus base-emitter voltage for a forwardactive biased *npn* transistor <sup>[27]</sup>

$$\int_{0}^{x_{B}} N_{a}(x) dx = \frac{Q_{B0}}{qA} = \frac{qAn_{i}^{2} D_{n}}{I_{S}}$$

(21)

is often referred to as the *Gummel* number. Equation 21 shows that  $I_S$ , the multiplying factor for transistor current at a given bias, is inversely proportional to the Gummel number, or total base doping. The lower the total base doping, the higher is the current at a given bias. Control of  $Q_{B0}$  during processing is of primary concern in obtaining reproducible transistor characteristics.

#### 2.2 Recombination Theory

Recombination in the base-emitter space-charge region can account for added base-emitter current observed at low biases. The equations describing generation and recombination in the space-charge zone through localized states or recombination centers were originally described by Shockley and Reed <sup>[29]</sup> and by Hall <sup>[30]</sup>. The process is referred to frequently as Shockly, Read, Hall (SRH) recombination. From their analysis, an equation describing the recombination current J<sub>r</sub> can be written

$$J_{r} \approx \frac{q \mathbf{x}' \mathbf{n}_{i}}{2\tau_{0}} e^{\frac{q \mathbf{v}_{a}}{2\mathbf{k}T}}$$

(22)

4

where  $\tau_0 = 1 / N_t \sigma v_{th}$ , the distance x' is a portion of the space-charge region thickness  $x_d$  and  $V_a$  is an applied bias.  $\tau_0$  is the lifetime associated with the recombination of excess carriers in

a region with a density  $N_t$  of recombination centers. From this equation it is seen that the current arising from recombination in the space-charge region varies with applied voltage as  $e^{\frac{qV_a}{2kT}}$ . Assuming x' is a weak function of voltage, it can be approximated by the entire space-charge region width  $x_d$ . With this approximation, the ratio between the ideal diode current  $J_t$

$$J_{t} = qn_{i}^{2} \left[ \frac{D_{p}}{N_{d}L_{p}} + \frac{D_{n}}{N_{a}L_{n}} \right] \left[ e^{\frac{qV_{a}}{kT}} - 1 \right] = J_{0} \left[ e^{\frac{qV_{a}}{kT}} - 1 \right]$$

(23)

and the space-charge zone recombination-current  $J_r$  under forward bias is given by

$$\frac{J_{t}}{J_{r}} = \frac{2n_{i}}{x_{d}} \left[ \frac{L_{n}}{N_{a}} + \frac{L_{p}}{N_{d}} \right] e^{\frac{qV_{a}}{2kT}}$$

(24)

where  $L_p = \sqrt{D_p \tau_p}$  is the diffusion length of a hole in a *n*-type region and  $L_n$  is the diffusion length of an electron in a *p*-type region. From the above relationship it is apparent that  $J_r$  is less significant relative to the ideal diode current as bias increases. Also, the more defect-free

the material, the longer the diffusion lengths and the more dominant is  $J_1$  over  $J_r$ .

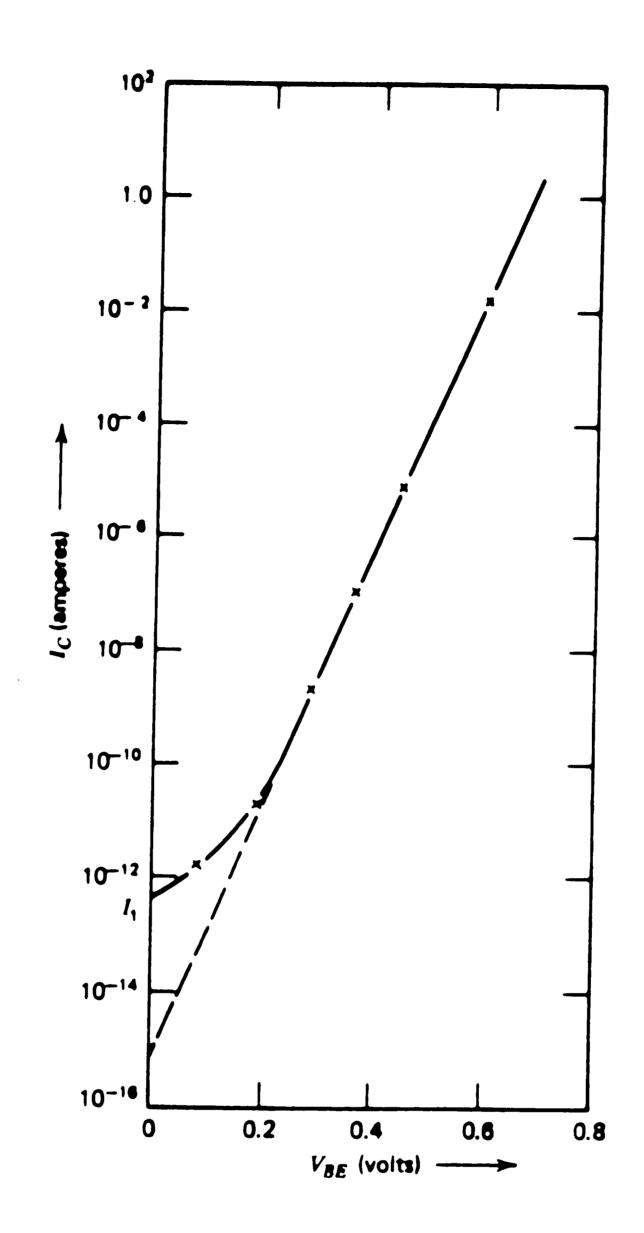

A semilogarithmic plot of  $I_C$  and  $I_B$  as a function of the base-emitter voltage illustrates this behavior. Typical data for an *npn* transistor is given in figure 3 <sup>[27]</sup>.

Figure 3. Measured collector and base currents plotted as a function of base-emitter voltage [27]

The excellent fit of the data to straight lines over the mid-range of currents is consistent with the exponential nature of the equations describing the current-voltage dependence. It can be seen that the collector current is "ideal" over a wider range than the base current. At low base-emitter voltage there is a change in the slope of the straight line variation of log  $I_B$  with  $V_{BE}$ . The experimental data fits a curve that is represented by

$$I_{\rm B} \approx I_0 \ e^{\frac{q \, V_{\rm BB}}{n k T}} \tag{25}$$

as  $V_{BE}$  goes to zero. The parameter n is generally found to be between one and two and  $I_0$  is larger than is the corresponding multiplier for an exponential form fitting the data at intermediate bias values. The equation for recombination current in the space-charge region derived from Shockley-Read-Hall theory has the same voltage dependence if n is equal to 2. Values for n between 1 and 2 would be indicative of variations of parameters affecting recombination within the space-charge region.

•

The loss of carriers to recombination in the base is measured by the base transport factor  $\alpha_{T}$

$$\alpha_{\rm T} = \frac{I_{\rm ne} - I_{\rm rb}}{I_{\rm ne}} = 1 - \frac{I_{\rm rb}}{I_{\rm ne}}$$

(26)

where  $I_{rb}$  is the recombination current in the base and  $I_{ne}$  is the electron current injected from the emitter. For a uniformly doped base

$$\alpha_{\rm T} = 1 - \frac{x_{\rm B}^2}{2D_{\rm n}\tau_{\rm n}} = 1 - \frac{x_{\rm B}^2}{2L_{\rm n}^2}$$

(27)

#### 2.3 Emitter Efficiency

The effectiveness of an emitter junction in injecting electrons into the base is measured by the emitter efficiency  $\gamma$

$$\gamma = \frac{I_{nE}}{I_{nE} + I_{pE}} = \frac{1}{1 + \frac{I_{pE}}{I_{nE}}}$$

(28)

With  $I_{nE} + I_{pE}$  being the total emitter current, the electron current crossing the emitter-base

15 \* .

junction  $(I_{nE})$  is  $\gamma I_E$ . For the simple prototype transistor with constant doping

$$\gamma = \frac{1}{1 + \frac{x_B N_{aB} D_{pE}}{x_E N_{dE} D_{nB}}}$$

(29)

where  $x_E$  is the emitter region width,  $x_B$  the base quasi-neutral width,  $N_{dE}$  the average emitter doping,  $N_{aB}$  the average base doping,  $D_{pE}$  the diffusion constant of holes in the emitter and  $D_{nB}$  the diffusion constant for electrons in the base. Values for this number are typically very close to unity.

#### 2.4 Forward-Active Current Gain

The ratio of the collector current  $I_C$  to the emitter current  $I_E$  is given by the symbol  $\alpha_F$ .

$\alpha_F$  is the product of the emitter efficiency  $\gamma$  and the base transport factor  $\alpha_T$ . By Kirchoff's current laws, all the currents into the transistor must sum to zero such that

$$I_{\rm B} + I_{\rm E} + I_{\rm C} = 0$$

(30)

$$I_{\rm B} - \frac{I_{\rm C}}{\alpha_{\rm F}} + I_{\rm C} = 0 \tag{31}$$

and

$$I_{\rm C} = \frac{\alpha_{\rm F} I_{\rm B}}{1 - \alpha_{\rm F}} = \beta_{\rm F} I_{\rm B}$$

(32)

where  $\beta_F \equiv I_C / I_B$  is the forward active current gain. Since  $\alpha_F$  is very nearly unity,  $\beta_F$  is very large. Small changes in  $\alpha_F$  caused by process variations in fabricating the transistor are magnified to large changes in  $\beta_F$ .

To the extent that  $\gamma$  and  $\alpha_T$  depart from unity represents a hole current that must be supplied from the base contact. For transistors with base widths much less than the diffusion length,  $\alpha_T$  has a value very close to unity and the current gain is given almost entirely by the emitter efficiency. With  $\alpha_T \approx 1$

.

•

σ, ε

$$\beta = \frac{\gamma}{1 - \gamma} \approx \frac{N_E}{N_B} W \approx \frac{N_E}{\frac{Q_{B0}}{qA}}$$

(33)

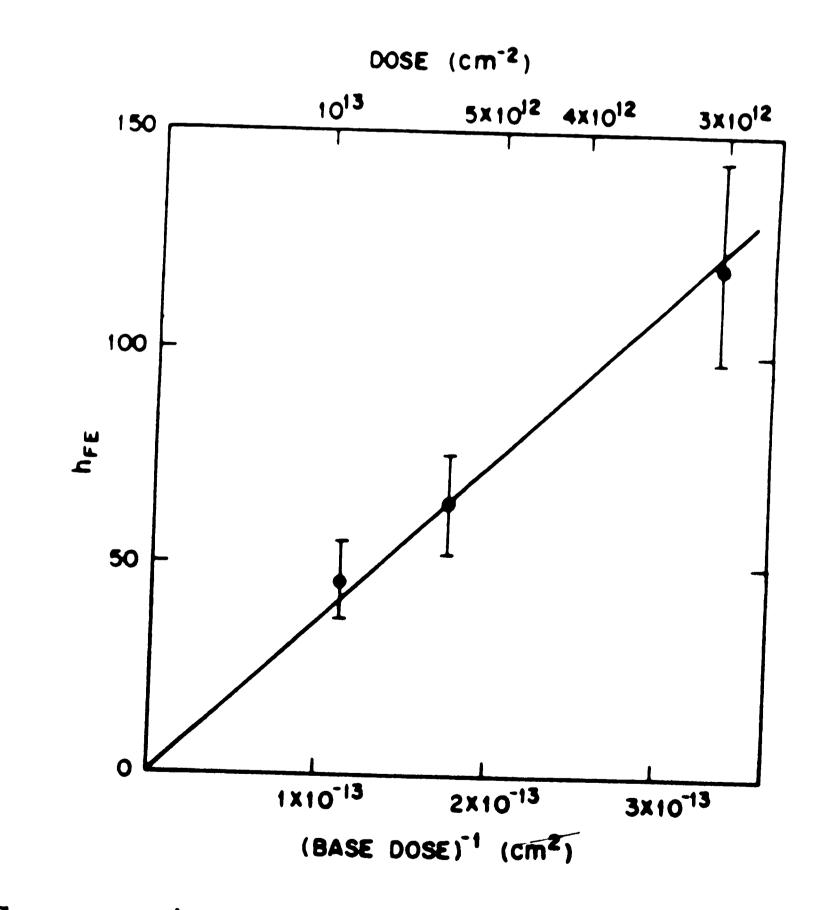

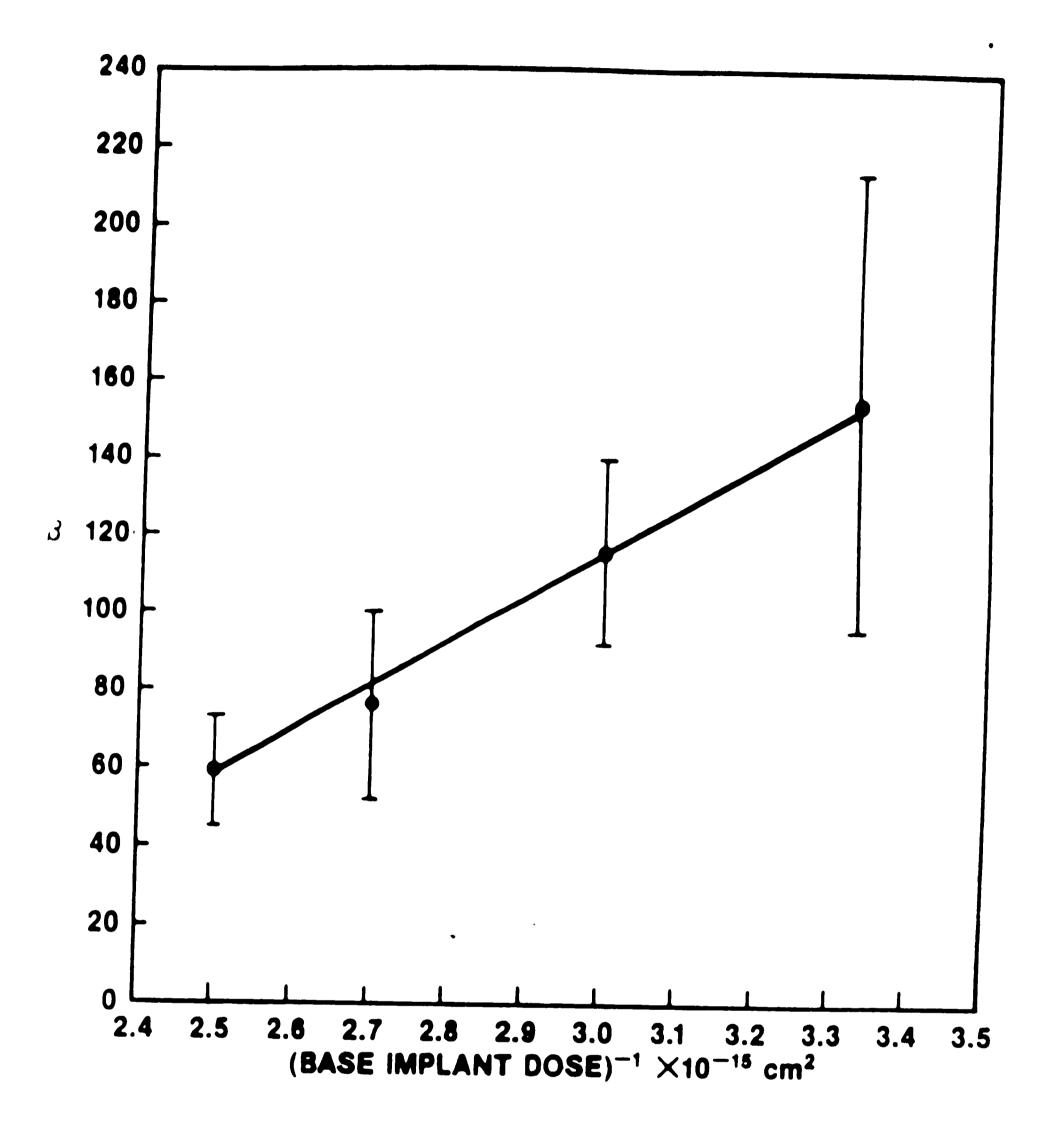

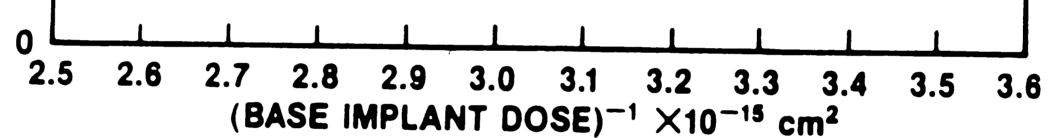

where  $N_E$  and  $N_B$  is the emitter and base doping respectively and  $Q_{B0}$  is the Gummel number defined earlier. Therefore, for a given emitter doping, the common-emitter current gain is inversely proportional to  $Q_{B0}$ . Figure 4 shows this relationship for ion implanted transistors having the same emitter doping.

Figure 4. Common-emitter current gain versus the inverse of the base implant dose for all implanted transistors <sup>[31]</sup>

The base dose is directly proportional to the Gummel number  $Q_B$  and it is seen that as the dose decreases the  $\beta$  increases. In equation 33 there is another dominant factor in addition to the Gummel number, the emitter doping concentration N<sub>E</sub>. To improve the gain (h<sub>FE</sub> or  $\beta$ ), the emitter should be much more heavily doped than the base, that is N<sub>E</sub> / N<sub>B</sub> > 1.

The importance of the recombination component relative to the injection components into the quasi-neutral base region increases as voltage is reduced. Recombination current in the space charge region flows only in the base-emitter leads. Collector current, consisting of collected electrons injected from the base-emitter junction is unaffected. Thus, at low biases the collector current is a smaller fraction of emitter current than it is in the intermediate bias range.

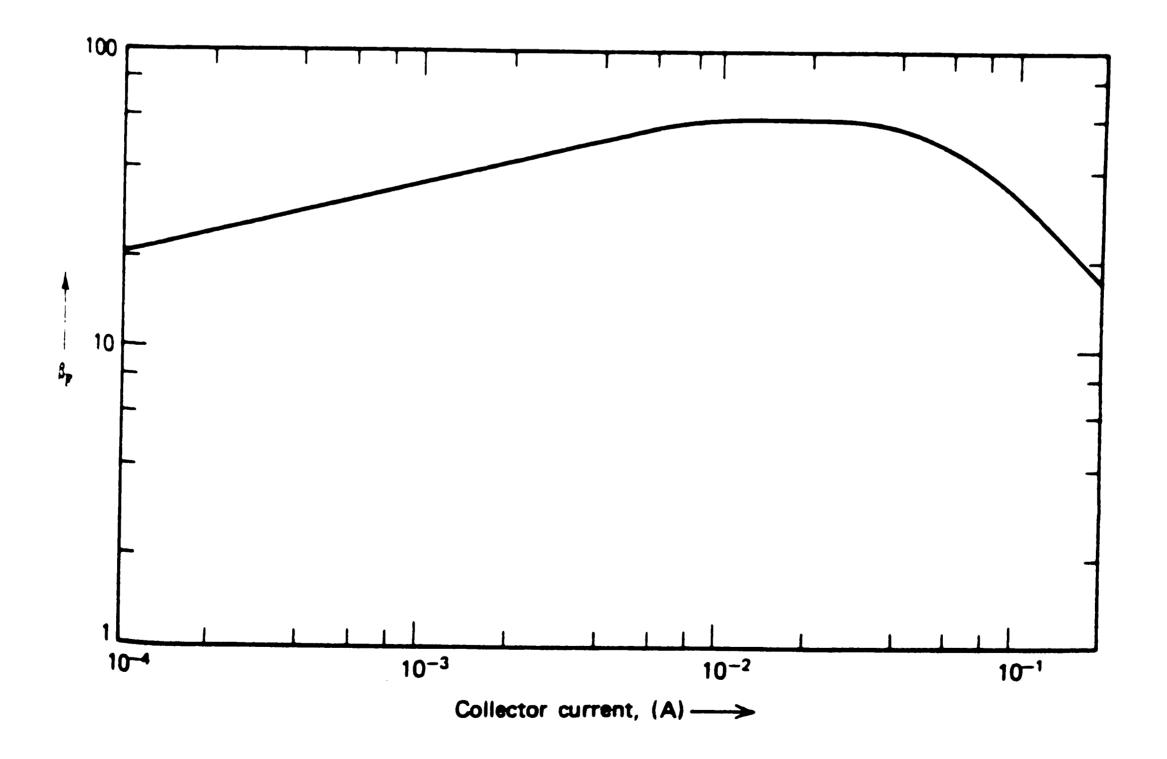

A plot of  $I_C / I_B$  (or  $\beta_f$ ) shows this behavior clearly (figure 5).

Figure 5. Forward active current gain ( $\beta_F$ ) as a function of collector current <sup>[27]</sup>

The decrease in  $\beta$  as V<sub>BE</sub> decreases represents a limitation to many circuit applications of the transistor. To improve the current characteristic in the low-current region, the trap densities in the depletion region and at the semiconductor surface must be reduced. During manufacture it is important to try and maintain as high a lifetime as possible within the base-emitter space charge region. At low collector current levels, the contribution of the recombination current in the emitter depletion region and the surface leakage current may be large compared with the diffusion of minority carriers across the bases making the efficiency low. By minimizing the bulk and surface traps,  $\beta$  can be improved at low current levels. As the base current reaches the "ideal" region  $\beta$  increases to a high plateau. At higher collector currents the injected minority-carrier density in the base approaches the majority-carrier density there (high level injection condition) and the injected carriers effectively increase the base doping, which, in turn, causes the emitter efficiency to decrease.

### 2.5 Graded Base Transistor

In the previous analysis of current gain, it was assumed that the impurity concentration in the base region was uniform. We will now consider, a *npn* junction transistor model having a step emitter junction and a graded base layer given by the impurity distribution  $N_{(x)}$ . This is a general impurity distribution where  $N_B$  denotes the impurity concentration at the base side of the emitter junction decreasing to zero at x = W, the base / collector junction. With the carrier concentration in the base being non-uniform, the energy bands will bend in accordance with the grading  $N_{(x)}$ . In the constant doped base model, the electrostatic potential  $\Psi$  is constant within the base region, so that the term  $d\Psi/dx$ , which is the electric field, is zero in the base region. For the graded base the potential  $\Psi$  is higher at the emitter than at the collector. Therefore,  $d\Psi/dx$  has a finite value indicating the existence of an electric field within the base region. This is a built-in field arising to prevent the majority carriers from diffusing because of their

concentration gradient  $dN_{(x)}/dx$ . This field, which keeps holes in their place, is in a direction to aid the transport of injected electrons. Thus, for the condition of low level injection, the electrons will move both by diffusion and drift.

From equation 11 we can express the base doping, N as a function of x and inserting the boundary conditions that p = 0 at x = W, the collector, the following expression is obtained for the injected electron concentration

$$n = \frac{J_n}{qD_n} \frac{1}{N_{(x)}} \int_x^W P_{(x)} dx$$

(34)

The result gives the electron concentration as a function of distance in the base layer. If this equation is evaluated at x = 0 where  $N_{(x)} = N_B$  then we obtain the injected electron concentration

$$n = \frac{J_n}{qD_n} \frac{1}{N_B} \int_0^W P_{(x)} dx$$

(35)

Using the quasi-Fermi-level argument

$$n = n_{pb} e^{\frac{qV_{EB}}{kT}} = \frac{n_i^2}{N_B} e^{\frac{qV_{EB}}{kT}}$$

(36)

with  $n_{pb}$  being the equilibrium electron concentration in the *p*-type base region. Setting the last two equations equal to each other,  $J_n$  becomes

$$J_{n} = \frac{qD_{n}n_{i}^{2}e^{\frac{qV_{EB}}{kT}}}{\int_{0}^{W}N_{(x)}dx}$$

(37)

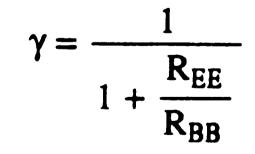

The emitter efficiency  $\gamma$ , can be expressed as

$$\gamma = \frac{1}{1 + \frac{J_p}{J_n}}$$

(38)

For a uniform emitter with impurity concentration  $N_E$ , the hole current density can be expressed as

$$J_{p} = \frac{qD_{p}p_{me}}{L_{pe}}e^{\frac{qV_{BE}}{kT}} = \frac{qD_{p}n_{i}^{2}}{L_{pe}N_{E}}e^{\frac{qV_{EB}}{kT}}$$

(39)

where  $P_{ne}$  equals the hole concentration in the *n*-type emitter and  $L_{pe}$  is the hole diffusion length in the emitter. Substituting the expressions for  $J_n$  and  $J_p$  into  $\gamma$  we obtain

$$\gamma = \frac{1}{1 + \frac{D_{p}}{D_{r}} \frac{1}{L - N_{r}} \int N_{(x)} dx}$$

(40)

replacing the ratio  $D_p / D_n$  with  $\mu_p / \mu_n$  and multiplying the integral expression by q / q gives

$$\gamma = \frac{1}{\frac{W}{q\mu_{pE} \int_{0}^{W} N_{(x)} dx}}$$

$$1 + \frac{1}{\frac{Q\mu_{nB} N_{E} L_{nE}}{Q\mu_{nB} N_{E} L_{nE}}}$$

(41)

This equation can be written in the form

(42)

$$R_{EE} = \frac{1}{q\mu_{nb}N_EL_{ne}} = \frac{\rho_E}{L_{ne}}$$

$$R_{BB} = \frac{1}{\frac{W}{W}} = \frac{\rho_{B(x)}}{W}$$

$$q\mu_{pe} \int_{0}^{W} N(x) dx$$

The terms  $R_{EE}$  and  $R_{BB}$  are referred to as sheet resistances and defined as the ohmic resistances as measured from edge to edge of a square sheet of material of a certain thickness x. Thus,  $R_{EE}$  is the sheet resistance of the emitter having a uniform resistivity  $\rho_E$  and a thickness equal to  $L_{nE}$ .  $R_{BB}$  is the sheet resistance of a base having a graded resistivity  $\rho_{B(x)}$ and a thickness W. For the uniform doped base,  $R_{BB} = \rho_B / W$ , and equation 42 reduces to equation 29.

$R_{BB}$  increases as a result of a graded impurity distribution, thus, the emitter efficiency is increased when the base region is graded. Regardless of the base impurity distribution, it is still required that the emitter doping be as heavy as possible for high emitter efficiency so that

the sheet-resistance ratio  $R_{EE} / R_{BB}$  remains small.

From equation 33, the forward-active current gain,  $\beta$  is related to emitter efficiency  $\gamma$  by

$$\beta = \frac{\gamma}{1-\gamma}$$

Substituting equation 42 for  $\gamma$  yields

$$\beta = \frac{\gamma}{1 - \gamma} = \frac{R_{BB}}{R_{EE}}$$

(43)

for the graded base transistor. Since integrated circuit processing involves diffused structures, it should be the equations derived for the graded base transistor that better describe the manufactured devices.

#### 3. EXPERIMENTS

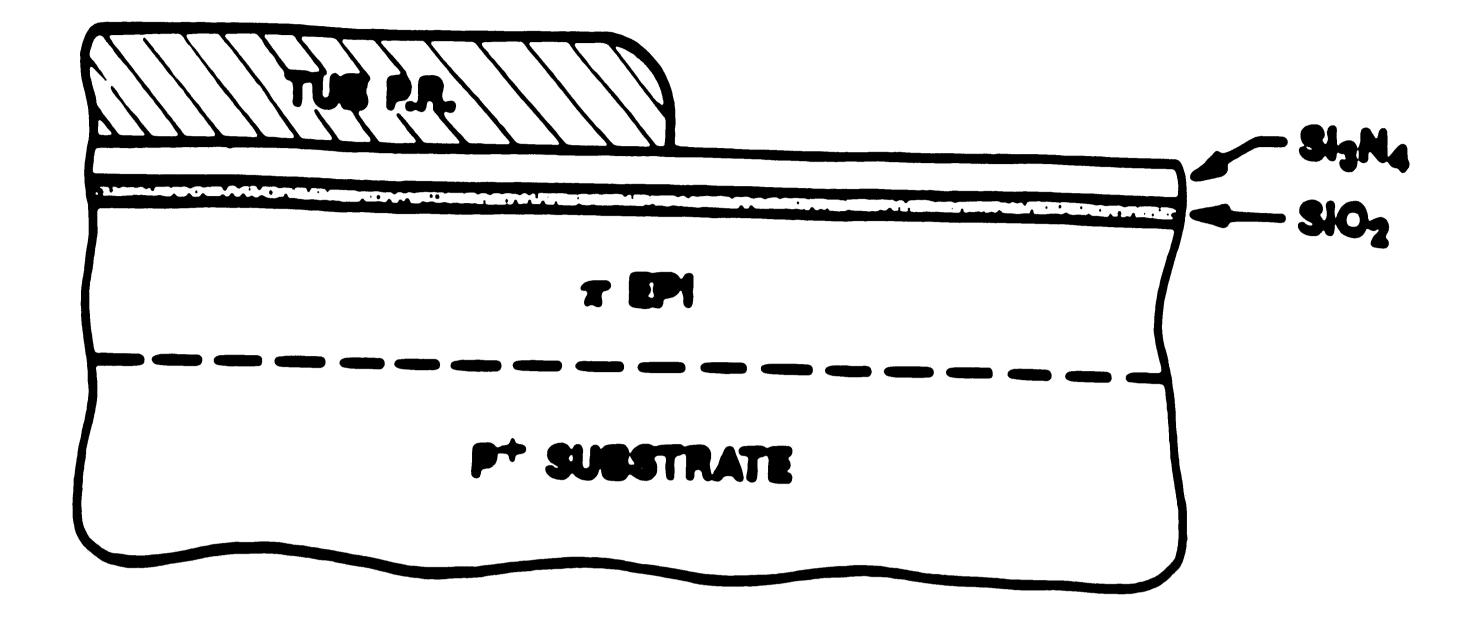

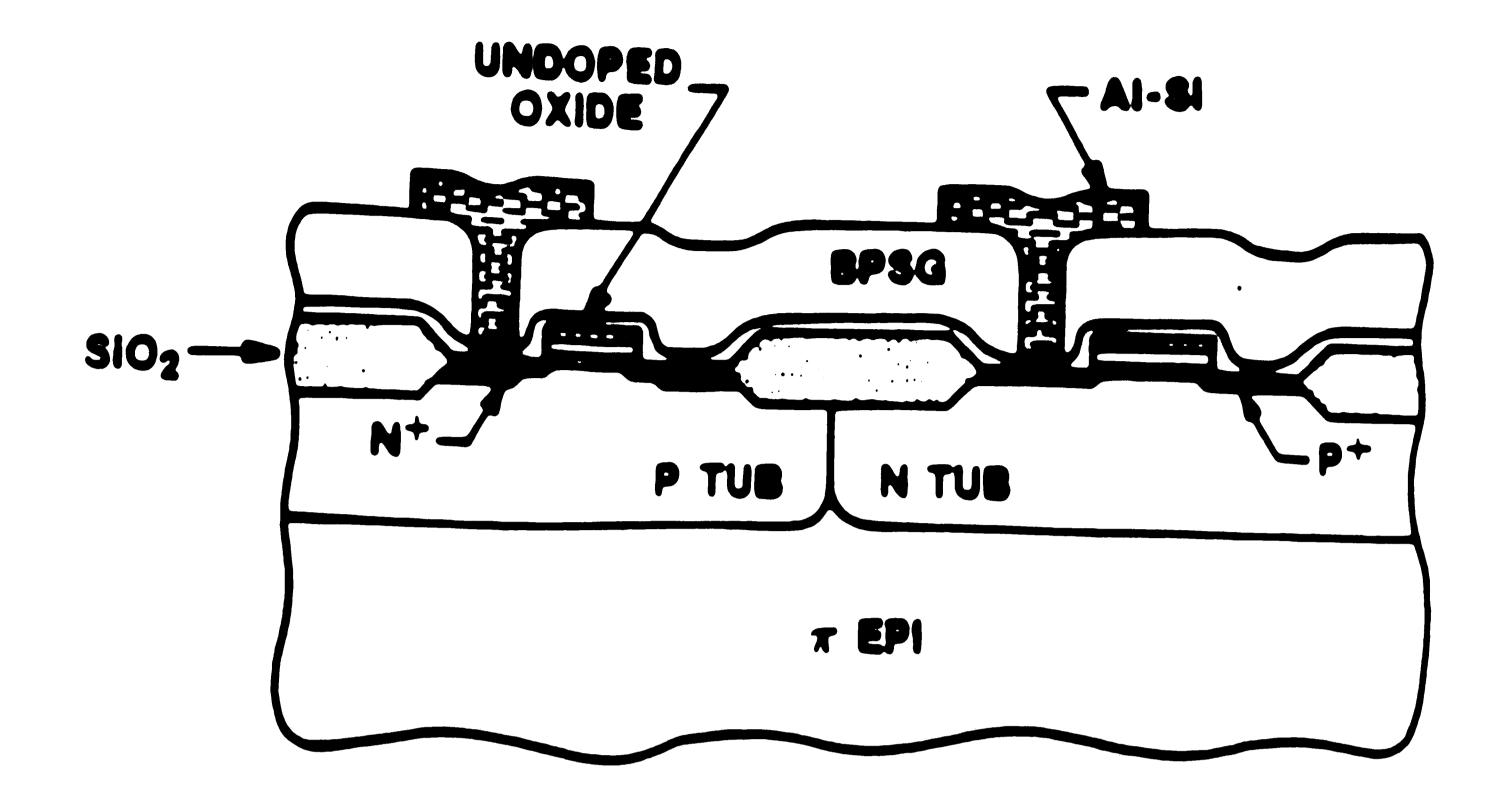

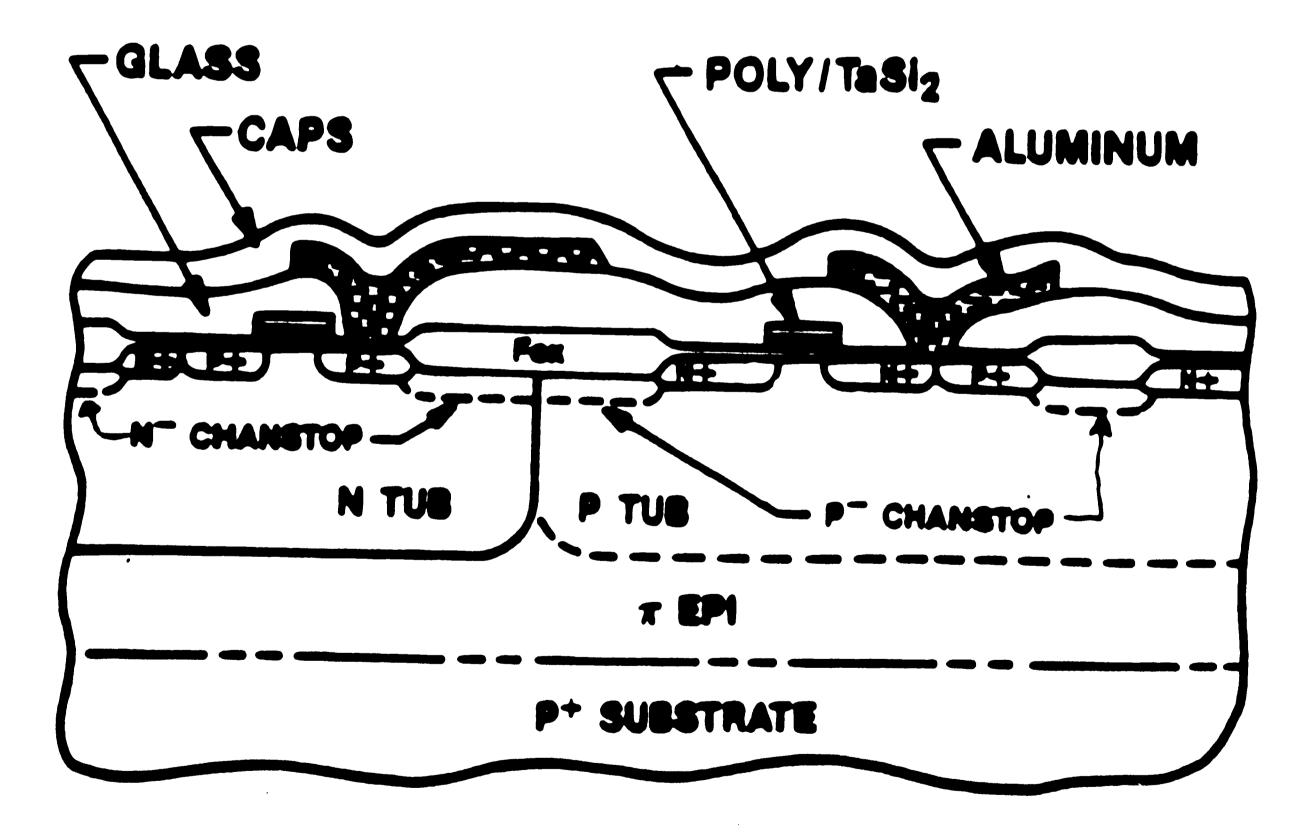

### 3.1 CMOS FABRICATION

The core process used for BiCMOS development is the third generation Twin-Tub CMOS Technology.<sup>[32]</sup> <sup>[33]</sup> <sup>[34]</sup> The two tub approach is used with a lightly doped epitaxial substrate to suppress latch-up and enable separate optimization of the *n*- and *p*-channel transistors. Although a *p*-epi over  $p^+$ -substrate is used, the technology is compatible with *n*-epi substrates since the active doping levels are established by implantation. The 5.0 volt transistor structures use a nominal 250 Å gate oxide, tantalum silicide over *n*-poly gate and 1.3µm nominal channel lengths. The threshold voltages of the *n*- and *p*-channel device are 0.70V and -1.10V.

The critical dimensions of this  $1.75\mu m$  design rule technology are outlined in table 1.

Critical Dimensions

| (µm)     |      |       |  |  |

|----------|------|-------|--|--|

|          | Line | Space |  |  |

| Active   | 1.5  | 2.5   |  |  |

| Polycide | 1.75 | 1.75  |  |  |

| Gates    | 2.25 |       |  |  |

| Windows  | 1.75 |       |  |  |

| Metal    | 1.75 | 1.75  |  |  |

TABLE 1. Critical dimensions of the Twin-Tub III CMOS technology

Photolithography is accomplished with 5x direct step on wafer (DSW) printing and all levels are reactive sputter etched. There are eight mask levels in the Twin-Tub III technology. The digital CMOS process sequence is now discussed along with a cross-sectional development of CMOS transistors.

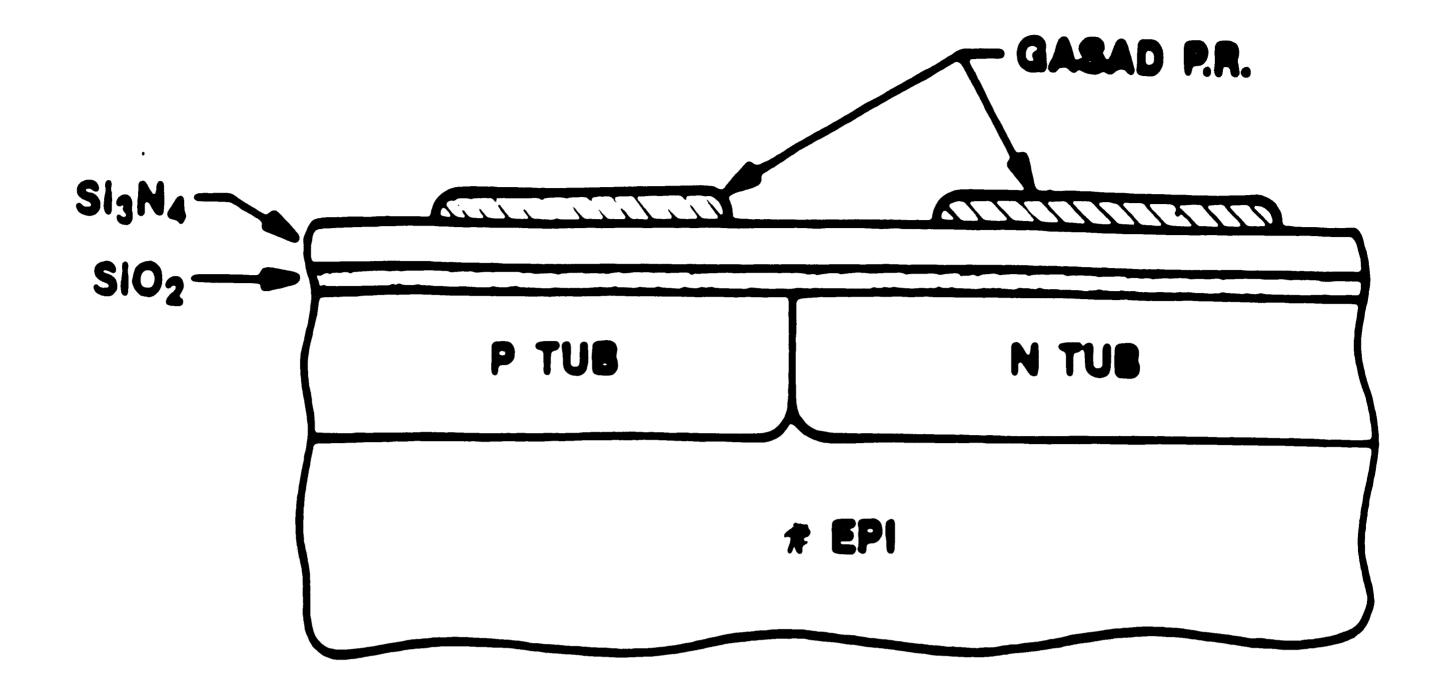

A self-aligned process is used to form the two tubs. An oxide-nitride sandwich is deposited and etched (figure 6). The exposed silicon is implanted with phosphorus and

Figure 6. Mask 1: n-tub formation

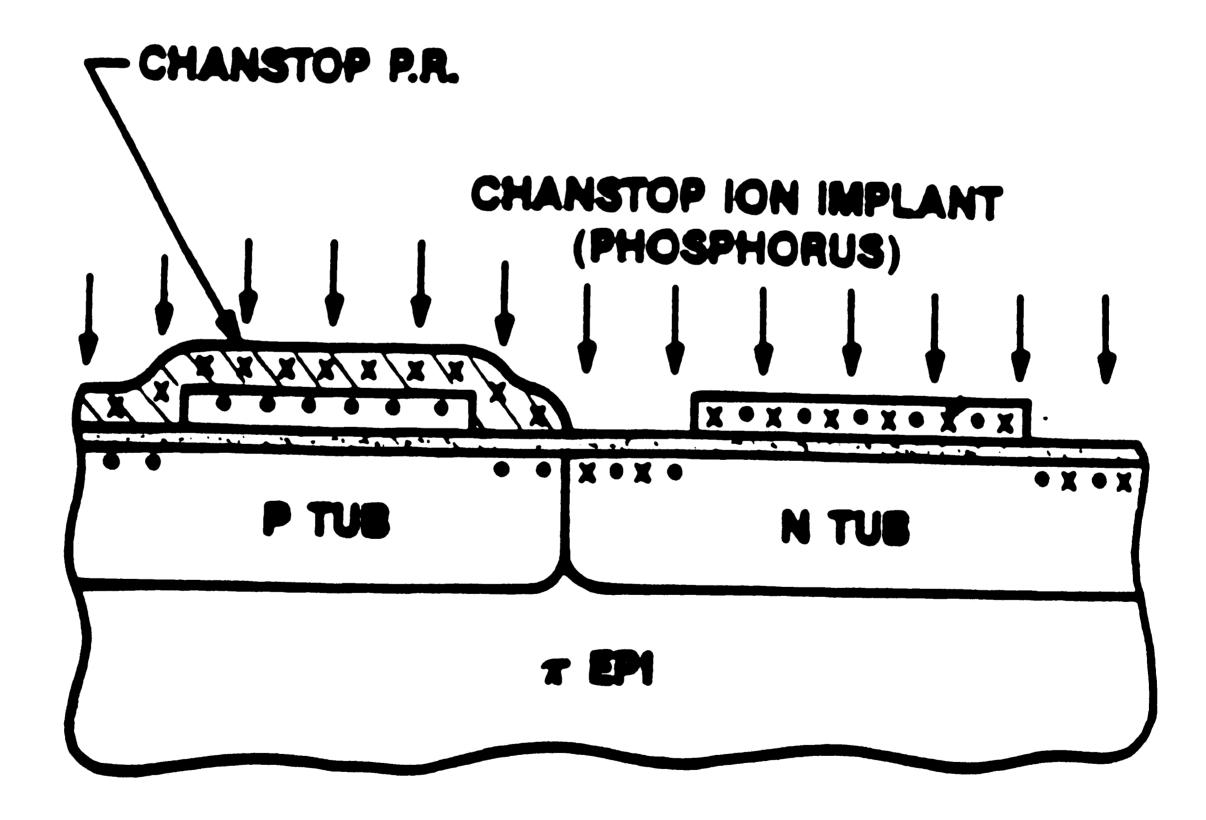

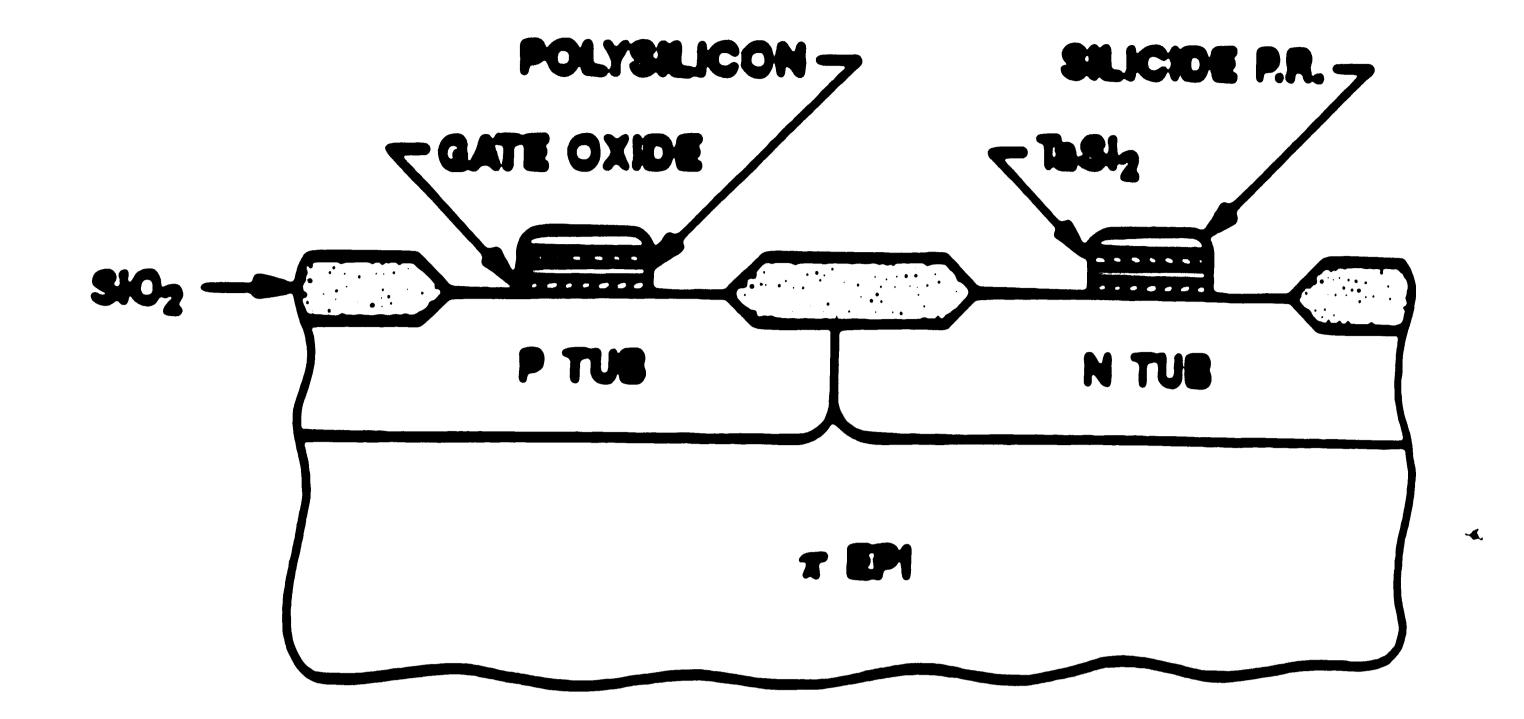

selectively oxidized to form the *n*-tub. The masking nitride is now removed and the *p*-tub is implanted, self-aligned to the oxide masked *n*-tub. Both tubs are driven to a depth of 4-5  $\mu$ m. A second oxide-nitride sandwich is deposited and etched (figure 7) to define the active gate regions. A blanket boron implant is performed followed by a masked phosphorus implant (figure 8) to achieve self-aligned channel stops. Device isolation is completed with a LOCOS field oxidation. The masking oxide-nitride layer is removed and a sacrificial oxide is grown. A non-selective boron implant is performed to define the threshold voltages of both the *n*- and *p*-channel transistors. After removal of this oxide, a 250 Å gate oxide is grown, polysilicon deposited and doped with phosphorus. A composite layer of TaSi<sub>2</sub> over *n*<sup>+</sup>-polysilicon is created to give a gate sheet resistance of 2.5  $\Omega$ /cl. The composite structure is etched with an anisotropic reactive sputter technique (figure 9).

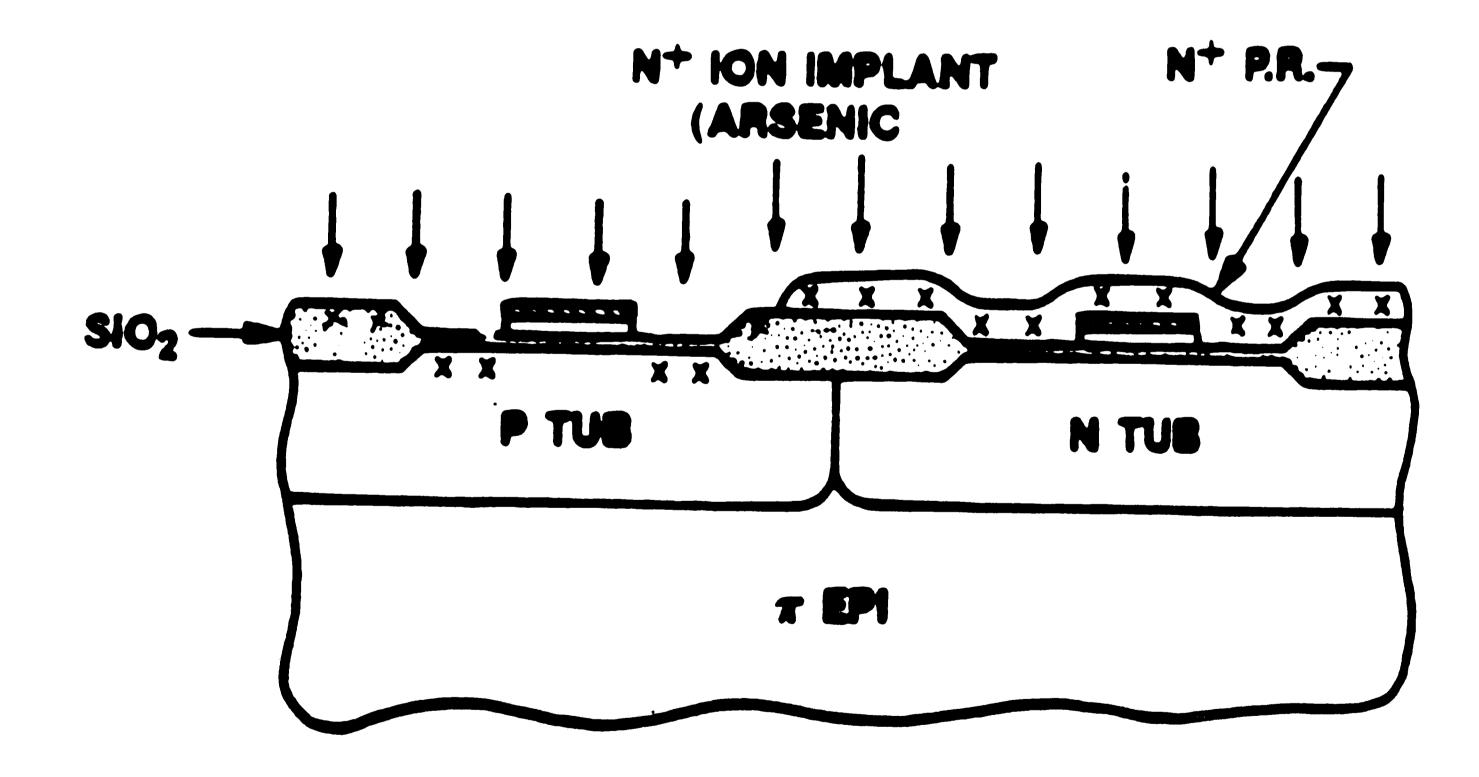

A selective arsenic/phosphorus implant is used for the doping of  $n^+$ -source and drain areas to obtain a graded junction (figure 10). In order to save another mask step, a blanket BF<sub>2</sub>

24

.

$\cdot$

Figure 7. Mask 2: Active gate region definition

Figure 8. Mask 3: Phosphorus channel-stop implant

١

• ; Figure 9. Mask 4: Gate definition

Figure 10. Mask 5: n-channel source/drain formation

•

2

implant is performed.

In order to achieve glass flow under the temperature restrictions of the process a Boro-Phospho-Silica Glass (BPSG) is used as the interlevel dielectric. Contact windows are formed (figure 11), the metal layer applied and patterned (figure 12)

Figure 11. Mask 6: Contact window formation

and a final SINCAPS passivation layer applied and patterned (figure 13).

Table 2 lists some of the key parameters of the technology.

The border of the tubs is a critical region. A design rule for  $n^+$ -diffusion to p-tub edge has been established to account for the out-diffusion of the p-dopant at the edge of the tub.

The p- and n-channel threshold voltages are sensitive to tub and threshold adjust dosages. With the threshold adjust counter doping the n-tub surface, the p-channel threshold voltage responds strongly to both the n-tub and threshold adjust implants. The n-channel threshold voltage is dominated by the adjust implant which essentially sets the surface concentration.

•

Figure 12. Mask 7: Metal interconnections formed

4

Figure 13. Mask 8: Encapsulation - completed device

Ф.,

.

| Key Parameters            |                      |  |  |

|---------------------------|----------------------|--|--|

| Gate Oxide                |                      |  |  |

| Nominal L' <sub>n,p</sub> | 1.3 µm               |  |  |

| V <sub>tn</sub>           | 0.7 V                |  |  |

| V <sub>p</sub>            | -1.0 V               |  |  |

| B                         | 75 μA/V <sup>2</sup> |  |  |

| B <sub>p</sub>            | 27 μA/V <sup>2</sup> |  |  |

TABLE 2. Key parameters of the Twin-Tub III CMOS technology

Hot carrier effects are suppressed by the grading of the  $n^+$ -junctions. The aluminum is doped with silicon to achieve non-spiking metalization.

### 3.2 Determination Of Base Parameters

**'**•

The 1.75 $\mu$ m Twin-Tub III CMOS technology<sup>[34]</sup> was examined to study the feasibility of producing a moderate performance *npn* vertical bipolar transistor compatible with CMOS processing. The development charter specified that the CMOS parameters remain unchanged and the total process be cost effective. Following the general approach to integrating bipolar transistors with *n*-well CMOS first outlined by Hoefflinger .et.al,<sup>[14]</sup> the MOS *n*-tub is used as the collector, the *n*<sup>+</sup> implant as an emitter and the *p*<sup>+</sup>-source and drain implant as the inactive base.

Momose .et.al<sup>[15]</sup> and Miyamoto .et.al<sup>[16]</sup> used the MOS threshold adjust step as the bipolar implant. At this point in the process the tubs have been set by the high temperature tub drivein and the field oxide isolation, with its associated channel stop doping, is complete. With these deep diffusions now in place they will not be changed substantially by any additional bipolar processing. It is, thus, a very advantageous point in the process to insert the active base implant. Since, however, the CMOS characteristics must not be altered by the bipolar

process it was decided to also follow the approach of Yue .et.al<sup>[17]</sup> and Reich .et.al<sup>[3]</sup> in using a separate photomask for the bipolar base processing. While adding additional steps to the process, it provides the capability of adjusting bipolar transistor parameters independent of the CMOS parameters.

Table 3 describes the proposed flow of the BiCMOS process.

| CMOS BASELINE FLOW                          | STEPS FOR BIPOLAR |

|---------------------------------------------|-------------------|

| p <sup>+</sup> Substrate                    |                   |

| p <sup>-</sup> Epitaxial Layer              |                   |

| n-Well With Self-aligned p-Well             | (Collector)       |

| Well Drive-in                               |                   |

| LOCOS/Chanstop Isolation                    |                   |

| Threshold Adjust Implant                    |                   |

|                                             | Pattern Base      |

|                                             | Implant Base      |

|                                             | Drive-in Base     |

| Gate Oxidation                              |                   |

| Gate Deposition/Definition                  |                   |

| Pattern/Implant n <sup>+</sup> Source/Drain | (Emitter)         |

| Blanket Implant $p^+$ Source/Drain          |                   |

| Deposit Interlevel Oxide                    |                   |

| Flow Interlevel Oxide/Drive-in Source/Drain |                   |

| Define Contact Windows                      |                   |

| Deposit/Define Metalization                 |                   |

|                                             |                   |

# TABLE 3. Proposed flow of the Twin-Tub III BiCMOS technology

A few details of the process are worth noting. With the use of LOCOS field oxide and the associated Kooi effect<sup>[35]</sup>, a 900Å sacrificial oxide is grown to obtain a quality surface for the subsequent MOS gate oxide. It is through this oxide that the non-selective boron CMOS threshold adjust dose is implanted. The boron base implantation is also carried out through

this oxide layer in order to avoid degradation of device performance by the formation of stacking faults during annealing.<sup>[36]</sup> To maximize the annealing of the implant damage in the base region, a dry nitrogen ambient was chosen for the base drive-in.<sup>[37]</sup>

With the  $p^+$ -substrate being heavily doped with boron, the  $p^-$ -epitaxial layer is grown very thick (17µm) in order to insure there is no problem with out diffusion of boron from the substrate during the high temperature well (tub) drive-in. This does not allow the addition of a  $n^+$ -buried layer for increased bipolar performance. Since the CMOS parameters must remain unaffected by bipolar processing and the total BiCMOS process remain cost effective, a wholesale redesign of the well structures is not a development option. The collector will therefore, be wholly defined by the properties of the CMOS *n*-well. For these same reasons the properties of the emitter will be defined by the existing CMOS *n*-channel source and drain processing. The steps dealing with the base process are thus the only parameters available for

bipolar transistor optimization. These parameters are the ion implant energy the ion implant dose and the thermal drive-in schedule.

An appropriate ion implant energy for the base was chosen by checking the projected range statistics into silicon dioxide.<sup>[38]</sup> The projected range for a 100 keV boron implant is  $3104\text{\AA}$  with a projected standard deviation of  $710\text{\AA}$ . This implant energy is adequate to penetrate the 900Å oxide screen. It is important to realize, however, that thickness variations in the sacrificial and final oxides will allow this implant energy to affect reproducibility. Since the base is implanted through the sacrificial oxide, its thickness influences how much of the boron goes through the oxide and into the silicon. With the subsequent growth of the final gate oxide, boron is removed from the silicon through segregation effects of the growing oxide. A variation in this oxide thickness will thus affect how much boron is lost from the silicon. Using a high base implant energy will put more of the boron deeper into the silicon, making both of these effects less important.

A base anneal/drive-in of 900°C for 60 minutes was chosen for the initial process. The ambient is inert dry nitrogen to maximize the annealing of the implant damage. This is a commonly used drive-in schedule already in place in the CMOS processes to anneal devices after implantation and was chosen for process commonality.

With the ion implant energy and drive-in schedule now specified, it is the ion implant dose that will be the variable to identify in obtaining the desired bipolar characteristics.

It has been shown that for a transistor with constant doping, the forward-active current gain,  $\beta$ , is approximately equal to  $N_E / Q_{B0}$  where  $N_E$  is the emitter doping and  $Q_{B0}$  is the total amount of charge in the base (Gummel number). Diffused transistors, however, will have a graded impurity profile. The gain,  $\beta$ , for graded base transistors is given by  $\beta = R_{BB} / R_{EE}$  where  $R_{BB}$  and  $R_{EE}$  are the sheet resistances of the active base and emitter respectively. With the emitter doping defined by the CMOS process and thus held constant, the gain of the bipolar

transistors is thus determined by  $R_{BB}$  which is defined by the base implant dose.

It should be noted, however, that in the calculations for the graded base device it has been assumed that the emitter / base junction is a step junction. In the Twin Tub III CMOS process the  $n^+$ -source / drain junction has been purposely graded, by way of a large dose phosphorus implant, to guard against hot carrier effects. The maximum impurity concentration in the base does not occur at the emitter / base metallurgical junction, but is shifted slightly towards the collector. There exists, therefore, an impurity gradient in the vicinity of the emitter junction which is opposite in slope to the aiding built-in field. This opposite impurity gradient establishes, in the base region close to the emitter junction, an electric field which is retarding the flow of injected minority carriers. This effect will lower the emitter efficiency,  $\gamma$ , as predicted by the graded base model.

AT&T Bell Laboratories has developed a computer program for the calculation of doping profiles of semiconductor devices called BICEPS.<sup>[39]</sup> By inputing information relating to the

oxidations, thermal drive-ins, implantations, depositions and etchings information relating to the resultant dopant concentration profiles are obtained. Since BICEPS calculates a net dose and sheet resistance for the metallurgical junctions, it provides a means to study various base implant and/or drive-in schedules and correlate them to device characteristics. The BICEPS calculation of particular interest is sheet resistance expressed in  $\Omega/\Box$  Given an indication of emitter, base and active base sheet resistance (base pinch sheet resistance) allows the experimental measurements on Van der Pauw test structures to be correlated with the theoretical and simulated results.

The sheet resistances calculated by the BICEPS simulation program do not, however, take into consideration any depletion layer effects. Values of active base sheet resistance would therefore be somewhat higher than that calculated. Also, the simulations are a development tool and are not absolute in predicting diffusion profiles. When trying to determine the active

base dopant concentration, we are dealing with the net difference of several impurity profiles where the tails of distributions take on added significance. It is not unusual, therefore, to expect some systematic errors in matching the output of the simulations to the manufactured device.

A current gain ( $\beta$ ) of between 50 to 100 was defined to be a good value for a general purpose *npn* transistor and the goal of the process development. The BICEPS simulation program calculations for the sheet resistance of the emitter and active base areas were then compared to see what value of R<sub>BB</sub> was necessary to achieve the proper gain. With the emitter sheet resistance being defined by the CMOS *n*<sup>+</sup>-source and drain process and thus fixed at R<sub>EE</sub> = 25 $\Omega/\Box$ , the active base sheet resistance should be on the order of R<sub>BB</sub> = 2000 $\Omega$ /square according to the equations derived for the graded base transistor.

Values for various base implant doses were input to the BICEPS simulation program and a dose of  $5.0 \times 10^{14}$  cm<sup>-2</sup> found to give a value of  $2650 \Omega / \Box$  for the active base sheet resistance.

.

With the limitations of the simulations and derived equations stated previously, it was anticipated that the active base sheet resistance, as simulated, should be higher than this amount. It was decided, therefore, to use this value of implant dose as an upper level and to systematically decrease the dose over a wide range in an effort to obtain devices with the desired current gains.

An experimental wafer lot was then started with base doses varying from  $5.0 \times 10^{14}$  cm<sup>-2</sup> to  $8.0 \times 10^{-2}$ . The measured active base sheet resistance and the common emitter forward-active current gain ( $\beta$ ) for the experimental cells are given in table 4.

| Experimental | Base Implant Dose                    | Active Base  | β         |

|--------------|--------------------------------------|--------------|-----------|

| Cell         | 100 keV                              | Rs<br>(Ω/□)  | @<br>10µA |

| 1            | $8.0 \times 10^{13} \text{ cm}^{-2}$ |              |           |

| 2            | $1.0 \times 10^{14} \text{ cm}^{-2}$ |              |           |

| 3            | $2.0 \times 10^{14} \text{ cm}^{-2}$ | 34,700±5,200 | 503±368   |

| 4            | $3.0 \times 10^{14} \text{ cm}^{-2}$ | 9,834±1,527  | 116±39    |

| 5            | $4.0 \times 10^{14} \text{ cm}^{-2}$ | 5,591±552    | 45±8      |

| 6            | $5.0 \times 10^{14} \text{ cm}^{-2}$ | 3,850±365    | 31±1      |

TABLE 4. Test results from the first experimental wafer lot - base drive-in at 900°C for 60 min

Base implants of  $8.0 \times 10^{13}$  cm<sup>-2</sup> and  $1.0 \times 10^{14}$  cm<sup>-2</sup> did not produce functional bipolar transistors. The graded phosphorus implant of the emitter overcompensated these boron implants resulting in the absence of an active base region. Although a dose of  $2.0 \times 10^{14}$  cm<sup>-2</sup> did result in working devices, their  $\beta$  of 500 was not representative of our defined goals and with a range of ±368 was clearly not a controllable manufacturing process.

Cells number 4 and 5, with base doses of  $3.0 \times 10^{14}$  cm<sup>-2</sup> and  $4.0 \times 10^{14}$  cm<sup>-2</sup> did produce transistors in the range of the desired  $\beta$  of 50 to 100. Cell number 6, with an implant of

$5.0 \times 10^{14}$  cm<sup>-2</sup> produced transistors with gains lower than the design goals and were thus not characterized extensively.

Based on the previous discussion on the limitations of the simulations and derived equations, it is not surprising that somewhat lower base implant doses than the predicted  $5.0 \times 10^{14}$  cm<sup>-2</sup> produced transistors with the specified gains.

The second wafer lot, builds on the information gathered from it's predecessor. The experimental cells of  $3.0 \times 10^{14}$  cm<sup>-2</sup> and  $4.0 \times 10^{14}$  cm<sup>-2</sup> which gave reasonable bipolar transistors were repeated. Doses of  $3.3 \times 10^{14}$  cm<sup>-2</sup> and  $3.7 \times 10^{14}$  cm<sup>-2</sup> were added to home in on the desired transistor parameters. Some wafers with these last two doses were given an additional 950°C 69 minute base drive-in to simulate heat treatments associated with the 1.75  $\mu$ m analog CMOS process.

| Experimental | Base Implant Dose                    | Active Base    | β      |

|--------------|--------------------------------------|----------------|--------|

|              | @                                    | Rs             | @      |

| Cell         | 100 keV                              | ( <b>Ω/</b> □) | 10µA   |

| 1            | $3.0 \times 10^{14} \text{ cm}^{-2}$ | 13,126±3,390   | 155±59 |

| 2            | $3.3 \times 10^{14} \text{ cm}^{-2}$ |                |        |

| 2a           | Single poly                          | 10,491±2,120   | 116±24 |

| 2b           | Double poly                          | 7,302±1,340    | 84±22  |

| 3            | $3.7 \times 10^{14} \text{ cm}^{-2}$ |                |        |

| 3 <b>a</b>   | Single poly                          | 7,637±1,861    | 76±24  |

| <b>3b</b>    | Double poly                          | 5,454±825      | 59±14  |

| 4            | $4.0 \times 10^{14} \text{ cm}^{-2}$ | 6,355±886      | 59±14  |

The key electrical parameters for each experimental cell are listed in table 5.

TABLE 5. Test results from the second experimental wafer lot - base drive-in at 900°C for 60 min

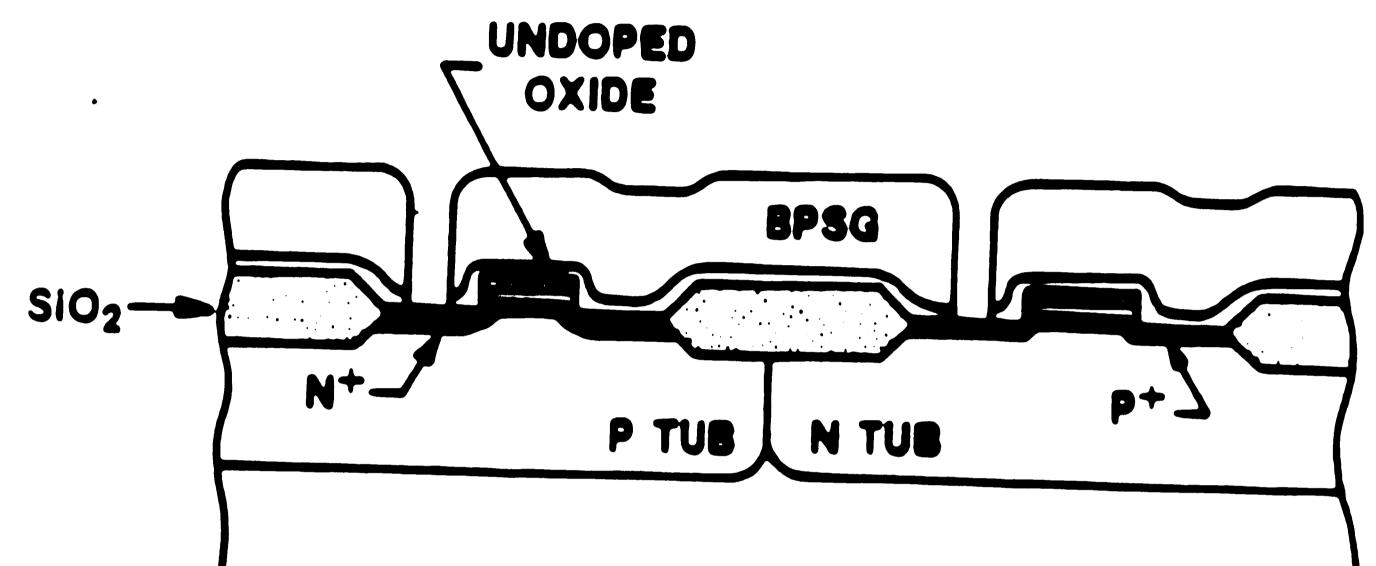

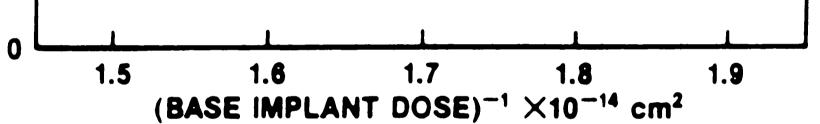

The gain versus the reciprocal of the base implant dose for the four experimental cells with a common base drive of 900°C 60 minutes are plotted in figure 14.

Figure 14. A plot of current gain versus the reciprocal of the base implant dose for the experimental cells of the second wafer lot

Some general comments on these results are in order. As the base implant dose increases the effective base width increases and the bipolar gain decreases. This effect is clearly seen in the data displayed in figure 14 where the error bars represent twice the standard deviation of an experimental cell. That the distribution of the gains also becomes tighter should be expected. A deeper base junction is less susceptible to the normal process variations any given lot of wafers experiences. Thus it is not surprising that there is much closer agreement between two

•

lots at a dose of  $4.0 \times 10^{14}$  cm<sup>-2</sup> than  $3.0 \times 10^{14}$  cm<sup>-2</sup>.

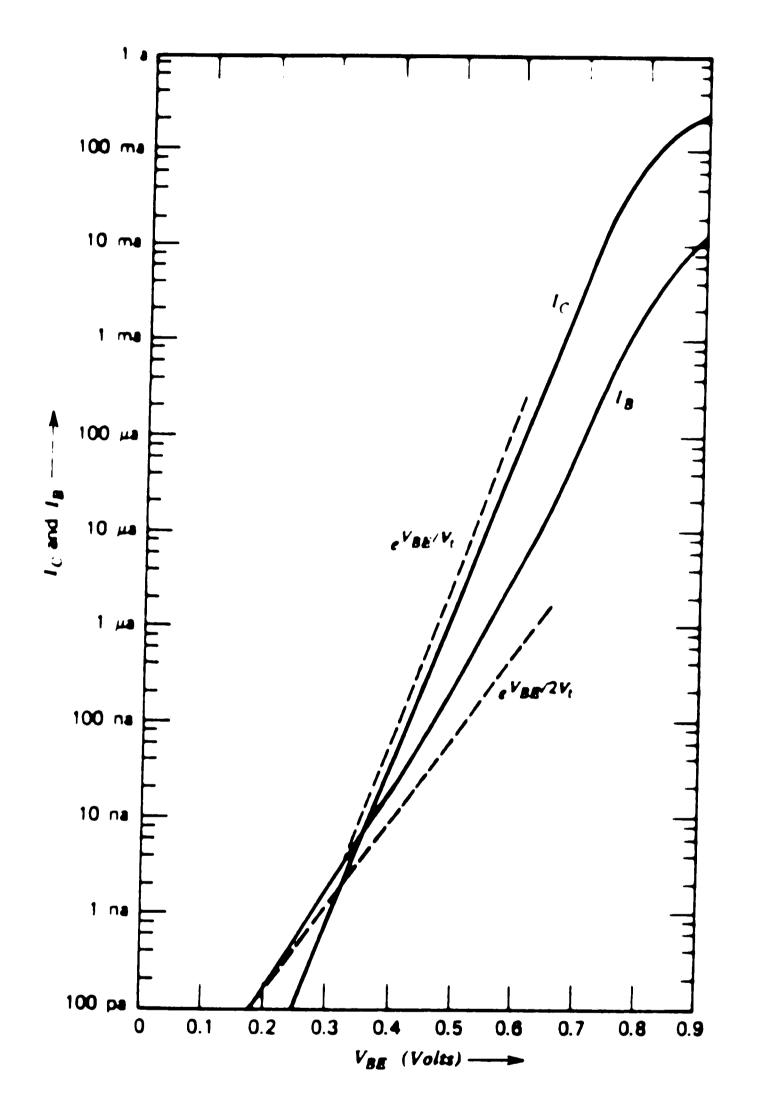

It has been shown that the electron current flowing into the collector junction of a npn transistor under forward active bias is

$$I_n \approx -I_S e^{\frac{qV_{BB}}{kT}}$$

(19)

where

; .

$$I_{S} = \frac{q^2 A^2 n_i^2 \tilde{D}_n}{Q_B}$$

(18)

Figure 2 shows a logarithmic plot of the collector current  $I_c$  as a function of the base-emitter bias  $V_{BE}$ . The intercept of an extrapolated line drawn through the collector current measurement with the current axis at  $V_{BE} = 0$  yields a value of  $I_S$  in equation 19. Once  $I_S$  is

known, the built-in base charge in the quasi-neutral region can be obtained from equation 18 since all the other parameters are known.

$Q_{B0}$  represents the total hole charge in the quasi-neutral base as the base-emitter bias tends to zero and, by rewriting equation 18, is expressed as

$$Q_{B0} = \frac{q^2 A^2 n_i^2 \tilde{D}_n}{I_S}$$

(20)

The number of base dopant atoms (per  $cm^2$ ) in the quasi-neutral region is given by

$$\int_{0}^{\mathbf{x}_{B}} \mathbf{N}_{\mathbf{a}}(\mathbf{x}) d\mathbf{x} = \frac{Q_{B0}}{qA} = \frac{qAn_{i}^{2}\tilde{D}_{n}}{I_{S}}$$

(21)

Substituting values of  $q = 1.6 \times 10^{-19}$  C,  $n_i = 1.45 \times 10^{10}$  cm<sup>-3</sup>,  $\tilde{D}_n = 20$  cm<sup>2</sup>/sec and  $A = 22.56 \times 10^{-8}$  cm<sup>2</sup> into equation 21 yields

Active base doping =

$$\frac{Q_{BO}}{qA} = \frac{1.52 \times 10^{-4}}{I_S} \text{ cm}^{-2}$$

Equation 21 also shows that Is, the multiplying factor for transistor current at a given bias, is inversely proportional to the total base doping. The lower the total base doping, the higher is the current at a given bias.

Transistors from the four experimental cells of the second wafer lot were further characterized to demonstrate the validity of these relationships. With the CMOS processing common to all cells, there should be no difference in the collector and emitter formation except  $Q_{1}$ that of normal process variation. The base implant energy and drive-in schedule were also kept constant with the base boron ion implant dose being the only process variable. It should be possible, therefore, to measure the collector current over many decades and obtain  $I_S$  from the intercept with the current axis at  $V_{BE} = 0$ . Once  $I_S$  is known, the active base doping ( $Q_{B0} / qA$ )

can be calculated and compared to the actual boron dose used for each device.

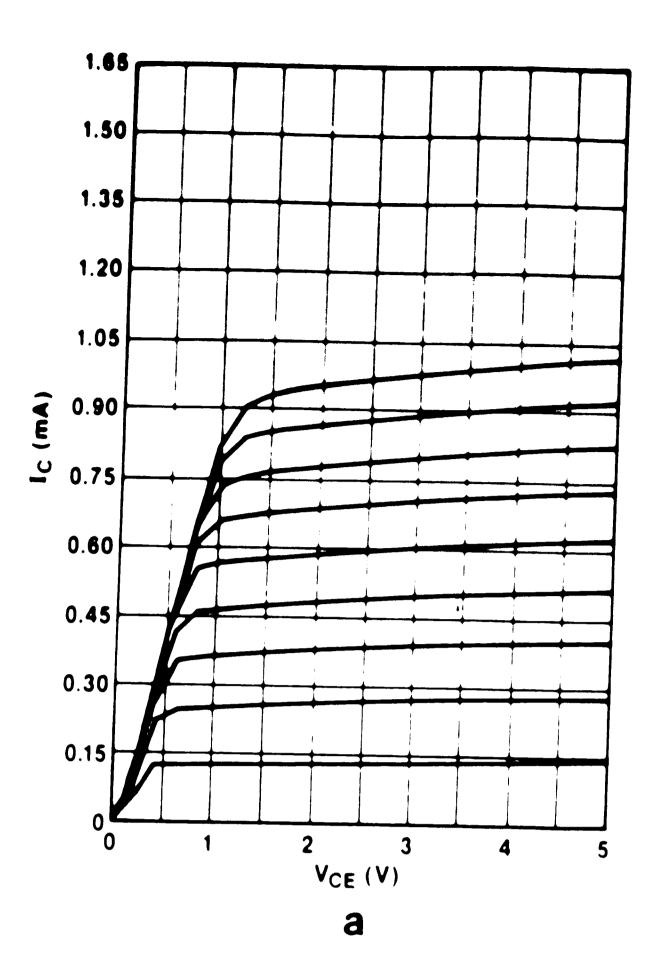

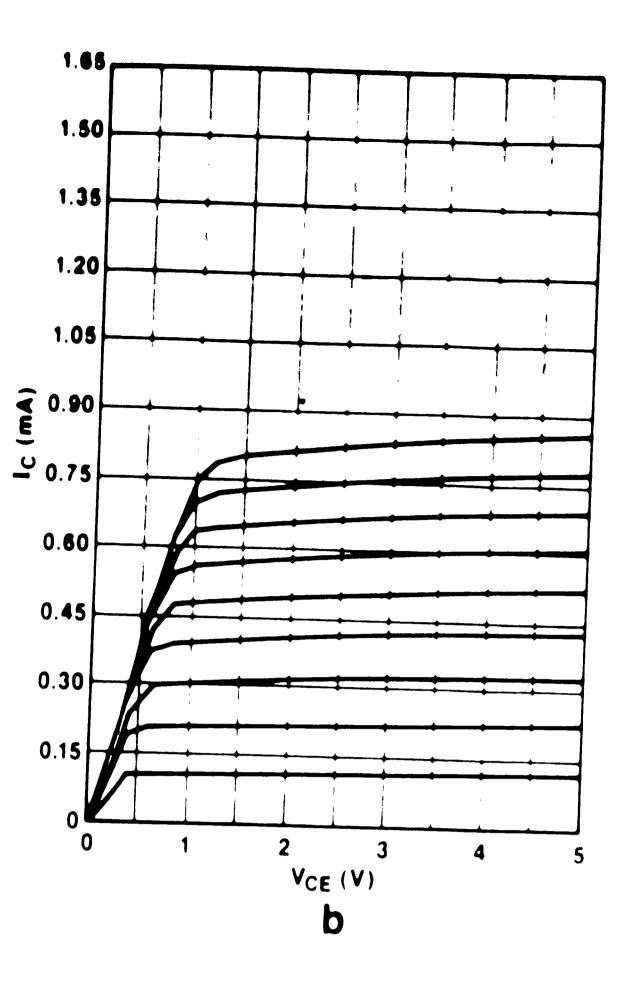

The transistors were characterized by measuring the forward-active gain ( $\beta$ ) versus baseemitter bias  $(V_{BE})$ , the logarithm of collector current  $(I_C)$  and base current  $(I_B)$  versus baseemitter bias ( $V_{BE}$ ) and the collector current ( $I_C$ ) versus collector-emitter bias ( $V_{CE}$ ) over a range of base current  $(I_B)$ . All measurements were done with an Electroglas 1034X probe station interfaced to a Hewlett Packard 4145B Semiconductor Parameter Analyzer.

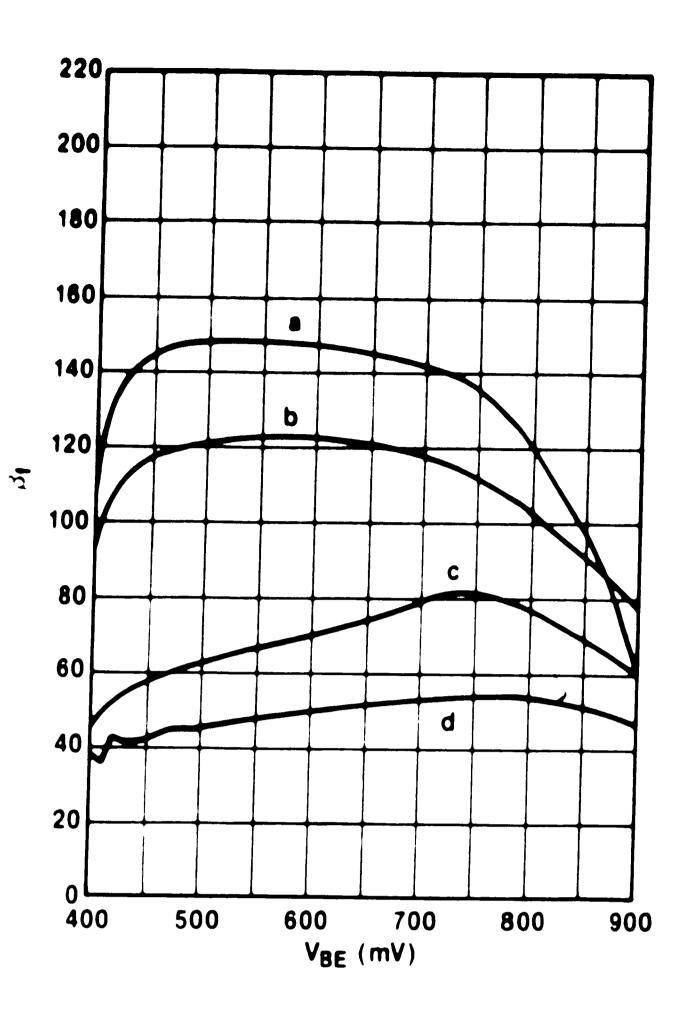

The forward-active gain ( $\beta$ ) versus base-emitter bias (V<sub>BE</sub>) was first measured in order to locate a device with a gain close to the average of the experimental cell and free of the  $\beta$  rolloff problem exhibited on many transistors. A plot of the gain versus  $V_{BE}$  for each of the four devices selected is shown in figure 15. With  $V_{BE}$  ranging from 0.4V to 0.9V, the collector current will vary from less than a nano ampere to more than a milli ampere. Very little  $\beta_f$ degradation was observed over this wide range of collector current for curves a, b and d. Curve c shows some of the effect of the  $\beta_f$  degradation due to the presence of recombination

Figure 15.  $\beta_f$  versus base-emitter bias (V<sub>BE</sub>) of the bipolar transistor for the active base implant conditions a)  $3.0 \times 10^{14}$  cm<sup>-2</sup> b)  $3.3 \times 10^{14}$  cm<sup>-2</sup> c)  $3.7 \times 10^{14}$  cm<sup>-2</sup> and d)  $4.0 \times 10^{14}$  cm<sup>-2</sup>. The emitter size is  $4.75 \mu m \times 4.75 \mu m$ .

centers in the emitter-base space charge region of the device.

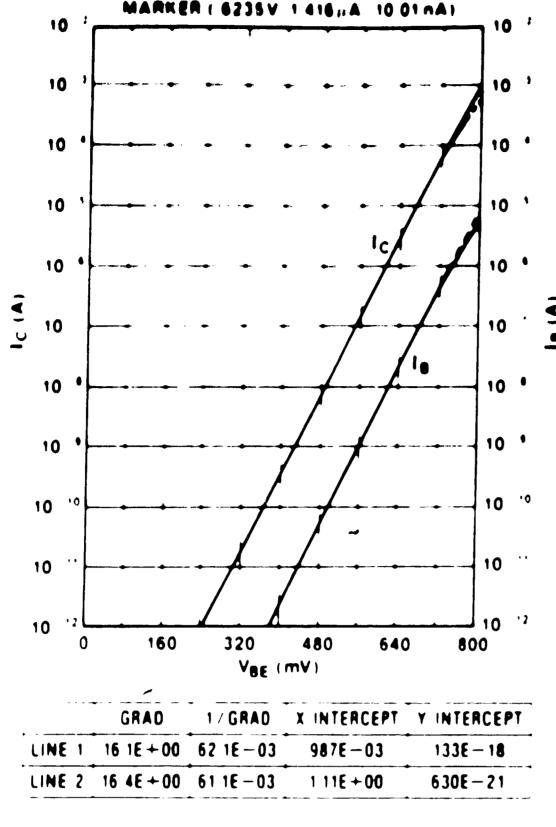

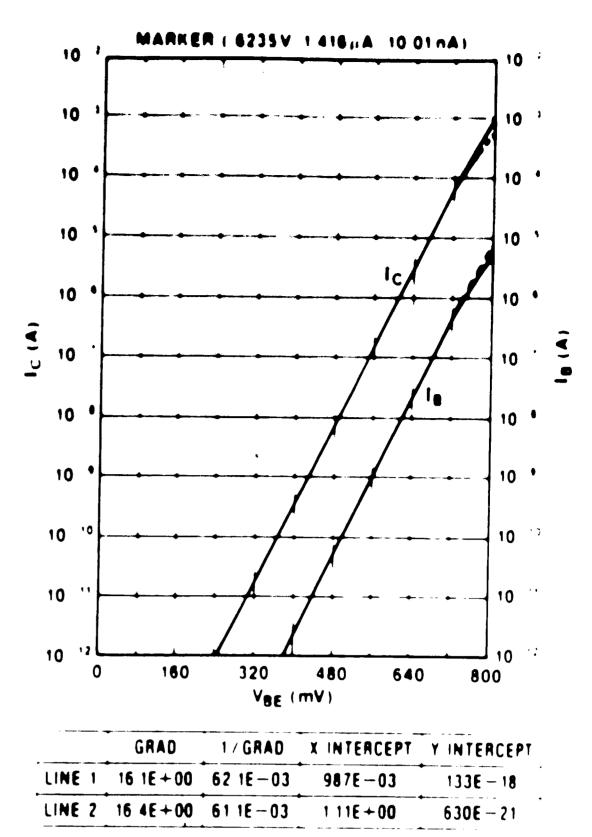

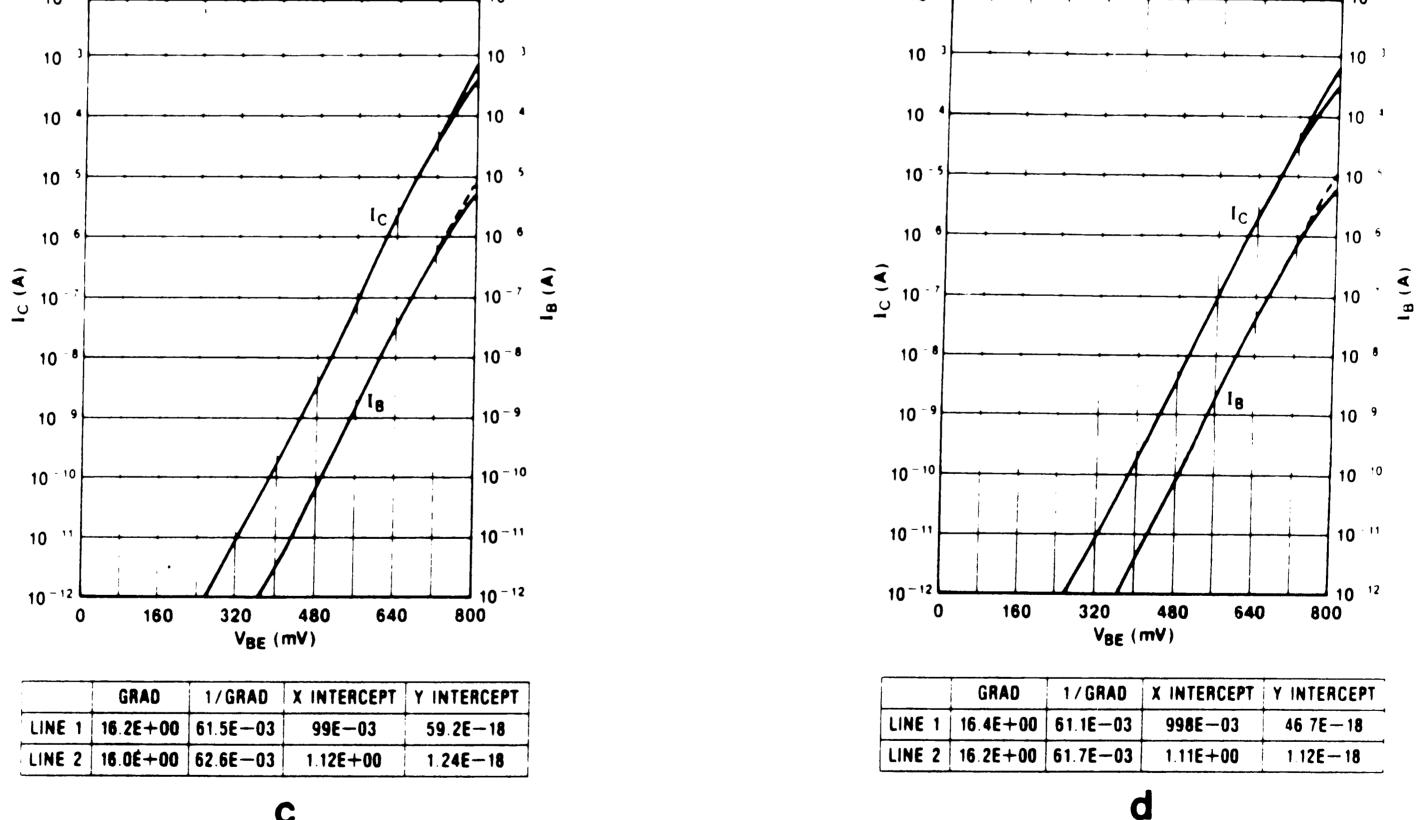

When plotting  $V_{BE}$  versus log  $I_C$  with  $V_{BC} = 0V$  (figure 16), a linear relationship over nearly eight decades of current was observed. The average slope of the four transistors was 61.6 mV/decade, very close to the voltage change for an ideal diode of 59.6 mV/decade. If the collector current,  $I_n$ , is expressed as

$$I_n \approx -I_S e^{\frac{q V_{BB}}{kT}}$$

(19)

where q is the electronic charge and kt the Boltzman energy,  $I_S$  can be measured from the plot of log  $I_C$  versus  $V_{BE}$ . These measurements and the extrapolations of collector current to the current axis at  $V_{BE} = 0$  are shown in the next figure with the results summarized in table 6.

#### a

d

Figure 16. Collector current  $I_C$  and base current  $I_B$  versus base-emitter voltage  $V_{BE}$  for a bipolar transistor with an active base doping of a)  $3.0 \times 10^{14}$  cm<sup>-2</sup> b)  $3.3 \times 10^{14}$  cm<sup>-2</sup> c)  $3.7 \times 10^{14}$  cm<sup>-2</sup> and d)  $4.0 \times 10^{14}$  cm<sup>-2</sup>. The emitter size is  $4.75 \mu m \times 4.75 \mu m$ .

-. ٠ . . . .

| Base Implant Dose                    | β    |                               | Y Intercept             |                           |

|--------------------------------------|------|-------------------------------|-------------------------|---------------------------|

| @                                    | @    | for                           | or                      | $\frac{Q_{B0}}{qA}$       |

| 100 keV                              | 10µА | I <sub>C</sub><br>(mV/decade) | I <sub>S</sub><br>(A)   | qA<br>(cm <sup>-2</sup> ) |

| $3.0 \times 10^{14} \text{ cm}^{-2}$ | 141  | 62.1                          | 133.0×10 <sup>-18</sup> | 1.14×10 <sup>12</sup>     |

| $3.3 \times 10^{14} \text{ cm}^{-2}$ | 116  | 61.6                          | 85.8×10 <sup>-18</sup>  | 1.77×10 <sup>12</sup>     |

| $3.7 \times 10^{14} \text{ cm}^{-2}$ | 75   | 61.5                          | 59.2×10 <sup>-18</sup>  | 2.57×10 <sup>12</sup>     |

| $4.0 \times 10^{14} \text{ cm}^{-2}$ | 53   | 61.1                          | 46.7×10 <sup>-18</sup>  | 3.25×10 <sup>12</sup>     |

- TABLE 6. Measurements of forward active current gain ( $\beta_f$ ), collector current slope, and  $I_s$ with calculated values of  $Q_{B0}/qA$  for each base implant dose of the second experimental wafer lot.

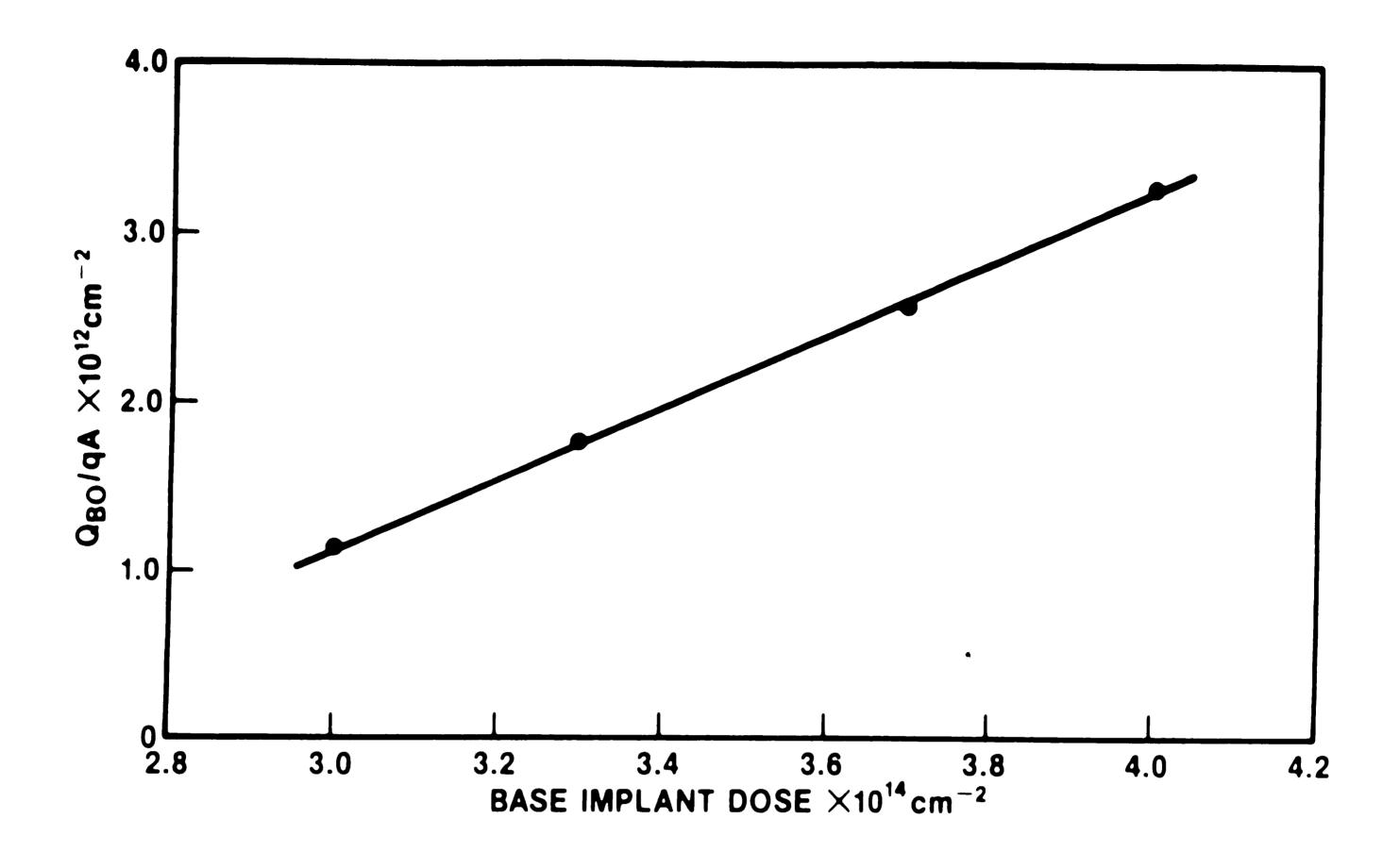

- A graph of  $Q_{B0}/qA$  versus base implant dose, figure 17, clearly shows the direct

relationship of the total hole charge in the quasi-neutral base region  $(Q_{B0})$  to the total base doping.

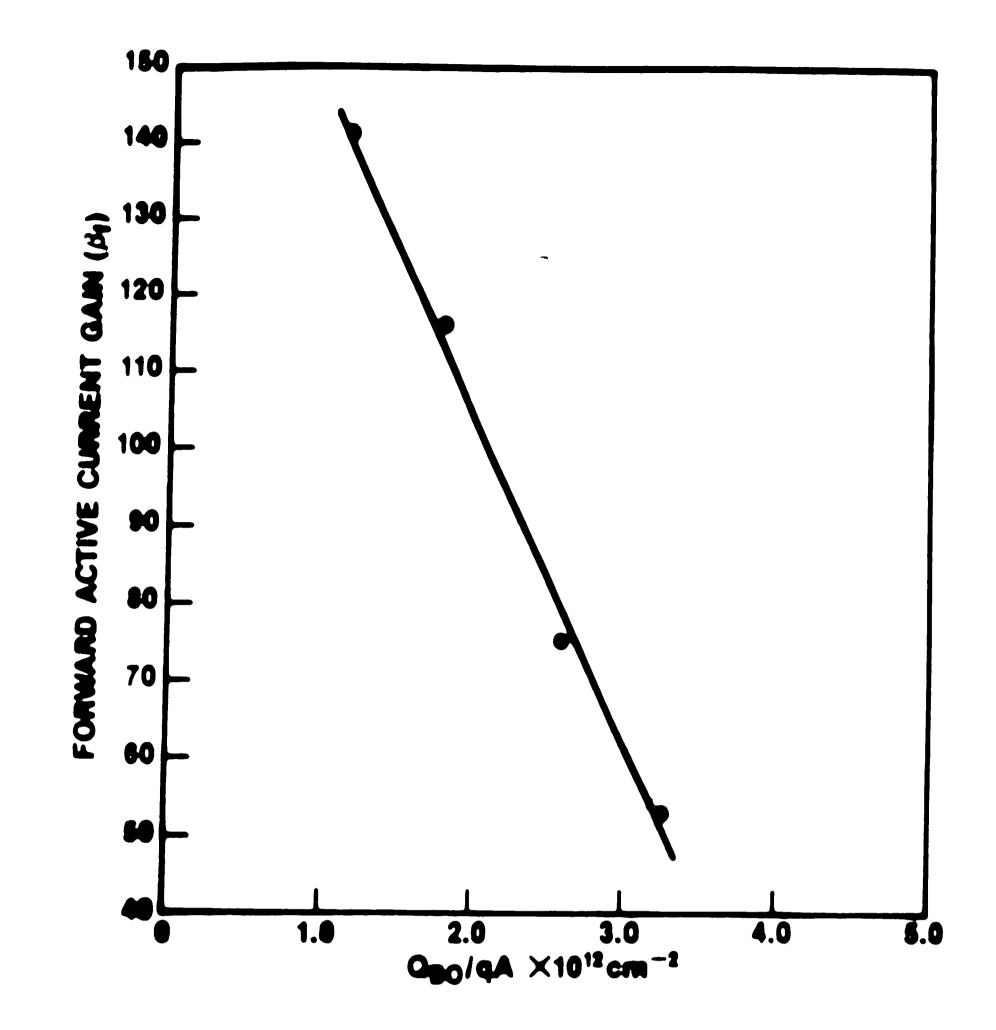

From equation 33 we know that the common-emitter current gain

$$\beta \approx \frac{N_E}{\frac{Q_{BO}}{qA}}$$

(33)

where  $N_E$  is the emitter doping and  $Q_{B0}$  is the total base doping in the quasi-neutral base. The inverse relationship between the common-emitter current gain and doping in the quasi-neutral base region is shown in figure 18 where  $B_f$  is plotted against  $Q_{B0}/qA$  for the four measured transistors of the second experimental lot. Since the emitter charge, base ion implant energy and thermal drive-in schedule are constant the gain of the bipolar transistor is inversely proportional to base Gummel number or active-base implant dose. The relationship given by equation 33 is verified in figure 18.

41 . .. . . ÷....

# Figure 17. A plot of the total hole charge in the quasi-neutral base region $Q_{B0}/qA$ versus base implant dose