#### Lehigh University Lehigh Preserve

Theses and Dissertations

1974

# A methodology for evaluating compiler performance /

James Patrick Clancy Lehigh University

Follow this and additional works at: https://preserve.lehigh.edu/etd Part of the Industrial Engineering Commons

#### **Recommended** Citation

Clancy, James Patrick, "A methodology for evaluating compiler performance /" (1974). *Theses and Dissertations*. 4448. https://preserve.lehigh.edu/etd/4448

This Thesis is brought to you for free and open access by Lehigh Preserve. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of Lehigh Preserve. For more information, please contact preserve@lehigh.edu.

# A METHODOLOGY FOR EVALUATING COMPILER PERFORMANCE

14

nie Cester Cest

、 なかー 、 ないとうなど 中部のをなる を見からる 、 そう、 ー・

by

James Patrick Clancy

Presented to the Graduate Committee

of Lehigh University

in Candidacy for the Degree of

Master of Science

in

Industrial Engineering

Lehigh University

1974

ُ ٦

#### CERTIFICATE OF APPROVAL

This thesis is accepted and approved in partial fulfillment of the requirements for the degree of Master of Science.

<u>974</u>

7 Professor in Charge

ц.

Chairman of the Department of Industrial Engineering

н Ч

ii 🤞 🕺 🕺

#### ACKNOWLEDGEMENTS

;.··

**s** .

τ.

والمتح فبالرباط فيتصافر والجماد المكانية

5

:•

.,,

The author wishes to express his appreciation to Dr. W. Shively, who served as facility advisor, for his advice and encouragement during the preperation and writing of this thesis.

Appreciation is also extended to Mr. G. E. Whitney and Dr. C. W. Cheng of Western Electric Company's Engineering Research Center for suggesting the topic and providing technical guidance and assistance throughout this project.

.

iii

# TABLE OF CONTENTS

Page

•

• •

.".

,

•

5

•

•

r

|         | ·                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| LIST OF | TABLES                                                                                                                                                                                                                                                                                                                                                                                                                         | vi                                                             |

| LIST OF | FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                        | vii                                                            |

| ABSTRAC | T                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                                                              |

| CHAPTER | <pre>1 Introduction.<br/>1.1 Problem Description.<br/>1.2 Methodology.<br/>1.2.1 Abstract Computer Definition.<br/>1.2.2 Compiler Design.<br/>1.2.2.1 Source Language.<br/>1.2.3 Experiment.</pre>                                                                                                                                                                                                                             | 3<br>4<br>6<br>7<br>11<br>11<br>13                             |

| CHAPTER | <pre>2 Definition of Star Abstract Computer.<br/>2.1 Architecture.<br/>2.1.1 Memory Structure.<br/>2.1.2 Addressing.<br/>2.1.3 Registers.<br/>2.2 Instruction Set.<br/>2.2.1 Single Operand Instructions.<br/>2.2.2 Double Operand Instructions.</pre>                                                                                                                                                                         | 15<br>15<br>16<br>20<br>22<br>25<br>25                         |

| CHAPTER | <pre>3.1 Compiler Description.<br/>3.1.1 Tables of Information.<br/>3.1.2 Symbolic Addresses.<br/>3.1.3 Analysis Phase.<br/>3.1.4 Internal Form of the Source Program.<br/>3.1.5 Synthesis Phase.<br/>3.2 Code Generation Techniques.<br/>3.2.1 Basic Executable Code.<br/>3.2.2 Register Map.<br/>3.2.3 Register Status.<br/>3.2.4 Assigned Base Register.<br/>3.3 Procedure Descriptions.<br/>3.4 Compiler Simulation.</pre> | 27<br>27<br>29<br>32<br>34<br>35<br>36<br>30<br>41<br>42<br>46 |

| CHAPTER | <pre>4 Experiment</pre>                                                                                                                                                                                                                                                                                                                                                                                                        | 48<br>48<br>50                                                 |

| CHAPTER | 5 Results and Conclusions                                                                                                                                                                                                                                                                                                                                                                                                      | 56<br>56<br>65                                                 |

# TABLE OF CONTENTS (cont'd)

|              |                                   | Pag |

|--------------|-----------------------------------|-----|

| 5.3          | Recommendations for Further Study | 66  |

| BIBLIOGRAPHY | ,                                 | 68  |

| APPENDIX A   | List of Symbols                   | 69  |

| APPENDIX B   | Quadruple Generation              | 71  |

| APPENDIX C   | Logical Procedure Descriptions    | 75  |

| APPENDIX D   | FORTRAN Conversion Procedure      | 78  |

| APPENDIX E   | Analysis of Sample Data           | 80  |

| APPENDIX F   | Glossary of Terms                 | 87  |

| VITA         |                                   | 93  |

••.

## LIST OF TABLES

| Table |                                                                                                                                                    | Pag |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1     | Storage Requirements and Execution Times of<br>Instructions Used for Simulated Execution                                                           | 51  |

| 2     | Results and Analysis of Experiment with Five<br>Levels of Optimization for Small Program<br>Environment (17 Arithmetic Statements per<br>Program)  | 57  |

| 3     | Results and Analysis of Experiment with Five<br>Levels of Optimization for Medium Program<br>Environment (46 Arithmetic Statements per<br>Program) | 58  |

| 4     | Results and Analysis of Experiment with Five<br>Levels of Optimization for Large Program<br>Environment (118 Arithmetic Statements per<br>Program) | 59  |

| 5     | Results and Analysis of Experiment with Four<br>Levels of Optimization for Small Program                                                           |     |

#### je

| ,  | vi                                                                                                                                                           |    |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|    |                                                                                                                                                              |    |

| 10 | Frequency Distribution of the Number of<br>Quadruples per Arithmetic Statement                                                                               | 86 |

| 9  | Cumulative Frequency Distributions of the<br>Number of Arithmetic Statements per Sampled<br>FORTRAN Program and the Total Number of<br>Arithmetic Statements | 83 |

| 8  | Cumulative Frequency Distributions of the<br>Number of Lines per Sampled FORTRAN Program<br>and the Total Number of Lines Sampled                            | 81 |

| 7  | Results and Analysis of Experiment with Four<br>Levels of Optimization for Large Program<br>Environment (118 Arithmetic Statements per<br>Program)           | 62 |

| 6  | Results and Analysis of Experiment with Four<br>Levels of Optimization for Medium Program<br>Environment (46 Arithmetic Statements per<br>Program)           | 61 |

|    | Environment (17 Arithmetic Statements per<br>Program)                                                                                                        | 60 |

#### LIST OF FIGURES

r

•

•

•

·

EN.

•

•

| Figure | ·                                                                                      | Page |

|--------|----------------------------------------------------------------------------------------|------|

| 1      | Some Characteristics of the PDP-11 and IBM 360 Computers                               | 8    |

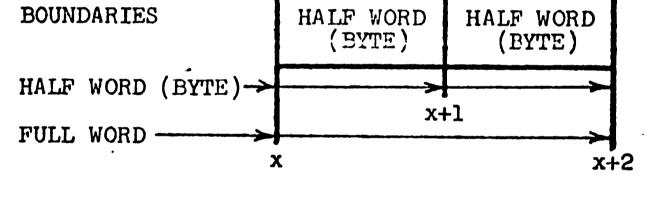

| 2      | Memory Formats of the IBM 360 and PDP-11                                               | 17   |

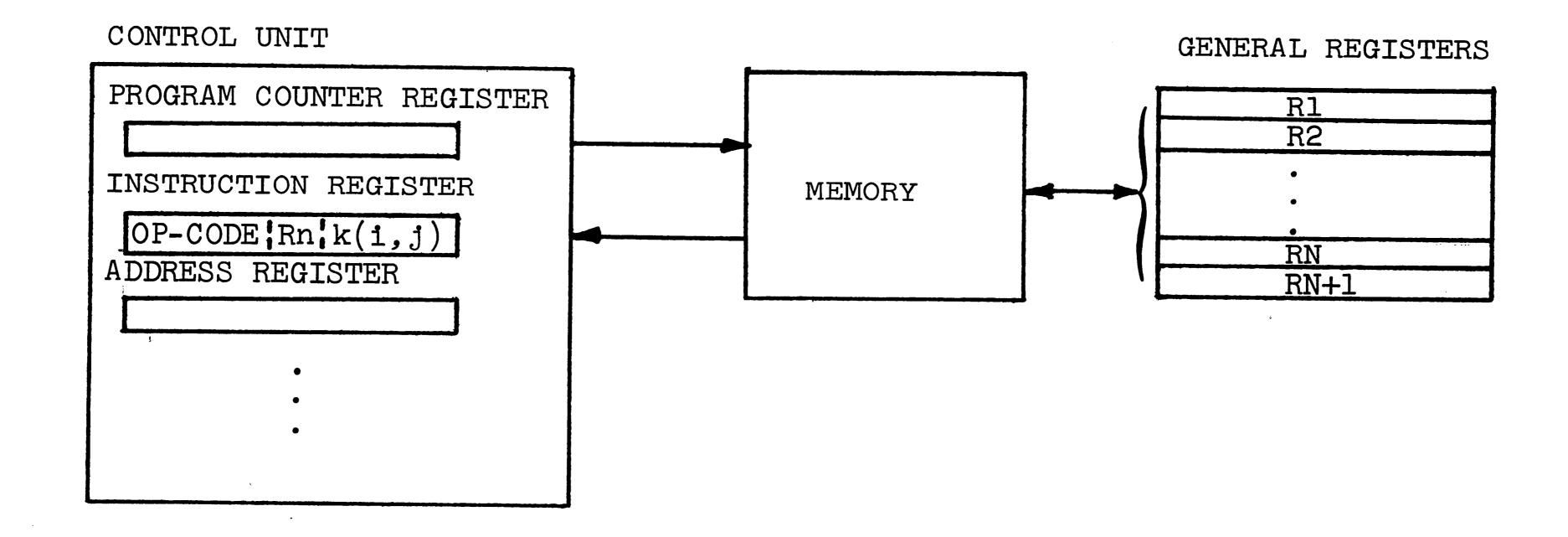

| 3      | The Structure of Star Abstract Computer(SAC)                                           | 23   |

| 4      | Conceptual Diagram of a Compiler                                                       | 28   |

| 5      | Diagram of Experimental Procedure                                                      | 55   |

| 6      | Example of Quadruple Generation                                                        | 74   |

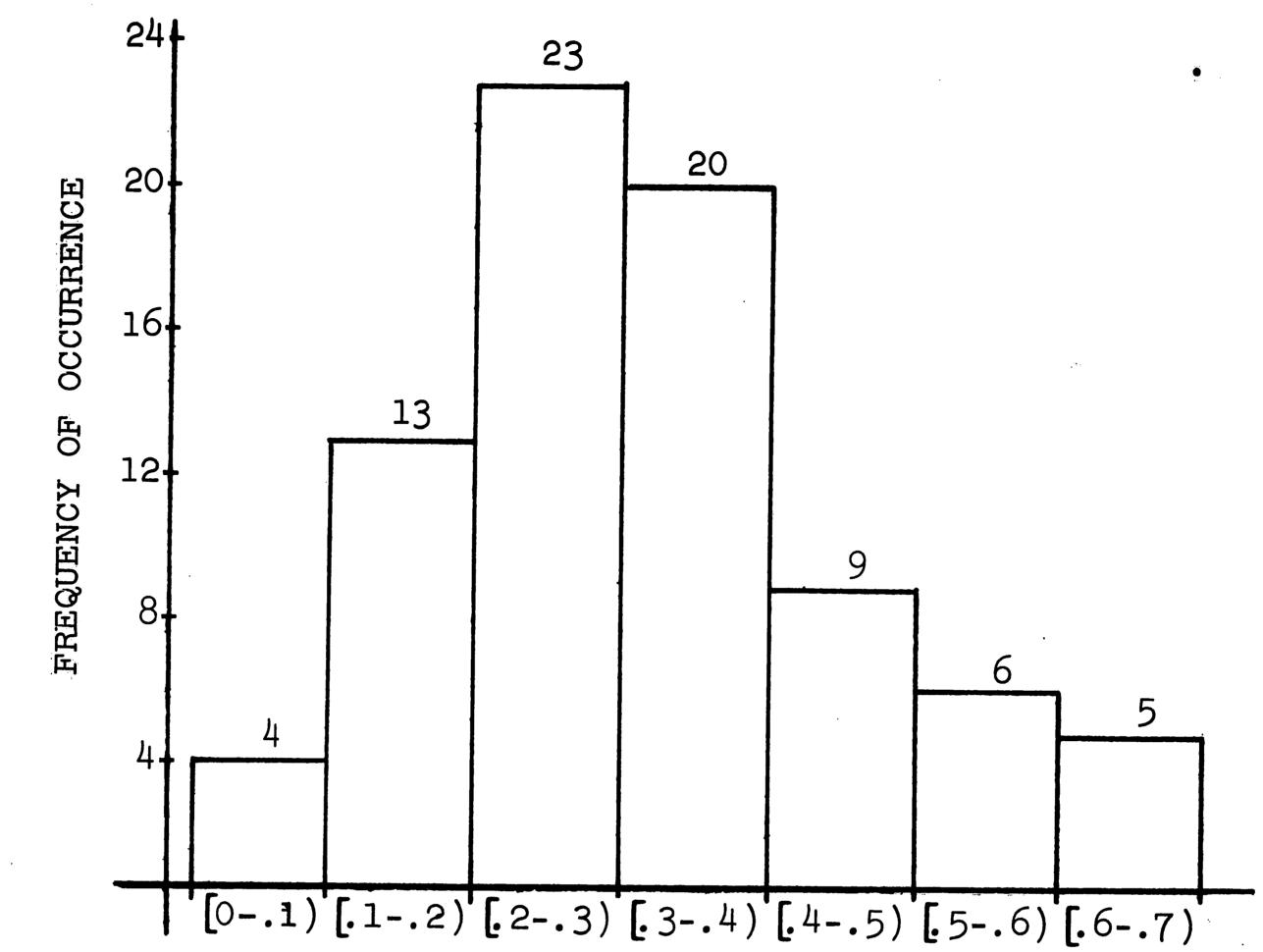

| 7      | Frequency Distribution of the Ratio of<br>Arithmetic Statements to Program Size(Lines) | 85   |

..

1

*3* А.

$\mathcal{T}$ 0

• **t**. ....

.51

## vii

•

н Х С ٠.

#### ABSTRACT

an a star frank A Lake A se

.

•

The introduction of compilers and high-level (user oriented) programming languages has made the computer available as a tool to those with only limited programming knowledge. Consequently, a great deal of effort was and still is being devoted to developing techniques to improve the object code produced by compilers. However, the measurement of overall compiler performance in terms of the cost of both compiling and executing a wide range of programs has been neglected, primarily due to the variations in machine and program environments. A methodology is proposed which can be applied to the measurement of compiler performance. The methodology consists of three parts: 1) define an abstract computer which can mimic the machine environment by using parameters; 2) design a compiler for this abstract computer; 3) design an experiment that will allow the application of statistical methods to the measurement of performance for different machine and program environments. The methodology is tested using a subset of FORTRAN describing arithmetic operations and a simulated compiler. A simplified abstract computer is defined and a compiler is described which can generate code for this computer. Three optimization techniques for allocating registers in the compiler and the method of simulating

1

compilation are described. An experiment is described which can serve as a prototype for implementation of this methodology. Analyses of the experimental results using an analysis of variance test and Duncan's multiple range test are provided. The results indicate that this methodology can be a valuable tool in measuring compiler performance.

#

$\bigvee$

ut de la companya de

۲ ۲ 2

.

.

#### CHAPTER 1

#### 1.0 Introduction

1

A translator is a program which accepts as input a program in one language called the source language and produces as output an equivalent program in another language called the object language. If the source language is a high level programming language and the object language is assembly or machine language, the translator is referred to as a compiler and the object program is referred to as object code [3]. Compilers, by allowing the use of high level programming languages, have made the computer available as a tool to those with only limited programming knowledge, such as engineers, scientists and businessmen. However, early compilers produced code which was not as efficient in terms of execution time and storage allocation as code written in assembly or machine language by experienced programmers.

A great deal of effort was and still is being devoted to developing techniques to optimize (a more accurate word is improve) the code generated by compilers. These techniques can generally be classified as machine dependent and machine independent. Those techniques which manipulate the source language are machine independent. The elimination of common subexpressions is an example of this type. Those techniques which manipulate the object

code are machine dependent. Register assignment algorithms are an example of this type. As a result of the work in this field, most present day compilers for the widely used programming languages can produce code which is as good as hand coding in a fraction of the time that hand coding requires. There remains, nevertheless, a large and growing number of special purpose programming languages which still require the design of compilers.

As in most design work, trade-offs must be made. The compiler designer must decide what level of code optimization is desired beyond the generation of basic executable code. The more optimization techniques included in the compiler, the more complex it becomes with resulting increases in storage requirements and compile time. The designer must trade-off these increases against the hoped for improvements in the storage requirements and/or execution time of the object code produced. These decisions require some method of determining performance levels of different compilers (or different versions of the same compiler).

#### 1.1 Problem Description

If the performance measure is the cost, as yet undefined, for compilation and execution of a program, then, theoretically, a measure of performance could be written as

#### Ct = Cc + hCe

X

where: Ct is the total cost of compiling and executing.

Cc is the total cost of compiling.

Ce is the total cost of executing.

h is the number of executions.

If these costs were known, then a decision could be made as to the relative merits of different compilers as a function of the number of executions of the object code. However, since these cost elements vary for each compiler program combination, this approach is not very practical.

Another difficulty in measuring performance is the variation in computer environments. As an example, consider the differences between an educational and

business environment. In an educational environment involved in the teaching of programming languages, the programs would typically be small, require little time to execute and require few repeated executions. In the business environment, the programs, which might involve payroll, inventory or accounting applications, would typically be large, require much execution time and are executed periodically. The best compiler for the educational environment would have little, if any, optimization, since compile time would probably exceed execution time. However, the business environment would require a very high level of optimization, since the

savings in repeated execution costs would more than offset the increased compile time. This variation in environments also extends to machines. Due to the machine dependence of many optimization techniques, the performance of a compiler including these techniques will vary depending upon the target machine.

Although there is an extensive literature on compiler optimization, there is none on the measurement of compiler performance. The typical paper [1,7,8] which describes a technique for optimization also defines a criteria to measure the performance of the technique. This criteria is usually the total number of object code instructions generated or the number of memory references required to perform a specific operation. Since the effect of optimization techniques on a specific compiler depend upon not only the existence of the condition which is to be improved but also the frequency with which this condition occurs in the compiler environment, a method of measuring overall performance which considers these factors is required.

## 1.2 Methodology

An approach to this problem is to develop a methodology for evaluating compiler performance. The methodology proposed consists of three parts:

- 1) Define an abstract computer which can mimic the machine environment by means of parameters.

- 2) Design a compiler (or compilers) for this abstract computer which can generate code which (with some intermediate processing) can be executed on the target machines.

- 3) Design an experiment that will allow the application of statistical methods to measure the performance of this compiler for different machine and program environments.

- 1.2.1 Abstract Computer Definition

The abstract computer developed is called the STAR <u>ABSTRACT COMPUTER</u> (SAC). Its definition requires the

specification of both an architecture and instruction set. These are described in Chapter 2. Since the target machines, IBM 360 and PDP-11, differ markedly in instruction capability and architecture, in the interests of simplicity, the definition of SAC was biased towards the IBM 360. Figure 1 lists some of the characteristics of the target machines. One advantage of this abstract computer, quite apart from the subject of this thesis, is its tutorial uses in teaching machine concepts without the necessity of learning assembly language or pecularities of specific machines.

#### **PDP-11**

Each operand consists of a register number and an address mode indicating how that register is to be used. There are eight address modes. The register mode indicates that the value of the operand is in the specified register. The index mode indicates that the contents of the register specified is to be added to the contents of the word following the instruction to form the address of the operand. Two modes are used to increment and decrement registers to facilitate stack operations. In addition, all four modes can be used to specify an indirect address where the address obtained from the instruction points to the address of the operand rather than the operand itself. The use of the program counter register in an operand address permits immediate addressing where the operand itself is in the word following the instruction in memory.

FIGURE 1. SOME CHARACTERISTICS OF THE PDP-11 AND IBM 360 COMPUTERS.

$\boldsymbol{\omega}$

#### IBM 360

#### ADDRESSING

Base-displacement addressing is used. Register operands are addressed by their number. Operands in storage are addressed by the sum of a displacement included in the instruction and the contents of a base register whose number is included in the instruction. The address may also include the contents of an index register specified in the instruction. The differentiation between a register number used as a base or index register and a number used to address a register is made by the use of different instructions for the different locations of operands. Indirect addressing is not available. Immediate addressing is available but the operand contained in the instruction is limited to one byte in length.

#### PDP-11

Both single and double operand instructions are used. Operands are designated as either a source or destination operand. Results of an instruction are left in the address specified by the destination operand. Neither operand is required to be in a register. Instructions include register to register, register to storage and storage to storage operations. There is one set of instructions which are used for the various combinations of addressing modes. For example, the "MOV" instruction can move an operand from one register to another, from a storage location into a register, from a register into a storage location or from one location in memory to another, depending upon the address modes of the operands.

Eight General registers are available numbered 0-7. Register 6 is used as a stack pointer and has hardware functions associated with

6

#### IBM 360

#### INSTRUCTION SET

Double operand instructions are used. No single operand instructions are available. There are five types of instructions which are used depending upon the location of the operands. For example, RR type instructions are used when both operands are in registers, RS and RX type instructions are used when the first operand is in a register and the second operand is in memory, and SS type instructions are used when both operands are in memory. The SI type of instruction is used when one operand is in memory and the other operand is contained in the instruction (this is the immediate operand and is limited to one byte in length).

#### REGISTERS

Sixteen general registers are available numbered 0-15. Registers 0, 1, 13, 14 and 15 are reserved by convention for such uses as passing

FIGURE 1. (cont'd) SOME CHARACTERISTICS OF THE PDP-11 AND IBM 360 COMPUTERS.

#### PDP-11

REGISTERS (cont'd)

interrupts and subroutine calls. Register 7 is the program counter register. (Some configurations can expand to 16 registers - 3 sets of 6 general purpose registers, 3 stack pointers and 1 program counter register.)

0

.

\*

FIGURE 1. (cont'd) SOME CHARACTERISTICS OF THE PDP-11 AND IBM 360 COMPUTERS.

IBM 360

subroutine parameters. The program counter register is not addressable by the programmer.

#### 1.2.2 Compiler Design

Since the design of an actual compiler is beyond the scope of this thesis, a compiler was simulated in FORTRAN. Chapter 3 describes the compiler and the methods used to simulate its various functions. A subset of FORTRAN describing arithmetic operations was chosen as the source language for the simulated compiler in order to allow the sampling of arithmetic statements from actual FORTRAN programs.

#### 1.2.2.1 Source Language

This subset of FORTRAN consists of scalar variables and constants of type integer. The allowable symbols are the alphabetic characters, A-Z, and the numeric characters, 0-9. Variable names may be single alphabetic characters only. Although no execution of the code from the simulated compiler is performed, scalar constants are included for completeness and for possible future implementation. The operators allowed in this language are

| + - / *                                  | Arithmetic operators       |  |  |  |  |

|------------------------------------------|----------------------------|--|--|--|--|

| ( )                                      | Precedence operators       |  |  |  |  |

|                                          | Assignment operator        |  |  |  |  |

| ;                                        | End of statement operator  |  |  |  |  |

| The operations of addition, subtraction, |                            |  |  |  |  |

| multiplication, division and             | d unary minus are the only |  |  |  |  |

arithmetic operations which will be considered. Since the

same operator is used to represent subtraction and unary minus, the latter must be determined from the context of the arithmetic statement. This language contains no branches of any kind so that any section of code has only one path to enter and one path to exit. This type of code is referred to as straight-line code.

A program in the source language consists of a sequence of arithmetic statements which have the general form:

#### A = B;

$\bigcap$

where A is a variable, B is an expression, = is the assignment operator and ; is the end of statement

operator. At execution time, the expression B is evaluated and the resultant value is assigned to the variable A. An expression is a sequence of scalar variables or constants of type integer seperated by arithmetic operators and parenthesis in accordance with mathematical convention and the following rules:

- 1. An expression may consist of a single basic element such as a scalar variable or constant.

- 2. Compound expressions may be formed by using the arithmetic operators to combine basic elements.

- 3. Compound expressions must be constructed according

- to the following rules:

**~**.

- a. Any expression may be enclosed in parenthesis and considered to be a basic element.

- b. Expressions which are preceeded by a sign are also expressions. (For convienence, leading + signs were not allowed)

- c. If the precedence of operations is not given

explicitely by parenthesis, it is understood to

be the following (in order of decreasing

precedence):

- \* and / multiplication and division

- + and addition and subtraction or

#### unary minus

In the case of operations of equal precedence, the calculations are performed from left to right.

d. No two arithmetic operators may appear in sequence.

Arithmetic expressions described by the above rules are said to be in infix notation.

#### 1.2.3 Experiment

The last step of this methodology is to design an experiment and select apropriate statistical tests which will serve as a prototype for a systematic evaluation procedure. These tests should have the ability to detect differences among alternative compilers (or versions of

the same compiler) due to different machine and program environments as well as indicating preferred alternatives. Inherent in this step is the definition of a cost function to characterize the compiler performance. The costs dealt with are limited to simulated execution costs. The compilation costs were not simulated since these would depend upon the skill of the compiler designer rather than the execution time of the simulated compiler. Chapter 4 describes the cost function, the experiment and the statistical tests used.

~~;

· 14

9**4**, #

r · · ·

#### CHAPTER 2

## 2.0 Definition of Star Abstract Computer

One of the reasons for using an abstract computer is to reduce the variability in the machine environment. If the common features of the target machines are identified and included in SAC, then optimization techniques which depend upon these features become "machine independent", at least for the machines of interest. Since the purpose of this thesis is to describe a methodology rather than develop the ideal SAC, to facilitate presentation, the architecture described below is biased towards the IBM 360, particularly in the method of addressing storage. Similiarly, the instruction set is limited to those operations which are required for integer arithmetic. However, in an actual implementation of this methodology, the desired instruction set would be the maximal intersection of the instruction sets of the target machines. Appendix A contains a list of symbols used in this and subsequent chapters.

#### 2.1 Architecture

#### 2.1.1 Memory Structure

The basic unit of memory is a word although the word size in terms of bytes (one byte equals eight bits) will not be specified. The two computers of interest use the byte as the basic unit of storage (i.e. the smallest

directly addressable unit). However, their differences in word size makes a common ground difficult and would unnecessarily complicate the symbolic nature of SAC. The IBM 360 [10] uses four bytes per word (32 bits) and allows half-word, full-word and double-word references, while the PDP-11 [11] uses two byte (16 bit) words and allows only half-word and full-word references. Figure 2 shows the memory formats of the target machines. Each word in memory is numbered consecutively from zero to some upper limit which is dependent upon the computer configuration available. This number constitutes the actual address of each word.

2.1.2 Addressing

Each word in memory is referenced by a number which indicates its actual address. In order for an instruction to reference an address, it must be able to contain a number as large as the highest address available. This could require extremely large instructions (large in the sense of the number of bits required to express them). In order to make all memory locations addressable, while at the same time limiting the size of the instructions, a scheme, which is derived from the IBM 360, is used. This scheme uses a register to specify a base address (BA) and the instruction to specify a displacement constant (DC), which, when added to the base address, provides the actual

|             | DOUBLE WORD |                     |      |           |                                         |      |      |      |

|-------------|-------------|---------------------|------|-----------|-----------------------------------------|------|------|------|

|             | FULL WORD   |                     |      | FULL WORD |                                         |      |      |      |

|             | HALF        | LF WORD / HALF WORD |      | . HALF    | WORD                                    | HALF | WORD |      |

| BOUNDARIES  | BYTE        | BYTE                | BYTE | BYTE      | BYTE                                    | BYTE | BYTE | BYTE |

| BYTE>       |             | ·                   |      | >         | >                                       | >    | >    | >    |

| HALF WORD>  | x+l         |                     | x+3  |           | x+5                                     |      | x+7  |      |

| FULL WORD   | x+2         |                     |      | х+б       |                                         |      |      |      |

| x+4         |             |                     |      |           | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |      |      |      |

| DOUBLE WORD |             |                     |      | ×         |                                         |      |      |      |

IBM 360 MEMORY FORMAT

| ALLOWABLE   | ADDRESSES                 |

|-------------|---------------------------|

| BYTE        | $\mathbf{x} = \mathbf{p}$ |

| HALF WORD   | x = p*2                   |

| FULL WORD   | x = p*4                   |

| DOUBLE WORD | x = p * 8                 |

#### PDP-11 MEMORY FORMAT

ALLOWABLE ADDRESSESHALF WORD(BYTE)x = pFULL WORDx = p\*2

x,...,x+1 ARE NUMERIC MEMORY ADDRESSES (ACTUAL ADDRESSES)

p = 0,1,2,...

FIGURE 2. MEMORY FORMATS OF THE IBM 360 AND PDP-11.

address required. Since registers are a full word in size, this provides the ability to reference the entire memory. (The IBM 360 requires only 24 of the 32 bits available for addressing). This method also uses the contents of another register called an index register. The use of an index register allows modification of an instruction address without permanently altering the instruction in memory by the use of arithmetic operations on the contents of this register. Thus, an address can be symbollically represented in the form k(i,j) where k is the displacement constant, i is the base register number and j is the index register number. The actual address

Webster and the second

specified is then

actual address = k + contents of base register i + contents of index register j

The actual address calculation is done in an address register, which is not addressable by the programmer, and neither k nor the contents of registers i or j are altered. By convention, if either i or j is zero, this means the number zero, rather than register zero. Thus k(0,0) addresses the k-th memory location. The instructions must be able to hold a displacement and two register numbers. The largest displacement allowed in SAC,  $K(=\max(k))$ , is dependent upon the number of bits available in the instruction. In the IBM 360, there are 12 bits to

hold the displacement constant. Thus,  $4096(=2^{12})$  bytes or 1024 full-words can be addressed from a given base register. The PDP-11 has the ability of using a full-word for the displacement constant and therefore can address  $65536(=2^{16})$  bytes or 32768 full-words from a given base register. Since our basic memory unit is the word, K is a parameter of SAC. For the IBM 360, K = 1023 and for the PDP-11, K = 32767.

Another advantage of base-displacement addressing is relocatability. Since the available memory locations, which are unknown at compile time, are determined when the object code is loaded, the addresses used in the object code can be altered by changing the base address values. Thus, the compiled program can be made relocatable to any area of memory. This ability is required in a multi-programming environment. Although this scheme allows for the use of an index register, this need not be used when dealing only with scalar variables and straight-line code. Consequently, a short-hand notation will be used such that k(i) is equivalent to k(i,0).

In addition to memory locations, data may be stored in registers. The address of a register is indicated by a unique number assigned to each register. Confusion with memory addresses is avoided by the form with which register addresses are specified. The address of a

register will be indicated by Rn which addresses the register numbered n. (The PDP-11 indicates register addresses by specifying a register number and an address mode indicating that the operand is in that register. The IBM 360 uses different instructions depending upon whether the operands are in memory or registers.)

#### 2.1.3 Registers

١.

.

this -

Registers are hardware devices used for the temporary storage of one or more words to facilitate arithmetic, logical or transferral operations in the computer. They are frequently referred to as "fast memory" because of their extremely fast access time.

Those registers which are used by the control unit of the computer to control the execution of the program are generally not addressable by the programmer. These include the program counter (PC) register, the instruction register and the address registers. The PC register holds the actual address of the instruction currently being executed. Upon completion of execution, this register is automatically incremented by 1, thereby pointing to the next instruction to be executed. The control unit uses this register to load the next instruction into the instruction register. This register controls the actual address calculations using the address registers and the execution of the operation code portion of the

instruction.

9

The registers that are available for the programmer's use are referred to as general purpose registers. The term general purpose register refers to those registers which can be used as accumulators to perform arithmetic operations or as base and index registers to address storage locations.

4

A minimum of two general purpose registers are required for arithmetic operations when base-displacement addressing is used. This can be understood from the situation when the value of one operand is in a register and the other operand requires a register to address its value in storage. However, the multiplication and division operations in both the IBM 360 and the PDP-11 require two consecutive registers. In multiplication of two full words, the result will be a double-word (i.e. 16 bits times 16 bits yields 32 bits) requiring two full-word registers. In division, one register is required to hold the quotient and another to hold the remainder. Since these are the target machines of SAC, a minimum of three general purpose registers will be assumed.

Since the source language is limited to scalar variables of type integer, the remainder in division is not required due to truncation. In multiplication, it is usually sufficient to retain only the low-order register.

However, if the high order register must also be retained, this requires scaling and arithmetic shift operations to

save the contents of both registers in a full-word of storage. Since this requirement would unnecessarily complicate the instruction set, it is assumed that the low order register need only be saved and the high order register can be ignored. Even though these operations ignore the result of the additional register, it is still included to facilitate compatibility with the target machines. The maximum number of general purpose registers, N(=max(n)), is dependent upon the target machines and is a parameter of SAC.

In addition to the N general purpose registers, another register, with limited use, is required. This register is assigned the special function of holding the address of the first memory location available at execution time. This register can be used only as a base register and not for arithmetic operations. It is assigned the address (N+1), and, for convienence, will be referred to as the R-th register. The purpose of this register will be described in the next chapter. A diagram of the SAC memory structure is shown in Figure 3.

## 2.2 Instruction Set

i de la composition d Inde la composition de la composition de

> The instruction set for SAC uses both single and double operand instructions with each instruction

23

2

-

-

÷. -

FIGURE 3. THE STRUCTURE OF STAR ABSTRACT COMPUTER (SAC)

requiring a full word of storage. register to register (R/R) operations as well as register to storage (R/S) operations are available with a single set of instructions used for both types of operations. (The IBM 360 uses different instructions for the same operation depending upon the location of the operands). Storage to storage operations are assumed not available. All operations require that the first operand be in a register. The following notations are used to explain the instructions:

a

[Rn, Rn+1]

1

Either a register, Rn, or a memory location, k(i). In the context of an instruction, "2" should be read as "the address specified by 2". In the instructions which follow, a may not be the same register as the first operand but may use that register as a base register. For example, the instruction LOAD R2,R2 is not allowed, but LOAD R2,k(2) is allowed. This is possible since the address calculation takes place before the operation code portion of the instruction is executed and does not change the contents of the specified base register. The concatenation of registers n and n+1. This means that the indicated register

A

## pair functions as one register.

÷ .

- 2.2.1 Single Operand Instructions NEG Rn Changes the sign of the contents of Rn. 2.2.2 Double Operand Instructions LOAD Rn, a Places the contents of 2 into Rn. The previous contents of Rn are lost and the contents of a are unchanged. STORE Rn, k(i) Puts the contents of Rn into memory location k(i) (i may equal n). The contents of Rn are unchanged and the previous contents of k(i) are lost. Adds the contents of a to the contents of ADD Rn, a

The contents of a are unchanged and Rn. the previous contents of Rn are lost. Subtracts the contents of a from the SUB Rn, a contents of Rn. The contents of a are unchanged and the previous contents of Rn are lost.

Both target machines require that multiplication and division be performed in a consecutive even-odd pair of registers. Therefore, the register, Rn, shown as the first operand in the subsequent instructions indicates the even-odd pair, [Rn,Rn+1]. (The PDP-11 also allows the use of an odd register alone for multiplication, but restricts the result to that register.)

**.** .

1 cm

Multiplies the contents of Rn+1 by the contents of 0 and leaves the result in [Rn,Rn+1]. (Rn+1 is assumed to hold the only meaningful result.) The contents of 0 are unchanged and the previous contents of [Rn,Rn+1] are lost.

DIV Rn, Divides the contents of [Rn,Rn+1] by the contents of D and leaves the quotient in Rn+1 and the remainder in Rn. (The PDP-11 reverses the quotient and remainder.) The contents of D are unchanged and the previous contents of [Rn,Rn+1] are lost.

MULT Rn, a

ha -

-

#

#### 26

*f*.

#### CHAPTER 3

#### 3.0 Introduction

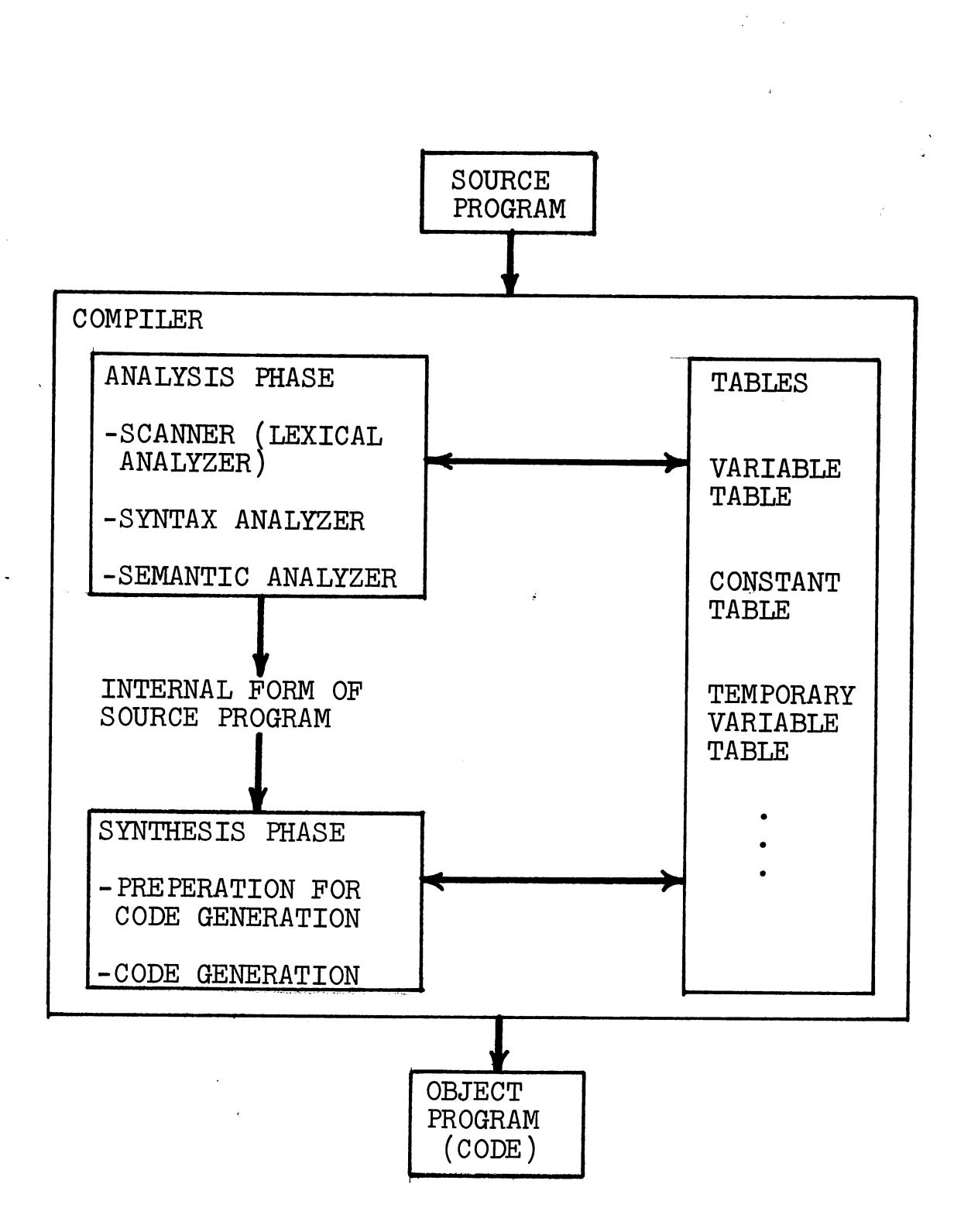

A compiler can be described in two phases. The first is an analysis of the source program which decomposes the source language into its constituent parts. The second is a synthesis of the object program using code generated from these basic parts. Figure 4 shows a diagram of a compiler. As information is gained at the local level in the analysis routines, it is stored in tables to make it available to all phases of the compiler.

- 3.1 Compiler Description

- 3.1.1 Tables of Information

The number and types of tables is determined by both the preferences of the compiler designer and the amount of information required for code generation. One table which is common to all compilers is the symbol or name table. This table holds the variable names of the source program and their attributes which include such things as type, precision, symbolic address and any additional information required for code generation. The compiler used in this thesis requires two additional tables. One is a constant table which holds the value, type, symbolic address, precision and other pertinent information about the constant. The other is a temporary variable table. Temporary variables are those used by the compiler to

ų.

والمروف والمحافظ وأستحج والمترقو

# FIGURE 4. CONCEPTUAL DIAGRAM OF A COMPILER.

Ď

represent the intermediate results generated when evaluating arithmetic expressions. The temporary variable table holds the type, symbolic address, precision and any other information required for code generation.

Since the source language allows variables and constants to have representations of varying length, this compiler replaces variables and constants by unique fixed length designations consisting of two integers. The first refers to a particular table and the second refers to an entry in that table. This form is also used for temporary variables. Thus variables, constants and temporary variables, all of which are called operands, can be denoted as follows:

(1, Pointer to variable table entry) (1,v)

(2, Pointer to constant table entry) (2,c)

(3, Pointer to temporary table entry) (3,t)

where the form on the right is a shorthand notation for these operands.

3.1.2 Symbolic Addresses

.

Since the memory locations that will be allocated at execution time are not known at compile time, symbolic addresses are assigned to variables, constants and temporary variables. These addresses are kept in the tables and used during code generation. Each address is represented by an ordered pair of integers, (d,k), where d

is the number of a data area and k is the displacement within that data area.

SAC memory is logically divided into contiguous blocks of words called data areas. The number of words in a data area is determined by the maximum displacement, K, allowed in an instruction. For example, the IBM 360 allows displacements up to 1023 full words. Thus, a data area for the IBM 360 consists of 1024 consecutive words of storage. The maximum number of data areas available, D', is determined by the memory capacity of the target machine and the size of the displacement allowed in that machines instruction set. Thus, if the IBM 360 configuration had a memory capacity of 131,072 full words, then the maximum number of data areas would be 121(=131072/1024). Data areas are numbered from zero to (D-1) where D is the number of data areas required for a given program.

Then D(K+1) is the size of the memory needed for this program (where K+1 is the number of words in a data area). If a contiguous memory block of size D(K+1) is allocated at execution time and the actual address of the first word in memory is denoted by T, then the actual address corresponding to the symbolic address, (d,k), would be actual address = T + d(K+1) + k The quantity, (T + d(K+1)), is the address of the first word of data area d. This quantity is the base

address of data area d and must be in a register in order to implement the addressing scheme described in Chapter 2. In order to implement base-displacement addressing, the first D words in data area 0 are reserved. Each of these D words contains the address of the data area whose number corresponds to the displacement of the word in data area 0. (i.e. the word whose symbolic address is (0,d) holds the base address of data area d) When the memory space is allocated, the operating system loads these addresses into the reserved area in data area 0 and also loads the starting address, T, into the R-th register (recall that the R-th register is the (N+1)-st register). This allows non-contiguous memory blocks to be allocated to different data areas. Base addresses can be loaded into any register, Rn, by using the R-th register as a base register and the data area number as a displacement with the following instruction

3

#### LOAD Rn,d(R)

# 3.1.3 Analysis Phase

-

The analysis phase is made up of the scanner, syntax and semantic analyzers. The scanner reads the source program character by character and builds the symbols (tokens) of the source language. These symbols might consist of variables, constants, key words, single and double character operators, etc. The scanner also stores

31

variables and constants in their appropriate table, replaces them with their fixed length form, identifies operators and replaces them with their internal form (usually an integer number). The syntax analyzer checks the symbols for syntactic correctness, enters their attributes in the tables and, when higher level syntax entities, such as arithmetic expressions, are encountered, calls the semantic routines to convert them to an internal form.

# 3.1.4 Internal Form of the Source Program

1

The internal form of the source program depends primarily upon the preferences of the compiler designer. However, some optimization techniques can be implemented more efficiently with particular internal forms.[6] For the SAC compiler, the infix notation of the source language is converted to quadruple notation which was selected because its simplicity aids the tutorial uses of SAC. Quadruple notation consists of a sequence of quadruples of the form

(operator, first operand, second operand, result) which, when taken in sequence, describe the operations needed to evaluate an arithmetic expression. The correspondence between the arithmetic and assignment operators and the quadruples which represent them are as follows:

| A+B        | (+,a,b,t) |

|------------|-----------|

| A-B        | (-,a,b,t) |

| A*B        | (*,a,b,t) |

| A/B        | (/,a,b,t) |

| <b>-</b> B | (-,b, ,t) |

| A=B        | (=,b,a, ) |

where upper case letters indicate symbols of the source program and lower case letters indicate their internal form. The operators themselves are used instead of their internal form for convienence and t represents the internal form of a temporary variable. An example of this notation is shown below for the arithmetic statement: A=B\*C+D;

(\*, b, c,tl) (+,tl, d,t2) (=,t2, a, )

The notation ti indicates the i-th entry in the temporary table. These are assigned sequentially to quadruples beginning with tl for each arithmetic statement processed. When code has been executed for an arithmetic statement (a sequence of quadruples the last one of which must be an assignment quadruple), the temporary variables used for that statement have no further use. Thus, space is allocated in the compiler for the temporary variable table based upon the maximum number of temporary variables that one statement can generate. This same principle is

33

...

.

applied to allocating storage for temporary variables at execution time by reserving a sufficient number of words in data area 0. The temporary variable table contains preassigned symbolic addresses. A temporary variable is then made addressable by obtaining the displacement from its entry in the temporary variable table and using the R-th register as a base register. A procedure is described in Appendix B which will convert an arithmetic statement in infix notation to a sequence of quadruples based upon the precedence rules described in Chapter 1.

Sec.

3.1.5 Synthesis Phase

N

The synthesis phase consists of preperation for code generation and code generation itself. Applying

optimization techniques to the source program (in its internal form - quadruples) is an important part of the preperation for code generation. These optimization techniques are machine independent. They will not be used nor discussed further in this thesis. This is followed by the code generation routines which generate target code from the internal form of the source program. Optimization techniques may be applied during or subsequent to the generation of object code. These are machine dependent techniques. Frequently a compiler will combine both techniques. The compiler used in this thesis converts the internal form directly to object code. Several compiler

34

<u>)</u>

techniques for generating code are discussed below. These techniques are not intended to be unique but rather to provide several distinct levels of object code for comparison.

# 3.2 <u>Code Generation Techniques</u>

Code generation for a quadruple can be divided into three steps. The first step generates code to make the operands addressable. This consists of insuring that either the operand itself or its base address is in a register. The second step generates code to load one of the operands into a register. This consists of insuring that the first operand is in a register. The third step generates code to perform the required operation. The implementation of these steps can be very simple or very complex depending upon the design of the compiler.

A code generation procedure, which follows these three steps, is discussed in the next section. This procedure requires six variables. Four variables, OPER, OPND1, OPND2, and RSLT, are designated for the elements of quadruples where OPER is the operator, OPND1 and OPND2 are the first and second operand respectively and RSLT is the temporary variable identifying the result of the operation. Two other variables, ADDR1 and ADDR2, are used to hold the addresses of the first and second operand respectively. These two variables may hold addresses of

the form Rn, k(i) or blank. All six variables are global since they must be available to all procedures of the compiler.

# 3.2.1 Basic Executable Code

.k

This procedure assumes that any operand or base address required in a register must always be loaded from memory. The following steps describe the procedure and are implemented sequentially unless otherwise indicated. Step 1 initializes the address variables and reads the next quadruple.

I. Initialize ADDR1=" " and ADDR2=" " and read the first (next) quadruple. If there are no remaining quadruples, code generation for the program is

complete.

Step 2 generates code to make the first operand addressable.

2. Generate "LOAD R3,dl(R)" (where dl is the data area number of the first operand) and set ADDRl="kl(3)" (where kl is the displacement of the first operand).

Step 3 generates code to make the second operand addressable.

3. If OPND2 equals " ", go to step 4. Otherwise generate "LOAD Rl,d2(R)" (where d2 is the data area number of the second operand) and set

ADDR2="k2(1)" (where k2 is the displacement of the second operand).

Step 4 generates code to place the first operand in a register.

4. Generate "LOAD R3, ADDR1". If OPER equals either

"\*" or "/", set I=2. Otherwise set I=3.

Step 5 generates code to perform the required operation using the procedure INSTR(I) where I is a register number specified by the calling procedure. This procedure will generate the appropriate machine language instruction for each quadruple based upon the operator involved. A detailed description of this

procedure is given in Appendix C.

5. Call INSTR(I).

1

Step 6 generates code to save the result of this quadruple and is required by the basic nature of this algorithm.

If OPER equals "=", go to step 1. Otherwise 6. generate "STORE R3, kt(R)" (where kt is the address in the temporary variable table entry pointed to by RSLT) and go to step 1.

Even though the number of available registers is a parameter of SAC, the registers used by this algorithm are explicitely stated. In this procedure the compiler does not keep track of the contents of the registers.

Therefore, the results of each quadruple must be stored before the next quadruple is encountered. One result of this is the lack of change in the object code if additional registers are available. This algorithm will generate the same code for three registers as for thirty registers. This lack of information about the contents of the registers prohibits the compiler from making a decision as to which register to chose when one is needed. 3.2.2 Register Map [3]

It is intuitively appealing to leave certain frequently used values in registers, thus eliminating some LOAD and STORE instructions. In order to accomplish this, the compiler must keep a running record of the contents of the registers, a so-called register map, by using an array named RV (Register Value). When the n-th element of this array, RV(n), contains an operand, this means that the value of that operand is in register n. We have already defined operands to describe variables, constants and temporary variables. Since the registers can also hold data area addresses, we define an additional operand as follows:

(4,Data area number) (4,d) If RV(n) contains (4,d), this indicates that the address of data area d is in register n. Thus RV(N+1) always contains (4,0). Each time code is generated which

changes the contents of a register, say Rn, the array element RV(n) must be updated. This technique makes it unnecessary to store the result of each quadruple since the result will be identified by an operand of the form (3,t) in RV.

A register can now be classified as free if it may be used without the necessity of saving its contents. Those registers which are empty are obviously free. Those which hold the value of operands of type (1,v), (2,c) and (4,d)are also free since these values are always available in memory. The only operand which must be stored when the register holding its value is required is of type (3,t). Thus Rn is free if it does not hold the value of a

temporary variable or, equivalently, if RV(n) does not hold an operand of type (3,t).

When a register is required, this technique chooses the first (lowest numbered) free register and avoids storing temporary variables unless no free registers are available. When a temporary variable in register n is to be stored, the storage address is obtained from its entry in the temporary variable table.

When implementing a register map, care must be taken to preserve the addressability of operands. If the n-th register were used to address the first operand (either by holding the value of the operand or by holding the base  $\gamma$

address of the operand), and there were no other free registers, then, if the address of the second operand required a free register, the addressability of the first operand would be destroyed. To avoid this problem a register must be tested to insure that it is not referenced by either one of the address variables, ADDR1 and ADDR2, before it is reused or its contents stored. 3.2.3 Register Status [3]

The previous method of selecting a free register does not differentiate between a register that is empty or one that contains variables or constants. Another technique which is used in combination with the register map provides this capability by using an array called RS (<u>Register Status</u>) to keep track of the importance of the contents of each register. The possible values of the n-th element of this array, RS(n), are:

- 0 Register n is empty and may be used without storing its contents.

- Register n holds either a constant, variable or data area address whose value is in memory and may be reused without storing its contents.

- 2 Register n holds a temporary variable whose value is not in memory and must be stored before being reused.

Each time the contents of a register are changed not

only is the RV array updated but also the RS array. When this technique requires a free register, it first searches for a register with status 0, then status 1 and finally status 2. Thus it will show a preference for using empty registers, thereby leaving constants, variables and base addresses in registers. This increases the liklihood that these values can be reused in subsequent operations without the necessity of loading them from memory.

3.2.4 Assigned Base Register

1

Since symbolic addresses are assigned sequentially as the variables and constants are encountered in the source program, variables and constants occuring in adjacent areas tend to be stored in the same data area. This technique takes advantage of this fact by assigning a specific register, RN, to be used as a base register. This register is loaded with the base address of the predominant data area and is not used for arithmetic operations. The method of determining the predominant data area for a particular block of coding and loading its address into the assigned base register is beyond the scope of this paper. This technique has the advantage of reducing the requirements for loading data area addresses but has the disadvantage of reducing the number of registers available for arithmetic operations. Because of this disadvantage, the minimum number of registers

required when using this technique is four.

#### 3.3 Procedure Descriptions

Providing the compiler with the ability to make decisions about register usage increases its complexity. Consequently, the procedure which implements the three steps of code generation using the techniques described above, is best described (and implemented) using five seperate procedures: FREANY, FREODD, FIXAD, PTINRG, and INSTR. The first two procedures are used to find free registers. The remaining three are used to perform the three steps of code generation. The INSTR procedure has been previously described. Functional descriptions of the remaining four procedures are given below and detailed logical descriptions are provided in Appendix C.

- FREODD(I) This procedure is used to find a free even-odd register pair. Since this procedure is used only when loading OPNDl into a register, the two registers involved may be referenced by

ADDR1. If no free pair can be found, code is generated to free a pair of registers and preserve addressability of the operands. The number of the odd register is returned in I. FIXAD(X,ADDR) This procedure is used to construct (fix) the addresses of the operands. X is either OPND1 or OPND2 and ADDR is the corresponding address variable (ADDR1 or ADDR2). This procedure first determines if either X or its base address is in a register, in which case, no code is required and the address variable is set to the appropriate value. If neither is in a register, the procedure FREANY(I) is called

Win Spectra

and code is generated to load the base address of X into RI. The address variable is then set to the appropriate value.

PTINRG(I) This procedure is used to place OPNDl in a register. If OPER is either "\*" or "/" (which requires OPNDl to be in an odd register), this procedure calls FREODD(J) and generates code, if necessary, to load OPNDl into the odd register, RJ. I returns the number of the preceeding even register (J-1). If OPER is not "\*" or "/", this procedure first determines if OPNDl is in a register, in which case, no code

is generated and I returns the number of that register. If it is not, FREANY(J) is called and code is generated to load OPND1 into RJ. I then returns register number J.

ie L

The procedure for code generation can now be described using the procedures FIXAD, PTINRG and INSTR.

- Initialize ADDR1=" " and ADDR2=" " and read the 1. first (next) quadruple. If there are no remaining quadruples, code generation for the program is complete.

- 2. Call FIXAD (OPND1, ADDR1)

- 3. Call FIXAD (OPND2, ADDR2)

- 4. Call PTINRG(I)

Call INSTR(I) 5.

Go to step 1. 6.

Both the register status and assigned base register techniques require knowledge of the contents of registers. Consequently both these techniques require a register map for implementation. Four possible combinations of these techniques will be considered. 3

Register map. a.

ю.

Ġ,

- Register map with register status. b.

- Register map and an assigned base register. C.

- Register map with register status and an assigned d. base register.

The differences between these four levels of code generation appear when implementing the logical steps described in Appendix C.

One difference occurs in the method used to find a free register. When using a register map without register status, the RV array is searched in numerical order (from 1 to N) for the first entry which is not type (3,t). If register status is used, then the RS array is searched in numerical order (from 1 to N) for the first entry whose value is 0. If none are found, then RS is again searched for the first entry whose value is 1. When an assigned base register is used with either of the above techniques, the range of the search is limited to the array entries from 1 to N-1, since the N-th register is used as the assigned base register.

The other differences consist of the requirements for updating the RV and RS arrays when code is generated which changes the value or status of the contents of a register. Register to register LOAD instructions of the form LOAD Rn,Rm require the values of RV(n) and RS(n) to be set equal to the values of RV(m) and RS(m) respectively. No changes are required in the values of RV(m) and RS(m). Storage to register LOAD instructions of the form LOAD Rn,d(R) require the value of RV(n) to be set equal to (4,d) and the value of RS(n) to be set equal to 1. STORE

instructions (except in the INSTR procedure) and storage to register LOAD instructions of the form LOAD Rn,k(i) do not require any changes in either RV or RS because they are always followed by an instruction which causes the necessary changes to be made.

The requirements for the procedure INSTR(I) depend upon the instruction generated. The ADD, SUB and NEG instructions require RV(I) to be set equal to RSLT and RS(I) to be set equal to 2. The MULT and DIV instructions require RV(I) to be cleared, RV(I+1) to be set equal to RSLT, RS(I) to be set equal to 0 and RS(I+1) to be set equal to 2. The STORE instruction requires RV(I) to be set equal to 0PND2 and RS(I) to be set equal to 1. All entries in RV of the form (3,t) must be cleared and all entries in RS that equal 2 must be changed to 0.

### 3.4 Compiler Simulation

The simplification obtained by using a simulated compiler occurs primarily in the analysis phase. The limited scope of the source language and the fact that execution is only simulated eliminates the need for tables. All variables are assumed to be stored in data area 1. Since displacements were not required for the simulation, the variable or temporary character was used in the address variable in place of displacement. This made printed code more readable.

-

Since all variables and operators are single characters, the scanner need not build any symbols. Differentiating between variables and operators is accomplished by testing the sign of the character since alphabetic characters have negative values and operators have positive values. Temporary variables were denoted by literal numeric characters which also have positive values. Syntax and semantic checking was not included because of the simple nature of the source language. The source language statements which were converted from FORTRAN were visually checked for correctness.

1

Service (

÷

.

#### CHAPTER 4

#### 4.1 Cost Model

The purpose of evaluating compiler performance is to provide a means of differentiating between different compilers (or levels of the same compiler) in terms of some cost function. The ideal cost function would be the one used by the computer center where the compiler is to be implemented. The cost function used in this thesis is relatively simple and an element of many computer billing schemes [2]. The cost is based on the time intergrated storage requirements of a program. The storage or space requirements of a program consist of two elements: the instruction space, which is required for the object code, and the variable space, which is required for the values of variables, constants and temporary variables. Since the space requirements of the variables used in the source language are not typical due to the limited number of variables allowed, the cost function was confined to the requirements of the instruction space. The cost function is

$$Ct = R\left(\sum_{i=1}^{i} n(i) T(i)\right) \left(\sum_{i=1}^{i} n(i) S(i)\right)$$

where T(i) is the execution time in seconds of the i-th

type of instruction.

S(i) is the storage requirement in kilo-bytes of the i-th type of instruction.

7

R is the rate charged per kilo-byte-second. n(i) is the number of times the i-th type of instruction is executed.

Ct is the "total" cost of executing a program.

This model shows no preference between space or time considerations. If, in a particular computer environment, either space or time were critical, than a different model would be used which would allow the use of weighting functions.

The different types of instructions refer to the instructions described in Chapter 2 but differentiate between register to register (R/R) and register to storage (R/S) operations. Since the source language is limited to straight line code, the number of times an instruction is executed is equal to the number of times that instruction is generated in the compiler. Thus, the simulated execution consisted of counting the number of times each type of instruction was generated by the simulated compiler. Execution times for each type of instruction were derived from typical execution times for similiar instructions published for the PDP-11 with the first operand in the register mode and the second operand in either the register mode for R/R instructions or index mode for R/S instructions.[1] The space requirements were obtained from the space required by the IBM 360 for R/R

49

\$

на. Ка

1 - C.

wand R/S instructions.[10] These are also the requirements for the PDP-11. The data used is shown in Table 1.

4.2 Experiment

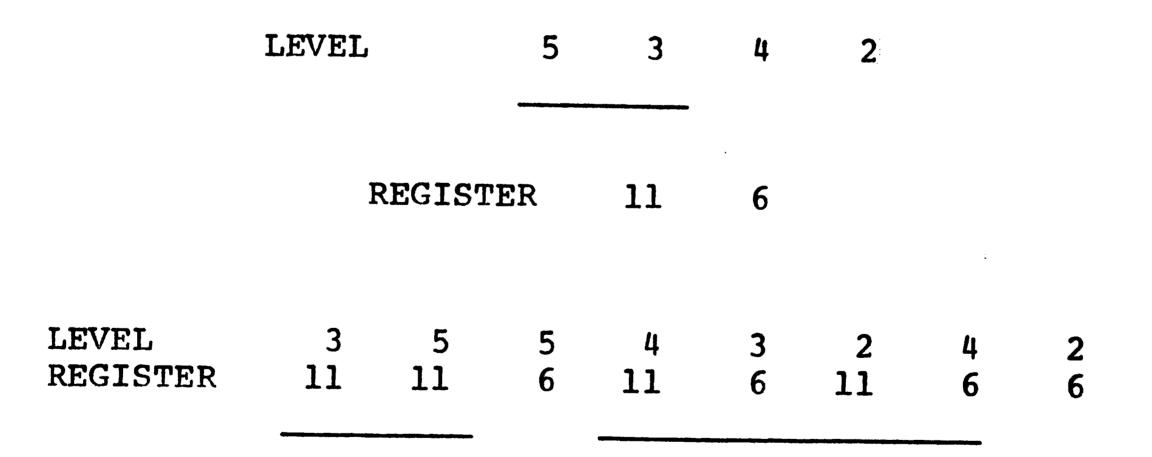

Two factors were selected for analysis: the level of optimization and the number of registers. Five levels of optimization were used:

1) Basic executable code.

2) Register map.

3) Register map with register status.

4) Register map and an assigned base register.

5) Register map with register status and an assigned base register.

The number of registers was chosen to reflect the

target machines. The IBM 360 has 16 registers numbered 0-15. However, registers 0, 1, 13, 14 and 15 are usually reserved by convention for special uses, leaving registers 2-12 for arithmetic operations. The PDP-11 has 8 registers numbered 0-7. However, register 6 is used as a stack pointer and register 7 is the program counter, leaving registers 0-5 for arithmetic operations. Therefore, the number of registers used were 6 and 11. Since the PDP-11 considers registers 0 and 1 to form an even-odd pair, both register configurations begin with even-odd pairs. The simulated compiler was modified to ignore register 1 in order to simulate this same register

• ·

¢.

41

• •

\*\***.**

**1**.

.

A**4** •

<del>:</del>

•

# TABLE 1. STORAGE REQUIREMENTS AND EXECUTION TIMES OF INSTRUCTIONS USED FOR SIMULATED EXECUTION.

configuration. Registers 2-12 were used for the IBM 360 and registers 2-7 were used for the PDP-11.[10,11]

Since cost is a function of program size (particularly with straight line code), the statistic chosen to characterize performance was the total cost of a program divided by the square of the number of quadruples which generated the cost. Since both the total space and total time requirements are each proportional to the number of quadruples in a program, dividing by the square of the number of quadruples should effectively eliminate program size as a variable. In order to provide convienent numbers for analysis, the rate charged per kilo-byte second was chosen as 10<sup>8</sup> (the units are irrelevant).

Thus, the statistic used is

$$X = (Ct/q^2) 10^8$$

where X is the observed statistic for each event

Ct is the total cost of the event

q is the number of quadruples comprising the event.

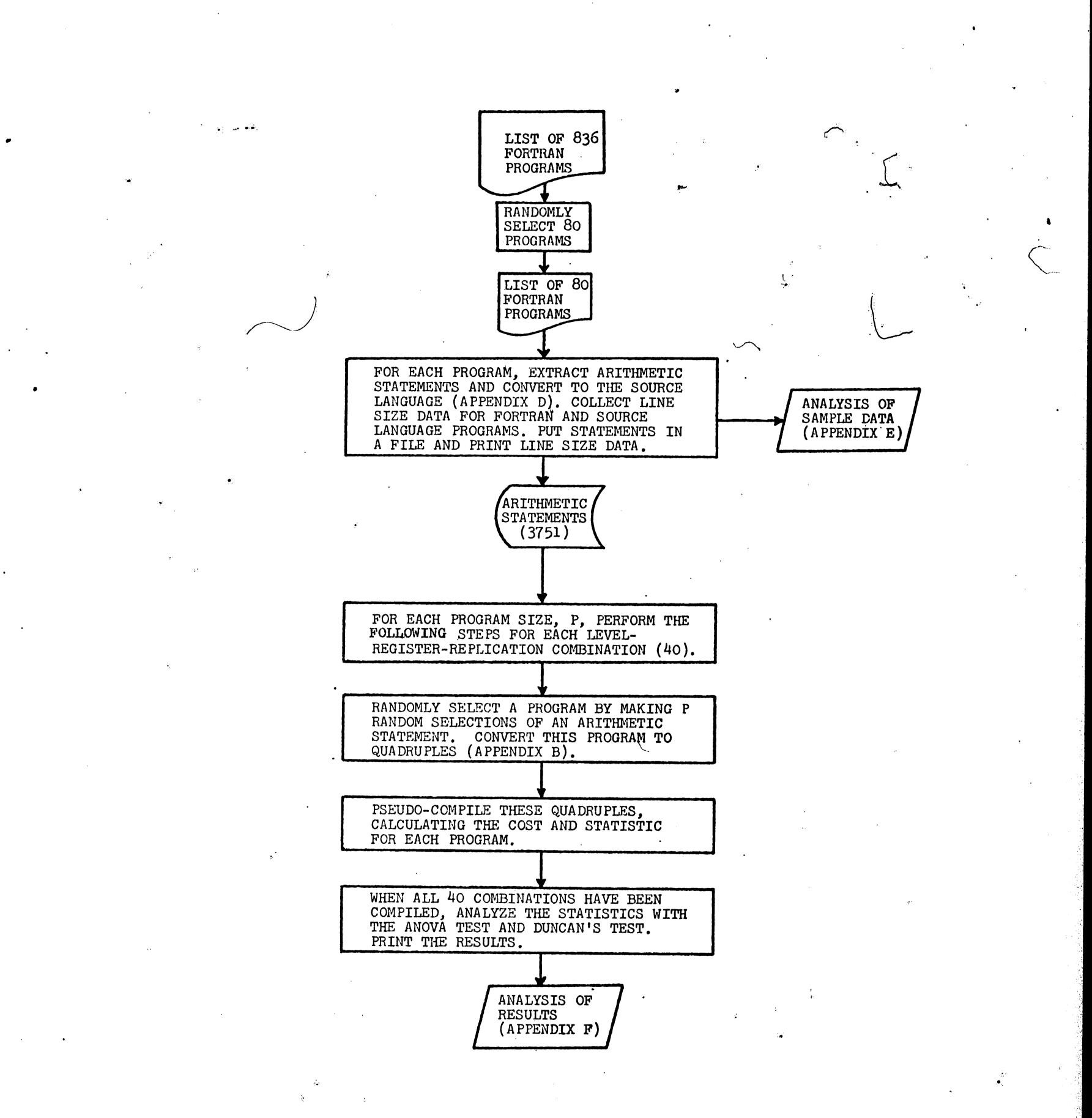

Eighty programs were randomly selected from a list of 836 FORTRAN programs provided by the local time sharing center. These 80 programs yielded 3751 arithmetic statements which were converted to the source language. A description of the procedure used to extract and convert arithmetic statements from these programs to the source language is given in Appendix D and some analysis of this

data is shown in Appendix E.

1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 19

Seperate experiments were performed for program sizes of 17, 46 and 118 arithmetic statements. These sizes were selected as the 50%, 70% and 90% points respectively of the cumulative frequency distribution of the number of arithmetic statements per FORTRAN program. Each event consisted of randomly selecting the appropriate number of statements from the 3751 available statements and simulating compilation with a particular level of optimization and a particular number of registers available. The experiment used was a factorial design which combined all levels of one factor (levels of optimization) with all levels of the other factor (number of registers). An experiment of this design can be easily extended to several factors. The number of replications (observations taken for each combination of factors) was four.

A two factor analysis of variance (ANOVA) test was used to analyze the results. The mathematical model for the ANOVA test is

$Xijk = u + Li + Rj + LRij + \varepsilon_k(ij)$

where Xijk is the k-th observation (k=1,...,4) of the i-th level of optimization (i=1,...,5) combined with the j-th number of registers available (j=6,11).

u is a common effect for the whole experiment.

Li is the effect of the i-th level of optimization.

Rj is the effect of the j-th level of available registers.

LRij is the interaction effect of Li and Rj.

<sup>E</sup>k(ij) represents the random error within the cell i,j.

Those factors which appeared significant in the ANOVA test were further analyzed by Duncan's multiple range test. This test orders the means of the factor being tested from low to high and then tests the means for significant differences.

A detailed explanation of both these tests can be found in Hicks[4]. Both tests were conducted at the 95% significance level, which means that there is a .05 probability that a factor which appears significant is, in fact, not significant. Those factors which were significant in the ANOVA test at the 99% significance level were noted. A diagram of the experimental procedure is shown in Figure 5.

54

÷.

FIGURE 5. DIAGRAM OF EXPERIMENTAL PROCEDURE

#### CHAPTER 5

#### 5.1 Results

2

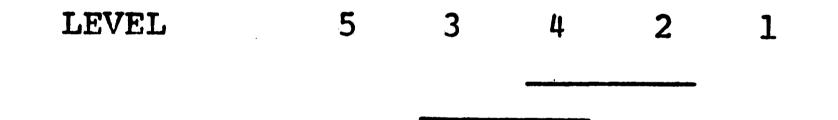

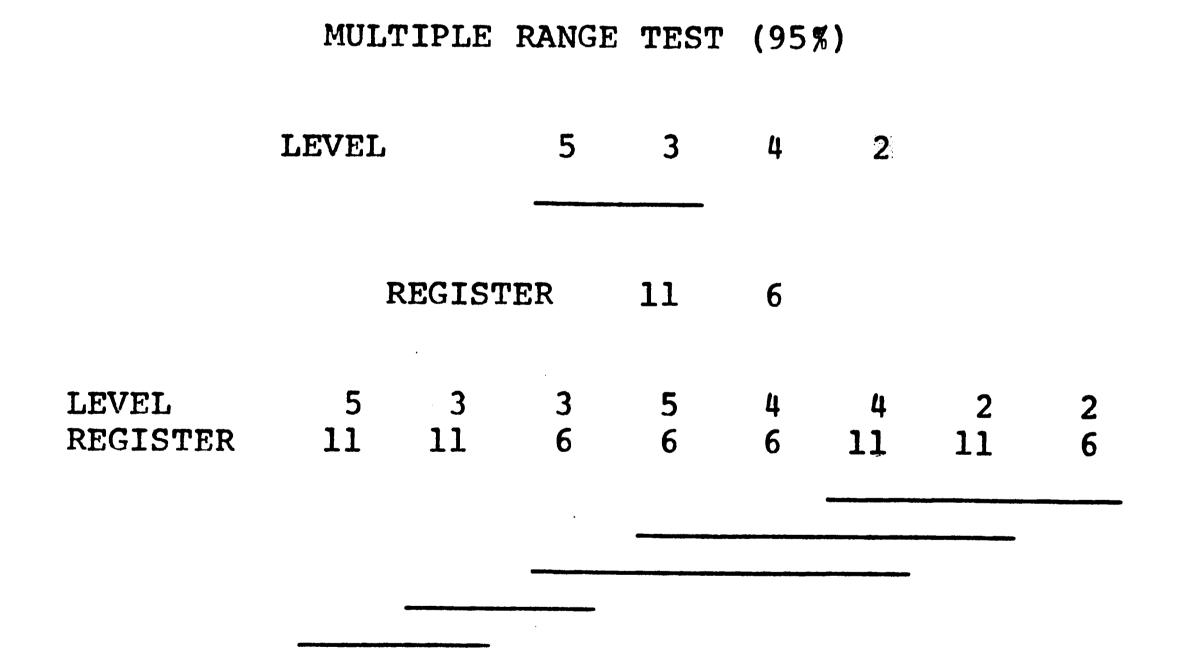

Tables 2 thru 4 show the results and analyses of three experiments using program sizes of 17, 46 and 118 arithmetic statements respectively. Tables 5 thru 7 show the results and analyses when the data for level 1 is excluded.

The multiple range test orders the means of each factor found significant from lowest to highest (left to right). The actual means are not shown but are calculated from the 8 values in a column (for levels), from the 20 values in a row (for registers) or from the 4 values in a column-row intersection (for level-register combinations). Those level, register or level-register combination indices which are underlined indicate that their means are not significantly different (i.e. they could have come from the same population). Conversely, those that are not underlined are statistically different. Thus, in Table 3, levels 4 and 2 are significantly different from level 1. In this same table, levels 5, 3 and 4 are significantly different from levels 4 and 2. The overlap of level 4 can be interpreted as having two distinct population distributions (i.e. different means) which have some overlap. Levels 2, 3 and 5 belong to either one or the other population, but, because of the overlap, level 4

| LEVELS          | 1                                | 2                            | 3                            | 4                            | 5                            |

|-----------------|----------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|

| REGISTERS<br>6  | 23.17<br>22.34<br>21.08<br>24.01 | 3.66<br>4.14<br>3.79<br>4.75 | 3.45<br>3.86<br>3.68<br>3.34 | 3.06<br>3.57<br>3.04<br>4.50 | 3.46<br>3.46<br>3.95<br>3.97 |

| REGISTERS<br>11 | 20.16<br>23.24<br>23.68<br>22.10 | 4.41<br>4.03<br>4.22<br>3.90 | 3.61<br>2.82<br>3.29<br>4.11 | 3.82<br>3.88<br>4.35<br>3.82 | 3.13<br>3.22<br>3.17<br>3.24 |

and the state of the second second state of the second second second second second second second second second

# ANOVA TABLE

| SOURCE                      | DF | SS      | MS     | EMS     | SIG |

|-----------------------------|----|---------|--------|---------|-----|

| LEVEL (Li)                  | 4  | 2255.09 | 563.77 | 1065.26 | 99% |

| REGISTERS (Rj)              | 1  | 0.11    | 0.11   | 0.20    |     |

| L X R INTERACTION (LRij).   |    | 1.08    | 0.27   | 0.51    |     |

| ERROR $(\varepsilon_k(ij))$ | 30 | 15.88   | 0.53   | 1.00    | `   |

| TOTALS                      | 39 | 2272.15 |        |         |     |

### MULTIPLE RANGE TEST (95%)

LEVEL 5 3 4 2 1