#### Lehigh University Lehigh Preserve

Theses and Dissertations

2016

## Efficient decoder design for error correcting codes

Chenrong Xiong Lehigh University

Follow this and additional works at: http://preserve.lehigh.edu/etd Part of the <u>Electrical and Computer Engineering Commons</u>

#### **Recommended** Citation

Xiong, Chenrong, "Efficient decoder design for error correcting codes" (2016). *Theses and Dissertations*. 2887. http://preserve.lehigh.edu/etd/2887

This Dissertation is brought to you for free and open access by Lehigh Preserve. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of Lehigh Preserve. For more information, please contact preserve@lehigh.edu.

## EFFICIENT DECODER DESIGN FOR ERROR CORRECTING CODES

BY

CHENRONG XIONG

PRESENTED TO THE GRADUATE AND RESEARCH COMMITTEE OF LEHIGH UNIVERSITY IN CANDIDACY FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

> IN Electrical Engineering Lehigh University

> > May 2016

© Copyright by Chenrong Xiong, 2016.

All Rights Reserved

Approved and recommended for acceptance as a dissertation in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

Date

Prof. Zhiyuan Yan (Dissertation Advisor)

Accepted Date

Committee Members:

Prof. Zhiyuan Yan (Committee Chair)

Prof. Meghanad D. Wagh

Prof. Tiffany Jing Li

Prof. Warren J. Gross McGill University

Dr. Ying Wang Qualcomm Inc.

#### Acknowledgements

Though only my name appears on the cover of this dissertation, a great many kind people have contributed to its production. I owe my gratitude to all those people who have made this dissertation possible and because of whom my graduate experience in Lehigh University has been one of the most cherishable things in my life.

First, I would like to express my deepest and most sincere gratitude and respect to my advisor, Professor Zhiyuan Yan, for his knowledge, guidance, mentorship, patience, encouragement, and friendship through my Ph.D career. I has been amazingly fortunate to have such an advisor, who always had time and patience for me and taught me so much in every aspect of research, from topic selection to idea development, from critical thinking to scientific writing, from presentation slide preparation to oral presentation skills. These skills are beneficial not only to my Ph.D study but also to my future career. Besides that, Professor Yan also recommended me for an intership, which provided me lots of precious industrial experience. I cannot have asked for a better advisor than him.

I am also very grateful to my committee members, Prof. Meghanad D. Wagh, Prof. Tiffany Jing Li, Prof. Warren J. Gross and Dr. Ying Wang for generously providing their time and expertise to better my work.

Special thanks are also due to the National Science Foundation (under Grants ECCS-0925890, ECCS-1055877 and ECCS-1509674) for the financial support during my Ph.D career.

I must acknowledge Dr. John Yu and Pinfen Lin. Their academic and industrial experiences inspire and encourage me to pursue my Ph.D. degree and to explore a wider world.

I also would like to thank all teaching and non-teaching staffs of Department of Electrical and Computer Engineering, Lehigh University for their generous assistance, help and support in numerous ways.

I am also thankful to many colleagues and friends, Ning Chen, Xuebin Wu, Feng Shi, Lihua Jiao, Hongmei Xie, Jun Lin, Yang Liu, Xuanxuan LV, Jiangfan Zhang, Ting Xu, Yun Li, Guanghai Ding, Jinhan Zhu, Guibao Xu, Li Zong, Dawei Li, Lei Zhang and Jian Lv for their encouragement, support, help, humor, and friendship. They make my life in Lehigh easier and more enjoyable.

Most importantly, none of this would have been possible without the love of my family. I would like to thank my parents and my brother for their love, their support and their unwavering faith and confidence in me. Many thanks must go to my children, two little lovely gentlemen – Zhuang Zhuang and Du Du. They make me full of energy and happiness. To my wife, Yan, words are not enough to express my gratitude. She has been standing beside me through this journey with her unconditional support, constant inspiration and encouragement, quiet patience and understanding, countless sacrifices and everlasting love.

Finally, I want to thank these people and many others not mentioned here again for their generous help and wish them all the best!

To my parents, my wife, and my children

## Contents

|   | Ack      | nowledg                | gements                                             | iv |  |

|---|----------|------------------------|-----------------------------------------------------|----|--|

|   | List     | st of Tables           |                                                     |    |  |

|   | List     | st of Figures          |                                                     |    |  |

|   | Abstract |                        |                                                     | 1  |  |

| 1 | Intr     | oductio                | n                                                   | 4  |  |

|   | 1.1      | Backg                  | round and Motivation                                | 5  |  |

|   |          | 1.1.1                  | Non-binary LDPC codes                               | 5  |  |

|   |          | 1.1.2                  | Polar Codes                                         | 7  |  |

|   | 1.2      | Outlin                 | e of the Dissertation                               | 10 |  |

| 2 | Imp      | roved N                | /ILGD Algorithms for Non-binary LDPC Codes          | 13 |  |

|   | 2.1      | Existir                | ng Majority-Logic Decoding Algorithms               | 16 |  |

|   | 2.2      | Two Ir                 | nprovements                                         | 17 |  |

|   |          | 2.2.1                  | New Reliability Information Update                  | 18 |  |

|   |          | 2.2.2                  | Re-selection Scheme                                 | 20 |  |

|   | 2.3      | Performance Evaluation |                                                     |    |  |

|   |          | 2.3.1                  | Error Performance and Average Numbers of Iterations | 25 |  |

|   |          | 2.3.2                  | Computational Complexity Reduction                  | 33 |  |

|   | 2.4 | Summ    | ary                                                        | 37 |

|---|-----|---------|------------------------------------------------------------|----|

| 3 | Sym | bol-Dec | cision Polar Decoder                                       | 39 |

|   | 3.1 | Polar ( | Codes and Existing Decoding Algorithms                     | 43 |

|   |     | 3.1.1   | Preliminaries                                              | 43 |

|   |     | 3.1.2   | Polar Codes                                                | 43 |

|   |     | 3.1.3   | SC Algorithm for Polar Codes                               | 44 |

|   |     | 3.1.4   | SCL and CA-SCL Algorithms for Polar Codes                  | 46 |

|   |     | 3.1.5   | Multi-bit SC and SCL Algorithms for Polar Codes            | 47 |

|   | 3.2 | M-bit   | Symbol-Decision Decoding Algorithms for Polar Codes        | 48 |

|   |     | 3.2.1   | Symbol-Decision SC and SCL Algorithms                      | 48 |

|   |     | 3.2.2   | Symbol-Based Recursive Channel Combination                 | 48 |

|   |     | 3.2.3   | Generalized Symbol-Decision SCL Algorithm                  | 56 |

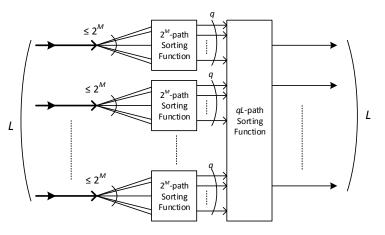

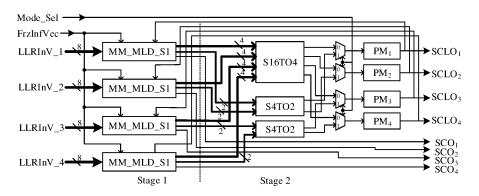

|   |     | 3.2.4   | Two-Stage List Pruning Network for the Symbol-Decision SCL |    |

|   |     |         | Algorithm                                                  | 58 |

|   | 3.3 | Pre-Co  | omputation Memory-Saving Technique                         | 61 |

|   | 3.4 | Impler  | nentation of Symbol-Decision SCL Decoders                  | 64 |

|   |     | 3.4.1   | Architecture of Symbol-Decision SCL Decoders               | 64 |

|   |     | 3.4.2   | Message Scheduling and Latency Analysis                    | 68 |

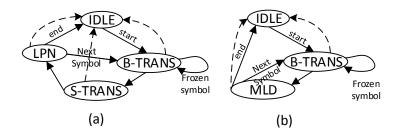

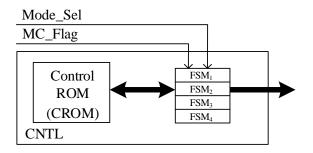

|   |     | 3.4.3   | Control Logic                                              | 73 |

|   |     | 3.4.4   | Synthesis results                                          | 74 |

|   | 3.5 | Summ    | ary                                                        | 77 |

| 4 | Mul | ti-Mode | e Area-Efficient SCL Polar Decoder                         | 79 |

|   | 4.1 | Prelim  | inaries                                                    | 83 |

|   |     | 4.1.1   | Construction Methods of Polar Codes                        | 83 |

|                  |     | 4.1.2   | Existing ML Decoding Units for Polar Decoders                | 84  |

|------------------|-----|---------|--------------------------------------------------------------|-----|

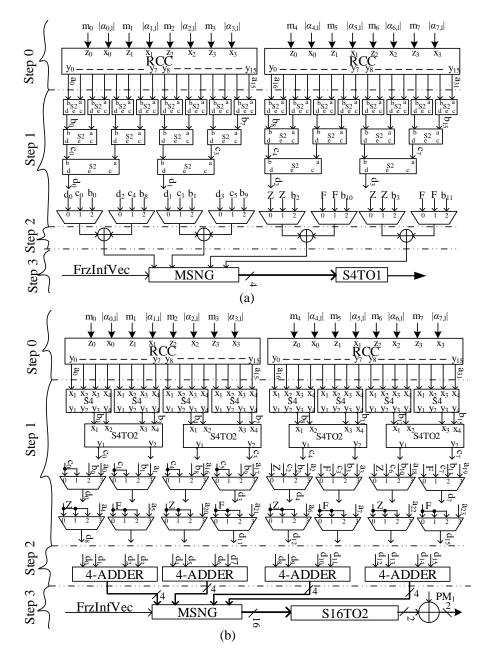

|                  | 4.2 | Divide  | -and-Conquer AML Decoding Unit                               | 86  |

|                  |     | 4.2.1   | Reformulation of the Divide-and-Conquer ML Unit for SC-based |     |

|                  |     |         | Algorithms [1] in the Probability Domain                     | 86  |

|                  |     | 4.2.2   | Divide-and-Conquer AML Decoding Unit for SCL-based Algo-     |     |

|                  |     |         | rithms                                                       | 89  |

|                  | 4.3 | Frozen  | -Location Patterns for Polar Codes                           | 93  |

|                  |     | 4.3.1   | Polar Codes for the BEC                                      | 93  |

|                  |     | 4.3.2   | Polar Codes for the AWGN Channel                             | 96  |

|                  |     | 4.3.3   | Computational Complexity of the Divide-and-Conquer AML De-   |     |

|                  |     |         | coding Unit                                                  | 97  |

|                  | 4.4 | Low-C   | Complexity AML Decoding Unit                                 | 97  |

|                  |     | 4.4.1   | Hardware Design for the LC-AML Decoding Unit                 | 98  |

|                  |     | 4.4.2   | Area-Efficient SCL Decoder                                   | 103 |

|                  |     | 4.4.3   | Synthesis Results                                            | 104 |

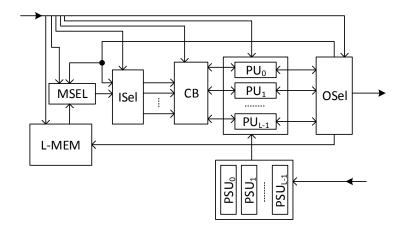

|                  | 4.5 | Multi-  | Mode SCL Decoder                                             | 105 |

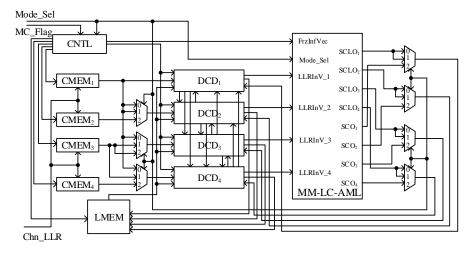

|                  |     | 4.5.1   | Architecture Description                                     | 106 |

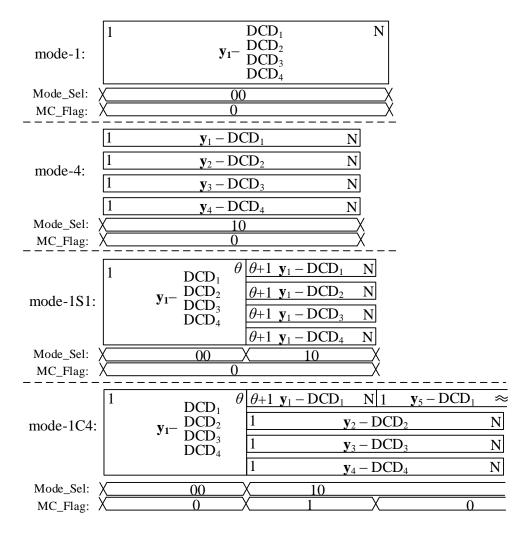

|                  |     | 4.5.2   | Simplified Modes and Mode Changes                            | 112 |

|                  |     | 4.5.3   | Synthesis Results                                            | 116 |

|                  | 4.6 | Summ    | ary                                                          | 120 |

| 5                | Con | clusion | and future work                                              | 121 |

|                  | 5.1 | Conclu  | ision                                                        | 121 |

|                  | 5.2 | Future  | work                                                         | 123 |

| Bibliography 125 |     |         |                                                              |     |

Vita

### **List of Tables**

| 2.1 | Average number of iterations of the Min-Max $(n_m = 16)$ , ISRB, IISRB                                      |    |

|-----|-------------------------------------------------------------------------------------------------------------|----|

|     | and RS-IISRB algorithms for the (255, 175) code                                                             | 27 |

| 2.2 | Average number of iterations of the ISRB, IISRB and RS-IISRB algo-                                          |    |

|     | rithms for the (837, 726) code                                                                              | 29 |

| 2.3 | Average number of iterations of the hard-reliability based algorithms for                                   |    |

|     | the (255, 175) code                                                                                         | 32 |

| 2.4 | Average number of iterations of the hard-reliability based algorithms                                       |    |

|     | algorithm for the (837, 726) code                                                                           | 33 |

| 2.5 | Computational complexities in initialization for various decoding algo-                                     |    |

|     | rithms, where $V = N2^r$ and $W = N\gamma$                                                                  | 35 |

| 2.6 | Computational complexities per iteration for various decoding algorithms,                                   |    |

|     | where $V = N2^r$ and $W = N\gamma$                                                                          | 35 |

| 2.7 | Computational complexities of the initialization step for various decod-                                    |    |

|     | ing algorithms to decode the (255,175) code                                                                 | 37 |

| 2.8 | Computational complexities required per iteration for various decoding                                      |    |

|     | algorithm to decode the (255,175) code                                                                      | 37 |

| 3.1 | The numbers of additions to calculate $W^{(j+1)}_{N,M}(\mathbf{y},\hat{u}^{jM}_1 u^{jM+M}_{jM+1})$ when the |    |

|     | (j+1)-th $M$ -bit symbol has no frozen bit                                                                  | 55 |

| 3.2 | Latencies of different decoders for a (1024, 480) CRC32-concatenated           |

|-----|--------------------------------------------------------------------------------|

|     | polar code with 64 processing units and $L = 4$                                |

| 3.3 | Synthesis results of proposed decoders with $L = 4$ for the aforemen-          |

|     | tioned (1024, 480) CRC32-concatenated polar code                               |

| 3.4 | Synthesis results of existing decoders with $L = 4$ for the aforemen-          |

|     | tioned (1024, 480) CRC32-concatenated polar code                               |

|     |                                                                                |

| 4.1 | Worst-case computational complexity of different methods when $M =$            |

|     | 8 and $q = 4$                                                                  |

| 4.2 | Areas of different ML decoding units for the (1024,512) polar code 104         |

| 4.3 | Areas (in mm <sup>2</sup> ) of the channel memory and the ML decoding unit for |

|     | MM-SCL and AE-SCL decoders when $N = 1024$ and r=0.5 117                       |

| 4.4 | Synthesizing results for different decoders when $N = 1024$ and r=0.5 117      |

| 4.5 | Synthesizing results for different decoders when $N=8192$ and r=0.5 118        |

| 4.6 | Synthesizing results for different decoders when $N=32768$ and $r=0.9$ . 118   |

## **List of Figures**

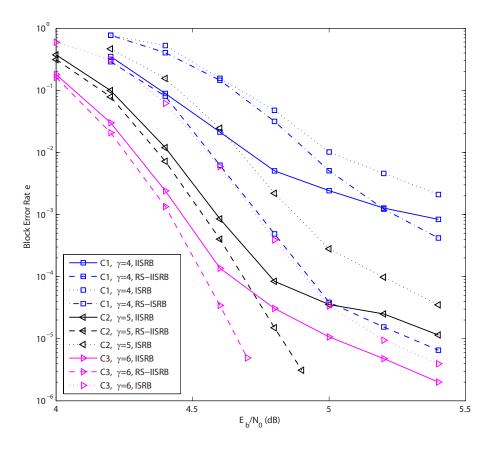

| 2.1 | BLERs of the soft-reliability based algorithms for different codes with    |    |

|-----|----------------------------------------------------------------------------|----|

|     | different column weights                                                   | 21 |

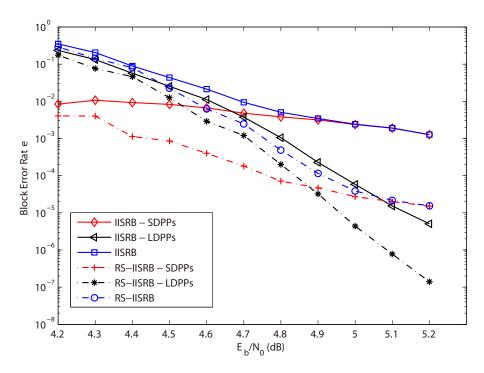

| 2.2 | BLERs of SDPPs and LDPPs for the IISRB and RS-IISRB algorithm to           |    |

|     | decode the (837, 726) code                                                 | 23 |

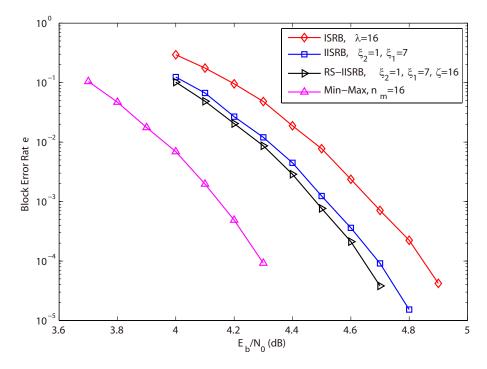

| 2.3 | BLERs of the ISRB, IISRB and RS-IISRB algorithms for the (255, 175)        |    |

|     | code                                                                       | 26 |

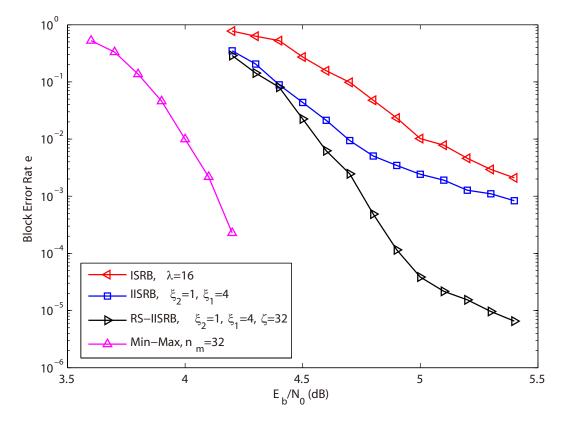

| 2.4 | BLERs of the ISRB, IISRB and RS-IISRB algorithms for the (837, 726)        |    |

|     | code                                                                       | 28 |

| 2.5 | BLERs of hard-reliability based algorithms for the (255,175) code          | 30 |

| 2.6 | BLERs of hard-reliability based algorithms for different non-binary LDPC   |    |

|     | codes with different column weights                                        | 31 |

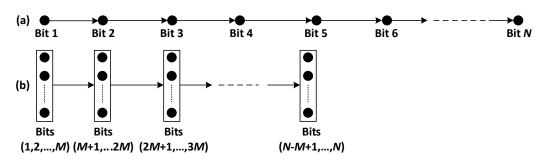

| 3.1 | (a) bit-decision vs. (b) <i>M</i> -bit decision                            | 47 |

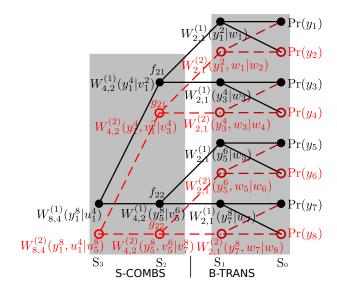

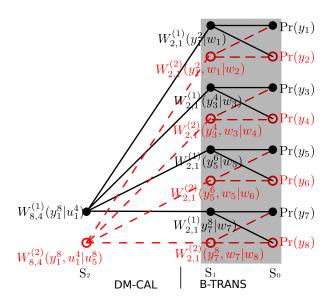

| 3.2 | The message flow graph of a four-bit symbol-decision SC algorithm for      |    |

|     | a polar code with code length eight by using the proposed symbol-based     |    |

|     | recursive channel combination.                                             | 53 |

| 3.3 | The message flow graph of a four-bit multi-bit SC algorithm for a polar    |    |

|     | code with code length eight by using direct-mapping calculation $[1-3]$ .  | 54 |

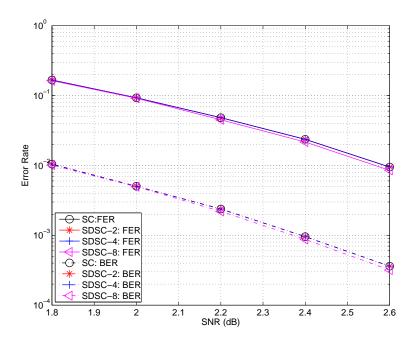

| 3.4 | Error rates of symbol-decision SC algorithms for a (1024, 512) polar code. | 56 |

|     |                                                                            |    |

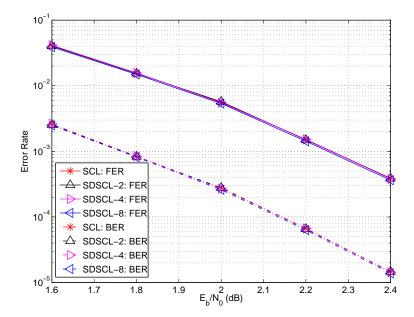

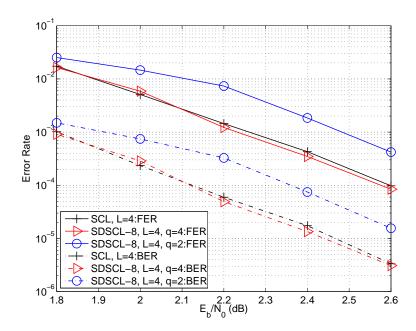

| 3.5  | Error rates of symbol-decision SCL algorithms for a (1024, 480) CRC32-                                          |     |

|------|-----------------------------------------------------------------------------------------------------------------|-----|

|      | concatenated polar code with $L = 4. \ldots \ldots \ldots \ldots \ldots$                                        | 58  |

| 3.6  | Message flow for a two-stage list pruning network.                                                              | 59  |

| 3.7  | Error rates of the SDSCL-8 decoder for a (1024, 480) CRC32-concatenated                                         | l   |

|      | polar code with $L = 4$ .                                                                                       | 60  |

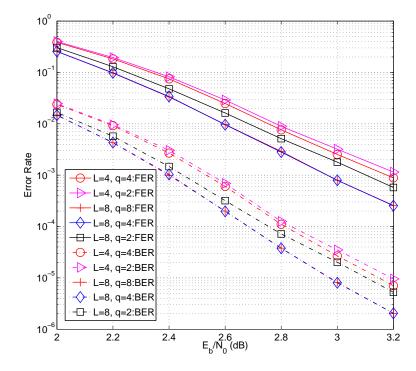

| 3.8  | Error rates of the SDSCL-4 algorithm for a (2048, 1401) CRC32-concatena                                         | ted |

|      | polar code with $L = 4$ and $L = 8$                                                                             | 60  |

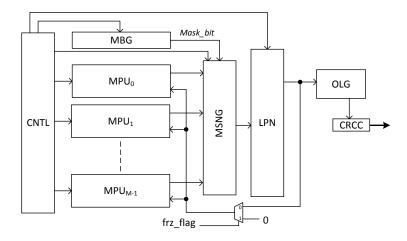

| 3.9  | Top architecture for an $M$ -bit symbol-decision SCL decoder                                                    | 64  |

| 3.10 | Architecture of an MPU.                                                                                         | 65  |

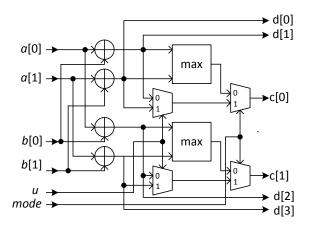

| 3.11 | Architecture of a processing unit.                                                                              | 66  |

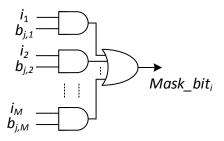

| 3.12 | Architecture for generating a mask bit                                                                          | 67  |

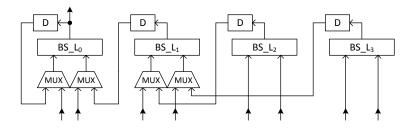

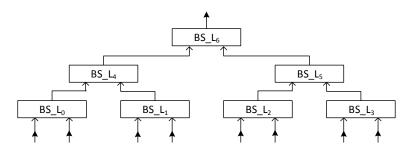

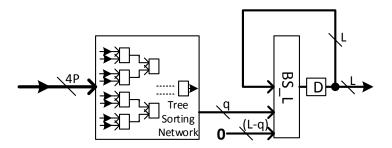

| 3.13 | Architecture for the folded sorting implementation when $2^M = 8$                                               | 67  |

| 3.14 | Architecture for the tree sorting implementation when $2^M = 8$                                                 | 68  |

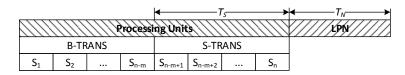

| 3.15 | Serial scheduling (in clock cycles).                                                                            | 69  |

| 3.16 | Overlapping scheduling (in clock cycles).                                                                       | 70  |

| 3.17 | A pipelined tree sorting implementation for the overlapping scheduling.                                         | 70  |

| 3.18 | Finite state machines for different scheduling schemes, (a) serial schedul-                                     |     |

|      | ing (b) overlapping scheduling                                                                                  | 74  |

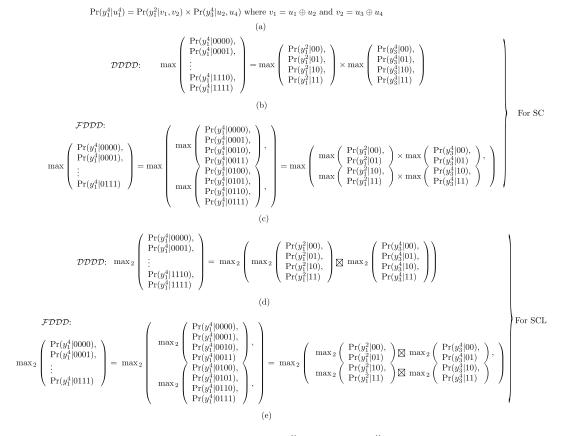

| 4.1  | Examples for calculating $max()$ and $max_2()$ functions when $M = 4$ ,                                         |     |

|      | $N = 4, q = 2$ , and $j = 0$ , (a) the calculation rule for $Pr(y_1^4 u_1^4)$ , (b)                             |     |

|      | the calculation of $\max(\Pr(y_1^4 u_1^4))$ in [1] when the frozen-location pat-                                |     |

|      | tern is ' $\mathcal{DDDD}$ ', (c) the calculation of $\max(\Pr(y_1^4 u_1^4))$ in [1] when the                   |     |

|      | frozen-location pattern is ' $\mathcal{FDDD}$ ', (d) the calculation of max <sub>2</sub> ( $\Pr(y_1^4 u_1^4)$ ) | )   |

|      | when the frozen-location pattern is ' $DDDD$ ', and (e) the calculation                                         |     |

|      | of $\max_2(\Pr(y_1^4 u_1^4))$ when the frozen-location pattern is ' $\mathcal{FDDD}$ '                          | 88  |

|      | (1,1,1,1) and the field form of particular $0 = 0 = 0 = 0$ .                                                    | 00  |

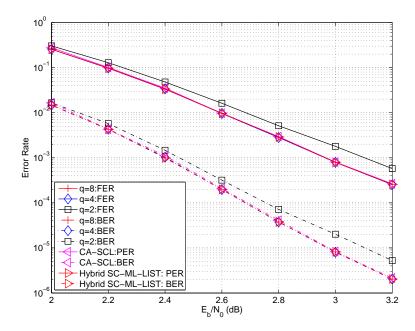

| 4.2  | Frame and bit error rates of CA-SCL decoders with different qs for a          |

|------|-------------------------------------------------------------------------------|

|      | (2048,1433) polar codes with a 32-bit CRC over the AWGN channel               |

|      | when adapting the LC-AML decoding unit                                        |

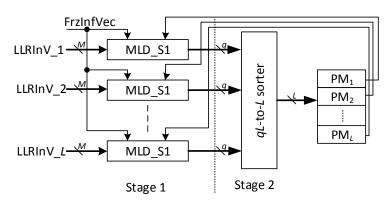

| 4.3  | Top architecture of the proposed LC-AML decoding unit                         |

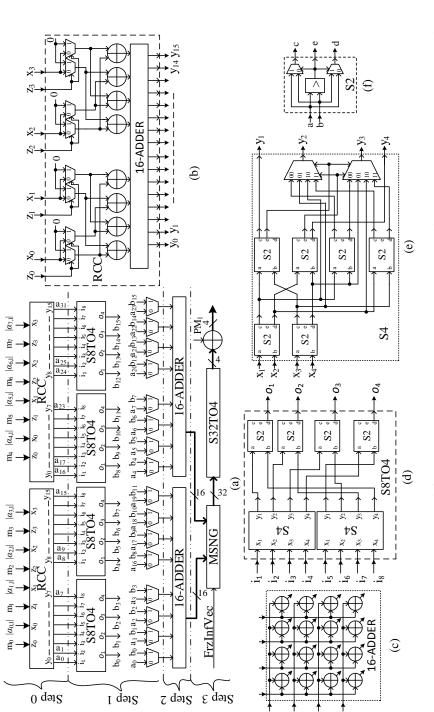

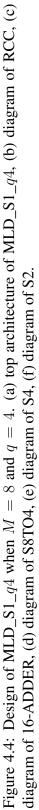

| 4.4  | Design of MLD_S1_q4 when $M = 8$ and $q = 4$ . (a) top architecture           |

|      | of MLD_S1_q4, (b) diagram of RCC, (c) diagram of 16-ADDER, (d)                |

|      | diagram of S8TO4, (e) diagram of S4, (f) diagram of S2                        |

| 4.5  | Top architecture of the MM-SCL decoder when $n_d = 4106$                      |

| 4.6  | Diagram of CNTL                                                               |

| 4.7  | Top architecture of MM-LC-AML for the MM-SCL decoder 108                      |

| 4.8  | (a) Design of MLD_S1_q1 for $q = 1$ , (b) design of MLD_S1_q2 for $q = 2.110$ |

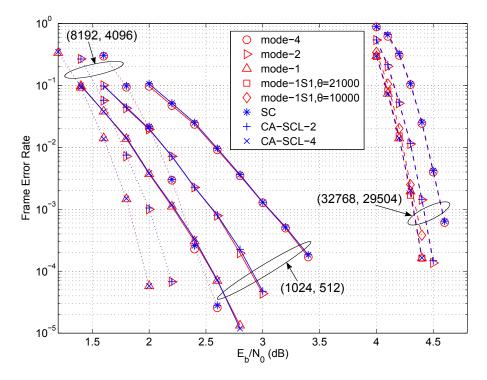

| 4.9  | Frame error rates of of the SC and CA-SCL algorithms and different            |

|      | modes for the MM-SCL decoder                                                  |

| 4.10 | Decoding schedules and control words for different modes                      |

#### Abstract

Error correctiong codes (ECC) are widly used in applications to correct errors in data transmission over unreliable or noisy communication channels. Recently, two kinds of promising codes attracted lots of research interest because they provide excellent error correction performance. One is non-binary LDPC codes, and the other is polar codes. This dissertation focuses on efficient decoding algorithms and decoder design for these two types of codes.

Non-binary low-density parity-check (LDPC) codes have some advantages over their binary counterparts, but unfortunately their decoding complexity is a significant challenge. The iterative hard- and soft-reliability based majority-logic decoding algorithms are attractive for non-binary LDPC codes, since they involve only finite field additions and multiplications as well as integer operations and hence have significantly lower complexity than other algorithms. We propose two improvements to the majority-logic decoding algorithms. Instead of the accumulation of reliability information in the existing majority-logic decoding algorithms, our first improvement is a new reliability information update. The new update not only results in better error performance and fewer iterations on average, but also further reduces computational complexity. Since existing majority-logic decoding algorithms tend to have a high error floor for codes whose parity check matrices have low column weights, our second improvement is a re-selection scheme, which leads to much lower error floors, at the expense of more finite field operations and integer operations, by identifying periodic points, re-selecting intermediate hard decisions, and changing reliability information.

Polar codes are of great interests because they provably achieve the symmetric capacity of discrete memoryless channels with arbitrary input alphabet sizes while having an explicit construction. Most existing decoding algorithms of polar codes are based on bit-wise hard or soft decisions. We propose symbol-decision successive cancellation (SC) and successive cancellation list (SCL) decoders for polar codes, which use symbolwise hard or soft decisions for higher throughput or better error performance. Then we propose to use a recursive channel combination to calculate symbol-wise channel transition probabilities, which lead to symbol decisions. Our proposed recursive channel combination has lower complexity than simply combining bit-wise channel transition probabilities. The similarity between our proposed method and Arıkan's channel transformations also helps to share hardware resources between calculating bit- and symbolwise channel transition probabilities. To reduce the complexity of the list pruning, a two-stage list pruning network is proposed to provide a trade-off between the error performance and the complexity of the symbol-decision SCL decoder. Since memory is a significant part of SCL decoders, we also propose a pre-computation memory-saving technique to reduce memory requirement of an SCL decoder.

To reduce the complexity of the recursive channel combination further, we propose an approximate ML (AML) decoding unit for SCL decoders. In particular, we investigate the distribution of frozen bits of polar codes designed for both the binary erasure and additive white Gaussian noise channels, and take advantage of the distribution to reduce the complexity of the AML decoding unit, improving the throughput-area efficiency of SCL decoders.

Furthermore, to adapt to variable throughput or latency requirements which exist widely in current communication applications, a multi-mode SCL decoder with variable list sizes and parallelism is proposed. If high throughput or small latency is required, the decoder decodes multiple received words in parallel with a small list size. However,

if error performance is of higher priority, the multi-mode decoder switches to a serial mode with a bigger list size. Therefore, the multi-mode SCL decoder provides a flexible tradeoff between latency, throughput and error performance at the expense of small overhead.

### Chapter 1

### Introduction

The only task of telecommunication systems is to maintain a reliable information transmission over unreliable communication channels. Unfortunately, noise is everywhere. Communication channels are not ideal and contain different kinds of noise, thus errors may be introduced during transmission from a transmitter to a receiver. Error correcting codes is used in telecommunication systems to detect or correct such errors and to restore transmitted data. There are a lot of error correcting codes: Hamming codes, Bose-Chaudhuri-Hocquenghem (BCH) codes, Reed-Solomon(RS) codes, convolutional codes, turbo codes, low-density parity check (LDPC) codes, non-binary LDPC codes, polar codes, and so on. Among these codes, LDPC codes, non-binary LDPC and polar codes have attracted lots of research interest recently because they have excellent error correction performance.

#### **1.1 Background and Motivation**

#### 1.1.1 Non-binary LDPC codes

Low-density parity-check (LDPC) codes were first developed by Gallager [4] in 1963. They were forgotten until they were rediscovered in the late 1990s by MacKay and Neal [5]. Since then, the academic and industrial communities have focused on binary LDPC codes, because long binary LDPC codes can achieve performance approaching the Shannon limit (see, for example, [6]). Hence binary LDPC codes have been used in various applications, such as digital television, Ethernet, home networking, and Wi-Fi. Efficient decoding algorithms, encoder implementations, and decoder implementations of binary LDPC codes (see, for example, [7–9]) have received significant attentions.

In 1998, the study of Davey and MacKay [10] showed that non-binary LDPC codes over GF(q) (q > 2) perform better than their binary counterparts for moderate code lengths. Moreover, non-binary LDPC codes also outperform binary LDPC codes on channels with bursty errors and high-order modulation schemes [11]. These advantages have motivated a steady stream of work on code designs [12, 13], decoding algorithms [10, 11, 14–20], and decoder implementations [21–23] for non-binary LDPC codes. Davey and MacKay [10] first used belief propagation (BP) to decode nonbinary LDPC codes. By applying the fast Fourier transform (FFT) of probabilities to the BP algorithm, they also proposed a fast Fourier transform (FFT) based q-ary sumproduct algorithm (SPA), called FFT-QSPA [15]. The FFT-QSPA was further improved by Barnault and Declercq [16]. Song and Cruz proposed a logarithm domain FFT-BP algorithm [11]. The Min-Sum algorithm was applied to non-binary LDPC codes by Wymeersch *et al.* [17]. Then Declercq and Fossorier [18] proposed the Extended MinSum (EMS) algorithm by using only a limited number of probabilities in the messages at inputs of check nodes. Savin [19] proposed the Min-Max algorithm.

The advantages of non-binary LDPC codes come at the expense of significantly higher decoding complexity than their binary counterparts. Since complexity of decoding non-binary LDPC codes is a key challenge, the iterative hard- and soft-reliability based majority-logic decoding, referred to as IHRB-MLGD and ISRB-MLGD, respectively, algorithms [20] are particularly attractive. When there is no ambiguity, MLGD is omitted when referring to majority-logic decoding algorithms for brevity. Based on the one-step majority logic decoding, these majority-logic decoding algorithms represent reliability information with finite field elements and integers, and hence involve only finite field additions (FAs) and finite field multiplications (FMs) as well as integer additions (IAs), integer comparisons (ICs), integer multiplications (IMs) and integer divisions (IDs). As a result, they require much lower computational complexities at the expense of moderate error performance degradation. For instance, while the error performance of the ISRB algorithm is within 1 dB of that of FFT-QSPA [16], its complexity is only a small fraction of that of the latter [20]. With a performance loss of 1 dB, the IHRB algorithm has even lower complexity than the ISRB algorithm [20]. Based on the IHRB algorithm, Zhang et al. [23] proposed an enhanced IHRB-MLGD (EIHRB) algorithm by introducing the soft-reliability initialization and re-computing the extrinsic information. The EIHRB algorithm has a similar complexity to that of the IHRB algorithm, but its error performance approaches that of the ISRB algorithm. The majoritylogic decoding algorithms are particularly effective for LDPC codes constructed based on finite geometries and finite fields [13].

However, in these MLGD algorithms, the reliability information includes all check-

to-variable messages of previous iterations. This leads to some performance loss and lower convergence speed. Furthermore, these MLGD algorithms tend to show a high error floor for codes whose parity check matrix have small column weights. In this dissertation, we will tackle these two problems of MLGD algorithms for non-binary LDPC codes.

#### **1.1.2 Polar Codes**

Polar codes, a groundbreaking finding by Arıkan [24] in 2009, have ignited a spark of research interest in the fields of communication and coding theory, because they provably achieve the symmetric capacity for both binary-input memoryless channel [24] and nonbinary-input memoryless channels [25]. The second reason polar codes are attractive is their low encoding and decoding complexity. For example, a polar code of length N can be decoded by the successive cancellation (SC) algorithm [24] with complexity  $O(N \log N)$ .

Polar codes' capacity-approaching performance is achieved only when the code length is large enough if the SC algorithm is used. For a short or moderate code length, in terms of the error performance, polar codes with the SC algorithm are inferior to Turbo codes or low-density parity-check (LDPC) codes [26, 27]. Thus, a lot of effort has been made to improve the error performance of short polar codes. Systematic polar codes [28] were proposed to reduce the bit error rate (BER) while guaranteeing the same frame error rate (FER) as their non-systematic counterparts. Although a Viterbi algorithm [29], a sphere decoding algorithm [30] and stack sphere decoding algorithm [31] can provide maximum likelihood (ML) decoding of polar codes, they are considered infeasible, especially for long polar codes, due to their much higher complexity than the SC algorithm. Recently, an SC list algorithm for polar codes was proposed in [32] to bridge the performance gap between the SC algorithm and ML algorithms at the cost of complexity  $O(LN \log N)$ , where *L* is the list size. Moreover, the concatenation of polar codes with cyclic redundancy check (CRC) codes was introduced in [26,33]. To decode the CRC-concatenated polar codes, a CRC detector is used in the SCL algorithm to help select the output codeword. The combination of an SCL algorithm and a CRC detector is called CRC-aided SCL (CA-SCL) algorithm. [33] shows that with the CA-SCL algorithm, the error performance of a (2048, 1024) CRC-concatenated polar code is better that of a (2304, 1152) LDPC code, which is used in the WiMax standard [34].

Several architectures have been proposed for the SC and SCL algorithms. Arikan [24] showed that a fully parallel SC decoder has a latency of 2N - 1 clock cycles. A tree SC decoder and a line SC decoder with complexity O(N) were proposed in [35]. These two decoders have the same latency as the fully parallel SC decoder. To reduce complexity further, Leroux *et al.* [36] proposed a semi-parallel SC decoder for polar codes by taking advantage of the recursive structure of polar codes to reuse processing resources. Assuming that the number of processing elements (PEs) are  $P(P = 2^p \le N)$ , the latency of the semi-parallel SC decoder is  $2N + \frac{N}{P} \log_2(\frac{N}{4P})$  clock cycles. A scalable semi-parallel architecture was proposed in [37]. To reduce the latency, a simplified SC (SSC) polar decoder was introduced in [38] and it was further analyzed in [39]. In the SSC polar decoder, a polar code is converted to a binary tree including three types of nodes: rate-one, rate-zero and rate-R nodes. Based on the SSC polar decoder, the ML SSC decoder makes use of the ML algorithm to deal with part of rate-R nodes in [40]. However, the SSC and ML-SSC polar decoders depend on positions of information bits and frozen bits, and are code-specific consequently. In [41], a pre-computation look-

ahead technique was proposed to reduce the latency of the tree SC decoder by half. For the SCL polar decoder, the semi-parallel architecture was adopted in [42]. In [43] Balatsoukas-Stimming *et al.* proposed an architecture of L = 4 to achieve a throughput of 124 Mbps and a latency of 8.25 ms when decoding a (1024, 512) polar code. In [44], Lin and Yan designed an SCL polar decoder with a throughput of 182 Mbps and a latency of 5.63 ms. To reduce the memory requirement, the log-likelihood ratio (LLR) messages are used in [45]. The throughput of existing polar decoders is still not high enough for high speed applications.

The aforementioned polar decoders are based on soft or hard bit decisions. That is, they deal with bits serially, leading to low throughput (or long latency). Several previous works attempt to improve the throughput (or latency) by dealing with multiple bits at a time. In [2], the data bits of a polar code are split into several streams, which are decoded simultaneously. This idea of parallel processing is extended in [1], where the SC decoder is transformed into a concatenated decoder, where all the inner SC decoders are carried out in parallel. Yuan and Parhi proposed a multi-bit SCL decoder [3]. But their computation methods for symbol-based transition probabilities have unnecessary high complexity. The first problem we deal with here for polar codes is how to design a low-complexity ML decoding unit to calculation symbol-based transition probabilities.

Many applications, such as modern wireless or wireline communication systems, require variable data rate transmission and have stringent latency requirements. As a potential candidate of FEC technique for future communication systems, a polar decoder supporting variable data rate and variable decoding latency is desired. Unfortunately, existing polar decoders provide only fixed latency and throughput (data rate). In this dissertation, we will introduce a multi-mode area-efficient SCL (MM-SCL) polar decoder with variable list sizes and parallelism. When the error performance is of higher priority, the MM-SCL decoders is under a mode with a large list size to provide a good error performance. However, when the channel is good enough and the error performance with a smaller list size is acceptable, the MM-SCL decoder switches to a mode with this smaller list size to provide a higher throughput and a shorter decoding latency. Therefore, the MM-SCL decoder provides a flexible trade-off between latency, throughput and error performance and can easily adapt to different communication channels and applications.

#### **1.2** Outline of the Dissertation

This dissertation is organized as follows:

In Chapter 2, two improvements to the majority-logic decoding algorithms are presented. Instead of the accumulation of reliability information in the existing majoritylogic decoding algorithms, our first improvement is a new reliability information update. The new update not only results in better error performance and fewer iterations on average, but also further reduces computational complexity. Since existing majority-logic decoding algorithms tend to have a high error floor for codes whose parity check matrices have low column weights, our second improvement is a re-selection scheme, which leads to much lower error floors, at the expense of more finite field operations and integer operations, by identifying periodic points, re-selecting intermediate hard decisions, and changing reliability information.

In Chapter 3, symbol-decision successive cancellation (SC) and successive cancel-

lation list (SCL) decoders for polar codes are presented, which use symbol-wise hard or soft decisions for higher throughput or better error performance. First, we propose to use a recursive channel combination to calculate symbol-wise channel transition probabilities, which lead to symbol decisions. Then we show that our proposed recursive channel combination has lower complexity than simply combining bit-wise channel transition probabilities. The similarity between our proposed method and Arıkan's channel transformations also helps to share hardware resources between calculating bit- and symbol-wise channel transition probabilities. Second, a two-stage list pruning network is proposed to provide a trade-off between the error performance and the complexity of the symbol-decision SCL decoder. Third, since memory is a significant part of SCL decoders, we propose a pre-computation memory-saving technique to reduce memory requirement of an SCL decoder. Finally, to evaluate the throughput advantage of our symbol-decision decoders, we design an architecture based on a semi-parallel successive cancellation list decoder. In this architecture, different symbol sizes, sorting implementations, and message scheduling schemes are considered.

In Chapter 4, an approximate ML (AML) decoding unit for SCL decoders is investigated. In particular, the distribution of frozen bits of polar codes designed for both the binary erasure and additive white Gaussian noise channels are investigated. By taking advantage of the distribution, the complexity of the AML decoding unit is reduced further. Moreover, to adapt to variable throughput and latency requirements which widely exist in practical applications, a multi-mode SCL decoder with variable list sizes and parallelisms is discussed. The multi-mode SCL decoder provides a flexible trade-off between throughput, latency and error performance.

Chapter 5 concludes this dissertation and discusses some future work regarding non-

binary LDPC codes and polar codes.

### Chapter 2

# Improved MLGD Algorithms for Non-binary LDPC Codes

The main contributions of this chapter are two improvements to the majority-logic decoding algorithms for non-binary LDPC codes.

- The first improvement is a new reliability information update, instead of the accumulation of reliability information used in existing majority-logic decoding algorithms.

- Since existing majority-logic decoding algorithms tend to have a high error floor for codes whose parity check matrices have small column weights, our second improvement is a re-selection scheme, which lowers error floors at the expense of more finite field operations and integer operations by identifying periodic points, re-selecting intermediate hard decisions, and changing reliability information.

In the ISRB and IHRB algorithm, the reliability information includes all check-tovariable (c-to-v) messages of previous iterations. The new reliability information update proposed in this chapter excludes the c-to-v messages of previous iterations. It not only results in better error performance and fewer iterations on average, but also greatly reduces computational complexities of *all* existing majority-logic decoding algorithms. For instance, when applied to the ISRB majority-logic decoding algorithm, the new reliability information update results in a 0.15 dB coding gain and reduces required number of iterations by 10% at 4.7 dB for a (16, 16)-regular (255, 175) cyclic LDPC code over  $GF(2^8)$  constructed with the method as describe in [46, Example 4]. Also, at a block error rate (BLER) of  $10^{-4}$ , the coding gain over the EIHRB algorithm is about 0.07 dB. At the SNR of 4.7 dB, the average number of iterations is reduced by about 25%. Furthermore, with the new reliability information update, the improved algorithms require significantly fewer IAs and ICs than the ISRB and EIHRB algorithms. Finally, the existing majority-logic decoding algorithms are based on the accumulation of reliability information, and hence the numerical range of the reliability information increases with iterations. In contrast, the proposed reliability information update results in a fixed numerical range and thus simplifies hardware implementations. Our new reliability update has been presented in part in [47]. By applying both the layered scheduling and our first improvement to the IHRB algorithm, we proposed a layered improved IHRB decoder with a high throughput in [48]. Because the architecture design of non-binary LDPC decoders is beyond the scope of this chapter, we will not discuss the layered improved IHRB decoder henceforth.

In the literature, to analyze the error floor of binary LDPC codes, some notions based on graphical structures have been introduced, such as stopping sets [49], trapping sets [50] and absorbing sets [51]. Unfortunately, trying to lower the error floor based

on graphical structures usually incurs very high complexity. Also, some approaches for binary LDPC codes cannot be readily adapted to non-binary ones. For instance, a selective biasing postprocessing algorithm is proposed in [51] to lower the error floors of binary LDPC codes based on the relaxed graphical structure of absorbing sets. However, for non-binary LDPC codes, trapping sets are difficult to identify because they involve not only the graph topology but also values of non-zero entries of parity-check matrices [52]. Moreover, the biasing rule between two elements for binary LDPC codes cannot be applied to non-binary codes directly, because there are more than two elements in a non-binary finite field.

In this chapter, for the majority-logic decoding algorithms, we propose a re-selection scheme based on periodic points to lower the error floors. The re-selection scheme is not a postprocessing algorithm and can be integrated into the regular iteration procedure easily. For instance, for an (837, 726) non-binary quasi-cyclic LDPC code over  $GF(2^5)$  constructed with the method in [13] with a column weight of four, the EIHRB algorithm has a BLER floor around  $10^{-3}$ , while the hard-reliability based algorithm with the new reliability information update and the re-selection scheme achieves a BLER floor below  $10^{-5}$ . Although this re-selection scheme requires additional computation, it is used only when existing majority-logic decoding algorithms have a high error floor.

The rest of our chapter is organized as follows. Section 2.1 reviews existing majoritylogic decoding algorithms for non-binary LDPC codes. Section 2.2 proposes the two improvements. In Section 2.3.1, the two improvements are applied to existing majoritylogic decoding algorithms to illustrate their advantages in error performance and average numbers of iterations. Section 2.3.2 discusses the reduction in the computational complexities due to the two improvements. Some conclusions are given in Section 2.4.

#### 2.1 Existing Majority-Logic Decoding Algorithms

The basic idea of the ISRB and IHRB algorithms [20] is the majority-logic decoding. They calculate reliability information of variable nodes iteratively. Based on the reliability information, by the majority-logic decoding, hard-decisions are made in each iteration and are passed from variable nodes to check nodes. After getting these harddecisions, check nodes provide votes for variable nodes. Here, a vote for a variable node provided by a check node is the value the variable node should be so that the check node is satisfied, assuming the other variable nodes adjacent to the check node take the values of hard decisions of the previous iteration. Then, based on the reliability information of the previous iteration and these votes, the reliability information of the current iteration is updated. Hence, the reliability information comes from the channel information and votes generated during iterations. The initial hard decisions come from the channel information. The difference between the ISRB and IHRB algorithms is that they use the soft and hard channel information, respectively, for the initial reliability information and vote information coefficients.

The EIHRB algorithm [23] was devised based on the IHRB algorithm by introducing a soft-reliability initialization. However, for vote information coefficients, the EIHRB algorithm still uses the hard channel information. Moreover, the EIHRB algorithm recalculate the extrinsic information to check nodes. Hence, if the soft-reliability information of the received symbol is available, the EIHRB algorithm achieves a better performance than the IHRB algorithm. Therefore, we focus on the EIHRB algorithm and do not consider the IHRB algorithm further.

For the ISRB, IHRB and EIHRB algorithm, the reliability information update is an

accumulation operation. To perform these three algorithm correctly, the reliability information must be kept from numerical saturation based on two methods. One is to use a very large numerical range to store the reliability information. The other is to carry out a clipping operation for the reliability information. Furthermore, the accumulated reliability information update conflicts the extrinsic information principle for the iteration message-passing algorithm.

#### 2.2 **Two Improvements**

A regular LDPC code C of length N over a finite field  $GF(2^r)$  is the null space of an  $M \times N$  sparse parity check matrix **H** over  $GF(2^r)$ . **H** has constant column and row weights of  $\gamma$  and  $\rho$ , respectively. Let  $\mathbf{h}_0, \mathbf{h}_1, \cdots, \mathbf{h}_{M-1}$  denote the rows of **H**, where  $\mathbf{h}_i = (h_{i,0}, h_{i,1}, \cdots, h_{i,N-1})$  for  $0 \leq i < M$ . Let  $(a_{l,0}, a_{l,1}, \cdots, a_{l,r-1})$ be the binary representation of  $a_l \in GF(2^r)$ , for  $0 \leq l < 2^r$ . Suppose a codeword  $\mathbf{x} = (x_0, x_1, \cdots, x_{N-1})$  is transmitted. Since  $x_i \in GF(2^r)$  can be represented by an r-tuple  $(x_{i,0}, x_{i,1}, \cdots, x_{i,r-1})$  over GF(2) for  $0 \leq i < N$ , an Nr-tuple over GF(2) is transmitted for each codeword. Let  $\mathbf{y} = (y_0, y_1, \cdots, y_{N-1})$  represent the received word, and  $\mathbf{z} = (z_0, z_1, \cdots, z_{N-1})$  and  $\mathbf{q} = (q_0, q_1, \cdots, q_{N-1})$  represent the hard decision and quantization, respectively, of the received word. Let  $N(i) = \{j : h_{i,j} \neq 0, 0 \leq j < N\}$ for  $0 \leq i < M$  and  $\mathcal{M}(j) = \{i : h_{i,j} \neq 0, 0 \leq i < M\}$  for  $0 \leq j < N$ .  $I_{\text{max}}$  represents the maximal iteration number. Throughout this chapter, the superscript (k) is added to denote variables in the k-th iteration.  $\mathbf{s}^{(k)}$  is the syndrome vector corresponding to  $\mathbf{z}^{(k)}$ .  $\sigma_{i,j}^{(k)}$  and  $\phi_{i,j}$  are the vote and vote information coefficient, respectively, from check node i to variable node j.  $\varphi_{j,l}, \psi_{j,l}^{(k)}$ , and  $R_{j,l}^{(k)}$  are the channel reliability, extrinsic reliability and overall reliability information, respectively, of the *j*-th received symbol being  $a_l$ .

#### 2.2.1 New Reliability Information Update

The reliability information update of the ISRB algorithm can be written as:

$$R_{j,l}^{(k+1)} = R_{j,l}^{(k)} + \psi_{j,l}^{(k)}$$

$$= R_{j,l}^{(0)} + \sum_{t=0}^{k} \psi_{j,l}^{(t)}$$

(2.1)

$R_{j,l}^{(k)}$  includes all check-to-variable (c-to-v) messages of previous iterations. This conflicts with the extrinsic information principle.

We propose a new reliability information update to exclude the c-to-v messages of previous iterations. The new reliability information update, shown as Eq. (2.2), uses only the channel information  $\varphi_{j,l}$  and  $\psi_{j,l}^{(k)}$  of the current iteration to compute the reliability information  $R_{j,l}^{(k+1)}$ :

$$R_{j,l}^{(k+1)} = \xi_1 \varphi_{j,l} + \xi_2 \psi_{j,l}^{(k)}, \qquad (2.2)$$

where  $\xi_1$  and  $\xi_2$  are two parameters to improve the error performance. Consequently the new algorithm, presented in Alg. 1, is called the IISRB algorithm.

To reduce complexity of the IISRB algorithm, we calculate  $\xi_1 \varphi_{i,j}$  and  $\xi_2 \phi_{i,j}$  in the initialization. This helps to reduce the complexity of each iteration.

By applying the new reliability information update to the EIHRB algorithm, we have

Algorithm 1: IISRB algorithm

/\* -----Initialization-----\*/ 1 for j = 0 : (N - 1) do  $z_j^{(0)} = z_j;$ 2 for  $l = 0 : (2^r - 1)$  do 3  $\begin{bmatrix} \varphi'_{j,l} = \sum_{t=0}^{r-1} (1 - 2a_{l,t}) q_{j,t}; \\ \varphi_{j,l} = \xi_1 \varphi'_{j,l}; \end{bmatrix}$ 4 5 6 for i = 0 : (M - 1) do for  $j \in \mathcal{N}(i)$  do 7  $\int \phi_{i,j} = \xi_2 \min_{t \in \mathcal{N}(i) \setminus \{j\}} \max_l \varphi'_{t,l};$ 8 /\* -----Iteration-----\*/ 9 for  $k = 0 : I_{\max} \operatorname{do}$  $\mathbf{s}^{(k)} = \mathbf{H} \cdot (\mathbf{z}^{(k)})^T;$ 10 if  $\mathbf{s}^{(k)} == 0$  then return  $\mathbf{z}^{(k)}$  else if  $k == I_{\max}$  then return Failure else 11 for j = 0 : (N - 1) do 12 for  $l = 0 : (2^r - 1)$  do 13  $\psi_{i,l}^{(k)} = 0;$ 14 for  $i \in \mathcal{M}(j)$  do 15  $\sigma_{i,j}^{(k)} = h_{i,j}^{-1} \sum_{t \in \mathcal{N}(i) \setminus \{j\}} h_{i,t} z_t^{(k)};$ for  $l = 0 : (2^r - 1)$  do 16 17  $\begin{bmatrix} \text{if } \sigma_{i,j}^{(k)} == a_l \text{ then } \psi_{j,l}^{(k)} = \psi_{j,l}^{(k)} + \phi_{i,j} \end{bmatrix}$ 18 for j = 0 : (N - 1) do 19 for  $l = 0 : (2^r - 1)$  do 20  $R_{j,l}^{(k+1)} = \varphi_{j,l} + \psi_{j,l}^{(k)};$ 21  $z_{j}^{(k+1)} = \arg_{a_{l}} \max R_{j,l}^{(k+1)};$ 22

the IEIHRB algorithm. For the sake of conciseness, we only present the initialization of the IEIHRB algorithm in Alg. 2, where  $c_1$ ,  $c_2$  and  $c_3$  are parameters to improve the error performance, because the iteration part of the IEIHRB algorithm is the same as that of the IISRB algorithm. For the IISRB algorithm,  $\phi_{i,j}$  is from the channel information. However, for the IEIHRB algorithm,  $\phi_{i,j}$  is a constant.

Algorithm 2: Initialization of the IEIHRB algorithm 1 for j = 0: (N - 1) do 2  $z_{j}^{(0)} = z_{j}$ ; 3 for l = 0:  $(2^{r} - 1)$  do 4  $\varphi_{j,l} = \sum_{t=0}^{r-1} (1 - 2a_{l,t})q_{j,t}$ ; 5  $R_{j,l}^{(0)} = \max(\lfloor \varphi_{j,l}/c_{1} \rfloor + c_{2} - \max_{l}(\lfloor \varphi_{j,l}/c_{1} \rfloor), 0)$ ; 6 for i = 0: (M - 1) do 7 for  $j \in \mathcal{N}(i)$  do 8  $\downarrow \phi_{i,j} = c_{3}$ ;

#### 2.2.2 Re-selection Scheme

Furthermore, we observe that the error floor of the ISRB algorithm becomes higher, as the column weight of the parity check matrix decreases. The IISRB algorithm suffers the same problem. Unless otherwise specified, the BPSK modulation, the additive white Gaussian noise (AWGN) channel with a single-sided power spectral density  $N_0$ , a 6-bit uniform quantization with 64 levels and an interval length  $\Delta = 0.0625$ , and  $I_{\text{max}} = 50$ are used in our following numerical simulations.

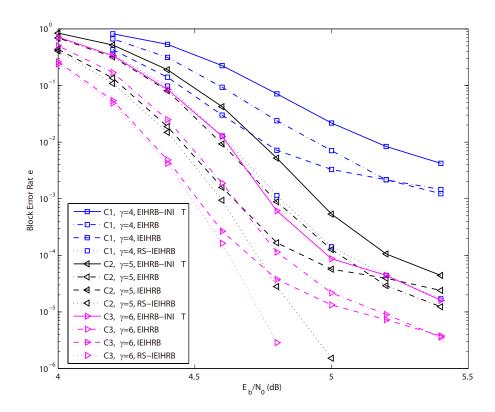

In Fig. 2.1, C1 is an (837, 726) LDPC code over  $GF(2^5)$  with a column weight of four, C2 an (806, 680) LDPC code over  $GF(2^5)$  with a column weight of five, C3 a (775, 634) LDPC code over  $GF(2^5)$  with a column weight of six. All three codes are

constructed based on Reed–Solomen codes with two information symbols [13]. The error floor of BLER performance becomes lower as the column weight of the parity check matrix increases. Hence, the column weight of the parity check matrix is one key factor for the error floor.

Figure 2.1: BLERs of the soft-reliability based algorithms for different codes with different column weights

We propose a re-selection scheme to address this problem. To simplify the discussion, here we focus on the IISRB algorithm. Our simulation results show that the re-selection scheme also applies to the ISRB, EIHRB and IEIHRB algorithms.

To analyze the error floor, the concept of periodic points is introduced. Given an

endomorphism  $f : Z \to Z$ , a point z in Z is called a *periodic point with a period of i* if there exists a smallest positive integer i so that  $f^{(i)}(z) = z$ , where  $f^{(i)} = f(f^{(i-1)}(z))$ .

An iteration of the IISRB algorithm can be considered a function f. The k-th iteration of the IISRB algorithm is  $\mathbf{z}^{(k)} = f(\mathbf{z}^{(k-1)}) = f^{(2)}(\mathbf{z}^{(k-2)}) = \cdots = f^{(k)}(\mathbf{z}^{(0)})$ , and if  $\mathbf{s}^{(k)} \neq 0$  and  $\mathbf{z}^{(k)} = \mathbf{z}^{(k-i)}$  for  $0 < i \leq k$ , the decoding algorithm results in a periodic point with a period of i. Our algorithm focuses on only the periodic points with a period of up to two for two reasons. First, our simulation results show that the BLERs are caused mainly by periodic points with periods one and two. Second, to identify the existence of a periodic point with a period of greater than two needs more memory to keep track of the hard decisions of the previous iterations.

If the Hamming distance between a periodic point and its corresponding transmitted codeword is less than  $\theta$ , the periodic point with a period of up to two is called a small-distance periodic point (SDPP). Otherwise, the periodic point with a period of up to two is called a large-distance periodic point (LDPP). The solid curves of Fig. 2.2 show the BLER of the IISRB algorithm and the BLER caused by SDPPs or LDPPs for the (837, 726) code when  $\theta = 8$ . For low SNRs, the overall BLER is dominated by those caused by LDPPs. The sum of the BLERs due to SDPPs and LDPPs is less than the overall BLER, because periodic points with a period greater than two also cause some BLERs. For high SNRs, the BLER caused by SDPPs dominates the total BLER. A similar trend for the ISRB algorithm was observed as well. Hence, for the ISRB and IISRB algorithms, the error floor is mainly caused by SDPPs.

Consider the hard decision process of line 22 of Alg. 1. If the most likely decision is wrong, the second most likely decision is supposed to be the best choice to be decoded. The smaller the difference between the maximal reliability information and the second

Figure 2.2: BLERs of SDPPs and LDPPs for the IISRB and RS-IISRB algorithm to decode the (837, 726) code

maximal reliability information, the greater the probability that the most likely decision is wrong.

Based on this intuition, when a periodic point is detected, the re-selection scheme tries to help the decoder get away from the periodic point by using the second most likely decision. The re-selection scheme consists of two steps. The first step is to identify the existence of a periodic point when the syndrome vector is a non-zero vector. The second step is to identify positions of erroneous symbols. A set is defined to include variable nodes adjacent to unsatisfied check nodes. This set contains some erroneous symbols. Then, among the variable nodes belonging to the set, the position of a variable node which has the smallest difference between its maximal reliability information and second maximal reliability information can be identified. If there are multiple variable nodes having the smallest difference, the first one is selected. Assume the index of this

position is rs\_n. Let us\_c<sub>j</sub> represent the number of unsatisfied check nodes connected with the *j*-th variable node for  $0 \le j < N$ . The most likely decision  $z_{rs_n}^{(k)}$  is replaced by the second most likely decision  $\tilde{z}_{rs_n}^{(k)}$ . Meanwhile,  $\varphi_{rs_n, z_{rs_n}^{(k)}}$  is reduced by a preset offset  $\zeta$  and  $\varphi_{rs_n, \tilde{z}_{rs_n}^{(k)}}$  is added by the same preset offset. The detailed re-selection scheme is described in Alg. 3. Here,  $s_i^{(k)}$  is the *i*-th value of the syndrome vector  $\mathbf{s}^{(k)}$ .

| Algorithm 3: Re-selection scheme                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>1</b> for $j = 0 : (N - 1)$ do                                                                                                                                                                                |

| 2 $\sum_{j=1}^{2} \tilde{z}_{j}^{(k)} = \arg_{a_l \in GF(2^r) \setminus \{z_j^{(k)}\}} \max R_{j,l}^{(k)};$                                                                                                      |

| 3 if $(\mathbf{z}^{(k-1)} == \mathbf{z}^{(k)})$ or $(\mathbf{z}^{(k-2)} == \mathbf{z}^{(k)})$ then                                                                                                               |

| 4 $\operatorname{dif}_{R=R}^{(k)} = R_{0,z_0^{(k)}}^{(k)};$                                                                                                                                                      |

| <b>5</b> for $j = 0 : (N - 1)$ do                                                                                                                                                                                |

| 6 $us_c_j = 0;$<br>7 for $i \in \mathcal{M}(j)$ do                                                                                                                                                               |

| 7 for $i \in \mathcal{M}(j)$ do                                                                                                                                                                                  |

| 8 <b>if</b> $(s_i^{(k)} > 0)$ then us_c <sub>j</sub> + +                                                                                                                                                         |

| 9 if $(us_c_j > 0)$ and $((R_{j,z_i^{(k)}}^{(k)} - R_{j,\tilde{z}_i^{(k)}}^{(k)}) < dif_R)$ then                                                                                                                 |

| 9 <b>if</b> $(us_c_j > 0)$ <b>and</b> $((R_{j,z_j^{(k)}}^{(k)} - R_{j,\tilde{z}_j^{(k)}}^{(k)}) < dif_R)$ <b>then</b><br>10 $dif_R = (R_{j,z_j^{(k)}}^{(k)} - R_{j,\tilde{z}_j^{(k)}}^{(k)});$<br>11 $rs_n = j;$ |

| 11   $rs_n = j;$                                                                                                                                                                                                 |

| 12                                                                                                                                                                                                               |

| 13 $\varphi_{\text{rs}_n, z_{\text{rs}_n}^{(k)}} = \varphi_{\text{rs}_n, z_{\text{rs}_n}^{(k)}} - \zeta;$                                                                                                        |

| 14 $\varphi_{\operatorname{rs}_{n},\tilde{z}_{\operatorname{rs}_{n}}^{(k)}} = \varphi_{\operatorname{rs}_{n},\tilde{z}_{\operatorname{rs}_{n}}^{(k)}} + \zeta;$                                                  |

| 15 $z_{rs_n}^{(k)} = \tilde{z}_{rs_n}^{(k)};$                                                                                                                                                                    |

| 16 for $i \in \mathcal{M}(\mathrm{rs\_n})$ do                                                                                                                                                                    |

| 17 $\begin{bmatrix} s_i^{(k)} = \mathbf{h}_i \cdot (\mathbf{z}^{(k)})^T; \end{bmatrix}$                                                                                                                          |

This scheme can be applied to any majority-logic decoding algorithms. For the IISRB algorithm, this scheme is added between lines 11 and 12. Similarly, the reselection scheme can be inserted at the corresponding position of other algorithms. "RS-" is prefixed in front of the name of the algorithms to show that an algorithm adopts the re-selection scheme. For instance, the ISRB algorithm with the re-selection scheme is called as the RS-ISRB algorithm.

The dash-dot lines of Fig. 2.2 show the BLERs of the RS-IISRB algorithm and those caused by SDPPs and LDPPs. Compared with the IISRB algorithm, the BLER caused by LDPPs descends to  $2 \times 10^{-4}$  from  $1.2 \times 10^{-3}$ , and the BLER caused by SDPPs is reduced to  $7 \times 10^{-5}$  from  $4 \times 10^{-3}$  when SNR is 4.8 dB. Hence, the rs-selection scheme reduces the occurrences of both SDPPs and LDPPs and works better on the former. Even for the RS-IISRB algorithm, SDPPs still are the primary reason for the error floor.

The re-selection scheme helps the decoding algorithm correct some periodic points. It is likely that the decoding algorithm goes out of a periodic point temporarily, and goes back to the same periodic point or results in another periodic point. Therefore, even with the re-selection scheme, the decoding algorithm still encounters the error floor problem. Moreover, the re-selection scheme works better on SDPPs because in general a SDPP involves fewer unsatisfied check nodes than a LDPP.

# 2.3 Performance Evaluation

#### **2.3.1** Error Performance and Average Numbers of Iterations

Our simulations focus on C1, C2, and C3, whose parity check matrices have small column weights, as well as a (255,175) cyclic LDPC code over  $GF(2^8)$  constructed with the method as describe in [46, Example 4], because it has a large column weight of 16.

We first compare the performance of the soft-reliability based algorithms. The ISRB, IISRB and RS-IISRB algorithms are used to decode the (255, 175) code. For the ISRB

algorithm, different values of  $\lambda = 4l$  for  $l = 1, 2, \dots, 8$ , were tried, and  $\lambda = 16$  leads to the best performance. For the new reliability information update, different combinations of  $\xi_1$  and  $\xi_2$  were tested. Since they are weighting factors, we fix  $\xi_2 = 1$  and try different values for  $\xi_1$ . For the (255, 175) code,  $\xi_1 = 4, 5, 6, 7, 8, 9, 10$  were tried and ( $\xi_1 = 7, \xi_2 = 1$ ) results in the best error performance<sup>1</sup>. The real values from 6.2 to 7 with a step size of 0.2 for  $\xi_1$  and  $\xi_2 = 1$  were tested as well. Performance differences between different real value coefficients are very small. Henceforth, integer values are used for  $\xi_1$  and  $\xi_2$  to reduce complexity.

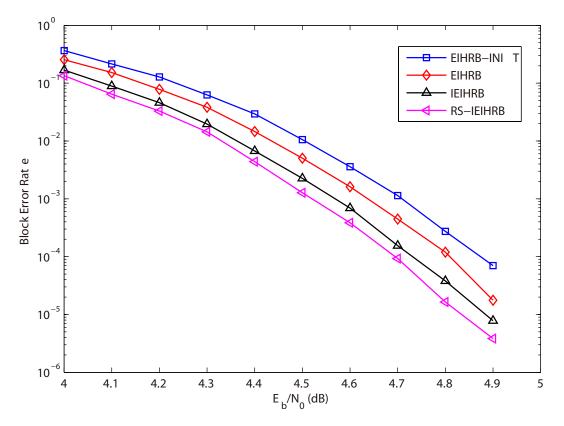

Figure 2.3: BLERs of the ISRB, IISRB and RS-IISRB algorithms for the (255, 175) code

The BLER curves of the ISRB, IISRB, RS-IISRB and Min-Max algorithms for the (255,175) code are shown in Fig. 2.3. The IISRB algorithm has a 0.15 dB coding gain versus the ISRB algorithm in this case. The RS-IISRB algorithm also achieves a slight

<sup>&</sup>lt;sup>1</sup>The comparison of these parameters is omitted due to the limited space, and can be found in an extended version of this manuscript [53].

improvement compared to the IISRB algorithm and has a performance loss of about 0.4 dB versus the Min-Max algorithm.

If a total of T iterations is used to decode K received words, the average number of iterations per received word is T/K. The average numbers of iterations per received word for the soft-reliability algorithms are compared in Table 2.1, where K is chosen such that at least 100 erroneous decoded words are observed for each SNR. Table 2.1 shows that both the RS-IISRB and IISRB algorithms require fewer iterations than the ISRB algorithm. At 4.7 dB, the average number of iterations of the IISRB algorithm is fewer by 10% than that of the ISRB algorithm. The advantage of the IISRB and RS-IISRB algorithm is even more pronounced for low SNRs.

Table 2.1: Average number of iterations of the Min-Max  $(n_m = 16)$ , ISRB, IISRB and RS-IISRB algorithms for the (255, 175) code

| $E_b/N_0(\mathrm{dB})$ | Min-Max [19] | ISRB [20] | IISRB | RS-IISRB |

|------------------------|--------------|-----------|-------|----------|

| 4.0                    | 2.35         | 18.76     | 11.58 | 11.25    |

| 4.1                    | 1.91         | 13.25     | 8.17  | 7.85     |

| 4.2                    | 1.60         | 9.10      | 5.78  | 5.71     |

| 4.3                    | 1.36         | 6.46      | 4.46  | 4.41     |

| 4.4                    | N/A          | 4.59      | 3.59  | 3.59     |

| 4.5                    | N/A          | 3.68      | 3.06  | 3.05     |

| 4.6                    | N/A          | 3.10      | 2.71  | 2.70     |

| 4.7                    | N/A          | 2.74      | 2.46  | 2.46     |

| 4.8                    | N/A          | 2.50      | 2.27  | 2.28     |

The ISRB, IISRB and RS-IISRB algorithms are also used to decode the (837, 726) code. The best BLER performance of the IISRB algorithm is achieved when  $\xi_1 = 4$  and  $\xi_2 = 1$ . Fig. 2.4 compares the BLERs of the ISRB, IISRB, RS-IISRB and Min-Max algorithms for this code. The IISRB algorithm has a 0.2 dB coding gain versus the ISRB algorithm, but both algorithms show an error floor around  $10^{-3}$ . Compared with these two algorithms, for low SNRs the RS-IISRB algorithm shows a slight improvement, and

for high SNRs the RS-IISRB algorithm lowers the error floor to below  $10^{-5}$  and has a performance loss of only 0.6 dB versus the Min-Max algorithm at the BLER of  $10^{-3}$ .

Figure 2.4: BLERs of the ISRB, IISRB and RS-IISRB algorithms for the (837, 726) code

The average numbers of iterations for the (837,726) code with different SNRs are listed in Table 2.2. The average numbers of iterations of the IISRB and RS-IISRB algorithms are fewer by at least 20% than that of the ISRB algorithm. The number of iterations of the RS-IISRB algorithm is slightly fewer than those of the IISRB algorithm because of the re-selection scheme. In addition, we compare the running time of different decoding algorithms (implemented in C) on a DELL Optiplex 755. To decode 10,000 codewords of the (837,726) code over the AWGN channel at the SNR of 5.4 dB, the ISRB, IISRB and RS-IISRB algorithms run 22.22, 19.48 and 19.37 seconds, respec-

tively. The running time is consistent with the comparison based on the average number

of iterations.

| $E_b/N_0$ (dB) | ISRB [20] | IISRB | <b>RS-IISRB</b> |

|----------------|-----------|-------|-----------------|

| 4.5            | 22.18     | 10.58 | 9.97            |

| 4.6            | 16.52     | 8.22  | 7.62            |

| 4.7            | 12.69     | 6.54  | 6.30            |

| 4.8            | 9.40      | 5.49  | 5.33            |

| 4.9            | 7.44      | 4.79  | 4.64            |

| 5.0            | 5.99      | 4.20  | 4.12            |

| 5.1            | 5.21      | 3.80  | 3.71            |

| 5.2            | 4.53      | 3.44  | 3.38            |

| 5.3            | 4.06      | 3.15  | 3.10            |

| 5.4            | 3.66      | 2.90  | 2.87            |

Table 2.2: Average number of iterations of the ISRB, IISRB and RS-IISRB algorithms for the (837, 726) code

For C1, C2 and C3, the BLERs of the RS-IISRB algorithm are shown with the dashed curves in Fig. 2.1. For C1 and C2,  $\xi_1 = 4$ ,  $\xi_2 = 1$ ,  $\lambda = 16$ ,  $\zeta = 32$ . For C3,  $\xi_1 = 5$ ,  $\xi_2 = 1$ ,  $\lambda = 16$ ,  $\zeta = 32$ . The RS-IISRB algorithm improves the BLER performance and lowers the error floor for all three codes. In Fig. 2.1, for C1, the simulation result for the RS-ISRB algorithm is shown as well, which does not adopt the new reliability information update but the re-selection scheme. It appears that the re-selection scheme also provides some performance gain. If both improvements are applied, the RS-IISRB algorithm achieves a greater performance gain.

We evaluate the proposed soft-reliability based algorithms over block fading channels, which are widely used in wireless communication systems involving slow timefrequency hopping or multi-carrier modulation using orthogonal frequency division multiplexing technique. We assume that each codeword experiences a block Rayleigh fading channel and that the receiver has perfect channel state information. For the (837,726) code over a block Rayleigh fading channel, the IISRB and RS-IISRB algorithms have a gain of about 0.2 dB over the ISRB algorithm, which is similar to that over the AWGN channel. The proposed improvements reduce the average number of iterations by about  $5\%^2$ .

Next, we compare the performances of hard-reliability based MLGD algorithms. The EIHRB-INIT algorithm [23] is a simplified version of the EIHRB algorithm without the recalculation of the extrinsic information. The RS-IEIHRB algorithm is developed by integrating the re-selection scheme describe in Section 2.2.2 into the IEIHRB algorithm.

Figure 2.5: BLERs of hard-reliability based algorithms for the (255,175) code

Fig. 2.5 shows the BLERs of different hard-reliability based algorithms for the  $^{2}$ More detail can be found in [53].

(255,175) code, and Table 2.3 lists the average numbers of iterations. For the EIHRB-INIT and EIHRB algorithm,  $c_1 = 4$  and  $c_2 = 15$ . For the IEIHRB and RS-IEIHRB algorithm,  $c_1 = 1$ ,  $c_2 = 63$ ,  $c_3 = 12$  and  $\zeta = 16$ . For the (255,175) code the new reliability information update provides about 0.05 dB performance gain, and the re-selection scheme provides another 0.05 dB performance gain. Hence, compared with the EIHRB algorithm, the RS-IEIHRB algorithm has about 0.1 dB performance gain, and the average number of iterations required by the RS-IEIHRB algorithm is reduced by about 30%.

Figure 2.6: BLERs of hard-reliability based algorithms for different non-binary LDPC codes with different column weights

Fig. 2.6 compares the BLERs of hard-reliability based algorithms for different nonbinary LDPC codes with different column weights. For C1 and C2,  $c_1 = 10$ ,  $c_2 = 63$ ,

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                        |           |            |       |        |                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------|-------|--------|------------------|

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                        | $E_b/N_0$ | EIHRB-INIT | EIHRB | IEIHRB | <b>RS-IEIHRB</b> |

|                                                                                                                                                                                                                                                               | (dB)      | [23]       | [23]  |        |                  |

|                                                                                                                                                                                                                                                               | 4.0       | 22.28      | 18.56 | 12.67  | 12.09            |

|                                                                                                                                                                                                                                                               | 4.1       | 16.48      | 13.62 | 8.99   | 8.85             |

| 4.46.445.573.703.694.55.154.703.103.104.64.294.072.732.724.73.753.652.472.474.83.383.332.282.28                                                                                                                                                               | 4.2       | 12.21      | 9.54  | 6.42   | 6.09             |

| 4.5         5.15         4.70         3.10         3.10           4.6         4.29         4.07         2.73         2.72           4.7         3.75         3.65         2.47         2.47           4.8         3.38         3.33         2.28         2.28 | 4.3       | 8.57       | 7.20  | 4.70   | 4.62             |

| 4.64.294.072.732.724.73.753.652.472.474.83.383.332.282.28                                                                                                                                                                                                     | 4.4       | 6.44       | 5.57  | 3.70   | 3.69             |

| 4.7         3.75         3.65         2.47         2.47           4.8         3.38         3.33         2.28         2.28                                                                                                                                     | 4.5       | 5.15       | 4.70  | 3.10   | 3.10             |

| 4.8 3.38 3.33 2.28 2.28                                                                                                                                                                                                                                       | 4.6       | 4.29       | 4.07  | 2.73   | 2.72             |

|                                                                                                                                                                                                                                                               | 4.7       | 3.75       | 3.65  | 2.47   | 2.47             |

| 4.9 3.09 3.06 2.14 2.14                                                                                                                                                                                                                                       | 4.8       | 3.38       | 3.33  | 2.28   | 2.28             |

|                                                                                                                                                                                                                                                               | 4.9       | 3.09       | 3.06  | 2.14   | 2.14             |

Table 2.3: Average number of iterations of the hard-reliability based algorithms for the (255, 175) code

$c_3 = 2$  and  $\zeta = 32$ . For C3,  $c_1 = 11$ ,  $c_2 = 63$ ,  $c_3 = 2$  and  $\zeta = 32$ . For the (837,726) code, the EIHRB algorithm also has an error floor of  $10^{-3}$ . For low SNRs, the IEIHRB algorithm outperforms the EIHRB algorithm and the RS-IEIHRB algorithm reduces the error floor to a level of  $10^{-5}$ . In the error floor region, the EIHRB algorithm is better than the IEIHRB algorithm because of the use of  $z_{i,t}^{(k)}$  and recalculating the extrinsic information in the latter. The two improvements in Section 2.2 also help to reduce the average number of iterations by at least 20% for the (837,726) code as listed in Table 2.4. For C2 and C3, the new reliability information update provides some performance gains for low SNRs, and the error floors are lowered effectively.

In summary, the two improvements introduced in Section 2.2 apply to both the softreliability and hard-reliability based MLGD algorithms. While both improvements improve the error performance and require fewer iterations on average, the re-selection scheme lowers the error floor of codes with low column weights effectively.

| $E_b/N_0$ | EIHRB-INIT | EIHRB | IEIHRB | <b>RS-IEIHRB</b> |

|-----------|------------|-------|--------|------------------|

| (dB)      | [23]       | [23]  |        |                  |

| 4.2       | 43.01      | 37.25 | 28.83  | 27.49            |

| 4.4       | 32.19      | 23.09 | 15.52  | 14.55            |

| 4.6       | 18.85      | 12.41 | 8.29   | 7.83             |