#### **Lehigh University** Lehigh Preserve

Theses and Dissertations

2015

## High Performance Decoder Architectures for Error Correction Codes

Jun Lin Lehigh University

Follow this and additional works at: http://preserve.lehigh.edu/etd

Part of the Electrical and Computer Engineering Commons

#### Recommended Citation

Lin, Jun, "High Performance Decoder Architectures for Error Correction Codes" (2015). Theses and Dissertations. 2686. http://preserve.lehigh.edu/etd/2686

This Dissertation is brought to you for free and open access by Lehigh Preserve. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of Lehigh Preserve. For more information, please contact preserve@lehigh.edu.

## HIGH PERFORMANCE DECODER ARCHITECTURES FOR ERROR CORRECTION CODES

by

Jun Lin

Presented to the Graduate and Research Committee of Lehigh University in Candidacy for the Degree of Doctor of Philosophy

in

Electrical Engineering

Lehigh University

May 2015

© Copyright 2015 by Jun Lin All Rights Reserved

| Date          |                                          |

|---------------|------------------------------------------|

|               |                                          |

|               | Prof. Zhiyuan Yan (Dissertation Advisor) |

| Accepted Date |                                          |

| -             | Committee Members:                       |

|               |                                          |

|               |                                          |

|               | Prof. Zhiyuan Yan<br>(Committee Chair)   |

|               |                                          |

|               | Prof. Meghanad D. Wag                    |

|               |                                          |

|               | Prof. Tiffany Jing Li                    |

|               |                                          |

|               | Dr. Zhongfeng Wang Broadcom Inc.         |

## Acknowledgments

First and foremost, I would like to express my special appreciation to my advisor Prof. Zhiyuan Yan for his continuous support of my Ph.D study and research. His rich experiences, insightful instructions and valuable expertise are the most important gifts I have ever received. Instead of sticking to a single topic, Prof. Yan encouraged me to explore more interesting and challenging research topics, which broadens my views and paves ways for my future career. His patience and encouragement inspired me to pursuit my dream as an academic researcher. Moreover, he taught me how to appreciate various ideas in a comprehensive manner and express complicated concepts and works in a clear way. Prof. Yan is also my life mentor and gave me a lot of valuable advices in seeking career opportunities. He recommended me for an internship in Qualcomm, which is one of the most wonderful experiences during the Ph. D study. It is really lucky for me to pursue my Ph.D degree under his guidance. I could not imagine having a better advisor and mentor for my Ph.D study.

Besides, I would like to thank Prof. Wagh, Prof. Tiffany Jing Li and Dr. Zhongfeng Wang for serving on my Ph.D committee and spending their precious time for examming my work. I am grateful for their encouragement, insightful

comments and inspiring questions.

Many sincere thanks to my labmates and friends in Lehigh University, Feng Shi, Hongmei Xie and Chenrong Xiong. We shared a lot of memorable time and exciting discussions. It is exciting to cooperate with them on developing wonderful ideas and results. In particular, I would like to thank them for helping me in finding an apartment and shopping grocery every week. My life in Lehigh University could be much harder without their help. Many thanks also go to my friends at Lehigh: Yang Liu, Jiangfan Zhang, Xuanxuan Lu et al. The wonderful time spent with you will be a precious part of my memory.

Finally, I would like to thank my parents for their endless support and unconditional love. They provided everything financially and spiritually for me to get better educations. Without their love and encouragement, I would not have made any achievements in my life.

## Contents

| A            | ckno  | wledgr      | ments                                             |      | iv           | 7 |

|--------------|-------|-------------|---------------------------------------------------|------|--------------|---|

| $\mathbf{C}$ | onter | $_{ m nts}$ |                                                   |      | $\mathbf{v}$ | i |

| Li           | st of | Table       | es                                                |      | x            | i |

| Li           | st of | Figur       | res                                               |      | xii          | i |

| $\mathbf{A}$ | bstra | ıct         |                                                   |      | ]            | L |

| 1            | Intr  | roduct      | ion                                               |      | 4            | 1 |

|              | 1.1   | Motiv       | vations                                           |      |              | 5 |

|              |       | 1.1.1       | Non-binary LDPC Codes                             |      | . !          | 5 |

|              |       | 1.1.2       | Polar Codes                                       |      | . ,          | 7 |

|              |       | 1.1.3       | Error Control Decoders for RLNC                   |      | . 8          | 3 |

|              | 1.2   | Contr       | ributions and Organization                        |      | . 10         | ) |

| 2            | An    | Efficie     | ent Shuffled Decoder Architecture for Nonbinary Q | uasi | i <b>-</b>   |   |

|              | Cyc   | clic LD     | OPC Codes                                         |      | 19           | ) |

|              | 2.1   | Introd      | luction                                           |      | . 19         | ) |

|   | 2.2               | Backg                                                 | $round \dots \dots$                                                                                               | 23                               |

|---|-------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|   | 2.3               | Shuffle                                               | ed and Modified Shuffled Schedule                                                                                                                                                                                       | 26                               |

|   |                   | 2.3.1                                                 | Shuffled Schedule                                                                                                                                                                                                       | 26                               |

|   |                   | 2.3.2                                                 | Modified Shuffled Schedule                                                                                                                                                                                              | 28                               |

|   |                   | 2.3.3                                                 | Simulation Results                                                                                                                                                                                                      | 29                               |

|   | 2.4               | Shuffle                                               | ed Decoder Architecture                                                                                                                                                                                                 | 32                               |

|   |                   | 2.4.1                                                 | Check Node Unit Architecture                                                                                                                                                                                            | 32                               |

|   |                   | 2.4.2                                                 | Variable Node Unit Architecture                                                                                                                                                                                         | 35                               |

|   |                   | 2.4.3                                                 | Top Decoder Architecture                                                                                                                                                                                                | 36                               |

|   |                   | 2.4.4                                                 | Implementation Results                                                                                                                                                                                                  | 38                               |

|   | 2.5               | Concl                                                 | usion                                                                                                                                                                                                                   | 40                               |

|   |                   |                                                       |                                                                                                                                                                                                                         |                                  |

| 3 | Λn                | Efficie                                               | ont Bully Parallol Docodor Architecture for Non-binary                                                                                                                                                                  |                                  |

| 3 |                   |                                                       | ent Fully Parallel Decoder Architecture for Non-binary                                                                                                                                                                  |                                  |

| 3 |                   | Efficie<br>PC Co                                      | · ·                                                                                                                                                                                                                     | <b>42</b>                        |

| 3 |                   | PC Co                                                 | · ·                                                                                                                                                                                                                     |                                  |

| 3 | LD                | PC Co                                                 | des                                                                                                                                                                                                                     | 42                               |

| 3 | <b>LD</b> ]       | PC Co                                                 | des 4                                                                                                                                                                                                                   | 42<br>46                         |

| 3 | <b>LD</b> ]       | PC Co Introd TBCF 3.2.1                               | des 4  Auction                                                                                                                                                                                                          | 42<br>46<br>46                   |

| 3 | 3.1<br>3.2        | PC Co Introd TBCF 3.2.1                               | des  duction                                                                                                                                                                                                            | 42<br>46<br>46<br>48             |

| 3 | 3.1<br>3.2        | PC Co Introd TBCF 3.2.1 Impro 3.3.1                   | des  duction                                                                                                                                                                                                            | 42<br>46<br>46<br>48             |

| 3 | 3.1<br>3.2        | PC Co Introd TBCF 3.2.1 Impro 3.3.1                   | des  des  duction                                                                                                                                                                                                       | 42<br>46<br>46<br>48             |

| 3 | 3.1<br>3.2        | PC Co Introd TBCF 3.2.1 Impro 3.3.1 3.3.2             | des  duction  algorithm  Trellis based check node processing algorithm  ved Decoding Algorithm for NB-LDPC Codes  RTBCP algorithm  LLR compression for a priori messages  Simplified variable node processing algorithm | 42<br>46<br>48<br>48<br>51       |

| 3 | 3.1<br>3.2        | PC Co Introd TBCF 3.2.1 Impro 3.3.1 3.3.2 3.3.3 3.3.4 | des  duction                                                                                                                                                                                                            | 42<br>46<br>46<br>48<br>51<br>52 |

| 3 | 3.1<br>3.2<br>3.3 | PC Co Introd TBCF 3.2.1 Impro 3.3.1 3.3.2 3.3.3 3.3.4 | des  uction                                                                                                                                                                                                             | 42<br>46<br>48<br>48<br>51<br>52 |

|   |      | 3.4.3   | Low-latency VNU architecture                               | . 65  |

|---|------|---------|------------------------------------------------------------|-------|

|   |      | 3.4.4   | Decoding schedule, decoder throughput, and interconnection | . 70  |

|   | 3.5  | Imple   | mentation Results and Comparisons                          | . 73  |

|   | 3.6  | Concl   | usion                                                      | . 75  |

| 4 | Effi | cient E | Error Control Decoder Architectures for Noncoherent Ra     | n-    |

|   | don  | n Linea | ar Network Coding                                          | 77    |

|   | 4.1  | Introd  | luction                                                    | . 77  |

|   | 4.2  | KK ar   | nd MV codes                                                | . 81  |

|   |      | 4.2.1   | KK codes and its decoding algorithms                       | . 81  |

|   |      | 4.2.2   | $\operatorname{MV}$ codes and its list decoding algorithm  | . 85  |

|   | 4.3  | Efficie | ent KK decoder architectures                               | . 89  |

|   |      | 4.3.1   | Serial decoder architecture                                | . 89  |

|   |      | 4.3.2   | Unfolded decoder architecture                              | . 96  |

|   | 4.4  | Efficie | ent MV list Decoder Architecture                           | . 98  |

|   |      | 4.4.1   | Serial list decoder architecture                           | . 98  |

|   |      | 4.4.2   | Efficient interpolator architecture for MV codes           | . 100 |

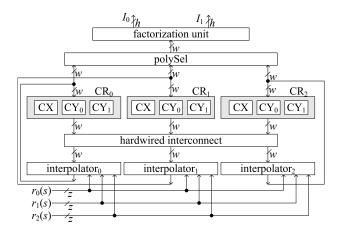

|   |      | 4.4.3   | Efficient factorization architecture for MV codes          | . 102 |

|   | 4.5  | Imple   | mentation Results                                          | . 112 |

|   | 4.6  | Concl   | usion                                                      | . 113 |

| 5 | An   | Efficie | ent List Decoder Architecture for Polar Codes              | 115   |

|   | 5.1  | Introd  | luction                                                    | . 115 |

|   | 5.2  | Polar   | Codes and Its CA-SCL Algorithm                             | . 118 |

|   |      | 591     | Polar Codos                                                | 110   |

|   |     | 5.2.2          | SCL and CA-SCL Algorithms                                 |

|---|-----|----------------|-----------------------------------------------------------|

|   | 5.3 | Two I          | mprovements of the CA-SCL Algorithm                       |

|   |     | 5.3.1          | Numerical Results                                         |

|   | 5.4 | Efficie        | ent List Decoder Architecture                             |

|   |     | 5.4.1          | Message Memory Architecture                               |

|   |     | 5.4.2          | Processing Unit Array                                     |

|   |     | 5.4.3          | Path Pruning Unit                                         |

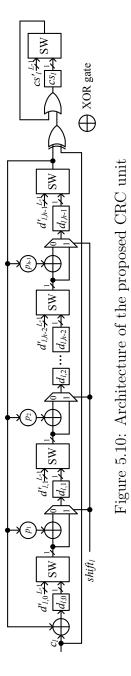

|   |     | 5.4.4          | Partial Sum Update Unit and the CRC Unit                  |

|   |     | 5.4.5          | Decoding Cycles                                           |

|   |     | 5.4.6          | Scalability of the Proposed List Decoder Architecture 148 |

|   | 5.5 | Imple          | mentation Results                                         |

|   | 5.6 | Concl          | usion                                                     |

| 6 | A F | Iigh T         | hroughput List Decoder Architecture for Polar Codes 153   |

|   | 6.1 | Introd         | luction                                                   |

|   | 6.2 | Prelin         | ninaries                                                  |

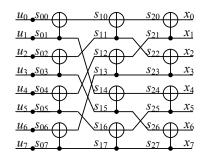

|   |     | 6.2.1          | Polar Codes                                               |

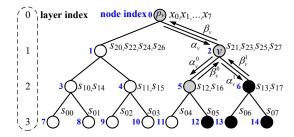

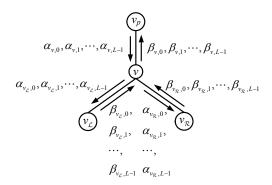

|   |     | 6.2.2          | Prior Tree-Based SC Algorithms                            |

|   |     | 6.2.3          | LLR Based List Decoding Algorithms                        |

|   | 6.3 | Reduc          | eed Latency List Decoding Algorithm                       |

|   |     | 6.3.1          | SCL Decoding on A Tree                                    |

|   |     |                |                                                           |

|   |     | 6.3.2          | Proposed RLLD algorithm                                   |

|   |     | 6.3.2<br>6.3.3 | Proposed RLLD algorithm                                   |

|   |     |                | •                                                         |

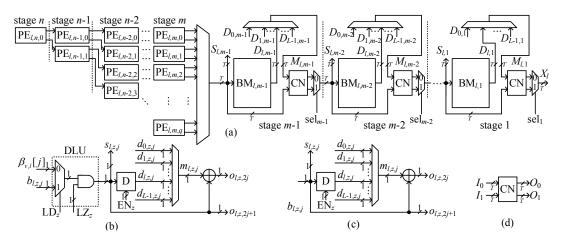

|                           | 6.4    | High '  | Throughput List Polar Decoder Architecture   | 176 |

|---------------------------|--------|---------|----------------------------------------------|-----|

|                           |        | 6.4.1   | Top Decoder Architecture                     | 176 |

|                           |        | 6.4.2   | Memory Efficient Quantization Scheme         | 178 |

|                           |        | 6.4.3   | Proposed path pruning unit                   | 180 |

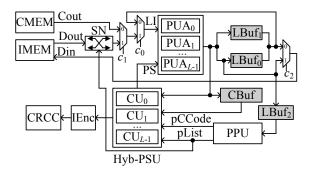

|                           |        | 6.4.4   | Proposed hybrid partial sum computation unit | 184 |

|                           |        | 6.4.5   | Latency and Throughput                       | 191 |

|                           | 6.5    | Imple   | mentation Results and Comparisons            | 196 |

|                           | 6.6    | Concl   | usion                                        | 199 |

| 7                         | Cor    | ıclusio | ons and Future Work                          | 200 |

|                           | 7.1    | Concl   | usions                                       | 200 |

|                           | 7.2    | Futur   | e Work                                       | 202 |

| $\mathbf{B}_{\mathbf{i}}$ | ibliog | graphy  | •                                            | 204 |

| $\mathbf{V}^{:}$          | ita    |         |                                              | 216 |

## List of Tables

| 2.1 | Decoder Complexity Comparison for an (837, 726) LDPC Code over               |

|-----|------------------------------------------------------------------------------|

|     | GF(32)                                                                       |

| 3.1 | Computational complexity comparison between the proposed SVNP                |

|     | and the VNP algorithm in [1]                                                 |

| 3.2 | Computational complexity comparison between the improved decod-              |

|     | ing algorithm and the RHS algorithm in [2]                                   |

| 3.3 | Comparisons of LGUs and CGU with a 32×5 SRAM 70                              |

| 3.4 | Comparisons with other decoder architectures                                 |

| 4.1 | Interpolation by Polynomials and Linearized Polynomials 84                   |

| 4.2 | Hardware implementation results comparison                                   |

| 5.1 | Area per Bit for RFs with Different Depth and Width 128 using                |

|     | TSMC 90nm CMOS technology                                                    |

| 5.2 | Bit width of LLM Inputs of $\mathrm{PU}_{l,j}$ when $n=10,T=8$ and $t=4$ 136 |

| 5.3 | Area comparison between fine grained PU array and regular PU using           |

|     | TSMC 90nm CMOS technology                                                    |

| 5.4 | Comparison of ASIC implementation results using TSMC 90nm CMOS           |

|-----|--------------------------------------------------------------------------|

|     | technology                                                               |

| 5.5 | Implementation Results With $R'=0.468$ and $R=0.5$                       |

| 6.1 | The Values of $q_{I_v,L}$ 's under Different List Sizes and $I_v$ 's 174 |

| 6.2 | Hardware resources needed by different methods per list 184              |

| 6.3 | Implementation Results for $N=2^{10}, R=0.5$                             |

| 6.4 | Implementation Results for $N=2^{13}, R=0.5$                             |

| 6.5 | Implementation Results for $N=2^{15}, R=0.9004$                          |

| 6.6 | $N_P^{(i)}$ with Respect to $I_n$ and $L$                                |

## List of Figures

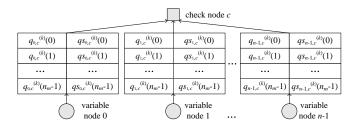

| 2.1  | Messages sent form check node to variable node                         | 24 |

|------|------------------------------------------------------------------------|----|

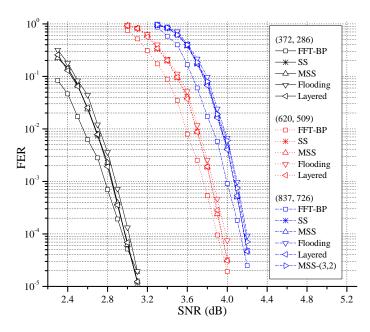

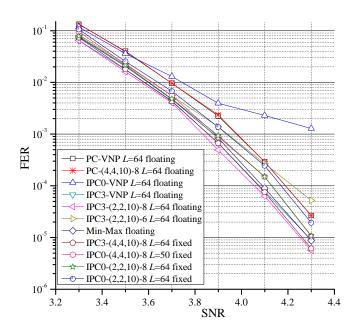

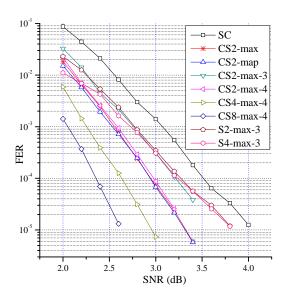

| 2.2  | FERs of selected codes                                                 | 30 |

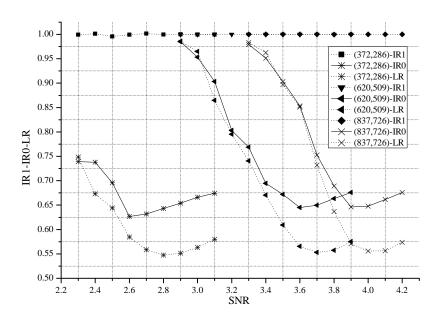

| 2.3  | Comparison of convergence rates                                        | 30 |

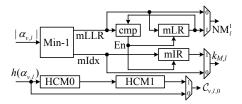

| 2.4  | CNU Architecture                                                       | 32 |

| 2.5  | Architecture of Proposed Top Sorter                                    | 33 |

| 2.6  | Proposed RMAG Architecture                                             | 33 |

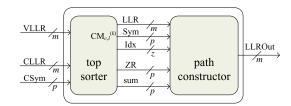

| 2.7  | Proposed Path Constructor Architecture                                 | 35 |

| 2.8  | Proposed VNU Architecture                                              | 36 |

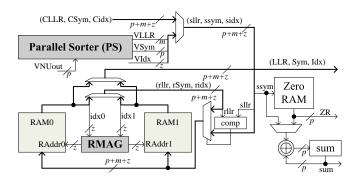

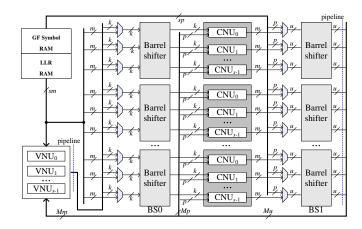

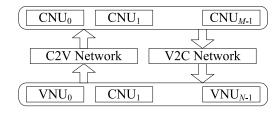

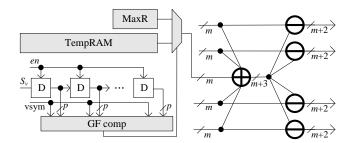

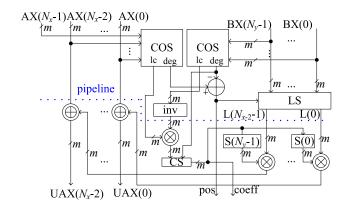

| 2.9  | Proposed shuffled decoder architecture for NB QC-LDPC codes $\ \ldots$ | 37 |

| 2.10 | Decoding Schedule of Proposed Shuffled Decoder                         | 38 |

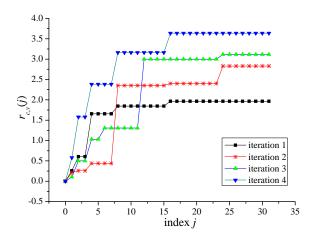

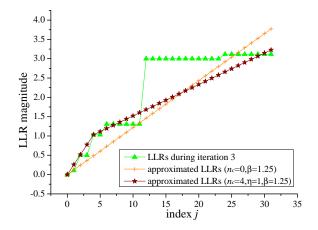

| 3.1  | LLR evolution                                                          | 49 |

| 3.2  | LLR approximation when $n_m = 32 \dots \dots \dots$                    | 50 |

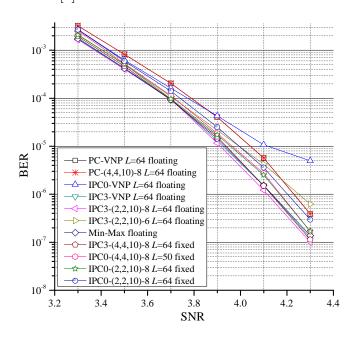

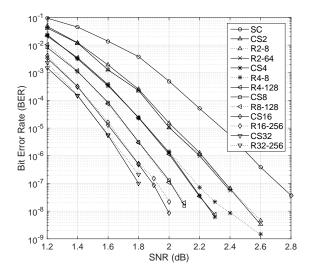

| 3.3  | BER performance of the (110, 88) NB-LDPC code over $\mathrm{GF}(256)$  | 55 |

| 3.4  | FER performance of the (110, 88) NB-LDPC code over $\mathrm{GF}(256)$  | 56 |

| 3.5  | BER performance of the (372, 248) NB-LDPC code over $\mathrm{GF}(32)$  | 59 |

| 3.6  | FER performance of the (372, 248) NB-LDPC code over $\mathrm{GF}(32)$  | 60 |

| 3.7  | Proposed fully parallel decoder architecture                           | 60 |

| 3.8  | Parallel CNU architecture                                                            | 61  |

|------|--------------------------------------------------------------------------------------|-----|

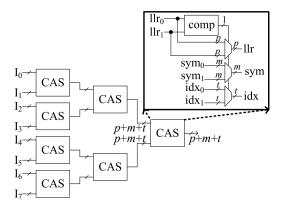

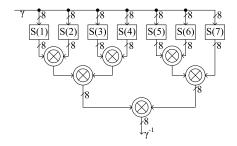

| 3.9  | Parallel sorter architecture                                                         | 62  |

| 3.10 | The macro architecture of MLF when the number of input is $8\ldots$                  | 63  |

| 3.11 | Path constructor architecture                                                        | 65  |

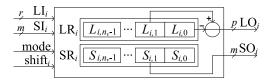

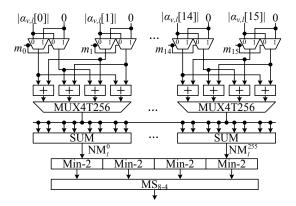

| 3.12 | VNU architecture assuming $d_v = 2 \dots \dots \dots \dots$                          | 66  |

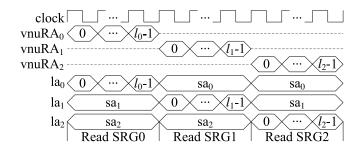

| 3.13 | Reading behavior of the SRGs during the variable node processing                     | 68  |

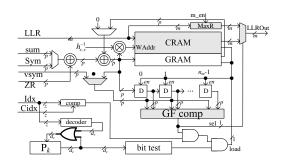

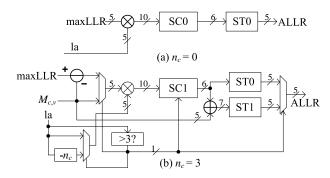

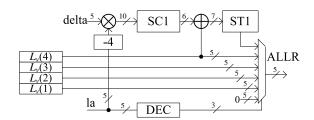

| 3.14 | Architectures of the proposed LGUs                                                   | 69  |

| 3.15 | Architectures of the proposed CGU                                                    | 69  |

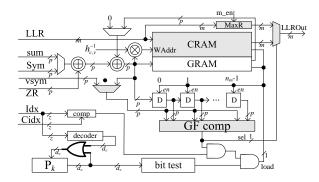

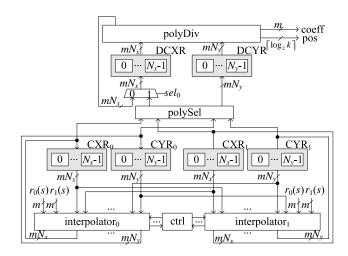

| 4.1  | Serial KK decoder architecture                                                       | 90  |

| 4.2  | Architecture of $interpolator_0$                                                     | 90  |

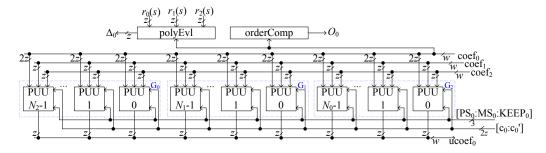

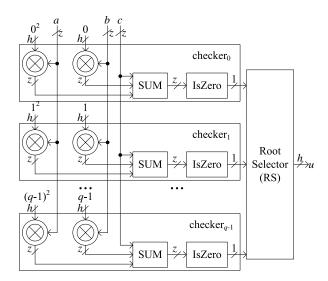

| 4.3  | Architecture of polyEvl for interpolator $0 \dots \dots \dots \dots \dots$           | 92  |

| 4.4  | Architecture of order<br>Comp for interpolator                                       | 92  |

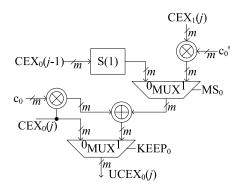

| 4.5  | Architecture of the PUU that updates the coefficient of $x^{[j]}$                    | 93  |

| 4.6  | Architecture of the polyDiv unit                                                     | 95  |

| 4.7  | Parallel inversion architecture over $\mathrm{GF}(2^8)$                              | 95  |

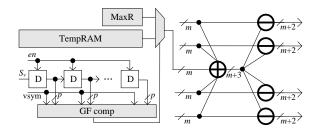

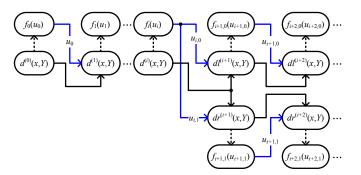

| 4.8  | Unfolded decoder architecture                                                        | 97  |

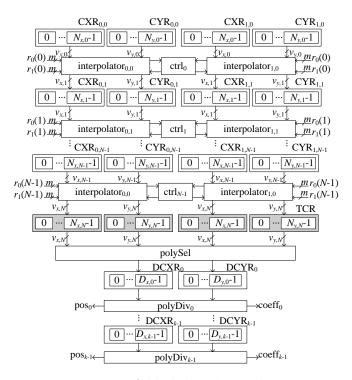

| 4.9  | Unfolded decoder architecture                                                        | 99  |

| 4.10 | The architecture of interpolator $_0$ for the proposed MV decoder 1                  | 00  |

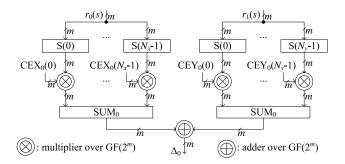

| 4.11 | Architecture of polyEvl for interpolator <sub>0</sub> of the proposed MV decoder 1   | 01  |

| 4.12 | Architecture of order<br>Comp for interpolator $_{0}$ of the proposed MV de-         |     |

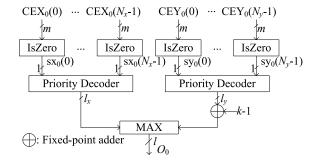

|      | coder                                                                                | 01  |

| 4.13 | Architecture of PUU that updates $x^{[j]}$ for interpolator <sub>0</sub> of the pro- |     |

|      | posed MV decoder                                                                     | 02  |

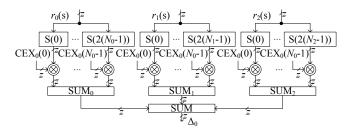

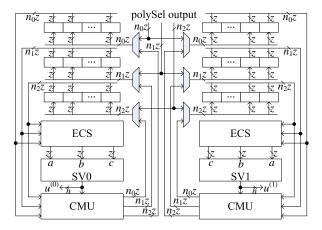

| 4.14 | Root pattern                                                                         | .05 |

| 4.15 | Architecture of factorization for MV decoder $(L=2)$ 109             |

|------|----------------------------------------------------------------------|

| 4.16 | Architecture of SV0                                                  |

| 5.1  | Compressed channel message                                           |

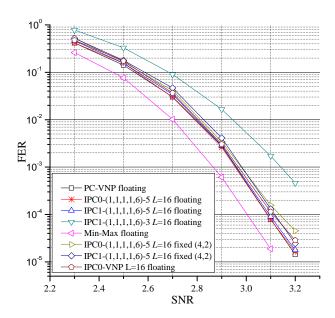

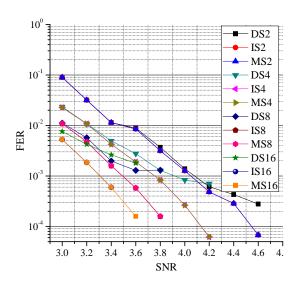

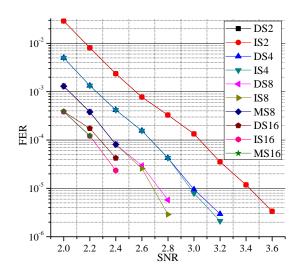

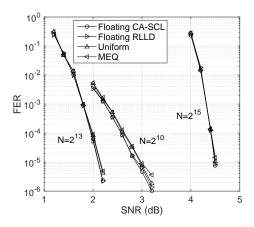

| 5.2  | FER performance of a polar code with $N=1024$                        |

| 5.3  | FER performances under CRC16 and rate 0.75                           |

| 5.4  | FER performances under CRC16 and rate 0.5                            |

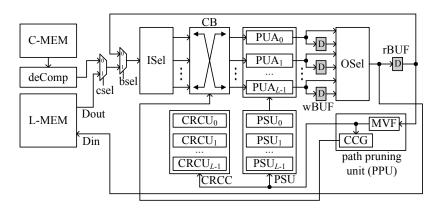

| 5.5  | Top architecture of the list decoder                                 |

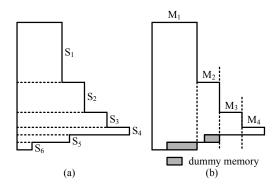

| 5.6  | The split of an irregular LLM memory                                 |

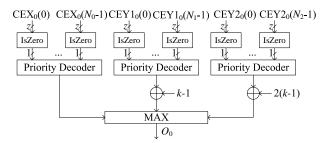

| 5.7  | Maximum values filter architecture                                   |

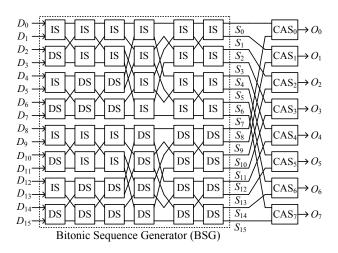

| 5.8  | (a) Architectures of IS (b) Architectures of DS (c) Architectures of |

|      | CAS $(z = x_1 + x_2 + 1)$                                            |

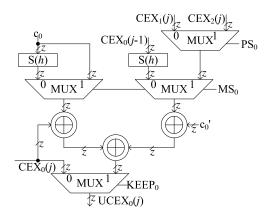

| 5.9  | PSU architecture                                                     |

| 5.10 | Architecture of the proposed CRC unit                                |

| 6.1  | Polar encoder with $N=8$                                             |

| 6.2  | Binary tree representation of an (8, 3) polar code                   |

| 6.3  | Node activation schedule for SC based list decoding on $G_n$ 163     |

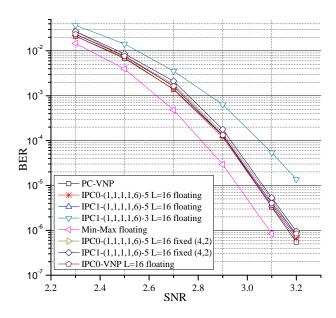

| 6.4  | BER performance for an (8192, 4096) polar code                       |

| 6.5  | Decoder top architecture                                             |

| 6.6  | Effects of the proposed MEQ scheme on the error performances $$ 180  |

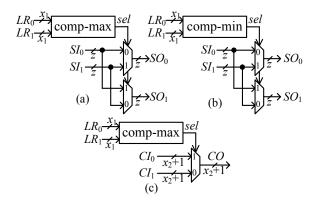

| 6.7  | The proposed architecture for PPU                                    |

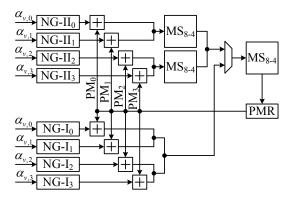

| 6.8  | Hardware architecture of the proposed NG-I $_l$                      |

| 6.9  | Architecture of NG-II <sub>1</sub>                                   |

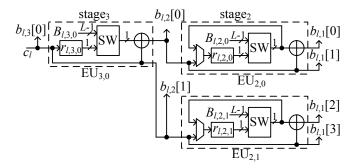

| 6.10 | (a) Top  | architecture | e of CU  | $U_l$ . | (b) | ] | Гур | e-I | PF | ᠍. ( | (c) | Τ, | ype | e-II | [ ] | PΕ | . ( | (d) |     |

|------|----------|--------------|----------|---------|-----|---|-----|-----|----|------|-----|----|-----|------|-----|----|-----|-----|-----|

|      | Inputs a | and outputs  | of the ( | CN.     |     |   |     |     |    |      |     |    |     |      |     |    |     |     | 187 |

### Abstract

Due to the rapid development of the information industry, modern communication and storage systems require much higher data rates and reliability to server various demanding applications. However, these systems suffer from noises from the practical channels. Various error correction codes (ECCs), such as Reed-Solomon (RS) codes, convolutional codes, turbo codes, Low-Density Parity-Check (LDPC) codes and so on, have been adopted in lots of current standards. With the increasing data rate, the research of more advanced ECCs and the corresponding efficient decoders will never stop.

Binary LDPC codes have been adopted in lots of modern communication and storage applications due their superior error performance and efficient hardware decoder implementations. Non-binary LDPC (NB-LDPC) codes are an important extension of traditional binary LDPC codes. Compared with its binary counterpart, NB-LDPC codes show better error performance under short to moderate block lengths and higher order modulations. Moreover, NB-LDPC codes have lower error floor than binary LDPC codes. In spite of the excellent error performance, it is hard for current communication and storage systems to adopt NB-LDPC codes due to

complex decoding algorithms and decoder architectures. In terms of hardware implementation, current NB-LDPC decoders need much larger area and achieve much lower data throughput.

Besides the recently proposed NB-LDPC codes, polar codes, discovered by Arıkan, appear as a very promising candidate for future communication and storage systems. Polar codes are considered as a major breakthrough in recent coding theory society. Polar codes are proved to be capacity achieving codes over binary input symmetric memoryless channels. Besides, polar codes can be decoded by the successive cancelation (SC) algorithm with of complexity of  $\mathcal{O}(N\log_2 N)$ , where N is the block length. The main sticking point of polar codes to date is that their error performance under short to moderate block lengths is inferior compared with LDPC codes or turbo codes. The list decoding technique can be used to improve the error performance of SC algorithms at the cost higher computational and memory complexities. Besides, the hardware implementation of current SC based decoders suffer from long decoding latency which is unsuitable for modern high speed communications.

ECCs also find their applications in improving the reliability of network coding. Random linear network coding is an efficient technique for disseminating information in networks, but it is highly susceptible to errors. Kötter-Kschischang (KK) codes and Mahdavifar-Vardy (MV) codes are two important families of subspace codes that provide error control in noncoherent random linear network coding. List decoding has been used to decode MV codes beyond half distance. Existing hardware implementations of the rank metric decoder for KK codes suffer from limited throughput, long latency and high area complexity. The interpolation-based list decoding algorithm for MV codes still has high computational complexity, and its

feasibility for hardware implementations has not been investigated.

In this exam, we present efficient decoding algorithms and hardware decoder architectures for NB-LDPC codes, polar codes, KK and MV codes. For NB-LDPC codes, an efficient shuffled decoder architecture is presented to reduce the number of average iterations and improve the throughput. Besides, a fully parallel decoder architecture for NB-LDPC codes with short or moderate block lengths is also presented. Our fully parallel decoder architecture achieves much higher throughput and area efficiency compared with the state-of-art NB-LDPC decoders. For polar codes, a memory efficient list decoder architecture is first presented. Based on our reduced latency list decoding algorithm for polar codes, a high throughput list decoder architecture is also presented. At last, we present efficient decoder architectures for both KK and MV codes.

## Chapter 1

### Introduction

Error correction codes (ECCs), such as Reed-Solomon (RS) codes, convolutional codes, turbo codes, Low-Density Parity-Check (LDPC) codes and so on, are widely used in current communication and storage systems. Non-binary LDPC codes and polar codes are recently emerged ECCs for future applications. However, NB-LDPC codes suffer from high decoding algorithms and inefficient hardware decoder architecture. The successive cancelation (SC) based list (SCL) decoding algorithm for polar codes has much better error performance that the SC algorithm. However, the hardware implementations of the SCL decoding algorithm suffer from long decoding latency, which is unsuitable for high speed applications. Besides, ECCs also find applications in random linear network coding (RLNC). The Kötter-Kschischang (KK) codes and Mahdavifar-Vardy (MV) codes are two important families of subspace codes that provide error control in noncoherent random linear network coding.

In this chapter, we first explain our motivations of our research in Sec. 1.1, and then present our main contributions in this dissertation as well as the organization

of this dissertation in Sec. 1.2.

#### 1.1 Motivations

#### 1.1.1 Non-binary LDPC Codes

Binary low-density parity-check (LDPC) codes are more and more popular in applications because of their capacity-approaching performance. In terms of performance, binary LDPC codes start to show their weaknesses when the codeword length is small or moderate, or when a higher order modulation is used. For these cases, nonbinary LDPC (NB-LDPC) codes over high order Galois fields have shown great potential [3, 4]. For instance, in [1], a rate-1/2 NB-LDPC code of length 84 over GF(64) is shown to perform 0.375dB better than a rate-1/2 binary irregular LDPC code of equivalent length 504 bits in [5] over binary input additive white Gaussian noise (AWGN) channel. Over the QAM-AWGN channels, NB-LDPC codes with a field order greater than or equal to the size of constellation have the advantage that the encoder/decoder works directly with symbols. All mapping choices of the codeword symbols to the constellation points are equivalent and lead to the same performance. In [1], an NB-LDPC code over GF(256) performs 0.5dB better than a rate-1/2 binary LDPC codes of the equivalent length 1008 bits over QAM256-AWGN channel.

A significant obstacle to the application of NB-LDPC codes is that their decoding algorithms have high complexities. Hence, a lot of research effort has been spent on efficient decoding algorithms for NB-LDPC codes [1,6]. Among them, the EMS [1] and the Min-Max [6] algorithms draw a lot of attention because of their low

computation and memory complexity. For an NB-LDPC code over  $GF(2^m)$ , both the EMS and the Min-Max algorithms store only the  $n_m$  ( $n_m \ll 2^m$ ) most reliable messages, thus reducing the memory requirement at the cost of small performance degradation. The check node processing of the EMS algorithm needs additions and comparisons, while the Min-Max algorithm needs only maximizations and comparisons in check node processing. The trellis-based check node processing (TBCP) algorithm [7] reduces the computational complexity of check node processing of the Min-Max algorithm by eliminating unnecessary check-to-variable messages.

Besides the Min-Max and EMS decoding algorithms, stochastic decoding [2,8,9] is another way to reduce the hardware complexity of NB-LDPC decoders while maintaining the decoding performance. Compared to conventional belief propagation decoding algorithms, the stochastic decoding algorithm has lower hardware complexity [9]. The relaxed half-stochastic decoding algorithm optimized for NB-LPDC codes with variable node degree 2, called the RD2 algorithm, was proposed in [8]. The RD2 decoding algorithm reduces the decoding complexity by reducing the number of real multiplications significantly. An improved version of the RD2 algorithm, called the NoX decoding algorithm [2], is proposed to further reduce the computational complexity.

Recently, a considerable amount of research effort has been spent on efficient decoder architectures for NB-LDPC codes [9–17]. Existing NB-LDPC decoders still suffer from low throughput and large hardware complexity. For example, a (248, 124) NB-LDPC decoder over GF(32) [15] achieves a throughput of 47.69 Mb/s at the cost of 10.33 mm<sup>2</sup> silicon area under 90nm technology. An (837, 726) NB-LDPC decoder [16] over GF(32) achieves a throughput of 60Mb/s at the cost of 1.29M

standard NAND gates using the 180nm technology. The FPGA implementation of a (192, 96) stochastic AMSA decoder [9] over GF(256) achieves a throughput of 64Mb/s at the frequency of 108MHz.

#### 1.1.2 Polar Codes

Polar codes, recently introduced by Arıkan [18], are a significant breakthrough in coding theory. It is proved that polar codes can achieve the channel capacity of any discrete or continuous memoryless channel [18, 19]. Polar codes can be efficiently decoded by the low-complexity successive cancelation (SC) decoding algorithm [18] with a complexity of  $O(N \log N)$ , where N is the block length. To approach the channel capacity using the SC algorithm, polar codes require very large code block length (for example,  $N > 2^{20}$  [20]), which is impractical in many applications. For short or moderate length, the error performance of polar codes under the SC algorithm is worse than that of Turbo or low-density parity-check (LDPC) codes [21].

Lots of efforts [21–28] have already been devoted to the improvement of error-correction performance of polar codes with short or moderate lengths. An SC list (SCL) decoding algorithm was proposed recently in [21], which performs better than the SC algorithm and performs almost the same as a maximum-likelihood (ML) decoder [21]. In [22–24], the cyclic redundancy check (CRC) is used to pick the output codeword from L candidates, where L is the list size. The CRC-aided SCL algorithm performs much better than the SCL algorithm at the expense of negligible loss in code rate.

In terms of hardware implementations of the SC algorithm, an efficient semiparallel SC decoder was proposed in [20], where resource sharing and semi-parallel

processing were used to reduce the hardware complexity. An overlapped computation method and a pre-computation method were proposed in [29] to improve the throughput and to reduce the decoding latency of SC decoders. Compared to the semi-parallel decoder architecture in [20], the pre-computation based decoder architecture [29] can double the throughput. A simplified SC decoder for polar codes, proposed in [30], reduces the decoding latency by more than 88% for a rate 0.7 polar code with length 2<sup>18</sup>.

Despite its significantly improved error performance, the hardware implementations of SC based list decoders [31–34] still suffer from long decoding latency and limited throughput due to the serial decoding schedule. In order to reduce the decoding latency of an SC based list decoder, M (M > 1) bits are decoded in parallel in [35–37], where the decoding latency can be reduced by M times ideally. However, for the hardware implementations of the algorithms in [35–37], the actually achieved decoding latency reduction is less than M due to extra decoding cycles on finding the L most reliable paths among  $2^M L$  candidates, where L is list size. A software adaptive SSC-list-CRC decoder was proposed in [38]. For a (2048, 1723) polar+CRC-32 code, the SSC-list-CRC decoder with L=32 was shown to be about 7 times faster than an SC based list decoder. However, it is unclear whether the list decoder in [38] is suitable for hardware implementation.

#### 1.1.3 Error Control Decoders for RLNC

Random linear network coding (RLNC) is an efficient technique for disseminating information in networks (see, for example, [39–42]). Due to its random linear operations, RLNC not only achieves network capacity with high probability in a

distributed manner, but also provides robustness against varying network conditions [43]. Unfortunately, it is highly susceptible to errors due to noise, malicious or malfunctioning nodes, or insufficient min-cut [44]. As a result, error control is vital for RLNC.

Error control methods proposed for RLNC assume two transmission models. The methods for the first model (see, for example, [45]) depend on and take advantage of the underlying network topology or the particular linear networking operations performed at various nodes. The methods for the other model (see, e.g., [44, 46]) assume that both the transmitter and the receiver have no knowledge of such channel transfer characteristics. The two models are referred to as coherent and noncoherent network coding, respectively. In this paper, we focus on error control for noncoherent RLNC.

An error control code for noncoherent network coding [44], called a subspace code, is a set of subspaces. Information is encoded in the choice of a subspace spanned by a set of transmitted packets. A subspace code is called a constant-dimension code (CDC) if all subspaces are of the same dimension. CDCs lead to simplified network protocols due to the constant dimension. A class of asymptotically optimal CDCs, referred to as Kötter-Kschischang (KK) codes, has been proposed in [44]. A decoding algorithm based on interpolation for bivariate linearized polynomials is also proposed for KK codes in [44]. It was shown in [46] that KK codes correspond to lifting of Gabidulin codes, a class of optimal rank metric codes. As a result, KK codes can be decoded by the generalized decoding algorithm for the rank metric codes [46].

Motivated by KK codes, a new family of subspace codes, referred to as Mahdavifar-Vardy (MV) codes in this paper, was proposed [47–49]. List decoding, which has been used to decode beyond the error correction diameter bound [50], can be applied to the decoding of MV codes. Using algebraic list decoding, it was shown [49] that MV codes can achieve a better tradeoff between rate and decoding radius than KK codes.

Error control for RLNC comes at the expense of additional computations needed for encoding and decoding. The complexities of existing decoding algorithms [44, 49, 51] for KK and MV codes are much higher than those of encoding, and are hence critical to applications of RLNC. Most previous works focus on theoretical aspects of network coding. For example, the decoding complexities of KK and MV codes were analyzed in [44, 46] and [47–49], respectively. However, theoretical analysis does not completely reflect how the decoding algorithms affect the hardware implementation results, such as area and throughput. For KK codes, decoder architectures based on the generalized decoding algorithm for rank metric codes [46] was proposed in [43]. Unfortunately, the rank metric decoder architectures in [43] suffer from limited throughput, long decoding latency and high area complexity. Besides, to the best of our knowledge, decoder architectures for MV codes and their hardware implementations have not been investigated in the open literature.

#### 1.2 Contributions and Organization

This dissertation has the following contributions and is organized as follows.

• In Chapter 2, the shuffled decoding algorithm and its corresponding decoder

architecture are investigated. Our main contributions of this chapter are twofold. First, we propose a shuffled schedule (SS) of the Min-Max algorithm for NB-LDPC codes. To reduce the memory requirement and improve the throughput, we also propose a modified shuffled schedule (MSS), which employs a novel shuffle sort (SST) algorithm to reduce the complexity of check node processing significantly. Our simulation results show that both the SS and MSS converge faster and have slightly better error performance than the flooding schedule, and that the degradation of the MSS in error performance as well as convergence rate is negligible. The simulation results also show that the error performance of the MSS and layered schedule are almost the same. Second, an efficient shuffled decoder architecture for NB QC-LDPC codes is proposed based on the Min-Max algorithm using the modified shuffled schedule. The proposed architecture has a similar top structure to other partly parallel decoder architectures for binary and nonbinary LDPC codes. However, it has several key novelties: 1) its underlying modified shuffled schedule is novel; 2) on-the-fly computation and hardware re-usage have been used to reduce memory consumption and to improve the throughput; 3) a random memory address generator (RMAG) has been employed in the check node unit (CNU) to reduce the number of cycles required by CNP; 4) since the variable node unit (VNU) becomes complex for decoders storing only the  $n_m$ most reliable values, the variable-to-check messages are stored in an improved way so as to simplify the message access.

• In Chapter 3, a fully parallel decoder architecture based on the proposed decoding algorithm is also proposed. The main contributions of this paper are

as follows:

- 1. Based on the Min-Max algorithm, a reduced memory complexity trellis based check node processing (RTBCP) algorithm is proposed.

- 2. A simplified algorithm is proposed to reduce the computational complexity of variable node processing (VNP). As a result, compared with the RHS algorithm in [2], a stochastic decoder, the proposed decoding algorithm needs fewer real multiplications but more real comparisons and finite field additions.

- 3. For each a priori message, all LLRs except several most reliable ones are approximated with a linear function. Two kinds of low complexity LLR generation units are also proposed for the approximation of the check-to-variable (c-to-v) LLR and a priori LLR, respectively. With 5-bit quantization scheme and  $n_m = 32$ , the areas of the two LGUs are 10.7% and 13.3%, respectively, of that of an SRAM which stores an LLR vector under a 90nm CMOS technology. A similar approach was proposed in [52] to approximate a priori LLR. The main differences between our work and that in [52] are as follows:

- Besides the approximation of channel LLR vectors, we try to approximate check-to-variable LLR vectors.

- A simplified variable node processing (SVNP) algorithm is proposed to compensate the performance degradation caused by LLR approximation.

- 4. A parallel check node unit (CNU) and a low-latency variable node unit (VNU) are proposed. Based on the proposed CNU and VNU, an efficient

fully parallel decoder architecture is also proposed. A fully parallel NB-LDPC decoders based on GF(256) is implemented with 28nm CMOS technology. The decoder over GF(256) achieves a throughput of 546Mb/s and an energy efficiency of 0.178nJ/b/iter.

Since routing congestion tends to be challenging for fully parallel LDPC decoder architectures, the proposed decoder architecture is not suitable for very long LDPC codes. The proposed fully parallel decoder architecture is particularly advantageous for NB-LDPC codes over large fields, since the memory reduction will be more significant when  $n_m$  is large.

- In Chapter 4, we focus on efficient architectures and their hardware implementations of interpolation based decoders for KK and MV codes. The main contributions of this paper are:

- 1. The decoder of KK codes has two stages: interpolation and factorization. The generalized interpolation algorithm in [51] is used for the first stage since it is more efficient than Gaussian elimination [51]. For factorization, we propose a reformulated right division algorithm for linearized polynomials, which is suitable for hardware implementations.

- 2. The list decoder of MV codes also has two stages: interpolation and factorization. The generalized interpolation algorithm in [51] is used in the interpolation process. A linearized Roth-Ruckenstein (LRR) algorithm [53] is proposed in [47] to solve the factorization problem for MV codes. In this paper, we make a more detailed study on the LRR algorithm. For list size L=2, we derive the equations used to compute all

- the information symbols and uncover the relation between two possible solutions. A matrix based LRR (M-LRR) algorithm, which is suitable for hardware implementations, is also proposed for factorization.

- 3. A serial decoder architecture and an unfolded decoder architecture for KK codes are proposed for applications with moderate and high throughputs, respectively. Both architectures are implemented for KK codes over GF(2<sup>8</sup>) and GF(2<sup>16</sup>) to demonstrate their efficiency. To the best of our knowledge, this is the first efficient implementation of interpolation-based decoder for KK codes. Compared to the rank metric decoder architectures for KK codes [43], the proposed serial decoder architecture improves the throughput by 4.9 and 13.2 times, while its gate counts are only 56% and 76% of their respective counterparts in [43]. Moreover, for these two codes, the unfolded architecture achieves a throughput of 12.5Gb/s and 41.6Gb/s, much higher than the throughput of 214Mb/s and 134Mb/s of their respective counterparts in [43]. The throughputs per thousand NAND gates of our architectures are much higher and their latency much shorter than their counterparts in [43].

- 4. A serial list decoder architecture for MV codes is proposed. To the best of our knowledge, this is the first hardware implementation of MV decoders. An efficient architecture for solving equations over an extension field  $GF(q^{ml})$  (q > 2 is moderate) is proposed. The proposed equation solver does not require complicated inversion operations over  $GF(q^{ml})$ . Besides, an implementation of factorization that computes all L possible transmitted packets in parallel is proposed, where L is the list size for

list decoding.

- In Chapter 5, we propose the first hardware implementation of the CA-SCL algorithm to the best of our knowledge. Based on both algorithmic and architectural improvements, our decoder architecture achieves better error performance and higher area efficiency compared with the decoder architecture in [31]. Specifically, the major contributions of this work are:

- 1. Message memories account for a significant fraction of an SC or SCL decoder [20,31]. In this chapter, an area efficient message memory architecture is proposed. Besides, a new compression method for the channel messages is used to reduce the area of the proposed decoder architecture.

- 2. An efficient processing unit (PU) is proposed. For the proposed list decoder architecture, a fine grained PU profiling (FPP) algorithm is proposed to determine the minimum quantization size of each input message for each PU so that there is no message overflow. By using the quantization size generated by the FPP algorithm for each PU, the overall area of all PUs is reduced.

- 3. An efficient scalable path pruning unit (PPU) is proposed to control the copying of decoding paths. Based on the proposed memory architecture and the scalable PPU, our list decoder architecture is suitable for large list sizes.

- 4. A low-complexity direct selection scheme is proposed for the CA-SCL algorithm when a strong CRC is used (e.g. CRC32). The proposed direct selection scheme simplifies the selection of the final output data

word.

- 5. For a (1024, 512) rate- $\frac{1}{2}$  polar code, the proposed list decoder architecture is implemented for list size L=2 and 4, respectively, under a 90nm CMOS technology. Compared with the decoder architecture in [31] synthesized under the same technology, our decoder achieves 1.24 to 1.83 times area efficiency (throughput normalized by area). Besides, the proposed CA-SCL decoder has better error performance compared with the SCL decoder in [31].

- In Chapter 6, a tree based reduced latency list decoding algorithm and its corresponding high throughput hardware architecture are proposed for polar codes. The main contributions are:

- A tree based reduced latency list decoding (RLLD) algorithm over logarithm likelihood ratio (LLR) domain is proposed for polar codes. Inspired by the simplified successive cancelation (SSC) [30] decoding algorithm and the ML-SSC algorithm [54], our RLLD algorithm performs the SC based list decoding on a binary tree. Previous SCL decoding algorithms visit all the nodes in the tree and consider all possibilities of the information bits, while our RLLD algorithm visits much fewer nodes in the tree and consider fewer possibilities of the information bits. When configured properly, our RLLD algorithm significantly reduces the decoding latency and hence improves throughput, while introducing little performance degradation.

Based on our RLLD algorithm, a high throughput list decoder architecture is proposed for polar codes. Compared with the state-of-arts SCL decoders in [32, 33, 36], our list decoder achieves lower decoding latency and higher area efficiency (throughput normalized by area).

More specifically, the major innovations of the proposed decoder architecture are:

- An index based partial sum computation (IPC) algorithm is proposed to avoid copying partial sums directly when one decoding path needs to be copied to another. Compared with the lazy copy algorithm in [55], our IPC algorithm is more hardware friendly since it copies only path indices, while the lazy copy algorithm needs more complex index computation.

- Based on our IPC algorithm, a hybrid partial sum unit (Hyb-PSU) is proposed so that our list decoder is suitable for larger block lengths. The Hyb-PSU is able to store most of the partial sums in area efficient memories such as register file (RF) or SRAM, while the partial sum units (PSUs) in [31–33] store partial sums in registers, which need much larger area when the block length N is larger. Compared with the PSU of [32], our Hyb-PSU achieves an area saving of 23% and 63% for block length  $N = 2^{13}$  and  $2^{15}$ , respectively, under the TSMC 90nm CMOS technology.

- For our RLLD algorithm, when certain types of nodes are visited, each current decoding path splits into multiple ones, among which the L most reliable paths are kept. In this paper, an efficient path pruning unit (PPU) is proposed to find the L most reliable decoding paths among

- the split ones. For our high throughput list decoder architecture, the proposed PPU is the key to the implementation of our RLLD algorithm.

- For the fixed-point implementation of our RLLD algorithm, a memory efficient quantization (MEQ) scheme is used to reduce the number of stored bits. Compared with the conventional quantization scheme, our MEQ scheme reduces the number of stored bits by 17%, 25% and 27% for block length  $N=2^{10}$ ,  $2^{13}$  and  $2^{15}$ , respectively, at the cost of slight error performance degradation.

## Chapter 2

# An Efficient Shuffled Decoder Architecture for Nonbinary Quasi-Cyclic LDPC Codes

#### 2.1 Introduction

Binary low-density parity-check (LDPC) codes are more and more popular in applications because of their capacity-approaching performance. In terms of performance, binary LDPC codes start to show their weaknesses when the code word length is small or moderate, or when higher order modulation is used for transmission. For these cases, nonbinary LDPC (NB-LDPC) codes over high order Galois fields have shown great potential [3,4]. For instance, in [1], a rate-1/2 NB-LDPC code of length 84 over GF(64) is shown to perform 0.375dB better than a rate-1/2 binary irregular LDPC code of equivalent length 504 bits in [5] over binary input

additive white Gaussian noise (AWGN) channel. Over the QAM-AWGN channels, NB-LDPC codes with a field order greater than or equal to the size of constellation have the advantage that the encoder/decoder works directly with symbols. All mapping choices of the codeword symbols to the constellation points are equivalent and lead to the same performance. In [1], an NB-LDPC code over GF(256) performs 0.5dB better than a rate-1/2 binary LDPC codes of the equivalent length 1008 bits over QAM256-AWGN channel.

A significant obstacle to the application of NB-LDPC codes is that their decoding algorithms are of high complexity. Hence, a lot of research effort has been spent on efficient decoding algorithms for NB-LDPC codes [3, 6, 56–58]. Among them, the EMS [58] and the Min-Max [6] algorithms draw the most attention because their low computation and memory complexity. Both the EMS and the Min-Max algorithms can store only the  $n_m$  ( $n_m \ll q$ ) most reliable messages, thus reducing the memory requirement at the cost of small performance degradation. The check node processing of the EMS algorithm needs addition and comparison operations, while the Min-Max algorithm needs only maximization and comparison in check node processing. The trellis-based check node processing (TBCP) algorithm [7] reduces the computational complexity of check node processing (CNP) of the Min-Max algorithm by eliminating unnecessary check-to-variable messages from CNP.

Recently, a considerable amount of research effort has already been spent on efficient decoder architectures for NB-LDPC codes [7, 10, 11, 15, 59] based on the EMS or the Min-Max algorithm. The existing NB-LDPC decoders still suffer from low throughput and large hardware complexity. For example, a (248, 124) NB-LDPC decoder over GF(32) [15] achieves a throughput of 47.69 Mb/s at the cost of

10.33 mm<sup>2</sup> silicon area under 90nm technology, while a (1200, 720) binary LDPC decoder [60] achieves a throughput of 5.92 Gb/s at the cost of 13.5 mm<sup>2</sup> silicon area under 180nm technology.

The main contributions of this chapter are two-fold. First, we propose a shuffled schedule (SS) of the Min-Max algorithm for NB-LDPC codes. To reduce the memory requirement and improve the throughput, we also propose a modified shuffled schedule (MSS), which employs a novel shuffle sort (SST) algorithm to reduce the complexity of check node processing significantly. Our simulation results show that both the SS and MSS converge faster and have slightly better error performance than the flooding schedule, and that the degradation of the MSS in error performance as well as convergence rate is negligible. The simulation results also show that the error performance of the MSS and layered schedule are almost the same. Second, an efficient shuffled decoder architecture for NB QC-LDPC codes is proposed based on the Min-Max algorithm using the modified shuffled schedule. The proposed architecture has a similar top structure to other partly parallel decoder architectures for binary and nonbinary LDPC codes. However, it has several key novelties: 1) its underlying modified shuffled schedule is novel; 2) on-the-fly computation and hardware re-usage have been used to reduce memory consumption and to improve the throughput; 3) a random memory address generator (RMAG) has been employed in the check node unit (CNU) to reduce the number of cycles required by CNP; 4) since the variable node unit (VNU) becomes complex for decoders storing only the  $n_m$  most reliable values, the variable-to-check messages are stored in an improved way so as to simplify the message access.

For NB-LDPC codes, a shuffled schedule for the EMS algorithm was proposed

in [1], and a shuffled schedule and a probabilistic shuffled schedule for the belief propagation were proposed in [61]. The work herein differs from the previous works in [1,61] in three aspects. First, while the works in [61] and [1] focus on the belief propagation and EMS decoding of NB-LDPC codes, respectively, our work considers the Min-Max algorithm. Second, while our shuffled schedule is similar to those in [1,61], our modified shuffled schedule with reduced-complexity check node processing is novel. Third, while the works in [1,61] focus on decoding algorithms, this work considers not only decoding algorithms but also decoder architectures as well as their hardware implementations.

For binary LDPC codes, a layered decoder architecture tends to be more efficient than a shuffled decoder architecture. This is because both the CNP and variable node processing (VNP) are relatively simple. However, for NB-LDPC codes, layered decoder architectures [7,15,59] have several drawbacks. First, The check node processing of existing decoding algorithms for NB-LDPC codes is complex and requires many cycles to finish. Processing the rows serially in the layered fashion requires more cycles than processing all rows at the same time. Second, the variable node processing for NB-LDPC codes is also complex compared to that of binary LDPC codes. A round of variable node processing for a variable node takes  $2n_m$  cycles for the nonbinary layered decoder architecture in [7]. Third, for layered decoder architectures, the variable node processing may be performed several times for one variable node during an iteration, leading to lower throughput. In contrast, the shuffled decoder architecture proposed in this chapter processes all rows concurrently and needs only a round of variable node processing for all variable nodes during an iteration. This reduces the number of cycles needed for an iteration.

#### 2.2. BACKGROUND

The shuffled schedule has also been used in decoder architectures for binary LDPC codes (see, e.g., [62]). However, each check to variable (c-2-v) or variable to check (v-2-c) message is a vector for NB-LDPC codes, whereas each c-2-v or v-2-c message is just a single log likelihood ratio (LLR) for binary codes. This fundamental difference also leads to higher complexities for decoder architectures of NB-LDPC codes than their binary counterparts. The key novelties mentioned above also apply when comparing the proposed architecture herein with that in [62].

The rest of this chapter is organized as follows. Section 2.2 briefly reviews the TBCP algorithm. Section 2.3 proposes the shuffled and modified shuffled schedule and presents our simulation results. Our decoder architecture and the hardware implementation results are presented in Section 2.4. The conclusion is drawn in Section 2.5.

## 2.2 Background

Consider check node m and variable node n in the Tanner graph [63] defined by H, respectively. Let M(n) denote the set of neighboring check nodes connected to n, and N(m) the set of variable nodes connected to m. For  $a \in GF(q)$ , let  $L_n(a)$  be the a priori information of variable node n concerning the symbol a and  $Q_n(a)$  be the posteriori information of the same symbol.  $R_{m,n}(a)$  and  $Q_{m,n}(a)$  denote the messages passed from m to n and from n to m concerning a, respectively. Let  $c_n$  be the (n + 1)-th coordinate of a codeword and  $s_n$  be the most likely symbol for  $c_n$ . The Min-Max decoding algorithm [6] can be formulated as follows, where  $I_{\text{max}}$  denotes the maximal number of iterations and  $A(m|a_n = a) \stackrel{\text{def}}{=} \{(a_j)(j \in a_n) \mid a_n \in a_n\}$

#### 2.2. BACKGROUND

Figure 2.1: Messages sent form check node to variable node

$$N(m) \setminus \{n\}$$

)|  $\sum_{j \in N(m) \setminus \{n\}} h_{m,j} a_j + h_{m,n} a = 0$ }:

#### **Algorithm 1:** Min-Max Algorithm [6]

```

Initialization:

```

```

L_{n}(a) = \ln(\Pr_{r}(c_{n} = s_{n} | \text{channel})) \Pr_{r}(c_{n} = a | \text{channel}))

Q_{m,n}(a) = L_{n}(a) \ (0 \le m < M, 0 \le a < q), i = 0

Iteration:

while HC \ne 0 and i < I_{max} do

\text{check node Processing:}

R_{m,n}(a) = \min_{(a_{j}) \in A(m | a_{n} = a)} (\max_{j \in N(m) \setminus \{n\}} Q_{m,j}(a_{j}))

variable node processing:

Q'_{m,n}(a) = L_{n}(a) + \sum_{m' \in M(n)} R_{m',n}(a)

Q'_{m,n} = \min_{a \in GF(q)} Q_{m,n}(a)

Q_{m,n}(a) = Q'_{m,n}(a) - Q'_{m,n}

tentatively decoding:

c_{n} = \operatorname{argmin}(Q_{m,n}(a))

i = i + 1

```

The Min-Max algorithm stores the  $n_m$  most reliable messages. Suppose there are n variable nodes connected with check node c. The truncated messages sent from n variable nodes to check node c are shown in Fig. 2.1, where  $q_{v,c}(k)$  is an LLR value and  $qs_{v,c}(k) \in GF(q)$ , where GF(q) is a finite field with q elements. Each v-2-c message contains  $n_m$  LLRs and  $n_m$  associated field symbols.

Normally, the CNP is performed in a forward-backward way [6], which is memory

#### 2.2. BACKGROUND

demanding. The TBCP algorithm [7] eliminates unnecessary v-2-c messages from CNP, thus reducing the memory consumption. The TBCP algorithm first sorts these  $n(n_m-1)$  nonzero LLRs in non-decreasing order as  $x_c(1), x_c(2), \dots, x_c(X)$ , and only the X smallest ones are kept. Their associated field symbols are  $\alpha_c(1), \alpha_c(2), \dots, \alpha_c(X)$ , and they belong to variable nodes with indices  $e_c(1), e_c(2), \dots, e_c(X)$ . A path construction (PC) algorithm shown in Algorithm 2 is proposed in [7] to compute the truncated c-2-v message:  $r_{c,v}$  and  $r_{c,v}$ , where  $r_{c,v}$  is the  $n_m$ -dimension LLR vector and  $r_{c,v}$  is the associated field symbol.

```

\begin{aligned} & \textbf{algorithm 2: PC Algorithm } [7] \\ & \textbf{input} : x_c(i), \alpha_c(i), e_c(i) \ i = 1, \cdots, X; \ z_c(v) \ v = 0, \cdots, d_c - 1; \ \alpha_{sum} \\ & \textbf{output: } r_{c,v}(j), rs_{c,v}(j) \ \text{ for } j = 0, \cdots, n_m - 1 \end{aligned}   \begin{aligned} & \textbf{Initialization:} \\ & r_{c,v}(0) = 0, rs_{c,v}(0) = \alpha_{sum} \oplus z_c(v), i = 1, cnt = 1, P_{c,0} = [0, 0, \cdots, 0] \\ & \textbf{while } cnt < n_m \ \textbf{do} \end{aligned}   \begin{aligned} & \textbf{if } e_c(i) \neq v \ \textbf{then} \\ & j = cnt \\ & \textbf{for } k = 0 \ to \ j - 1 \ \textbf{do} \end{aligned}   \begin{aligned} & a = rs_{c,v}(k) \oplus z_c(e_c(i)) \oplus \alpha_c(i) \\ & \textbf{if } P_{c,k}(e_c(i)) \neq 1 \ \textbf{for } \alpha \not\in rs_{c,t} \ \textbf{then} \end{aligned}   \begin{aligned} & r_{c,v}(cnt) = x_c(i); rs_{c,v}(cnt) = \alpha \\ & P_{c,cnt}(e_c(i)) = 1 \\ & P_{c,cnt}(s) = P_{c,k}(s) \ \text{for } s \neq e_c(i) \\ & cnt = cnt + 1 \end{aligned}

```

As shown in Algorithm 2,  $z_c(v) = \alpha_{c,v}(0)$ ,  $v = 1, \dots, n$  and  $\alpha_{sum} = \sum_{k=1}^n z_c(j)$ .  $P_{c,k}$  is an *n*-dimension vector over GF(2) which stores the constructed path.  $\oplus$  denotes addition over GF(q). The constructed  $n_m$  LLRs are picked from the sorted list  $x_c(i)$ , and stored in  $r_{c,v}$ . Their associated field symbols are stored in  $r_{c,v}$ .

#### 2.3. SHUFFLED AND MODIFIED SHUFFLED SCHEDULE

is set to  $1.5n_m$  [7] so that the decoding performance could be maintained. It takes  $2n_m$  iterations to compute  $r_{c,v}$ ,  $r_{c,v}$  [7].

## 2.3 Shuffled and Modified Shuffled Schedule

#### 2.3.1 Shuffled Schedule

Suppose H is divided into G block columns:  $H = [H_0 \ H_1 \ ... \ H_{G-1}]$ , where  $H_i$  is an  $M \times g$  sub-matrix and g = N/G. Let M(n) denote the set of neighboring check nodes connected to n, and N(m) denote the set of variable nodes connected to m. Let  $I_v(i), S_v(i)$  for  $i = 0, \dots, n_m - 1$  denote an  $n_m$ -ary a priori message, where  $I_v$  is the LLR vector and  $S_v$  is the corresponding field symbol vector, respectively. Let  $\mathrm{CM}_{c,l}^{(k)}(i) = (x_{c,l}^{(k)}(i), \alpha_{c,l}^{(k)}(i), e_{c,l}^{(k)}(i))$  for  $i = 1, \dots, X$ , which are the inputs of the PC algorithm [7] when computing updated c-2-v messages within block column l in iteration k. Let  $(q_{v,c}^{(k)}, qs_{v,c}^{(k)})$  and  $(r_{c,v}^{(k)}, rs_{c,v}^{(k)})$  denote a v-2-c and c-2-v message in iteration k, respectively. Suppose the row weight for each  $H_i$  is exactly 1, which can be easily satisfied by QC-LDPC codes. The proposed shuffled schedule is shown in Algorithm 3.

During the initialization step, for each check node c, the init\_sort (IS) algorithm sorts out X LLR values in a non-decreasing order from incoming  $d_c(n_m - 1)$  v-2-c message elements, where  $d_c$  is the corresponding check node degree. The IS algorithm is shown in Algorithm 4, where  $n = d_c$ ; t, ts and ti are all X-dimension vectors.

The block\_vnp(l) function in Algorithm 3 computes the corresponding  $q_{v,c}^{(k+1)}$ ,

#### 2.3. SHUFFLED AND MODIFIED SHUFFLED SCHEDULE

#### Algorithm 3: Shuffled Schedule

#

#### **Algorithm 4:** IS Algorithm

$qs_{v,c}^{(k+1)}$  messages within block l. Take variable node v as an example. The q-ary message  $Q_{v,c}$  are firstly computed as  $Q_{v,c}(s) = L_v(s) + \sum_{c' \in M(j) \setminus c} R_{c',v}(s)$  for  $s = 0, 1, \dots, q-1$ . Here,  $L_v(s) = I_v(i)$  if  $S_v(i) = s$ , otherwise  $L_v(s) = I_v(n_m-1)$  which is maximum of  $I_v$ . Besides,  $R_{c',v}(s) = r_{c',v}^{(k+1)}(i_{c'})$  if  $rs_{c',v}^{(k+1)}(i'_c) = s$ , otherwise  $R_{c',v}(s) = r_{c',v}^{(k+1)}(n_m-1)$ . Finally,  $q_{v,c}^{(k+1)}$  and  $qs_{v,c}^{(k+1)}$  are computed by sorting  $Q_{v,c}$ .

### 2.3.2 Modified Shuffled Schedule

For the shuffled schedule in Algorithm 3, the computation of  $CM_{c,l+1}^{(k)}$  employ the IS algorithm, which needs  $(d_c - 1)X$  comparisons. Thus,  $d_c(d_c - 1)X$  comparisons are needed for computing all  $CM_{c,l}^{(k)}$  during an iteration. Besides, all v-2-c messages need to be stored. This results in low throughput as well as a significant memory requirement. Instead, we propose a modified shuffled schedule (MSS) which uses a shuffled sort (SST) algorithm to compute  $CM_{c,l+1}^{(k)}$  as shown in Algorithm 5.

```

Algorithm 5: SST Algorithm input : (q_{v,c}^{(k+1)}, q_{v,c}^{(k+1)}, l), CM_{c,l}^{(k)}

output: CM_{c,l+1}^{(k)}

a = 1, b = 1, c = 1

for x = 0 to n_m + X - 2 do

| if e_{c,l}^{(k)} == l then b = b + 1; continue

if c == X + 1 then break

```

The proposed SST algorithm needs at most  $n_m + X - 1$  comparisons to compute  $CM_{c,l+1}^{(k)}$  based on  $CM_{c,l}^{(k)}$  and  $(q_{v,c}^{(k+1)}, q_{v,c}^{(k+1)})$ . It only takes at most  $(d_c - 1)X + (d_c - 1)X$  $1)(n_m + X - 1) = (d_c - 1)(n_m + 2X - 1)$  comparisons to compute all  $CM_{c,l}^{(k)}$  during an iteration. Besides, only  $(q_{v,c}^{(k+1)}, q_{v,c}^{(k+1)})$  need to be stored. As a result, compared to the shuffled schedule in Algorithm 3, the MSS using the SST algorithm needs fewer comparisons and less memory.

#### 2.3.3Simulation Results

Fig. 2.2 shows the frame error rate (FER) performance of the FFT-BP algorithm and the Min-Max algorithm with flooding schedule, shuffled and modified shuffled schedule as well as the layered schedule for three NB-LDPC codes on GF(32) [64] over the AWGN channel with BPSK modulation. For our simulations,  $I_{max} = 30$ ,  $n_m = 16$ , and  $X = 1.5 n_m = 24$  for the SS and MSS. The flooding and layered

#### 2.3. SHUFFLED AND MODIFIED SHUFFLED SCHEDULE

Figure 2.2: FERs of selected codes

Figure 2.3: Comparison of convergence rates

#### 2.3. SHUFFLED AND MODIFIED SHUFFLED SCHEDULE

schedule also use the TBCP algorithm in CNP. For all three codes, the error performance with the MSS and SS is slightly better than that with the flooding schedule. The layered schedule, the SS, and the MSS have nearly the same error performance, which implies that the MSS results in little or no error performance degradation.

We also compare the convergence speed of the MSS, SS and layered schedule with the flooding schedule in Fig. 2.3. Here IR0 =  $N_{\rm mss}/N_f$ , IR1 =  $N_{\rm ss}/N_{\rm mss}$  and LR =  $N_l/N_f$ , where  $N_{\rm ss}$ ,  $N_{\rm mss}$ ,  $N_f$  and  $N_l$  are the average numbers of iterations of the SS, the MSS, the flooding and layered schedule, respectively. Several observations can be made about Fig. 2.3. First, throughout the SNR range, IR0 < 1 and IR1  $\approx$  1. Thus, the MSS results in no degradation in convergence speed compared with the SS, and both the MSS and SS converge faster than the flooding schedule. Second, when FER is around  $10^{-4}$ , the average number of iteration of the MSS is only 60% - 70% of that of the flooding schedule. Third, IR0 and LR start to grow in high SNR region, since even the flooding schedule converge very fast at high SNR. Thus the advantage of the MSS and SS in convergence speed decreases when the SNR is high. The same phenomenon was observed in [61].

As shown in Fig. 2.3, the layered schedule requires fewer iterations for the simulated codes than the MSS and SS, especially when the SNR is high. However, in a hardware implementation, the MSS results in fewer clock cycles per iteration than the layered schedule for two reasons. First, all rows can be processed at the same time for the MSS, while only a block of rows can be processed concurrently for the layered schedule. Second, the proposed MSS with the shuffled sort algorithm simplifies the CNP after init\_sort is finished. In order to update the c-2-v messages in one block column, only the updated v-2-c messages in the previous block column and

Figure 2.4: CNU Architecture

old CMs are needed. As a result, the number of real value comparisons is reduced.

## 2.4 Shuffled Decoder Architecture

In this section, a shuffled decoder architecture with reduced memory consumption and higher throughput is proposed for nonbinary QC-LDPC codes whose parity check matrices consist of sub-matrices that are either the zero or shifted identity matrices with nonzero entries replaced by elements of GF(q), where  $q = 2^p$ .

#### 2.4.1 Check Node Unit Architecture

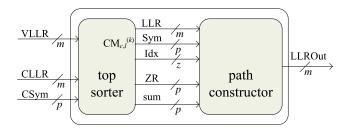

The architecture of the proposed CNU which includes a top sorter and a path constructor is shown in Fig. 2.4, where m denotes the quantization bits of an LLR message and  $z = \lceil \log_2 d_c \rceil$ . The top sorter provides corresponding inputs for the path constructor which implements Algorithm 2. Take check node c as an example, the top sorter in Fig. 2.4 computes  $CM_{c,0}^{(0)}$  using the IS algorithm at the initialization step. It also computes  $CM_{c,l+1}^{(k)}$  for  $l = 0, 1, \dots, G-1$  using the SST algorithm during the iteration process. Once  $CM_{c,l}^{(k)}$  is available, the path constructor computes updated c-2-v messages within block column l using Algorithm 2.

The architecture of the proposed top sorter is shown in Fig. 2.5. It consists

Figure 2.5: Architecture of Proposed Top Sorter

Figure 2.6: Proposed RMAG Architecture

of a parallel porter (PS), two  $X \times (m+p+z)$ -bits RAMs (RAM0 and RAM1) used to store  $CM_{c,l}^{(k)}$ , and a random memory address generator (RMAG). Each word of RAM0 and RAM1 stores an LLR value, the associated field symbol and index. At the initialization step, the computation of  $CM_{c,0}^{(0)}$  is carried out in  $d_c$  rounds. In the first round,  $q_{v_1,c}^{(0)}$  and  $q_{v_1,c}^{(0)}$  are copied into the corresponding location of RAM0. Besides, the index values of each word of RAM0 are set to 1. In the second round, the temp results  $T_{c,0}^{(0)}$  as shown in Algorithm 4 is stored in RAM1. In the next round,  $T_{c,0}^{(0)}$  will be stored in RAM0. This repeats until  $CM_{c,0}^{(0)}$  is computed.

The computation of  $CM_{c,l+1}^{(k)}$  can be implemented in the same way as the computation of  $CM_{c,0}^{(0)}$ . However, extra cycles are spend on testing whether  $e_{c,l}^{(k)} = l$  as shown in Algorithm 5. Under the worst condition,  $n_m - 1$  cycles are used on the index testing. As shown in Fig. 2.6, a random memory address generator is proposed to eliminate the cycles used in index testing during the computing of  $CM_{c,l+1}^{(k)}$ . As a result, only X cycles are needed for the computation of  $CM_{c,l+1}^{(k)}$ . Assuming X = 5, suppose we need to compute  $CM_{c,1}^{(0)}$ , and  $CM_{c,0}^{(0)}$  is stored in RAM0. Suppose  $e_{c,0}^{(0)}(1) = e_{c,0}^{(0)}(3) = 0$ . Then the RMAG generates a read address sequence (0, 2, 4). The RMAG first stores a binary sequence  $S_l = (s_1, s_2, \dots, s_X)$ , where  $s_i = 1$

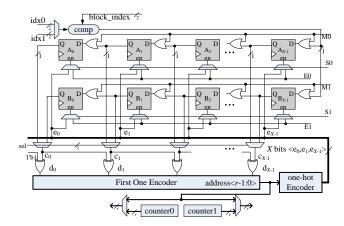

The RMAG first stores a binary sequence  $S_l = (s_1, s_2, \dots, s_X)$ , where  $s_i = 1$  if  $e_{c,l}^{(k)}(i) = l$ , otherwise  $s_i = 0$ . Then,  $S_l$  is used to generate the read address sequence for the computation of  $CM_{c,l+1}^{(k)}$ . As shown in Fig. 2.6, at the initiation step,  $S_0$  is computed and stored in registers  $A_0, A_1, \dots, A_{X-1}$ , which are used to generate read address sequence when computing of  $CM_{c,1}^{(0)}$ . Meanwhile,  $S_1$  are stored in  $B_0, B_1, \dots, B_{X-1}$ , which are used in the computation of  $CM_{c,2}^{(0)}$ . This repeats until the decoding of a codeword is finished. The First One Encoder outputs the smallest i such that  $d_i = 1$ . The one-hot Encoder (OE) in Fig. 2.6 outputs a binary sequence  $(e_0, e_1, \dots, e_{X-1})$ , where  $e_x = 1$ .  $e_j = 0$  if  $j \neq x$ . Here x is the decimal value of the input of OE.